(19) **日本国特許庁(JP)**

(51) Int. Cl.

# (12) 特 許 公 報(B2)

FL

(11) 特許番号

特許第5010164号 (P5010164)

(45) 発行日 平成24年8月29日(2012.8.29)

(24) 登録日 平成24年6月8日(2012.6.8)

\_\_\_\_\_

GO6F 9/46 (2006.01)

GO6F 9/46 350

請求項の数 8 (全 35 頁)

(21) 出願番号 特願2006-97594 (P2006-97594)

審查請求日

(22) 出願日 平成18年3月31日 (2006.3.31)

(65) 公開番号 特開2007-272576 (P2007-272576A) (43) 公開日 平成19年10月18日 (2007.10.18)

平成20年10月16日 (2007.10.16)

||(73)特許権者 000005108

株式会社日立製作所

東京都千代田区丸の内一丁目6番6号

||(74)代理人 100114236

弁理士 藤井 正弘

(74)代理人 100075513

弁理士 後藤 政喜

|(74)代理人 100084537

弁理士 松田 嘉夫

(72) 発明者 服部 直也

東京都国分寺市東恋ヶ窪一丁目280番地

株式会社日立製作所 中央研究所内

||(72)発明者 森本 俊臣

東京都国分寺市東恋ヶ窪一丁目280番地 株式会社日立製作所 中央研究所内

最終頁に続く

(54) 【発明の名称】サーバ装置及び仮想計算機の制御プログラム

### (57)【特許請求の範囲】

## 【請求項1】

一つ以上のCPUと、データ及びプログラムを格納するメモリと、外部とでデータを送 受信するインターフェースと、を備えたサーバ装置において、

前記 CPUが前記メモリに格納されたプログラムを実行することによって、オペレーティングシステムが稼働する一以上の仮想計算機を稼働させる仮想計算機モニタが実行されており、

前記オペレーティングシステム又は前記オペレーティングシステム上で稼働するアプリケーションは、所定の処理の実行を要求する操作コードを出力し、

前記CPUは、ハードウェア操作許可モードとハードウェア操作禁止モードとの二つの動作モードを備え、

前記仮想計算機モニタは、

前記オペレーティングシステム又は前記オペレーティングシステム上で稼働するアプリケーションから前記サーバ装置のハードウェアに対する操作を要求するハードウェア操作コードを含む前記操作コードが出力されたときに、前記ハードウェア操作コードに基づいて前記サーバ装置のハードウェアに対する操作をエミュレーションするエミュレーションモジュールと、

前記ハードウェア操作コードを検出することによって前記CPUが発生させる例外イベントを契機として、前記CPUの前記動作モードを前記ハードウェア操作許可モードに切り替え、前記エミュレーションモジュールを呼び出す例外イベントハンドラモジュールと

20

前記 CPUの前記動作モードを前記ハードウェア操作許可モードに切り替え、前記エミュレーションモジュールを呼び出す変換コードを管理するコード管理モジュールと、

<u>前記操作</u>コードに対応する<u>前記変換コード</u>を生成し、前記操作コード<u>及び</u>前記生成された変換コードを対応づけて前記メモリ上に格納する生成モジュールと、

所定の判断条件との比較の結果、<u>前記操作コードに含まれる</u>前記ハードウェア操作コードの実行頻度が高頻度であるか否かを判断する頻度判断モジュールと、

前記実行頻度の判断の結果に基づいて、前記ハードウェア操作コードを含む前記操作コードに対して、前記CPUが前記例外イベントを発生させ、前記操作コードの実行の強制中断処理を終了した後に実行される前記例外イベントハンドラモジュールによって前記エミュレーションモジュールを呼び出す<u>VT方式、又は、前記ハードウェア操作コードを含む</u>前記操作コードに対応する前記<u>変換コード</u>を実行することによって前記エミュレーションモジュールを呼び出す<u>コード変換方式のいずれの動作方式を適用するか</u>を決定する切り替えモジュールと、を備え、

前記変換コードは、前記 C P U の前記動作モードを前記ハードウェア操作禁止モードから前記ハードウェア操作許可モードに切り替え、前記ハードウェア操作コードをエミュレーションさせる昇格コードと、前記昇格コードを含むシャドウコードとから構成され、

<u>前記コード管理モジュールは、前記ハードウェア操作コード及び前記変換コードを対応</u> づけた変換コード表を保持し、

前記切り替えモジュールは、前記ハードウェア操作コードを含む前記操作コードと、当該操作コードに対して適用される前記動作方式とを対応づけた動作方式表を保持し、

前記仮想計算機モニタは、

前記動作方式表を参照して、前記ハードウェア操作コードを含む前記操作コードに適用 される前記動作方式を判断し、

前記ハードウェア操作コードを含む前記操作コードの前記動作方式がVT方式である場合、前記例外イベントを発生させ、前記CPUの動作モードをハードウェア操作禁止モードから前記ハードウェア操作許可モードに変更した後に、前記ハードウェア操作コードのエミュレーションを実行し、

<u>前記実行された操作コードに含まれる前記ハードウェア操作コードの実行頻度が高頻度</u>であるか否かを判断し、

前記実行された操作コードに含まれるハードウェア操作コードの実行頻度が高頻度である場合、前記動作方式表のうち、前記実行され他ハードウェア操作コードを含む前記操作コードに対応する前記動作方式を、前記VT方式から前記コード変換方式に変更し、

前記変換コード表を参照して、前記実行されたハードウェア操作コードを含む前記操作 コードに対応する前記変更コードを検索し、

前記変換コード表に、前記実行されたハードウェア操作コードを含む前記操作コードに 対応する前記変換コードが存在しないと判断された場合、前記実行されたハードウェア操 作コードを含む前記操作コードに対応する前記シャドウコードと、前記実行されたハード ウェア操作コードに対応する前記昇格コードとを含む前記変換コードを生成し、

前記生成されたシャドウコード及び前記生成された昇格コードとの対応関係を前記コード変換表に追加することを特徴とするサーバ装置。

#### 「善哉頂って

<u>前記メモリは、前記ハードウェア操作コードを含む前記操作コードと、当該操作コード</u>が実行された時を特定可能な時刻情報とを対応づけた操作履歴表を格納し、

前記仮想計算機モニタは、

前記実行された操作コードに含まれる前記ハードウェア操作コードの実行頻度が高頻度であるか否かを判断する場合に、当該操作コードが実行された時を特定可能な第1の時刻情報を取得し、前記操作履歴表を参照して、当該操作コードが前回実行された時を特定可能な第2の時刻情報を取得し、

前記第1の時刻情報及び前記第2の時刻情報に基づいて、前記操作コードに含まれる前

10

20

30

40

記ハードウェア操作コードによって実行された前記ハードウェアの操作の間隔を算出し、 前記算出した間隔が所定の閾値よりも小さいときに、前記実行された操作コードに含まれる前記ハードウェア操作コードの実行頻度が高いと判断することを特徴とする請求項1 に記載のサーバ装置。

## 【請求項3】

前記切り替えモジュールは、前記オペレーティングシステム又は前記オペレーティングシステム上で稼働するアプリケーションによって、前記コード変換方式が適用される前記操作コードが変更されたことを前記仮想計算機モニタが検出したときに、前記変更された操作コードに対応する前記シャドウコードを無効化し、

前記仮想計算機モニタは、前記変更された操作コードを実行するときに、前記例外イベントを発生させて前記変更された操作コードに含まれる前記ハードウェア操作コードのエミュレーションを実行するように設定することを特徴とする請求項2に記載のサーバ装置

## 【請求項4】

前記切り替えモジュールは、

前記シャドウコード及び前記昇格コードを保持するために必要な前記メモリの容量が不 足したとき、前記変換コード表に格納される前記変換コードのうち、実行されていない期 間が最も長い前記変換コードを選択し、

前記選択された変換コードの情報を前記変換コード表から削除し、

前記仮想計算機モニタは、前記削除された変換コードと対応する前記操作コードを実行する場合に、当該削除された変換コードを実行する代わりに、前記例外イベントを発生させて、前記削除された変換コードと対応する前記操作コードに含まれる前記ハードウェア操作コードの前記エミュレーションを実行するように設定することを特徴とする請求項2に記載のサーバ装置。

#### 【請求項5】

一つ以上のCPUと、データ及びプログラムを格納するメモリと、外部とでデータを送受信するインターフェースと、を備えたサーバ装置に、オペレーティングシステムが稼働する一以上の仮想計算機を稼働させる仮想計算機の制御プログラムであって、

<u>前記オペレーティングシステム又は前記オペレーティングシステム上で稼働するアプリ</u>ケーションは、所定の処理の実行を要求する操作コードを保持し、

前記 C P U は、ハードウェア操作許可モードとハードウェア操作禁止モードとの二つの 動作モードを備え、

前記メモリは、

前記サーバ装置のハードウェアに対する操作を要求するハードウェア操作コードを含む 前記操作コードと、前記 C P U の前記動作モードを前記ハードウェア操作許可モードに切 り替え、前記ハードウェア操作コードをエミュレーションさせる変換コードとを対応づけ た変換コード表と、

前記ハードウェア操作コードを含む前記操作コードと、前記ハードウェア操作コードの エミュレーション方式とを対応づけた動作方式表と、を格納し、

前記変換コードは、前記CPUの前記動作モードを前記ハードウェア操作禁止モードから前記ハードウェア操作許可モードに切り替え、前記ハードウェア操作コードをエミュレーションさせる昇格コードと、前記昇格コードを含むシャドウコードとから構成され、

前記エミュレーション方式は、前記ハードウェア操作コードを含む前記操作コードに対して、前記CPUが前記例外イベントを発生させ、前記操作コードの実行の強制中断処理を終了した後に、当該ハードウェア操作コードをエミュレーションするVT方式、又は、前記ハードウェア操作コードを含む前記操作コードに対応する前記変換コードを実行することによって、前記ハードウェア操作コードをエミュレーションするコード変換方式とを含み、

前記仮想計算機の制御プログラムは、

前記ハードウェア操作コードを含む操作コードを検出した場合に、前記動作方式表を参

10

20

30

40

<u>照し、前記ハードウェア操作コードを含む前記操作コードに対応する前記エミュレーショ</u>ン方式を特定する第 1 の手順と、

前記特定されたエミュレーション方式が前記VT方式である場合、例外イベントを発生させて、前記CPUの前記動作モードを前記ハードウェア操作許可モードに切り替えて、前記出力された操作コードに含まれる前記ハードウェア操作コードをエミュレーションする第2の手順と、

前記特定されたエミュレーション方式が前記コード変換方式である場合、前記検出された操作コードに対応する前記シャドウコードに含まれる前記昇格コードに基づいて、前記出力された操作コードに含まれる前記ハードウェア操作コードをエミュレーションする第3の手順と、

前記操作コードに含まれる前記ハードウェア操作コードのエミュレーションが完了した 後、所定の判断条件に基づいて、当該ハードウェア操作コードの実行頻度が高頻度である か否かを判断する第4の手順と、

前記判断された実行頻度に基づいて、前記第2の手順、又は、前記第3の手順のいずれ を実行して前記操作コードに含まれる前記ハードウェア操作コードをエミュレーションさ せるかを決定し、前記決定に基づいて前記動作方式表を更新する第5の手順と、

前記変換コード表を参照して、前記実行されたハードウェア操作コードを含む前記操作 コードに対応する前記変更コードを検索する第6の手順と、

前記変換コード表に、前記実行されたハードウェア操作コードを含む前記操作コードに 対応する前記変換コードが存在しないと判断された場合、前記実行されたハードウェア操 作コードを含む前記操作コードに対応する前記シャドウコードと、前記実行されたハード ウェア操作コードに対応する前記昇格コードとを含む前記変換コードを生成する第7の手 順と、

前記生成されたシャドウコード及び前記生成された昇格コードとの対応関係を前記コード変換表に追加する第8の手順と、を前記サーバ装置に実行させることを特徴とする仮想計算機の制御プログラム。

### 【請求項6】

<u>前記メモリは、前記ハードウェア操作コードを含む前記操作コードと、当該操作コード</u>が実行された時を特定可能な時刻情報とを対応づけた操作履歴表を格納し、

前記第4の手順は、

前記ハードウェア操作コードを含む前記操作コードが実行された時を特定可能な第1の 時刻情報を取得し、前記操作履歴表を参照して、前記ハードウェア操作コードを含む前記 操作コードが前回実行された時を特定可能な第2の時刻情報を取得し、

前記第1の時刻情報及び前記第2の時刻情報に基づいて、前記操作コードに含まれる前記ハードウェア操作コードによって実行された前記ハードウェアの操作の間隔を算出する手順と、

前記算出した間隔が所定の閾値よりも小さいときに、前記操作コードに含まれる前記ハ ードウェア操作コードの実行頻度が高いと判断する手順と、を含むことを特徴とする請求 項5に記載の仮想計算機の制御プログラム。

#### 【請求項7】

管理者によって入力された前記所定の判断条件を受け付ける手順と、

前記入力された所定の判断条件を記憶装置に保存する手順と、を含むことを特徴とする請求項6に記載の仮想計算機の制御プログラム。

## 【請求項8】

前記第2の手順は、VMexitイベントの発生によって前記CPUをVMX roo <u>tモードに設定することによって、前記ハードウェア操作許可モードに遷移する手順を含</u> み、

前記第3の手順は、前記昇格コードに含まれる特権レベル減少分岐命令を実行して前記 CPUの特権レベルを0に設定することによって、前記ハードウェア操作許可モードに遷 移する手順を含むことを特徴とする請求項6に記載の仮想計算機の制御プログラム。 10

20

30

#### 【発明の詳細な説明】

### 【技術分野】

### [0001]

本発明はサーバ装置において実現される仮想計算機システムに関して、ハードウェアエ ミュレーションの効率化に関する。

## 【背景技術】

#### [0002]

ITシステムに含まれるサーバ台数が増加するにつれて、運用に関する複雑さが増加するため、その運用コストが問題化する。運用コストを低減するために、複数サーバを1台のサーバに統合するサーバ統合が知られている。サーバ統合を実現する技術として、一つのコンピュータを任意の割合で論理的に分割する仮想計算機技術が知られている。

#### [0003]

仮想計算機技術は、例えば、ハイパバイザなどのファームウェア又はミドルウェアが、物理計算機を複数の論理区画(LPAR:Logical PARtition)に分割し、分割された各LPARに計算機資源(CPU、主記憶及びI/O)を割り当てる。この各LPAR上でオペレーティングシステム(OS)が動作する。また、一つのサーバ上で一つのホストOS(物理計算機を直接使用するOS)を実行し、このホストOS上で稼動するハイパバイザが同様に物理計算機をLPARに分割する。この各LPAR上でゲストOS(LPAR上で稼動するOS)が稼動してもよい。

## [0004]

このように、仮想計算機技術は、従来複数のサーバで稼動していたOS及びOS上で稼動するソフトウェアを、1台のサーバで稼動させることを可能にする。これによって、サーバ統合が実現される。

#### [0005]

この仮想計算機技術は、従来は汎用機(MainFrame)等の大型計算機で用いられてきた 技術であるが、近年のマイクロプロセッサの性能向上によって、ローエンドサーバやパー ソナルコンピュータにも適用可能である。

#### [0006]

この仮想計算機技術を適用することによって、物理計算機は、ゲスト(ゲストOS及びゲストOS上で稼動するアプリーケーションソフトウェアの総称)を稼動させる複数の仮想計算機(Virtual Machine)と、仮想計算機の制御を行う仮想計算機モニタ(Virtual Machine Monitor、以下VMMとする)とを有する仮想計算機システムが構成される(特許文献 1 参照)。

## [0007]

なお、OSは、本来、サーバのハードウェアを全て独占して使用することを前提に作られている。しかし、仮想計算機システムでは、複数のゲストOSが稼動する。しかしながら、ゲストOSはサーバのハードウェアを独占することはできない。そこで、VMMが、ゲストOSによるハードウェア操作に対応して、ゲストOSがサーバのハードウェアを独占している状態と同じ振る舞いをエミュレーションする。

#### [00008]

VMMは、このエミュレーションの処理のために時間とメモリを使用する。そのため、ゲストOSによってVMMによるエミュレーションの回数が増加すると、処理時間とメモリが増加することによって、ゲストの性能が低下し、ゲストの利用可能なメモリ量が減少する問題がある。この問題を軽減するために、エミュレーションの高速化(高性能化)技術や省メモリ化技術が考案されている。

## [0009]

エミュレーションの高速化技術の一つにコード変換方式がある。コード変換方式は、VMMが、ゲストOSによる操作コード(OSコードとも呼ぶ)に対応する変換コードをメモリ上に作成する。この変換コードの作成処理をコード変換と呼ぶ。変換コードを作成するときに、対応するOSコードに含まれるハードウェア操作は、エミュレーションコード

10

20

30

40

に置き換えられる。このコード変換方式では、OSコードの代わりに変換コードを実行することで、必要最小限の処理のみでハードウェア操作のエミュレーションを可能とする。コード変換方式は、実行に必要な全てのOSコードに対してコード変換を実施する。コード変換は処理時間を要するため速度低下の原因になり得る。そこで本方式では、作成した変換コードをメモリ上に保持し続け、2度目以降はメモリ上の変換コードを再利用し、速度低下を防止する。ただし、変換コードを保持するメモリが不足した場合は、全ての変換コードを保持できないので実行頻度の低い変換コードを破棄する。

## [0010]

エミュレーションの省メモリ化技術であるVT方式は、Inte1社製CPUに搭載されたVT(Virtualization Technology)機能を利用する。VT機能を用いるとCPUの動作モードとして、HW操作コードを一切実行できないHW操作完全禁止モードが選択可能になる。CPUがHW操作完全禁止モードのときにHW操作コードの実行を試みると、CPUが例外イベントを発生してコード実行を強制中断する。このとき、CPUはHW操作が可能なHW操作許可モードに遷移した上で、事前に登録されたコードを実行する。逆に、HW操作許可モードで例外イベントからの再開処理を実行すると、CPUはHW操作完全禁止モードに遷移し、指定アドレスから実行を再開する(非特許文献 1、非特許文献 2 参照)。

## [0011]

この方式では、エミュレーション処理を実施するエミュレーションモジュールをCPUに事前登録し、ゲストをHW操作禁止モードで実行させることで、HW操作をエミュレーションする。本方式は、VMMのメモリにエミュレーションモジュール及びエミュレーションに使用するデータのみを保持するため、VMMのメモリ使用量が少ない。

【特許文献1】米国特許6,397,242号明細書

【非特許文献 1】Intel Virtualization Technology Specification for the Intel Itan ium Architecture

【非特許文献 2 】Intel Virtualization Technology Specification for the IA-32 Intel Architecture

#### 【発明の開示】

【発明が解決しようとする課題】

## [0012]

先行技術であるコード変換方式と、VT方式はそれぞれ問題を有している。

#### [0013]

コード変換方式は高性能だが、実行に必要な全てのOSコードを変換するため、変換コードの保持に使用するメモリ量が多く、省メモリは望めない。省メモリ化のためにメモリ量を無理に減らした場合は、変換コードの再利用が十分に機能しなくなり、コード変換の回数が増加して性能低下を招くため、高性能が望めない。

## [0014]

VT方式はエミュレーションの開始時に必ず例外イベントを起こすが、昨今のCPUは例外イベントが発生しないことを仮定して高度な並列実行を行っているため、例外イベントが発生するとCPUは内部状態の有効性判断、破棄、再実行等の複雑な処理を行う必要がある。したがって例外イベントの発生には遅延を要する。そのためVT方式は、省メモリではあるが、高性能は望めない。

## [0015]

以上のように先行技術は、高性能と省メモリの何れか一方のみを解決しており、高性能 と省メモリがトレードオフの関係にあって、両立できていない問題がある。

## [0016]

本発明は、前記のような問題点を鑑みてなされたものであり、エミュレーション方式における高性能と省メモリを両立できる仮想計算機システムを提供することを目的とする。

### 【課題を解決するための手段】

## [0017]

10

20

30

課題を解決するために、本発明ではゲストのプログラムコードを、HW操作の実行頻度に応じて二つの部分に分類し、実行頻度の高い部分にコード変換方式を、実行頻度の低い部分にVT方式を適用する。

#### 【発明の効果】

### [0018]

本発明ではゲストコードを、高頻度のHW操作コードを含む部分と、その他、すなわち低頻度の部分に分類し、高頻度のHW操作コードのエミュレーションにコード変換方式を適用し、低頻度に含まれるHW操作のエミュレーションにVT方式を適用する。このようにすることによって、高性能と省メモリを両立させる仮想計算機システムが実現できる。

【発明を実施するための最良の形態】

[0019]

以下に、本発明の実施の形態を添付の図面に基づいて説明する。

[0020]

<実施形態1>

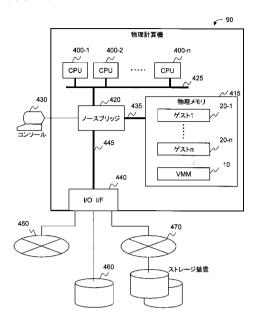

図1は、本発明の第1の実施の形態の物理計算機のブロック図である。

[0021]

この図は、仮想計算機システムが動作する物理計算機90の構成を示す。

[0022]

物理計算機 9 0 は、1 つ以上の C P U 4 0 0 ( 4 0 0 - 1 ~ 4 0 0 - n ) を含む。これらの C P U 4 0 0 は、フロントサイドバス 4 2 5 を介してノースブリッジ 4 2 0 と接続する。

[0023]

ノースブリッジ420は、メモリバス435を介して物理メモリ415と接続する。また、バス445を介してI/Oインターフェース440と接続する。また、コンソール4 30と直接接続する。

[0024]

[0025]

CPU400は、ノースブリッジ 420を介して物理メモリ 415にアクセスし、物理メモリ 415に格納されているプログラムを実行することによって、プログラムに規定された処理を実行する。また、CPU400は、ノースブリッジ 420及び I/Oインターフェース 440を介して、物理計算機 900外部にある I/Oデバイスにアクセスする。

[0026]

ノースブリッジ 4 2 0 は、ホスト物理メモリ 4 1 5 へのデータの入出力を制御する。また、ノースブリッジ 4 2 0 は、グラフィックコントローラを含んでおり、コンソール 4 3 0 に画像やデータを表示する。

[0027]

物理メモリ415には、仮想計算機モニタ(Virtual Machine Monitor、以下、「VMM」と表記する)10とゲスト20(20-1~20-n)を実現するためのプログラムが格納されている。CPUがこのプログラムを実行することによって、VMM10が実行され、このVMM10によって、ゲスト20が実行される。

[0028]

CPU400(400-1~400-n)は、VT-i機能を備えるIPF(Itanium Processor Family)プロセッサである。CPU400は、CPU400が備えるレジスタのうち、PSR(Processor Status Register)のVMビットが1であるときはHW操作完全禁止モードで動作する。また、PSRのVMビットが0であり、かつ、PSRのCP

10

20

30

40

L (Current Privilege Level)フィールドが 0 であるときは H W 操作許可モードで動作する。また、何れの条件も満たさない場合は、 H W 操作部分禁止モードで動作する。

#### [0029]

また、CPU400は、命令の仮想アドレスと物理アドレスとを変換するための命令アドレス変換機構を備える。この命令アドレス変換機構は、命令TLB(Translation Look aside Buffer)を用いる。なお、CPU400が、命令TLBと命令ページテーブルを組み合わせてアドレス変換機構を実現してもよい。

### [0030]

次に、本実施の形態の仮想計算機システムを説明する。

#### [0031]

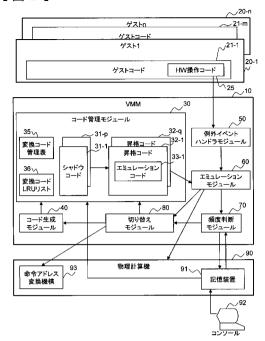

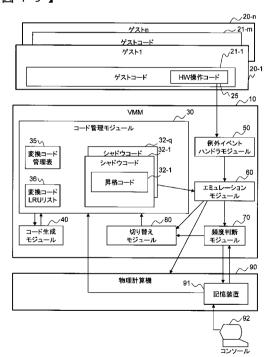

図 2 は、物理計算機 9 0 において、ゲスト 2 0 ( 2 0 - 1 ~ 2 0 - n ) とゲスト 2 0 を稼動させる V M M 1 0 とを含むハードウェア及びソフトウェアのブロック図である。

#### [0032]

図 2 において、物理計算機 9 0 上では、複数のゲスト 2 0 ( 2 0 - 1 ~ 2 0 - n ) を管理する V M M 1 0 が稼動している。 V M M 1 0 は、これら複数のゲスト 2 0 が実行するハードウェアへの操作(以下、「H W 操作」と表記する)をエミュレーションする。

#### [0033]

各ゲスト 2 0 は、稼動に必要なゲストコード 2 1 ( 2 1 - 1 ~ 2 1 - m ) を 1 つ以上備える。このゲストコード 2 1 は、HW操作コード 2 5 を含む。

### [0034]

V M M 1 0 は、コード管理モジュール 3 0、コード生成モジュール 4 0、例外イベントハンドラモジュール 5 0、エミュレーションモジュール 6 0、頻度判断モジュール 7 0、切り替えモジュール 8 0 を含む。

#### [0035]

以降、ゲスト20がHW操作コードを含むゲストコードを実行したときのVMM10の 処理を説明する。

### [0036]

VMM10は、ゲストコード21をHW操作完全禁止モードで実行させる。ゲスト20がHW操作コードを含むゲストコード21を実行した場合は、CPU400は例外イベントを発生させる。そして、CPU400がHW操作許可モードに遷移した後、VMM10の例外イベントハンドラモジュール50が実行される。

## [0037]

例外イベントハンドラモジュール 5 0 は、例外イベントの発生要因を解析し、その例外イベント、すなわち H W 操作コードに対応するエミュレーションモジュール 6 0 を呼び出す。

#### [0038]

エミュレーションモジュール60は、必要に応じて物理計算機90を操作する。これによって、HW操作コードに対応するエミュレーションが実施される。エミュレーションモジュール60は、エミュレーションを実施する際に、頻度判断モジュール70を呼び出す

## [0039]

頻度判断モジュール70は、アドレスグループ毎のHW操作の頻度を判断し、切り替え モジュール80に判断結果を渡す。

## [0040]

なお、当該HW操作コードの命令アドレスを含む所定のアドレスの範囲をアドレスグループと呼ぶ。本実施の形態では、アドレスグループに、ページを用いる。

#### [0041]

また、頻度判断モジュール70は、モジュールの初期化時など必要に応じて、物理計算機90が有する記憶装置91を参照して、記憶装置91に格納された方式切り替え条件を取得する。

10

20

30

40

#### [0042]

切り替えモジュール80は、頻度判断モジュール60からページ毎のHW操作の頻度を取得する。そして、頻度が高いと判断した場合は、コード管理モジュール30に、当該HW操作に対応する変換コードの検索を依頼する。

## [0043]

コード管理モジュール30は、変換コードを管理する。コード管理モジュール30は、変換コード管理表35と、変換コードLRU(Least Recent Used)リスト36とを含む。変換コード管理表35は、変換コードを検索するための情報を保持する。変換コードLRUリスト36は、未使用時間が長い変換コードの情報を保持する。

#### [0044]

切り替えモジュール80は、コード管理モジュール30への依頼の結果、変換コード管理表35が当該HW操作コードのアドレスが含まれるページに対応する情報を記録していない場合は、コード生成モジュール40を呼び出す。

### [0045]

コード生成モジュール 4 0 は、当該 H W 操作コードのアドレスが含まれるページを参照して、対応する複数のシャドウコード 3 1 (3 1 - 1 ~ 3 1 - p)と複数の昇格コード 3 2 (3 2 - 1 ~ 3 2 - q)とを、コード管理モジュール 3 0 が管理するメモリ上に生成する。そして、その内容を変換コード管理表 3 5 に格納する。

#### [0046]

その後、切り替えモジュール80は、物理計算機90が有する命令アドレス変換機構9 3に、当該ページの仮想アドレスと、シャドウコード31の物理アドレスとの対応付けを 設定する。

### [0047]

以上の操作によって、以降は、ゲスト20によるHW操作コードのアドレスが含まれるページが実行されたときは、シャドウコード31が実行される。

### [0048]

VMM10は、一連の処理の最後に、CPUの動作モードをHW操作完全禁止モードに 戻すための「rfi命令」を実行する。これによって、シャドウコードはゲストコードと 同じく、HW操作完全禁止モードで実行される。

## [0049]

シャドウコード31は、HW操作コードの代わりに昇格コード32を呼び出す。

## [0050]

昇格コード32は、CPUをHW操作許可モードに遷移させ、エミュレーションモジュール60を呼び出す。又は、エミュレーションモジュール60の部分複製であるエミュレーションコード33(33-1)を実行する。これによって、HW操作のエミュレーションが実行される。その後、CPUをHW操作完全禁止モードに戻す。

## [0051]

なお、CPUをHW操作許可モードに遷移させるために、昇格コード32は、PSRのVMビットを操作する命令である「vmsw.0」と「vmsw.1」とを含む。

### [0052]

なお、ゲスト20によって、シャドウコード31に対応するゲストコード21が書き換えられる場合がある。エミュレーションモジュール60は、この書き換えを検出した場合は、頻度判断モジュール70と切り替えモジュール80に、この書き換えを通知する。頻度判断モジュール70は、書き換えられたページの頻度を「低頻度」に設定する。切り替えモジュール80は、書き換えられたページに対応していた変換コードを無効化し、これを変換コード管理表35に記録する。さらに、物理計算機90が有する命令アドレス変換機構93から、書き換えられたページに関する設定を削除する。

### [0053]

物理計算機90は、コンソール92と接続されている。システム管理者がコンソール9 2を用いてコード変換の設定を変更したときは、コード変換の設定を格納する記憶装置9 10

20

30

40

10

20

30

40

50

1 に、その内容を記録する。また、頻度判断モジュール70及びコード管理モジュール3 0 に、その内容を伝える。

[0054]

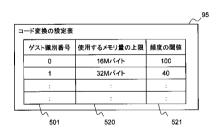

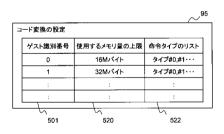

図3は、記憶装置91に格納されているコード変換の設定表95の一例の説明図である

[0055]

コード変換の設定表 9 5 は、ゲスト 2 0 毎に、そのゲストが使用するメモリ量の上限と、そのゲストのゲストコードが高頻度であるか低頻度であるかを判断するための頻度の閾値とを格納する。

[0056]

コード変換の設定95は、ゲスト識別番号フィールド501、使用するメモリ量の上限フィールド520及び頻度の閾値フィールド521を含む。

[0057]

ゲスト識別番号フィールド 5 0 1 は、ゲスト 2 0 毎に付された識別子であるゲスト識別番号を格納する。使用するメモリ量の上限フィールド 5 2 0 は、メモリ変換コードを保持するために使用するメモリ量の上限を格納する。頻度の閾値フィールド 5 2 1 は、ゲストコードが高頻度であるか低頻度であるかを判断するための閾値を格納する。

[0058]

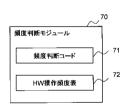

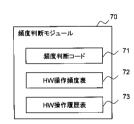

図4は、頻度判断モジュール70の構成ブロック図である。

[0059]

頻度判断モジュール70は、頻度判断コード71とHW操作頻度表72とを含む。

[0060]

頻度判断コード 7 1 は、HW操作頻度表 7 2 を参照・更新して、HW操作の頻度を判断するプログラムである。HW操作頻度表 7 2 は、ゲスト 2 0 によって実行されたHW操作の回数を、ゲストコードの物理ページ単位で格納する表である。

[0061]

図5は、HW操作頻度表72の一例の説明図である。

[0062]

HW操作頻度表 7 2 は、ゲスト 2 0 毎に、ゲストコードの物理ページアドレスと、そのページでの HW操作の実行回数とを格納する。

[0063]

HW操作頻度表72は、ゲスト識別番号フィールド501と、ゲストコードの物理ページのアドレスフィールド503と、HW操作実行回数フィールド506とを含む。

[0064]

ゲスト識別番号フィールド 5 0 1 は、前述のコード変換の設定表 9 5 のゲスト識別番号と同じものを格納する。ゲストコードの物理ページのアドレスフィールド 5 0 3 は、ゲストコードの物理ページのアドレスを格納する。 H W 操作実行回数フィールド 5 0 6 は、ゲストコードの物理ページに対応する H W 操作が実行された回数を格納する。なお、 H W 操作実行回数の初期値は 0 である。

[0065]

図6は、変換コード管理表35の一例の説明図である。

[0066]

変換コード管理表 3 5 は、ゲスト 2 0 毎に、ゲストコードの物理ページアドレスと、そのゲストコードに対応する変換コードの物理ページのアドレスを格納する。

[0067]

変換コード管理表 3 5 は、ゲスト識別番号フィールド 5 0 1 と、ゲストコード物理ページのアドレスフィールド 5 0 3 と、 v a l i d ビットフィールド 5 0 4 と、変換コードの物理ページのアドレス 5 0 5 とを含む。

[0068]

ゲスト識別番号フィールド501は、前述のコード変換表95及びHW操作頻度表70

のゲスト識別番号と同じものを格納する。ゲストコード物理ページのアドレスフィールド503は、前述のHW操作頻度表72のゲストコードの物理ページのアドレスと同じものを格納する。 validビットフィールド504は、そのページに対応する変換コードが有効であるか否かを示す識別子である validビットを格納する。この validビットの初期値は0(無効)である。変換コードの物理ページのアドレスフィールド505は、ゲストコードの物理ページのアドレスに対応する変換コードの物理ページのアドレスを格納する。

[0069]

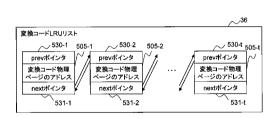

図7は、変換コードLRUリスト36の一例の説明図である。

[0070]

変換コードLRUリスト36は、変換コード物理ページのアドレス毎に、そのアドレスの未使用時間が短い順に保持するための双方向線形リストである。

[0071]

変換コードLRUリスト36は、prevポインタフィールド530(530-1~530-t)、変換コードの物理ページのアドレスフィールド505(505-1~505-t)及びnextポインタフィールド531(531-1~531-t)を一つの要素とし、これらの要素を、それぞれのポインタによって結合したものである。

[0072]

prevポインタフィールド530は前の要素を示すprevポインタを格納する。nextポインタフィールド531は次の要素を示すnextポインタを格納する。変換コードの物理ページのアドレスフィールド505は、前述の変換コード管理表35の変換コードの物理ページのアドレスと同じものを格納する。

[0073]

次に、ゲスト20の動作に伴うVMM10の処理を、フローチャートを参照して説明する。

[0074]

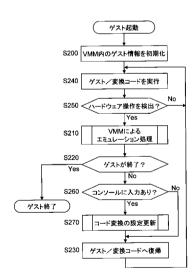

図8は、VMM10がゲスト20を稼動するときの処理のフローチャートである。

[0075]

まず、仮想計算機の電源の投入等によって、ゲスト20が起動すると、VMM10は、自身が有するゲスト情報を参照し、起動されたゲストに関するエントリを初期化する(S200)。

[0076]

その後、ゲスト20が、HW操作完全禁止モードでゲストコード又は変換コードを実行する(S240)。VMM10は、ゲスト20によるゲストコードの実行によって、HW操作コードの実行を検出したか否かを判断する(S250)。

[0077]

ゲスト20によるHW操作コードの実行を検出したと判断した場合は、VMM10は、例外イベントを発生させて、CPU400の動作モードをHW操作許可モードに変更する。その後、ステップS210へ進む。また、ゲスト20による昇格コードの実行を検出し、エミュレーションモジュール60が呼ばれたと判断した場合も同様に、VMM10は、CPU動作モードをHW操作許可モードに変更する。その後、S210へ進む。一方、VMM10が、HW操作コード又は昇格コードの実行を検出しないと判断した場合は、ステップS240に戻り、次のゲストコードの実行の検出を待機する。

[0078]

ステップ S 2 1 0 では、 V M M 1 0 は、 H W 操作のエミュレーション処理を実施する。 また、このエミュレーション処理によって、次に実行するコードの種別を決定する。

[0079]

次に、VMM10は、仮想計算機の電源遮断等によってゲスト20が終了したか否かを 判断する。ゲスト20が終了したと判断した場合は、VMM10は、当該ゲスト20の処 理を終了する。一方、ゲスト20は終了せず、動作が継続すると判断した場合は、ステッ 10

20

30

40

プS260に進む。

## [0080]

S 2 6 0 では、V M M 1 0 は、システム管理者によるコード変換の設定の変更がコンソール 9 2 に入力されたか否かを判断する。コンソール 9 2 への入力によってコード変換の設定 9 5 に変更があったと判断した場合は、ステップ S 2 7 0 に移行する。一方、コード変換の設定 9 5 に変更がなければ、ステップ S 2 3 0 に進む。

#### [0081]

ステップS270では、物理計算機90は、コンソール92によって設定された内容を受け取り、記憶装置91のコード変換の設定95を更新するコード変換の設定更新処理を実行する。

[0082]

次に、VMM10は、ステップS210によって決定したコードの種別を設定する。すなわち、ゲストコード又はシャドウコードに復帰する場合は、VMM10は、CPU動作モードをHW操作完全禁止モードに変更する命令を実行する。その後、ステップS240に戻る。また、昇格コードに復帰する場合は、なにもせずそのままS240に戻る。その後、昇格コード内の命令が実行されることによって、CPU動作モードがHW操作完全禁止モードに変更される。

[0083]

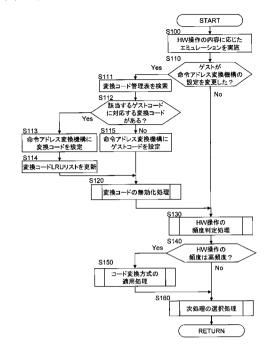

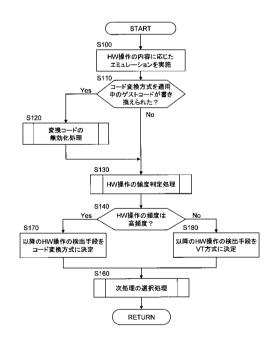

図 9 は、図 8 のステップ S 2 1 0 の V M M のエミュレーション処理のフローチャートである。

[0084]

まず、ゲスト 2 0 によって実行された H W 操作コードの内容に応じて、 V M M 1 0 がエミュレーションを実施する ( S 1 0 0 )。

[0085]

このとき、VMM10は、エミュレーションの内容はコード変換の対象となったゲストコードの変更を含むか否か、すなわち、命令アドレス変換機構93の設定を変更するか否かを判断する(S110)。なお、VMM10は、ゲスト20によってキャッシュ操作命令であるFC(Flush Cache)命令の実行が試みられたと場合に、ゲストコードが書き換えられたと判断する。変更しないと判断した場合は、ステップS130に進む。

[0086]

変更すると判断した場合は、VMM10は、変換コード管理表35を検索して(S11)、該当するゲストコードに対応する変換コードがあるか否かを判断する(S112)

[0087]

対応する変換コードがあると判断した場合は、VMM10は、該当するゲストコードの仮想アドレスと変換コードの物理アドレスとの対応付けを命令アドレス変換機構93に設定する(S113)。さらに、VMM10は、当該変換コードの情報を、変換コードLRUリスト36を更新する(S114)。

[0088]

一方、対応する変換コードがないと判断した場合は、VMM10は、該当するゲストコードの仮想アドレスと該当するゲストコードの物理アドレスとの対応付けを命令アドレス 変換機構93に設定する(S115)。

[0089]

次に、VMM10は、書き換えられたゲストコードに対応する変換コードの無効化処理を実行する。この処理によって、当該ゲストコードのページのエミュレーション方式をVT方式に切り替える(S120)。

[0090]

ステップS130では、VMM10は、HW操作の頻度判定処理を実行する。この処理によって、ゲスト20によってなされたHW操作の頻度が高頻度であるか低頻度であるかが判定される。

10

20

30

40

[0091]

次に、VMM10は、HW操作の頻度低処理の結果、頻度が高頻度であるか否かを判断する(S140)。高頻度であると判断した場合はステップS150に進む。低頻度であると判断した場合はステップS160に進む。

[0092]

ステップS150では、VMM10は、当該ページに含まれるHW操作のエミュレーションにコード変換方式を適用する処理を実行する。

[0093]

ステップ S 1 6 0 では、 V M M 1 0 は、当該 H W 操作の次の処理の選択処理を実行する。

10

[0094]

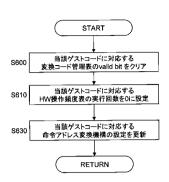

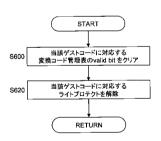

図10は、前述の図9のステップS120の変換コードの無効化処理のフローチャートである。

[0095]

VMM10は、変換コード管理表35を参照して、書き換えられたゲストコードに対応するエントリのvalidビットをクリアする。すなわち、validビットを0に変更する(S600)。

[0096]

次に、VMM10は、HW操作頻度表72を参照して、書き換えられたゲストコードに対応するエントリのHW操作の実行回数を0に設定する(S610)。

20

[0097]

次に、VMM10は、書き換えられたゲストコードの仮想アドレスと当該ゲストコードの物理アドレスとの対応付けを命令アドレス変換機構93に設定する(S630)。

[0098]

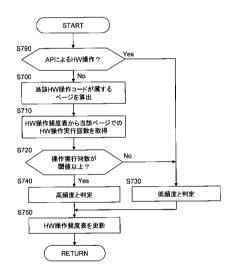

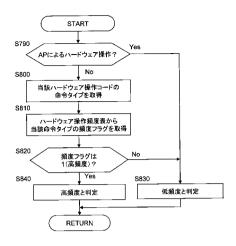

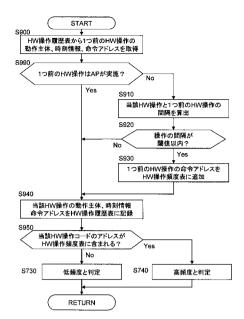

図11は、前述の図9のS130の頻度の判定処理のフローチャートである。

[0099]

まず、VMM10は、当該HW操作コードを実行したのは、ゲスト20のアプリケーションであるか否かを判断する(S790)。アプリケーションが実行したと判断した場合は、ステップS730に進む。ゲスト20のOSが実行したと判断した場合は、ステップS700に進む。

30

[0100]

ステップ S 7 0 0 では、V M M 1 0 は、当該 H W 操作コードが属するページの物理アドレスを算出する。

[0101]

次に、VMM10は、HW操作頻度表72を参照して、算出したページの物理アドレスに対応するエントリの、HW操作の実行回数を取得する(S710)。

[0102]

次に、VMM10は、コード変換の設定表95を参照して、HW操作コードの要求元のゲスト20の識別番号のエントリから、頻度の閾値を取得する。そして、取得したHW操作の実行回数と取得した頻度の閾値とを比較して、実行回数が閾値以上であるか否かを判断する(S720)。実行回数が閾値以上であると判断した場合は、ステップS730に進む。

40

50

[0103]

S 7 4 0 では、V M M 1 0 は、当該ページでの H W 操作の頻度は高頻度であると判定する。

[0104]

S 7 3 0 では、V M M 1 0 は、当該ページでの H W 操作の頻度が低頻度であると判定する。

[0105]

次に、VMM10は、HW操作頻度表72の当該ページのHW操作の実行回数に1を加

算して、HW操作頻度表72を更新する(S750)。

### [0106]

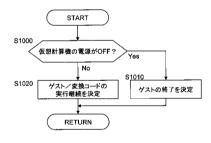

図 1 2 は、前述の図 9 のステップ S 1 6 0 の次処理の選択処理のフローチャートである

## [0107]

V M M 1 0 は、ゲスト 2 0 が終了したか否か、すなわち、ゲスト 2 0 が稼働する仮想計算機 2 1 の電源が O F F にされたか否かを判断する(S 1 0 0 0 )。仮想計算機 2 1 の電源が O F F にされたと判断した場合はステップ S 1 0 1 0 に進む。そうでなければステップ S 1 0 2 0 に進む。

#### [0108]

ステップS1010では、VMM10は、次に実行する処理として、ゲスト終了を選択する。

#### [0109]

ステップS1020では、VMM10は、次に実行する処理にゲストコード又は変換コードを継続して適用することを決定する。

#### [0110]

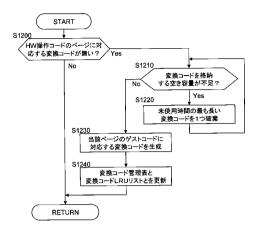

図 1 3 は、前述の図 9 のステップ S 1 5 0 のコード変換方式の適用処理のフローチャートである。

#### [0111]

ステップS1200では、VMM10は、変換コード管理表35を参照して、当該HW操作コードを含むページの物理アドレスに対応する変換コードの有無を判断する。変換コードが存在しないと判断した場合は、ステップS1210に進む。変換コードが設定されていると判断した場合は、本処理を終了して、図9のフローチャートに戻る。

#### [0112]

S1210では、VMM10は、変換コードを格納するためのメモリ領域のメモリ容量に必要な空き容量が存在するか否かを判断する。メモリ領域に必要な空き容量が存在しないと判断した場合は、ステップS1220に移行する。必要な空き容量が存在すると判断した場合は、ステップS1230に進む。

## [0113]

ステップS1220では、VMM10は、変換コードLRUリスト36を参照して、未使用時間の最も長い変換コードを含む要素を一つ選択する。そして、選択された要素に含まれる変換コードに属するページの物理アドレスを無効化することによって、変換コードをメモリ領域から破棄する。さらに、選択された要素に含まれる変換コードの情報を、変換コードLRU36から削除する。そして、ステップS1210に戻る。すなわち、必要な空き容量が確保できるまで、未使用時間の最も長い変換コードをメモリ領域から破棄する。

## [0114]

ステップS1230では、VMM10は、当該ページのゲストコードに対応する変換コードを生成し、生成された変換コードを保存する。変換コードのうち、シャドウコードはゲストコードと1対1に対応し、HW操作コードの代わりに昇格コードを呼び出す。また、変換コードのうち、昇格コードは、VMSW命令を含み、エミュレーションモジュール60の部分複製であるエミュレーションコード33の少なくとも一方を含む。

## [0115]

次に、VMM10は、生成した変換コードの情報を、変換コード管理表35に格納する。また、生成した変換コードの情報を変換コードLRU36リストに追加する(S1240)。

## [0116]

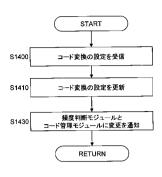

図14は、前述の図8のステップS270のコード変換の設定更新処理のフローチャートである。

10

20

30

40

10

20

30

40

50

#### [0117]

まず、物理計算機 9 0 が、システム管理者によって設定されたコード変換の設定の変更を、コンソールから受信する(S 1 4 0 0 )。

#### [0118]

物理計算機90は、受け取った変更内容を、記憶装置91のコード変換の設定表95に 反映させて、コード変換の設定表95を更新する(S1410)。

#### [0119]

次に、物理計算機90は、更新されたコード変換の設定表95を、頻度判断モジュール70及びコード管理モジュール30に通知する。これによって、頻度判断モジュール70及びコード管理モジュール30は、自身が格納しているコード変換の設定表95を更新する。

### [0120]

以上のように、本発明の第1の実施の形態の仮想計算機システムでは、ゲスト20によってHW操作を含むゲストコードの実行が要求されたときに、VMM10は、当該HW操作の実行頻度に応じて処理方法を変える。すなわち、当該HW操作を二つの部分に分け、実行頻度の高い部分に実行効率の高いコード変換方式を適用し、実行頻度の低い部分にメモリ消費量の少ないVT方式を適用する。このようにすることによって、高性能と省メモリとを両立することが可能なエミュレーション処理が可能となる。

### [0121]

<実施形態2>

次に、本発明の第2の実施の形態の仮想計算機システムを説明する。第2の実施の形態では、操作の種別である命令タイプによって、HW操作の頻度を判断する。

## [0122]

なお、第2の実施の形態のハードウェア構成は図1と同一である。また、第1の実施の 形態と同一の作用をする構成には同一の符号を付し、その説明は省略する。

### [0123]

第2の実施形態では、頻度判断に命令タイプを用いるため、コード変換の設定内容、H W操作頻度表のフォーマットの2点のみが実施例1と異なる。

#### [0124]

図15は、第2の実施の形態の、コード変換の設定表95の説明図である。

#### [0125]

第1の実施の形態において前述した図4とは異なり、コード変換の設定表95は、高頻度を判断するために、閾値ではなく命令タイプを格納する。

### [0126]

コード変換の設定95は、ゲスト識別番号フィールド501、使用するメモリ量の上限フィールド502及び命令タイプのリストフィールド522を含む。

## [0127]

ゲスト識別番号フィールド 5 0 1 は、ゲスト 2 0 毎に付された識別子であるゲスト識別番号を格納する。使用するメモリ量の上限フィールド 5 2 0 は、メモリ変換コードを保持するために使用するメモリ量の上限を格納する。命令タイプのリストフィールド 5 2 2 は、ゲストコードの命令タイプのうち、高頻度であると判断する命令タイプをリスト形式で格納する。

## [0128]

図16は、第2の実施の形態のHW操作頻度表72の説明図である。

#### [0129]

第1の実施の形態において前述した図5とは異なり、HW操作頻度表72は、ゲスト20毎に、命令タイプ507と、その命令タイプが高頻度であるか否かを判断するための頻度フラグ508とを格納する。

### [0130]

このHW操作頻度表72は、管理者によって設定されたコード変換の設定表95を元に

、頻度判断コード 7 1 によって生成される。すなわち、コード変換の設定表 9 5 のゲスト 識別番号及び命令タイプのリストを、ゲスト識別番号と命令タイプとによって並び替えた ものである。

[0131]

HW操作頻度表72は、ゲスト識別番号フィールド501と、命令タイプフィールド507と、頻度フラグフィールド508とを含む。

[0132]

ゲスト識別番号フィールド 5 0 1 は、前述のコード変換の設定表 9 0 1 のゲスト識別番号と同じものを格納する。命令タイプフィールド 5 0 7 は、ゲストコードの命令タイプを示す識別子を格納する。頻度フラグフィールド 5 0 8 は、命令タイプに対応する頻度フラグ格納する。頻度フラグは 1 であれば高頻度であることを示し、 0 であれば低頻度であることを示す。なお、頻度フラグの初期値は、頻度判断モジュール 7 0 がコード変換の設定表 9 5 から取得する。

[0133]

次に、第2の実施の形態の、ゲスト20の動作に伴うVMM10の処理を、フローチャートを参照して説明する。

[0134]

なお、第2の実施の形態の処理の概要は、前述の第1の実施の形態において前述した図8と同一である。

[0135]

また、前述の図 8 のステップ S 2 1 0 の V M M のエミュレーション処理は、前述の図 9 の処理と同一である。

[0136]

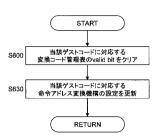

図 1 7 は、前述の図 9 のステップ S 1 2 0 の、第 2 の実施の形態の変換コードの無効化処理のフローチャートである。

[0137]

VMM 1 0 は、変換コード管理表 3 5 を参照して、書き換えられたゲストコードに対応するエントリの、 Validビットフィールド 5 0 4 をクリアする。すなわち、 Validビットを 0 に変更する (S 6 0 0)。

[0138]

次に、VMM10は、書き換えられたゲストコードの仮想アドレスと当該ゲストコードの物理アドレスとの対応付けを命令アドレス変換機構93に設定する(S630)。

**[** 0 1 2 0 **]**

図18は、前述の図9のステップS130の、第2の実施の形態の頻度判断処理のフローチャートである。

[0140]

まず、VMM10は、当該HW操作コードを実行したのは、ゲスト20のアプリケーションであるか否かを判断する(S790)。アプリケーションが実行したと判断した場合は、ステップS830に進む。ゲスト20のOSが実行したと判断した場合は、ステップS800に進む。

[0141]

ステップS800では、VMM10は、当該HW操作コードの命令タイプを取得する。

[0142]

次に、VMM10は、HW操作頻度表72を参照して、取得した命令タイプに対応するエントリの頻度フラグを取得する(S810)。

[0143]

次に、VMM10は、取得した頻度フラグが1であるか否かを判断する。頻度フラグが 1、すなわち高頻度を示すものであればステップS840に進む。頻度フラグが0、すな わち、低頻度を示すものであればステップS830に進む(S820)。

[0144]

50

10

20

30

30

40

50

ステップS840では、VMM10は、当該ページでのHW操作の頻度が高頻度であると判定する。

### [0145]

ステップS830では、VMM10は、当該ページでのHW操作の頻度が低頻度であると判定する。

#### [0146]

なお、図9のステップS160の次処理の選択処理は、前述の第1の実施の形態の図12の処理と同一である。

### [0147]

また、図9のステップS150のコード変換方式の適用処理は、前述の第1の実施の形 10 態の図13の処理とほぼ同一であるが、以下の1点のみが異なる。

#### [0148]

まず、ステップS1230では、VMM10は、当該ページに含まれる命令タイプが高頻度でない命令は、コード変換の対象から除外し、シャドウコードにゲストコードの命令をそのままコピーする。

#### [0149]

また、図8のステップS270のコード変換の設定更新処理は、前述の第1の実施の形態の図14と同一である。

#### [ 0 1 5 0 ]

以上のように、本発明の第2の実施の形態では、ゲストコードをHW操作の命令タイプ 20 に応じて二つの部分に分類する。そして、実行頻度の高い命令タイプを含む部分に、コード変換方式を適用し、実行頻度の高い命令タイプを含まない部分にVT方式を適用する。このようにすることによって、高性能と省メモリを両立させるエミュレーション処理が可能となる。

## [0151]

### <実施形態3>

次に、本発明の第3の実施の形態の仮想計算機システムを説明する。第3の実施の形態では、HW操作の間隔によって頻度を判断する。

#### [0152]

なお、第1の実施の形態と同一の作用をする構成には同一の符号を付し、その説明は省 略する。

## [0153]

第3の実施の形態のハードウェア構成は図1とほぼ同一である。しかしながら、第3の 実施の形態では、用いられるCPU(400-1~400-n)の機能が異なる。

## [0154]

CPU400(400-1~400-n)は、VT-x機能に対応したx86プロセッサである。このCPU400は、HW操作完全禁止モードと、HW操作許可モードと、HW操作部分禁止モードとを備える。HW操作完全禁止モードはCPU400をVMX non-rootモードに設定することで有効化される。HW操作許可モードはCPU400をVMX rootモードかつ特権レベル(CPL: Current Privilege Level)を0に設定することで有効化される。HW操作部分禁止モードはCPU400をVMX rootモードかつCPLを非0に設定することで有効化される。

## [0155]

また、CPU400が、VMX rootモードからVMX non-rootモードに遷移するためには、VMentry操作を実行する必要がある。VMentry操作とは、ゲストOSの起動を指示するためのVMLAUNCH命令の実行と、ゲストOSを一時停止するためのVMRESUME命令の実行との総称である。また、VMX non-rootモードからVMX rootモードに遷移するためには、VMexitイベントを実行する必要がある。VMexitイベントとは、VMexit0トである。

### [0156]

次に、第3の実施の形態の仮想計算機システムを説明する。

#### [0157]

図 1 9 は、物理計算機 9 0 において、ゲスト 2 0 ( 2 0 - 1 ~ 2 0 - n ) とゲスト 2 0 を稼動させる V M M 1 0 とを含むハードウェア及びソフトウェアのブロック図である。

#### [0158]

図19は、前述の第1の実施の形態の図2のブロック図とほぼ同一である。しかしなが ら、コード管理モジュール30の動作が異なる。

#### [0159]

以降、ゲスト20がHW操作コードを含むゲストコードを実行したときのVMM10の 処理を説明する。

#### [0160]

VMM10は、ゲスト20がHW操作コード25を含むゲストコード25を実行した場合は、VMM10は例外イベントを発生させる。この例外イベントによって、CPU400がHW操作許可モードに遷移する。その後、VMM10の例外イベントハンドラモジュール50が実行される。

### [0161]

例外イベントハンドラモジュール 5 0 は、例外イベントの発生要因を解析し、その例外イベント、すなわち、HW操作コードに対応するエミュレーションモジュール 6 0 を呼び出す。

#### [0162]

エミュレーションモジュール60は、必要に応じて物理計算機90を操作する。これによって、HW操作コードに対応するエミュレーションが実施される。エミュレーションモジュール60は、エミュレーションを実施する際に、頻度判断モジュール70を呼び出す

## [0163]

頻度判断モジュール70は、ゲスト20によって、前回のHW操作がされたときの時刻情報と今回のHW操作がされたときの時刻情報との差から、HW操作間隔の短さ、すなわちHW操作の頻度を算出する。そして、算出された頻度の履歴を用いて、今回のHW操作がされたときの時刻情報と次回にHW操作がされたときの時刻情報の間隔の短さ、すなわち頻度を判断する。この結果を、切り替えモジュール80に渡す。

## [0164]

なお、時刻情報とは時刻を特定可能な情報であり、本実施形態にではゲストによって実行されたページ間の分岐命令の回数である。時刻情報には、物理計算機90が備える時計の時刻の値や、実行されたゲスト命令数、実行されたゲストのCALL命令及びRET命令数等、時刻を近似できる任意の情報が利用できる。

## [0165]

頻度判断モジュール70は、モジュール初期化時など、必要に応じて、物理計算機90の記憶装置91に格納された方式切り替え条件を参照し、その内容を頻度判断モジュール70内に格納しておく。

## [0166]

頻度判断モジュール70によって、今回のHW操作と次回のHW操作の間隔が長い、すなわち、低頻度であると判断された場合は、切り替えモジュール80は、CPU400の動作モードをHW操作完全禁止モードに戻す。すなわち、切り替えモジュール80は、CPU400に対してVMentry操作を実行する。この操作の後に、処理をゲストコードに分岐する。

### [0167]

一方、頻度判断モジュール70によって、今回のHW操作と次回のHW操作の間隔が短い、すなわち、高頻度であると判断された場合は、切り替えモジュール80は、まず、次に実行するゲストコードに対応する変換コードのアドレスを、コード管理モジュール30

20

10

30

40

に問い合わせる。そして、CPU400の動作モードをHW操作部分禁止モードに戻す。 すなわち、切り替えモジュール80は、CPL増加分岐命令を実行する。この命令の後に 、処理を変換コードに分岐する。この処理によって、変換コードはHW操作部分禁止モー ドで実行される。なお、CPL増加分岐命令には、IRET命令、SYSRET命令、S YSEXIT命令等を用いる。

### [0168]

切り替えモジュール80からの問い合わせに対して、コード管理モジュール30は、変換コード管理表35を検索して、問い合わせコードに対応する変換コードが存在するか否かを判断する。変換コードが存在する場合は、当該変換コードのアドレスを返す。問い合わせコードに対応する変換コードが存在しない場合は、コード生成モジュール40を呼び出して、変換コードを生成し、生成された変換コードのアドレスを返す。

[0169]

コード生成モジュール 4 0 は、次のゲストコードページを参照して対応するシャドウコード 3 1 (31-1~31-p)と昇格コード 3 2 (32-1)とを、コード管理モジュール 3 0 が管理するメモリ上に生成する。そして、その内容を変換コード管理表 3 5 に登録する。

[0170]

[0171]

なお、ゲスト20によって、シャドウコード31に対応するゲストコード21が書き換えられる場合がある。エミュレーションモジュール60は、この書き換えを検出した場合は、切り替えモジュール80に、この書き換えを通知する。切り替えモジュール80は、書き換えられたページに対応していた変換コードを無効化して、これを変換コード管理表35に記録する。

[0172]

なお、記憶装置 9 1 に格納されているコード変換の設定表 9 5 は、前述の第 1 の実施の 形態の図 3 と同一である。

[0173]

図20は、頻度判断モジュール70の構成ブロック図である。

[0174]

頻度判断モジュール70は、第1の実施の形態の頻度判断モジュール71とほぼ同一であるが、HW操作履歴表73を含んでいる。

[0175]

HW操作頻度表72は、あるHW操作Xと次に実行されたHW操作との間隔が短い、すなわち高頻度である場合に、そのHW操作Xを実施するゲストコードの物理アドレスを格納する。HW操作履歴表73は、最後に処理されたHW操作を実行した動作主体(OSまたはAP)と、ゲストコードの物理アドレスと、時刻情報を格納する。

[0176]

図21は、HW操作頻度表72の一例の説明図である。

[0177]

HW操作頻度表72は、ゲスト20毎に、当該エントリの有効性を示すvalidビットと、ゲストコードの物理アドレスとを格納する。

[0178]

HW操作頻度表 7 2 は、ゲスト識別番号フィールド 5 0 1 と、 v a l i d ビットフィールド 5 0 4 と、ゲストコードの物理アドレスフィールド 5 0 9 とを含む。

10

20

30

40

[0179]

ゲスト識別番号フィールド 5 0 1 は、ゲスト 2 0 毎に付された識別子であるゲスト識別番号を格納する。 v a l i d ビットフィールド 5 0 4 は、ゲストコードのうち、その物理アドレスが、 H W 操作の間隔が短い、すなわち、高頻度である部分の始点又は中間点であることを示す v a l i d ビットを格納する。ゲストコードの物理のアドレスフィールド 5 0 9 は、ゲストコードの物理アドレスを格納する。

[ 0 1 8 0 ]

なお、本表に含まれないゲストコードの物理アドレスは、HW操作の間隔が長い、すなわち、低頻度である部分の始点又は中間点である。また、validビットの初期値は0、すなわち無効である。

[0181]

図22は、HW操作履歴表73の一例の説明図である。

[0182]

HW操作履歴表 7 3 は、ゲスト識別番号フィールド 5 0 1 と、 C P U 識別番号フィールド 5 0 2 と、動作主体フィールド 5 2 3 と、ゲストコードの物理アドレスフィールド 5 0 9 と、時刻情報フィールド 5 1 0 とを含む。

[0183]

ゲスト識別番号フィールド501は、前述の図21のゲスト識別番号と同じものを格納する。CPU識別番号フィールド502は、CPU400を識別するための番号を格納する。動作主体フィールド523は、最後に処理されたHW操作を実行した主体はOSであるかAPであるかを区別するための識別子を格納する。ゲストコードの物理アドレス509は、前述の図21のゲストコード物理アドレスと同じものを格納する。時刻情報フィールド510は、前述のように、最後に処理されたHW操作の時点での、ゲストによって実行されたページ間の分岐命令の回数を格納する。なお、物理計算機90が備える時計の時刻の値や、実行されたゲスト命令数、実行されたゲストのCALL命令及びRET命令数等、時刻を近似できる任意の情報が利用できる。

[0184]

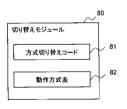

図23は、切り替えモジュール80の構成ブロック図である。

[0185]

切り替えモジュール80は、方式切り替えコード81と動作方式表82とを含む。

[0186]

なお、動作方式とは、エミュレーションモジュールの呼び出し方式である。本実施の形態では、VT方式又はコード変換方式を用いる。方式切り替えコード81は、頻度に応じて動作方式であるコード変換方式とVT方式を切り替え、その結果を操作方式表82に格納する。動作方式表82は、現在適用中の動作方式を格納する。

[0187]

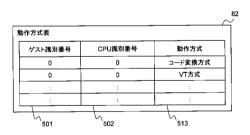

図24は、動作方式表82の一例の説明図である。

[0188]

動作方式表 8 2 は、ゲスト識別番号フィールド 5 0 1 と、 C P U 識別番号フィールド 5 0 2 と動作方式フィールド 5 1 3 とを含む。

[0189]

ゲスト識別番号フィールド501は、前述の図21のHW操作頻度表72のゲスト識別番号と同じものを格納する。CPU識別番号フィールド502は、前述の図22のHW操作履歴表73のCPU識別番号と同じものを格納する。動作方式フィールド513は、現在適用中の動作方式を格納する。なお、動作方式の初期値は「VT方式」である。

[0190]

図25は、変換コード管理表35の一例の説明図である。

[0191]

変換コード管理表 3 5 は、ゲスト 2 0 毎に、ゲストコードの物理アドレス 5 0 9 と、そのゲストコードに対応する変換コードの物理アドレス 5 1 1 を格納する。

10

20

30

40

[0192]

変換コード管理表 3 5 は、ゲスト識別番号フィールド 5 0 1 と、ゲストコード物理アドレスフィールド 5 0 9 と、 v a l i d ビットフィールド 5 0 4 と、変換コードの物理アドレス 5 1 1 とを含む。

[0193]

ゲスト識別番号フィールド501は、前述の図21のHW操作頻度表72のゲスト識別番号と同じものを格納する。ゲストコードの物理アドレス509は、前述の図21のゲストコード物理アドレスと同じものを格納する。validビットフィールド504は、その物理アドレスに対応する変換コードが有効であるか否かを示す識別子であるvalidビットを格納する。このvalidビットの初期値は0(無効)である。変換コードの物理アドレスフィールド509は、ゲストコードの物理アドレスに対応する変換コードの物理アドレスを格納する。

[0194]

次に、第3の実施の形態の、ゲスト20の動作に伴うVMM10の処理を、フローチャートを参照して説明する。

[0195]

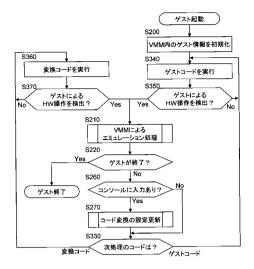

図26は、VMM10がゲスト20を稼動するときの処理のフローチャートである。

[0196]

図 2 6 は、前述の第 1 の実施の形態の図 8 のフローチャートに類似しているが、最初の H W 操作は必ずゲストコードによってエミュレーションされる点が異なる。

[0197]

まず、仮想計算機の電源の投入等によって、ゲスト20が起動すると、VMM10は、 自身が有するゲスト情報を参照し、起動されたゲストに関するエントリを初期化する(S 200)。

[0198]

その後、ゲスト 2 0 が、H W 操作完全禁止モードでゲストコードを実行する(S 3 4 0 )。 V M M 1 0 は、ゲスト 2 0 によるゲストコードの実行によって、H W 操作コードの実行を検出したか否かを判断する(S 3 5 0 )。

[0199]

ゲスト20によるHW操作コードの実行を検出した場合は、VMM10は、例外イベントを発生させて、CPU400の動作モードをHW操作許可モードに変更する。その後、ステップS210へ進む。一方、VMM10が、HW操作コードの実行を検出しない場合は、ステップS340に戻り、次のゲストコードを実行する。

[0200]

ステップS210では、VMM10は、HW操作のエミュレーション処理を実施する。 また、このエミュレーション処理によって、次に実行するコードの種別を決定する。

[0201]

次に、VMM10は、仮想計算機の電源遮断等によってゲスト20が終了したか否かを 判断する。ゲスト20が終了したと判断した場合は、VMM10は、当該ゲスト20の処理を終了する。一方、ゲスト20は終了せず、動作が継続すると判断した場合は、ステップS260に進む。

[0202]

S 2 6 0 では、V M M 1 0 は、システム管理者によるコード変換の設定の変更がコンソール9 2 に入力されたか否かを判断する。コンソール9 2 への入力によってコード変換の設定9 5 に変更があったと判断した場合は、ステップS 2 7 0 に移行する。一方、コード変換の設定9 5 に変更がなければ、ステップS 3 3 0 に進む。

[0203]

ステップ S 2 7 0 では、物理計算機 9 0 は、コンソール 9 2 によって設定された内容を受け取り、記憶装置 9 1 のコード変換の設定 9 5 を更新するコード変換の設定更新処理を実行する。

10

20

30

40

10

20

30

40

50

[0204]

次に、VMM10は、次にゲスト20によって実行される処理が変換コードの実行であるか否かを判断する(S330)。次の処理が変換コードの実行であると判断した場合は、VMM10は、CPL増加分岐命令を実行してCPU動作モードをHW操作部分禁止モードに変更する。その後、ステップS360に進む。一方、次の処理がゲストコードの実行であると判断した場合は、VMM10は、VMentry操作を実行してCPU動作モードをHW操作完全禁止モードに変更する。その後、ステップS340に戻る。

[0205]

ステップS360では、VMM10は、HW操作部分禁止モードで変換コードを実行する。

[0206]

次に、VMM10は、ゲスト20による昇格コードの実行を検出し、エミュレーションモジュール60が呼ばれたか否かを判断する(S370)。昇格コードが実行されてエミュレーションモジュールが呼ばれた場合は、VMM10は、CPU動作モードをHW操作許可モードに変更して、S210へ進む。一方、VMM10が、昇格コードの実行を検出しない場合は、ステップS360に戻り、次の変換コードを実行する。

[0207]

図 2 7 は、図 2 6 のステップ S 2 1 0 の V M M のエミュレーション処理のフローチャートである。

[0208]

まず、ゲスト20によって実行されたHW操作コードの内容に応じて、VMM10がエミュレーションを実施する(S100)。

[0209]

このとき、VMM10は、エミュレーションの内容はコード変換の対象となったゲストコードの変更を含むか否かを判断する(S110)。なお、VMM10は、ライトプロテクトを設定したページに対してゲスト20が書き込みを行った場合に、当該ページにゲストコードが存在するか否かを判定して、ゲストコードの変更の有無を判断する。変更しないと判断した場合は、ステップS120に進む。一方、変更すると判断した場合は、ステップS120に進む。

[0210]

ステップ S 1 2 0 では、 V M M 1 0 は、書き換えられたゲストコードに対応する変換コードの無効化処理を実行する ( S 1 2 0 )。

[0211]

ステップS130では、VMM10は、HW操作の頻度判定処理を実行する。この処理によって、ゲスト20によってなされたHW操作の頻度が高頻度であるか低頻度であるかが判定される。

[0212]

次に、VMM10は、HW操作の頻度判定処理の結果、頻度が高頻度であるか否かを判断する(S140)。高頻度であると判断した場合はステップS170に進む。低頻度であると判断した場合はステップS180に進む。

[0213]

ステップS170では、VMM10は、以降のHW操作の検出手段をコード変換方式に 決定する。そして、動作方式表82の当該ゲスト及びCPUに対応する動作方式513を コード変換方式に変更する。

[0214]

一方、ステップ S 1 8 0 では、V M M 1 0 は、以降の H W 操作の検出手段を V T 方式に決定する。そして、動作方式表 8 2 の当該ゲスト及び C P U に対応する動作方式 5 1 3 を V T 方式に変更する。

[0215]

次に、VMM10は、S160では、当該HW操作の次の処理の選択処理を実行する。

[0216]

図28は、図27のステップS120の変換コードの無効化処理のフローチャートである。

[0217]

VMM10は、変換コード管理表35を参照して、書き換えられたゲストコードに対応するエントリのvalidビットをクリアする。すなわち、validビットを0に変更する(S600)。

[0218]

次に、VMM10は、書き換えられたゲストコードに対応するライトプロテクトを解除する(S620)。

[0219]

図29は、図27のステップS130の頻度判断処理のフローチャートである。

[0220]

まず、VMM10は、HW操作履歴表73を参照して、1つ前に実行されたHW操作に関するエントリを取得する。そして、当該エントリの、動作主体とゲストコードの物理アドレスと時刻情報とを取得する(S900)。

[0221]

次にVMM10は、1つ前に実行されたHW操作の動作主体がアプリケーション(AP)であるか否かを判断する(S990)。動作主体がAPであると判断した場合はステップS940に進む。動作主体がAPではない、すなわち動作主体がOSであると判断した場合はステップS910に進む。

[0222]

ステップ S 9 1 0 では、 V M M 1 0 は、今回の H W 操作の時刻情報と 1 つ前の H W 操作の時刻情報との差から、 H W 操作の間隔を算出する。

[0223]

次に、VMM10は、算出したHW操作の間隔と、コード変換の設定表95から取得した閾値とを比較する。比較の結果、算出したHW操作の間隔が取得した閾値の範囲以内であるか否かを判断する(S920)。算出したHW操作の間隔が閾値以内であると判断した場合はステップS930に進む。一方、算出したHW操作の間隔が、閾値を越えると判断した場合はステップS940に進む。

[0224]

ステップS930では、VMM10は、1つ前のHW操作に関するエントリのゲストコードの物理アドレスを、HW操作頻度表72に追加する。そして、追加したエントリのvalidビットを1に設定する。これによって、このゲストコードの物理アドレスが、高頻度部分の始点又は中間点として設定される。

[0225]

ステップS940では、VMM10は、今回実行されたHW操作に関するエントリ、すなわち、動作主体とゲストコードの命令アドレスと時刻情報とをHW操作履歴表73に格納する。

[0226]

次に、VMM10は、今回実行されたHW操作に関して、当該HW操作のゲストコードの命令アドレスがHW操作頻度表72に含まれているか否かを判断する(S950)。HW操作頻度表72に含まれていると判断した場合はステップS740に進む。HW操作頻度表72に含まれていないと判断した場合はステップS730に進む。

[0227]

ステップS740では、VMM10は、今回実行されたHW操作は高頻度部分の始点又は中間点であると判定する。

[0228]

ステップS730では、VMM10は、今回実行されたHW操作は低頻度部分の始点又は中間点であると判定する。

10

20

30

40

10

20

30

40

50

[0229]

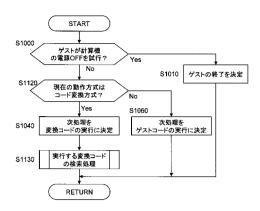

図30は、図27のステップS160の次処理の選択処理のフローチャートである。

[0230]

V M M 1 0 は、ゲスト 2 0 が終了したか否か、すなわち、ゲスト 2 0 が稼働する仮想計算機 2 1 の電源が O F F にされたか否かを判断する(S 1 0 0 0 )。仮想計算機 2 1 の電源が O F F にされたと判断した場合はステップ S 1 0 1 0 に進む。そうでなければステップ S 1 1 2 0 に進む。

[0231]

ステップ S 1 0 1 0 では、 V M M 1 0 は、次に実行する処理として、ゲスト終了を選択する。

[0232]

ステップS1120では、VMM10は、動作方式表82を参照して、現在の動作方式がコード変換方式であるか否かを判断する。現在の動作方式がコード変換方式であると判断した場合はステップS1040に進む。現在の動作方式がVT方式であると判断した場合はステップS1060に進む。

[0233]

ステップS1040では、VMM10は、次に実行する処理に変換コードを適用することを決定する。そして、次に実行する変換コードを検索するための変換コードの検索処理を実行する(S1130)。

[0234]

一方、ステップ S 1 0 6 0 では、 V M M 1 0 は、次に実行する処理にゲストコードを適用することを決定する。

[0235]

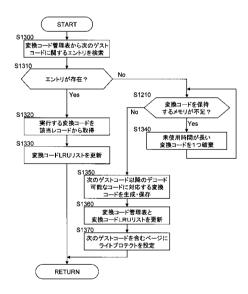

図31は、図30のステップS1130の変換コードの検索処理のフローチャートである。

[0236]

まず、VMM10は、変換コード管理表35を参照して、今回処理したHW操作コードの次のゲストコードに対応するエントリを検索する(S1300)。

[0237]

次に、VMM10は、該当するエントリが存在するか否かを判断する(S1310)。 エントリが存在すると判断した場合はステップS1320に進む。エントリが存在しない と判断した場合はステップS1210に進む。

[0238]

ステップS1210では、VMM10は、変換コードを格納するためのメモリ領域のメモリ容量に必要な空き容量が存在するか否かを判断する。メモリ領域に必要な空き容量が存在しないと判断した場合は、ステップS1340に移行する。必要な空き容量が存在すると判断した場合は、ステップS1350に進む。

[0239]

ステップS1340では、VMM10は、変換コードLRUリスト36を参照して、未使用時間の最も長い変換コードを含む要素を一つ選択する。そして、選択された要素に含まれる変換コードに属するページの物理アドレスを無効化することによって、変換コードをメモリ領域から破棄する。さらに、選択された要素に含まれる変換コードの情報を、変換コードLRUリスト36から削除する。そして、ステップS1210に戻る。すなわち、必要な空き容量が確保できるまで、未使用時間の最も長い変換コードをメモリ領域から破棄する。

[0240]

一方、ステップS1350では、VMM10は、次に実行されるゲストコード以降のコードのうち、デコード可能なコードに対応する変換コードを生成し、生成されたコードを保存する。なお、変換コードはシャドウコードと昇格コードとで構成される。シャドウコードはゲストコードに対応して生成される。また、シャドウコードはゲストコードに含ま

れるHW操作コードの代わりに、昇格コードを含む。昇格コードはエミュレーションモジ ュールを呼び出すためのCPL減少分岐命令を含む。なお、本ステップにおいて生成した 変換コードを、検索の結果とする。

#### [0241]

次に、VMM10は、生成した変換コードの情報を変換コード管理表35に格納する。 さらに、変換コードLRUリスト36の末尾に生成した変換コードの情報を追加する(S 1360)

### [0242]

次に、VMM10は、ゲストコードの書き換えを検出するために、当該ゲストコードを 含むページにライトプロテクトを設定する(S1370)。

### [0243]

一方、ステップS1320では、VMM10は、次に実行すべき変換コードのアドレス を、検索されたエントリから取得する。取得された変換コードを検索の結果とする。

### [0244]

次に、VMM10は、当該エントリに対応する変換コードの組を最新に変更することに よって、変換コードLRUリスト36を更新する(S1330)。

### [0245]

なお、図26のステップS270のコード変換の設定更新処理は、前述の第1の実施の 形態の図14のフローチャートと同一である。

## [0246]

以上のように、本発明の第3の実施の形態の仮想計算機システムではゲスト20によっ てHW操作を含むゲストコードの実行が要求されたときに、VMM10は、当該HW操作 の実行間隔に応じて処理方法を変える。すなわち、当該HW操作を二つの部分に分け、実 行間隔が小さい部分(すなわち、実行頻度が高い)に実行効率の高いコード変換方式を適 用し、実行間隔が大きい(すなわち、実行頻度が高い)部分にメモリ消費量の少ないVT 方式を適用する。このようにすることによって、高性能と省メモリとを両立することが可 能なエミュレーション処理が可能となる。

【産業上の利用可能性】

## [0247]

本発明は、CPUとして、VT・i機能を搭載したIPFやVT・x機能を搭載したx 86を備えた仮想計算機システムに適用することができる。

30

40

50

10

20

## 【図面の簡単な説明】

### [0248]

【図1】本発明の第1の実施の形態の、仮想計算機システムを動作させる物理計算機のブ ロック図である。

【図2】本発明の第1の実施の形態の、仮想計算機システムのソフトウェアとハードウェ アの要部を示すブロック図である。

【図3】本発明の第1及び第3の実施の形態の、コード変換の設定表の説明図である。

【図4】本発明の第1の実施の形態の、頻度判断モジュールのブロック図である。

【図5】本発明の第1の実施の形態の、HW操作頻度表の説明図である。

- 【図6】本発明の第1の実施の形態の、変換コード管理表の説明図である。

- 【図7】本発明の第1の実施の形態の、変換コードLRUリストの説明図である。

- 【図8】本発明の第1の実施の形態の、VMMの動作のフローチャートである。

- 【図9】本発明の第1の実施の形態の、エミュレーション処理を示すフローチャートであ

【図10】本発明の第1の実施の形態の、変換コードの無効化処理のフローチャートであ

【図11】本発明の第1の実施の形態の、ハードウェア操作の頻度判断処理のフローチャ ートである。

【図12】本発明の第1の実施の形態の、エミュレーション後の次処理選択処理のフロー

チャートである。

- 【図13】本発明の第1の実施の形態の、コード変換方式の適用処理のフローチャートである。

- 【図14】本発明の第1の実施の形態の、方式切り替え条件の更新処理のフローチャートである。

- 【図15】本発明の第2の実施の形態の、コード変換の設定表の説明図である。

- 【図16】本発明の第2の実施の形態の、HW操作頻度表の説明図である。

- 【図 1 7 】本発明の第 2 の実施の形態の、変換コードの無効化処理のフローチャートである。

- 【図18】本発明の第2の実施の形態の、HW操作の頻度判断処理のフローチャートであ 10る。

- 【図19】本発明の第3の実施の形態の、仮想計算機システムのソフトウェアとハードウェアの要部のブロック図である。

- 【図20】本発明の第3の実施の形態の、頻度判断モジュールのプロック図である。

- 【図21】本発明の第3の実施の形態の、HW操作頻度表の説明図である。

- 【図22】本発明の第3の実施の形態の、HW操作履歴表の説明図である。

- 【図23】本発明の第3の実施の形態の、切り替えモジュールのブロック図である。

- 【図24】本発明の第3の実施の形態の、動作方式表の説明図である。

- 【図25】本発明の第3の実施の形態の、変換コード管理表の説明図である。

- 【図26】本発明の第3の実施の形態の、VMMの動作のフローチャートである。

- 【図27】本発明の第3の実施の形態の、エミュレーション処理のフローチャートである

- 【図 2 8 】本発明の第 3 の実施の形態の、変換コードの無効化処理のフローチャートである。

- 【図29】本発明の第3の実施の形態の、ハードウェア操作の頻度判断処理のフローチャートである。

- 【図30】本発明の第3の実施の形態の、エミュレーション後の次処理選択処理のフローチャートである。

- 【図31】本発明の第3の実施の形態の、変換コードの検索処理のフローチャートである

### 【符号の説明】

## [0249]

- 1 0 V M M

- 20 ゲスト

- 30 コード変換モジュール

- 3 1 シャドウコード

- 3 2 昇格コード

- 35 変換コード管理表

- 40 コード生成モジュール

- 50 例外イベントハンドラモジュール

- 60 エミュレーションモジュール

- 7 0 頻度判断モジュール

- 80 切り替えモジュール

- 90物理計算機

- 9 1 記憶装置

- 92 コンソール

30

20

【図1】

【図2】

【図3】

【図4】

【図6】

## 【図5】

√<sub>506</sub>

√503

√ 501

| E換コード管理表    |                      |       |                     |  |  |

|-------------|----------------------|-------|---------------------|--|--|

| ゲスト識別<br>番号 | ゲストコード物理ページの<br>アドレス | valid | 変換コード物理ページの<br>アドレス |  |  |

| 0           | 0x00000000           | 1     | 0xF0001000          |  |  |

| 0           | 0x00001000           | 0     | •                   |  |  |

| :           | :                    | :     | ;                   |  |  |

| : -         | :                    |       | :                   |  |  |

# 【図7】

# 【図8】

【図9】

【図10】

## 【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

| 作頻度表   |       |        |

|--------|-------|--------|

| スト識別番号 | 命令タイプ | 頻度フラグ  |

| 0      | タイプ#0 | 1(高頻度) |

| 0      | タイプ#2 | 0(低頻度) |

| :      | :     | :      |

| :      | :     | _ :    |

【図17】

【図18】

【図19】

【図20】

【図21】

【図22】

| ゲスト識別番号 | valid | ゲストコード物理ページのアドレス |

|---------|-------|------------------|

| 0       | 1     | 0x000003FC       |

| 0       | 1     | 0x0000123E       |

| 0       | 0     | _                |

| :       | :     | :                |

| ゲスト<br>識別番号 | CPU<br>識別番号 | 動作主体 | ゲストコードの<br>物理アドレス | 時刻情報  |

|-------------|-------------|------|-------------------|-------|

| 0           | 0           | os   | 0x0000010F6       | 7000  |

| 1           | 0           | AP   | 0xFFFFFFE         | 25000 |

| :           | :           | :    | :                 | :     |

| :           | -           | :    | :                 | :     |

【図23】

【図24】

## 【図25】

# 【図26】

## 【図27】

## 【図28】

## 【図29】

## 【図30】

## 【図31】

## フロントページの続き

# (72)発明者 對馬 雄次

東京都国分寺市東恋ヶ窪一丁目280番地 株式会社日立製作所 中央研究所内

審査官 吉田 美彦

(56)参考文献 特開平01-243155(JP,A)

特開昭62-031437(JP,A)

特開2000-22221(JP,A)

(58)調査した分野(Int.CI., DB名)

G06F 9/46