## (19) 대한민국특허청(KR)

## (12) 등록특허공보(B1)

(51) 국제특허분류(Int. Cl.)

**H01L 23/12** (2006.01) **H01L 23/48** (2006.01) **H01L 33/48** (2010.01)

(21) 출원번호

10-2013-0041236

(22) 출원일자

2013년04월15일

심사청구일자

2018년03월14일

(65) 공개번호

10-2014-0123851

(43) 공개일자

2014년10월23일

(56) 선행기술조사문헌

US07915739 B2\*

US20080236876 A1\*

US20100237378 A1\*

\*는 심사관에 의하여 인용된 문헌

(45) 공고일자 2019년12월26일

(11) 등록번호 10-2059402

(24) 등록일자 2019년12월19일

(73) 특허권자

### 삼성전자주식회사

경기도 수워시 영통구 삼성로 129 (매탄동)

(72) 발명자

### 임성준

경기 용인시 수지구 진산로 90, 519동 905호 (풍덕천동, 진산마을삼성5차아파트)

### 손민영

서울 금천구 시흥대로 165, 207동 1404호 ( 시흥동, 남서울힐스테이트아파트)

(뒷면에 계속)

(74) 대리인

특허법인씨엔에스

전체 청구항 수 : 총 8 항

심사관: 김진우

### (54) 발명의 명칭 전자소자 패키지 및 이에 사용되는 패키지 기판

#### (57) 요 약

본 발명의 실시 형태에 따른 전자소자 패키지는, 일 면 상에 형성된 제1 전국 및 제2 전국을 포함하는 전자소자; 및 전자소자가 탑재되는 제1 면 및 제1 면에 대향하는 제2 면을 갖는 패키지 기판을 포함하며, 패키지 기판은, 제1 면 상에서 제1 전국 및 제2 전국 각각과 전기적으로 연결되는 제1 전국패턴 및 제2 전국패턴과, 전자소자가 탑재되는 영역의 외측에 위치하는 적어도 하나의 비아홀과, 제1 면 상에 비아홀과 인접하여 위치하는 요철부를 포함한다.

#### 대 표 도 - 도2

### (72) 발명자

### 권용민

서울 강서구 공항대로75길 17, 107동 302호 (염창 동, 한화꿈에그린아파트)

## 김학환

경기 수원시 영통구 태장로82번길 32, 105동 401호 (망포동, 동수원엘지빌리지1차)

### 명 세 서

#### 청구범위

#### 청구항 1

일 면 상에 형성된 제1 전극 및 제2 전극을 포함하는 전자소자; 및

상기 전자소자가 탑재되는 제1 면 및 상기 제1 면에 대향하는 제2 면을 갖는 패키지 기판을 포함하며,

상기 패키지 기판은,

상기 제1 면 상에서 상기 제1 전극 및 상기 제2 전극 각각과 전기적으로 연결되는 제1 전극패턴 및 제2 전극패턴 단과.

상기 전자소자가 탑재되는 영역의 외측에 위치하는 적어도 하나의 비아홀과,

상기 제1 면 상에 상기 비아홀과 인접하여 위치하는 요철부를 포함하고,

상기 제1 전극패턴은 상기 제1 전극으로부터, 상기 제1 전극과 상기 비아홀의 사이에 배치되는 상기 요철부를 지나며, 상기 비아홀의 내측벽을 통해 상기 제2 면으로 연장되는 전자소자 패키지.

### 청구항 2

삭제

#### 청구항 3

제1항에 있어서,

상기 요철부는 오목부를 포함하고,

상기 오목부는 적어도 일부가 상기 제1 전극패턴 또는 상기 제2 전극패턴으로 충전되는 것을 특징으로 하는 전 자소자 패키지.

#### 청구항 4

제1항에 있어서,

상기 요철부는 상기 제1 전극 및 상기 제2 전극 중 인접하는 어느 하나와 상기 비아홀을 연결하는 라인에 수직 하게 배치되는 것을 특징으로 하는 전자소자 패키지.

### 청구항 5

삭제

#### 청구항 6

제1항에 있어서,

상기 제1 전극패턴 및 상기 제2 전극패턴 각각은,

상기 제1 전극 및 상기 제2 전극과 각각 연결되는 소자 접속부;

상기 제2 면 상에 위치하는 외부 접속부;

상기 비아홀 내에 위치하며 상기 소자 접속부와 상기 외부 접속부를 연결하는 연결부; 및

상기 요철부 상의 노치부를 포함하는 것을 특징으로 하는 전자소자 패키지.

#### 청구항 7

제6항에 있어서,

상기 전자소자는 평면 상에서 원형의 형상을 가지고,

상기 패키지 기판은 사각형의 형상을 가지며,

상기 패키지 기판의 네 개의 꼭지점 각각에서, 상기 전자소자 외측에 상기 비아홀이 위치하는 것을 특징으로 하는 전자소자 패키지.

### 청구항 8

제1항에 있어서.

상기 전자소자는, 제1 도전형 반도체층, 활성층 및 제2 도전형 반도체층을 구비하는 발광구조물을 포함하고, 상기 제1 전극 및 상기 제2 전극은 각각 상기 제1 도전형 반도체층 및 상기 제2 도전형 반도체층과 접속되는 것

#### 청구항 9

제1항에 있어서.

봉지부를 더 포함하고,

상기 봉지부를 이루는 물질은 상기 비아홀 내로 연장되어 상기 비아홀을 충전하는 것을 특징으로 하는 전자소자 패키지.

### 청구항 10

전자소자가 탑재되는 제1 면 및 상기 제1 면에 대향하는 제2 면을 가지며,

상기 제1 면에 위치하는 전극패턴;

을 특징으로 하는 전자소자 패키지.

상기 전자소자가 탑재되는 영역의 외측에 위치하는 비아홀; 및

상기 제1 면 상에 상기 비아홀과 인접하여 위치하는 요철부;

를 포함하고.

상기 전극패턴은 상기 전자소자가 탑재되는 영역으로부터, 상기 전자소자가 탑재되는 영역과 상기 비아홀의 사이에 배치되는 상기 요철부를 지나며, 상기 비아홀의 내측벽을 통해 상기 제2 면으로 연장되는 패키지 기판.

### 발명의 설명

## 기술분야

[0001] 본 발명은 전자소자 패키지 및 이에 사용되는 패키지 기판에 관한 것이다.

#### 배경기술

[0002] 전자소자(electronic device)는 외부로부터 전기적 에너지를 인가 받아 구동되는 소자로서, 반도체 발광소자 또

는 태양 전지와 같은 광전자소자를 포함한다.

[0003] 일반적으로, 전자소자는 패키지 상태로 원하는 기기에 장착되어 사용될 수 있다. 이러한 패키지에 사용되는 패키지 기판은 전자소자의 전극에 대응되는 전극패턴을 포함할 수 있다. 또한, 패키지 기판은 관통 실리콘 비아 (Through Si Via, TSV)를 포함할 수 있다. 관통 실리콘 비아 기술은, 패키지 기판을 관통하는 홀을 형성하고, 패키지 기판의 위와 아래를 연결하여 전자소자 및 외부 장치 사이에 신호 및 파워를 전달할 수 있도록 하는 기술이다.

### 발명의 내용

#### 해결하려는 과제

- [0004] 본 발명의 기술적 사상이 이루고자 하는 기술적 과제 중 하나는, 초소형 패키지의 구현이 가능한 전자소자 패키지 및 패키지 기판을 제공하는 것이다.

- [0005] 본 발명의 기술적 사상이 이루고자 하는 기술적 과제 중 하나는, 신뢰성이 향상된 전자소자 패키지 및 패키지 기판을 제공하는 것이다.

### 과제의 해결 수단

- [0006] 본 발명의 일 실시 형태에 따른 전자소자 패키지는, 일 면 상에 형성된 제1 전국 및 제2 전국을 포함하는 전자소자; 및 상기 전자소자가 탑재되는 제1 면 및 상기 제1 면에 대향하는 제2 면을 갖는 패키지 기판을 포함하며, 상기 패키지 기판은, 상기 제1 면 상에서 상기 제1 전국 및 상기 제2 전국 각각과 전기적으로 연결되는 제1 전국패턴 및 제2 전국패턴과, 상기 전자소자가 탑재되는 영역의 외측에 위치하는 적어도 하나의 비아홀과, 상기 제1 면 상에 상기 비아홀과 인접하여 위치하는 요철부를 포함한다.

- [0007] 본 발명의 일부 실시 형태에서, 상기 요철부는, 상기 제1 전극 및 제2 전극 중 적어도 하나와, 상기 비아홀의 사이에 배치될 수 있다.

- [0008] 본 발명의 일부 실시 형태에서, 상기 요철부는 오목부를 포함하고, 상기 오목부는 적어도 일부가 상기 제1 전극 패턴 또는 상기 제2 전극패턴으로 충진될 수 있다.

- [0009] 본 발명의 일부 실시 형태에서, 상기 요철부는 볼록부를 포함하고, 상기 볼록부는 상기 제1 전극패턴 또는 상기 제2 전극패턴으로 덮일 수 있다.

- [0010] 본 발명의 일부 실시 형태에서, 상기 요철부는 상기 제1 전극 및 상기 제2 전극 중 인접하는 어느 하나와 상기 비아홀을 연결하는 라인에 수직하게 배치될 수 있다.

- [0011] 본 발명의 일부 실시 형태에서, 상기 요철부는 상기 라인과 동일한 방향에서의 길이보다 상기 라인에 수직한 방향에서의 길이가 더 길 수 있다.

- [0012] 본 발명의 일부 실시 형태에서, 상기 요철부는 두 개 이상이 서로 인접하여 나란히 배열될 수 있다.

- [0013] 본 발명의 일부 실시 형태에서, 상기 제1 전극패턴 및 상기 제2 전극패턴은 상기 제2 면 상으로 연장될 수 있다.

- [0014] 본 발명의 일부 실시 형태에서, 상기 제1 전극패턴 및 상기 제2 전극패턴 중 적어도 하나는 상기 비아홀 내측벽을 통해 상기 제2 면 상으로 연장될 수 있다.

- [0015] 본 발명의 일부 실시 형태에서, 상기 제1 전극패턴 및 상기 제2 전극패턴 각각은, 상기 제1 전극 및 상기 제2 전극과 각각 연결되는 소자 접속부; 상기 제2 면 상에 위치하는 외부 접속부; 상기 비아홀 내에 위치하며 상기 소자 접속부와 상기 외부 접속부를 연결하는 연결부; 및 상기 요철부 상의 노치부를 포함할 수 있다.

- [0016] 본 발명의 일부 실시 형태에서, 상기 전자소자는 평면 상에서 원형의 형상을 가지고, 상기 소자 접속부는 적어 도 한 면이 원형의 일부에 해당하는 곡면으로 이루어질 수 있다.

- [0017] 본 발명의 일부 실시 형태에서, 상기 패키지 기판은 사각형의 형상을 가지고, 상기 패키지 기판의 네 개의 꼭지

점 각각에서, 상기 전자소자 외측에 상기 비아홀이 위치할 수 있다.

- [0018] 본 발명의 일부 실시 형태에서, 상기 전자소자는, 제1 도전형 반도체층, 활성층 및 제2 도전형 반도체층을 구비하는 발광구조물을 포함하고, 상기 제1 전극 및 상기 제2 전극은 각각 상기 제1 도전형 반도체층 및 상기 제2 도전형 반도체층과 접속될 수 있다.

- [0019] 본 발명의 일부 실시 형태에서, 봉지부를 더 포함하고, 상기 봉지부를 이루는 물질은 상기 비아홀 내로 연장되어 상기 비아홀을 충진할 수 있다.

- [0020] 본 발명의 일 실시 형태에 따른 패키지 기판은, 전자소자가 탑재되는 제1 면 및 상기 제1 면에 대향하는 제2 면을 가지며, 상기 제1 면에 위치하는 전극패턴; 상기 전자소자가 탑재되는 영역의 외측에 위치하는 비아홀; 및 상기 제1 면 상에 상기 비아홀과 인접하여 위치하는 요철부;를 포함한다.

### 발명의 효과

- [0021] 초소형 패키지의 구현이 가능하면서도 신뢰성이 확보될 수 있는 전자소자 패키지 및 패키지 기판이 제공될 수 있다.

- [0022] 본 발명의 다양하면서도 유익한 장점과 효과는 상술한 내용에 한정되지 않으며, 본 발명의 구체적인 실시형태를 설명하는 과정에서 보다 쉽게 이해될 수 있을 것이다.

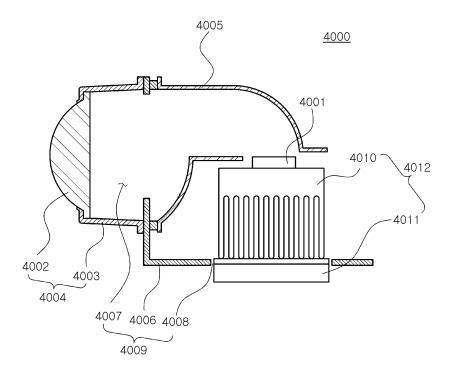

### 도면의 간단한 설명

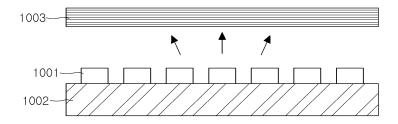

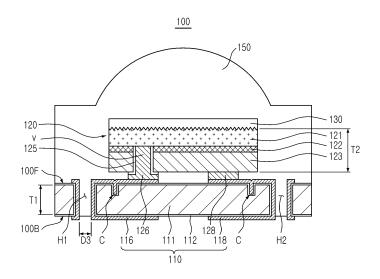

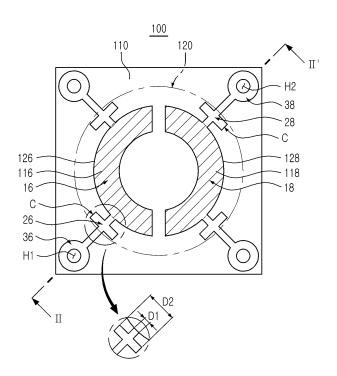

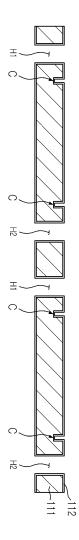

[0023] 도 1은 본 발명의 일 실시 형태에 따른 반도체 발광소자 패키지를 개략적으로 도시하는 평면도다.

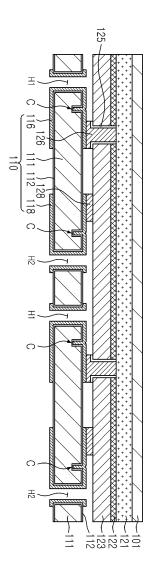

도 2는 도 1의 절취선  $\Pi$ - $\Pi$ '을 따라 절취한 반도체 발광소자 패키지의 단면을 개략적으로 도시하는 단면도이다.

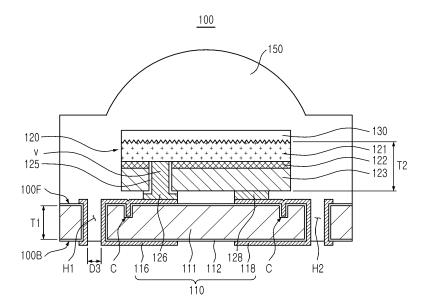

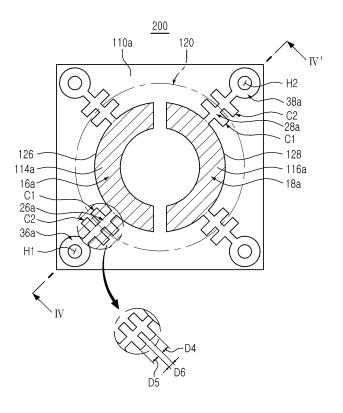

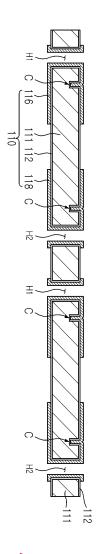

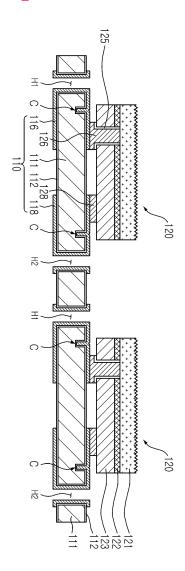

도 3은 본 발명의 일 실시 형태에 따른 반도체 발광소자 패키지를 개략적으로 도시하는 평면도다.

도 4는 도 3의 절취선 IV-IV'을 따라 절취한 반도체 발광소자 패키지의 단면을 개략적으로 도시하는 단면도이다.

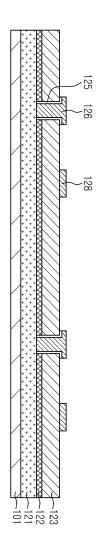

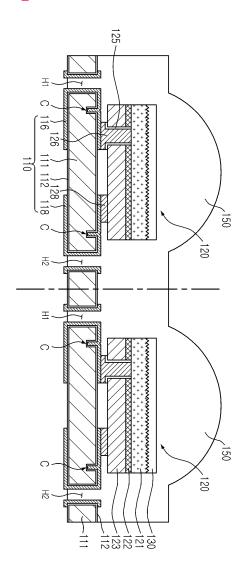

도 5는 본 발명의 일 실시 형태에 따른 반도체 발광소자 패키지를 개략적으로 도시하는 단면도이다.

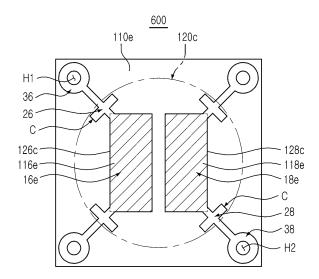

도 6 내지 도 8은 본 발명의 일 실시 형태에 따른 반도체 발광소자 패키지를 개략적으로 도시하는 평면도다.

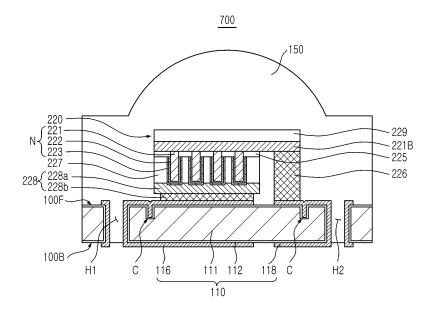

도 9는 본 발명의 일 실시 형태에 따른 반도체 발광소자 패키지를 개략적으로 도시하는 단면도이다.

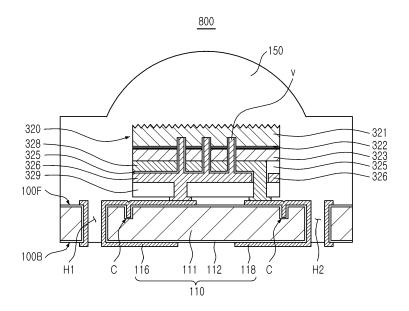

도 10은 본 발명의 일 실시 형태에 따른 반도체 발광소자 패키지를 개략적으로 도시하는 단면도이다.

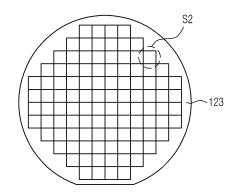

도 11a 내지 도 11i는 본 발명의 일 실시 형태에 따른 반도체 발광소자 패키지의 제조 방법을 개략적으로 나타 내는 주요 단계별 도면들이다.

도 12 및 도 13은 본 발명의 일 실시 형태에 따른 반도체 발광소자 패키지를 백라이트 유닛에 적용한 예를 나타 낸다.

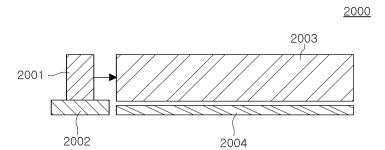

도 14는 본 발명의 실시예에 의한 반도체 발광소자 패키지를 조명 장치에 적용한 예를 나타낸다.

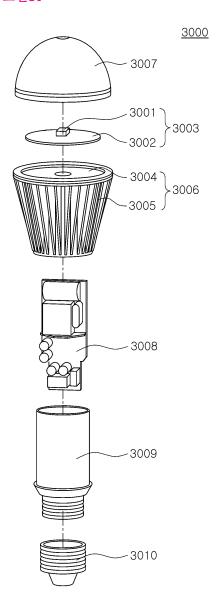

도 15는 본 발명의 실시예에 의한 반도체 발광소자 패키지를 헤드 램프에 적용한 예를 나타낸다.

### 발명을 실시하기 위한 구체적인 내용

- [0024] 이하, 첨부된 도면을 참조하여 본 발명의 바람직한 실시 형태들을 다음과 같이 설명한다.

- [0025] 본 발명의 실시 형태는 여러 가지 다른 형태로 변형되거나 여러 가지 실시 형태가 조합될 수 있으며, 본 발명의 범위가 이하 설명하는 실시 형태로 한정되는 것은 아니다. 또한, 본 발명의 실시 형태는 당해 기술분야에서 평균적인 지식을 가진 자에게 본 발명을 더욱 완전하게 설명하기 위해서 제공되는 것이다. 따라서, 도면에서의 요소들의 형상 및 크기 등은 보다 명확한 설명을 위해 과장될 수 있으며, 도면 상의 동일한 부호로 표시되는 요

소는 동일한 요소이다.

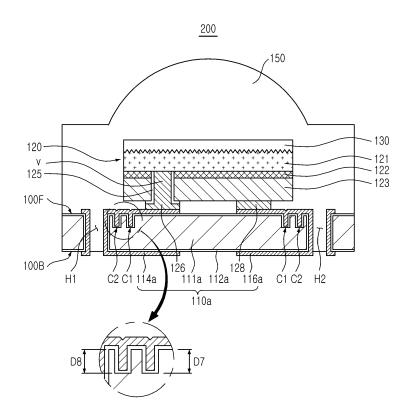

- [0026] 도 1은 본 발명의 일 실시 형태에 따른 반도체 발광소자 패키지를 개략적으로 도시하는 평면도다. 도 2는 도 1 의 절취선 Ⅱ-Ⅱ'을 따라 절취한 반도체 발광소자 패키지의 단면을 개략적으로 도시하는 단면도이다.

- [0027] 본 발명의 실시 형태에 따른 전자소자 패키지는, 반도체 발광소자 패키지 또는 태양 전지 패키지와 같은 광전자소자 패키지, 메모리 소자 패키지 또는 로직 소자 패키지 등을 포함할 수 있다. 구체적으로, 도 1 및 도 2는 전자소자 패키지 중 일 예로 반도체 발광소자 패키지를 도시하며, 이하에서 반도체 발광소자 패키지를 이용하여 본 발명을 설명한다.

- [0028] 도 1에서는 이해를 돕기 위하여 도 2의 구성 요소 중 파장변환부(130) 및 렌즈부(150)를 생략하고 도시하였다.

- [0029] 도 1 및 도 2를 참조하면, 본 발명의 일 실시 형태에 따른 반도체 발광소자 패키지(100)는 패키지 기판(110) 및 패키지 기판(110) 상에 탑재된 반도체 발광소자(120)를 포함하며, 파장변환부(130) 및 렌즈부(150)를 더 포함할 수 있다. 본 실시 형태의 반도체 발광소자 패키지(100)는 칩 스케일 패키지(Chip Scale Package, CSP)이며, 웨이퍼 레벨 패키지(Wafer Level Package, WLP)일 수 있다.

- [0030] 패키지 기판(110)은 몸체부(111), 몸체부(111)를 둘러싸는 절연층(112) 및 절연층(112) 상의 제1 및 제2 전극패 턴(116, 118)을 포함할 수 있다. 반도체 발광소자(120)는 제1 도전형 반도체층(121), 활성층(122) 및 제2 도전 형 반도체층(123)의 발광구조물, 및 제1 및 제2 전극(126, 128)을 포함할 수 있다.

- [0031] 본 명세서에서, '상', '상부', '상면', '하', '하부', '하면', '측면' 등의 용어는 도면을 기준으로 한 것이며, 실제로는 소자나 패키지가 배치되는 방향에 따라 달라질 수 있을 것이다.

- [0032] 패키지 기판(110)은 반도체 발광소자(120)가 탑재되는 제1 면(110F) 및 제1 면(110F)에 대향하는 제2 면(110B)을 갖는다. 패키지 기판(110)에는 패키지 기판(110)을 관통하는 제1 및 제2 비아홀들(H1, H2)이 형성될 수 있으며, 제1 면(110F) 상에 요철부들(C)을 포함할 수 있다.

- [0033] 몸체부(111)는 Si과 같은 반도체 물질, AIN 및 Al<sub>2</sub>O<sub>3</sub>와 같은 세라믹 물질, 금속 물질 또는 고분자 물질을 포함할 수 있다. 몸체부(111)는 도전성 또는 절연성 물질을 포함할 수 있으며, 예를 들어, 복수의 금속충들이 적충된 형태를 가질 수 있다. 몸체부(111)의 두께(T1)는 약 600 µm 내지 약 800 µm의 범위일 수 있다.

- [0034] 요철부들(C)이 몸체부(111)의 제1 면(110F) 상에 형성될 수 있다. 요철부들(C)은 반도체 발광소자(120)의 제1 전극(126)과 제1 비아홀(H1)의 사이 및 제2 전극(128)과 제2 비아홀(H2)의 사이에 위치할 수 있다. 또한, 도 1에 도시된 것과 같이, 요철부들(C)은 제1 및 제2 전극패턴(116, 118)이 제1 및 제2 비아홀(H1, H2)로 연장되는 방향에 수직한 방향으로 배치될 수 있다. 본 실시 형태에서는 총 4개의 요철부들(C)이 예시되었으나, 요철부 (C)의 개수는 이에 한정되지 않으며 다양할 수 있다. 본 실시 형태에서 요철부들(C)은 오목부일 수 있으며, 노치 또는 리세스된 영역일 수 있다. 요철부들(C)은 제1 및 제2 전극패턴(116, 118) 중 어느 하나로 충진될 수 있으며, 실시 형태에 따라 요철부들(C)의 일부만 충진될 수도 있다.

- [0035] 절연층(112)은 몸체부(111)의 적어도 일면을 덮도록 형성될 수 있다. 절연층(112)은 전기 절연성을 갖는 물질, 예컨대 수지로 이루어질 수 있다. 절연층(112)은 몸체부(111)가 절연성 물질로 이루어진 경우, 생략될 수도 있다.

- [0036] 제1 및 제2 전극패턴(116, 118)은 각각 반도체 발광소자(120)의 제1 및 제2 전극(126, 128)과 연결되며, 절연층 (112) 상에 형성되어 몸체부(111)와 전기적으로 절연될 수 있다. 제1 및 제2 전극패턴(116, 118)은 각각 제1 및 제2 비아홀(H1, H2)의 내측벽을 통해 제1 면(110F)으로부터 제2 면(110B) 상으로 연장될 수 있다.

- [0037] 제1 및 제2 전극패턴(116, 118)은 도 1에 도시된 것과 같이, 반도체 발광소자(120)의 제1 및 제2 전극(126,

128)과 연결되는 영역인 소자 연결부(16, 18), 패키지 기판(110)의 요철부들(C) 상의 노치부(26, 28) 및 제1 및 제2 비아홀(H1, H2) 둘레의 연결부(36, 38)를 포함할 수 있다. 소자 연결부(16, 18)는 반도체 발광소자(120)의 제1 및 제2 전극(126, 128)과 연결되며, 반도체 발광소자(120)의 형상과 유사한 외측면을 가질 수 있다. 예를 들어, 소자 연결부(16, 18)는 도 1에 도시된 것과 같이 원형의 일부를 이루는 곡면을 포함할 수 있다. 도면에는 도시되지 않았으나, 제2 면(110B) 상에도 소자 연결부(16, 18)와 유사한 형상을 가지며 외부 장치와 연결되는 외부 연결부가 형성될 수 있다. 노치부(26, 28)는 제1 및 제2 전극패턴(116, 118)이 제1 및 제2 비아홀(H1, H2)을 향해 연장되는 방향에 수직한 방향으로 연장되는 폭(D1)보다 넓은 폭(D2)을 가질 수 있다. 노치부(26, 28)는 소자 연결부(16, 18)와 연결부(36, 38)의 사이에 위치하며, 노치부(26, 28)가 제1 및 제2 비아홀(H1, H2)로부터 이격된 거리는 도면에 도시된 것에 한정되지 않고 실시 형태에 따라 변화될 수 있다.

- [0038] 제1 및 제2 비아홀들(H1, H2)은 예를 들어, 관통 실리콘 비아(Through Si Via, TSV)일 수 있다. 제1 및 제2 비아홀들(H1, H2)은 도 1에 도시된 것과 같이, 평면 상에서 반도체 발광소자(120)가 탑재된 영역의 외측에 위치할 수 있다. 제1 및 제2 비아홀들(H1, H2)은 패키지 기판(110)의 네 개의 꼭지점에 각각 배치될 수 있다. 이러한 제1 및 제2 비아홀들(H1, H2)의 배치에 의해, 제1 및 제2 비아홀들(H1, H2) 상부에 상대적으로 얇은 반도체 발광소자(120)가 배치되지 않아, 반도체 발광소자 패키지(100)의 제조 시 발생할 수 있는 반도체 발광소자(120)의 기계적 손상을 방지할 수 있다. 또한, 제1 및 제2 비아홀들(H1, H2) 의 상부가 개방되어, 렌즈부(150)의 형성 시, 제1 및 제2 비아홀들(H1, H2) 내부가 동시에 채워질 수 있어 공정이 단순화될 수 있다.

- [0039] 제1 및 제2 비아홀들(H1, H2)의 내부 지름(D3)은 약 250 ㎞ 내지 약 350 ㎞의 범위일 수 있다. 제1 및 제2 비아홀들(H1, H2)의 내측면에는 절연층(112) 및 제1 및 제2 전극패턴(116, 118)이 형성될 수 있다.

- [0040] 반도체 발광소자(120)는 패키지 기판(110) 상에 탑재되며, 제1 도전형 반도체층(121), 활성층(122) 및 제2 도전형 반도체층(123)의 발광구조물, 및 제1 및 제2 전극(126, 128)을 포함할 수 있다. 상기 발광구조물은 도 1에 도시된 것과 같이, 원형의 형상을 가질 수 있다. 상기 발광구조물의 두께(T2)는 약 3 ㎞ 내지 약 10 ㎞의 범위일 수 있다. 본 실시 형태에 따르면, 상대적으로 큰 지름(D3)을 가지는 제1 및 제2 비아홀들(H1, H2) 상에 상대적으로 작은 두께(T2)를 가지는 상기 발광구조물이 배치되지 않을 수 있어서, 제조 공정 중이나 그 이후에 발생할 수 있는 반도체 발광소자(120)의 손상이 방지될 수 있다.

- [0041] 제1 및 제2 도전형 반도체층(121, 123)은 각각 n형 반도체층 및 p형 반도체층이 될 수 있으나, 이에 제한되는 것은 아니며, 반대로 각각 p형 및 n형 반도체층이 될 수도 있을 것이다. 제1 및 제2 도전형 반도체층(121, 123)은 질화물 반도체, 예컨대, Al<sub>x</sub>In<sub>y</sub>Ga<sub>1-x-y</sub>N (0≤x≤1, 0≤y≤1, 0≤x+y≤1)의 조성을 갖는 물질로 이루어질 수 있으며, 각각의 층은 단일층으로 이루어질 수도 있지만, 도핑 농도, 조성 등의 특성이 서로 다른 복수의 층을 구비할 수도 있다. 다만, 제1 및 제2 도전형 반도체층(121, 123)은 질화물 반도체 외에도 AlInGaP나 AlInGaAs 계열의 반도체를 이용할 수도 있을 것이다.

- [0042] 제1 도전형 반도체층(121)과 제2 도전형 반도체층(123)의 사이에 배치된 활성층(122)은 전자와 정공의 재결합에 의해 소정의 에너지를 갖는 광을 방출하며, 양자우물층과 양자장벽층이 서로 교대로 적층된 다중 양자우물(MQW) 구조, 예컨대, 질화물 반도체일 경우, GaN/InGaN 구조가 사용될 수 있다. 다만, 단일 양자우물(SQW) 구조가 사용될 수도 있을 것이다.

- [0043] 또한, 도면에는 도시되지 않았으나, 반도체 발광소자(120)는 제1 도전형 반도체충(121) 상에 위치하는 성장용 기판을 더 포함할 수 있다. 상기 성장용 기판은 제1 도전형 반도체충(121)이 형성되지 않은 면 상에 형성된 요 철 구조를 포함할 수 있다. 상기 성장용 기판은 레이저 리프트 오프 등의 공정을 수행하여 제거될 수 있다. 또한, 도면에는 도시되지 않았으나, 패시베이션층이 반도체 발광소자(120)의 상면 및 측면 중 적어도 일부를 덮도록 형성될 수도 있다. 상기 패시베이션층은 실리콘 질화물 또는 실리콘 산화물일 수 있다.

- [0044] 제1 도전형 반도체층(121)은 표면에 요철이 형성된 구조를 가질 수 있으며, 이에 의해 광 추출 효율이 더욱 향

상될 수 있다. 예컨대, 상기 요철은 상기 성장용 기판을 발광구조물로부터 제거한 후에 제1 도전형 반도체층 (121)을 습식 식각하거나 플라즈마를 이용하여 건식 식각함으로써 얻어질 수 있다.

- [0045] 제1 및 제2 전극(126, 128)은 반도체 발광소자(120)의 하면에 위치할 수 있다. 제1 및 제2 전극(126, 128)은, 도 1에 도시된 것과 같이, 제1 및 제2 전극패턴(116, 118)의 소자 연결부(16, 18)와 동일한 형상을 가질 수 있으며, 각각 소자 연결부(16, 18)와 연결될 수 있다.

- [0046] 제1 및 제2 전극(126, 128)은 당 기술 분야에서 공지된 도전성 물질, 예컨대, Ag, Al, Ni, Cr, Cu, Au, Pd, Pt, Sn, W, Rh, Ir, Ru, Mg, Zn, Ti 또는 이들을 포함하는 합금 물질 중 하나 이상으로 이루어질 수 있다. 본실시예에서, 제1 전극(126)은 제2 도전형 반도체층(123) 및 활성층(122)을 관통하여 제1 도전형 반도체층(121) 과 전기적으로 연결되는 비아(v)를 포함할 수 있다. 비아(v)의 둘레에는 제1 전극(126)을 제2 도전형 반도체층(123) 및 활성층(122)과 전기적으로 절연시키기 위한 전극절연층(125)이 위치할 수 있다. 비아(v)는 복수 개형성될 수 있으며, 비아(v)는 예를 들어 복수의 행 및 열로 배열될 수도 있다.

- [0047] 파장변환부(130)는 반도체 발광소자(120)로부터 방출된 빛에 의해 여기되어 다른 파장의 빛을 내는 형광체를 포함할 수 있다. 이러한 형광체의 방출광과 반도체 발광소자(120)의 방출광이 결합하여 백색광 등 원하는 출력광을 얻을 수 있다. 실시 형태에 따라, 파장변환부(130)는, 렌즈부(150) 내에서 반도체 발광소자(120)로부터 소정 거리로 이격된 형태로 형성될 수도 있다.

- [0048] 렌즈부(150)는 반도체 발광소자(120)를 덮어 봉지하는 봉지부이며, 패키지 기판(110)의 제1 및 제2 비아홀들 (H1, H2)의 내부 공간을 채울 수 있다. 렌즈부(150)는 예를 들어, 실리콘(silicone), 에폭시, 유리, 플라스틱 등 광 투과성 및 내열성이 우수한 재료를 사용할 수 있다. 렌즈부(150)는 볼록 또는 오목한 형상의 렌즈 구조에 의해 렌즈부(150) 상면을 통해 방출되는 빛의 지향각을 조절하는 것이 가능하다. 렌즈부(150)는 발광구조물(S)에서 발생한 빛을 최소한의 손실로 통과시킬 수 있는 높은 투명도의 수지로 선택될 수 있으며, 예를 들어 탄성 수지, 실리콘, 에폭시 수지 또는 플라스틱을 사용할 수 있다.

- [0049] 렌즈부(150)는 도시된 바와 같이 상면이 볼록한 돔 형상의 구조로 형성될 수 있지만, 본 발명은 이에 한정되지는 않는다. 예를 들어, 조명 장치 또는 백라이트 유닛에서 광 확산을 향상시키기 위하여, 렌즈부(150)는 표면상에 위치하는 콜로이드 입자를 포함할 수 있으며, 평평한 형태의 상면을 가질 수도 있다. 또는, 렌즈부(150)는 비구면 및/또는 비대칭 형상을 가지거나, 상면에 요철이 형성될 수도 있다. 또한, 카메라 플래시 등에서 광의 직진성을 향상시키기 위하여 프레넬 형상의 집광부를 포함할 수 있으며, 상면에 요철이 형성될 수도 있다.

- [0050] 제1 및 제2 비아홀들(H1, H2)의 내부가 렌즈부(150) 물질로 채워짐으로써 반도체 발광소자 패키지(100)의 제조 공정이 단순화될 수 있다. 제1 및 제2 비아홀들(H1, H2) 내부의 렌즈부(150) 물질이 내부 또는 외부로부터의 열에 의해 팽창하는 경우, 제1 및 제2 전극패턴(116, 118)에 가해지는 응력이 요철부들(C) 상의 노치부(26, 2 8)에 의하여 완화될 수 있다. 따라서, 제1 및 제2 전극패턴(116, 118)은 제1 및 제2 비아홀들(H1, H2) 내부의 렌즈부(150)과 연계되어 변형되지 않을 수 있어, 반도체 발광소자(120)의 손상을 방지할 수 있다.

- [0051] 도 3은 본 발명의 일 실시 형태에 따른 반도체 발광소자 패키지를 개략적으로 도시하는 평면도다. 도 4는 도 3 의 절취선 IV-IV'을 따라 절취한 반도체 발광소자 패키지의 단면을 개략적으로 도시하는 단면도이다.

- [0052] 도 3 및 도 4를 참조하면, 본 발명의 일 실시 형태에 따른 반도체 발광소자 패키지(200)는 패키지 기판(110a) 및 패키지 기판(110a) 상에 탑재된 반도체 발광소자(120)를 포함하며, 파장변환부(130) 및 렌즈부(150)를 더 포함할 수 있다.

- [0053] 패키지 기판(110a)은 몸체부(111a), 몸체부(111a)를 둘러싸는 절연층(112a) 및 절연층(112a) 상의 제1 및 제2 전극패턴(116a, 118a)을 포함할 수 있다. 패키지 기판(110a)에는 패키지 기판(110a)을 관통하는 제1 및 제2 비아홀들(H1, H2)이 형성될 수 있으며, 상면에 요철부들(C1, C2)을 포함할 수 있다.

- [0054] 본 실시 형태에서는, 도 1 및 도 2의 반도체 발광소자 패키지(100)에서와 달리, 요철부들(C1, C2)은 서로 인접하게 배열되는 제1 및 제2 요철부들(C1, C2)을 포함한다. 제1 및 제2 요철부들(C1, C2)은 반도체 발광소자 (120)의 제1 전극(126)과 제1 비아홀(H1)의 사이 및 제2 전극(128)과 제2 비아홀(H2)의 사이에 위치할 수 있다. 제1 및 제2 요철부들(C1, C2)은 제1 및 제2 전극패턴(116, 118)이 제1 및 제2 비아홀(H1, H2)로 연장되는 방향으로 각각 일정 너비(D4, D5)를 가질 수 있으며, 제1 요철부(C1)의 너비(D4)와 제2 요철부(C2)의 너비(D5)는 실시 형태에 따라 동일하거나 상이할 수 있다. 제1 요철부(C1)와 제2 요철부(C2) 사이의 이격 거리(D6)도 실시 형태에 따라 변화될 수 있다. 또한, 제1 및 제2 요철부(C1, C2)는 패키지 기판(110a)의 상면으로부터 각각 일정 깊이(D7, D8)로 형성될 수 있으며, 제1 요철부(C1)의 깊이(D7)와 제2 요철부(C2)의 깊이(D8)는 실시 형태에 따라 동일하거나 상이할 수 있다. 상기 너비(D4, D5), 상기 이격 거리(D6) 및 상기 깊이(D7, D8)는 예를 들어, 제1 및 제2 전극패턴(116a, 118a)의 두께, 폭 및 형상에 따라 적절하게 선택될 수 있다.

- [0055] 제1 및 제2 전극패턴(116a, 118a)은 도 1에 도시된 것과 같이, 반도체 발광소자(120)의 제1 및 제2 전극(126, 128)과 연결되는 영역인 소자 연결부(16a, 18a), 패키지 기판(110a)의 요철부들(C1, C2) 상의 노치부(26a, 28a) 및 제1 및 제2 비아홀(H1, H2) 둘레의 연결부(36a, 38a)를 포함할 수 있다.

- [0056] 본 실시 형태의 반도체 발광소자 패키지(200)에서는, 제1 및 제2 비아홀들(H1, H2) 내부의 렌즈부(150) 물질이 내부 또는 외부로부터의 열에 의해 팽창하는 경우에도, 나란하게 배치된 제1 및 제2 요철부들(C1, C2)에 의하여 제1 및 제2 전극패턴(116a, 118a)에 가해지는 스트레스의 완화가 더욱 효율적으로 이루어질 수 있다.

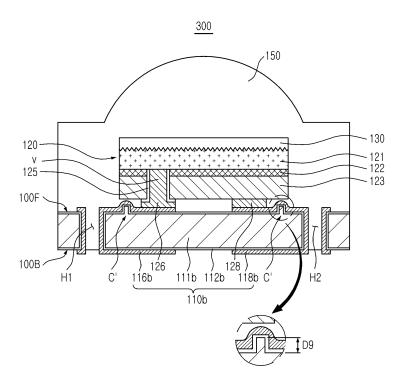

- [0057] 도 5는 본 발명의 일 실시 형태에 따른 반도체 발광소자 패키지를 개략적으로 도시하는 단면도이다.

- [0058] 도 5를 참조하면, 본 발명의 일 실시 형태에 따른 반도체 발광소자 패키지(300)는 패키지 기판(110b) 및 패키지 기판(110b) 상에 탑재된 반도체 발광소자(120)를 포함하며, 파장변환부(130) 및 렌즈부(150)를 더 포함할 수 있다.

- [0059] 패키지 기판(110b)은 몸체부(111b), 몸체부(111b)를 둘러싸는 절연충(112b) 및 절연충(112b) 상의 제1 및 제2 전극패턴(116b, 118b)을 포함할 수 있다. 패키지 기판(110b)에는 패키지 기판(110b)을 관통하는 제1 및 제2 비아홀들(H1, H2)이 형성될 수 있으며, 상면에 요철부들(C')을 포함할 수 있다.

- [0060] 본 실시 형태에서는, 도 1 및 도 2의 반도체 발광소자 패키지(100)에서와 달리, 요철부들(C')은 볼록부 형태를 갖는다. 요철부들(C')은 반도체 발광소자(120)의 제1 전극(126)과 제1 비아홀(H1)의 사이 및 제2 전극(128)과 제2 비아홀(H2)의 사이에 위치할 수 있다. 요철부들(C')은 패키지 기판(110b)의 상면으로부터 일정 높이(D9)로 형성될 수 있으며, 상기 높이(D9)는 예를 들어, 제1 및 제2 전극패턴(116b, 118b)의 두께, 요철부(C')의 폭, 및 반도체 발광소자(120)의 발광구조물과 패키지 기판(100b) 사이의 거리에 따라 적절하게 선택될 수 있다. 특히, 상기 높이(D9)는 제1 및 제2 전극패턴(116b, 118b)이 반도체 발광소자(120)의 발광구조물과 접촉되지 않도록 결정될 수 있다.

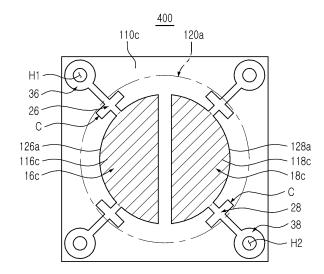

- [0061] 도 6 내지 도 8은 본 발명의 일 실시 형태에 따른 반도체 발광소자 패키지를 개략적으로 도시하는 평면도다. 도 6 내지 도 8에서, 반도체 발광소자 패키지의 일부 구성 요소는 생략되어 도시되어 있을 수 있으며, 생략된 구성 요소에 대해서는 도 1 및 도 2를 참조하여 상술한 설명을 참조한다.

- [0062] 도 6을 참조하면, 본 발명의 일 실시 형태에 따른 반도체 발광소자 패키지(400)는 패키지 기판(110c) 및 패키지 기판(110c) 상에 탑재된 반도체 발광소자(120a)를 포함한다. 패키지 기판(110c)은 제1 및 제2 전극패턴(116c, 118c)을 포함할 수 있다.

- [0063] 제1 및 제2 전극패턴(116c, 118c)은 소자 연결부(16c, 18c)를 통해 각각 반도체 발광소자(120a)의 제1 및 제2 전극(126a, 128a)과 연결될 수 있다. 소자 연결부(16c, 18c)는 원형인 반도체 발광소자(120a)의 형상과 유사한 외측면을 가질 수 있다. 본 실시 형태에서, 소자 연결부(16c, 18c)는 반원형의 형상을 가질 수 있다. 도면에는 도시되지 않았으나, 패키지 기판(110c)의 타측 면 상에도 소자 연결부(16c, 18c)와 유사한 형상을 가지며 외

부 장치와 연결되는 외부 연결부가 형성될 수 있다.

- [0064] 제1 및 제2 전극(126a, 128a)은 반도체 발광소자(120a)의 하면에 위치할 수 있다. 제1 및 제2 전극(126a, 128a)은 제1 및 제2 전극패턴(116c, 118c)의 소자 연결부(16c, 18c)와 동일한 형상을 가질 수 있으며, 각각 소자 연결부(16c, 18c)과 연결될 수 있다.

- [0065] 본 실시 형태에 의하면, 제1 및 제2 전극(126a, 128a)과 제1 및 제2 전극패턴(116c, 118c)의 면적이 최대화될 수 있어 반도체 발광소자(120a)로부터 발생하는 열을 효율적으로 방출할 수 있다.

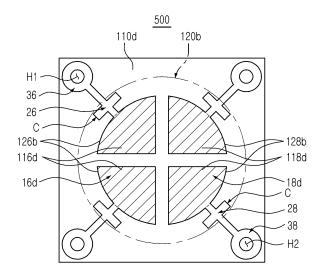

- [0066] 도 7을 참조하면, 본 발명의 일 실시 형태에 따른 반도체 발광소자 패키지(500)는 패키지 기판(110d) 및 패키지 기판(110d) 상에 탑재된 반도체 발광소자(120b)를 포함한다. 패키지 기판(110d)은 제1 및 제2 전극패턴(116d, 118d)을 포함할 수 있다.

- [0067] 제1 및 제2 전극패턴(116d, 118d)은 소자 연결부들(16d, 18d)를 통해 각각 반도체 발광소자(120b)의 제1 및 제2 전극(126b, 128b)과 연결될 수 있다. 소자 연결부들(16d, 18d)은 원형인 반도체 발광소자(120b)의 형상과 유사한 외측면을 가질 수 있다. 본 실시 형태에서, 소자 연결부들(16d, 18d)은 원형의 일부, 예를 들어, 원형의 1/4에 해당하는 형상을 가질 수 있다. 또한, 도 7에 도시된 것과 같이, 제1 및 제2 전극패턴(116d, 118d)은 비아홀들(H1, H2) 중 하나와 연결되는 두 개의 소자 연결부들(16d, 18d)을 각각 포함한다. 도면에는 도시되지 않았으나, 패키지 기판(110d)의 타측 면 상에도 소자 연결부들(16d, 18d)과 유사한 형상을 가지며 외부 장치와 연결되는 외부 연결부가 형성될 수 있다.

- [0068] 제1 및 제2 전극(126b, 128b)은 반도체 발광소자(120b)의 하면에 위치할 수 있다. 제1 및 제2 전극(126b, 128b)은 제1 및 제2 전극패턴(116d, 118d)의 소자 연결부들(16d, 18d)과 동일한 형상을 가지도록 복수 개로 형성될 수 있으며, 각각 소자 연결부들(16d, 18d)과 연결될 수 있다. 다만, 본 발명은 이에 한정되지 않으며, 실시 형태에 따라, 제1 및 제2 전극(126b, 128b)과 제1 및 제2 전극패턴(116d, 118d)의 소자 연결부들(16d, 18d)은 서로 다른 형상을 가질 수도 있다.

- [0069] 본 실시 형태에 의하면, 제1 및 제2 전극(126b, 128b)과 소자 연결부들(16d, 18d)이 복수 개로 형성되어, 반도 체 발광소자 패키지(500)의 신뢰성이 향상될 수 있다.

- [0070] 도 8을 참조하면, 본 발명의 일 실시 형태에 따른 반도체 발광소자 패키지(600)는 패키지 기판(110e) 및 패키지 기판(110e) 상에 탑재된 반도체 발광소자(120c)를 포함한다. 패키지 기판(110e)은 제1 및 제2 전극패턴(116e, 118e)을 포함할 수 있다.

- [0071] 제1 및 제2 전극패턴(116e, 118e)은 소자 연결부들(16e, 18e)를 통해 각각 반도체 발광소자(120c)의 제1 및 제2 전극(126c, 128c)과 연결될 수 있다. 소자 연결부들(16e, 18e)은 사각형의 반도체 발광소자(120c)의 형상과 형상을 가질 수 있다. 본 실시 형태에서, 소자 연결부들(16e, 18e)은 각각 사각형의 형상을 가질 수 있다. 도면에는 도시되지 않았으나, 패키지 기판(110e)의 타측 면 상에도 소자 연결부들(16e, 18e)과 유사한 형상을 가지며 외부 장치와 연결되는 외부 연결부가 형성될 수 있다.

- [0072] 제1 및 제2 전극(126c, 128c)은 반도체 발광소자(120c)의 하면에 위치할 수 있다. 제1 및 제2 전극(126c, 128c)은 제1 및 제2 전극패턴(116e, 118e)의 소자 연결부들(16e, 18e)과 동일한 형상을 가지도록 형성될 수 있으며, 각각 소자 연결부들(16e, 18e)과 연결될 수 있다. 다만, 본 발명은 이에 한정되지 않으며, 실시 형태에따라, 제1 및 제2 전극(126c, 128c)과 제1 및 제2 전극패턴(116e, 118e)의 소자 연결부들(16e, 18e)은 서로 다른 형상을 가질 수도 있다.

- [0073] 도 9는 본 발명의 일 실시 형태에 따른 반도체 발광소자 패키지를 개략적으로 도시하는 단면도이다.

- [0074] 도 9를 참조하면, 본 발명의 일 실시 형태에 따른 반도체 발광소자 패키지(700)는 패키지 기판(110) 및 패키지 기판(110) 상에 탑재된 반도체 발광소자(220)를 포함한다. 본 실시 형태의 반도체 발광소자(220)는 나노 발광 구조물(N)을 포함할 수 있다.

- [0075] 반도체 발광소자(220)는 기판(229), 기판(229) 상에 형성된 제1 도전형 반도체 베이스층(221B), 절연층(225) 및

제1 및 제2 전극(226, 228)을 더 포함할 수 있다. 나노 발광구조물(N)은 제1 도전형 반도체 베이스층(221B)으로부터 성장되어 형성된 제1 도전형 반도체 코어(221), 활성층 (222) 및 제2 도전형 반도체층(223)을 포함한다.

### [0076]

- [0077] 기판(229)은 나노 발광구조물(N)의 성장용 기판으로 제공될 수 있으며, 사파이어, SiC, Si, MgAl<sub>2</sub>O<sub>4</sub>, MgO, LiAlO<sub>2</sub>, LiGaO<sub>2</sub>, GaN 등과 같은 물질을 이용할 수 있으며, 절연성 물질, 도전성 물질, 또는 단결정 또는 다결정의 물질을 이용할 수 있다. 이 경우, 절화물 반도체 성장용 기판으로 널리 이용되는 사파이어의 경우, 육각-롬 보형(Hexa-Rhombo R3c) 대칭성을 갖는 결정체로서 c축 및 a측 방향의 격자상수가 각각 13.001Å과 4.758Å이며, C(0001)면, A(1120)면, R(1102)면 등을 갖는다. 이 경우, 상기 c면은 비교적 질화물 박막의 성장이 용이하며, 고온에서 안정하기 때문에 질화물 성장용 기판으로 주로 사용된다. 한편, 기판(229)으로 사용하기에 적합한 다른 물질로는 Si 기판을 들 수 있으며, 대구경화에 보다 적합하고 상대적으로 가격이 낮은 Si 기판을 사용하여양산성이 향상될 수 있다. Si 기판을 이용하는 경우, 기판(229) 상에 Al<sub>x</sub>Ga<sub>1-x</sub>N과 같은 물질로 이루어진 핵생성 등을 형성한 후 그 위에 원하는 구조의 질화물 반도체를 성장할 수 있을 것이다.

- [0078] 도면에는 도시되지 않았으나, 반도체 발광소자(220)는 기판(229)과 제1 도전형 반도체 베이스층(221B) 사이에 위치하는 버퍼층을 더 포함할 수 있다.

- [0079] 나노 발광구조물(N)은 제1 도전형 반도체 코어(221), 활성충 (222) 및 제2 도전형 반도체충(223)를 포함한다. 도 9에 도시된 바와 같이, 반도체 발광소자(220)는 기판(229) 상에 형성된 복수의 나노 발광구조물들(N)을 포함할 수 있으며, 나노 발광구조물(N)은 코어-셀(core-shell) 구조로서 로드구조로 예시되어 있으나, 이에 한정되지 않고 피라미드 구조와 같은 다른 구조를 가질 수 있다. 예를 들어, 실시 형태에 따라, 나노 발광구조물(N)은 나노 와이어, 양자점, 또는 나노 박스 구조를 포함할 수 있다. 이외에도 나노 발광구조물(N)은 기판(229)면에 대해 경사면을 가지는 구조를 가질 수 있으며, 기판(229)에 평행한 단면의 형상이 삼각형, 사각형, 오각형, 육각형, 팔각형 등의 다각형 또는 원형 등 다양한 형태를 가질 수 있다.

- [0080] 제1 도전형 반도체 베이스층(221B)은 나노 발광구조물(N)의 성장면을 제공하는 층일 수 있다. 절연층(225)은 나노 발광구조물(N)의 성장을 위한 오픈 영역을 제공하며, SiO<sub>2</sub> 또는 SiN<sub>x</sub>와 같은 유전체 물질일 수 있다. 상기 오픈 영역의 크기는 5nm 내지 10um의 범위를 가질 수 있다. 반도체 발광소자(220)는 나노 발광구조물들(N) 사이를 충진하는 충진부(227)를 더 포함한다. 충진부(227)는 나노 발광구조물(N)을 구조적으로 안정화시킬 수 있으며, 빛을 투과 또는 반사하는 역할을 수행할 수 있다. 충진부(227)가 투광성 물질을 포함하는 경우, 충진부(208)는 SiO<sub>2</sub>, SiNx, 탄성 수지, 실리콘(silicone), 에폭시 수지, 고분자 또는 플라스틱과 같은 투명한 물질로 형성될 수 있다. 충진부(227)가 반사성 물질을 포함하는 경우, 충진부(227)는 PPA(polypthalamide) 등의 고분자 물질에 광반사율이 높은 TiO<sub>2</sub> 또는 Al<sub>2</sub>O<sub>3</sub> 등이 함유된 물질을 이용할 수 있으며, 내열 및 내광 안정성이 높은 물질로 이루어질 수 있다.

- [0081] 제1 및 제2 전극(226, 228)은 반도체 발광소자(220)의 하면에 배치될 수 있다. 제1 전극(226)은 제1 도전형 반도체 베이스층(221B)의 노출된 상면에 위치하고, 제2 전극(228)은 나노 발광구조물(N) 및 충진부(227)의 하부에 형성되는 오믹 콘택층(228a) 및 전극 연장부(228b)를 포함한다. 실시 형태에 따라, 오믹 콘택층(228a)과 전극 연장부(228b)는 일체로 형성될 수도 있다. 오믹 콘택층(228a)은 반사성 또는 투광성 물질을 포함할 수 있다. 반사성 물질로 Ag 또는 Al 또는 이들을 포함하는 합금을 포함할 수 있으며, 오믹 콘택층(228a)은 이들의 다층 적층 구조로 형성될 수도 있다. 또는 DBR(distributed Bragg reflector) 구조를 이용한 반사 구조도 이용될 수 있다. 도면에 도시하지는 않았으나, 반도체 발광소자(220)에서 기판(229) 표면에 요철이 형성될 수 있으며, 기판(229) 상에 형광체를 포함하는 과장변환부가 배치될 수 있다. 또한, 실시 형태에 따라, 기판(229)이 제거되고 제1 도전형 반도체 베이스층(221B)의 표면에 요철이 형성되거나 과장변환부가 배치될 수도 있다.

- [0082] 도 10은 본 발명의 일 실시 형태에 따른 반도체 발광소자 패키지를 개략적으로 도시하는 단면도이다.

- [0083] 도 10을 참조하면, 본 발명의 일 실시 형태에 따른 반도체 발광소자 패키지(800)는 패키지 기판(110) 및 패키지 기판(110) 상에 탑재된 반도체 발광소자(320)를 포함한다.

- [0084] 본 실시 형태의 반도체 발광소자(320)는 기판(329), 제1 도전형 반도체층(321), 활성층(322), 제2 도전형 반도 체층(323), 및 제1 및 제2 전극(326, 328)을 포함한다.

- [0085] 제1 전극(326)은 기판(329) 상에 위치하며, 비아(v)를 통하여 제1 도전형 반도체층(321)과 전기적으로 연결되고, 제2 전극(328)은 제1 전극(326) 상에 위치하며 제2 도전형 반도체층(323)과 연결된다. 제1 및 제2 전극(326, 328)은 각각 기판(329) 방향으로 연장되어 기판(329)의 하면으로 노출되며, 이러한 구조를 갖기 위하여, 제2 전극(328)은 제1 전극(326)에 형성된 관통홀을 통과하도록 형성될 수 있다.

- [0086] 비아(v)의 둘레에는 제1 전극(326)을 제2 도전형 반도체층(323) 및 활성층(322)과 전기적으로 절연시키기 위한 전극절연층(325)이 위치할 수 있다. 전극절연층(325)은 제1 전극(326)과 제2 전극(328)의 사이에도 개재될 수 있으며, 이 경우 약 0.7 ㎞ 내지 1.2 ㎞ 두께의 실리콘 산화물 또는 실리콘 질화물이 이용될 수 있다.

- [0087] 도 11a 내지 도 11i는 본 발명의 일 실시 형태에 따른 반도체 발광소자 패키지의 제조 방법을 개략적으로 나타 내는 주요 단계별 도면들이다. 도 11a 내지 도 11i는, 도 1 및 도 2의 발광소자 패키지를 기준으로 설명하지만, 도 3 내지 도 10의 반도체 발광소자 패키지 역시 유사한 방식으로 제조될 수 있을 것이다.

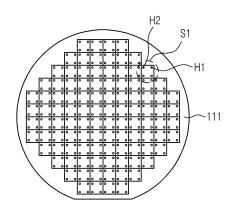

- [0088] 도 11a를 참조하면, 패키지 기판(110)(도 2 참조)를 이루는 몸체부(111)가 웨이퍼 형태로 제공된다. 몸체부 (111)는 복수의 소자 영역들(S1)을 포함할 수 있다.

- [0089] 다음으로, 각 소자 영역(S1)에 몸체부(111)를 관통하는 복수의 제1 및 제2 홀들(H1, H2)이 형성될 수 있다. 복수의 제1 및 제2 홀들(H1, H2)은 몸체부(111)의 전체 영역에 걸쳐 행과 열을 가지며 일정한 패턴으로 배열될 수 있다. 복수의 제1 및 제2 홀들(H1, H2)은 드릴 가공 또는 식각 공정 등을 통해 형성될 수 있다. 복수의 제1 및 제2 홀들(H1, H2)은 하기의 공정에 의해 반도체 발광소자(120)(도 2 참조)가 탑재될 영역의 외측에 형성될 수 있다.

- [0090] 도 11b를 참조하면, 몸체부(111)의 상면에 복수의 요철부들(C)을 형성하는 공정이 수행된다. 복수의 요철부들 (C)은 각각 복수의 제1 및 제2 홀들(H1, H2)에 인접하여 위치할 수 있다.

- [0091] 복수의 요철부들(C)은 도시하지 않은 마스크층 등을 이용하여 식각 공정을 수행함으로써 형성될 수 있다. 상기 식각 공정은 건식 식각 또는 습식 식각 공정일 수 있다.

- [0092] 도 11c를 참조하면, 복수의 제1 및 제2 홀들(H1, H2)의 표면 및 몸체부(111)의 표면을 덮는 절연층(112)을 형성 한다.

- [0093] 절연층(112)은 예를 들어, 유동성을 갖는 수지를 도포하는 방식을 통해 형성될 수 있으며, 이러한 도포 공정은 스크린 프린팅 공정이나 스핀 코팅 공정에 의할 수 있다.

- [0094] 도 11d를 참조하면, 절연층(112) 상에 제1 및 제2 전극패턴(116, 118)을 형성한다.

- [0095] 제1 및 제2 전극패턴(116, 118)은 구리, 은 등의 전기 전도성 물질을 도금이나 증착 공정을 통해 박막 형태로 형성한 후 패터닝 공정을 수행하여 형성될 수 있다. 제1 및 제2 전극패턴(116, 118)은 몸체부(111) 및 절연층 (112)의 적층 구조물의 상면과 하면의 일부, 제1 및 제2 홀들(H1, H2)의 내측면을 덮는 구조로 형성될 수 있다.

- [0096] 제1 및 제2 전극패턴(116, 118)을 형성함으로써, 패키지 기판(110)이 제조될 수 있으며, 제1 및 제2 전극패턴 (116, 118)은 제1 및 제2 홀들(H1, H2)을 통해 패키지 기판(110)의 상면으로부터 하면으로 연장될 수 있다.

- [0097] 실시 형태에 따라, 제1 및 제2 전극패턴(116, 118)은 박막 형태로 제조되어 절연층(112) 상에 부착하는 방식으로 형성될 수도 있다. 이 경우, 패키지 기판(110)의 상면과 하면에 각각 마련된 제1 및 제2 전극패턴(116,

118)을 상호 전기적으로 연결하기 위해 제1 및 제2 홀(H1, H2)의 내측면에 도전층을 형성하는 공정을 별도로 수행할 필요가 있다.

- [0098] 도 11e 및 도 11f를 참조하면, 기판(101) 상에 제1 도전형 반도체층(121), 활성층(122) 및 제2 도전형 반도체층 (123)을 포함하는 발광구조물을 형성하는 공정이 수행된다.

- [0099] 기판(101)은 웨이퍼 레벨일 수 있으며, 복수의 반도체 발광소자들을 형성하기 위한 발광구조물이 동시에 제조될 수 있다. 기판(101)에는 복수의 반도체 발광소자를 이루는 소자 영역들(S2)이 형성될 수 있다. 하나의 소자 영역(S2)은 하나의 반도체 발광소자 칩의 영역이며, 예를 들어, 일 측의 길이가 300 # 내지 10000 # 범위의 길이인 정사각형, 직사각형, 삼각형 또는 다른 형태의 다각형의 형태일 수 있다.

- [0100] 기판(101)은 반도체 성장용 기판으로 제공되며, 예를 들어, Si 기판을 사용할 수 있다. 유기 금속 화학 증착 (Metal Organic Chemical Vapor Deposition, MOCVD), 수소화 기상 에피택시(Hydride Vapor Phase Epitaxy, HVPE), 분자선 에피택시(Molecular Beam Epitaxy, MBE) 등과 같이 당 기술 분야에서 공지된 공정을 이용하여 기판(101) 상에 제1 도전형 반도체층(121), 활성층(122) 및 제2 도전형 반도체층(123)이 순차적으로 성장될 수 있다.

- [0101] 다음으로, 제1 전극(126)을 이루는 비아(v)를 형성하기 위하여 마스크를 이용한 식각 공정에 의해 비아 홀을 형성한 후 전극절연층(125)을 증착할 수 있다. 도면에 도시된 것에 한정되지 않고, 비아(v)는 하나의 소자 영역 (S2)에 복수 개 형성될 수 있다. 복수의 비아들(v)이 제1 도전형 반도체층(121)과 접촉하는 영역의 평면 상에서 차지하는 면적은 반도체 발광소자(120)(도 2 참조)의 면적의 1 % 내지 5 %의 범위가 되도록 비아(v)의 개수 및 접촉 면적이 조절될 수 있다.

- [0102] 다음으로, 상기 발광구조물 상에 도전성 오믹 물질을 증착하여 제1 및 제2 전극(126, 128)을 형성한다. 예를 들어, 제1 및 제2 전극(126, 128)은 오믹 특성 또는 반사 특성을 향상시키기 위해 다양한 재료 또는 적층 구조 가 적용될 수 있다.

- [0103] 도 11g를 참조하면, 도 11d를 참조하여 상술한 패키지 기판(110)과 발광구조물이 형성된 도 11f의 기판(101)을 접합하는 공정이 수행된다.

- [0104] 패키지 기판(110)의 제1 및 제2 전극패턴(116, 118)이 각각 기판(101) 상의 제1 및 제2 전극(126, 128)과 연결 되도록 상기 접합 공정이 수행될 수 있다. 상기 접합 공정은 예를 들어, 공융 접합(eutectic bonding)을 이용할 수 있다. 실시 형태에 따라, 제1 및 제2 전극패턴(116, 118)과 제1 및 제2 전극(126, 128)의 사이에 별도의 솔더볼 또는 접합층이 개재될 수도 있다.

- [0105] 도 11h를 참조하면, 먼저 기판(101)이 제거될 수 있다. 기판(101)이 사파이어와 같이 투명한 물질로 이루어진 경우 레이저를 조사하는 레이저 리프트 오프(laser lift off) 공정을 통해 제거할 수 있으며, 실리콘 기판인 경우, 기계적 연마 또는 폴리싱 또는 습식 또는 건식 식각에 의해 제거할 수 있다. 실시 형태에 따라, 기판(101)은 제거되지 않을 수도 있다.

- [0106] 다음으로, 제1 도전형 반도체층(121)의 상부면에 광추출 효율 향상을 위한 요철을 형성할 수 있다. 기판(101)이 제거되지 않는 경우, 기판(101)의 상부면에 요철을 형성할 수 있다. 상기 요철은 예를 들어, 기계적 컷팅, 연마, 습식 식각 또는 플라즈마를 이용한 건식 식각에 의할 수 있다. 상기 요철은 1.0 ㎞ 내지 3.0 ㎞의 범위의 높이 또는 1.0 ㎞ 내지 3.0 ㎞ 범위의 직경을 가지는 마이크로 요철 패턴 또는 'V'형 홈을 가지는 라인 패턴을 가질 수 있다.

- [0107] 다음으로, 발광구조물을 반도체 발광소자(120) 단위로 분리하는 공정이 수행된다. 이에 의해 복수의 반도체 발광소자들(120)이 형성될 수 있다. 반도체 발광소자(120)는 도 1에 도시된 것과 같이 평면 상에서 원형의 형상을 가질 수 있다. 본 분리 공정이 수행되기 전에, 발광적충체의 적어도 일부를 덮는 패시베이션충(미도시)이 형성될 수도 있다. 또한, 제1 도전형 반도체충(121) 상의 요철은 발광구조물의 분리 공정 후에 형성될 수도 있다.

- [0108] 본 실시 형태에 따르면, 제1 및 제2 비아홀(H1, H2)이 반도체 발광소자(120)의 외측에 배치되어, 상대적으로 큰 직경의 제1 및 제2 비아홀(H1, H2) 상에 반도체 발광소자(120)가 위치하지 않기 때문에, 기판(101)이 제거된 이 후의 공정 중에 반도체 발광소자(120)의 손상이 방지될 수 있다.

- [0109] 도 11i를 참조하면, 반도체 발광소자(120) 상에 파장변환부(130) 및 렌즈부(150)가 형성된다.

- [0110] 파장변환부(130)는 산화물(oxide)계, 규산염(silicate)계, 질화물(nitride)계 및 황화물(sulfide)계 형광체 혼합물 등으로 이루어질 수 있다. 산화물계 물질의 경우, 황색 및 녹색 형광체인 (Y, Lu, Se, La, Gd, Sm)₃(Ga, Al)₅0₁₂:Ce, 청색 형광체인 BaMgAl₁₀0₁₂:Eu, 3Sr₃(PO₄)₂값CaCl:Eu 등이 사용될 수 있으며, 규산염계 물질의 경우, 황색 및 녹색 형광체인 (Ba, Sr)₂SiO₄:Eu, 황색 및 등색 형광체인 (Ba, Sr)₃SiO₅:Eu 등이 사용될 수 있다. 또한, 질화물계 물질의 경우, 녹색 형광체인 β-SiAlON:Eu, 황색 형광체인 (La, Gd, Lu, Y, Sc)₃Si₆N₁₁:Ce, 등색 형광체인 α-SiAlON:Eu, 적색 형광체인 (Sr, Ca)AlSiN₃:Eu, (Sr, Ca)AlSi(ON)₃:Eu, (Sr, Ca)₂Si₅Nぁ:Eu, (Sr, Ca)₂Si₅(ON)ቈ:Eu, (Sr, Ba)SiAl₄N₂:Eu 등이 사용될 수 있으며, 황화물계 물질의 경우, 적색 형광체인 (Sr, Ca)S:Eu, (Y, Gd)₂O₂S:Eu, 녹색 형광체인 SrGa₂S₄:Eu 등이 사용될 수 있다.

- [0111] 렌즈부(150)는 파장변환부(130) 상에, 예컨대, 스프레이 코팅에 의해 형성될 수도 있다. 렌즈부(150)는 반도체 발광소자(120) 및 파장변환부(130)의 상부에 일정 형태로 형성되어 경화되는 방식으로 형성될 수 있다. 렌즈부 (150)는 제1 및 제2 비아홀(H1, H2) 내를 채우도록 형성될 수 있다.

- [0112] 다음으로, 반도체 발광소자 패키지 단위로 일점쇄선을 따라 분리 공정이 수행되어 최종적으로 도 1 및 도 2의 반도체 발광소자 패키지(100)가 형성된다. 상기 분리 공정은 블레이드 소잉 또는 레이저 소잉을 통해 수행될 수 있다. 이를 통해 반도체 발광소자 패키지(100)를 대량으로 제조할 수 있다. 특히, 본 실시 형태의 칩 스케일 패키지(CSP)는 반사컵 구조의 몰딩 구조물이 생략되어 있어 전체적인 패키지 사이즈가 칩의 크기에 대응하므로 제품의 소형화에 적합하다는 장점을 갖는다. 또한, 원형의 반도체 발광소자(120) 상에 원형의 렌즈부(150)를 형성하기 때문에, 패키지의 크기가 더욱 소형화될 수 있다.

- [0113] 도 12 및 도 13은 본 발명의 일 실시 형태에 따른 반도체 발광소자 패키지를 백라이트 유닛에 적용한 예를 나타 낸다.

- [0114] 도 12를 참조하면, 백라이트 유닛(1000)은 기판(1002) 상에 광원(1001)이 실장되며, 그 상부에 배치된 하나 이 상의 광학 시트(1003)를 구비한다. 광원(1001)은 도 1 내지 도 10을 참조하여 상술한 구조 또는 이와 유사한 구조를 갖는 반도체 발광소자 패키지를 이용할 수 있다.

- [0115] 도 12의 백라이트 유닛(1000)에서 광원(1001)은 액정표시장치가 배치된 상부를 향하여 빛을 방사하는 것과 달리, 도 13에 도시된 다른 예의 백라이트 유닛(2000)은 기판(2002) 위에 실장된 광원(2001)이 측 방향으로 빛을 방사하며, 이렇게 방시된 빛은 도광판(2003)에 입사되어 면광원의 형태로 전환될 수 있다. 도광판(2003)을 거친 빛은 상부로 방출되며, 광 추출 효율을 향상시키기 위하여 도광판(2003)의 하면에는 반사층(2004)이 배치될 수 있다.

- [0116] 도 14는 본 발명의 실시예에 의한 반도체 발광소자 패키지를 조명 장치에 적용한 예를 나타낸다.

- [0117] 도 14의 분해사시도를 참조하면, 조명장치(3000)는 일 예로서 벌브형 램프로 도시되어 있으며, 발광모듈(3003) 과 구동부(3008)와 외부접속부(5010)를 포함한다. 또한, 외부 및 내부 하우징(3006, 3009)과 커버부(3007)와 같은 외형구조물을 추가적으로 포함할 수 있다. 발광모듈(3003)은 도 1 내지 도 10을 참조하여 상술한 반도체 발광소자 패키지 구조 또는 이와 유사한 구조를 갖는 광원(3001)과 그 광원(3001)이 탑재된 회로기판(3002)을 포함할 수 있다. 본 실시형태에서는, 하나의 광원(3001)이 회로기판(3002) 상에 실장된 형태로 예시되어 있으나, 필요에 따라 복수 개로 장착될 수 있다.

- [0118] 외부 하우징(3006)은 열방출부로 작용할 수 있으며, 발광모듈(3003)과 직접 접촉되어 방열효과를 향상시키는 열

방출판(3004) 및 조명장치(3000)의 측면을 둘러싸는 방열핀(3005)을 포함할 수 있다. 커버부(3007)는 발광모듈 (3003) 상에 장착되며 볼록한 렌즈형상을 가질 수 있다. 구동부(3008)는 내부 하우징(3009)에 장착되어 소켓구조와 같은 외부접속부(3010)에 연결되어 외부 전원으로부터 전원을 제공받을 수 있다. 또한, 구동부(3008)는 발광모듈(3003)의 반도체 발광소자(3001)를 구동시킬 수 있는 적정한 전류원으로 변환시켜 제공하는 역할을 한다. 예를 들어, 이러한 구동부(3008)는 AC-DC 컨버터 또는 정류회로부품 등으로 구성될 수 있다.

- [0119] 또한, 도면에는 도시되지 않았으나, 조명장치(3000)는 통신 모듈을 더 포함 할 수도 있다.

- [0120] 도 15는 본 발명의 실시예에 의한 반도체 발광소자 패키지를 헤드 램프에 적용한 예를 나타낸다.

- [0121] 도 15를 참조하면, 차량용 라이트 등으로 이용되는 헤드 램프(4000)는 광원(4001), 반사부(4005), 렌즈 커버부 (4004)를 포함하며, 렌즈 커버부(4004)는 중공형의 가이드(4003) 및 렌즈(4002)를 포함할 수 있다. 광원(200 1)은 도 1 내지 도 10 중 어느 하나의 반도체 발광소자 패키지를 적어도 하나 포함할 수 있다.

- [0122] 헤드 램드(4000)는 광원(4001)에서 발생된 열을 외부로 방출하는 방열부(4012)를 더 포함할 수 있으며, 방열부(4012)는 효과적인 방열이 수행되도록 히트싱크(4010)와 냉각팬(4011)을 포함할 수 있다. 또한, 헤드 램프(4000)는 방열부(4012) 및 반사부(4005)를 고정시켜 지지하는 하우징(4009)을 더 포함할 수 있으며, 하우징(4009)은 일면에 방열부(4012)가 결합하여 장착되기 위한 중앙홀(4008)을 구비할 수 있다.

- [0123] 하우정(4009)은 상기 일면과 일체로 연결되어 직각방향으로 절곡되는 타면에 반사부(4005)가 광원(4001)의 상부 측에 위치하도록 고정시키는 전방홀(4007)을 구비할 수 있다. 이에 따라, 반사부(4005)에 의하여 전방측은 개 방되며, 개방된 전방이 전방홀(4007)과 대응되도록 반사부(4005)가 하우징(4009)에 고정되어 반사부(4005)를 통해 반사된 빛이 전방홀(4007)을 통과하여 외부로 출사될 수 있다.

- [0124] 본 발명은 상술한 실시형태 및 첨부된 도면에 의해 한정되는 것이 아니며 첨부된 청구범위에 의해 한정하고자한다. 따라서, 청구범위에 기재된 본 발명의 기술적 사상을 벗어나지 않는 범위 내에서 당 기술분야의 통상의지식을 가진 자에 의해 다양한 형태의 치환, 변형 및 변경이 가능할 것이며, 이 또한 본 발명의 범위에 속한다고 할 것이다.

#### 부호의 설명

[0125] 100, 200, 300, 400, 500, 600, 700, 800: 반도체 발광소자 패키지

101: 기판

110: 패키지 기판

111: 몸체부

112: 절연층

116: 제1 전극패턴

118: 제2 전극패턴

120: 반도체 발광소자

121: 제1 도전형 반도체층

122: 활성층

123: 제2 도전형 반도체층

125: 전극절연층

126: 제1 전극

128: 제2 전극

130: 파장변환부

150: 렌즈부

## 도면

## 도면1

## 도면10

# 도면11a

# *도면11b*

# 도면11c

# 도면11d

## 도면11e

# *도면11f*

# 도면11g

# 도면11h

# 도면11i

## 도면12

<u>1000</u>