#### (12) INTERNATIONAL APPLICATION PUBLISHED UNDER THE PATENT COOPERATION TREATY (PCT)

(19) World Intellectual Property Organization

International Bureau

(10) International Publication Number WO 2014/203558 A1

(43) International Publication Date 24 December 2014 (24.12.2014)

(51) International Patent Classification: G06F 13/16 (2006.01) G06F 13/42 (2006.01)

(21) International Application Number:

PCT/JP2014/053391

(22) International Filing Date:

6 February 2014 (06.02.2014)

(25) Filing Language:

English

(26) Publication Language:

English

(30) Priority Data:

2013-129832 20 June 2013 (20.06.2013) JP 2014-019731 4 February 2014 (04.02.2014) JP

- (71) Applicant: KABUSHIKI KAISHA TOSHIBA [JP/JP]; 1-1, Shibaura 1-chome, Minato-ku, Tokyo, 1058001 (JP).

- (72) Inventors: FUJIMOTO, Akihisa; c/o Intellectual Property Division, Toshiba Corporation, 1-1, Shibaura 1-chome, Minato-ku, Tokyo, 1058001 (JP). SAKAMOTO, Hiroyuki; c/o Intellectual Property Division, Toshiba Corporation, 1-1, Shibaura 1-chome, Minato-ku, Tokyo, 1058001 (JP). MATSUKAWA, Shinichi; c/o Intellectual Property Division, Toshiba Corporation, 1-1, Shibaura 1-chome, Minato-ku, Tokyo, 1058001 (JP).

- (74) Agents: KURATA, Masatoshi et al.; c/o SUZUYE & SUZUYE, 6th floor, Kangin-Fujiya Bldg. 1-3-2, Toranomon, Minato-ku, Tokyo, 1050001 (JP).

- (81) Designated States (unless otherwise indicated, for every kind of national protection available): AE, AG, AL, AM, AO, AT, AU, AZ, BA, BB, BG, BH, BN, BR, BW, BY, BZ, CA, CH, CL, CN, CO, CR, CU, CZ, DE, DK, DM, DO, DZ, EC, EE, EG, ES, FI, GB, GD, GE, GH, GM, GT, HN, HR, HU, ID, IL, IN, IR, IS, KE, KG, KN, KP, KR, KZ, LA, LC, LK, LR, LS, LT, LU, LY, MA, MD, ME, MG, MK, MN, MW, MX, MY, MZ, NA, NG, NI, NO, NZ, OM, PA, PE, PG, PH, PL, PT, QA, RO, RS, RU, RW, SA, SC, SD, SE, SG, SK, SL, SM, ST, SV, SY, TH, TJ, TM, TN, TR, TT, TZ, UA, UG, US, UZ, VC, VN, ZA, ZM, ZW.

- (84) Designated States (unless otherwise indicated, for every kind of regional protection available): ARIPO (BW, GH, GM, KE, LR, LS, MW, MZ, NA, RW, SD, SL, SZ, TZ, UG, ZM, ZW), Eurasian (AM, AZ, BY, KG, KZ, RU, TJ, TM), European (AL, AT, BE, BG, CH, CY, CZ, DE, DK, EE, ES, FI, FR, GB, GR, HR, HU, IE, IS, IT, LT, LU, LV, MC, MK, MT, NL, NO, PL, PT, RO, RS, SE, SI, SK, SM, TR), OAPI (BF, BJ, CF, CG, CI, CM, GA, GN, GQ, GW, KM, ML, MR, NE, SN, TD, TG).

[Continued on next page]

(54) Title: DEVICE AND MEMORY SYSTEM

There are 5 functions in CONFIG

- (1) Set user key

- (2) Clear user key

- (3) Verify user key

- (4) Enable key ciphering

- (5) Disable key ciphering

- (6) Enable config. mode

- (7) Disable config. mode

FIG. 3

(57) Abstract: According to one embodiment, a device includes a semiconductor memory and a controller. The semiconductor memory includes first and second areas which are accessible from an outside. The controller controls the semiconductor memory. The device includes an unlocked state where reading from the first area and the second area is allowed, and a locked state where the reading from the first area is allowed and the reading from the second area is prohibited. The first area stores at least part of file system information. In the locked state, the at least part of the file system information is readable from the outside.

#

#### Published:

- with amended claims (Art. 19(1))

— with international search report (Art. 21(3))

- 1 -

# DESCRIPTION DEVICE AND MEMORY SYSTEM

Cross-Reference to Related Applications

This application is based upon and claims the benefit of priority from prior Japanese Patent Application No. 2013-129832, filed June 20, 2013; and No. 2014-019731, filed February 04, 2014, the entire contents of all which are incorporated herein by reference.

5

15

20

25

#### Field

The embodiments described herein relate generally to a device, a host apparatus, a host system, and a memory system.

#### Background

As a recording medium, a memory device using a NAND flash memory has broadly prevailed.

As such a memory device, a memory card is known. Further, there is known the memory card having a lock function of prohibiting an access to the card. However, according to the conventional lock function, a memory area cannot be read at all in a locked state, and hence there has been the problem that the memory card is not recognized by a host apparatus which does not support the lock function. Furthermore, even a host apparatus supporting the lock function cannot access the memory card until the locked state is released, and hence it cannot be distinguished whether the access is impossible due to the locked state or due to an error. To manage the locked

- 2 -

state, a special utility is required. Consequently, in the host apparatus, it has been difficult to manage the handling of the card which is in the locked state.

Brief Description of the Drawings

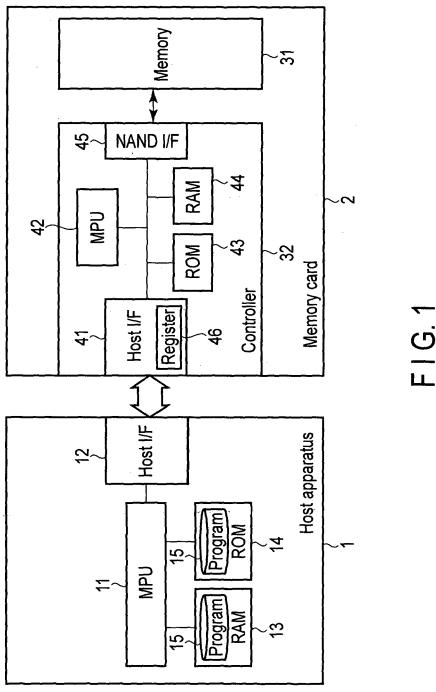

- FIG. 1 is a block diagram of a memory system according to one embodiment;

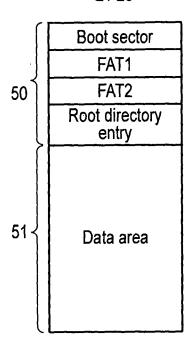

- FIG. 2 is a concept diagram of a memory space of the memory system according to the one embodiment;

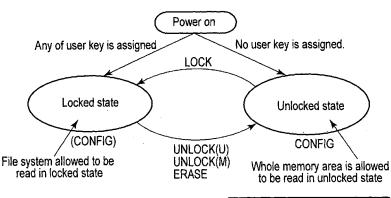

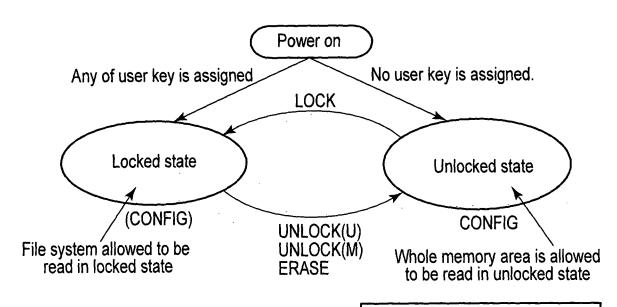

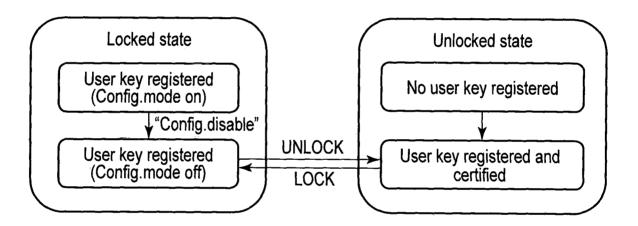

- FIG. 3 and FIG. 4 are state transition diagrams of a memory card according to the one embodiment;

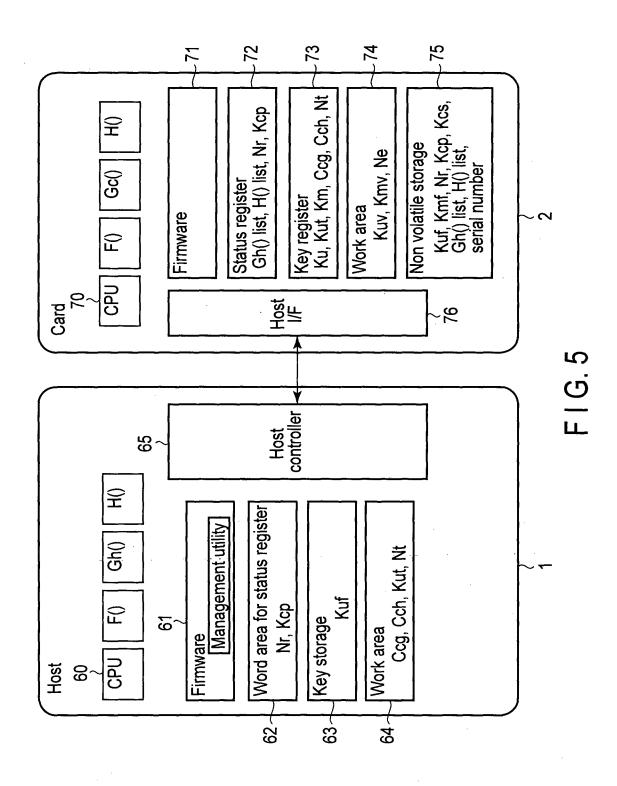

- FIG. 5 is a block diagram of the memory system according to the one embodiment;

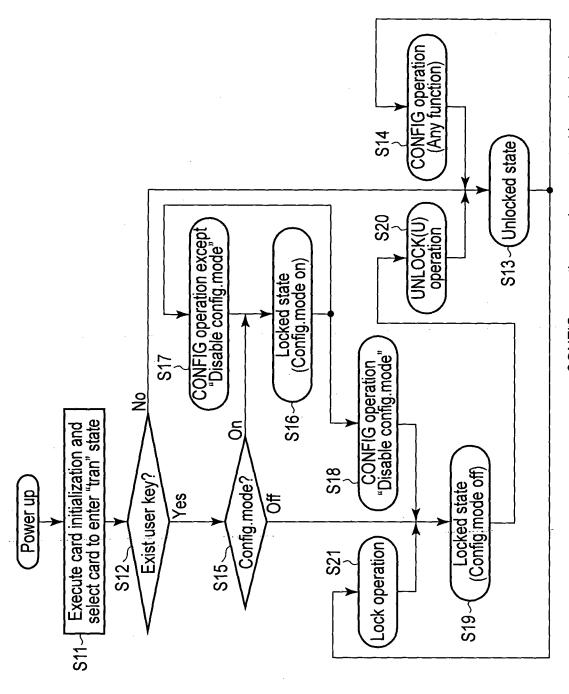

- FIG. 6 is a flowchart showing an operation of the memory card according to the one embodiment;

- 15 FIG. 7 is a diagram showing a function of a configuration mode according to the one embodiment;

10

25

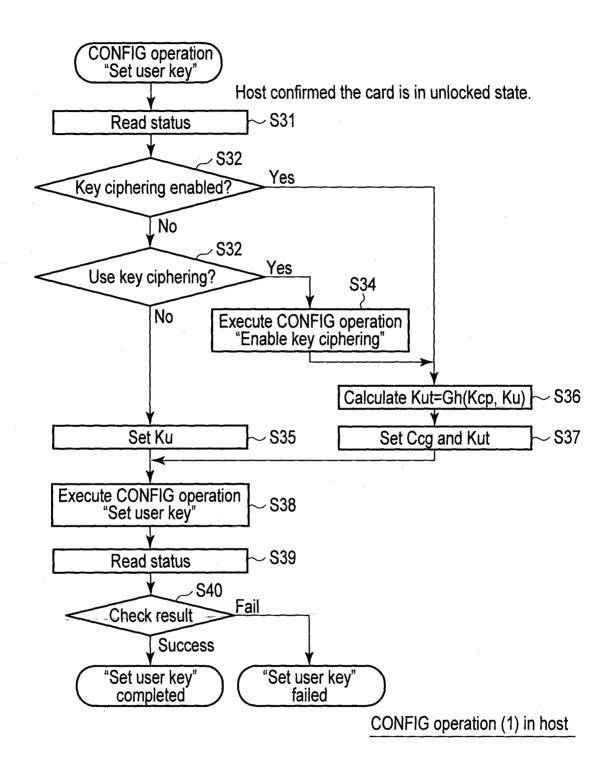

- FIG. 8 is a flowchart showing an operation of a host apparatus during execution of a "Set User Key" function according to the one embodiment;

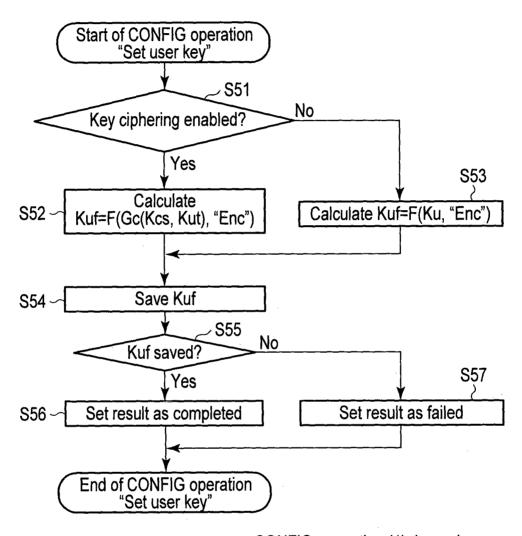

- FIG. 9 is a flowchart showing an operation of the memory card during the execution of the "Set User Key" function according to the one embodiment;

- FIG. 10 is a flowchart showing an operation during the execution of the "Set User Key" function according to the one embodiment;

- FIG. 11 is a flowchart showing an operation during the execution of the "Set User Key" function according to the

- 3 -

one embodiment;

5

10

15

20

25

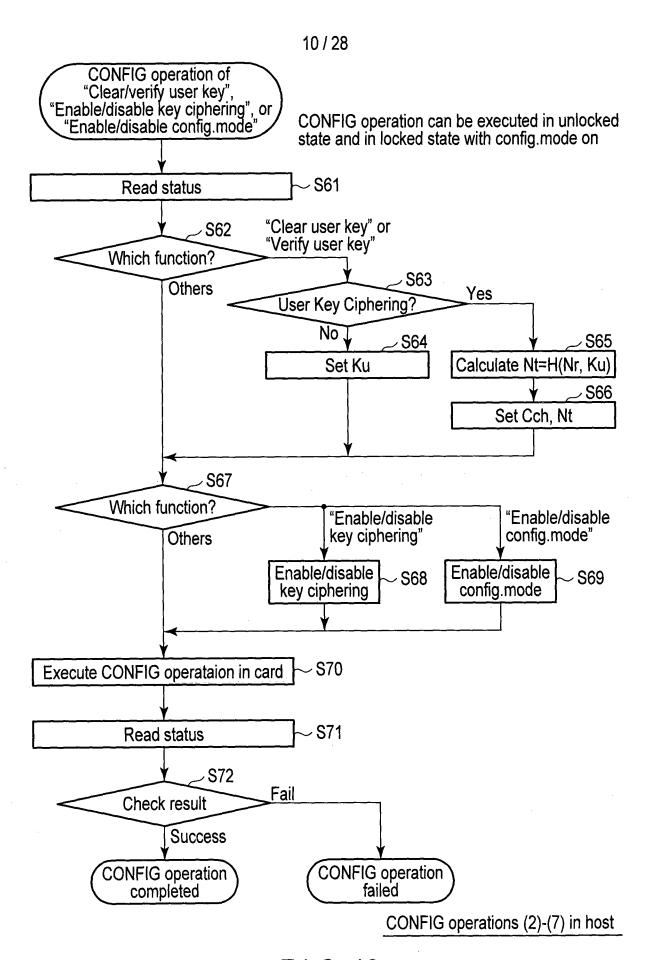

FIG. 12 is a flowchart showing an operation of the host apparatus during execution of a "Clear/Verify User Key" function and "Enable/Disable Key Ciphering" according to the one embodiment;

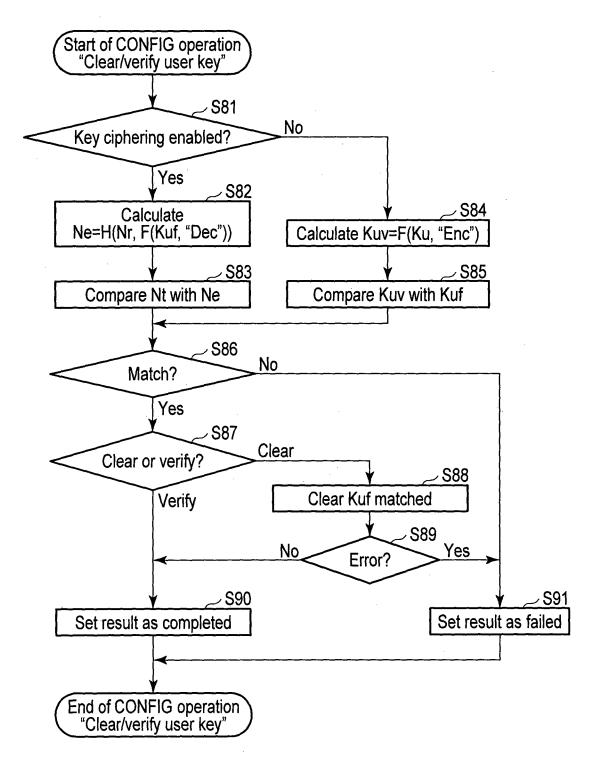

FIG. 13 is a flowchart showing an operation of the memory card during the execution of the "Clear/Verify User Key" function according to the one embodiment;

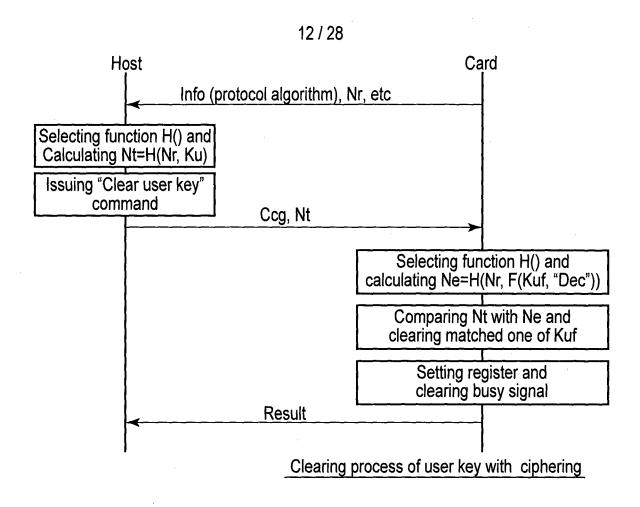

FIG. 14 is a flowchart showing an operation during the execution of a "Clear User Key" function according to the one embodiment;

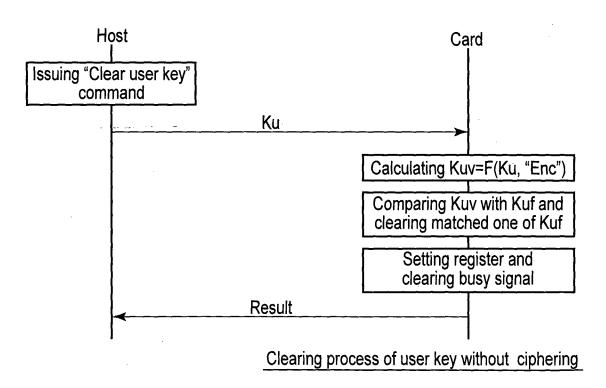

FIG. 15 is a flowchart showing an operation during the execution of the "Clear User Key" function according to the one embodiment;

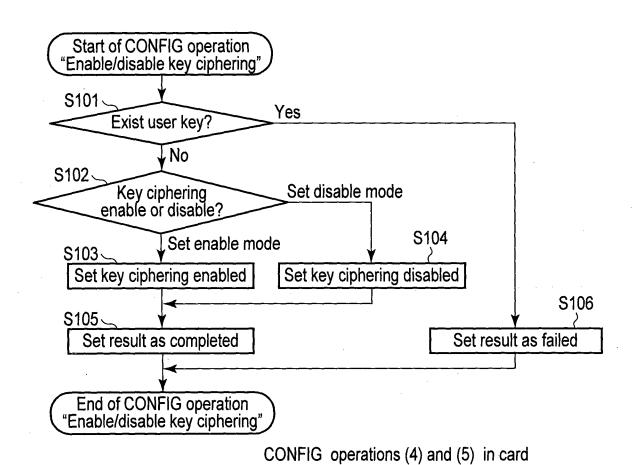

FIG. 16 is a flowchart showing an operation of the memory card during the execution of the "Enable/Disable Key Ciphering" according to the one embodiment;

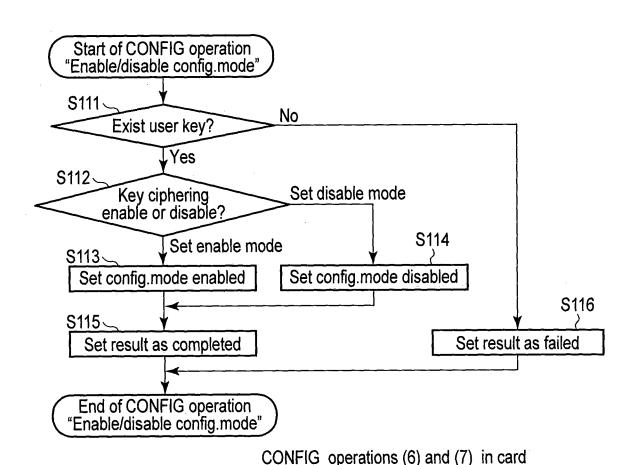

FIG. 17 is a flowchart showing an operation of the memory card during execution of "Enable/Disable Config. Mode" according to the one embodiment;

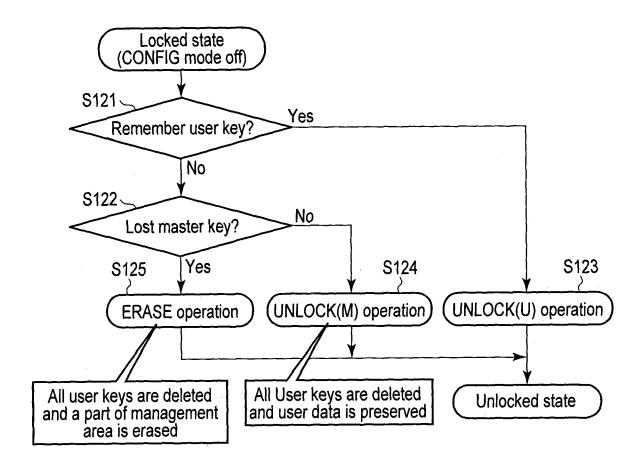

FIG. 18 is a flowchart of an unlocking operation according to the one embodiment;

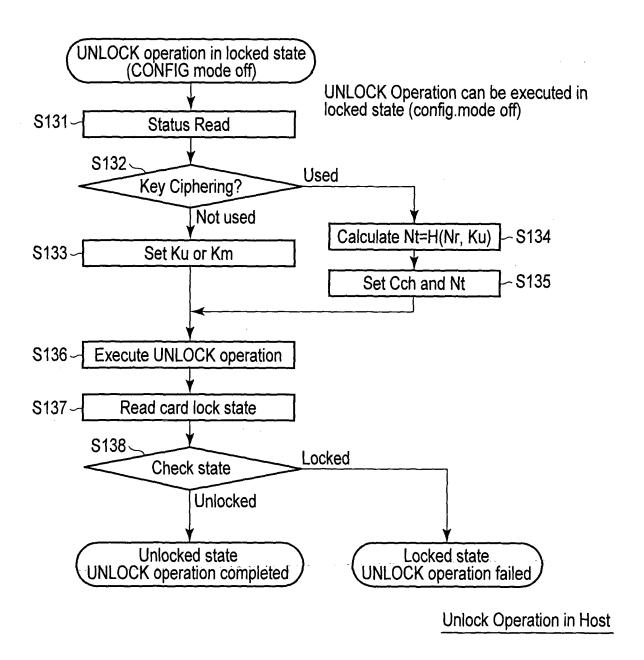

FIG. 19 is a flowchart of the unlocking operation in the host apparatus according to the one embodiment;

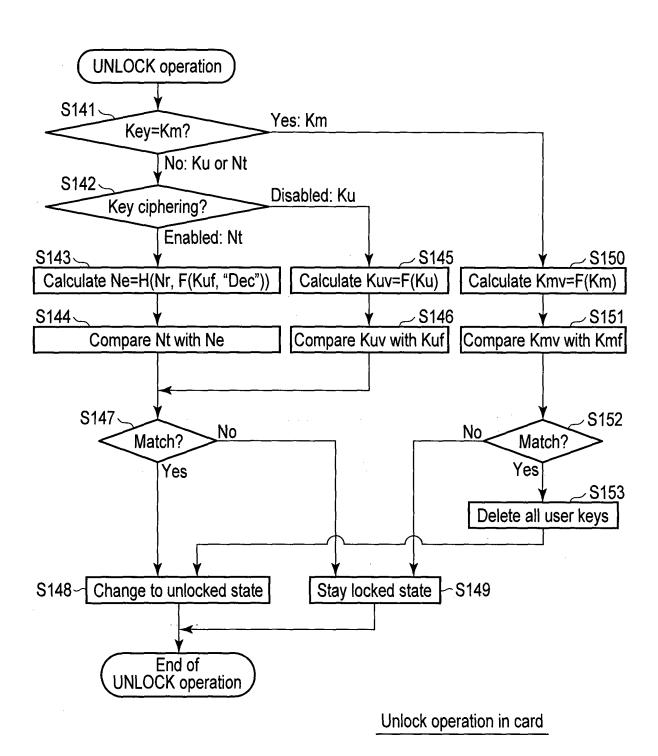

FIG. 20 is a flowchart of the unlocking operation in the memory card according to the one embodiment;

FIG. 21 to FIG. 24 are flowcharts of the unlocking

- 4 -

operation according to the one embodiment;

5

10

15

20

25

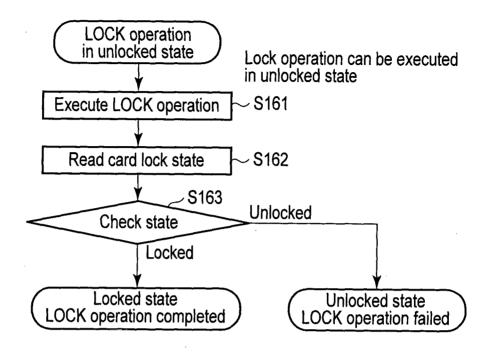

FIG. 25 is a flowchart of a locking operation in the host apparatus according to the one embodiment;

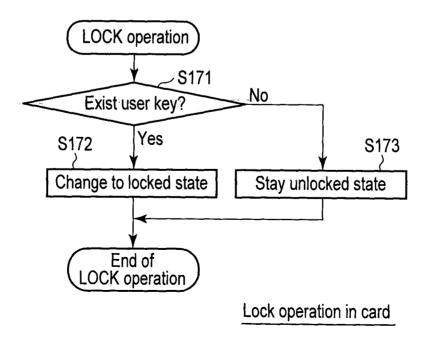

FIG. 26 is a flowchart of the locking operation in the memory card according to the one embodiment;

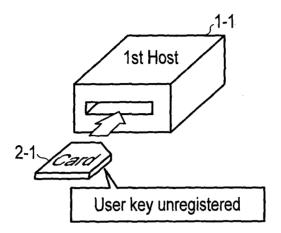

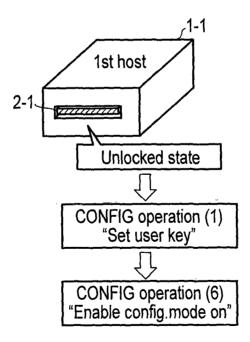

FIG. 27 is a schematic view of the memory system according to the one embodiment;

FIG. 28 to FIG. 33 are schematic views of the memory system according to the one embodiment;

FIG. 34 is a block diagram of a memory system according to a modification of the one embodiment;

FIG. 35 is a block diagram of a partial area of a memory card according to the modification of the one embodiment; and

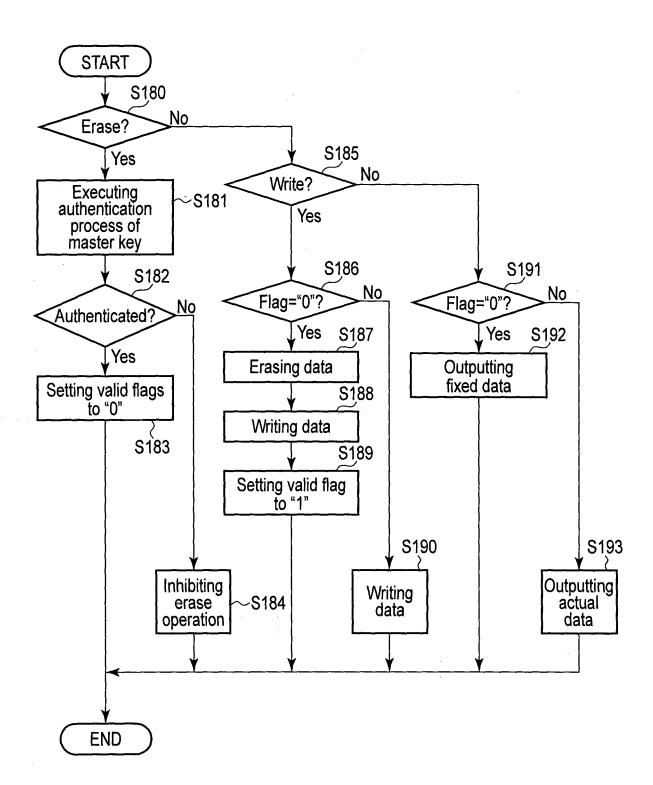

FIG. 36 is a flowchart showing an operation of the memory card according to the modification of the one embodiment.

#### Detailed Description

In general, according to one embodiment, a device includes a semiconductor memory and a controller. The semiconductor memory includes first and second areas which are accessible from an outside. The controller controls the semiconductor memory. The device includes an unlocked state where reading from the first area and the second area is allowed, and a locked state where the reading from the first area is allowed and the reading from the second area is prohibited. The first area stores at least part of file

- 5 -

system information. In the locked state, the at least part of the file system information is readable from the outside.

The device, a host apparatus, a host system and a memory system according to the one embodiment will be described. Hereinafter, the memory system including a memory card and the host apparatus which accesses this memory card will be described as an example. Moreover, in the present description, a case where the memory card is an SD memory card will be described as an example.

1. Structure of System

5

10

15

20

25

First, structure of the host apparatus and the memory card will be described with reference to FIG. 1. FIG. 1 is a block diagram showing a hardware structure of the memory system according to the present embodiment.

1.1 Structure of Host Apparatus

First, the structure of the host apparatus will be described with reference to FIG. 1. As shown in the drawing, a host apparatus 1 includes a micro processing unit (MPU) 11, a host interface (e.g., SD<sup>TM</sup> interface) circuit 12, a read only memory (ROM) 14, a random access memory (RAM) 13 and the like. The ROM 14 includes a storage device such as a hard disk which enables general writing, and the ROM is not especially restricted by a type of hardware.

The MPU 11 controls the whole operation of the host apparatus 1. When the host apparatus 1 receives power supply, a firmware (a control program (a command)) stored

- 6 -

in the ROM 14 is read onto the RAM 13. Then, the MPU 11 executes predetermined processing in accordance with the firmware (the command). Moreover, the MPU 11 executes programs 15 held in the RAM 13 and the ROM 14, thereby realizing various functions. The programs 15 include various pieces of application software, operating systems, file systems, and the like. Furthermore, the program 15 includes a management utility for preparing a user key described later.

The host interface circuit 12 manages a communication protocol between this circuit and a memory card 2. The host interface circuit 12 operates in accordance with various agreements required to perform communication between the host apparatus 1 and the memory card 2, and comprises various sets of commands which can mutually be communicated with a host interface 41 of the memory card 2 described later.

# 1.2 Structure of Memory Card

5

10

15

20

25

Next, the structure of the memory card 2 will be described continuously with reference to FIG. 1. As shown in the drawing, the memory card 2 includes a NAND flash memory 31 and a controller 32.

The NAND flash memory 31 stores data in a nonvolatile manner. The NAND flash memory 31 writes or reads the data in units called pages including a plurality of the memory cells. An inherent physical address is allocated to each page. Furthermore, the NAND flash memory 31 erases the

5

10

15

20

25

- 7 -

data in units called blocks, including a plurality of the pages. It is to be noted that the physical address may be allocated to the block unit.

The controller 32 instructs the NAND flash memory 31 to write, read, and erase the data in response to a request from the host apparatus 1. Moreover, the controller 32 manages a stored state of the data in the NAND flash memory 31. The management of the stored state includes the management of a relationship between the logical address and the physical address, and the management of whether a specific physical address page (or block) is in an erased state (a state where nothing is written or invalid data is held).

As shown in FIG. 1, the controller 32 includes the host interface circuit 41, an MPU 42, a RAM 44, a ROM 43, and a NAND interface circuit 45.

The host interface circuit 41 controls the communication between the memory card 2 and the host apparatus 1. More specifically, the host interface circuit 41 controls transmission/reception of various commands or data between the host interface circuit and the host interface circuit 12 of the host apparatus 1. Moreover, the host interface circuit 41 includes a register 46. The register 46 stores various pieces of information, whereby the host apparatus 1 can be notified of the state of the memory card 2. This information is set, for example, by the MPU 42. Furthermore, the register 46 stores various

- 8 -

pieces of information received from the host apparatus 1.

The MPU 42 controls the whole operation of the memory card 2. When the memory card 2 receives the power supply, firmware (a control program (a command)) stored in the ROM 43 is read onto the RAM 44. Then, the MPU 42 executes predetermined processing in accordance with the firmware (the command). The MPU 42 prepares various tables on the RAM 44 in accordance with the control program, or executes predetermined processing for the NAND flash memory 31 in accordance with the command received from the host apparatus 1.

5

10

15

20

25

The ROM 43 stores the control program or the like to be controlled by the MPU 42. The RAM 44 is used as an operation area of the MPU 42, and temporarily stores the control program or various tables. These tables include a conversion table (a logical address/physical address conversion table) of the logical address allocated to the data and the physical address of the page in which the data is stored. The NAND interface circuit 45 performs interface processing between the controller 32 and the NAND flash memory 31.

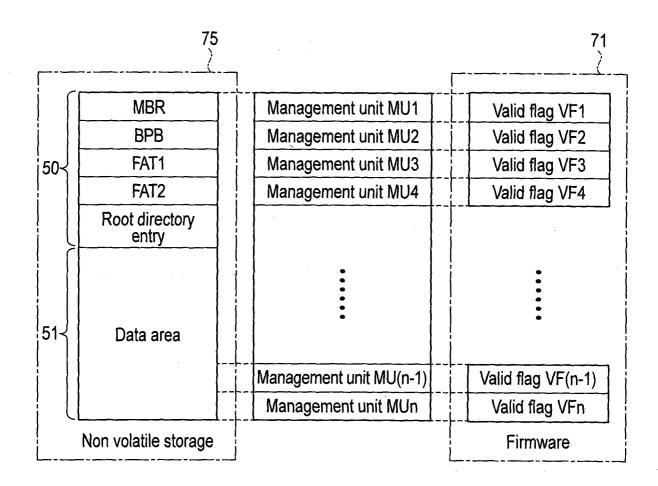

### 1.3 Memory Space of Memory System

Next, a memory space of the memory system of the above structure will be described. FIG. 2 is a memory map showing the memory space which is accessible from the outside of the memory card 2, and shows an example where the memory space is managed by a file allocation table

- 9 -

(FAT) file system.

5

10

15

20

25

As shown in the drawing, the memory space is roughly divided into a file system management area 50 and a file system data area 51. Each area is divided into units called clusters, and controlled in the cluster unit. A combination of the file system management area 50 and the file system data area 51 is called a data area.

The management area 50 is disposed to manage a file (data) recorded in the NAND flash memory 31, and it holds management information of the file. A system to manage the file (the data) recorded in the memory in this way is called a file system. In the file system, there are set up a preparing method of directory information of the file, a folder or the like, a moving method or deleting method of the file, the folder or the like, a recording system of the data, a location or a utilizing method of the management area, and the like.

The management area 50 includes, for example, a boot sector, a FAT1, a FAT2, and a root directory entry. The boot sector is an area where boot information is stored. The boot sector includes, for example, a master boot record (MBR) and a BIOS parameter block (BPB). Each of the MBR and the BPB is, for example, a 512 byte area. The FAT1 and the FAT2 store specific clusters in which the data is stored. The memory space is a set of spaces each having a definite size which are called clusters. Moreover, when the data to be written is larger than the cluster size, the

- 10 -

data is divided into cluster units, and stored therein. In this case, in the FAT, there is prepared a cluster chain indicating specific clusters into which the data is divided and written, whereby the data is managed. It is to be noted that both the FAT1 and the FAT2 hold the same value, which enables the recovery of the FAT even when one of the FAT1 and FAT2. Hereinafter, the FAT1 and the FAT2 will collectively be called the FAT. The root directory entry stores information of the file present on a root directory. More specifically, together with a file name or a folder name, a file size, an attribute, update date and time of the file and the like, a specific cluster which is the top cluster of the file is stored. When the top cluster is known, all the data is accessible from a FAT chain.

5

10

15

20

25

The file system data area 51 is an area other than the management area 50, and a data capacity which can be stored in the memory card depends upon a size of this area.

Moreover, the area holds net user data or directory entry.

1.4 Locked State and Unlocked State

Next, the locked state and the unlocked state which can be taken by the memory card 2 according to the present embodiment will be described with reference to FIG. 3. FIG. 3 is a state transition diagram of the memory card 2, and especially shows a state immediately after power is turned on, and a transition between the locked state and the unlocked state.

To bring the memory card into the locked state, the

- 11 -

user key needs to be registered, and is required to perform the transition between the locked state and the unlocked state. There are a case where the key is used as "a password" to be directly input from the host apparatus 1 by a user, and a case where the key is managed by the management utility of the host apparatus 1 without inputting the password by the user, because a key which is so long as to be unsuitable for the user to input is also handled.

5

10

15

20

25

As shown in FIG. 3, when the memory card 2 is connected to the host apparatus 1 and the power is supplied from the host apparatus 1 to the memory card 2, the memory card 2 takes one of the locked state and the unlocked state in accordance with the presence/absence of the setting of the user key. When the user key is not set, the memory card 2 becomes in the unlocked state. In the unlocked state, a writing access and a reading access to the memory space of the memory card 2 can be performed without limit (with the proviso that the writing is limited by a use application of a ROM card or the like sometimes). The control of the memory card is executed in accordance with a command, and examples of a memory access command include a writing command, a reading command, and a control command to control the lock function of the present embodiment. The host apparatus 1 can register the user key in the The control memory card 2 by use of the control command. command is controlled as an executable command irrespective

- 12 -

of the locked state or the unlocked state.

5

10

15

20

25

On the other hand, when the user key is set to the memory card 2, the memory card 2 becomes in the locked state. In the locked state, the writing access to the memory card 2 is prohibited, and the reading access is limited. For example, the management area 50 described with reference to FIG. 2, more specifically, information on the file system (e.g., the FAT1, FAT2 and root directory entry in FIG. 2, which will hereinafter be called the file system information) can be read, but when the reading command for the area other than the management area 50 is received, the execution of the command is rejected. When the writing command is received, the execution of the command is rejected irrespective of the area.

The host apparatus 1 can read at least a part of the file system information even when the memory card 2 is in the locked state. Therefore, when the file system information is read, the host apparatus can recognize the memory card 2 as a formatted memory device, and can further allocate a drive letter to the memory card 2.

For example, in the host apparatus 1, when only the information stored in a master boot record (MBR) described later and shown in FIG. 35 is read, the memory card 2 can be mounted. In this case, the host apparatus 1 controls the memory card such that, when the card is in the locked state, the card is shown as an empty drive, and when the card is in the unlocked state, the directory or the file

- 13 -

name stored in the card can be read.

5

10

15

20

25

A boundary between the file system management area 50 and the file system data area 51 depends upon a format parameter of the file system, and hence the memory card 2 does not need to strictly distinguish the boundary. The required size of the management area 50 can roughly be predicted from the memory capacity. Therefore, in the locked state, for example, the MBR or BPB may be read, or a little larger area including the management area 50 may be read. In consequence, the memory card 2 does not have to recognize a format of the file system.

In general, when the device is mounted, the identification of the device and partition information are Therefore, when the MBR can be read at minimum in the locked state, the memory card 2 can often be mounted. Device information can be identified by reading the MID, after the memory card 2 is initialized. The MID is a type of card identification information which is held in a card identification (CID) register included in the memory card 2. Furthermore, the MBR is information required to obtain the partition information of the memory card 2. However, when a rule indicating that an only first partition of the memory card 2 is valid is determined in advance, the memory card 2 can be mounted without reading the MBR. As one example of the host apparatus 1 which can read the memory card 2 in the locked state, the following case can be considered as one example in the case of a memory system of

- 14 -

FIG. 35. That is, for mounting the memory card2, the host apparatus 1:

(a) can read the MBR only,

5

10

15

20

25

- (b) can read the MBR and BPB only,

- (c) can read from the MBR to the FAT, or

- (d) can read from the MBR to the root directory entry.

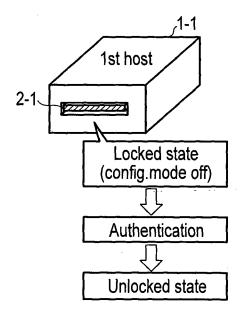

When the memory card 2 in the unlocked state executes a locking operation by use of the control command, and when the user key is registered, the memory card can change to the locked state. Furthermore, when the memory card 2 in the locked state executes an unlocking operation by use of the control command, and when a designated key matches the registered key, the memory card can change to the unlocked state. Examples of the unlocking operation include an unlocking operation using the user key, and an unlocking operation using a master key described later. Furthermore, the locked state can be changed to the unlocked state also by erasing a part of the data including the user key in accordance with the control command. Details of these operations will be described later.

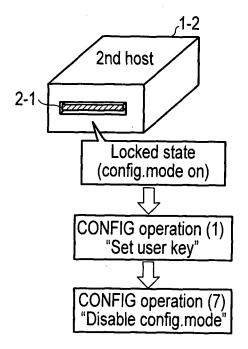

Additionally, in the memory card 2, various settings (configuration operations) concerning the user key are executable by using the control command. This configuration operation is usually executable in the unlocked state, but the memory card has a configuration mode (Config. Mode) which can allow the configuration operation even in the locked state. That is, the memory

- 15 *-*

card 2 in which the configuration mode is in the on-state can execute the configuration operation even in the locked state. On the other hand, when the configuration mode is in the off-state, the memory card 2 in the locked state cannot execute the configuration operation. Details of the configuration operation will be described later.

5

10

15

20

25

FIG. 4 is a diagram showing internal states of the locked state and the unlocked state in more detail. As described above, if the user key is not registered when the power is turned on, the memory card 2 is in the unlocked state. In the unlocked state (on the right side of FIG. 4), the configuration mode is the on-state at default setting. Furthermore, the host apparatus 1 executes the configuration operation by use of the control command to register the user key. On the other hand, if the user key is registered when the power is turned on, the memory card 2 is in the locked state (on the left side of FIG. 4). There are two states where the configuration mode is on and off. When the configuration mode is the off-state, the unlocking operation cannot be executed.

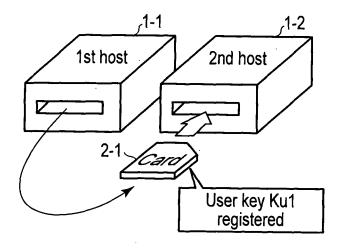

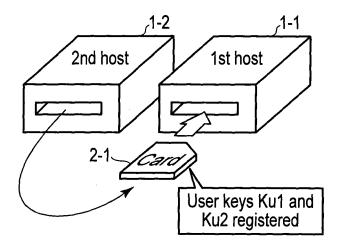

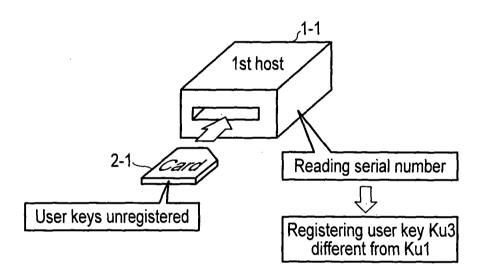

For example, when the memory card 2 in which the user key is registered by a certain host apparatus 1 (a host apparatus 1-1) is connected to another host apparatus 1 (a host apparatus 1-2), the memory card 2 becomes in the locked state. However, when the configuration mode is set to the on-state by the host apparatus 1-1, the host apparatus 1-2 can set the user key to the memory card 2 in

- 16 -

the locked state. Afterward, when the host apparatus 1-2 set the configuration mode to the off-state, the configuration operation cannot be executed.

The user keys can be registered, and the user keys of the host apparatuses to be registered can be registered up to the maximum registration number. In the unlocking operation, the locked state can be released, when one of the user keys is matched with the input key.

#### 1.5 Function Block of Memory Card

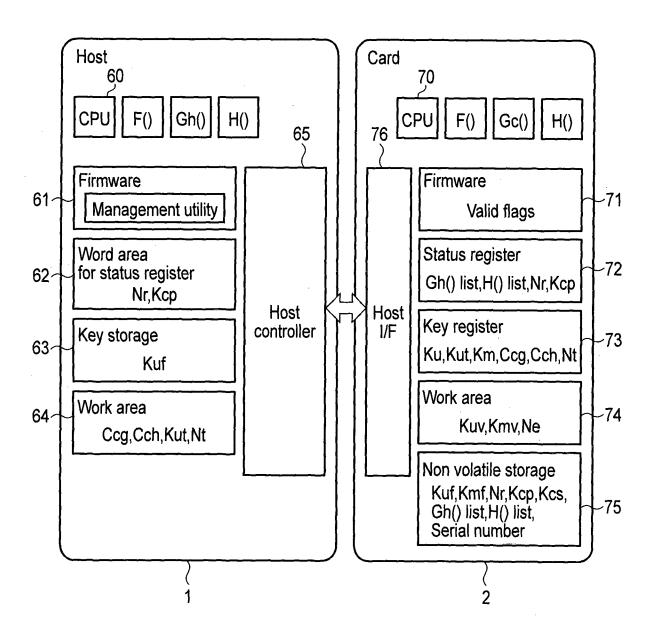

Next, a function block of the memory card 2 which is focused especially on the configuration operation will be described with reference to FIG. 5. FIG. 5 is a function block diagram of the memory system.

#### 1.5.1 Symbol Definition

5

15

20

Prior to the explanation of the function block, symbols for use in the present description are defined as follows.

- (i) Definition of Usual Key Symbols

- •Ku (User Key): a key to be set by the user

- •Km (Master Key): a key set at shipping and having a high priority

- •Kcp (Card Public Key): a public key of a card RSA cipher

- •Kcs (Card Secret Key): a secret key of the card RSA cipher

- •Ccx (Cipher Code, x = g or h): a code indicating a cipher system and an algorithm for use

- 17 -

•Nr: a random number

- (ii) Type and Notation of Conversion Function

- ulletF(): a cipher function for storage in the flash memory

5 Encode: Kuf = F(Ku, "Enc")

10

15

Decode: Ku = F(Kuf, "Dec")

It is to be noted that the conversion function F() also includes a case where the conversion is not performed (Kuf = Ku). The host apparatus and the card use a common notation, but the function itself does not have to be the same, and an individual function may be used.

•Gh(), Gc(): a cipher function using an RSA cipher and a decode function

Kcp host encode: Kut = Gh(Kcp, Ku)

Kcs card decode: Ku = Gc(Kcs, Kut)

When there are plural Gh() and Gc() functions, types of Gh() and Gc() for use are shown by Ccg.

ulletH(): a conversion function for the registration of the user key

20 When a long key is converted to a short key by use of a compressive function, the comparison of keys can be facilitated.

Nt = H(Nr, Ku)

- (iii) Type and Notation of Key

- of a key of the state of the s

x = m: the master key, x = u: the user key

y = f: Ciphered by F() so that the key is held in the

- 18 -

flash memory

5

10

15

20.

25

y = t: a time of transmission/reception between the host and the card, y = v: a time of verification

Types of the master keys: Km, and Kmf

Types of the user keys: Ku, Kut, Kuf, and Kuv

•Nx: a notation of the random number for use in challenge

x = r: a random number seed

x = t: a random number in which the key for use at the transmission/reception between the host and the card is buried

x = e: an expected value calculated by the card Types of challenge numbers: Nr, Nt, and Ne 1.5.2 Regarding Host Apparatus 1

As shown in FIG. 5, the host apparatus 1 includes a CPU 60, conversion functions Gc(), H() and F(), a firmware 61, a register 62, a key storage area 63, a work memory 64, and a host controller 65.

The CPU 60 controls the whole operation of the host apparatus 1, and corresponds to the MPU 11 described with reference to FIG. 1. Moreover, the CPU 60 can access to the conversion functions Gh() and H(), the firmware 61, the register 62, the key storage area 63, the work memory 64 and the host controller 65.

The conversion function Gh() is a cipher function for use during the registration of the user key. For the conversion function Gh(), for example, an RSA cipher system

- 19 -

is used in which the user key is ciphered by the public key read from the memory card 2. The conversion function Gh() may be software (e.g., stored in the ROM 14 described with reference to FIG. 1), but may be hardware for achieving a high speed. When a plural conversion functions Gh() is prepared, the conversion function is selected from a Gh() list included in status information of the memory card 2 (held in a register 72 of FIG. 5). That is, the Gh() list is a list of the conversion functions, which are supported by the memory card 2, for the registration of the user key. The host apparatus 1 selects the function supported by the host apparatus 1 from this Gh() list. A code Ccg indicating the selected function is held in the work memory 64. When there is only one type of Gh(), it is not essential to use the Gh() list.

5

10

15

The conversion function H() is a cipher function for use during authentication of the user key. The user key is ciphered utilizing the conversion function H() by use of the random number read from the memory card 2. The

20 conversion function H() may also be software (e.g., stored in the ROM 14 described with reference to FIG. 1), but is preferably hardware from the viewpoint of the achievement of the high speed. The conversion function H() is selected from an H() list of the status information of the memory card 2 (held in the register 72 of FIG. 5). That is, the H() list is a list of the conversion functions, which are supported by the memory card 2, for the authentication of

- 20 -

the user key. The host apparatus 1 selects the function supported by the host apparatus 1 from this H() list. A code Cch indicating the selected function is held in the work memory 64. When there is only one type of H(), it is not essential to use the H() list. As the conversion function H(), a hash function can be used, and when the long key is converted to the short key by this function, the comparison of the keys can be facilitated. An example of H() is MD5(Nr||Ku). H() may have an inverse function, but in the present embodiment, H() indicates an example where the function does not have the inverse function (for F(), the inverse function is defined by "Dec" and "Enc").

5

10

15

20

25

The host controller 65 performs interface processing between the host apparatus 1 and the memory card 2. The host controller 65 corresponds to the host interface circuit 12 in FIG. 1. The host controller 65 issues various commands to the card 2, and controls the execution of the command in accordance with a response of the card 2.

The CPU 60 operatively executes the firmware 61, and controls the operation of the host apparatus 1. Moreover, the firmware 61 includes the above-mentioned management utility. The management utility prepares the user key on the basis of the random number or the information inherent in the host apparatus 1 without accepting, for example, the input of the password from the user. As the method of preparing the user key, various known methods can be used, and examples of the information inherent in the host

- 21 -

apparatus 1 include random number generation, and a manufacturing number or serial number of the host apparatus 1. Alternatively, the user key may be prepared on the basis of the results of calculation using the information inherent in the host apparatus 1 and information inherent in the memory card 2. The firmware 61 is stored, for example, in the ROM 14 of FIG. 1.

5

10

15

20

25

The register 62 holds the status information read from the memory card 2. Examples of the status information include a random number Nr and a cipher key Kcp of the RSA cipher. As the register 62, for example, a volatile memory can be used, and the register corresponds to, for example, the RAM 13 in FIG. 1.

In the key storage area 63, a user key Ku prepared by the management utility or an accepted user key Ku input from the user is ciphered by F(), and held as Kuf. The key storage area 63 corresponds to, for example, a nonvolatile semiconductor memory (which may be referred to as "host memory) which is not shown in FIG. 1. Information in the key storage area 63 is managed so that the information cannot easily be read from the outside.

The work memory 64 is used as a work area when the CPU 60 executes various pieces of processing such as processing concerning the user key, and it corresponds to, for example, the RAM 13 in FIG. 1. Furthermore, the work memory 64 holds the codes Ccg and Cch for use, or keys Kut, Nt and the like calculated by the CPU 60.

- 22 -

#### 1.5.3 Memory Card 2

5

10

15

20

25

A CPU 70 controls the whole operation of the memory card 2, and corresponds to the MPU 42 described with reference to FIG. 1. Moreover, the CPU 70 can access to the conversion functions Gc(), H() and F(), firmware 71, registers 72 and 73, a work memory 74 and a nonvolatile memory 75.

The conversion function Gc() is a cipher function for use during the registration of the user key. Furthermore, for the conversion function Gc(), for example, an RSA cipher system is used in which the user key is decoded by the secret key. The conversion function Gc() may be software (e.g., stored in the ROM 14 described with reference to FIG. 1), but may be hardware for achieving the high speed. The conversion function Gc() corresponds to the conversion function Gh() of the host apparatus 1. Additionally, the conversion function Gc() is any function included in the Gh() list as a list of the functions, which are supported by the memory card 2, for the registration of the user key.

The conversion function H() is a cipher function for use during the authentication of the user key. The user key is ciphered utilizing the conversion function H() by use of the random number read from the nonvolatile memory 75. The conversion function H() may also be software (e.g., stored in the ROM 14 described with reference to FIG. 1), but is preferably hardware from the viewpoint of the

. - 23 **-**

achievement of the high speed. The conversion function H() corresponds to the conversion function H() of the host apparatus 1. Additionally, the conversion function H() is any function included in the H() list as a list of the functions, which are supported by the memory card 2, for the authentication of the user key. As described above, in the conversion function H(), a hash function can be used, whereby a key length can be shortened and the comparison can be facilitated.

5

10

15

20

25

A host interface 76 performs interface processing between the memory card 2 and the host apparatus 1. The host interface 76 corresponds to the host interface 41 in FIG. 1.

The firmware 71 is executed by the CPU 70. Moreover, the CPU 70 operatively executes the firmware 71, and controls the operation of the memory card 2. The firmware 71 is stored, for example, in the ROM 43 of FIG. 1, and cannot be seen or accessed from the host apparatus 1.

The register 72 can hold the status information indicating the state of the memory card 2. The host apparatus 1 can read the status information from the register 72 by use of the control command, and can grasp the state of the memory card 2. The random number Nr is updated to a different value, for example, by the CPU 70, every time the unlocking operation, or an erasing operation or a checking operation of the user key is performed. The secret key Kcs is not shown to the host apparatus, and

- 24 -

hence the key is not held in the register 72.

5

10

15

20

25

The register 73 is a register which is writable by the host apparatus 1. Furthermore, the register 73 holds various pieces of key information (e.g., Ku, Kut, Km, Ccg, Cch, Nt, etc.) transmitted from the host apparatus 1.

When the registers 72 and 73 are hardware, these registers correspond to, for example, the register 46 in FIG. 1, but a virtual register can be made of the firmware 71 on the RAM 44. As to an initial value of a status, when the memory card 2 is initialized, the CPU 70 copies required information from the nonvolatile memory 75 to the register 72. Examples of the information include the Gh() list, the H() list, the random number Nr, and the public key Kcp.

The work memory 74 is used as a work area when the CPU 70 executes various pieces of processing such as the processing concerning the user key, and corresponds to, for example, the RAM 44 in FIG. 1. Furthermore, the work memory 74 holds calculated comparison values Kuv and Kmv, an expected value Ne, and the like. The work memory 74 cannot directly be accessed by the host apparatus 1.

The nonvolatile memory 75 corresponds to the NAND flash memory 31 in FIG. 1. The host apparatus 1 cannot directly access the nonvolatile memory 75, and accesses the memory via the host interface 76 or the CPU 70 (the controller 32 in FIG. 1). The nonvolatile memory 75 holds various pieces of necessary information (e.g., Kuf, Kmf, Nr,

- 25 -

Kcp, Kcs, the Gh() list, the H() list, etc.) in the nonvolatile manner. These pieces of information are held in the area which cannot be seen from the host apparatus 1, and the information cannot directly be accessed by the host apparatus 1. That is, these pieces of information are held in an area which is not shown in FIG. 2. Furthermore, these pieces of information basically have fixed values. However, as described above, the random number seed Nr is updated by the CPU 70. In this case, the CPU 70 updates Nr so that the updated value does not become the same as a past value. Additionally, the nonvolatile memory 75 holds the inherent information of the memory card 2, for example, the serial number in the nonvolatile manner. The serial number can be read by the host apparatus 1.

2. Operation of Memory System

5

10

15

20

25

Next, an operation of the memory system of the abovementioned constitution will be described. Hereinafter, the configuration operation and the locking/unlocking operation will successively be described.

2.1 Operation of Memory Card immediately after

Powered On

First, there will be described an operation immediately after the memory card 2 is connected to the host apparatus 1 and the power is turned on, with reference to FIG. 6. FIG. 6 is a flowchart showing the operation of the memory card 2. It is to be noted that the processing in FIG. 6 is executed mainly by the CPU 70.

- 26 -

When the memory card 2 is connected to the host apparatus 1, the host apparatus 1 supplies the power to the memory card 2. Then, the CPU 60 of the host apparatus 1 issues an initialization command, to initialize the memory card 2. In response to this command, the CPU 70 of the memory card 2 executes an initializing operation (step S11). The initialization is processing to obtain a state where the memory space of the memory card 2 is accessible from the host apparatus 1, and more specifically processing to obtain a state where the reading command can be accepted from the host apparatus 1. This state will be called a transfer state (the "tran" state). Moreover, in the process of the initialization processing, the required information is read from the nonvolatile memory 75 to the register 73. Further in the process of the initialization processing, a transfer mode of a bus between the host apparatus 1 and the memory card 2 is selected. For example, transfer modes are prepared in the bus, and a transfer speed of the data varies in accordance with the transfer mode. Any one of these transfer modes is selected in the initialization processing.

10

15

20

25

The CPU 70 of the memory card 2 which has changed to the transfer state determines whether or not at least one user key is set in the memory card 2 (step S12). This determination is executable with reference to the nonvolatile memory 75 by the CPU 70. More specifically, the CPU 70 can perform the determination by checking

- 27 -

whether or not the ciphered user key Kuf is held in the nonvolatile memory 75. Alternatively, information indicating whether the user key is set may be held as a part of the status information in the register 72.

5

10

15

20

25

When the user key is not set (the step S12, NO), the CPU 70 brings the memory card into the unlocked state (the step S13). That is, the host apparatus 1 can execute the reading access and the writing access to both the file system management area 50 and the file system data area 51 of the memory card.

In the unlocked state, all the configuration operations are executable (step S14). The registration, erasing, checking and the like of the user key can be performed. Moreover, in the memory card 2, the configuration mode is in off-state turned off at the default setting. Therefore, for example, when the user key is set in another host apparatus 1 (a second host apparatus 1), the configuration operation is executed to set the configuration mode to the on-state. Next, a flow of the processing in this case will be described.

When the memory card 2 in which the user key is set and set the configuration mode to the on-state in the step S14 by the first host apparatus 1 is connected to the second host apparatus 1, the CPU 70 of the memory card 2 recognizes that a certain user key is registered on the basis of the fact that the ciphered user key Kuf is held in the nonvolatile memory 75, or the like (the step S12, YES).

- 28 -

Then, the CPU 70 determines whether or not the configuration mode is in the on-state (step S15). This determination is executable with reference to the status information set to, for example, the register 72 in the memory card 2.

5

10

15

20

25

When the configuration mode is in the on-state (the step S15, ON), the memory card 2 is in the locked state, and the configuration operation is in an executable state (step S16). The second host apparatus 1 sets the user key (step S17). Then, as long as the configuration mode is not turned off, it remains in the step S16.

When the second host apparatus 1 turns off the configuration mode in the step S16 (step S18), the execution of the configuration operation is prohibited, while the memory card 2 maintains the locked state (step S19).

In the step S19, the host apparatus can execute the unlocking operation (step S20). In the unlocking operation, when the memory card 2 is authenticated by the user key registered by the second host apparatus, the memory card 2 changes to the unlocked state (the step S13). In consequence, the host apparatus 1 can access the file system data area 51 of the memory card 2. Whether to prohibit the reading of the data from the file system management area 50 depends on a mounting condition.

Moreover, when the host apparatus 1 executes the locking operation to the memory card 2 in the unlocked

- 29 -

state, the memory card 2 can be changed to the locked state.

At this time, the host apparatus 1 determines whether or

not the user key is matched, and when matched, the host

apparatus 1 sets the memory card to the locked state.

Alternatively, the host apparatus 1 may only confirm that the user key is registered, and when any user key is registered, the host apparatus 1 may set the memory card to the locked state.

## 2.2 Configuration Operation

5

20

The details of the above configuration operation will be described with reference to FIG. 7. FIG. 7 is a table showing contents of the configuration operation.

The configuration operation includes the following seven functions.

- 15 (1) "Set User Key": a function of setting (registering) the user key

- (2) "Clear User Key": a function of clearing the registered user key

- (3) "Verify User Key": a function of verifying the registered user key

- (4) "Enable Key Ciphering": a function of enabling the ciphering of the key

- (5) "Disable Key Ciphering": a function of disabling the ciphering of the key

- 25 (6) "Enable Config. Mode": a function for turning on the configuration mode in the locked state

- (7) "Disable Config. Mode": a function for turning

- 30 -

off the configuration mode in the locked state

Here, the seven basic functions are exemplified, but a configuration function can be expanded. Therefore, for example, when the unlocked state is changed by a specific user key, it is possible to add the setting of performing a special operation in which the reading of the memory space is only allowed, and the writing is not allowed. There is no special restriction on the type of the function.

Hereinafter, the details of the configuration operation will successively be described.

#### 2.3 "Set User Key" Function

5

10

15

20

25

The "Set User Key" function will be described. As described above, an unique user key can be set as the user key for each host apparatus. Then, after the user keys are set, the memory card can be set to a usable state (the unlocked state) by inputting any registered user key. The use of the long key considerably lowers the probability that the same key is set for different host apparatuses.

#### 2.3.1 Operation of Host Apparatus 1

First, the operation of the host apparatus 1 during the execution of the "Set User Key" function will be described with reference to FIG. 8. FIG. 8 is a flowchart showing a flow of the processing of the host apparatus 1, and this processing is performed, for example, mainly by the CPU 60.

As shown in the drawing, the CPU 60 of the host apparatus 1 issues the reading command for the register 72

- 31 -

of the memory card 2, and reads the status information of the memory card 2 (step S31). Then, the CPU 60 checks whether the key ciphering is enabled or disabled (step S32). The information on whether the key ciphering is enabled or disabled is read as a part of the status information in the step S31. Moreover, the enabling/disabling of the key ciphering can be set in a state where no user keys are registered, and the enabling/disabling cannot be changed once the user key is registered. However, when all the user keys are cleared, the enabling/disabling can be set again. It is to be noted that the key ciphering is disabled as the default.

5

10

15

20

25

When the key ciphering is used (step S33, YES), the host apparatus 1 executes the "Enable Key Ciphering" function, to enable the key ciphering (step S34).

When the key ciphering is not used (the step S33, NO), the host apparatus 1 transmits a plaintext of the user key Ku as it is, from the host controller 65 to the memory card 2 (step S35). This user key Ku may automatically be prepared by using of the management utility by the CPU 60, or the input of the user key from the user may be accepted. The transmitted user key Ku is ciphered by F() and held in the register 73 of the memory card 2 (Kuf).

When the key ciphering is used (the step S32, YES, and the step S34), the conversion function Gh() for use is determined on the basis of the status information read in the step S31, and the code Ccg corresponding to the

- 32 -

function is determined. From Gc() and Gh() pairs supported by the card, one pair which is usable by the host apparatus is selected. Then, the user key Ku is ciphered by using the conversion function Gh() (step S36). The ciphered user key Kut is calculated in accordance with Kut = Gh(Kcp, Ku).

Then, the host apparatus 1 transmits the determined code Ccg and the ciphered user key Kut from the host controller 65 to the memory card 2 (step S37). These pieces of information are held in the register 73 of the memory card 2.

5

10

15

20

25

Afterward, the host apparatus 1 issues an execution command of the "Set User Key" function to the memory card 2. In response to this command, the "Set User Key" function is executed in the memory card 2 (step S38). The processing in the memory card 2 will be described later with reference to FIG. 9.

Afterward, when a busy state of the memory card 2 is cleared, the host apparatus 1 recognizes that the processing in the memory card 2 is completed. The busy state is a state where the memory card 2 cannot accept any commands. When the busy state is cleared to change to a ready state, the memory card 2 can accept the command. This information is sent as a ready/busy signal (or packet information to be sent from the card to the host apparatus) from the memory card 2 to the host apparatus 1.

Then, the host apparatus 1 reads the status information, for example, from the register 72 of the

- 33 -

memory card 2 (step S39). Then, the host apparatus 1 checks the execution result in the memory card 2 (step S40). As a result, when the configuration operation in the memory card 2 is successful (the step S40, Success), the host apparatus 1 recognizes that the "Set User Key" function is normally completed. On the other hand, when the configuration operation fails (the step S40, Fail), the host apparatus 1 recognizes that the "Set User Key" function has failed.

2.3.2 Operation of Memory Card 2

5

10

15

20

25

Next, the operation of the memory card 2 in the above step S38 will be described with reference to FIG. 9. FIG. 9 is a flowchart showing the processing of the memory card.

As shown in the drawing, when the execution command of the "Set User Key" function is received from the host apparatus 1, for example, the CPU 70 of the memory card 2 judges whether or not the key ciphering is enabled (step S51). When the key ciphering is enabled (the step S51, YES), the CPU 70 reads the information set to the register 73 to process the information. The conversion function Gc() corresponding to the code Ccg received from the host apparatus 1 is determined, and further the ciphered user key Kuf to be stored in the nonvolatile memory 75 is calculated from the received ciphered user key Kut by use of the conversion function F() (step S52). More specifically, the ciphered user key Kuf is calculated in accordance with Kuf = F(Gc(Kcs, Kut), "Enc"). Kut is

- 34 -

decoded to Ku by Kcs which is the secret key of the RSA cipher Gc. Therefore, Gc(Kcs, Kut) = Ku. When the key is stored in the flash memory, the key is set so that the key cannot be seen. Kuf obtained by ciphering Ku by the conversion function F() is calculated.

5

10

15

20

25

On the other hand, when the key ciphering is not enabled (the step S51, NO), the CPU 70 calculates Kuf by ciphering the received plaintext user key Ku with the conversion function F() (step S53). More specifically, the ciphered user key Kuf is calculated in accordance with Kuf = F(Ku, "Enc").

After the step S52 or S53, the CPU 70 writes the calculated ciphered user key Kuf into the nonvolatile memory 75 (step S54). Then, the CPU 70 checks whether or not the writing of the ciphered user key Kuf into the nonvolatile memory 75 is successful (step S55).

When the writing is successful (the step S55, YES), the CPU 70 stores the status information indicating that the configuration operation is successful, for example, in the register 72 (step S56). On the other hand, when the writing fails (the step S55, NO), the CPU 70 stores, in the register 72, the status information indicating that the configuration operation has failed (step S57).

Afterward, the CPU 70 clears the busy state, to end the configuration operation.

2.3.3 "Set User Key" Sequence

Next, a sequence during the execution of the above

- 35 -

"Set User Key" function will be described. In the present description, the above descriptions of 2.3.1 and 2.3.2 are simplified and summarized.

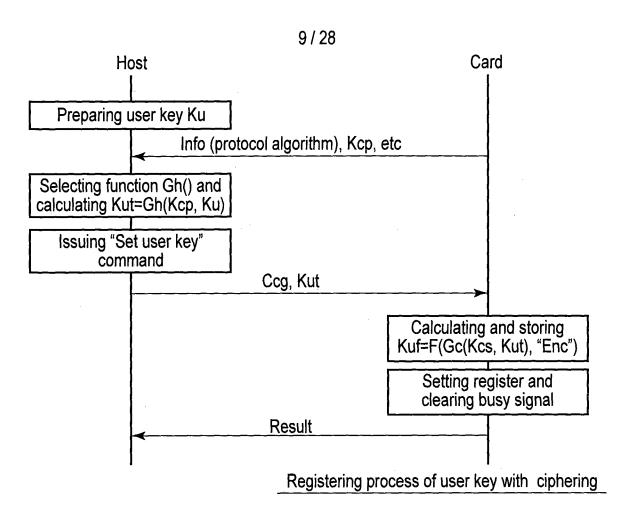

FIG. 10 shows a "Set User Key" sequence of a case where the key ciphering is enabled.

5

10

15

20

25

As shown in the drawing, the host apparatus 1 first determines the user key Ku. As described above, the user key Ku is prepared by the management utility, or the input of the user key from the user is accepted. Then, the host apparatus 1 ciphers the user key Ku by the conversion function F(), to prepare the ciphered user key Kuf, and this key is held in the key storage area 63. It is to be noted that the host apparatus 1 reads the ciphered user key from the key storage area 63, and decodes this key by the conversion function F(), whereby the plaintext user key Ku can be obtained.

Then, the host apparatus 1 reads card information (a protocol/algorithm of the ciphering (the Gh() list) or the public key Kcp) from the memory card 2. Then, the host apparatus 1 selects the usable conversion function Gh() from the Gh() list, and ciphers the user key Ku to calculate the ciphered user key Kut (= Gh(Kcp, Ku)). Furthermore, the host apparatus 1 transmits, to the memory card 2, the code Ccg indicating the selected Gh() and the ciphered user key Kuf (sets the information in the register 73), and the host apparatus instructs the memory card 2 to register the prepared user key Ku.

- 36 -

The memory card 2 selects the conversion function Gc() on the basis of the code Ccg received in the register 73, and deciphers (decodes) the ciphered user key Kut by the corresponding secret key Kcs, to obtain the plaintext user key Ku. Then, the memory card 2 prepares the ciphered user key Kuf (= F(Ku, "Enc") by use of the key conversion function F(), and stores the key in the nonvolatile memory 75. Then, the memory card 2 notifies the host apparatus 1 of the registration completion or registration failure.

5

10

15

20

25

By the above, the user key Ku is registered between the host apparatus 1 and the memory card 2. It is to be noted that as the cipher function Gh, for example, the ciphering of RSA2048 is used, and as Gc, for example, the decoding of RSA2048 is used.

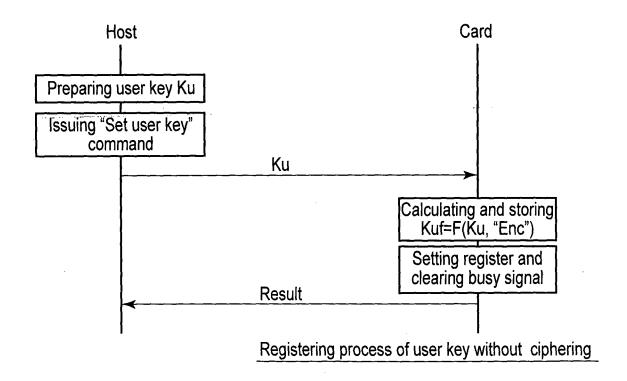

FIG. 11 shows the "Set User key" sequence of a case where the key ciphering is disabled. The status information indicating that the ciphering is disabled is present in the status register 72, but it is assumed that the host apparatus 1 already reads this register, and hence the information is omitted from FIG. 11.

As shown in the drawing, the host apparatus 1 first determines the user key Ku. As described above, the user key Ku is prepared by the management utility, or the input of the user key from the user is accepted. Then, the host apparatus 1 ciphers the user key Ku by the conversion function F(), to prepare the ciphered user key Kuf, and this key is held in the key storage area 63.

- 37 **-**

Then, the host apparatus 1 transmits the plaintext user key Ku to the memory card 2, and instructs the memory card 2 to register the prepared user key Ku.

The memory card 2 prepares the ciphered user key Kuf (= F(Ku, "Enc")) by use of the key conversion function F(), and stores the key in the nonvolatile memory 75. Then, the memory card 2 notifies the host apparatus 1 of the registration completion or registration failure.

5

10

15

20

25

2.4 "Clear/Verify User Key", "Enable/Disable Key Ciphering", and "Enable/Disable Config. Mode" Functions

Next, there will be described the "Clear User Key" function, the "Verify User Key" function, the "Enable Key Ciphering" function, the "Disable Key Ciphering" function, the "Enable Key Config. Mode" function and the "Disable Config. Mode" function. The "Clear User Key" function is the function for clearing the registered user key from the memory card 2. The "Verify User Key" function is the function for verifying whether the registered user key is valid or not (correct or not). The "Enable Key Ciphering" and "Disable Key Ciphering" functions are the functions for enabling and disabling the key ciphering, respectively. The "Enable Config. Mode" and "Disable Config. Mode" functions are functions for turning on and off the configuration mode, respectively.

2.4.1 Operation of Host Apparatus 1

The operation of the host apparatus 1 during the execution of the above "Clear/Verify User Key",

- 38 -

"Enable/Disable Key Ciphering" or "Enable/Disable Config.

Mode" function will be described with reference to FIG. 12.

FIG. 12 is a flowchart showing a flow of the processing of the host apparatus 1, and this processing is performed, for example, mainly by the CPU 60.

5

10

15

20

25

As shown in the drawing, the CPU 60 of the host apparatus 1 issues the reading command for the register 72 of the memory card 2, and reads the status information of the memory card 2 (step S61). When the function to be executed is "Clear User Key" or "Verify User Key" (step S62, "Clear User Key" or "Verify User Key"), the processing proceeds to the processing of step S63. Then, the CPU 60 checks whether the key ciphering is enabled or disabled (the step S63). When the key ciphering is disabled (the step S63, NO), the host apparatus 1 transmits the plaintext user key Ku as it is, from the host controller 65 to the memory card 2 (step S64). The transmitted user key Ku is held in the register 73 of the memory card 2.

When the key ciphering is enabled (the step S63, NO), the host apparatus determines the conversion function H() for use on the basis of the status information (the H() list) read in the step S61, and determines the code Cch corresponding to the determined function. Then, the host apparatus ciphers the user key Ku by use of the conversion function H(), to calculate the challenge number Nt (step S65). The challenge number Nt is calculated in accordance with Nt = H(Nr, Ku). The random number Nr is also

- 39 -

information read as the status information from the memory card 2. Then, the host apparatus 1 transmits the determined code Cch and the challenge number Nt from the host controller 65 to the memory card 2 (step S66). These pieces of information are held in the register 73 of the memory card 2.

5

10

15

20

25

Afterward, the host apparatus 1 issues the execution command of the "Clear User Key" function or the "Verify User Key" function to the memory card 2. In response to this command, in the memory card 2, the "Clear User Key" function or the "Verify User Key" function is executed (step S70). The processing in the memory card 2 will be described later with reference to FIG. 13.

When the busy state of the memory card 2 is cleared, the host apparatus 1 recognizes that the processing in the memory card 2 is completed. Then, the host apparatus 1 reads the status information, for example, from the register 72 of the memory card 2 (step S71). Then, the host apparatus 1 checks the execution result in the memory card 2 (step S72). In consequence, when the configuration operation in the memory card 2 is successful (the step S72, Success), the host apparatus 1 recognizes that "Clear User Key" or "Verify User Key" is normally completed. That is, when the "Clear User Key" function is executed, the host apparatus recognizes that the user key Ku transmitted in the step S64 is cleared. On the other hand, when the "Verify User Key" function is executed, the host apparatus

- 40 -

recognizes that the user key Ku transmitted in the step S64 or the step S66 is the correct user key.

On the other hand, when the configuration operation fails in the step S70 (the step S72, Fail), the host apparatus 1 recognizes that "Clear User Key" or "Verify User Key" has failed. That is, when the "Clear User Key" function is executed, the host apparatus recognizes that the user key Ku transmitted in the step S64 is not cleared. On the other hand, when the "Verify User Key" function is executed, the host apparatus recognizes that the user key Ku transmitted in the step S64 or the step S66 is the wrong user key.

5

10

15

20

25

When the function to be executed is "Enable Key Ciphering", "Disable Key Ciphering", "Enable Config. Mode" or "Disable Config. Mode" (the step S62, Others), the user key Ku is not required, and hence the processing of the steps S64 to S66 is omitted. Then, when the "Enable Key Ciphering" function or the "Disable Key Ciphering" function is executed, the CPU 60 issues an enabling command or a disabling command of the key ciphering, and transmits the command to the memory card 2 (step S68). On the other hand, when the "Enable Config. Mode" function or the "Disable Config. Mode" function is executed, the CPU 60 issues the enabling command or the disabling command of Config. Mode, and transmits the command to the memory card 2 (step S69).

In response to these commands, in the memory card 2, the "Enable Key Ciphering", "Disable Key Ciphering",

- 41 **-**

"Enable Config. Mode" or "Disable Config. Mode" operation is executed (the step S70). These details will be described later with reference to FIG. 16 and FIG. 17.

5

10

15

20

25

Afterward, the processing advances to the step S71. It is to be noted that as described above, the setting of the key ciphering is possible when the user key is not registered. Therefore, when the user key is registered and when the "Enable/Disable Key Ciphering" function is executed, the operation is notified as failure from the memory card 2 to the host apparatus 1.

2.4.2 Operation of Card of "Clear/Verify User Key"

Next, the operation of the card in the execution of

the "Clear/Verify User Key" function in the above step S70

will be described with reference to FIG. 13. FIG. 13 is a

flowchart showing the processing of the memory card 2.

As shown in the drawing, when the execution command of the "Clear/Verify User Key" function is received from the host apparatus 1, for example, the CPU 70 of the memory card 2 judges whether or not the key ciphering is enabled (step S81). When the key ciphering is enabled (the step S81, YES), the CPU 70 determines the conversion function H() corresponding to the code Cch received from the host apparatus 1, and further calculates the expected value Ne by use of the conversion function F(), the ciphered user key Kuf held in the nonvolatile memory 75, and the random number Nr held as the status information in the register 72 (step S82). More specifically, the expected value Ne is

- 42 -

calculated in accordance with Ne = H(Nr, F(Kuf, "Dec")). Then, the CPU 70 compares the challenge number Nt received from the host apparatus 1 with the calculated expected value Ne (step S83).

5

10

15

20

25

When the key ciphering is not enabled (the step S81, NO), the CPU 70 ciphers the received plaintext user key Ku to calculate the comparison value Kuv by use of the conversion function F() (step S84). More specifically, the comparison value Kuv is calculated in accordance with Kuv = F(Ku, "Enc"). Then, the CPU 70 compares the ciphered user key Kuf read from the nonvolatile memory 75 with the calculated comparison value Kuv (step S85).

As a result of the comparison, when both the values are not matched (step S86, NO), the CPU 70 stores the status information indicating that the configuration operation has failed, for example, in the register 72 (step S91).

As a result of the comparison, when both the values are matched (the step S86, YES), the processing proceeds to the processing of step S87. That is, when the function to be executed is "Clear User Key" (the step S87, Clear), the ciphered user key Kuf matched in the step S83 or S85 is cleared from the nonvolatile memory 75 (step S88). When the clearing fails (step S89, YES), the processing proceeds to the step S91. When the clearing is successful (the step S89, NO), the CPU 70 stores, in the register 72, the status information indicating that the configuration operation is

- 43 -

successful (step S90). When the function to be executed is "Verify User Key" (the step S87, Verify), the processing proceeds to the step S90.

Afterward, the CPU 70 clears the busy state, to end the configuration operation.

### 2.4.3 "Clear User Key" Sequence

5

10

15

20

25

Next, a sequence during the execution of the above "Clear User Key" function will be described. In the present description, the description of the "Clear User Key" function in the above 2.4.1 and 2.4.2 is simplified and summarized.

FIG. 14 shows the "Clear User Key" sequence of the case where the key ciphering is enabled.

As shown in the drawing, the host apparatus 1 first reads the card information (the protocol/algorithm of the ciphering (the H() list) or the random number Nr) from the memory card 2. Then, the host apparatus 1 selects the usable conversion function H() from the H() list, and ciphers the user key Ku by use of the random number Nr, to calculate the challenge number Nt (= H(Nr, Ku)). Here, the user key Ku to be ciphered is a user key desired to be cleared by the host apparatus 1. Furthermore, the host apparatus 1 transmits, to the memory card 2, the code Ccg indicating the selected H() and the calculated challenge number Nt, and instructs the memory card 2 to clear the user key Ku.

The memory card 2 reads the ciphered user key Kuf

- 44 -

stored in the nonvolatile memory 75, and deciphers (decodes) the key by the conversion function F(), to obtain the plaintext user key Ku. Then, the memory card 2 selects the conversion function H() on the basis of the received code Ccg, and calculates the expected value Ne ( $\approx$  H(Nr, F(Kuf, "Dec"))).

5

10

15

20

25

Then, the memory card 2 compares the challenge number Nt with the expected value Ne, and clears the corresponding ciphered user key Kuf from the nonvolatile memory 75. It is to be noted that when a plurality of ciphered user keys Kuf are stored in the nonvolatile memory 75, the expected value Ne is calculated for each key, and each expected value Ne is compared with the challenge number Nt. Then, the memory card clears the ciphered user key Kuf corresponding to the expected value matching the challenge number Nt, among the expected values Ne. Then, the memory card 2 notifies the host apparatus 1 of clearing completion or clearing failure of the user key.

By the above, the host apparatus 1 can clear the user key registered in the memory card 2.

FIG. 15 shows the "Clear User Key" sequence of the case where the key ciphering is disabled. The status information indicating that the ciphering is disabled is present in the register 72, but it is presumed that the host apparatus 1 has already read this register, and hence the status information is omitted from FIG. 15.

As shown in the drawing, the host apparatus 1 first

- 45 -

transmits the plaintext user key Ku to the memory card 2, and instructs the memory card 2 to clear the user key Ku.

5

10

15

20

25

Then, the memory card 2 ciphers the received plaintext user key Ku by use of the conversion function F(), to obtain the comparison value Kuv. Then, the memory card 2 compares the comparison value Kuv with the ciphered user key Kuf held in the nonvolatile memory 75, and clears the ciphered user key Kuf from the nonvolatile memory 75. Then, the memory card 2 notifies the host apparatus 1 of the clearing completion or the clearing failure of the user key.

It is to be noted that although not shown in the drawing, there is also a method in which Kuv is calculated in accordance with Kuv = F(Kuf, "Dec"), and compared with Ku.

It is to be noted that a sequence of the "Verify User Key" function corresponds to FIG. 14 and FIG. 15 from which the clearing processing of Kuf is omitted, and hence a detailed description is omitted.

2.4.4 Operation of Card of "Enable/Disable Key Ciphering"

Next, an operation of the card in the execution of the "Enable/Disable Key Ciphering" function in the step S70 of FIG. 12 will be described with reference to FIG. 16. FIG. 16 is a flowchart showing the processing of the memory card 2.

As shown in the drawing, when the execution command of the "Enable Key Ciphering" function or the "Disable Key

- 46 -

Ciphering" function is received from the host apparatus 1, for example, the CPU 70 of the memory card 2 judges whether or not the user key is registered (step S101). When the user key has already been registered by any host apparatus 1 (the step S101, NO), the on/off of the key ciphering cannot be changed, and hence the processing proceeds to step S106 in which the execution of the function fails. That is, the CPU 70 stores the status information indicating that the configuration operation has failed, for example, in the register 72.

5

10

15

20

25

When the user key is not registered (the step S101, YES), the "Enable/Disable Key Ciphering" function is executable. When the execution command of the "Enable Key Ciphering" function is received (step S102, Set Enable mode), the CPU 70 enables the key ciphering, and stores information indicating the enabling as the status information in the register 72 (step S103). When the execution command of the "Disable Key Ciphering" function is received (the step S102, Set Disable mode), the CPU 70 disables the key ciphering, and stores information indicating the disabling as the status information in the register 72 (step S104).

Then, the CPU 70 stores the status information indicating that the configuration operation is successful, for example, in the register 72 (step S105). Afterward, the CPU 70 clears the busy state, to end the configuration operation.

- 47 -

2.4.5 Operation of Card of "Enable/Disable Config. Mode"

Next, an operation of the card in the execution of the "Enable/Disable Config. Mode" function in the step S70 of FIG. 12 will be described with reference to FIG. 17. FIG. 17 is a flowchart showing the processing of the memory card 2.

5

10

15

20

25

As shown in the drawing, when the execution command of the "Enable Config. Mode" or the "Disable Config. Mode" function is received from the host apparatus 1, for example, the CPU 70 of the memory card 2 judges whether or not the user key is registered (step S111). When the user key is not registered (the step S111, NO), the memory card 2 is in the unlocked state. Therefore, the host apparatus 1 can execute the configuration operation freely between the host apparatus and the memory card 2. Therefore, it is not necessary to set the configuration mode, and the processing proceeds to step S116 in which the execution of the function fails. That is, the CPU 70 stores the status information indicating that the configuration operation has failed, for example, in the register 72.

When the user key is registered (the step S111, YES), the "Enable/Disable Config. Mode" function is executable. When the execution command of the "Enable Config. Mode" function is received (step S112, Set Enable mode), the CPU 70 turns on the configuration mode (step S113). When the execution command of the "Disable Config. Mode" function is

- 48 -

received (the step S112, Set Disable mode), the CPU 70 turns off the configuration mode (step S114).

After the step S113 or S114, the CPU 70 stores the status information indicating that the configuration operation is successful, for example, in the register 72 (step S115). Afterward, the CPU 70 clears the busy state, to end the configuration operation.

#### 2.5 Unlocking Operation

5

10

15

20

25

Next, there will be described the unlocking operation for changing the memory card 2 in the locked state to the unlocked state in the memory system according to the present embodiment.

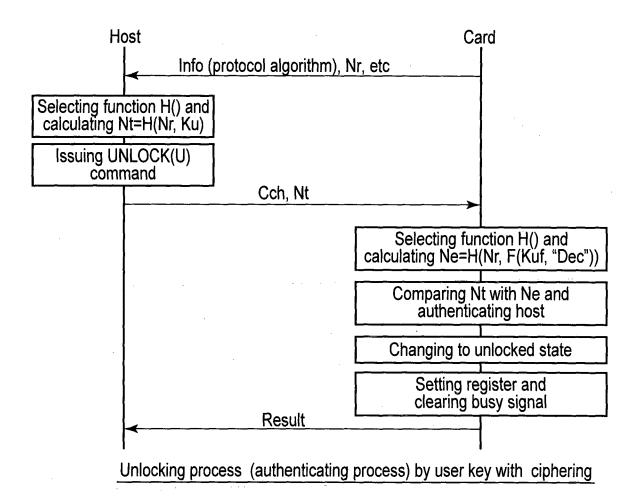

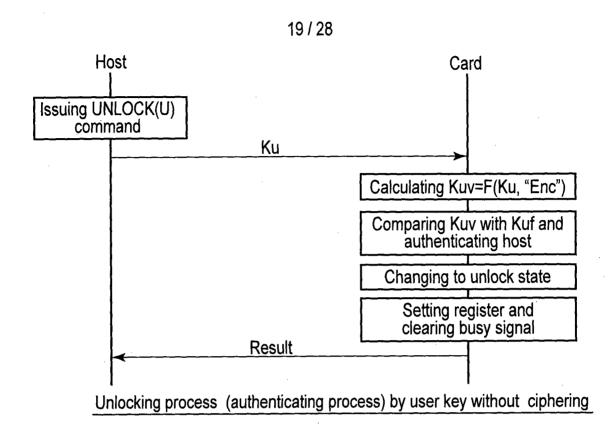

# 2.5.1 Type of Unlocking Operation

In the present embodiment, three types of unlocking operations are prepared. These unlocking operations will be described with reference to FIG. 18. FIG. 18 is a flowchart showing how to select the three types of the unlocking operation.

As shown in the drawing, when the user key is known (step S121, YES), the unlocking operation using the user key (an UNLOCK(U) operation) is executed (step S123). The case where the user key is known is a case where the user key Ku prepared by the management utility is correctly held in the host apparatus 1, a case where the correct user key input by the user is accepted, or the like.

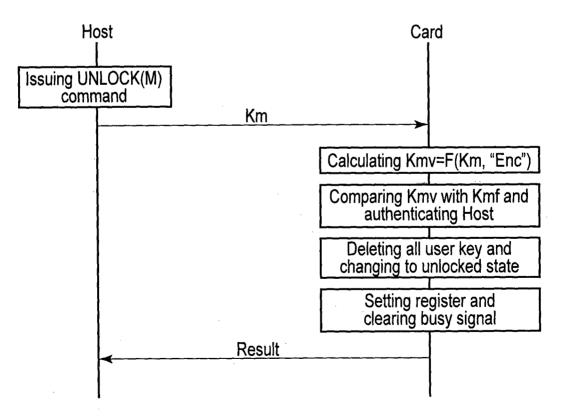

Even when the user key is not remembered (the step S121, NO) and if the user knows the master key (step S122,

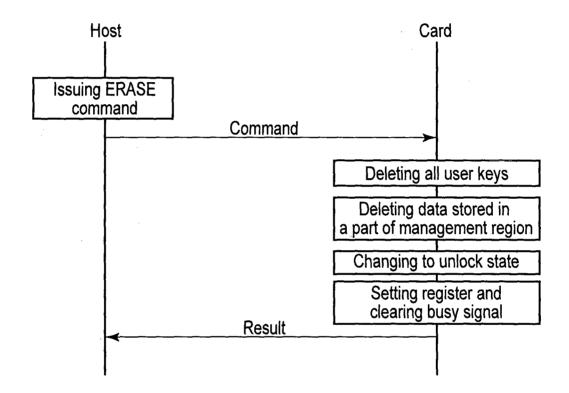

NO), an unlocking operation using the master key (an UNLOCK(M) operation) is possible (step S124). That is, when the input of the correct master key is accepted from the user, the UNLOCK(M) operation is executed, and the memory card 2 can be changed to the unlocked state. However, when the UNLOCK(M) operation is executed, all the user keys registered in the memory card 2 are erased deleted differently from the UNLOCK(U) operation. However, the file system management area 50 and the file system data area 51 are not erased.

5

10

15

20

When the master key is lost (the step S122, YES), the memory card 2 can be changed from the locked state to the unlocked state by performing the erase operation (step S125). In this case, not only all the user keys but also at least a part of the information in the management area 50 is erased. When all the memory area 51 is erased, a considerably long time is required. Therefore, by a method in which a part of the user data area is erased or a method in which the controller 32 shuffles, for example, a table for converting the logical address to the physical address, the read data is changed to meaningless data, which shortens the time to disable the data.

### 2.5.2 Operation of Host Apparatus 1

Next, details of the above unlocking operation will be described. FIG. 19 is a flowchart showing the processing of the host apparatus 1 in the unlocking operation using the user key or the master key (in the UNLOCK(U) or

<del>-</del> 50 -

UNLOCK(M) operation). This unlocking operation is executable, when the memory card 2 is in the locked state and the configuration mode is off-state.

5

10

15

20

25

As shown in the drawing, the CPU 60 of the host apparatus 1 issues the reading command for the register 72 of the memory card 2, and reads the status information of the memory card 2 (step S131). The status information includes information indicating whether or not the key ciphering is enabled, information (the H() list) indicating the type of a usable cipher system, the public key (Kcp), and the random number (Nr) when the key ciphering is enabled. Then, the CPU 60 checks, on the basis of the read status information, whether the key ciphering is enabled or disabled (step S132).

When the key ciphering is not enabled (the step S132, Not Used), the host apparatus 1 transmits the plaintext of the user key Ku or the master key Km as it is, from the host controller 65 to the memory card 2 (step S133).

When the key ciphering is enabled (the step S132, Used), the CPU 60 of the host apparatus 1 determines the conversion function H() for use on the basis of the H() list read in the step S131, and determines the code Cch corresponding to the determined function. Then, the CPU ciphers the user key Ku with the random number Nr by use of the conversion function H(), to calculate the challenge number Nt (step S134). That is, the challenge number Nt is calculated in accordance with Nt = H(Nr, Ku).

- 51 -

Then, the host apparatus 1 transmits the determined code Cch and the calculated challenge number Nt from the host controller 65 to the memory card 2 (the step S133). These pieces of information are held in the register 73 of the memory card 2.

5

10

15

20

25

It is to be noted that when one type of usable cipher system is determined, it is not necessary to identify the system, and hence the code Cch does not necessarily have to be sent. Moreover, even when the key ciphering is enabled, the ciphering of the master key does not have to be performed. In this case, it may be determined in advance that the master key is not ciphered, for example, between the host apparatus 1 and the memory card 2. In this case, there is the merit that the mounting lock/unlock function can easily be achieved.

Afterward, the host apparatus 1 issues the execution command of the unlocking operation (UNLOCK(U), UNLOCK(M)) to the memory card 2. In response to this command, the unlocking operation is executed in the memory card 2 (step S136). The processing in the memory card 2 will be described later with reference to FIG. 20.

When the busy state of the memory card 2 is cleared, the host apparatus 1 recognizes that the processing in the memory card 2 is completed. Then, the host apparatus 1 reads the status information from the register 72 of the memory card 2 (step S137). When state information included in the status information indicates that the memory card 2

- 52 -

is in the unlocked state (step S138, Unlocked), the host apparatus 1 recognizes that the unlocking operation is successful. On the other hand, when the state information indicates that the memory card 2 is in the locked state (the step S138, Locked), the host apparatus 1 recognizes that the unlocking operation has failed.

## 2.5.3 Operation of Memory Card 2

5

10

15

20

25