(19) **日本国特許庁(JP)**

(51) Int. Cl.

# (12)特許公報(B2)

(11)特許番号

特許第5537681号 (P5537681)

(45) 発行日 平成26年7月2日(2014.7.2)

(24) 登録日 平成26年5月9日(2014.5.9)

HO4N 19/60 (2014.01) HO4N 7/133

FL

$\mathbf{Z}$

請求項の数 15 (全 26 頁)

(21) 出願番号 特願2013-6987 (P2013-6987) (22) 出願日 平成25年1月18日 (2013.1.18) (65) 公開番号 特開2013-150323 (P2013-150323A) (43) 公開日 平成25年8月1日(2013.8.1) 審査請求日 平成25年1月18日 (2013.1.18)

(31) 優先権主張番号 12151973.0

平成24年1月20日 (2012.1.20) (32) 優先日

(33) 優先権主張国 欧州特許庁(EP) (73)特許権者 500043574

ブラックベリー リミテッド

カナダ国 エヌ2ケー 〇エー7 オンタ リオ、 ウォータールー、 ユニバーシテ ィ アベニュー イースト 2200

(74)代理人 100107489

弁理士 大塩 竹志

|(72)発明者 ワン ジン

カナダ国 エヌ2エル 3ダブリュー8, オンタリオ、 ウォータールー、 フィ リップ ストリート 295、 エクステ ンション 75923

最終頁に続く

(54) 【発明の名称】変換ユニット内の複数サインビット秘匿

# (57)【特許請求の範囲】

# 【請求項1】

変換ユニットに対する係数を再構成することによってエンコードされたビデオのビット ストリームをデコーダがデコードする方法であって、該ビットストリームは、該変換ユニ ットに対するサインビットの2つ以上のセットをエンコードし、サインビットの各セット は、該変換ユニットに対する係数のそれぞれのセットに対応しており、各サインビットは 、該それぞれのセット内の対応する非ゼロ係数のサインを示しており、

該方法は、

サインビットの該2つ以上のセットの各々に対して、

サインビットの当該セットに対応する該それぞれのセットに対する係数の絶対値を合計 して、パリティ値を取得することと、

該パリティ値が偶数であるか奇数であるかに基づいて、該それぞれのセット内の該係数 のうちの1つにサインを割り当てることと

を含む、方法。

## 【請求項2】

係数の前記それぞれのセットの各々は、それぞれの4×4係数ブロックに対応している 、請求項1に記載の方法。

## 【請求項3】

係数の前記それぞれのセットの各々は、それぞれの4×4係数ブロックのグループに対 応しており、該グループの各々における該係数プロックは、ブロックレベルスキャン順序

20

における連続ブロックである、請求項1に記載の方法。

# 【請求項4】

前記方法は、スキャン順序における第1非ゼロ係数と最終非ゼロ係数との間の係数の前記それぞれのセット内の係数の数が、閾値を超えていることを決定することをさらに含む、請求項1~3のいずれか一項に記載の方法。

# 【請求項5】

割り当てることは、前記パリティ値が奇数の場合には、前記係数のうちの1つを負にし、前記パリティ値が偶数の場合には、前記係数のうちの1つを正のままにすることを含む、請求項1~4のいずれか一項に記載の方法。

# 【請求項6】

変換ユニットに対する係数を再構成するようにエンコードされたデータのビットストリームをデコードするデコーダであって、

該デコーダは、

プロセッサと、

メモリと、

メモリ内に格納され、かつ請求項 1 ~ 5 のいずれか一項に記載の方法を実行するように該プロセッサを構成するための命令を含むデコーディングアプリケーションと

を含む、デコーダ。

# 【請求項7】

変換ユニットに対する係数に対するサインビットをエンコードすることによ<u>って</u>ビデオ のビットストリームをエンコーダがエンコードする方法であって、

該方法は.

該変換ユニットに対する係数の2つ以上のセットの各々に対して、

当該セットに対する係数の絶対値を合計して、パリティ値を取得することと、

当該セット内の係数のうちの1つのサインが該パリティ値に対応していないことを決定 することと、

該係数のうちの1つのサインに対応するように該パリティ値を変化させるために、当該セット内の係数のレベルを1だけ調整することと

を含む、方法。

# 【請求項8】

係数の前記2つ以上のセットの各々に対して、該係数のうちの1つを除いて、当該セット内のすべての非ゼロ係数に対するサインビットをエンコードすることをさらに含む、請求項7に記載の方法。

# 【請求項9】

係数の前記2つ以上のセットの各々は、それぞれの4×4係数ブロックを含む、請求項7または請求項8に記載の方法。

# 【請求項10】

係数の前記セットの各々は、それぞれの4×4係数ブロックのグループに対応しており、該グループの各々における該係数ブロックは、ブロックレベルスキャン順序における連続ブロックである、請求項7または請求項8に記載の方法。

【請求項11】

前記方法は、スキャン順序における第1非ゼロ係数と最終非ゼロ係数との間の係数のセット内の係数の数が閾値を超えていることを決定することをさらに含む、請求項7~10のいずれか一項に記載の方法。

## 【請求項12】

レベルを調整することは、レート歪み最適化を用いて調整されるべき前記セット内の係数を選択することを含む、請求項 7 ~ 1 1 のいずれか一項に記載の方法。

# 【請求項13】

前記レート歪み最適化は、レートコストを評価するために、予め定義されたコストメト リックを用いる、請求項12に記載の方法。 10

20

30

40

## 【請求項14】

変換ユニットに対する係数に対するサインデータをエンコードすることにより、ビデオ のビットストリームをエンコードするエンコーダであって、

該エンコーダは、

プロセッサと、

メモリと、

メモリ内に格納され、かつ請求項7~13のいずれか一項に記載の方法を実行するように<u>該</u>プロセッサを構成するための命令を含むエンコーディングアプリケーションと を含む、エンコーダ。

# 【請求項15】

プロセッサ実行可能な命令を格納してい<u>る</u>プロセッサ読み取り可能な<u>記録</u>媒体であって、該命令は、実行されたときに、請求項1~5、7~13のうちのいずれか一項における方法を1つ以上のプロセッサに実行させる、プロセッサ読み取り可能な記録媒体。

【発明の詳細な説明】

## 【技術分野】

# [0001]

# (著作権情報)

本文書および付随する題材の開示の一部分は、著作権の主張がなされる題材を含んでいる。著作権所有者は、特許文書または特許開示は特許商標庁のファイルまたは記録に現れているので、該特許文書または特許開示の何人による複製に対しても異議を有してはいないが、その他のすべての著作権については、どのようなものであっても留保している。

### [00002]

(分野)

本願は、概して、データ圧縮に関し、特に、残余ビデオデータをエンコードおよびデコードするときにサインビットを秘匿するための方法およびデバイスに関している。

## 【背景技術】

# [0003]

## (背景)

データ圧縮は、多くのコンテキストにおいて行われる。データ圧縮は、情報を効率的に格納、伝送、再生するために、通信およびコンピュータネットワーキングにおいて、非常に一般的に用いられている。データ圧縮は、イメージ、オーディオ、ビデオのエンコーディングにおいて、特定の用途を見出している。ビデオは、各ビデオフレームに対して必要な大量のデータと、エンコーディングおよびデコーディングを行うためにしばしば必要とされるスピードとを理由として、データ圧縮に対する重大な挑戦を提示している。ビデオコーディングに対する現在の技術水準は、ITU・T H.264/AVCビデオコーディング規格である。該規格は、メインプロファイル、ベースラインプロファイル等を含む、異なる用途に対する多くの異なるプロファイルを定義している。次世代のビデオエンコーディング規格は、High Efficienfy Video Coding(HEVC)といわれるMPEG・ITUの合同研究を通して現在開発中である。該研究は、最終的には、MPEG・Hと一般的に称されるビデオコーディング規格をもたらし得るものである。

# [0004]

ブロックベースのコーディングプロセスを用いるH.264を含む、イメージおよびビデオをエンコード / デコードするための多くの規格が存在する。これらのプロセスにおいて、イメージまたはフレームは、典型的には4×4または8×8であるブロックに分割され、該ブロックは、係数へとスペクトル的に変換され、量子化され、エントロピーエンコードされる。多くの場合においては、変換されるデータは、実際のピクセルデータではなく、予測オペレーションの後の残余データである。予測は、イントラフレーム、すなわちフレーム / イメージ内のブロックごとであり得、あるいはインターフレーム、すなわちフレームの間であり得る(動き予測とも称される)。MPEG・Hもまた、これらの特徴を

10

20

30

40

有し得ることが期待されている。

# [0005]

残余データをスペクトル的に変換するときに、これらの規格のうちの多くは、離散コサイン変換(DCT)またはそれに対するなんらかの変形の使用を記述する。結果としてのDCT係数は、その後、量子化器を用いて量子化され、量子化された変換ドメイン係数または指標を生成する。

### [0006]

量子化された変換ドメイン係数のブロックまたは行列(「変換ユニット」と称される場合がある)は、その後、特定のコンテキストモデルを用いて、エントロピーエンコードされる。 H . 2 6 4 / A V C において、そして、M P E G - H に対する現在開発中の仕事において、量子化された変換係数は、(a)変換ユニットにおける最終非ゼロ係数の位置を示す最終有意係数位置をエンコードすることと、(b)非ゼロ係数を含む変換ユニットにおける位置(最終有意係数位置以外)を示す有意マップをエンコードすることと、(c)非ゼロ係数の大きさをエンコードすることと、(d)非ゼロ係数のサイン(sign)をエンコードすることとにより、エンコードされる。量子化された変換係数のこのエンコーディングは、しばしば、ビットストリーム内のエンコードされたデータの30~80%を占める。

# [0007]

### 【発明の概要】

【課題を解決するための手段】

# [0008]

## (概要)

### [0009]

一局面において、本願は、変換ユニットに対する係数を再構成することによって、エンコードされたビデオのビットストリームをエンコードするための方法を記載しており、該ビットストリームは、変換ユニットに対するサインビットの2つ以上のセットをエンコードし、各セットは、変換ユニットに対する係数のそれぞれのセットに対応しており、各サインビットは、それぞれのセット内の対応する非ゼロ係数のサインを示す。方法は、サインビットの2つ以上のセットの各々に対して、サインビットの当該セットに対応するそれぞれのセットに対する係数の絶対値を合計して、パリティ値を取得することと、該パリティ値が奇数または偶数であるかどうかに基づいて、それぞれのセット内の係数のうちの1

10

20

30

40

つにサインを割り当てることを含む。

# [0010]

別の局面において、本願は、変換ユニットに対する係数に対するサインビットをエンコードすることにより、ビデオのビットストリームをエンコードするための方法を記載している。方法は、変換ユニットに対する係数の2つ以上のセットの各々に対して、当該セットに対する係数の絶対値を合計して、パリティ値を取得することと、当該セット内の係数のうちの1つのサインが、パリティ値に対応しないことを決定することと、係数のうちの1つの係数のサインに対応するように、パリティ値を変化させるために、1によって当該セット内の係数のレベルを調整することとを含む。

(5)

[0011]

10

さらなる局面において、本願は、エンコードおよびデコードするためのこのような方法 を実装するように構成されたエンコーダおよびデコーダを記載している。

#### [0012]

なおもさらなる局面において、本願は、実行されたときに、エンコードおよび / またはデコードするための記載された方法を実行するようにプロセッサを構成するコンピュータ 実行可能なプログラム命令を格納している持続性のコンピュータ読み取り可能な媒体を記載している。

#### [ 0 0 1 3 ]

本願のその他の局面および特徴は、当業者によって、添付図面と関連して以下の例の記載を参照することから、理解され得る。

20

## [0014]

本発明は、例えば、以下を提供する。

# (項目1)

変換ユニットに対する係数を再構成することによってエンコードされたビデオのビットストリームをデコードする方法であって、該ビットストリームは、該変換ユニットに対するサインビットの2つ以上のセットをエンコードし、サインビットの各セットは、該変換ユニットに対する係数のそれぞれのセットに対応しており、各サインビットは、該それぞれのセット内の対応する非ゼロ係数のサインを示しており、

該方法は、

サインビットの該2つ以上のセットの各々に対して、

30

40

50

サインビットの当該セットに対応する該それぞれのセットに対する係数の絶対値を合計 して、パリティ値を取得することと、

該パリティ値が偶数または奇数であるかどうかに基づいて、該それぞれのセット内の該係数のうちの1つにサインを割り当てることと

を含む、方法。

# (項目2)

係数の前記それぞれのセットの各々は、それぞれの4×4係数ブロックに対応している 、上記項目に記載の方法。

## (項目3)

係数の前記それぞれのセットの各々は、それぞれの4×4係数ブロックのグループに対応しており、該グループ内の各々における該係数ブロックは、ブロックレベルスキャン順序における連続ブロックである、上記項目のいずれか一項に記載の方法。

(項目4)

前記方法は、スキャン順序における第1非ゼロ係数と最終非ゼロ係数との間の係数の前記それぞれのセット内の係数の数が、閾値を超えていることを決定することをさらに含む、上記項目のいずれか一項に記載の方法。

# (項目5)

割り当てることは、前記パリティ値が奇数の場合には、前記係数のうちの1つを負にし、前記パリティ値が偶数の場合には、前記係数のうちの1つを正のままにすることを含む、上記項目のいずれか一項に記載の方法。

## (項目6)

変換ユニットに対する係数を再構成するようにエンコードされたデータのビットストリームをデコードするためのデコーダであって、

該デコーダは、

プロセッサと、

メモリと、

メモリ内に格納され、かつ上記項目のいずれか一項に記載の方法を実行するように該プロセッサを構成するための命令を含むデコーディングアプリケーションと を含む、デコーダ。

(項目7)

変換ユニットに対する係数に対するサインビットをエンコードすることにより、ビデオ のビットストリームをエンコードするための方法であって、

該方法は、

該変換ユニットに対する係数の2つ以上のセットの各々に対して、

当該セットに対する係数の絶対値を合計して、パリティ値を取得することと、

当該セット内の係数のうちの1つのサインが該パリティ値に対応していないことを決定 することと、

該係数のうちの1つのサインに対応するように該パリティ値を変化させるために、当該セット内の係数のレベルを1だけ調整することと

を含む、方法。

(項目8)

係数の前記2つ以上のセットの各々に対して、該係数のうちの1つを除いて、当該セット内のすべての非ゼロ係数に対するサインビットをエンコードすることをさらに含む、上記に記載の方法。

(項目9)

係数の前記2つ以上のセットの各々は、それぞれの4×4係数ブロックを含む、上記項目のいずれか一項に記載の方法。

(項目10)

係数の前記セットの各々は、それぞれの 4 × 4 係数ブロックのグループに対応しており、該グループの各々における該係数ブロックは、ブロックレベルスキャン順序における連続ブロックである、上記項目のいずれか一項に記載の方法。

(項目11)

前記方法は、スキャン順序における第1非ゼロ係数と最終非ゼロ係数との間の係数のセット内の係数の数が閾値を超えていることを決定することをさらに含む、上記項目のいずれか一項に記載の方法。

(項目12)

レベルを調整することは、レート歪み最適化を用いて調整されるべき前記セット内の係数を選択することを含む、上記項目のいずれか一項に記載の方法。

(項目13)

前記レート歪み最適化は、レートコストを評価するために、予め定義されたコストメト リックを用いる、上記項目のいずれか一項に記載の方法。

(項目14)

変換ユニットに対する係数に対するサインデータをエンコードすることにより、ビデオ のビットストリームをエンコードするためのエンコーダであって、

該エンコーダは、

プロセッサと、

メモリと、

メモリ内に格納され、かつ上記項目のいずれか一項に記載の方法を実行するように前記 プロセッサを構成するための命令を含むエンコーディングアプリケーションと

を含む、エンコーダ。

10

20

30

50

## (項目15)

プロセッサ実行可能な命令を格納している持続性のプロセッサ読み取り可能な媒体であ って、該命令は、実行されたときに、上記項目のいずれか一項における方法を実行するよ うに1つ以上のプロセッサを構成する、プロセッサ読み取り可能な媒体。

## [0015]

(摘要)

ビデオデータをエンコードおよびデコードするための方法が、変換ユニットに対するエ ンコーディング係数またはデコーディング係数に対して記載される。特に、非ゼロ係数に 対するサインビットは、サインビット秘匿を用いてエンコードされる。係数の2つ以上の セットが、変換ユニットに対して定義され、サインビットは、各セットに対して秘匿され 得、閾値テストを満たす対象となる。セットは、別様にマルチレベル有意マップエンコー ディングおよびデコーディングにおいて用いられる係数グループに対応し得る。

【図面の簡単な説明】

[0016]

ここで、例として、本願の例示的な実施形態を示す添付図面に対する参照がなされ得る

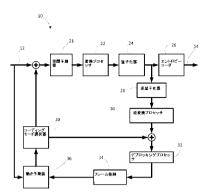

【図1】図1は、ブロック図形式において、ビデオをエンコードするためのエンコーダを 示している。

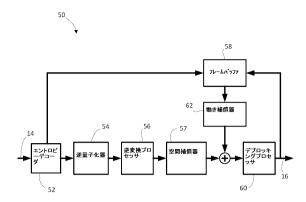

【図2】図2は、ブロック図形式において、ビデオをデコードするためのデコーダを示し ている。

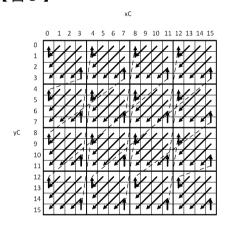

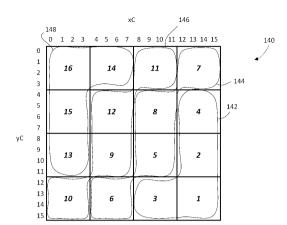

【図3】図3は、16×16変換ユニットに対するマルチレベルスキャン順序の例を示し

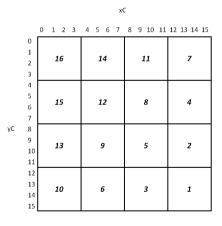

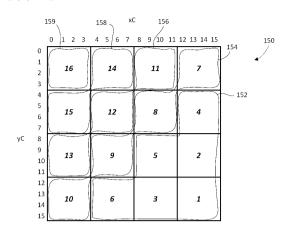

【図4】図4は、逆グループレベルスキャン順序において番号付けされた係数グループへ と区画化される例示的な16×16変換ユニットを示している。

【図5】図5は、係数グループのうちの4つのグループがサインビット秘匿のために形成 される変換ユニットの1つの例を示している。

【図6】図6は、サインビット秘匿のための係数グループのグルーピングの別の例を例示 している。

【図7】図7は、サインビット秘匿のための係数グループのグルーピングのなおも別の例 を示している。

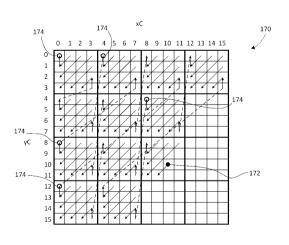

【図8】図8は、サインビット秘匿のために係数のセットを動的に形成する例を例示して いる。

【図9】図9は、フローチャート形式において、サインビット秘匿のための例示的なプロ セスを示している。

【図10】図10は、エンコーダの例示的な実施形態の簡略化されたブロック図を示して

【図11】図11は、デコーダの例示的な実施形態の簡略化されたブロック図を示してい る。

[0017]

異なる図面において用いられ得る類似した参照番号は、類似した構成要素を示している

【発明を実施するための形態】

[0018]

(例示的な実施形態の記載)

以下の記載においては、ビデオコーディングのためのH.264規格および/または開 発中のMPEG-H規格に関連して、いくつかの実施形態が記載されている。当業者であ れば、本願は、H.264/AVC規格および/またはMPEG-Hに限定されず、可能 性のある将来の規格、マルチビューコーディング規格、スケーラブルビデオコーディング 規格、および再構成可能ビデオコーディング規格を含む、その他のビデオコーディング/ デコーディング規格に対して適用可能であり得ることを理解し得る。

10

20

30

40

10

20

30

40

50

## [0019]

以下の記載において、ビデオまたはイメージに言及するとき、フレーム、ピクチャ、ス ライス、タイル、および矩形スライスグループという用語は、いくぶん互換的に用いられ 得る。当業者であれば、H.264規格の場合において、フレームは、1つ以上のスライ スを含み得ることを理解し得る。また、適用可能なイメージまたはビデオコーディング規 格の特定の要件または術語に依存して、特定のエンコーディング/デコーディングオペレ ーションが、フレームごとに実行されること、いくつかがスライスごとに実行されること 、いくつかがピクチャごとに実行されること、いくつかがタイルごとに実行されること、 およびいくつかが矩形スライスグループによることも、理解され得る。任意の特定の実施 形態において、適用可能なイメージまたはビデオコーディング規格は、以下に記載される オペレーションが、場合によって、フレームおよび/またはスライスおよび/またはピク チャおよび/またはタイルおよび/または矩形スライスグループに関連して実行されるか どうかを決定し得る。したがって、当業者であれば、本開示に照らして、本明細書中に記 載されている特定のオペレーションまたはプロセス、ならびにフレーム、スライス、ピク チャ、タイル、矩形スライスグループに対する特定の言及が、所与の実施形態に対して、 フレーム、スライス、ピクチャ、タイル、矩形スライスグループ、またはこれらのうちの いくつかまたはすべてに対して適用可能であるかどうかを理解し得る。また、これは、以 下の記載に照らして明らかになり得るように、変換ユニット、コーディングユニット、コ ーディングユニットのグループ等に対しても当てはまる。

# [0020]

本願は、変換ユニットの非ゼロ係数に対してサインビットをエンコードおよびデコードするための例示的プロセスおよびデバイスを記載している。非ゼロ係数は、有意マップによって識別される。有意マップは、変換ユニットまたは係数の定義されたユニット(例えば、いくつかの変換ユニット、変換ユニットの一部分、またはコーディングユニットにマップする、または該変換ユニットまたは係数の定義されたユニットに対応する、フラグは、変換ユニットまたは係数の定義されたユニットに対応する、でのブロック、行列、グループまたはセットである。各フラグは、変換ユニットまたは行ってあるがどうかを示す。既存の規格においては、これらのフラグは、有意係数フラグと称され得る。既存の規格においてはよいでは、これらのフラグは、有意係数フラグと称され得る。既存の規格においてはまたは順序において、DC係数から最終有意係数まで、係数ごとに1つのフラグが存在するには、対応する係数がゼロである場合には、ゼロであるビットであり、対応する係数がゼロである場合には、ゼロであるビットであり、対応する意数が非ゼロである場合には、1に設定される。本明細書中で用いられる際の用語「有意でップ」は、以下の記載から理解され得るような、変換ユニットに対する有意係数フラグの行列または順序付けられたセット、あるいは本願のコンテキストから明確であり得る、係数の定義されたユニットを意味することが意図されている。

# [0021]

以下の記載に照らして、マルチレベルエンコーディングおよびデコーディング構造が、特定の状況に対して適用可能であり得、これらの状況が、ビデオコンテンツタイプ等のサイド情報(シーケンス、ピクチャ、またはスライスへッダ内で識別されるような自然なビデオまたはグラフィクス)から決定され得ることが、理解され得る。例えば、2つのレベルが自然なビデオに対して用いられ得、3つのレベルがグラフィクスに対して用いられ得る(これは、典型的には、遥かに希少である)。さらに別の可能性は、シーケンス、ピクチャ、またはスライスへッダのうちの1つにおいてフラグを提供して、構造が1つ、2つ、または3つのレベルを有しているかどうかを示し、これにより、エンコーダに、現在のコンテンツに対する最も適切な構造を選択するフレキシビリティを可能にすることである。別の実施形態においては、フラグは、コンテンツタイプを表し得、これは、レベルの数に関連付けられ得る。例えば、コンテンツタイプ「グラフィック」は、3つのレベルを特徴とし得る。

# [0022]

ここで図1に対する参照がなされ、該図面は、ブロック図形式において、ビデオをエンコードするためのエンコーダ10を示している。また、図2に対する参照もなされ、該図

面は、ビデオをデコードするためのデコーダ 5 0 のブロック図を示している。本明細書中に記載されているエンコーダ 1 0 およびデコーダ 5 0 が、それぞれ、 1 つ以上の処理要素およびメモリを含む、特定用途向けまたは汎用コンピューティングデバイス上に実装され得ることが理解され得る。エンコーダ 1 0 またはデコーダ 5 0 によって実行されるオペレーションは、場合によって、例えば、特定用途向け集積回路によって実装され得るか、あるいは汎用プロセッサによって実行可能な格納されたプログラム命令によって実装され得る。デバイスは、例えば、基本デバイス機能を制御するためのオペレーティングシステムを含む、付加的ソフトウェアを含み得る。その内部でエンコーダ 1 0 またはデコーダ 5 0 が実装され得るデバイスまたはプラットフォームの範囲は、以下の記載に接した当業者によって理解され得る。

[0023]

エンコーダ10は、ビデオソース12を受信し、かつエンコードされたビットストリーム14を生成する。デコーダ50は、エンコードされたビットストリーム14を受信し、かつデコードされたビデオフレーム16を出力する。エンコーダ10およびデコーダ50は、多くのビデオ圧縮規格に準拠して動作するように構成され得る。例えば、エンコーダ10およびデコーダ50は、H.264/AVC準拠であり得る。その他の実施形態においては、デコーダ10およびエンコーダ50は、MPEG・H等のH.264/AVCの規格の進化型を含む、その他のビデオ圧縮規格に準拠し得る。

[0024]

エンコーダ10は、空間予測器21、コーディングモード選択器20、変換プロセッサ 2 2 、量子化器 2 4 、およびエントロピーエンコーダ 2 6 を含む。当業者によって理解さ れ得るように、コーディングモード選択器20は、例えば、対象フレーム/スライスがI タイプ、PタイプまたはOタイプであるかどうか、ならびにフレーム/スライス内の特定 のコーディングユニット(例えば、マクロブロック、コーディングユニット等)が、イン ターコードまたはイントラコードされるかどうか等、ビデオソースに対する適切なコーデ ィングモードを決定する。変換プロセッサ22は、空間ドメインデータに基づいて、変換 を実行する。特に、変換プロセッサ22は、ブロックベースの変換を適用して、空間ドメ インデータを空間成分に変換する。例えば、多くの実施形態においては、離散コサイン変 換(DCT)が用いられる。例えば離散サイン変換等のその他の変換が、いくつかの場合 においては、用いられ得る。ブロックベースの変換は、コーディングユニット上で、マク ロブロックまたはサブブロックベースで、マクロブロックまたはコーディングユニットの サイズに依存して、実行される。H.264規格においては、例えば、典型的な16x1 6 マクロブロックは、 1 6 個の 4 × 4 変換ブロックを含み、 D C T プロセスが該 4 × 4 ブ ロックに対して実行される。いくつかの場合においては、変換プロックは、8×8であり 得、これは、マクロブロックごとに4つの変換ブロックが存在することを意味している。 なおも他の場合においては、変換ブロックは、その他のサイズであり得る。いくつかの場 合においては、16×16マクロブロックは、4×4および8×8マクロブロックの非重 複組み合わせを含み得る。

[0025]

ブロックベースの変換をピクセルデータのブロックに適用することは、変換ドメイン係数のセットをもたらす。このコンテキストにおける「セット」とは、係数が係数位置を有する順序付けられたセットのことである。いくつかの場合においては、変換ドメイン係数のセットは、係数の「ブロック」または行列として考慮され得る。本明細書中の記載において、フレーズ「変換ドメイン係数のセット」または「変換ドメイン係数のブロック」は、互換的に用いられており、かつ変換ドメイン係数の順序付けられたセットを示すことが意図されている。

[0026]

変換ドメイン係数のセットは、量子化器 2 4 によって量子化される。量子化された係数 および関連付けられた情報は、その後、エントロピーエンコーダ 2 6 によってエンコード される。 10

20

30

40

## [0027]

量子化された変換ドメイン係数のブロックまたは行列は、本明細書中では、「変換ユニット」(TU)と称され得る。いくつかの場合においては、TUは、非正方であり得、例えば、non-squre quadrature transform(NSQT)であり得る。

## [0028]

イントラコードされたフレーム / スライス(すなわち、タイプI)は、その他のフレーム / スライスを参照せずに、エンコードされる。換言すると、これらは、時間的予測を採用していない。しかしながら、イントラコードされたフレームは、空間予測器21によって図1内に例示されているような、フレーム / スライス内の空間予測に依拠していない。すなわち、特定のブロックをエンコードするときに、ブロック内のデータは、そのフレーム / スライスに対して既にエンコードされているブロック内の近隣のピクセルのデータと比較され得る。予測アルゴリズムを用いることにより、ブロックのソースデータは、残余データに変換され得る。変換プロセッサ22は、その後、残余データをエンコードする。例えば、H.264は、4×4変換ブロックに対して9つの空間予測モードを記述する。いくつかの実施形態においては、9つのモードのそれぞれは、ブロックを独立的に処理するために用いられ得、レート歪み最適化が、その後、最良モードを選択するために用いられる。

# [0029]

また、H.264規格は、時間予測を活用するために、動き予測/補償の使用を記述し ている。したがって、エンコーダ10は、逆量子化器28、逆変換プロセッサ30、およ びデブロッキングプロセッサ32を含むフィードバックループを有する。デブロッキング プロセッサ32は、デブロッキングプロセッサおよびフィルタリングプロセッサを含み得 る。これらの要素は、フレーム/スライスを再生するために、デコーダ50によって実装 されるデコーディングプロセスを反映している。フレーム格納34が、再生されたフレー ムを格納するために用いられる。このように、動き予測は、何がデコーダ50において再 構成されるフレームであり得るかに基づいており、エンコーディング/デコーディング内 に含まれる損失性のある圧縮に起因して再構成されたフレームとは異なり得るオリジナル フレームに基づいてはいない。動き予測器36は、類似したブロックを識別するという目 的のために、現在のフレームに対する比較のためのソースフレーム/スライスとして、フ レーム格納34に格納されるフレーム/スライスを用いる。したがって、それに対して動 き予測が適用されるマクロブロックまたはコーディングユニットに対して、変換プロセッ サ22がエンコードする「ソースデータ」は、動き予測プロセスに由来する残余データで ある。例えば、これは、基準フレーム、空間変位または「動きベクトル」、および基準ブ ロックと現在のブロックとの間の(もしあれば)相違を表す残余ピクセルデータに関する 情報を含み得る。基準フレームおよび/または動きベクトルに関する情報は、変換プロセ ッサ22および/または量子化器24によって処理されないことがあり得るが、その代り に、量子化された係数とともに、ビットストリームの一部分としてエンコードするために 、エントロピーエンコーダ26に供給され得る。

## [0030]

当業者であれば、ビデオエンコーダを実装するための詳細および可能性のある変形を理解し得る。

# [0031]

デコーダ 5 0 は、エントロピーデコーダ 5 2 、逆量子化器 5 4 、逆変換プロセッサ 5 6 、空間補償器 5 7 、およびデブロッキングプロセッサ 6 0 を含む。デブロッキングプロセッサ 6 0 は、デブロッキングおよびフィルタリングプロセッサを含み得る。フレームバッファ 5 8 は、動き補償を適用する際における、動き補償器 6 2 による使用のために、再構成されたフレームを供給する。空間補償器 5 7 は、既にデコードされたブロックから特定のイントラコードされたブロックに対するビデオデータを復元するオペレーションを表す

10

20

30

10

20

30

40

50

## [0032]

ビットストリーム14は、エントロピーデコーダ52によって受信され、かつデコードされて、量子化された係数を復元する。また、サイド情報が、エントロピーデコーディングプロセスの間に復元され得、そのうちの一部は、(もしあれば)動き補償における使用のために、動き補償ループに供給され得る。例えば、エントロピーデコーダ52は、イントラコードされたマクロブロックに対して、動きベクトルおよび/または基準フレーム情報を復元し得る。

# [0033]

量子化された係数は、その後、逆量子化器 5 4 によって逆量子化されて、変換ドメイン係数を生成し、該係数は、その後、逆変換プロセッサ 5 6 による逆変換の対象となり、「ビデオデータ」を再形成する。理解され得るように、例えばイントラコードされたマクロブロックまたはコーディングユニットの場合等のいくつかの場合においては、再形成された「ビデオデータ」は、フレーム内の既にデコードされたブロックに対する空間補償における使用のための残余データである。空間補償器 5 7 は、既にデコードされたブロックからの残余データおよびピクセルデータからビデオデータを生成する。例えばイントラコードされたマクロブロックまたはコーディングユニット等のその他の場合においては、逆変力であるの再形成された「ビデオデータ」は、異なるフレームからの基準ブロックに対する動き補償における使用のための残余データデある。空間補償および動き補償の両方は、本明細書中では、「予測オペレーション」として称され得る。

# [0034]

動き補償器62は、特定のインターコードされたマクロブロックまたはコーディングユニットに対して特定されたフレームバッファ58内に基準ブロックを配置する。該補償器は、インターコードされたマクロブロックまたはコーディングユニットに対して特定された基準フレーム情報および動きベクトルに基づいて、これを行う。該補償器は、その後、残余データとの組み合わせのために、基準ブロックピクセルデータを供給して、コーディングユニット / マクロブロックに対する再構成されたビデオデータに到達する。

## [0035]

デブロッキングプロセッサ60によって示されているように、ブロッキング/フィルタリングプロセスが、その後、再構成されたフレーム/スライスに対して適用され得る。デブロッキング/フィルタリングの後、フレーム/スライスは、例えば、ディスプレイデバイス上の表示のために、デコードされたビデオフレーム16として出力される。例えばコンピュータ、セットトップボックス、DVDまたはブルーレイプレーヤー、および/またはモバイルハンドヘルドデバイス等のビデオ再生機は、出力デバイス上の表示の前にメモリ内にデコードされたフレームをバッファし得るということが理解され得る。

## [0036]

MPEG-H準拠エンコーダおよびデコーダは、これらと同じまたは類似した特徴の多くを有し得ることが期待されている。

## [0037]

(量子化された変換ドメイン係数のエンコーディングおよびデコーディング)

上述したように、量子化された変換ドメイン係数のブロックまたはセットのエントロピーコーディングは、量子化された変換ドメイン係数のブロックまたはセットに対する有意マップ(例えば、有意係数フラグのセット)をエンコードすることを含む。有意マップは、どの位置(DC位置から最終有意係数位置まで)に非ゼロ係数が現れるかを示すブロックのバイナリマッピングである。有意マップは、スキャン順序(該順序は、適用可能なコーディング規格によって記述されている垂直、水平、対角線、ジグザグ、またはその他の任意の順序であり得る)にしたがって、ベクトルに変換され得る。スキャンは、典型的には、「逆」順序で行われ、すなわち、最終有意係数から出発し、[0,0]における左上コーナーにおける有意係数フラグに到達するまで、逆方向に、有意マップを通って、逆行して機能する。本記載においては、用語「スキャン順序」は、(場合によって)フラグ、係数、またはグループが処理される順序を意味することが意図されており、口語的に「逆

10

20

30

40

50

スキャン順序」として称される順序を含み得る。

## [0038]

各有意係数フラグは、その後、適用可能なコンテキスト適応コーディングスキームを用いてエントロピーエンコードされる。例えば、多くの用途においては、context‐adaptive binary arithmetic coding(CABAC)スキームが用いられ得る。

### [0039]

$1.6 \times 1.6$  および  $3.2 \times 3.2$  有意マップの場合、有意係数フラグに対するコンテキストは、隣接する有意係数フラグ値に(ほとんどの場合には)基づいている。  $1.6 \times 1.6$  および  $3.2 \times 3.2$  有意マップに対して用いられるコンテキストの中で, [.0] 、0.1 におけるビット位置に対して専用である、そして(いくつかの例示的な実装においては)隣接するビット位置に対して専用である、特定のコンテキストが存在するが、有意係数フラグのうちのほとんどは、隣接する有意係数フラグの累積値に依存する 4 つまたは 5 つのコンテキストのうちの 1 つをとる。これらの場合においては、有意係数フラグに対する正確なコンテキストの決定は、隣接する位置(典型的には 5 つの位置であるが、いくつかの場合においては、より多くまたはより少ないことがあり得る)における有意係数フラグの値を決定し、かつ合計することに依存している。

# [0040]

これらの非ゼロ係数に対する有意係数レベルは、その後に、エンコードされ得る。1つの例示的な実装においては、レベルは、1よりも大きい絶対値を有するこれらの非ゼロ係数のマップを最初にエンコーディングすることにより、エンコードされ得る。別のマップは、その後に、2よりも大きいレベルを有するこれらの非ゼロ係数のエンコードされたものであり得る。2よりも大きい絶対値を有する係数のうちのいずれかの値またはレベルは、その後に、エンコードされる。いくつかの場合においては、エンコードされた値は、実際の値マイナス3であり得る。

## [0041]

非ゼロ係数のサインもまた、エンコードされる。各非ゼロ係数は、非ゼロ係数のレベルが負または正であるかどうかを示すサインビットを有している。変換ユニット内の第1係数に対するサインビットを秘匿するための提案がなされてきた(C1are,Gordon,et al.,"Sign Data Hiding",JCTVC-G271,7<sup>t h</sup> Meeting,Geneva,21-30 November,2011)。この提案のもとで、変換ユニット内の第1係数のサインは、変換ユニット内の量子化された係数の和のパリティを用いてエンコードされる。パリティが第1係数の実際のサインに対応しない場合には、エンコーダは、パリティを調整するために、係数のうちの1つのレベルを1だけ上下するように調整する必要がある。どの係数をどの方向に調整するかを決定するために、RDOOが用いられるべきである。

# [0042]

いくつかの以前の仕事は、マルチレベル有意マップを用いることに焦点を当てていた。ここで図3に対する参照がなされ、該図面は、例示されているマルチレベル対角線スキャン順序を用いる16×16変換ユニット100を示している。変換ユニット100は、16個の連続4×4係数グループまたは「有意係数フラグのセット」へと区画化される。各係数グループ内では、変換ユニット100の全体にわたってではなく、対角線スキャン順序が該グループ内に適用される。セットまたは係数グループ自体は、スキャン順序において処理され、該順序もまた、この例示的な実装においては、対角線スキャン順序である。この例におけるスキャン順序は、「逆」スキャン順序において例示されているということに留意されたい。いくつかの実においては、同じスキャン順序が、その他の方向において定義され得、すなわち、エンコーディングの間に適用されるときに、右上向き対角線方向に進行し、あるいはデコーディングが「逆」スキャン順序において適用され得る。

## [0043]

マルチレベル有意マップの使用は、どの係数グループが非ゼロ有意係数フラグを含むと期待され得、かつどの係数グループがすべてのゼロ有意係数フラグを含むかを示す、L1またはより高レベルの有意マップのエンコーディングを含む。非ゼロ有意係数フラグを含むことが期待され得る係数グループは、それらの有意係数フラグをエンコードさせるが、その一方ですべてのゼロ有意係数フラグを含む係数グループは、(それらが少なくとも1つの非ゼロ有意係数フラグを含むと想定されることによる特別な場合の例外を理由としてエンコードされるグループであるときを除いて)エンコードされない。各係数グループは、(例えば最終有意係数を含むグループ、左上グループ等の、係数グループが想定値のフラグを有する特別な場合に該当するときを除いて)有意係数グループフラグを有する。

[0044]

マルチレベル有意マップの使用は、エンコーディングおよびデコーディングのための残余データのモジュール式処理を容易にする。

## [0045]

より大きいTUは、複数サインビットを秘匿する機会を提示する。TUは、非ゼロ係数のセットへと分割または区画化され得、サインビットは、当該セット内の非ゼロ係数の和のパリティを用いて、非ゼロ係数の各セットに対して秘匿され得る。一実施形態において、非ゼロ係数のセットは、マルチレベル有意マップに対して定義された係数グループに対応させられ得る。

[0046]

単一の閾値が、データタイプに関わらず、非ゼロ係数の特定のセットに対してサインビットを秘匿するかどうかを決定するために用いられ得る。一例においては、閾値テストは、セット内の第1非ゼロ係数と最終非ゼロ係数との間の係数の数に基づいている。すなわち、セット内の第1非ゼロ係数と最終非ゼロ係数との間に、少なくとも閾値数の係数が存在するかどうかに基づいている。別の例においては、テストは、セット内に少なくとも閾値数の非ゼロ係数が存在していることに基づき得る。なおも別の実施形態においては、テストは、閾値を超えるセット内の非ゼロ係数の絶対値の和に基づき得る。なおもさらなる実施形態においては、これらのテストの組み合わせが、適用され得る。すなわち、セット内には少なくとも最小数の係数が存在するはずであり、係数の累積絶対値は、閾値を超える必要がある。これらの閾値テストに対する変形もまた、採用され得る。

[0047]

ここで図 4 に対する参照がなされ、該図面は、例示的な 1 6  $\times$  1 6 変換ユニット 1 2 0 を示している。変換ユニット 1 2 0 は、 4  $\times$  4 係数グループに分割される、すなわち、係数の 1 6 個のセットに分割される。係数グループは、例えば逆対角スキャン順序等の、それらが処理される順序において、 1 , 2 , 3 , … 1 6 に番号付けされる。

[0048]

第1実施形態において、各係数グループは、サインビット秘匿という目的のための係数のセットである。すなわち、各係数グループは、係数グループがサインビット秘匿のために適切であるかどうかを決定するために、閾値に対してテストされる。上述したように、テストは、係数グループが、当該係数グループ内の第1非ゼロ係数と最終非ゼロ係数との間に少なくとも最小数の係数を含んでいるかどうかというものであり得る。

[0049]

第2実施形態においては、サインビット秘匿のための係数のセットは、係数グループをグルーピングすることによって形成される。図5は、16×16 TU140を示しており、該図面においては、係数の4つのセットへの係数グループの例示的なグルーピングが例示されている。この例においては、サインビット秘匿という目的のための係数の各セットは、4つの係数グループを含む。各セットにおける4つの係数グループは、スキャン順序における連続グループである。例えば、係数の第1セット142は、係数グループ16、15、14、および13を含む。係数の第2セット144は、係数グループ12、11、10、および9を含む。係数の第3セット146は、係数グループ8、7、6、および

10

20

30

40

10

20

30

40

50

5 を含む。最後に、係数の第 4 セット 1 4 8 は、係数グループ 4 、 3 、 2 、および 1 を含む。この実施形態においては、サインビットは、係数の各セットに対して秘匿され得る。 すなわち、 4 までのサインビットが、 T U 1 4 0 ごとに秘匿され得る。

## [0050]

係数の各セット142、144、146、148に対して、第1非ゼロ係数と最終非ゼロ係数との間の係数の数(または非ゼロ係数の数、またはこれらの係数の累積合計値)は、当該セットに対してサインビットを秘匿するかどうかを決定するために、閾値に対してテストされる。セット内のこれらの係数の絶対値の和のパリティは、それを介してサインビットが秘匿される機構である。パリティが秘匿されるべきサインに対応しない場合には、パリティは、セット内の係数のうちの1つのレベルを調整することによって、調整される。

## [0051]

図6は、16×16 TU150の場合のサインビット秘匿のための係数のセットの第3実施形態を例示している。この実施形態においては、セットは、再度、係数グループを含むわけではない。例えば、この例示においては、係数の5つのセットが定義されている。第1セット152は、係数グループ1~6を含む。第2セット154は、4つの係数グループ7、8、9、および10を含む。第3セット156は、係数グループ11、12、および13を含む。第4セット158は、係数グループ14および15を含む。第5セット159は、左上係数グループ16だけを含む。この実施形態は、それに対してより少ない非ゼロ係数が存在する可能性のある変換ユニット150の領域内に係数のより小さなセットを提供することが、理解され得る。上述した実施形態は、32×32またはより大きなTUサイズならびに8×8TUサイズに対しても当てはまり得、係数グループ構造が、これらのTUに対して適用されるということに留意されたい。

# [0052]

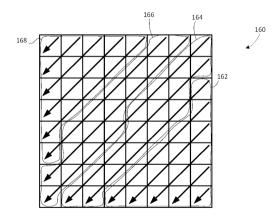

図7は、第4実施形態を例示しており、該図面においては、 $8\times8$ 変換ユニット 160 内のサインビット秘匿のための係数のセットが、係数グループ構造に固着することなく形成される。 $8\times8$  変換ユニットは、有意マップエンコーディングの目的のための係数グループ区画化を有し得ることも、有しないこともあり得る。いずれの場合においても、この実施形態においては、変換ユニットベースの対角線スキャンが、サインビットのエンコーディングおよび秘匿のために係数を処理するために用いられる。この場合においては、係数のセットは、スキャン順序において、連続係数をグルーピングするために形成される。例えば、この例示においては、変換ユニット 1600 は、係数の 400 のセットにグルーピングされ、各セットは、スキャニング順序において、1600 は、係数を含んでいる。グループは、図7においては、1621 に 1641 1 1661 に 1681 に 168

# [0053]

なおも別の実施形態においては、係数のセットは、スキャン順序に固着しないものであり得る。すなわち、各セットは、変換ユニット内のより高い頻度位置からのいくつかの係数と、変換ユニット内のより低い頻度位置からのいくつかの係数とを含み得る。これらのセット内の全ての係数は、必ずしも、スキャン順序において隣接してはいないことがあり得る。

## [0054]

図8は、第5実施形態を示しており、該図面においては、16×16変換ユニット170内のサインビット秘匿のための係数のセットが、係数グループ構造およびスキャン順序を用いて、動的に形成される。この実施形態においては、係数の固定されたセットが変換ユニットサイズおよびスキャン順序に基づいて予め定義されているというよりもむしろ、スキャン順序をたどり、かつ閾値が満たされるまで閾値に対して何らかの量が測定されて

いるかどうかを追跡することにより、エンコーダおよびデコーダが、セットを形成する。 いったん閾値が満たされると、その後にエンコーダまたはデコーダが処理する係数グルー プに対して、サインビットが秘匿される。

## [0055]

例えば、図8は、係数グループ[2,2]内の最終有意係数を例示している。スキャン順序において、エンコーダおよびデコーダは、その後に、係数グループ[1,3],[3,0],および[2,1]へと順に移る。係数グループ[2,1]における係数を処理している間に、閾値が満たされる。したがって、係数グループ[2,1]において逆スキャン順序において処理されるべき最終非ゼロ係数に対するサインビット(グループ内の最も左上の非ゼロ係数)は、最終有意係数から、現在の係数グループ[2,1]におけるすべての係数までの、そして該現在の係数グループ[2,1]におけるすべての係数を含む、係数の累積絶対値のパリティ内に秘匿される。この例における閾値テストは、最小数の非ゼロ係数が存在すること、または係数の絶対値がなんらかの閾値を超えることに基づき得る。参照番号174は、特定の係数グループにおける「最終」または最も左上の係数に対するサインビット秘匿オペレーションを示している。

### [0056]

第6実施形態において、サインビット秘匿は、係数グループに基づいて行われ、係数グループがサインビット秘匿のために適切であるかどうかを決定するために用いられる基準は、既にデコードされた係数グループにしたがって動的に調整される。例として、そのすぐ右の係数グループまたはそのすぐ下の係数グループのいずれかが非ゼロ係数を有している場合には、現在の係数グループは、それが2つの非ゼロ係数の最小値を含んでいる限り、サインビット秘匿のために適切であると決定される。また、上述した実施形態のうちのいくつかにおいて記載されているように、係数グループは、それが、当該係数グループ内の第1非ゼロ係数と最終非ゼロ係数との間に少なくとも最小数の係数を含んでいる場合には、適切であると決定され得る。

## [0057]

上述した実施形態のうちのいくつかにおいて理解され得るように、サインビットは、別の係数グループにおける係数に依存するパリティ値に基づいて、1つの係数グループ内に秘匿され得る。換言すると、1つの係数グループ内の係数のサイン値は、別の係数グループにおける係数へのレベル変化により、パリティ内に秘匿され得る。

## [0058]

さらに、上述した実施形態のうちのいくつかにおいて理解され得るように、係数のセット内に秘匿されたサインビットは、動きベクトル相違フラグ(例えば、mvd\_sign \_\_flg)等の異なるシンタックス要素からのものであり得る。

# [0059]

エンコーダ側においては、パリティ値がサインに対応しない場合において、サインビットを秘匿するために、どの係数を調整するかに関する決定がなされる。パリティ値が調整される必要がある場合には、パリティを変化させるために、係数レベルが、1だけ増加または減少される必要がある。

## [0060]

一実施形態においては、係数レベルを調整するためのプロセスにおける第1ステップは、検索範囲を決定すること、すなわちスキャン順序における開始位置および終了位置を決定することである。この範囲内の係数は、その後に評価され、1つのものが、変化させられるように選択される。1つの例示的な実施形態においては、検索範囲は、スキャニング順序における、第1非ゼロ係数から最終係数までであり得る。

# [0061]

マルチレベル有意マップの使用により、サブセットに対する検索範囲に対する終了位置は、ブロックレベル情報を利用するために、変化させられ得る。特に、1つのサブセットが、全体のTU内のまさに最終の非ゼロ係数を含んでいる場合(大域的最終または最終有意係数と称される)には、検索範囲は、第1非ゼロ係数から最終非ゼロ係数までとして確

10

20

30

40

立され得る。その他のサブセットに対しては、検索範囲は、第 1 非ゼロ係数から現在のサブブロックの終了までの範囲に拡張され得る。

## [0062]

一実施形態において、開始位置は、第1非ゼロ量子化係数よりも前の非量子化係数を条件的に含むように拡張され得る。特に、量子化の前のすべての係数を考慮する。秘匿されるべきサインと同じサインを有する非量子化係数は、検索内に含まれ得る。位置ゼロから第1非ゼロ量子化係数の位置までの非量子化係数に対して、量子化係数をゼロから1に変化させるコストが、検索において評価され、テストされ得る。

## [0063]

係数レベルを調整するためのプロセスにおける別の問題は、調整の影響を評価するために用いられるコスト計算を定義することである。計算複雑性が問題となる場合には、コストは、歪みに基づき得、レートは考慮に入れられないことがあり得、この場合においては、検索は、歪みを最小化するものである。一方で、計算複雑性が優先的な問題ではない場合には、コストは、レート歪みコストを最小化するために、レートおよび歪みの両方を含み得る。

## [0064]

RDOQが有効化された場合には、RDOQは、レベルを調整するために用いられ得る。しかしながら、多くの場合においては、RDOQの計算複雑性は、望ましくないことがあり得、RDOQは、有効化されないことがあり得る。したがって、いくつかの実施形態においては、サインビット秘匿を実装するために、簡略化されたレート歪み解析が、エンコーダにおいて適用され得る。

#### [0065]

セット内の第1非ゼロ係数とセット内の最終非ゼロ係数との間の各係数は、係数を1だけ増大させることから、そして係数を1だけ減少させることから、歪みを大雑把に計算することによってテストされ得る。一般的にいうと、uの係数値は、u+ の実際値を有する。歪みは、( q)  $^2$  によって与えられる。この係数uが1だけ増加してu+1に調整された場合には、結果としての歪みは、

$q^{2}(1-2)$

と推定され得る。

# [0066]

係数 u が 1 だけ減少して u ・ 1 に調整された場合には、結果としての歪みは、

$q^{2}(1+2)$

と推定され得る。

# [0067]

インターコードされた場合に対して、量子化歪み は、RDOQがオフの場合には、[-1/6から+5/6]の範囲に存在すると認識され得る。イントラコードされたブロックの場合には、量子化歪み は、RDOQがオフの場合には、[-1/3から+2/3]の範囲に存在する。RDOQがオンの場合には、 の範囲は、変動し得る。しかしながら、歪み増加の上述した計算は、 の範囲に関わらず、依然として有効である。

## [0068]

また、エンコーダは、論理規則のセット、すなわち予め定義されたレートコストメトリックを用いて、様々な係数に対するレートコストに関する大雑把な評価を行い得る。例えは、予め定義されたレートコストメトリックは、一実施形態においては、

# [0069]

20

10

30

10

20

30

40

50

# 【化1】

*u*+1 (*u*≠0 かつ *u*≠-1) → 0.5ビット

*u*-1 (*u*≠0 かつ *u*≠+1) → -0.5ビット

u = 1または -1 かつ 0 に変化  $\rightarrow$  -1-0.5-0.5ビット

*u*=0 かつ 1または -1に変化 → 1+0.5+0.5ビット

### を含み得る。

ここで、サインフラグのコストは、1 ビットとして推定され、有意係数フラグのコストは、0.5 ビットとして推定され、u から u + 1 までのコスト増加は、0.5 ビットとして推定される。

#### [0070]

その他の規則または推定が、その他の実施形態において用いられ得る。

### [0071]

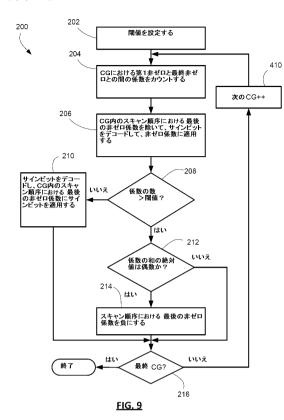

ここで図9に対する参照がなされ、該図面は、係数グループベースのサインビット秘匿を用いてビデオデータをデコードするための例示的なプロセス200を示している。プロセス200は、上述した第2実施形態に基づいている。本記載を読んだ後には、記載されているその他の実施形態を実行するためのプロセス200に対する代替および改変が、当業者によって認識され得る。

## [0072]

閾値が、オペレーション202において設定される。いくつかの実施形態においては、この閾値は、デコーダ内で予め定義され得るか、または予め構成され得る。その他の実施 形態においては、この値は、エンコードされたビデオデータのビットストリームから抽出 され得る。例えば、閾値は、ピクチャヘッダにおいて、またはビットストリーム内の別の 位置において存在し得る。

## [0073]

オペレーション 2 0 4 において、デコーダは、スキャン順序において、現在の係数グループ内の、すなわち係数のセット内の第 1 非ゼロ位置を識別し、そして現在の係数グループ内の最終非ゼロ位置を識別する。その後これは、係数グループ内の第 1 非ゼロ係数と最終非ゼロ係数との間において、スキャン順序において、係数の数を決定する。

# [0074]

オペレーション206において、デコーダは、ビットストリームからサインビットをデコードする。デコーダは、係数グループ内の最も左上の非ゼロ係数(逆スキャン順序における最終非ゼロ係数)を除いて、係数グループ内のすべての非ゼロ係数に対して、サインビットをデコードする。サインビットは、これらのそれぞれの非ゼロ係数に対して適用される。例えば、適用可能な規約が、ゼロのサインビットが正であり、かつ、1のサインビットが負であるというものである場合には、1に設定されたすべてのサインビットに対して、対応する係数レベルは、負にされる。

## [0075]

オペレーション208において、デコーダは、係数グループ内のスキャン順序における第1非ゼロ係数と最終非ゼロ係数との間の係数の数が、閾値を超えているかどうかを評価する。超えていない場合には、エンコーダにおいてサインビット秘匿は用いられないので、オペレーション210において、デコーダは、最も左上の非ゼロ係数(逆スキャン順序における最後)に対するサインビットをデコードし、かつそれを係数レベルに適用する。係数の数が閾値を満たさない場合には、オペレーション212において、デコーダは、係数グループ内の係数の和の絶対値が、偶数または奇数であるかどうか、すなわちそのパリティを見積もる。偶数である場合には、最も左上の非ゼロ係数のサインは、正であり、デコーダは、それを調整する必要はない。奇数の場合には、最も左上の非ゼロ係数のサインは、負であり、それゆえ、オペレーション214において、デコーダは、当該係数を負に

する。

## [0076]

オペレーション 2 1 6 においては、デコーダは、係数グループを処理することが終了したかどうかを決定する。終了したと決定した場合には、プロセス 2 0 0 は終了する。そうでない場合には、デコーダは、オペレーション 2 1 8 において、グループスキャン順序において次の係数グループに移り、オペレーション 2 0 4 に戻る。

#### [0077]

その他の実施形態においては、係数のセットのサイズは、単一の係数まで低減され得る。すなわち、サインビット秘匿は、単一係数ベースのサイン秘匿であり得る。この実施形態においては、各係数は、それのサイン情報が秘匿されているかどうかを見るためにテストされる。1つの例示的なテストは、係数レベルの大きさと所与の閾値とを比較することである。閾値よりも大きいレベルを有する係数は、それらのサインビットを秘匿させ、そうでない場合には、規約サインビットエンコーディング/デコーディングが用いられる。

# [0078]

単一係数の場合においてサインビット秘匿を適用するために、サイン情報は、係数レベルのパリティと比較される。一例として、偶数のパリティは、正のサインに対応し得、奇数は、負に対応し得る。エンコーダは、その後に、レベルがサインに対応していない場合には、レベルを調整する。この技術は、閾値よりも上方ではすべての負のレベルは奇数であり、すべての正のレベルは偶数であるということを示唆していることが理解され得る。ある意味で、これは、事実上、閾値よりも大きい大きさを有する係数に対する量子化ステップサイズの改変であると考えられ得る。

## [0079]

サインビット秘匿を実装するための例示的なシンタックスの例が、以下に提供される。この例示的なシンタックスは、1つの可能性のある実装にすぎない。この例において、サインビット秘匿は、係数グループベースで適用され、閾値テストは、係数グループ内の第1非ゼロ係数から係数グループ内の最終非ゼロ係数までの係数の数に基づいている。sign\_data\_hidingと記されたフラグは、サインビット秘匿がオンであるかどうかを示すために、ピクチャヘッダ内で送信される。これが有効な場合には、ヘッダはまた、パラメータtsigをも含み、これは、閾値である。例示的なシンタックスは、以下のように設定される。

[0800]

【化2】

| pic_parameter_set_rbsp() {   | 記述子   |

|------------------------------|-------|

| pic_parameter_set_id         | ue(v) |

| seq_parameter_set_id         | ue(v) |

| sign_data_hiding             | u(1)  |

| if ( sign_data_hiding ) {    |       |

| tsig                         | u(4)  |

| }                            |       |

| entropy_coding_synchro       | u(v)  |

| cabac_istate_reset_flag      | u(1)  |

| if( entropy_coding_synchro ) |       |

| num_substreams_minus1        | ue(v) |

| •••                          |       |

40

以下の擬似コードは、係数グループベースのサインビット秘匿の 1 つの例示的な実装を 例示している。

[0081]

10

20

# 【化3 - 1】

| residual_coding_cabac(x0, y0, log2TrafoWidth, log2TrafoHeight, scanIdx, cIdx) {   | 記述子   |          |

|-----------------------------------------------------------------------------------|-------|----------|

| last_significant_coeff_x_prefix                                                   | ae(v) |          |

| last_significant_coeff_y_prefix                                                   | ae(v) |          |

| if (last_significant_coeff_x_prefix > 3)                                          |       |          |

| last_significant_coeff_x_suffix                                                   | ae(v) |          |

| if (last_significant_coeff_y_prefix > 3)                                          |       |          |

| last_significant_coeff_y_suffix                                                   | ae(v) |          |

| numCoeff = 0                                                                      |       |          |

| do {                                                                              |       | 10       |

| xC = ScanOrder[ log2TrafoWidth ][ log2TrafoHeight ][ scanIdx ][ numCoeff ][ 0 ]   |       |          |

| yC = ScanOrder[ log2TrafoWidth ][ log2TrafoHeight ][ scanIdx ][ numCoeff ][ 1 ]   |       |          |

| numCoeff++                                                                        |       |          |

| } while((xC != LastSignificantCoeffX)  (yC != LastSignificantCoeffY))             |       |          |

| numLastSubset = (numCoeff - 1) >> 4                                               |       |          |

| for( $i = numLastSubset$ ; $i \ge 0$ ; $i )$ {                                    |       |          |

| offset = i << 4                                                                   |       |          |

| if( max( log2TrafoWidth, log2TrafoHeight ) > 3) {                                 |       |          |

| omitted                                                                           |       |          |

| } else {                                                                          |       |          |

| omitted                                                                           |       | <b>-</b> |

| }                                                                                 |       | 20       |

| firstNZPosInCG = 1<<4;                                                            |       |          |

| lastNZPosInCG = - 1;                                                              |       |          |

| for( n = 15; n >= 0; n) {                                                         |       |          |

| xC = ScanOrder[ log2TrafoWidth ][ log2TrafoHeight ][ scanIdx ][ n + offset ][ 0 ] |       |          |

[ 0 0 8 2 ]

# 【化3-2】

| yC = ScanOrder[ log2TrafoWidth ][ log2TrafoHeight ][ scanIdx ][ n + offset ][ 1 ] |       | 7 |     |

|-----------------------------------------------------------------------------------|-------|---|-----|

| if(significant coeff flag[xC][yC]) {                                              |       | † |     |

| coeff_abs_level_greater1_flag[n]                                                  | ae(v) | † |     |

| if( lastNZPosInCG ==-1)                                                           |       | † |     |

| lastNZPosInCG = n                                                                 |       | † |     |

| firstNZPosInCG = n                                                                |       | † |     |

| }                                                                                 |       | † |     |

| }                                                                                 |       | † |     |

| signHidden = lastNZPosInCG - firstNZPosInCG + 1 >= tsig                           |       | 1 | 1(  |

| for( $n = 15$ ; $n >= 0$ ; $n ) {$                                                |       | 1 | - ' |

| if(coeff_abs_level_greaterl_flag[n])                                              |       | 1 |     |

| coeff_abs_level_greater2_flag[ n ]                                                | ae(v) | 1 |     |

| }                                                                                 |       | † |     |

| for( $n = 15$ ; $n >= 0$ ; $n ) {$                                                |       | 1 |     |

| xC = ScanOrder[ log2TrafoWidth ][ log2TrafoHeight ][ scanIdx ][ n + offset ][ 0 ] |       | 1 |     |

| yC = ScanOrder[ log2TrafoWidth ][ log2TrafoHeight ][ scanIdx ][ n + offset ][ 1 ] |       | 1 |     |

| if(significant_coeff_flag[xC][yC]) {                                              |       | † |     |

| if (!sign_data_hiding    !signHidden    n != firstNZPosInCG)                      |       | † |     |

| coeff_sign_flag[ n ]                                                              | ae(v) | 1 |     |

| else                                                                              |       | 1 |     |

| $coeff_sign_flag[n] = 0$ ;                                                        |       | † | 20  |

| }                                                                                 |       | † |     |

| }                                                                                 |       | 1 |     |

| sumAbs = 0;                                                                       |       | 1 |     |

| for( $n = 15$ ; $n \ge firstNZPosInCG$ ; $n$ ) {                                  |       | 1 |     |

| if(coeff_abs_level_greater2_flag[n])                                              |       | 1 |     |

| coeff_abs_level_minus3[ n ]                                                       | ae(v) | 1 |     |

| xC = ScanOrder[ log2TrafoWidth ][ log2TrafoHeight ][ scanIdx ][ n + offset ][ 0 ] |       | 1 |     |

| yC = ScanOrder[ log2TrafoWidth ][ log2TrafoHeight ][ scanIdx ][ n + offset ][ 1 ] |       | 1 |     |

| if( significant_coeff_flag[ xC ][ yC ] ) {                                        |       | 1 |     |

| transCoeffLevel[ x0 ][ y0 ][ cIdx ][ xC ][ yC ] =                                 |       | 1 |     |

| (coeff_abs_level_minus3[n]+3)*(1-2*coeff_sign_flag[n])                            |       | _ | _   |

| if (sign_data_hiding && signHidden)                                               |       | _ | 30  |

| sumAbs += coeff_abs_level_minus3[n]+3                                             |       | _ |     |

| } else                                                                            |       | _ |     |

| transCoeffLevel[ x0 ][ y0 ][ cIdx ][ xC ][ yC ] = 0                               |       | _ |     |

| }                                                                                 |       | 4 |     |

| if (sign_data_hiding && signHidden && (sumAbs%2 == 1))                            |       | 4 |     |

| transCoeffLevel[x0][y0][cIdx][xC][yC] = - transCoeffLevel[x0][y0][cIdx][xC][yC]   |       | 1 |     |

| }                                                                                 | 1     | 1 |     |

| <del>}</del>                                                                      |       |   |     |

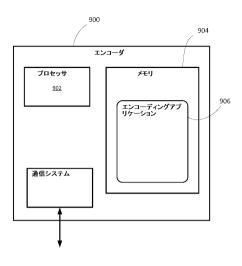

ここで図10に対する参照がなされ、該図面は、エンコーダ900の例示的な実施形態の簡略化されたブロック図を示している。エンコーダ900は、プロセッサ902、メモリ904、およびエンコーディングアプリケーション906を含んでいる。エンコーディングアプリケーション906は、メモリ904内に格納され、本明細書中に記載されているようなオペレーションを実行するようにプロセッサ902を構成するための命令を含んでいる、コンピュータプログラムまたはアプリケーションを含み得る。例えば、エンコーディングアプリケーション906は、本明細書中に記載されているプロセスにしたがって、エンコードし、エンコードされたビットストリームを出力し得る。エンコーディングアプリケーション906は、例えばコンパクトディスク、フラッシュメモリデバイス、ランダムアクセスメモリ、ハードドライブ等のコンピュータ読み取り可能な媒体上に格納され得ることが理解され得る。

[0083]

50

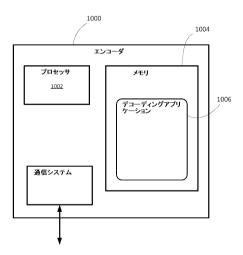

ここで図11に対する参照がなされ、該図面は、デコーダ1000の例示的な実施形態の簡略化されたブロック図を示している。デコーダ1000は、プロセッサ1002、メモリ1004、およびデコーディングアプリケーション1006を含む。デコーディングアプリケーション1006は、メモリ1004に格納され、本明細書中に記載されているようなオペレーションを実行するようにプロセッサ1002を構成するための命令を含んでいる、コンピュータプログラムまたはアプリケーションを含み得る。デコーディングアプリケーション1006は、少なくとも部分的に、本明細書中に記載されているように、有意係数フラグを再構成することに基づいて、残余を再構成するように構成されたエントロピーデコーダを含み得る。デコーディングアプリケーション1006は、例えばコンパクトディスク、フラッシュメモリデバイス、ランダムアクセスメモリ、ハードドライブ等のコンピュータ読み取り可能媒体上に格納され得るということが理解され得る。

[0084]

本願にしたがうデコーダおよび / またはエンコーダは、サーバ、適切にプログラムされた汎用コンピュータ、オーディオ / ビデオエンコーディングおよび再生デバイス、セットトップテレビジョンボックス、テレビジョンブロードキャスト機器、およびモバイルデバイスを含むがこれらに限定されない、多くのコンピューティングデバイスにおいて実装され得るということが理解され得る。デコーダまたはエンコーダは、本明細書中に記載されている機能を実行するようにプロセッサを構成するための命令を含むソフトウェアによって実装され得る。ソフトウェア命令は、CD、RAM、ROM、フラッシュメモリ等を含む、任意の適切な持続性コンピュータ読み取り可能メモリ上に格納され得る。

[0085]

本明細書中に記載されているエンコーダ、およびエンコーダを構成するための記載された方法 / プロセスを実装するモジュール、ルーチン、プロセス、スレッド、またはその他のソフトウェアコンポーネントは、標準的なコンピュータプログラミング技術および言語を用いて実現され得る。本願は、特定のプロセッサ、コンピュータ言語、コンピュータプログラミング規約、データ構造、その他のこのような実装の詳細に限定されない。当業者は、記載されているプロセスが、特定用途向け集積チップ(ASIC)等の一部分として揮発性または不揮発性メモリに格納されたコンピュータ実行可能コードの一部分として実装され得ることを認識し得る。

[0086]

記載された実施形態の特定の適応および改変がなされ得る。したがって、上述した実施 形態は、例示的なものであり、限定的なものではないと考慮されるべきである。

## 【符号の説明】

# [0087]

- 10 エンコーダ

- 12 ビデオソース

- 14 ビットストリーム

- 20 コーディングモード選択器

- 2 1 空間予測器

- 22 変換プロセッサ

- 2 4 量子化器

- 26 エントロピーコーダ

- 28 逆量子化器

- 30 逆変換プロセッサ

- 32 デブロッキングプロセッサ

- 34 フレーム格納

- 36 動き予測器

20

10

30

# 【図1】

# 【図2】

FIG. 1

FIG. 2

# 【図3】

# 【図4】

<u>FIG. 3</u>

<u>FIG. 4</u>

# 【図5】

# 【図6】

FIG. 5

<u>FIG. 6</u>

# 【図7】

【図8】

<u>FIG. 7</u>

<u>FIG. 8</u>

# 【図9】

【図10】

FIG. 10

# 【図11】

FIG. 11

## フロントページの続き

(72)発明者 ユ シアン

カナダ国 エヌ2エヌ 3アール5 , オンタリオ , キッチナー , レモン グラス クレセント 268

(72)発明者 ヒー デイク

カナダ国 エヌ2エル 3ダブリュー8, オンタリオ, ウォータールー, フィリップ スト リート 295, エクステンション 78760

# 審査官 久保 光宏

Gordon CLARE, et.al., "Sign Data Hiding", Document: JCTVC-G271, [online], Joint Colla borative Team on Video Coding (JCT-VC) of ITU-T SG16 WP3 and ISO/IEC JTC1/SC29/WG11, 2 0 1 1年11月, [平成25年10月24日検索], インターネット, URL, http://phenix.it-s udparis.eu/jct/doc\_end\_user/documents/7\_Geneva/wg11/JCTVC-G271-v3.zip 三宅恭介(外2名),「JPEG符号化列に対するステガノグラフィ」,コンピュータセキュリティシンポジウム2002論文集(情報処理学会シンポジウムシリーズ, Vol.2002, No.16),日本,社団法人情報処理学会,2002年10月30日,第227~232頁,ISSN:1344-0640 Joel Sole, et.al., "Non-CE11: Diagonal sub-block scan for HE residual coding", [online], Joint Collaborative Team on Video Coding (JCT-VC) of ITU-T SG16 WP3 and ISO/IEC JTC 1/SC29/WG11,2011年11月,Document: JCTVC-G323,[平成26年3月20日検索],インターネット,URL,http://phenix.int-evry.fr/jct/doc\_end\_user/documents/7\_Geneva/wg11/JCTVC-G323-v1.zip

Nguyen, T., et.al., "IMPROVED CONTEXT MODELING FOR CODING QUANTIZED TRANSFORM COEFFICI ENTS IN VIDEO COMPRESSION", Proceedings of the 28th Picture Coding Symposium (PCS 2010), 2 0 1 0 年 1 2 月, p.378-381, ISBN:978-1-4244-7134-8

Cheung Auyeung, et.al., "CE11: Hardware complexity of large zig-zag scan for level-coding of transform oefficients", [online], Joint Collaborative Team on Video Coding (JCT-VC) of ITU-T SG16 WP3 and ISO/IEC JTC1/SC29/WG11, 2 0 1 1年 7月, Document: JCTVC-F597, [平成26年3月20日検索], インターネット, URL, http://phenix.int-evry.fr/jct/doc\_end\_user/documents/6\_Torino/wg11/JCTVC-F597-v1.zip

小野定康(外2名)著,「ユビキタス技術 動画像の高能率符号化 - MPEG-4とH.264-」,日本,株式会社オーム社,2005年 4月20日,第1版,第129~134頁,ISBN:4-274-20060-4

Nguyen, N., et.al., "Multi-level significance maps for Large Transform Units", [online], Joint Collaborative Team on Video Coding (JCT-VC) of ITU-T SG16 WP3 and ISO/IEC JTC 1/SC29/WG11, 2 0 1 1年11月, Document: JCTVC-G644, [平成26年3月20日検索], インターネット, URL, http://phenix.int-evry.fr/jct/doc\_end\_user/documents/7\_Geneva/wg11/JCTVC-G644-v1.zip

画像電子学会編,「電子透かし技術」,日本,東京電機大学出版局,2004年 1月20日, 第1版,第59~71頁,ISBN:4-501-32320-5

"Index of /jct/doc\_end\_user/documents/7\_Geneva/wg11", [online], [平成26年3月20日検索], インターネット, URL, http://phenix.int-evry.fr/jct/doc\_end\_user/documents/7\_Geneva/wg11/

"Index of /jct/doc\_end\_user/documents/6\_Torino/wg11", [online], [平成26年3月20日検索], インターネット, URL, http://phenix.int-evry.fr/jct/doc\_end\_user/documents/6\_Torino/wg11/

"Index of /jct/doc\_end\_user/documents/7\_Geneva/wg11", [online], [平成25年10月24日検索], インターネット, URL, http://phenix.it-sudparis.eu/jct/doc\_end\_user/documents/7\_Geneva/wg11/

# (58)調査した分野(Int.CI., DB名)

H 0 4 N 1 9 / 0 0 - 1 9 / 9 8 , H 0 4 N 7 / 1 2 - 7 / 3 2 , C S D B (日本国特許庁) , I E E E X p l o r e ( I E E E )