## (19) **日本国特許庁(JP)**

# (12) 公 開 特 許 公 報(A)

(11)特許出願公開番号

特開2011-199643 (P2011-199643A)

(43) 公開日 平成23年10月6日(2011.10.6)

| (51) Int.Cl. |               |           | FΙ   |       |     | テーマコード (参考) |

|--------------|---------------|-----------|------|-------|-----|-------------|

| HO4N         | 5/374         | (2011.01) | HO4N | 5/335 | 740 | 4M118       |

| HO4N         | <i>5/3</i> 55 | (2011.01) | HO4N | 5/335 | 550 | 5CO24       |

| HO1L         | 27/146        | (2006.01) | HO1L | 27/14 | Α   |             |

| HO1L         | 27/14         | (2006.01) | HO1L | 27/14 | D   |             |

|           |                            | 審査請求     | 未請求 請求項の数 9 OL (全 17 頁) |

|-----------|----------------------------|----------|-------------------------|

| (21) 出願番号 | 特願2010-64742 (P2010-64742) | (71) 出願人 | 000003078               |

| (22) 出願日  | 平成22年3月19日 (2010.3.19)     |          | 株式会社東芝                  |

|           |                            |          | 東京都港区芝浦一丁目1番1号          |

|           |                            | (74) 代理人 | 100108855               |

|           |                            |          | 弁理士 蔵田 昌俊               |

|           |                            | (74) 代理人 | 100091351               |

|           |                            |          | 弁理士 河野 哲                |

|           |                            | (74) 代理人 | 100088683               |

|           |                            |          | 弁理士 中村 誠                |

|           |                            | (74) 代理人 | 100109830               |

|           |                            |          | 弁理士 福原 淑弘               |

|           |                            | (74) 代理人 | 100075672               |

|           |                            |          | 弁理士 峰 隆司                |

|           |                            | (74) 代理人 | 100095441               |

|           |                            |          | 弁理士 白根 俊郎               |

|           |                            |          | 最終頁に続く                  |

## (54) 【発明の名称】固体撮像装置

## (57)【要約】

【課題】ダイナミックレンジの拡大及び高感度画素に対 するケラレの発生を抑制する。

【解決手段】半導体基板10内に一定ピッチPで連続して形成され、且つ高感度画素32aに対応するものと低感度画素32bに対応するものとが交互に配置されたフォトダイオード32と、基板10上に設けられた高感度画素用配線(ピッチC)と、基板10上に設けられた低感度画素用配線(ピッチC)と、各配線の基板10と反対側に設けられ高感度画素32aに対する入射光の波長を制限する高感度画素用カラーフィルタ35a(ピッチA)と、各配線の基板と反対側に設けられ低感度画素に対する入射光の波長を制限する低感度画素用カラーフィルタ35b(ピッチB)とを備えた固体撮像装置であって、開口A,BとピッチC,Dとの関係を、B<D<P<C<Aに設定した。

【選択図】 図9

#### 【特許請求の範囲】

## 【請求項1】

半導体基板内に一定ピッチPで連続して形成され、且つ高感度画素に対応するものと低感度画素に対応するものとが交互に配置されたフォトダイオードと、前記基板上に設けられた高感度画素用配線と、前記各配線の前記基板と反対側に設けられ前記高感度画素に対する入射光の波長を制限する高感度画素用カラーフィルタと、前記各配線の前記基板と反対側に設けられ前記低感度画素に対する入射光の波長を制限する低感度画素用カラーフィルタとを具備し、

前記高感度画素用カラーフィルタのピッチAは前記低感度画素用カラーフィルタのピッチBよりも大きく、前記高感度画素用配線のピッチCは前記ピッチAと等しく前記ピッチPよりも大きく、前記低感度画素用配線のピッチDは前記ピッチBと等しく前記ピッチPよりも小さいことを特徴とする固体撮像装置。

## 【請求項2】

半導体基板内に一定ピッチPで連続して形成され、且つ高感度画素に対応するものと低感度画素に対応するものとが交互に配置されたフォトダイオードと、前記基板上に設けられた高感度画素用配線と、前記各配線の前記基板と反対側に設けられ前記高感度画素に対する入射光の波長を制限する高感度画素用カラーフィルタと、前記各配線の前記基板と反対側に設けられ前記低感度画素に対する入射光の波長を制限する低感度画素用カラーフィルタとを具備し、

前記高感度画素用カラーフィルタのピッチAは前記低感度画素用カラーフィルタのピッチBよりも大きく、前記高感度画素用配線のピッチCは前記ピッチAよりも小さく前記ピッチPよりも大きく、前記低感度画素用配線のピッチDは前記ピッチBよりも大きく前記ピッチPよりも小さいことを特徴とする固体撮像装置。

#### 【請求項3】

半導体基板内に一定ピッチPで連続して形成され、且つ高感度画素に対応するものと低感度画素に対応するものとが交互に配置されたフォトダイオードと、前記基板上に複数層に設けられた高感度画素用配線と、前記基板上に複数層に設けられた低感度画素用配線と、前記各配線の前記基板と反対側に設けられ前記高感度画素に対する入射光の波長を制限する高感度画素用カラーフィルタと、前記各配線の前記基板と反対側に設けられ前記低感度画素に対する入射光の波長を制限する低感度画素用カラーフィルタとを具備し、

前記高感度画素用カラーフィルタのピッチAは前記低感度画素用カラーフィルタのピッチBよりも大きく、前記高感度画素用配線の下層側のピッチC1は上層側のピッチC2よりも小さく前記ピッチP以上で、前記ピッチC2は前記ピッチAよりも小さく、前記低感度画素用配線の下層側のピッチD1は上層側のピッチD2よりも大きく前記ピッチP以下で、前記ピッチD2は前記ピッチBよりも大きいことを特徴とする固体撮像装置。

## 【請求項4】

前記高感度画素の開口を規定する高感度画素用マイクロレンズと、前記低感度画素の開口を規定する低感度画素用マイクロレンズとを備え、前記高感度画素用マイクロレンズのピッチは前記高感度画素用カラーフィルタのピッチ B と同じであることを特徴とする請求項 1 ~ 3 の何れか 1 項に記載の固体撮像装置。

#### 【請求項5】

前記高感度画素用マイクロレンズと前記低感度画素用マイクロレンズは互いに市松模様状に配置されていることを特徴とする請求項4記載の固体撮像装置。

#### 【請求項6】

前記高感度画素に対応する第1のフォトダイオードに接続され、信号電荷を読み出す第 1の読み出しトランジスタと、

前記低感度画素に対応する第2のフォトダイオードに接続され、信号電荷を読み出す第2の読み出しトランジスタと、

前記第1及び第2の読み出しトランジスタに接続され信号電荷を蓄積するフローティン

10

20

30

40

グディフュージョンと、

前記フローティングディフュージョンの電位をリセットするリセットトランジスタと、

前記フローティングディフュージョンの電位を増幅する増幅トランジスタと、

を更に有することを特徴とする請求項1~5の何れか1項に記載の固体撮像装置。

## 【請求項7】

前記第1のフォトダイオードの信号電荷と前記第2のフォトダイオードの信号電荷とを 前記フローティングディフュージョンで加算した電位を増幅して信号を出力する第1の動 作モードと、

前記第2のフォトダイオードの信号電荷が前記第2の読出しトランジスタにより読み出された前記フローティングディフュージョンの電位を増幅して信号を出力する第2の動作モードと、

を有することを特徴とする請求項6記載の固体撮像装置。

#### 【請求項8】

前記第1のフォトダイオードの信号電荷と前記第2のフォトダイオードの信号電荷とを、別々に読み出して信号を出力する第1の動作モードと、

前記第2のフォトダイオードの信号電荷を読み出して信号を出力する第2の動作モードと、

を有することを特徴とする請求項6記載の固体撮像装置。

## 【請求項9】

前記第1のフォトダイオードの光感度をSENS1、飽和レベルをVSAT1、前記第2のフォトダイオードの光感度をSENS2、飽和レベルをVSAT2で表すと、

VSAT1 / SENS1 < VSAT2 / SENS2

の関係式を満たすことを特徴とする請求項7又は8記載の固体撮像装置。

【発明の詳細な説明】

## 【技術分野】

## [0001]

本発明は、高感度画素と低感度画素の2種の画素で単位画素を構成した固体撮像装置に関する。

#### 【背景技術】

## [0002]

近年、CCDイメージセンサやCMOSイメージセンサ等の固体撮像装置において、撮像領域内に高感度画素と低感度画素を隣接して設けることによってダイナミックレンジを拡大する技術が提案されている(例えば、特許文献1参照)。この装置では、高感度画素に対しては画素ピッチよりも開口を大きくし(マイクロレンズの径が大)、低感度画素に対しては画素ピッチよりも開口を小さくしている(マイクロレンズの径が小)。

#### [0003]

しかしながら、この種の装置にあっては次のような問題があった。即ち、高感度画素に対しては画素ピッチよりも開口の方が大きいため、高感度画素に対して大きな角度を持って光が入射することになる。このとき、高感度画素及び低感度画素の各々の配線ピッチは共に画素ピッチと同じにしているため、配線ピッチよりも開口の方が大きくなる。このため、大きな角度を持って入射する光が高感度画素の配線で遮られて、いわゆるケラレが発生する問題があった。

【先行技術文献】

## 【特許文献】

#### [0004]

【特許文献1】特開2008-99073号公報

### 【発明の概要】

【発明が解決しようとする課題】

## [0005]

本発明の目的は、ダイナミックレンジの拡大と共に高感度画素に対するケラレの発生を

10

20

30

40

抑制し得る固体撮像装置を提供することにある。

【課題を解決するための手段】

## [0006]

本発明の一態様に係わる固体撮像装置は、半導体基板内に一定ピッチPで連続して形成され、且つ高感度画素に対応するものと低感度画素に対応するものとが交互に配置されたフォトダイオードと、前記基板上に設けられた高感度画素用配線と、前記基板上に設けられた低感度画素用配線と、前記各配線の前記基板と反対側に設けられ前記高感度画素に対する入射光の波長を制限する低感度画素用カラーフィルタと、前記各配線の前記基板と反対側に設けられ前記低感度画素に対する入射光の波長を制限する低感度画素用カラーフィルタのピッチAは前記低感度画素用カラーフィルタのピッチBよりも大きく、前記高感度画素用配線のピッチCは前記ピッチBと等しく前記ピッチPよりも小さいことを特徴とする。

## [0007]

また、本発明の別の一態様に係わる固体撮像装置は、半導体基板内に一定ピッチPで連続して形成され、且つ高感度画素に対応するものと低感度画素に対応するものとが交互に配置されたフォトダイオードと、前記基板上に設けられた高感度画素用配線と、前記各配線の前記基板と反対側に設けられ前記高感度画素に対する入射光の波長を制限する高感度画素用カラーフィルタと、前記各配線の前記基板と反対側に設けられ前記低感度画素に対する入射光の波長を制限する低感度画素用カラーフィルタとを具備し、前記高感度画素用カラーフィルタのピッチAは前記低感度画素用カラーフィルタのピッチBよりも大きく、前記高感度画素用配線のピッチCは前記ピッチAよりも小さく前記ピッチPよりも大きく、前記低感度画素用配線のピッチDは前記ピッチBよりも大きく前記ピッチPよりも小さいことを特徴とする。

#### [00008]

また、本発明の更に別の一態様に係わる固体撮像装置は、半導体基板内に一定ピッチPで連続して形成され、且つ高感度画素に対応するものと低感度画素に対応するものとが交互に配置されたフォトダイオードと、前記基板上に複数層に設けられた高感度画素用配線と、前記各配線の前記基板と反対側に設けられが記憶度画素用の場と、前記各配線の前記基板と反対側に設けられ前記低感度画素用カラーフィルタとを具備し、前記高感度画素用カラーフィルタのピッチBよりも大きく、前記高感度画素用カラーフィルタのピッチBよりも大きく、前記に感度画素用のピッチC2よりも小さく前記ピッチP以上で、前記ピッチC2は前記ピッチAよりも小さく、前記低感度画素用配線の下層側のピッチC1は上層側のピッチC2は前記ピッチBよりも大きく前記ピッチBよりとを特徴とする。

## 【発明の効果】

## [0009]

本発明によれば、高感度画素と低感度画素を隣接して設けた固体撮像装置において、ダイナミックレンジの拡大をはかると共に、高感度画素に対するケラレの発生を抑制することができる。

【図面の簡単な説明】

[0010]

【 図 1 】 第 1 の 実 施 形 態 に 係 わ る C M O S イ メ ー ジ セ ン サ の 概 略 構 成 を 示 す ブ ロ ッ ク 図 。

【 図 2 】 図 1 の C M O S イメージセンサにおけるレイアウトイメージの一部を概略的に示す図。

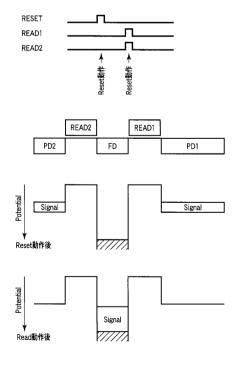

【図3】図1のCMOSイメージセンサの動作タイミング及びポテンシャル電位を説明するための図(高照射モード)。

【図4】図1のCMOSイメージセンサの動作タイミング及びポテンシャル電位を説明す

10

20

30

40

るための図(低照射モード)。

【 図 5 】 図 1 の C M O S イメージセンサにおけるダイナミックレンジ拡大効果を説明する ための特性図。

【図 6 】第 1 の実施形態におけるマイクロレンズ、配線、及び画素の配置関係を示す断面図。

【図7】第1の実施形態において高入射角の光が入射した状態を示す断面図。

【図8】第1の実施形態の変形例に係わるCMOSイメージセンサにおけるレイアウトイメージの一部を概略的に示す図。

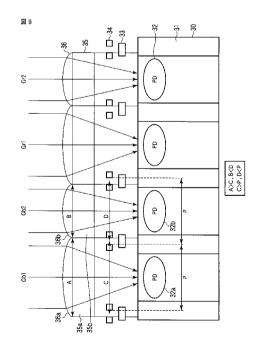

【図9】第2の実施形態におけるマイクロレンズ、配線、及び画素の位置関係を示す断面図。

【図10】第2の実施形態において高入射角の光が入射した状態を示す断面図。

【図11】第3の実施形態におけるマイクロレンズ、配線、及び画素の位置関係を示す断 面図。

【図12】第4の実施形態におけるマイクロレンズ、配線、及び画素の位置関係を示す断面図。

【発明を実施するための形態】

[0011]

以下、本発明の詳細を図示の実施形態によって説明する。

[0012]

(第1の実施形態)

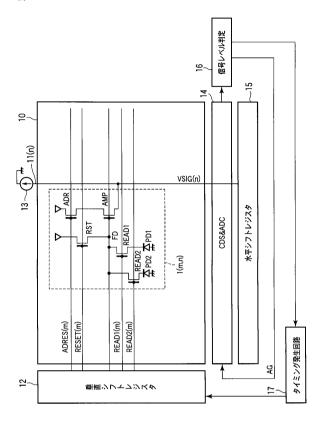

図1は、第1の実施形態に係わるCMOSイメージセンサを概略的に示すブロック図である。なお、このCMOSイメージセンサの全体構成は後述する別の実施形態においても同様である。

[0013]

撮像領域10はm行n列に配置された複数の単位画素(ユニットセル)1(m,n)を含む。ここでは、各単位画素のうち、m行目n列目の1つの単位画素1(m,n)、及び撮像領域の各カラムに対応して列方向に形成された垂直信号線のうちの1本の垂直信号線11(n)を代表的に示す。

[0014]

撮像領域10の一端側(図中左側)には、撮像領域の各行に ADRES(m), RESET(m), READ1(m), READ2(m) などの画素駆動信号を供給する垂直シフトレジスタ (Vertical Shift Register) 1 2 が配置されている。

[0015]

撮像領域10の上端側(図中上側)には、各カラムの垂直信号線11(n)に接続されている電流源13が配置されており、画素ソースフォロワ回路の一部として動作する。

[0016]

撮像領域の下端側(図中下側)には、各カラムの垂直信号線11(n)に接続されている相関二重サンプリング(Correlated double Sampling:CDS)回路&アナログ・デジタル変換回路(Analog Digital Convert:ADC)回路を含むCDS&ADC14と、水平シフトレジスタ(Horizontal Shift Register)15が配置されている。CDS&ADC14は、画素のアナログ出力をCDS処理し、デジタル出力に変換する。

[0017]

信号レベル判定回路16は、CDS&ADC14でデジタル化された出力信号のレベルに基づいて単位画素の出力信号VSIG(n)が所定値より小さいか大きいかを判定し、判定出力をタイミング発生回路(Timing Generator)17に供給すると共に、CDS&ADC14にアナログゲイン(Analog Gain)制御信号として供給する。

[0018]

タイミング発生回路17は、フォトダイオードの蓄積時間を制御する電子シャッタ制御信号や動作モード切替用の制御信号等をそれぞれ所定のタイミングで発生し、垂直シフトレジスタ12に供給する。

10

20

30

40

10

### [0019]

各単位画素は同一の回路構成を有しており、本実施形態では、各単位画素の中に、高感度画素と低感度画素を一つずつ配置している。ここで、図1中の単位画素1(m,n)の構成を説明する。

## [0020]

単位画素1(m,n)は、入射光を光電変換して蓄積する第1のフォトダイオードPD1に接続され、第1のフォトダイオードPD1に接続され、第1のフォトダイオードPD1に接続され、第1のフォトダイオードPD1で高行を読み出し制御する第1の読み出しトランジスタREAD1と、第1のフォトダイオードPD2に接続され、第2のフォトダイオードPD2に接続され、第2のフォトダイオードPD2に接続され、第1の2と、第1及2の読み出しトランジスタREAD2と、第1及び第2の読み出しトランジスタREAD1,READ2の各一端に接続され、第1及び第2の読み出しトランジスタREAD1,READ2により読み出された信号電荷を一時のに出フローティングディフュージョンFDの信号を増幅しつが接続されてプローティングディフュージョンFDの信号を増幅して垂直信で(n)に出力する増幅トランジスタAMPと、増幅トランジスタAMPのゲート電位をリセットするリセットトランジスタAMPC電面方向における所望水平位置の単位画素を選択制御するために増幅トランジスタAMPに電源電圧を供給制御する選択トランジスタAORを有する。なお、各トランジスタは、本例ではn型のMOSFETである。

### [0021]

選択トランジスタADR、リセットトランジスタRST、第1の読み出しトランジスタREAD1、第2の読み出しトランジスタREAD2は、それぞれ対応する行の信号線 ADRES(m), RESET(m), READ1(m), READ2(m) により制御される。また、増幅トランジスタAMPの一端は、対応する列の垂直信号線11(n)に接続されている。

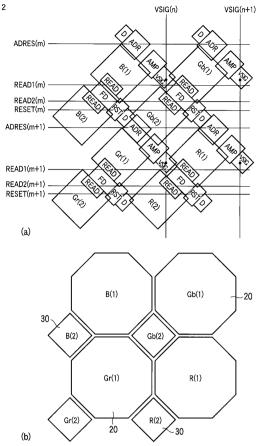

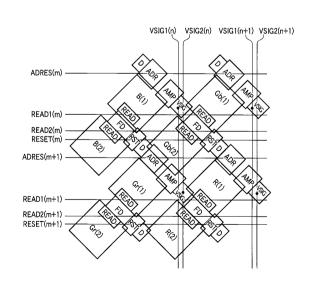

## [0022]

図2(a)は、図1のCMOSイメージセンサの撮像領域における一部分を取り出して素子形成領域及びゲートのレイアウトイメージを概略的に示す図である。図2(b)は、図1のCMOSイメージセンサにおける撮像領域の一部を取り出して色フィルタ・マイクロレンズのレイアウトイメージを概略的に示す図である。色フィルタ・マイクロレンズの配列は、通常のRGBベイヤー配列を採用している。

## [ 0 0 2 3 ]

図 2 ( a ) ( b )において、 R ( 1 ) ,R ( 2 )は R 用画素、 B ( 1 ) ,B ( 2 )は B 用画素、 G b ( 1 ) ,G b ( 2 ),G r ( 1 ),G r ( 2 )は G 用画素に対応する領域を示している。 D はドレイン領域を示している。また、信号線との対応関係を示すために、 m 行目の信号線 ADRES(m) ,RESET(m),READ1(m),READ2(m) 及び( m + 1 )行目の信号線 ADRES(m+1),RESET(m+1),READ1(m+1),READ2(m+1)、 n 列目の垂直信号線 1 1 ( n )、 ( n + 1 )列目の垂直信号線 1 1 ( n + 1 )を示している。

## [0024]

なお、図2(a)では、説明を簡単にするために各種信号線が画素に重なっているように示すが、実際には各種信号線は画素に重ならないで、画素の周辺を通るようになっている。

## [0025]

図 2 ( a ) ( b ) に示したように、単位画素の中に高感度画素と低感度画素が配置され、高感度画素上には面積の大きな色フィルタ及びマイクロレンズ 2 0 が配置され、低感度画素上には面積の小さな色フィルタ及びマイクロレンズ 3 0 が配置されている。

#### [0026]

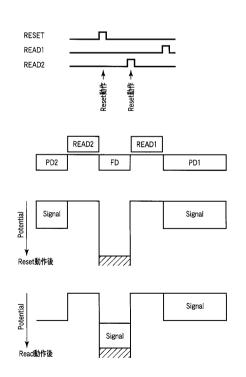

図3は、図1のCMOSイメージセンサにおいて、第1及び第2のフォトダイオードPD1,PD2に蓄積される信号電荷量が多い場合(明時)に適した低感度モードにおける画素の動作タイミング、リセット動作(Reset Operation)時における半導体基板内のポ

10

20

30

40

テンシャル(Potential)電位及び読み出し動作(Read Operation)時のポテンシャル電位の一例を示す図である。信号電荷量が多い場合は、センサの感度を落として、センサがなるべく飽和しないようにして、ダイナミックレンジを拡大することが求められる。

### [0027]

まず、リセットトランジスタRSTをオンさせてリセット動作を行うことにより、リセット動作を行った直後のフローティングディフュージョンFDの電位はドレイン(画素の電源)と同じ電位レベルに設定される。リセット動作の終了後は、リセットトランジスタRSTをオフする。すると、垂直信号線11には、フローティングディフュージョンFDの電位に応じた電圧が出力される。この電圧値をCDS&ADC14内のCDS回路に取り込んでおく(暗時レベル)。

## [0028]

次に、第1の読み出しトランジスタREAD1或いは第2の読み出しトランジスタREAD2をオンさせて、それまでにフォトダイオードPD1或いはPD2に蓄積された信号電荷をFDに転送する。低感度モードでは、第2の読み出しトランジスタREAD2のみをオンし、より感度の低い第2のフォトダイオードPD2で蓄積した信号電荷のみをフローティングディフュージョンFDに転送する読出し動作を行う。この信号電荷の転送に伴って、FD電位が変化する。垂直信号線11には、フローティングディフュージョンFDの電位に応じた電圧が出力されるので、この電圧値をCDS回路に取り込む(信号レベル)。その後、CDS回路で信号レベルから暗時レベルを引き算することにより、増幅トランジスタAMPのVth(閾値)ばらつき等のノイズをキャンセルし、純粋な信号成分のみを取り出す(CDS動作)。

### [0029]

なお、低感度モードでは、説明簡便のため、第1のフォトダイオードPD1と第1の読み出しトランジスタREAD1の動作に関しては説明を省略している。実際は、第1のフォトダイオードPD1の信号電荷がフローティングディフュージョンFDに溢れてくるのを防止するため、フローティングディフュージョンFDのリセット動作を行う直前に第1の読み出しトランジスタREAD1をオンさせ、第1のフォトダイオードPD1に蓄積された信号電荷を排出すると良い。また、フローティングディフュージョンFDのリセット動作と第2のフォトダイオードPD2からの信号の読出し動作を行っている期間以外は、常に第1の読み出しトランジスタREAD1をオンさせてもよい。

### [0030]

一方、図4は、図1のCMOSイメージセンサにおいて、フローティングディフュージョンFDに蓄積される信号電荷量が少ない場合(暗時)に適した高感度モードにおける画素の動作タイミング、リセット動作時における半導体基板内のポテンシャル電位及び読み出し動作時のポテンシャル電位の一例を示す図である。フローティングディフュージョンFDの信号電荷量が少ない場合は、CMOSイメージセンサの感度を上げてS/N比を向上させることが求められる。

## [0031]

まず、リセットトランジスタRSTをオンさせてリセット動作を行うことにより、リセット動作を行った直後のフローティングディフュージョンFDの電位(Potential)はドレイン(画素の電源)と同じ電位レベルに設定される。リセット動作の終了後は、リセットトランジスタRSTをオフする。すると、垂直信号線11には、フローティングディフュージョンFDの電位に応じた電圧が出力される。この電圧値をCDS&ADC14内のCDS回路に取り込んでおく(暗時レベル)。

#### [0032]

次に、第1及び第2の読み出しトランジスタREAD1,READ2をオンさせて、それまでに第1及び第2のフォトダイオードPD1,PD2に蓄積された信号電荷をフローティングディフュージョンFDに転送する。高感度モードでは、第1及び第2の読み出しトランジスタREAD1,READ2の両方をオンさせて、暗い状態で取得した信号電荷の全てをフローティングディフュージョンFDに転送する読出し動作を行う。この信号電

10

20

30

40

荷の転送に伴って、FD電位が変化する。垂直信号線11には、フローティングディフュージョンFDの電位に応じた電圧が出力されるので、この電圧値をCDS回路に取り込む(信号レベル)。その後、信号レベルから暗時レベルを引き算することにより、増幅トランジスタAMPのVthばらつき等のノイズをキャンセルし、純粋な信号成分のみを取り出す(CDS動作)。

#### [0033]

一般に、CMOSイメージセンサでは、発生する全ノイズの中で、増幅トランジスタAMPで発生する熱雑音や1/fノイズが大きな割合を占めている。従って、本実施形態のCMOSイメージセンサのように、ノイズが発生する前にフローティングディフュージョンFDに転送する段階で信号を加算して信号レベルを大きくすることは、S/N比を向上させる上で有利である。また、フローティングディフュージョンFDに転送する段階で信号を加算することにより、画素数が減少するので、CMOSイメージセンサのフレームレートを上げ易いという効果が得られる。

[0034]

なお、フローティングディフュージョンFDで信号電荷を加算することに限定されるものではない。第1及び第2のフォトダイオードPD1,PD2の信号電荷を、別々に画素ソースフォロワ回路を用いて出力してもよい。この場合、CMOSセンサの外部の信号処理回路において、第1及び第2のフォトダイオードPD1,PD2の信号電荷の単純加算ではなく、例えば2:1の比率で重み付け加算を行うようにしてもよい。

[0035]

上述したように、本実施形態ではCMOSイメージセンサにおける単位画素中に、高感度画素と低感度画素をそれぞれ一つ設ける。そして、信号電荷量の少ない時は、高感度画素と低感度画素の信号を両方使用する。その際、単位画素の中で信号電荷を加算して読み出すと良い。また、信号電荷量が多い時は、低感度画素の信号のみを読み出す。このように、二つの動作モードを使い分ける。

[0036]

本実施形態では単位画素の中に高感度画素と低感度画素を一つずつ配置するので、次式(1)の関係が成り立つと考えてよい。即ち、従来画素の光感度/飽和レベル、高感度画素の光感度/飽和レベルを

従来画素の光感度:SENS

従来画素の飽和レベル:VSAT 高感度画素の光感度:SENS1 高感度画素の飽和レベル:VSAT1

低感度画素の飽和レベル:VSAT2

低感度画素の光感度: SENS2

で表すと、

SENS = SENS1 + SENS2

VSAT = VSAT1 + VSAT2 ... (1)

高感度画素が飽和して低感度モードに切り替わると、得られる信号電荷量が減少してS/Nが低下する。高感度画素が飽和する光量は、VSAT1/SENS1で表される。この光量での低感度画素の信号出力は、VSAT1 × SENS2/SENS1 となる。従って、この光量での信号出力の低下率は、

(VSAT1 x SENS2 / SENS1) / (VSAT1 x SENS / SENS1) = SENS2 / SENS ... (2) となる。高感度 / 低感度モード切替時の信号低下は避けたいので、SENS2 / SENS は、10%から50%の間に設定するのが妥当と考えられる。本実施形態では、SENS2 / SENS = 1/4 = 25%に設定している。

#### [0037]

一方、ダイナミックレンジの拡大効果は、低感度モードでの最大入射光量 VSAT2 / SENS 2 と従来画素の最大入射光量(ダイナミックレンジ)VSAT / SENS との比をとり、

$(VSAT2 / VSAT) \times (SENS / SENS2)$  ... (3)

20

10

30

40

となる。この式(3)より明らかなように、VSAT2 / VSAT は可能な限り大きくした方が良い。これは、高感度画素と低感度画素の飽和レベルは、同程度か、若しくは低感度画素の方を大きくした方が良いということを意味している。数式で表すと、

VSAT1 / SENS1 < VSAT2 / SENS2 ... ( 4 )

を満たすと、ダイナミックレンジを拡大することができる。

#### [ 0 0 3 8 ]

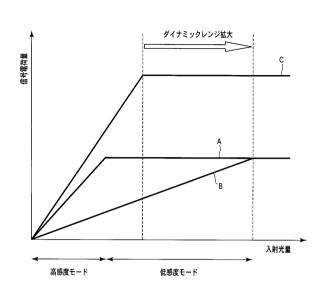

図5は、本実施形態のCMOSイメージセンサにおけるダイナミックレンジ拡大効果を 説明するために特性の一例を示す図である。図5中、横軸は入射光量を示し、縦軸はフォトダイオードに発生した信号電荷量を示している。ここでは、高感度画素(PD1)の特性A、低感度画素(PD2)の特性B、従来の単位画素中の画素(従来画素)の特性Cを示している。

[0039]

本実施形態では、高感度画素(PD1)の光感度は従来画素の3/4に設定され、低感度画素(PD2)の光感度は従来画素の1/4に設定されている。また、高感度画素(PD1)の飽和レベルは従来画素の1/2に設定され、低感度画素(PD2)の飽和レベルは従来画素の1/2に設定されている。

[0040]

図5から分かるように、高感度画素(PD1)の光感度は、従来画素と比べて3/4に設定され、低感度画素(PD2)の光感度は従来画素と比べて1/4に設定されているので、高感度画素(PD1)と低感度画素(PD2)の出力を加算する高感度モードでは、信号電荷量は従来の単位画素と同等である。

[0041]

一方、低感度画素(PD2)は、従来画素と比べて飽和レベルは1/2、光感度は1/4であるので、結果として、低感度画素(PD2)が飽和しないで動作する範囲は従来画素と比較して2倍広がっている。即ち、低感度画素(PD2)の出力を用いる低感度モードでは、ダイナミックレンジは従来画素と比較して2倍拡大していることが分かる。

[0042]

次に、本実施形態の更なる特徴である、レンズピッチ、配線ピッチ、画素ピッチの関係について説明する。

[0043]

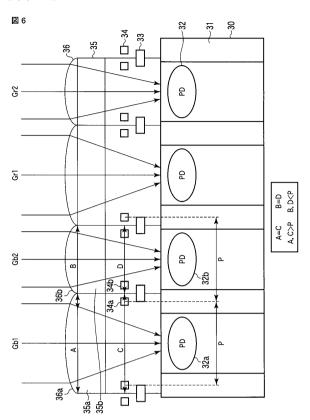

図6は、本実施形態におけるマイクロレンズ、配線、画素の関係を示す断面図であり、図中の30は半導体基板、31は素子分離絶縁膜、32は画素(PD)、33,34は配線、35はカラーフィルタ、36はマイクロレンズを示している。

[0044]

各画素32は一定ピッチPで配置され、隣接する画素32間は素子分離絶縁膜31で分離されている。画素32は、高感度画素32a、低感度画素32bの2種類の画素から構成されており、高感度画素32aの開口Aはマイクロレンズ36aで規定され、低感度画素32bの開口Bはマイクロレンズ36bにより規定されている。即ち、マイクロレンズ36aのピッチがマイクロレンズ36bのピッチよりも大きく、高感度画素32aの開口Aは低感度画素32bの開口Bよりも大きい構造となっている。下層側の配線33は前記出力信号 VSIG に相当するものであり、上層側の配線34は前記信号線 ADRES, RESET, READ に相当するものである。ここでは特に、上層側の配線34を高感度画素用34aと低感度画素用34bに分けて示している。

[0045]

なお、マイクロレンズ36aのピッチとは、レンズの中心を通る線上で見て、マイクロレンズ36aと隣接する2つのマイクロレンズ36bとの境界間の距離である。同様に、マイクロレンズ36bのピッチとは、レンズの中心を通る線上で見て、マイクロレンズ36bと隣接する2つのマイクロレンズ36aとの境界間の距離である。このピッチの定義はカラーフィルタ35及び配線33,34についても同様である。

[0046]

10

20

30

40

カラーフィルタ35は高感度画素用のフィルタ35aと低感度画素用のフィルタ35bの2種類から構成され、対応するマイクロレンズ36と同じピッチとなっている。即ち、高感度画素32aの開口Aはマイクロレンズ36a,カラーフィルタ35aのピッチと同じであり、低感度画素32bの開口Bはマイクロレンズ36b,カラーフィルタ35bのピッチと同じである。

[0047]

ここで、配線ピッチは画素ピッチPと同じではなく、本実施形態では、高感度配線ピッチCを低感度配線ピッチDよりも大きくしている。即ち、高感度画素配線ピッチCと低感度画素配線ピッチDの境界部(例えば、ここでは配線33上の配線34aと34bの中間点)は、高感度画素32bの開口Bの境界部と一致した構造である。

10

[0048]

従って、

A = C, B = D

となる。また、半導体基板 3 0 内に作られる P D (フォトダイオード) 3 2 は高感度画素 3 2 a , 低感度画素 3 2 b に対し等間隔に連続して形成される。つまり、画素( P D ) ピッチを P とすると、以下の関係が成立する。

[0049]

A = C > P, B = D < P

即ち、

20

30

40

「高感度画素開口Aと高感度画素配線ピッチCは等しく、画素ピッチPより大きい」「低感度画素開口Bと低感度画素配線ピッチDは等しく、画素ピッチPより小さい」となる。

[0050]

このように、高感度画素 3 2 a 及び低感度画素 3 2 b の各々で配線ピッチを開口ピッチに等しくすることにより、図 7 に示すように、高入射角で光が入射した場合に高感度画素 3 2 a においても、入射光が配線 3 3 , 3 4 で遮られるのを防止することができる。即ち、高感度画素 3 2 a におけるケラレを防止することができる。

[0051]

なお、高感度画素 3 2 a の開口率に比べて低感度画素 3 2 b の開口率が低下してしまうが、低感度画素 3 2 b への入射光の画角は高感度画素 3 2 a に比べて小さいので、入射光のケラレの増加は少ない。

[0052]

以上のように、本実施形態のCMOSイメージセンサでは、低感度モードを利用することでダイナミックレンジを拡大でき、高感度モードを利用することで光量が少ない場合(暗い場合)での光感度の劣化を少なくできる、という効果が得られる。即ち、光感度と信号電荷取扱量のトレードオフ(二律背反)の関係を乗り越え、暗時の低ノイズを維持したまま、信号電荷取扱量を大きくすることが可能である。

[0053]

これに加えて本実施形態では、高感度画素配線ピッチCを高感度画素開口Aと等しく1画素ピッチPより大きくし、低感度画素配線ピッチDを低感度画素開口Bと等しく1画素ピッチPより小さくすることにより、高感度画素に対する入射光のケラレ発生を防止することができる。

[0054]

さらに、本実施形態は、CMOSイメージセンサでダイナミックレンジの拡大を実現し、CMOSイメージセンサの利点、即ち間引き動作などを利用してフレームレートの高い、高速センサを容易に設計することが可能である。

[0055]

なお、本実施形態のCMOSイメージセンサでは、第1のフォトダイオードPD1だけ、或いは第2のフォトダイオードPD2だけに着目した場合、それぞれ一般的に用いられ

るRGBベイヤー配列となっているので、高感度モード、低感度モードとも、出力信号はRGBベイヤー配列に対応している。従って、デモザイクなどの色信号処理は、従来の処理をそのまま利用できる。

### [0056]

また、本実施形態のCMOSイメージセンサでは、第1、第2のフォトダイオードPD1、PD2が市松模様状に配置されている。そこで、図2(a)に示したように、フローティングディフュージョンFDを第1及び第2のフォトダイオードPD1,PD2の間に配置し、さらに残った隙間に各トランジスタAMP,RSTを配置すると、画素内で各部品のレイアウトを容易に行うことができる。

## [0057]

<第1の実施形態の変形例>

図8は、第1の実施形態の変形例に係わるCMOSイメージセンサの撮像領域における素子形成領域及びゲートのレイアウトイメージの一部を信号線と共に概略的に示す図である。

## [0058]

図 8 中、信号線は、m行目の信号線 ADRES(m), RESET(m), READ1(m), READ2(m) 及び(m+1)行目の信号線 ADRES(m+1), RESET(m+1), READ1(m+1), READ2(m+1)、n列目の2本の垂直信号線 VSIG1(n), VSIG2(n)、(n+1)列目の2本の垂直信号線 VSIG1(n+1), VSIG2(n+1)を示している。なお、色フィルタ及びマイクロレンズのレイアウトは、図2(b)に示した第1の実施形態におけるレイアウトと同じである。

#### [0059]

この変形例に係わる C M O S イメージセンサは、第 1 の実施形態と同様に、単位画素中に高感度画素と低感度画素が配置され、高感度画素上には面積の大きなマイクロレンズが配置されている。ここでは、フレームレート( 1 秒間に出力可能な画面数)を高くするために、撮像領域の各列に対して 2 本の垂直信号線を配置し、画素ソースフォロアの出力を撮像領域の 1 行おきに異なる垂直信号線に接続することにより、 2 行の画素の信号を同時に読み出すことができる。

#### [0060]

(第2の実施形態)

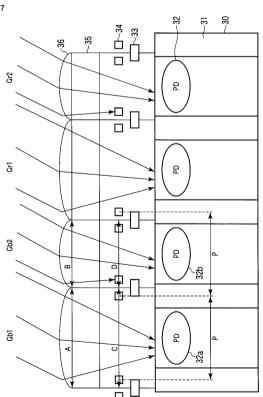

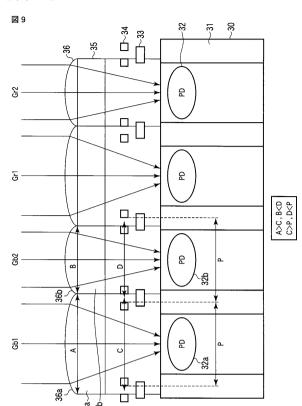

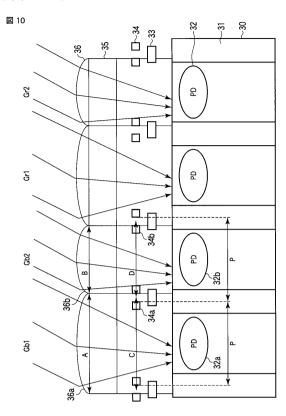

図9は、本発明の第2の実施形態に係わる固体撮像装置を説明するためのもので、マイクロレンズ、配線、及び画素の配置関係を示す断面図である。なお、図6と同一部分には同一符号を付して、その詳しい説明は省略する。

#### [0061]

各画素は先に説明した第1の実施形態と同様に、高感度画素32a、低感度画素32bの2種類の画素から構成されており、高感度画素32aの開口Aは低感度画素32bの開口Bよりも大きい構造となっている。ここで、高感度画素配線ピッチCと低感度画素配線ピッチDの境界部は、高感度画素32aの開口Aと低感度画素32bの開口Bの境界部に一致しておらず、以下の関係が成立する構造となっている。

## [0062]

A > C , B < D

また、半導体基板30内に作られるPD32は高感度画素32a,低感度画素32bに対し等間隔に連続して形成される。ここで、画素(PD)ピッチPを含めると

A > C > P , B < D < P

の関係が成立する。つまり、

「高感度画素配線ピッチCは高感度画素開口Aより小さく、画素ピッチPより大きい」「低感度画素配線ピッチDは高感度画素開口Bより大きく、画素ピッチPより小さい」となる。

### [0063]

先に説明した第1の実施形態では、低感度画素配線ピッチDが低感度画素32bの開口 Bと同等の大きさであったため、高感度画素32aの開口率に比べ低感度画素32bの開 10

20

30

40

口率が低下し、ケラレの発生する可能性があった。これに対し本実施形態では、低感度画素配線ピッチ D を低感度画素 3 2 b の開口 B より大きく、画素ピッチ P より小さく設計することで画素開口率を第 1 の実施形態の構造より改善させることができる。従って、図 1 0 に示すように、低感度画素 3 2 b へ高入射角の光が入射した場合にも、低感度画素用配線 3 4 b で光が遮られることはなく、低感度画素 3 2 b に発生していた入射光のケラレを低減することができる。

#### [0064]

即ち、高感度画素配線ピッチ C と低感度画素配線ピッチ D の最適化を行うことで、高感度画素 3 2 a 及び低感度画素 3 2 b において発生する光のケラレの低減をはかることができる。従って、高感度画素 3 2 a と低感度画素 3 2 b の感度比のズレを抑制することが可能となり、高感度画素 3 2 a と低感度画素 3 2 b を使用した高ダイナミックレンジな固体撮像装置を実現することが可能となる。

# [0065]

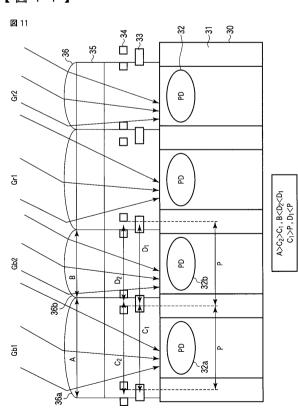

(第3の実施形態)

図 1 1 は、本発明の第 3 の実施形態に係わる固体撮像装置を説明するためのもので、マイクロレンズ、配線、及び画素の配置関係を示す断面図である。なお、図 6 と同一部分には同一符号を付して、その詳しい説明は省略する。

#### [0066]

各画素は先の第1の実施形態と同様に高感度画素32a、低感度画素32bの2種類の画素から構成されており、高感度画素32aの開口Aは低感度画素32bの開口Bよりも大きい構造となっている。ここで、高感度画素32aの第1層配線33aのピッチC1、低感度画素の第1層配線33bのピッチD1、高感度画素32aの第2層配線34aのピッチC2、低感度画素32bの第2層配線34bのピッチD2とする。高感度画素32aの開口Aと低感度画素32bの開口Bの境界部は、各配線層の高感度画素配線ピッチと低感度画素配線ピッチの境界部と一致しておらず、以下の関係が成立する構造となっている

## [0067]

A > C 2 > C 1 , B < D 2 < D 1

また、半導体基板30内に作られるPD32は高感度画素32a、低感度画素32bに対し等間隔に連続して形成される。ここで画素(PD)ピッチPを含めると

A > C 2 > C 1 > P , B < D 2 < D 1 < P

の関係が成立する。

# [0068]

このように本構造は、先の第2実施形態での全配線層を一律に動かすのとは異なり、各配線層の画素配線ピッチを決定することにより第2の実施形態よりも更に高感度画素32 aと低感度画素32bの感度比のズレを抑制することが可能となる。従って、より一層の高感度画素32aと低感度画素32bを使用した高ダイナミックレンジな固体撮像装置を実現することが可能である。

## [0069]

なお、配線層は必ずしも2層に限るものではなく、3層以上であっても良い。3層以上の場合、高感度画素では上層ほど配線ピッチを大きくし、低感度画素では上層ほど配線ピッチを小さくすればよい。

## [0070]

(第4の実施形態)

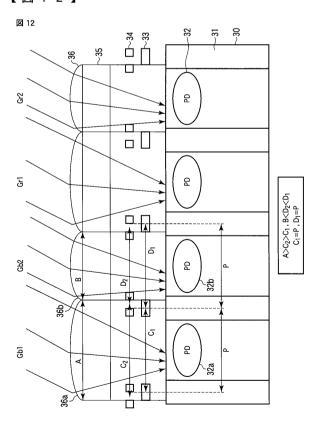

図12は、本発明の第4の実施形態に係わる固体撮像装置を説明するためのもので、マイクロレンズ、配線、及び画素の配置関係を示す断面図である。なお、図6と同一部分には同一符号を付して、その詳しい説明は省略する。

### [0071]

基本的な構成は先に説明した第3の実施形態と同様であり、本実施形態が第3の実施形態と異なる点は、高感度画素32a及び低感度画素32bの第1層配線33a,33bの

10

20

30

40

ピッチを画素ピッチPと等しくしたことにある。即ち、

A > C 2 > C 1 = P, B < D 2 < D 1 = P

の関係が成立する。

## [0072]

つまり、本実施形態での各第1配線ピッチと画素ピッチの関係は、

「高感度画素第1層配線33aのピッチC1は、画素ピッチPと等しい」

「低感度画素第1層配線33bのピッチD1は、画素ピッチPと等しい」

関係が成り立ち、第1層配線ピッチと画素ピッチPは当ピッチということである。

## [0073]

これにより、第2層配線層(TOP配線層)では低感度画素32bで発生するケラレを抑制し、第1層配線層(最下層配線層)は隣接する画素に対する光学クロストークの低減及び各画素のPDを分離する拡散層に光が入射することを防止し、キャリアのクロストークの発生などを抑制することが可能である。

## [0074]

以上より本実施形態構造は、高感度画素32aと低感度画素32bを使用した高ダイナミックレンジな固体撮像装置と共に低混色な固体撮像装置を実現することが可能となる。

#### [0075]

#### (変形例)

なお、本発明は上述した各実施形態に限定されるものではない。実施形態では、 C M O S イメージセンサの例で説明したが、本発明は C M O S イメージセンサに限らず C C D イメージセンサに適用することも可能である。さらに、前記図 1 に示した回路構成は一例であり、本発明は高感度画素と低感度画素を備えた各種の固体撮像装置に適用することができる。

#### [0076]

また、前記図6に示したデバイス構成の各構成要素は一例に過ぎず、仕様に応じて適宜変更可能である。例えば、高感度画素では開口Aを画素ピッチPよりも大きくするためにマイクロレンズは必須であるが、低感度画素では開口Bを画素ピッチPよりも小さくしているので、マイクロレンズを省略することも可能である。その他、本発明の要旨を逸脱しない範囲で、種々変形して実施することができる。

## 【符号の説明】

## [0077]

1 … 単位画素、PD1,PD2…フォトダイオード、FD…フローティングディフュージョン、READ1,READ2…読み出しトランジスタ、AMP…増幅トランジスタ、RST…リセットトランジスタ、ADR…選択トランジスタ、10…撮像領域、11…垂直信号線、12…垂直シフトレジスタ、13…電流源、14…サンプリング&アナログ・デジタル変換回路、15…水平シフトレジスタ、16…信号レベル判定回路、17…タイミング発生回路、30…半導体基板、31…素子分離絶縁膜、32…画素(PD)、33…第1層配線(下層配線)、34…第2層配線(上層配線)、35カラーフィルタ、36…マイクロレンズ。

10

20

# 【図1】

図 1

# 【図2】

図 2

# 【図3】

図 3

【図4】

図 4

# 【図5】

図 5

# 【図6】

# 【図7】

図 7

# 【図8】

図 8

【図9】

【図10】

【図11】

【図12】

## フロントページの続き

(74)代理人 100084618

弁理士 村松 貞男

(74)代理人 100103034

弁理士 野河 信久

(74)代理人 100119976

弁理士 幸長 保次郎

(74)代理人 100153051

弁理士 河野 直樹

(74)代理人 100140176

弁理士 砂川 克

(74)代理人 100101812

弁理士 勝村 紘

(74)代理人 100124394

弁理士 佐藤 立志

(74)代理人 100112807

弁理士 岡田 貴志

(74)代理人 100111073

弁理士 堀内 美保子

(74)代理人 100134290

弁理士 竹内 将訓

(74)代理人 100127144

弁理士 市原 卓三

(74)代理人 100141933

弁理士 山下 元

(72)発明者 成瀬 純次

東京都港区芝浦一丁目1番1号 株式会社東芝内

(72)発明者 田中 長孝

東京都港区芝浦一丁目1番1号 株式会社東芝内

F ターム(参考) 4M118 AA02 AB01 BA14 CA02 CA22 DD04 FA06 FA07 FA28 FA33

GB03 GB16 GC07 GC08 GC14 GD04 GD07

5C024 AX01 CX41 CX43 DX01 EX43 GX03 GX07 GY31