(21) 3 140 388

## (12) DEMANDE DE BREVET CANADIEN **CANADIAN PATENT APPLICATION**

(13) **A1**

- (86) Date de dépôt PCT/PCT Filing Date: 2020/05/15

- (87) Date publication PCT/PCT Publication Date: 2020/11/26

- (85) Entrée phase nationale/National Entry: 2021/11/12

- (86) N° demande PCT/PCT Application No.: US 2020/033285

- (87) N° publication PCT/PCT Publication No.: 2020/236659

- (30) Priorité/Priority: 2019/05/17 (US62/849,494)

- (51) Cl.Int./Int.Cl. H02J 13/00 (2006.01). H02H 3/08 (2006.01), H03K 17/0812 (2006.01), H03K 17/16 (2006.01), H03K 17/687 (2006.01), H05B 47/25 (2020.01)

- (71) Demandeur/Applicant: LUTRON TECHNOLOGY COMPANY LLC, US

- (72) Inventeurs/Inventors: BOLLINGER, BRIAN J., US; CHITTA, VENKATESH, US: WALDRON, JONATHAN, US; CHOLASHARI, FIROZBABU, US

- (74) Agent: GOWLING WLG (CANADA) LLP

- (54) Titre: DISPOSITIF DE COMMANDE DE CHARGE AYANT UN CIRCUIT D'ATTAQUE DE GRILLE EN BOUCLE **FERMEE**

- (54) Title: LOAD CONTROL DEVICE HAVING A CLOSED-LOOP GATE DRIVE CIRCUIT

#### (57) Abrégé/Abstract:

A load control device for controlling power delivered from an AC power source to an electrical load may have a closed-loop gate drive circuit for controlling a semiconductor switch of a controllably conductive device. The controllably conductive device may be coupled in series between the source and the load. The gate drive circuit may generate a target signal in response to a control circuit. The gate drive circuit may shape the target signal over a period of time and may increase the target signal to a predetermined level after the period of time. The gate drive circuit may receive a feedback signal that indicates a magnitude of a load current conducted through the semiconductor switch. The gate drive circuit may generate a gate control signal in response to the target signal and the feedback signal, and render the semiconductor switch conductive and non-conductive in response to the gate control signal.

#### (12) INTERNATIONAL APPLICATION PUBLISHED UNDER THE PATENT COOPERATION TREATY (PCT)

### (19) World Intellectual Property Organization

International Bureau

(43) International Publication Date 26 November 2020 (26.11.2020)

(10) International Publication Number WO 2020/236659 A1

(51) International Patent Classification:

H05B 39/04 (2006.01)

H05B 47/25 (2020.01)

H05B 41/392 (2006.01)

H03K 17/16 (2006.01)

H05B 47/14 (2020.01)

(21) International Application Number:

PCT/US2020/033285

(22) International Filing Date:

15 May 2020 (15.05.2020)

(25) Filing Language:

English

(26) Publication Language:

English

US

(30) Priority Data:

62/849,494

17 May 2019 (17.05.2019)

- (71) Applicant: LUTRON TECHNOLOGY COMPANY LLC [US/US]; 7200 Suter Road, Coopersburg, Pennsylvania 18036-1299 (US).

- (72) Inventors: BOLLINGER, Brian J.; 7200 Suter Road, Coopersburg, Pennsylvania 18036-1299 (US). CHITTA, Venkatesh; 7200 Suter Road, Coopersburg, Pennsylvania 18036-1299 (US). WALDRON, Jonathan; 7200 Suter Road, Coopersburg, Pennsylvania 18036-1299 (US). CHOLASHARI, Firozbabu; 7200 Suter Road, Coopersburg, Pennsylvania 18036-1299 (US).

- (74) Agent: PISCITELLI, Michael F.; 1835 Market street, Suite 1050, Philadelphia, Pennsylvania 19103 (US).

- (81) Designated States (unless otherwise indicated, for every kind of national protection available): AE, AG, AL, AM, AO, AT, AU, AZ, BA, BB, BG, BH, BN, BR, BW, BY, BZ, CA, CH, CL, CN, CO, CR, CU, CZ, DE, DJ, DK, DM, DO,

(54) Title: LOAD CONTROL DEVICE HAVING A CLOSED-LOOP GATE DRIVE CIRCUIT

(57) Abstract: A load control device for controlling power delivered from an AC power source to an electrical load may have a closed-loop gate drive circuit for controlling a semiconductor switch of a controllably conductive device. The controllably conductive device may be coupled in series between the source and the load. The gate drive circuit may generate a target signal in response to a control circuit. The gate drive circuit may shape the target signal over a period of time and may increase the target signal to a predetermined level after the period of time. The gate drive circuit may receive a feedback signal that indicates a magnitude of a load current conducted through the semiconductor switch. The gate drive circuit may generate a gate control signal in response to the target signal and the feedback signal, and render the semiconductor switch conductive and non-conductive in response to the gate control signal.

#

DZ, EC, EE, EG, ES, FI, GB, GD, GE, GH, GM, GT, HN, HR, HU, ID, IL, IN, IR, IS, JO, JP, KE, KG, KH, KN, KP, KR, KW, KZ, LA, LC, LK, LR, LS, LU, LY, MA, MD, ME, MG, MK, MN, MW, MX, MY, MZ, NA, NG, NI, NO, NZ, OM, PA, PE, PG, PH, PL, PT, QA, RO, RS, RU, RW, SA, SC, SD, SE, SG, SK, SL, ST, SV, SY, TH, TJ, TM, TN, TR, TT, TZ, UA, UG, US, UZ, VC, VN, WS, ZA, ZM, ZW.

(84) Designated States (unless otherwise indicated, for every kind of regional protection available): ARIPO (BW, GH, GM, KE, LR, LS, MW, MZ, NA, RW, SD, SL, ST, SZ, TZ, UG, ZM, ZW), Eurasian (AM, AZ, BY, KG, KZ, RU, TJ, TM), European (AL, AT, BE, BG, CH, CY, CZ, DE, DK, EE, ES, FI, FR, GB, GR, HR, HU, IE, IS, IT, LT, LU, LV, MC, MK, MT, NL, NO, PL, PT, RO, RS, SE, SI, SK, SM, TR), OAPI (BF, BJ, CF, CG, CI, CM, GA, GN, GQ, GW, KM, ML, MR, NE, SN, TD, TG).

#### Published:

- with international search report (Art. 21(3))

- before the expiration of the time limit for amending the claims and to be republished in the event of receipt of amendments (Rule 48.2(h))

## LOAD CONTROL DEVICE HAVING A CLOSED-LOOP GATE DRIVE CIRCUIT

## CROSS-REFERENCE TO RELATED APPLICATIONS

[0001] This application claims the benefit of Provisional U.S. Patent Application No. 62/849,494, filed May 17, 2019, the disclosure of which is incorporated herein by reference in its entirety.

#### **BACKGROUND**

Prior art load control devices, such as dimmer switches, may be coupled in series electrical connection between an alternating-current (AC) power source and a lighting load for controlling the amount of power delivered from the AC power source to the lighting load. A standard dimmer switch may typically comprise a bidirectional semiconductor switch, *e.g.*, a thyristor (*e.g.*, such as a triac) or two field-effect transistors (FETs) in anti-series connection. The bidirectional semiconductor switch may be coupled in series between the AC power source and the load and is controlled to be conductive and non-conductive for portions of a half cycle of the AC power source to thus control the amount of power delivered to the electrical load. Generally, dimmer switches may use either a forward phase-control dimming technique or a reverse phase-control dimming technique in order to control when the bidirectional semiconductor switch is rendered conductive and non-conductive to thus control the power delivered to the load.

[0003] There is a need for load control devices that meet the electromagnetic compatibility (EMC) performance requirements during turn-on and turn-off events across a variety of electrical loads. The inconsistency of EMC performance across a variety of electrical loads can cause some load control devices to create audible buzzing noises or damage their internal components during turn-on or turn-off events. Such EMC inconsistencies limit the compatible range of electrical loads for a load control device.

[0004] There is also a need for load control devices that are compatible with a broader range of internal components. For example, when an internal component, such as a semiconductor switch of an existing load control device has been changed or second sourced, the load control device may become inoperable or require a redesign due to the change is operating characteristics of the internal component. This is not only burdensome, but also costly.

[0005] Further, there are a need for overcurrent protection design in a load control device that allows for greater tolerance of natural overcurrent conditions but also prevents high current runaway. Existing overcurrent protection schemes in load control devices are rigid and do not allow for broad load compatibility. For example, some existing overcurrent protection schemes may trigger when a current limit is exceeded, regardless of any determined characteristics of the semiconductor switch or load.

#### **SUMMARY**

[0006] A load control device for controlling power delivered from an AC power source to an electrical load may have a closed-loop gate drive circuit for controlling a semiconductor switch (e.g., a field-effect transistor) of a controllably conductive device. The controllably conductive device may be adapted to be coupled in series between the AC power source and the electrical load, such that the semiconductor switch may conduct a load current through the electrical load.

[0007] A load control device may further comprise a control circuit that may generate a drive signal for controlling the gate drive circuit. The gate drive circuit may generate a target signal in response to the control circuit. For example, the gate drive circuit may generate a target signal in response the drive signal generated by the control circuit. The gate drive circuit may shape (e.g., wave-shape) the target signal over a period of time, for example, by adjusting a magnitude of the target signal with respect to time over the period of time. The gate drive circuit may receive a first feedback signal that may indicate a magnitude of the load current conducted through the semiconductor switch.

[0008] The gate drive circuit may generate a gate control signal in response to the target signal and the feedback signal. For example, the gate drive circuit may render the semiconductor

switch of the controllably conductive device conductive and non-conductive in response to the gate control signal. The gate drive circuit may adjust a magnitude of the gate control signal in response to a magnitude of the feedback signal to adjust the magnitude of the load current towards a target current indicated by a magnitude of the target signal. For example, the gate drive circuit may monitor the load current through the electrical load and may adjust the magnitude of the gate control signal in response to the magnitude of the feedback signal and adjust the magnitude of the load current towards to the target current indicated by the magnitude of the target signal.

The gate drive circuit may further receive a second feedback signal that may indicate a magnitude of a voltage developed across the semiconductor switch. When rendering the semiconductor switch non-conductive, the gate drive circuit may shape (e.g., wave-shape) over a turn-off period. For example, the gate drive circuit may begin to shape the gate control signal (e.g., at the beginning of the turn-off period) in response to the second feedback signal (e.g., when the magnitude of the second feedback signal exceeds a threshold).

[0010]When rendering the semiconductor switch conductive, the gate drive circuit may shape the target signal over a turn-on period. In examples, the gate drive circuit may increase the target signal to a predetermined level after the turn-on period. When the magnitude of the target signal is at the predetermined level, the gate drive circuit may limit the magnitude of the load current to a maximum level (e.g., a maximum current level) set by the predetermined level. As described herein, the gate drive circuit may limit the magnitude of the load current to the maximum current level while the semiconductor switch is conductive. The gate drive circuit may detect an overcurrent condition when the magnitude of the gate drive signal is at the predetermined level (e.g., which indicates that the magnitude of the load current is at the maximum current level). The gate drive circuit may render the semiconductor switch non-conductive after a trip time period from when the overcurrent condition is detected. The trip time period may be based on a parameter of the semiconductor switch. The parameter of the semiconductor switch may include a temperature across the semiconductor switch, a power of the semiconductor switch, a voltage developed across the semiconductor switch, and/or the like. Alternatively, in some examples, the trip time period may be a fixed value.

## BRIEF DESCRIPTION OF THE DRAWINGS

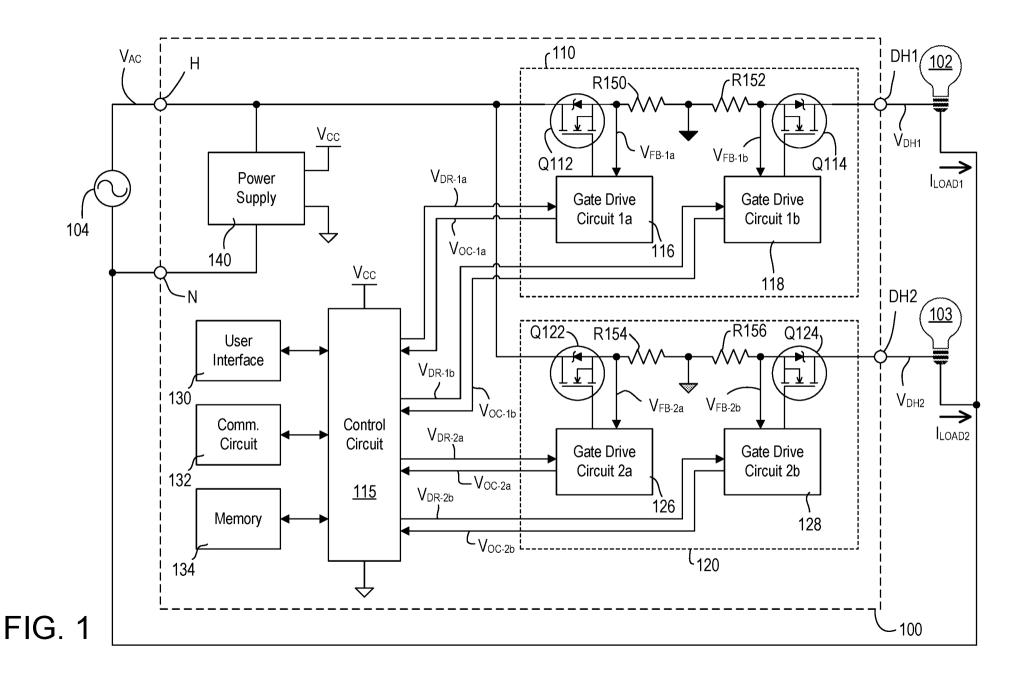

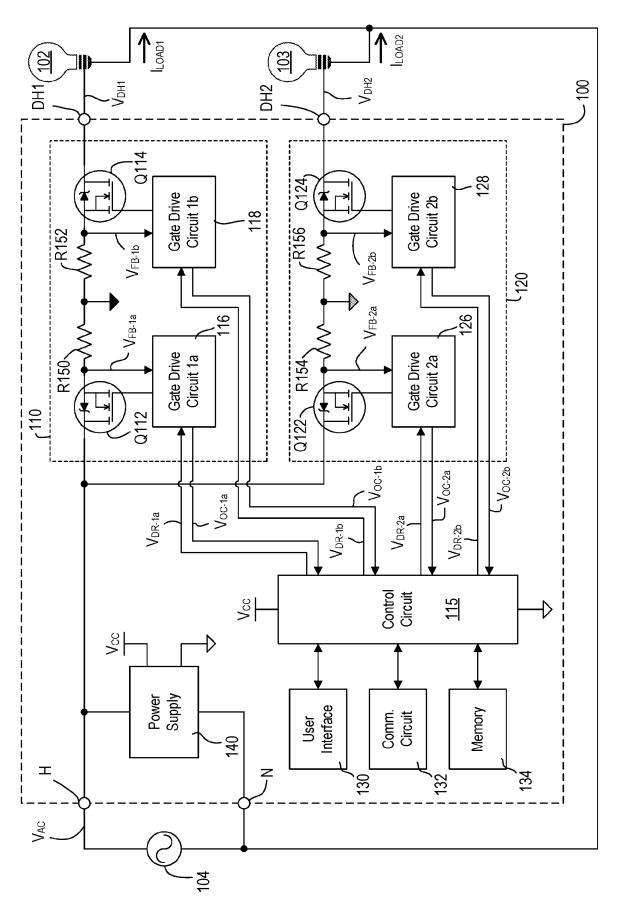

- [0011] FIG. 1 is a block diagram of an example load control device for controlling the amount of power delivered to an electrical load.

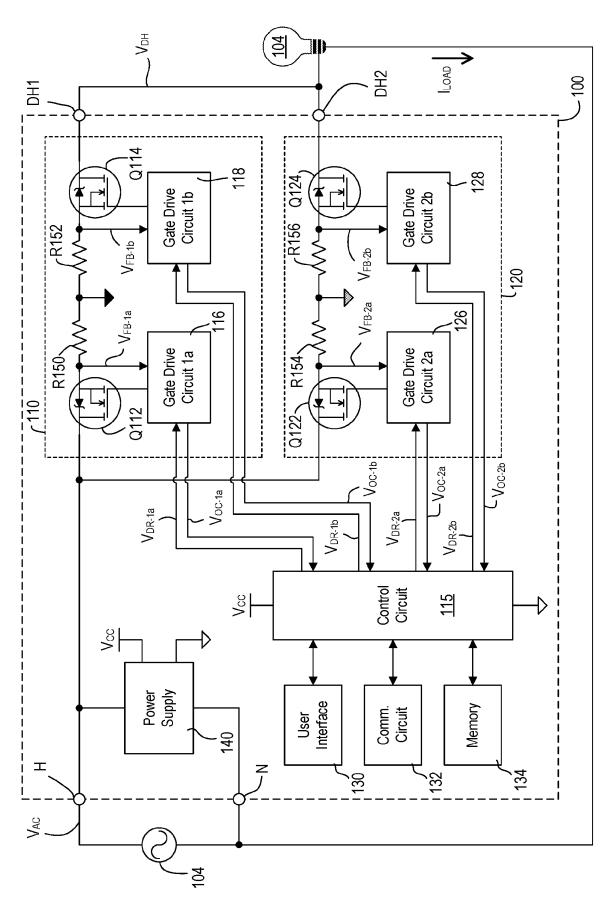

- [0012] FIG. 2 is a block diagram of the load control device of FIG. 1 in an alternate configuration for controlling the amount of power delivered to an electrical load via a parallel output configuration.

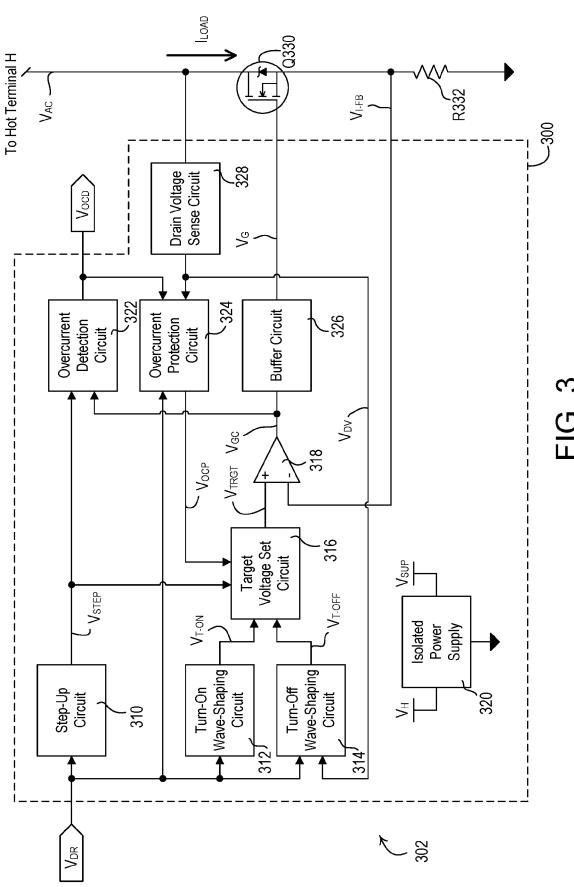

- [0013] FIG. 3 is a block diagram of an example gate drive circuit configured to control the amount of power delivered to an electrical load.

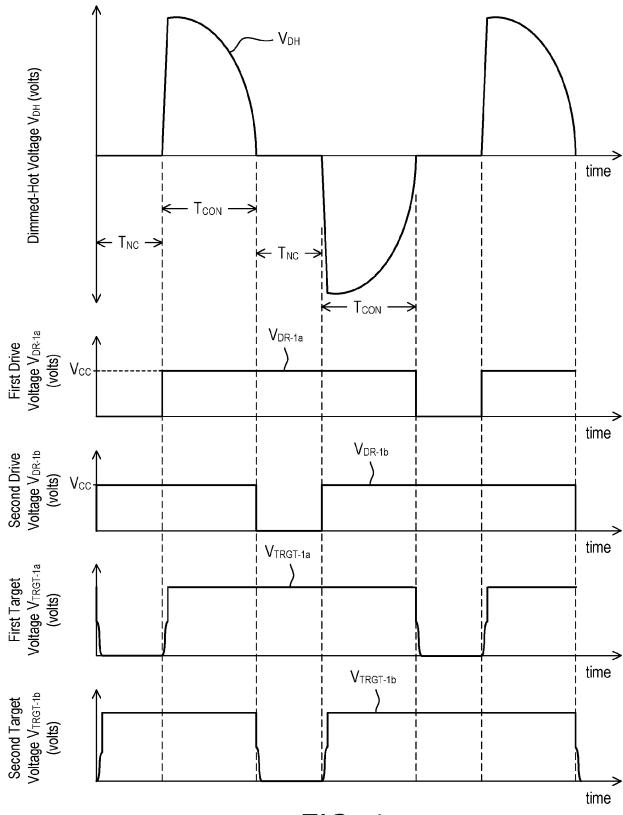

- [0014] FIG. 4 shows examples of waveforms that illustrate an operation of a load control device using a forward phase-control dimming technique.

- [0015] FIG. 5 shows examples of waveforms that illustrate an operation of a load control device using a reverse phase-control dimming technique.

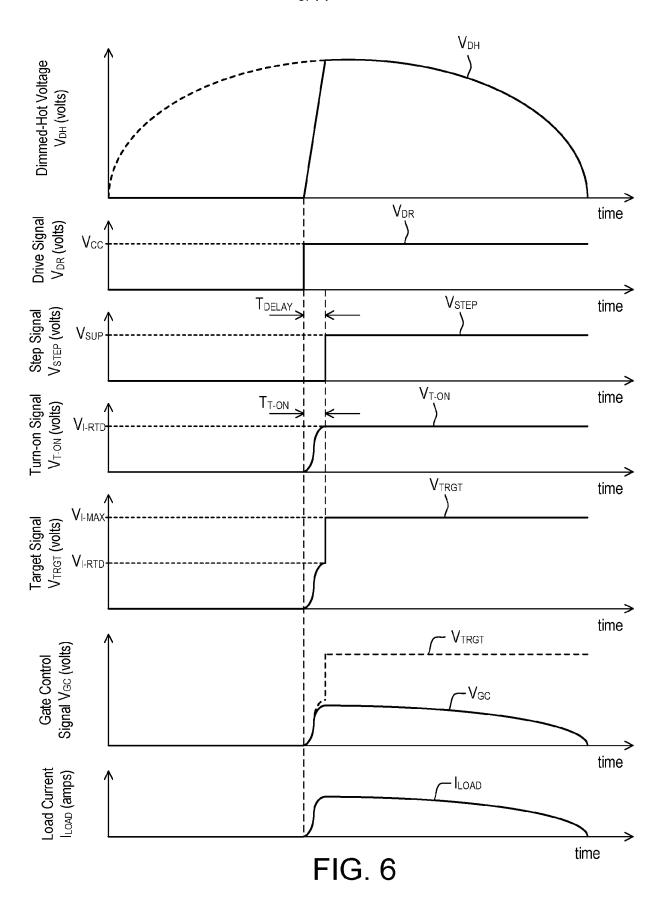

- [0016] FIG. 6 shows examples of waveforms that illustrate an operation of a gate drive circuit to render a semiconductor switch conductive using a forward phase-control dimming technique.

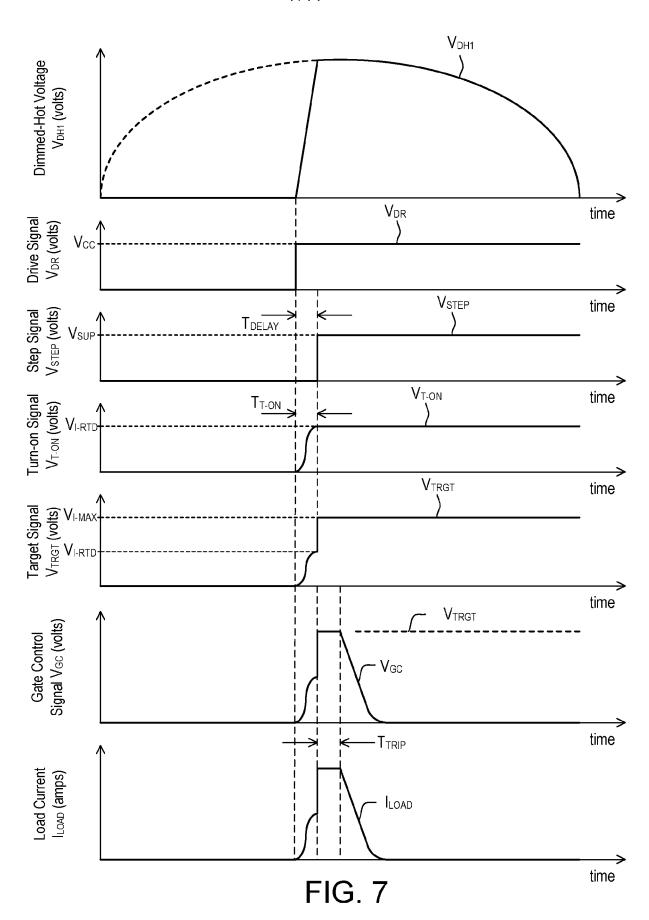

- [0017] FIG. 7 shows examples of waveforms that illustrate an operation of a gate drive circuit to render a semiconductor switch conductive using a forward phase-control dimming technique when the semiconductor switch is experiencing an overcurrent condition.

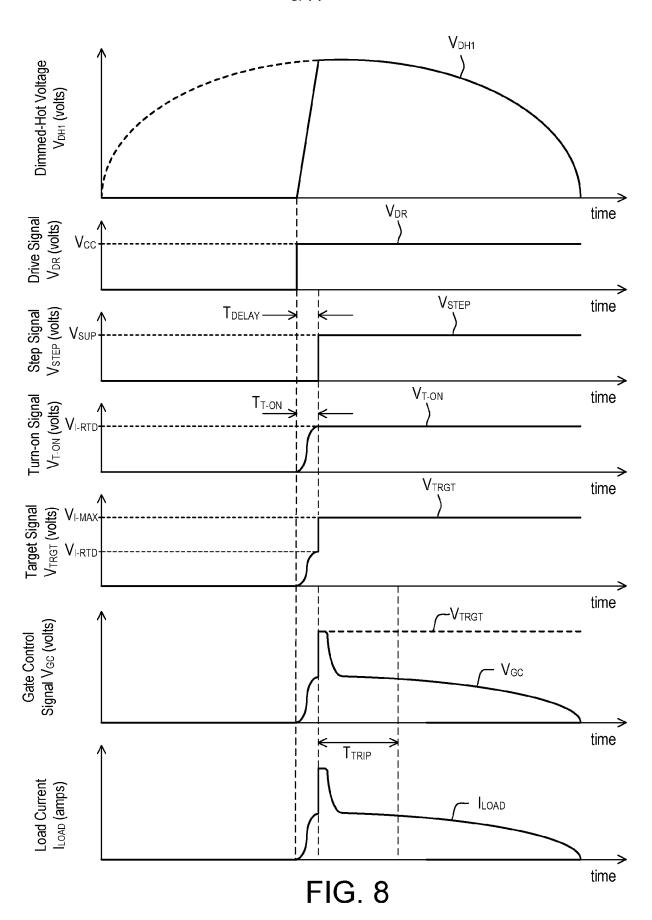

- [0018] FIG. 8 shows examples of waveforms that illustrate an operation of a gate drive circuit to render a semiconductor switch conductive using a forward phase-control dimming technique when the semiconductor switch is experiencing an inrush current condition.

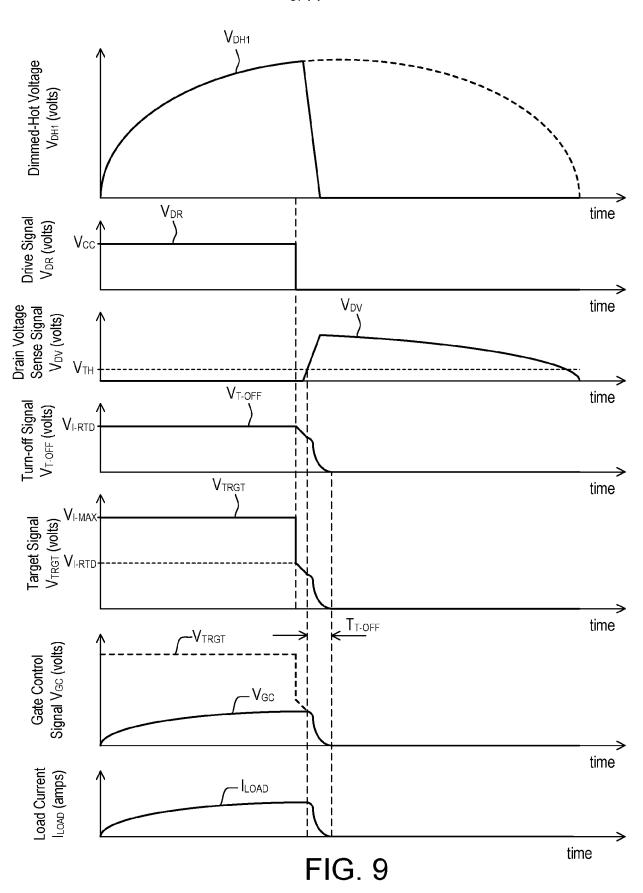

- [0019] FIG. 9 shows examples of waveforms that illustrate an operation of a gate drive circuit to render a semiconductor switch non-conductive using a reverse phase-control dimming technique.

## **DETAILED DESCRIPTION**

[0020] FIG. 1 is a block diagram of an example load control device 100 (e.g., a dimmer switch) for controlling the amount of power delivered from an alternating-current (AC) power source to one or more electrical loads, such as lighting loads 102, 103. The load control device 100 may include a hot terminal H coupled to a hot side of the AC power source 104 for receiving an AC mains line voltage V<sub>AC</sub>, a first dimmed-hot terminal DH1 coupled to the lighting load 102, and a second dimmed-hot terminal DH2 coupled to the lighting load 103. The load control device 100 may also include a neutral terminal N that may be adapted to be coupled to a neutral side of the AC power source 104.

The load control device 100 may comprise a first load control circuit 110 (e.g., a first dimming circuit) and a second load control circuit 120 (e.g., a second dimming circuit). The first load control circuit 110 may comprise a first controllably conductive device having semiconductor switches, such as two field-effect transistors (FETs) Q112, Q114. The FETs Q112, Q114 may be coupled in anti-series connection between the hot terminal H and the dimmed-hot terminal DH1. The junction of the FETs Q112, Q114 may be coupled to circuit common. The first load control circuit 110 may also include a first drive circuit 116 (e.g., a first closed-loop gate drive circuit) for controlling the first FET Q112 and a second drive circuit 118 (e.g., a second closed-loop gate drive circuit) for controlling the second FET Q114. In some alternate examples, the first controllably conductive device of the first load control circuit 110 may comprise a single FET in a full-wave bridge rectifier and the first load control circuit may comprise a single closed-loop gate drive circuit.

The load control device 100 may comprise a control circuit 115, *e.g.*, a digital control circuit, for controlling the first load control circuit 110 to conduct a first load current I<sub>LOAD1</sub> through the first lighting load 102, and for controlling the second load control circuit 120 to conduct a second load current I<sub>LOAD2</sub> through the second lighting load 103. The control circuit 115 may include one or more of a processor (*e.g.*, a microprocessor), a microcontroller, a programmable logic device (PLD), a field programmable gate array (FPGA), an application specific integrated circuit (ASIC), or any suitable controller or processing device. The load control device 100 may include a memory 134 configured to store operational characteristics of the load control device 100. The memory 134 may be implemented as an external integrated circuit (IC) or as an internal circuit of the control circuit

115. The load control device 100 may include a communication circuit 132 configured to transmit and receive messages (*e.g.*, digital messages). The communication circuit 132 may be implemented as an external circuit or as an internal circuit of the control circuit 115.

The load control device 100 may include a user interface 130. The user interface 130 may include one or more actuators (*e.g.*, buttons) for receiving user inputs and/or one or more visual indicators for providing user feedback. For example, the user interface 130 may include a toggle actuator and/or an intensity adjustment actuator (*e.g.*, such as a slider control or a pair of raise and lower buttons) for controlling the lighting loads 102, 103. The control circuit 115 may be configured to control the load control circuits 110, 120 to control the amount of power delivered to the lighting load 102, 103 in response to actuations of the actuators of the user interface 130. In addition, the user interface 130 may also include one or more light-emitting diodes (LEDs) for illuminating the visual indicators, for example, to provide a visual indication of a status and/or a present intensity of a lighting load, and/or a visual indication of a selected preset. For example, the user interface 130 may comprise a vertically-oriented linear array of visual indicators. The control circuit 115 may be coupled to the LEDs for illuminating the visual indicators of the user interface 130 to provide feedback.

The control circuit 115 may generate one or more drive signals. For example, the control circuit 115 may generate first and second drive signals V<sub>DR-1a</sub>, V<sub>DR-1b</sub>, respectively, that may be received by the first and second gate drive circuits 116, 118, respectively, for controlling the FETs Q112, Q114. The drive signals V<sub>DR-1a</sub>, V<sub>DR-1b</sub> may be provided to the first and second gate drive circuits 116, 118 of the first load control circuit 110 for adjusting the magnitude of a first dimmed-hot voltage V<sub>DH1</sub> (*e.g.*, a first load voltage) generated across the lighting load 102 and/or the magnitude of the first load current I<sub>LOAD1</sub> conducted through the lighting load 102, for example, to control the intensity of the lighting load 102 to a target intensity L<sub>TRGT1</sub>, which may range between a high-end intensity L<sub>HE</sub> (*e.g.*, 100%) and a low-end intensity L<sub>LE</sub> (*e.g.*, 0.1-5%). The control circuit 115 may adjust a duty cycle (*e.g.*, an on time) of the drive signals V<sub>DR-1a</sub>, V<sub>DR-1b</sub> to adjust the intensity of the lighting load 102.

[0025] The control circuit 115 may generate the drive signals V<sub>DR-1a</sub>, V<sub>DR-1b</sub> to render the first FET Q112 to be non-conductive to prevent the first load current I<sub>LOAD1</sub> from flowing through

the lighting load 102 during the positive half cycles, and the second FET Q114 to be non-conductive to prevent the first load current I<sub>LOAD1</sub> from flowing through the lighting load 102 during the negative half cycles. When the first controllably conductive device (*e.g.*, the first FET Q112) is rendered conductive during the positive half cycles of the AC power source 104, the first load current I<sub>LOAD1</sub> may be conducted through the drain-source channel of the first FET Q112 and the body diode of the second FET Q114. When the first controllably conductive device (*e.g.*, the second FET Q114) is rendered conductive during the negative half cycles of the AC power source 104, the load current I<sub>LOAD</sub> may be conducted through the drain-source channel of the second FET Q114 and the body diode of the first FET Q112.

The first and the second gate drive circuits 116, 118 may receive the drive signals V<sub>DR-1a</sub>, V<sub>DR-1b</sub> from the control circuit 115 and use the drive signals V<sub>DR-1a</sub>, V<sub>DR-1b</sub> to control the magnitude of the first load current I<sub>LOAD1</sub> conducted through the lighting load 102. For example, the first and second gate drive circuits 116, 118 may generate respective gate control signals in response to the drive signals V<sub>DR-1a</sub>, V<sub>DR-1b</sub>, and provide the respective gate control signals to the gates of the first and second FETs Q112, Q114 to render the FETs Q112, Q114 conductive and non-conductive and control the intensity of the lighting load 102. The gate drive circuits 116, 118 may include a wave-shaping circuit, a target voltage set circuit, an overcurrent protection circuit, an overcurrent detection circuit, and/or the like (*e.g.*, as described herein).

The first load control circuit 110 may include first and second feedback circuits, such as a first sense resistor R150 and a second sense resistor R152, respectively, that generate first and second feedback signals V<sub>FB-1a</sub>, V<sub>FB-1b</sub> indicative of a magnitude of the first load current I<sub>LOAD1</sub> conducted through the FETs Q112, Q114. For example, the first sense resistor R150 may generate a first feedback signal V<sub>FB-1a</sub> that is indicative of a magnitude of the first load current I<sub>LOAD1</sub> conducted through the FET Q112 during the positive half cycles, while the second sense resistor R152 may generate a second feedback signal indicative V<sub>FB-1b</sub> that is indicative of a magnitude of the first load current I<sub>LOAD1</sub> conducted through the FET Q114 during the negative half cycles.

[0028] The first gate drive circuit 116 may receive the first feedback signal  $V_{FB-1a}$  and may generate the first gate control signal for controlling the first FET Q112 in response to the first drive signal  $V_{DR-1a}$  and the first feedback signal  $V_{FB-1a}$ . For example, the first gate drive circuit 116 may

be configured to adjust a magnitude of the first gate control signal in response to a magnitude of the first feedback signal V<sub>FB-1a</sub> to adjust the magnitude of the first load current I<sub>LOAD1</sub> towards a target current indicated by a magnitude of a target signal. Further, in some examples, the first gate drive circuit 116 may generate a shaped (*e.g.*, wave-shaped) target signal based on the drive signal V<sub>DR-1a</sub>, and the first gate drive circuit 116 may generate the first gate control signal for the first FET Q112 in response to the shaped target signal and the first feedback signal V<sub>FB-1a</sub> (*e.g.*, as described herein). For example, the control circuit 115 may be configured to generate the first drive signal V<sub>DR-1a</sub>, and the first gate drive circuit 116 may be configured to shape (*e.g.*, start shaping) the target signal in response to the first drive signal V<sub>DR-1a</sub>.

V<sub>FB-1b</sub> and may generate the second gate control signal for controlling the second FET Q114 in response to the second drive signal V<sub>DR-1b</sub> and the second feedback signal V<sub>FB-1b</sub>. For example, the second gate drive circuit 118 may be configured to adjust a magnitude of the second gate control signal in response to a magnitude of the second feedback signal V<sub>FB-1b</sub> to adjust the magnitude of the first load current I<sub>LOAD1</sub> towards a target current indicated by a magnitude of a target signal. Further, in some examples, the second gate drive circuit 118 may generate a shaped target signal based on the second drive signal V<sub>DR-1b</sub>, and the second gate drive circuit 118 may generate the gate control signal for the second FET Q114 in response to the shaped target signal and the second feedback signal V<sub>FB-1b</sub> (e.g., as described herein). For example, the control circuit 115 may be configured to generate the second drive signal V<sub>DR-1b</sub>, and the second gate drive circuit 118 may be configured to shape (e.g., start shaping) the target signal in response to the second drive signal V<sub>DR-1b</sub>.

The gate drive circuits 116, 118 may generate respective overcurrent detection signals V<sub>OC-1a</sub>, V<sub>OC-1b</sub>, which may be received by the control circuit 115. The gate drive circuits 116, 118 may be configured to detect an overcurrent condition in the respective FETs Q112, Q114 and generate the overcurrent detection signals V<sub>OC-1a</sub>, V<sub>OC-1b</sub> to indicate the overcurrent condition. The control circuit 115 may control the user interface 130 to provide feedback to a user to indicate the overcurrent condition (*e.g.*, by illuminating one or more visual indicators).

[0031] The first load control circuit 110 (*e.g.*, the first and second gate drive circuits 116, 118) may be configured to provide overcurrent protection for the load control device 100. In some

examples, the first and second gate drive circuits 116, 118 may be configured to detect an overcurrent condition in the respective FET Q112, Q114 in response to the respective gate control signal. Further, in some examples, the first gate drive circuit 116 may be configured to limit the magnitude of the first load current ILOAD1 to a maximum current level when the FET Q112 is conductive during the positive half cycles, detect an overcurrent condition when the magnitude of the first load current ILOADI is at the maximum current level, and render the FET Q112 nonconductive after a trip time period from when the overcurrent condition is detected. Similarly, the second gate drive circuit 118 may be configured to limit the magnitude of the first load current ILOAD1 to a maximum current level when the FET Q114 is conductive during the negative half cycles, detect an overcurrent condition when the magnitude of the first load current ILOAD1 is at the maximum current level, and render the FET Q114 non-conductive after a trip time period from when the overcurrent condition is detected. The length of the trip time period may be based on a parameter of the FET Q112, Q114, such as temperature of the semiconductor switch, a measured power of the semiconductor switch, or a drain source voltage of developed across the semiconductor switch. The length of the trip time period may be fixed. Further, in some examples, the gate drive circuits 116, 118 may be configured to render the FET Q112, Q114 non-conductive by driving the magnitude of the respective gate control signals to zero volts.

[0032] The control circuit 115 may also be configured to provide overcurrent protection (*e.g.*, redundant overcurrent protection) for the load control device 100 in response to the overcurrent detection signals Voc-1a, Voc-1b generated by the gate drive circuits 116, 118. For example, the control circuit 115 may be configured to control the drive signals VDR-1a, VDR-1b to render the FETs Q112, Q114 non-conductive when the either of the overcurrent detection signals Voc-1a, Voc-1b indicates an overcurrent condition. If the overcurrent condition persists repeatedly (*e.g.*, for a number of half cycles, such as 10 half cycles in a row), the control circuit 115 may render the FETs Q112, Q114 to turn off the lighting load 102 for a period of time (*e.g.*, a few seconds), and then attempt to turn the lighting load 102 back on.

[0033] The second load control circuit 120 may operate similar to the first load control circuit 110 as described herein. The second load control circuit 120 may comprise a second controllably conductive device having semiconductor switches, such as two field-effect transistors

CA 03140388 2021-11-12

(FETs) Q122, Q124. The FET Q122, Q124 may be coupled in anti-series connection between the hot terminal H and the dimmed-hot terminal DH2. The junction of the FETs Q122, Q124 may be coupled to circuit common. The second load control circuit 120 may also include a first gate drive circuit 126 (*e.g.*, a first closed-loop gate drive circuit) for controlling a first FET Q122, and a second gate drive circuit 128 (*e.g.*, a second closed-loop gate drive circuit) for controlling a second FET Q124. In some alternate examples, the second controllably conductive device of the second load control circuit 120 may comprise a single FET in a full-wave bridge rectifier and the second load control circuit 120 may comprise a single closed-loop gate drive circuit.

The control circuit 115 may control the second load control circuit 120 to conduct the second load current I<sub>LOAD2</sub> through the second lighting load 103. For example, the control circuit 115 may generate first and second drive signals V<sub>DR-2a</sub>, V<sub>DR-2b</sub>, respectively, that may be received by the first and second gate drive circuits 126, 128, respectively, for controlling the FETs Q122, Q124. The drive signals V<sub>DR-2a</sub>, V<sub>DR-2b</sub> may be provided to the first and second gate drive circuits 126, 128 of the second load control circuit 120 for adjusting the magnitude of a second dimmed-hot voltage V<sub>DH2</sub> (*e.g.*, a first load voltage) generated across the lighting load 103 and/or the magnitude of the second load current I<sub>LOAD2</sub> conducted through the lighting load 103, for example, to control the intensity of the lighting load 103 to a target intensity L<sub>TRGT2</sub>, which may range between a high-end intensity L<sub>HE</sub> (*e.g.*, 100%) and a low-end intensity L<sub>LE</sub> (*e.g.*, 0.1-5%). The control circuit 115 may adjust a duty cycle (*e.g.*, an on time) of the drive signals V<sub>DR-2a</sub>, V<sub>DR-2b</sub> to adjust the intensity of the lighting load 103.

The control circuit 115 may generate the drive signals V<sub>DR-2a</sub>, V<sub>DR-2b</sub> to render the first FET Q122 to be non-conductive to prevent the second load current I<sub>LOAD2</sub> from flowing through the lighting load 103 during the positive half cycles, and the second FET Q124 to be non-conductive to prevent the second load current I<sub>LOAD2</sub> from flowing through the lighting load 103 during the negative half cycles. When the second controllably conductive device (*e.g.*, the first FET Q122) is rendered conductive during the positive half cycles of the AC power source 104, the second load current I<sub>LOAD2</sub> may be conducted through the drain-source channel of the first FET Q122 and the body diode of the second FET Q124. When the second controllably conductive device (*e.g.*, the second FET Q124) is rendered conductive during the negative half cycles of the AC power source

104, the second load current I<sub>LOADs</sub> may be conducted through the drain-source channel of the second FET Q124 and the body diode of the first FET Q122.

The first and the second gate drive circuits 126, 128 may receive the drive signals V<sub>DR-2a</sub>, V<sub>DR-2b</sub> from the control circuit 115 and use the drive signals V<sub>DR-2a</sub>, V<sub>DR-2b</sub> to control the magnitude of the second load current I<sub>LOAD2</sub> conducted through lighting load 103. For example, the first and second gate drive circuits 126, 128 may generate respective gate control signals in response to the drive signals V<sub>DR-2a</sub>, V<sub>DR-2b</sub>, and provide the respective gate control signals to the gates of the first and second FETs Q122, Q124 to render the FETs Q122, Q124 conductive and non-conductive and control the intensity of the lighting load 103. The gate drive circuits 126, 128 may include a wave-shaping circuit, a target voltage set circuit, an overcurrent protection circuit, an overcurrent detection circuit, and/or the like (*e.g.*, as described herein).

The second load control circuit 120 may include first and second feedback circuits, such as a first sense resistor R154 and a second sense resistor R156, respectively, that generate first and second feedback signals V<sub>FB-2a</sub>, V<sub>FB-2b</sub> indicative of a magnitude of the second load current I<sub>LOAD2</sub> conducted through the FETs Q122, Q124. For example, the first sense resistor R154 may generate a first feedback signal V<sub>FB-2a</sub> that is indicative of a magnitude of the second load current I<sub>LOAD2</sub> conducted through the FET Q122 during the positive half cycles, while the second sense resistor R156 may generate a second feedback signal indicative V<sub>FB-2b</sub> that is indicative of a magnitude of the second load current I<sub>LOAD2</sub> conducted through the FET Q124 during the negative half cycles.

The first gate drive circuit 126 may receive the first feedback signal V<sub>FB-2a</sub> and may generate a gate control signal for controlling the first FET Q122 in response to the first drive signal V<sub>DR-2a</sub> and the first feedback signal V<sub>FB-2a</sub>. For example, the first gate drive circuit 126 may be configured to adjust a magnitude of the first gate control signal in response to a magnitude of the first feedback signal V<sub>FB-2a</sub> to adjust the magnitude of the second load current I<sub>LOAD2</sub> towards a target current indicated by a magnitude of a target signal. Further, in some examples, the first gate drive circuit 126 may generate a shaped target signal based on the drive signal V<sub>DR-2a</sub>, and the first gate drive circuit 126 may generate the first gate control signal for the first FET Q122 in response to the shaped target signal and the first feedback signal V<sub>FB-2a</sub> (*e.g.*, as described herein). For example, the

control circuit 115 may be configured to generate the first drive signal  $V_{DR-2a}$ , and the first gate drive circuit 126 may be configured to shape (*e.g.*, start shaping) the target signal in response to the first drive signal  $V_{DR-2a}$ .

Similarly, the second gate drive circuit 128 may receive the second feedback signal V<sub>FB-2b</sub> and may generate the second gate control signal for controlling the second FET Q124 in response to the second drive signal V<sub>DR-2b</sub> and the second feedback signal V<sub>FB-2b</sub>. For example, the second gate drive circuit 128 may be configured to adjust a magnitude of the second gate control signal in response to a magnitude of the second feedback signal V<sub>FB-2b</sub> to adjust the magnitude of the second load current I<sub>LOAD2</sub> towards a target current indicated by a magnitude of a target signal. Further, in some examples, the second gate drive circuit 128 may generate a shaped target signal based on the second drive signal V<sub>DR-2b</sub>, and the second gate drive circuit 128 may generate the gate control signal for the second FET Q124 in response to the shaped target signal and the second feedback signal V<sub>FB-2b</sub> (*e.g.*, as described herein). For example, the control circuit 115 may be configured to generate the second drive signal V<sub>DR-2b</sub>, and the second gate drive circuit 128 may be configured to shape (*e.g.*, start shaping) the target signal in response to the second drive signal V<sub>DR-2b</sub>.

The gate drive circuits 126, 128 may generate respective overcurrent signals V<sub>OC-2a</sub>, V<sub>OC-2b</sub>, which may be received by the control circuit 115. The gate drive circuits 126, 128 may be configured to detect an overcurrent condition in the respective FETs Q122, Q124 and generate the overcurrent detection signals V<sub>OC-2a</sub>, V<sub>OC-2b</sub> to indicate the overcurrent condition. The control circuit 115 may control the user interface 130 to provide feedback to a user to indicate the overcurrent condition (*e.g.*, by illuminating one or more visual indicators).

[0041] The second load control circuit 120 (*e.g.*, the first and second gate drive circuits 126, 128) may be configured to provide overcurrent protection for the load control device 100. In some examples, the first and second gate drive circuits 126, 128 may be configured to detect an overcurrent condition in the semiconductor switch Q122, Q124 in response to their respective gate control signals. Further, in some examples, the first gate drive circuit 126 may be configured to limit the magnitude of the second load current I<sub>LOAD2</sub> to a maximum current level when the semiconductor switch Q122 is conductive during the positive half cycles, detect an overcurrent condition when the

magnitude of the second load current I<sub>LOAD2</sub> is at the maximum current level, and render the semiconductor switch Q122 non-conductive after a trip time period from when the overcurrent condition is detected. Similarly, the second gate drive circuit 128 may be configured to limit the magnitude of the second load current I<sub>LOAD2</sub> to a maximum current level when the semiconductor switch Q124 is conductive during the negative half cycles, detect an overcurrent condition when the magnitude of the second load current I<sub>LOAD2</sub> is at the maximum current level, and render the semiconductor switch Q124 non-conductive after a trip time period from when the overcurrent condition is detected. The length of the trip time period may be based on a parameter of the semiconductor switch Q122, Q124, such as temperature of the semiconductor switch, a measured power of the semiconductor switch, or a drain source voltage of developed across the semiconductor switch. Further, in some examples, the gate drive circuits 126, 128 may be configured to render the semiconductor switches Q122, Q124 non-conductive by driving the magnitude of the respective gate control signals to zero volts.

[0042] The control circuit 115 may also be configured to provide overcurrent protection (*e.g.*, redundant overcurrent protection) for the load control device 100 in response to the overcurrent detection signals Voc-2a, Voc-2b generated by the gate drive circuits 126, 128. For example, the control circuit 115 may be configured to control the drive signals V<sub>DR-2a</sub>, V<sub>DR-2b</sub> to render the FETs Q122, Q124 non-conductive when the either of the overcurrent detection signals Voc-2a, Voc-2b indicates an overcurrent condition. If the overcurrent condition persists repeatedly (*e.g.*, for a number of half cycles, such as 10 half cycles in a row), the control circuit 115 may render the FETs Q122, Q124 to turn off the lighting load 103 for a period of time (*e.g.*, a few seconds), and then attempt to turn the lighting load 103 back on.

The load control device 100 may include a power supply 140. The power supply 140 may receive the AC mains line voltage V<sub>AC</sub> and may generate a direct-current (DC) supply voltage V<sub>CC</sub> (*e.g.*, approximately 3.3V). For example, the power supply 140 may power the control circuit 115 and/or other low-voltage circuits of the load control device 100. Each of the first and second load control circuits 110, 120 may comprise a respective power supply (not shown) configured to generate respective supply voltages (*e.g.*, approximately 15V) for driving the respective

semiconductor switches Q112, Q114, Q122, Q124 (e.g., as will be described in greater detail below with reference to FIG. 3).

[0044] The control circuit 115 may be configured to determine times of zero-crossing points of the AC mains line voltage V<sub>AC</sub> of the AC power source 104. For example, the load control device 100 may comprise a zero-crossing detect circuit (not shown) that may be coupled to the hot terminal H and the neutral terminal N, and generates a zero-cross signal that indicates the zero-crossing points of the AC mains line voltage VAC. The control circuit 115 may then render the semiconductor switches Q112, Q114, Q122, Q124 conductive and/or non-conductive at predetermined times (e.g., at a firing time or firing angle) relative to the zero-crossing points of the AC mains line voltage V<sub>AC</sub> (e.g., as determined from the zero-cross signal) to generate a phasecontrol dimmed-hot voltage V<sub>PC</sub> using a phase-control dimming technique (e.g., a forward phasecontrol dimming technique and/or a reverse phase-control dimming technique). For example, the control circuit 115 may use the forward phase-control dimming technique to control inductive loads and may use the reverse phase-control dimming technique to control capacitive loads. Examples of dimmers are described in greater detail in commonly-assigned U.S. Patent No. 7,242,150, issued July 10, 2007, entitled DIMMER HAVING A POWER SUPPLY MONITORING CIRCUIT; U.S. Patent No. 7,546,473, issued June 9, 2009, entitled DIMMER HAVING A MICROPROCESSOR-CONTROLLED POWER SUPPLY; and U.S. Patent No. 8,664,881, issued March 4, 2014, entitled TWO-WIRE DIMMER SWITCH FOR LOW-POWER LOADS, the entire disclosures of which are incorporated by reference herein.

The control circuit 115 may be configured to adjust a firing time (*e.g.*, a phase angle) of the controllably conductive devices of the load control circuits 110, 120 each half cycle to control the amount of power delivered to the lighting load 102, 103 and to control the intensity of the lighting loads 102, 103 toward respective target intensities. The control circuit 115 may be configured to control the semiconductor switches Q112, Q114, Q122, Q124 using the forward phase-control dimming technique and/or the reverse phase-control dimming technique. When using the forward phase-control dimming technique, the control circuit 115 may render one or more of the semiconductor switches Q112, Q114, Q122, Q124 non-conductive (*e.g.*, to cause the controllably conductive devices 110, 120 to be non-conductive) at the beginning of each half cycle of the AC

CA 03140388 2021-11-12

mains line voltage, and then render one or more of the semiconductor switches Q112, Q114, Q122, Q124 conductive (*e.g.*, to cause the controllably conductive devices 110, 120 to be conductive) at a firing time during the half cycle after which the controllably conductive devices 110, 120 may remain conductive until the end of the half cycle. When using the reverse phase-control dimming technique, the control circuit 115 may render one or more of the semiconductor switches Q112, Q114, Q122, Q124 conductive (*e.g.*, to cause the controllably conductive devices 110, 120 to be conductive) at the beginning of each half cycle of the AC mains line voltage, and then render one or more of the semiconductor switches Q112, Q114, Q122, Q124 non-conductive (*e.g.*, to cause the controllably conductive devices 110, 120 to be non-conductive) at a firing time during the half cycle after which the controllably conductive devices 110, 120 may remain non-conductive until the end of the half cycle.

[0046] FIG. 2 is a block diagram of the load control device 100 in an alternate configuration. The first and second dimmed-hot terminals DH1, DH2 may be coupled together to a single lighting load 104. For example, the lighting load 104 may having a high power rating than the lighting loads 102, 104 of FIG. 1, and may conduct a load current ILOAD having a higher magnitude through the load control device 100. Because the first and second dimmed-hot terminals DH1, DH2 are coupled together, the first controllably conductive device of the first load control circuit 110 and the second controllably conductive device of the second load control circuit 120 may be electrically coupled in parallel with each other, and may each conduct at least a portion of the load current ILOAD through the lighting load 104. The control circuit 115 may control the first controllably conductive device 110 and the second controllably conductive device 120 together to control the lighting load 104. For example, the control circuit 115 may generate the first drive signals V<sub>DR-1a</sub>, V<sub>DR-2a</sub>, such that the first drive signals V<sub>DR-1a</sub>, V<sub>DR-2a</sub> are the same, for example, having the same duty cycles and in phase with each other (e.g., synchronized to the AC mains line voltage V<sub>AC</sub>). In addition, the control circuit 115 may generate the second drive signals V<sub>DR-1b</sub>, V<sub>DR-2b</sub>, such that the second drive signals V<sub>DR-1b</sub>, V<sub>DR-2b</sub> are also the same, for example, having the same duty cycles and in phase with each other (e.g., synchronized to the AC mains line voltage V<sub>AC</sub>). Because the first and second controllably conductive devices are coupled in parallel with each other and share the load current ILOAD, the load control device may be able to control lighting loads having a higher power rating

than when the lighting loads are coupled individually coupled to the load control circuits 110, 120 as shown in FIG. 1.

FIG. 3 is a block diagram of an example gate drive circuit 300 of a load control circuit 302 of a load control device, such as the gate drive circuits 116, 118, 126, 128 shown in FIGs. 1 and 2. As described herein, the gate drive circuit 300 may monitor a load current ILOAD conducted through an electrical load, such as a lighting load (*e.g.*, lighting loads 102, 103, 104 shown in FIGs. 1 and 2), and may generate a signal (*e.g.*, a gate control signal V<sub>GC</sub>) to control a semiconductor switch, such as a FET Q330 (*e.g.*, FETs Q112, Q114, Q122, Q124 shown in FIGs. 1 and 2), to control the amount of power delivered to an electrical load.

The gate drive circuit 300 may receive a signal, such as a drive signal V<sub>DR</sub> from a control circuit (*e.g.*, such as the drive signals V<sub>DR-1a</sub>, V<sub>DR-1b</sub>, V<sub>DR-2a</sub>, V<sub>DR-2b</sub> generated by the control circuit 115 shown in FIG. 1 or the control circuit 215 shown in FIG. 2). The gate drive circuit 300 may be configured to render the FET Q330 conductive and non-conductive in response to the drive signal V<sub>DR</sub>. The gate drive circuit 300 may generate a target signal V<sub>TRGT</sub> in response to the drive signal V<sub>DR</sub> received from the control circuit. The target signal V<sub>TRGT</sub> may be shaped, *e.g.*, having a magnitude that adjusts with respect to time over a period of time. The period of time may be a preconfigured period of time and may allow the gate drive circuit 300 to have smooth turn-on and/or turn-off transitions. The gate drive circuit 300 may generate the target signal V<sub>TRGT</sub> (*e.g.*, using a turn-on signal V<sub>T-ON</sub>, a turn-off signal V<sub>T-OFF</sub>, etc.) by adjusting a magnitude of the target signal V<sub>TRGT</sub> over the period of time, for example, as described herein.

The gate drive circuit 300 may receive a feedback signal V<sub>I-FB</sub> that may have a magnitude that indicates a magnitude of the load current I<sub>LOAD</sub> conducted through the FET Q330 (*e.g.*, and conducted through the electrical load). For example, the load control circuit 302 may include a feedback circuit, such as a sense resistor R332, that generates the feedback signal V<sub>I-FB</sub>. The sense resistor R332 may be coupled between the FET Q330 and circuit common, and may conduct the load current I<sub>LOAD</sub>. The feedback signal V<sub>I-FB</sub> may be generate across the sense resistor R332 and may be referenced to as circuit common of the gate drive circuit 300. The magnitude of the feedback signal V<sub>I-FB</sub> (*e.g.*, the voltage generated across the sense resistor R332) may be proportional to the magnitude of the load current I<sub>LOAD</sub> conducted through the FET Q330 (*e.g.*,

dependent upon a resistance of the sense resistor R332). The gate drive circuit 300 may generate the gate control signal V<sub>GC</sub> in response to the target signal V<sub>TRGT</sub> and the feedback signal V<sub>I-FB</sub>. When the FET Q330 is conductive, the gate drive circuit 300 may control the FET Q330 in the linear region to adjust an impedance (*e.g.*, a drain-source impedance) of the FET Q330 based on the gate control signal V<sub>GC</sub>. The gate drive circuit 300 may control the FET Q330 to adjust the impedance of the FET Q330 in response to the feedback signal V<sub>I-FB</sub> to control the magnitude of the load current I<sub>LOAD</sub> towards the target signal V<sub>TRGT</sub>.

[0050] The gate drive circuit 300 may comprise a step-up circuit 310, a turn-on wave-shaping circuit 312, and a turn-off wave-shaping circuit 314. The step-up circuit 310, the turn-on wave-shaping circuit 312, and/or the turn-off wave-shaping circuit 314 may receive the drive signal V<sub>DR</sub> from the control circuit. In addition, the drive signal V<sub>DR</sub> may be coupled to the step-up circuit 310, the turn-on wave-shaping circuit 312, and/or the turn-off wave-shaping circuit 314 via an optocoupler (not shown), such that the control circuit is electrically isolated from the gate drive circuit 300.

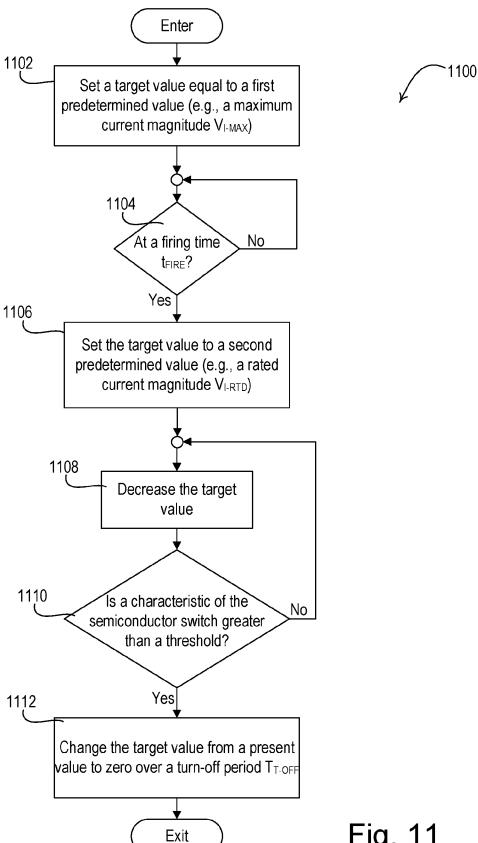

[0051] The turn-on wave-shaping circuit 312 may receive the drive signal V<sub>DR</sub> from the control circuit and may generate a turn-on signal V<sub>T-ON</sub>. For example, the turn-on wave-shaping circuit 312 may shape (e.g., wave-shape) the turn-on signal V<sub>T-ON</sub> during a turn-on period T<sub>T-ON</sub> (e.g., approximately 50 μsec). The turn-on wave-shaping circuit 312 may shape (e.g., begin shaping) the turn-on signal V<sub>T-ON</sub> at a time during the turn-on period T<sub>T-ON</sub> (e.g., at the beginning time of the turn-on period T<sub>T-ON</sub>). The turn-on wave-shaping circuit 312 may provide the turn-on signal V<sub>T-ON</sub> to a target voltage set circuit 316, which may use the turn-on signal V<sub>T-ON</sub> to generate the target signal V<sub>TRGT</sub>. The turn-on wave-shaping circuit 312 may shape the turn-on signal V<sub>T-ON</sub> with a preconfigured shape, such as an S-shape. For example, the turn-on wave-shaping circuit 312 may wave-shape the turn-on signal V<sub>T-ON</sub> with a first shape during a first portion of the turn-on period T<sub>T-ON</sub> and wave-shape the turn-on signal V<sub>T-ON</sub> with a second shape during a second portion of the turn-on period T<sub>T-ON</sub> so that the target signal V<sub>TRGT</sub> has a preconfigured shape, such as an Sshape. Although illustrated as an S-shape, the turn-on wave-shaping circuit 312 may shape the turnon signal V<sub>T-ON</sub> with any shape (e.g., such as a ramp). The turn-on wave-shaping circuit 312 may control the magnitude of the turn-on signal V<sub>T-ON</sub> to a rated current magnitude V<sub>I-RTD</sub> (e.g., a rated

current value) at the end of the turn-on period  $T_{T-ON}$ . For example, the rated current magnitude  $V_{I-RTD}$  may be approximately 7.5 volts.

The step-up circuit 310 may receive the drive signal V<sub>DR</sub> from the control circuit and provide a step signal V<sub>STEP</sub> to the target voltage set circuit 316, which may use the step signal V<sub>STEP</sub> to generate the target signal V<sub>TRGT</sub>. For example, the step signal V<sub>STEP</sub> may be similar to the drive signal V<sub>DR</sub> received from the control circuit. The step-up circuit 310 may drive the magnitude of the step signal V<sub>STEP</sub> high (*e.g.*, towards the isolated supply voltage V<sub>SUP</sub>) after a delay period T<sub>DELAY</sub> after the drive signal V<sub>DR</sub> is driven high (*e.g.*, towards the DC supply voltage V<sub>CC</sub>).

The gate drive circuit 300 may also include a drain voltage sense circuit 328 that is coupled to the FET Q330 (*e.g.*, to the drain of the FET Q330). The drain voltage sense circuit 328 may detect a magnitude of a voltage developed across the FET Q330. The drain voltage sense circuit 328 may provide a second feedback signal (*e.g.*, a drain voltage sense signal V<sub>DV</sub>) to the turn-off wave-shaping circuit 314. The drain voltage signal V<sub>DV</sub> may indicate the magnitude of the voltage across the FET Q330.

[0054] The turn-off wave-shaping circuit 314 may receive the drive signal V<sub>DR</sub> from the control circuit and the drain voltage signal V<sub>DV</sub> from the drain voltage sense circuit 328. The turnoff wave-shaping circuit 314 may generate a turn-off signal V<sub>T-OFF</sub> in response to the drive signal V<sub>DR</sub> and the drain voltage signal V<sub>DV</sub>. For example, the turn-off wave-shaping circuit 314 may shape the turn-off signal V<sub>T-OFF</sub> over a period of time, such as during a turn-off period T<sub>T-OFF</sub>, to generate the turn-off signal V<sub>T-OFF</sub>. The turn-off wave-shaping circuit 314 may shape the turn-off signal V<sub>T-OFF</sub> in response to receiving the drain voltage signal V<sub>DV</sub> from the drain voltage sense circuit 328. For example, upon receiving the drain voltage signal V<sub>DV</sub>, the turn-off wave-shaping circuit 314 may shape (e.g., begin to shape) the turn-off signal V<sub>T-OFF</sub>. The turn-off wave-shaping circuit 314 may provide the turn-off signal V<sub>T-OFF</sub> to a target voltage set circuit 316, which may use the turn-off signal V<sub>T-OFF</sub> to generate the target signal V<sub>TRGT</sub>. The turn-off wave-shaping circuit 314 may shape the turn-off signal V<sub>T-OFF</sub> with a preconfigured shape, such as a S-shape, so that the turnoff signal V<sub>T-OFF</sub> also has the preconfigured shape. For example, the turn-off wave-shaping circuit 314 may shape the turn-off signal V<sub>T-OFF</sub> with a first shape during a first portion of the turn-off period T<sub>T-OFF</sub>, and may shape the turn-off signal V<sub>T-OFF</sub> with a second shape during a second portion

of the turn-off period  $T_{T-OFF}$  so that the target signal  $V_{TRGT}$  has a preconfigured shape, such as an S-shape. Although illustrated as an S-shape, the turn-off wave-shaping circuit 315 may shape the turn-off signal  $V_{T-OFF}$  with any shape (e.g., such as a ramp).

The target voltage set circuit 316 may receive the turn-on signal V<sub>T-ON</sub> from the turn-on wave-shaping circuit 312, the turn-off signal V<sub>T-OFF</sub> from the turn-off wave-shaping circuit 314, and/or the step signal V<sub>STEP</sub> from the step-up circuit 310. For example, the target voltage set circuit 316 may act as a combining circuit and combine one or more of the turn-on signal V<sub>T-ON</sub> from the turn-on wave-shaping circuit 312, the turn-off signal V<sub>T-OFF</sub> from the turn-off wave-shaping circuit 314, and/or the step signal V<sub>STEP</sub> from the step-up circuit 310 to generate the target signal V<sub>TRGT</sub>. The target signal V<sub>TRGT</sub> may be used to control the FET Q330.

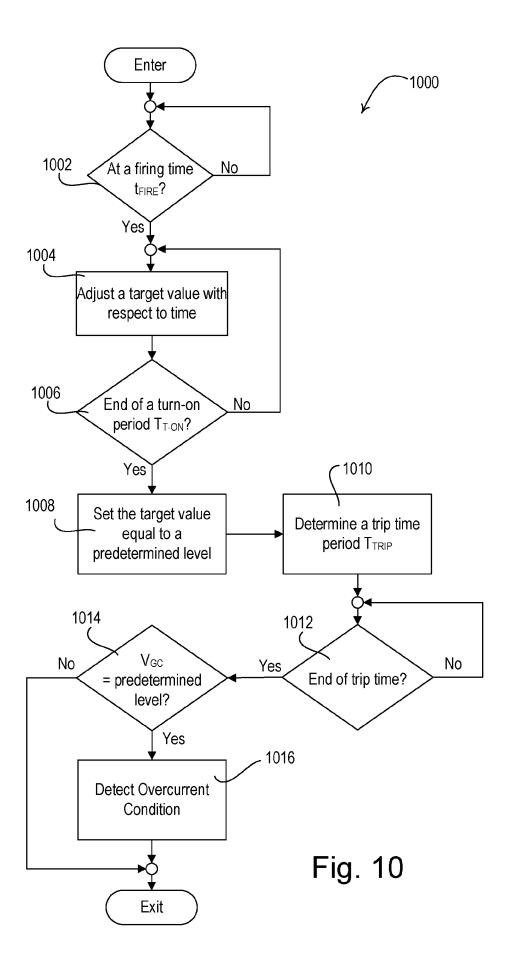

When rendering the FET Q330 conductive, the control circuit may be configured to drive the drive signal V<sub>DR</sub> high (*e.g.*, towards the DC supply voltage V<sub>CC</sub>) to generate a rising edge in the drive signal V<sub>DR</sub>. In response to the rising edge of the drive signal V<sub>DR</sub>, the target voltage set circuit 316 may set the target voltage V<sub>TRGT</sub> to be equal to the turn-on signal V<sub>T-ON</sub> during the turn-on period T<sub>T-ON</sub>. As noted above, the turn-on signal V<sub>T-ON</sub> may be shaped. The target voltage set circuit 316 may set the magnitude of the target voltage V<sub>TRGT</sub> to be equal to the rated current magnitude V<sub>I-RTD</sub> at the end of the turn-on period T<sub>T-ON</sub>. When the magnitude of the target signal V<sub>TRGT</sub> is equal to the rated current magnitude V<sub>I-RTD</sub> at the end of the turn-on period T<sub>T-ON</sub>, the gate drive circuit 300 may attempt to control the magnitude of the load current I<sub>LOAD</sub> to a maximum rated current I<sub>RATED</sub> (*e.g.*, approximately 10A).

After the delay period T<sub>DELAY</sub>, the target voltage set circuit 316 may set the target signal V<sub>TRGT</sub> to be equal to a maximum current magnitude V<sub>I-MAX</sub> (*e.g.*, a maximum current value) in response to the step signal V<sub>STEP</sub> (*e.g.*, to be equal to the magnitude of the step signal V<sub>STEP</sub>). For example, the maximum current magnitude V<sub>I-MAX</sub> may be approximately 15 volts). The delay period T<sub>DELAY</sub> may be approximately equal to (*e.g.*, equal to) the turn-on period T<sub>T-ON</sub>, such that the target voltage signal T<sub>TRGT</sub> is set to the magnitude of the step signal V<sub>STEP</sub> after the turn-on period T<sub>T-ON</sub>. When the magnitude of the target signal V<sub>TRGT</sub> is equal to the maximum current magnitude V<sub>I-MAX</sub> after the turn-on period T<sub>T-ON</sub>, the gate drive circuit 300 may attempt to control the magnitude of the load current I<sub>LOAD</sub> to a maximum current level I<sub>MAX</sub> (*e.g.*, approximately 20A).

[0058] When rendering the FET Q330 non-conductive, the control circuit may be configured to drive the drive signal  $V_{DR}$  low (e.g., to approximately circuit common) to generate a falling edge in the drive signal V<sub>DR</sub>. In response to the falling edge of the drive signal V<sub>DR</sub>, the gate drive circuit 300 may be configured to decrease (e.g., start decreasing) the magnitude of the target voltage V<sub>TRGT</sub> with respect to time. More specifically, when turning-off, the target voltage set circuit 316 may set the target voltage V<sub>TRGT</sub> to be equal to the turn-off signal V<sub>T-OFF</sub>. For example, the turn-off waveshaping circuit 314 may set the magnitude of the turn-off signal V<sub>T-OFF</sub> to a predetermined value, e.g., approximately the rated current magnitude V<sub>I-RTD</sub>, which may be approximately 50% of the maximum current magnitude V<sub>I-MAX</sub> (e.g., from approximately 15V to 7.5V). Thereafter, the turnoff wave-shaping circuit 314 may gradually decrease the magnitude of the turn-off signal V<sub>T-OFF</sub> until the turn-off wave-shaping circuit 314 the drain voltage signal V<sub>DV</sub> from the drain voltage sense circuit 328 indicates that the voltage across the FET 330 is starting to rise (e.g., has exceeding a drain voltage threshold V<sub>TH</sub> indicating that the FET is starting to become non-conductive). Once the magnitude of the voltage developed across the FET Q330 as indicated by the drain voltage signal V<sub>DV</sub> exceeds the drain voltage threshold V<sub>TH</sub>, the turn-off wave-shaping circuit 314 may begin to shape the turn-off signal V<sub>T-OFF</sub> from the present magnitude (e.g., the magnitude at the time the drain voltage signal V<sub>DV</sub> indicates that the magnitude of the voltage across the FET 330 has exceeded the drain voltage threshold V<sub>TH</sub>) to zero volts. The target voltage set circuit 316 may set the target voltage V<sub>TRGT</sub> to be equal to the turn-off signal V<sub>T-OFF</sub>.

The gate drive circuit 300 may include an operational amplifier circuit 318. The operational amplifier circuit 318 may having a non-inverting input configured to receive the target signal V<sub>TRGT</sub> from the target voltage set circuit 316 and an inverting input configured to receive the feedback signal V<sub>I-FB</sub> from the sense resistor R332. The operational amplifier circuit 318 may generate the gate control signal V<sub>GC</sub> at an output based on the target signal V<sub>TRGT</sub> and the feedback signal V<sub>I-FB</sub>. For example, the operational amplifier circuit 318 may adjust the gate control signal V<sub>GC</sub> to control the FET Q330 and thus control the magnitude of the load current I<sub>LOAD</sub> towards a target current indicated by the magnitude of the target signal V<sub>TRGT</sub>. The operational amplifier circuit 318 may be referenced to circuit common of the gate drive circuit 300 (*e.g.*, to which the feedback signal V<sub>I-FB</sub> is referenced). As previously mentioned, the magnitude of the feedback signal V<sub>I-FB</sub> may be proportional to the magnitude of the load current I<sub>LOAD</sub>. Accordingly, the operational

amplifier circuit 318 may control the magnitude of the gate control signal V<sub>GC</sub> in response to the magnitude of the load current I<sub>LOAD</sub>. Some lighting loads, such as LED light sources, may be capacitive loads, which may cause changes in a load voltage (*e.g.*, a dimmed-hot voltage) across the lighting load that are not representative of the magnitude of the load current I<sub>LOAD</sub> (*e.g.*, proportional to the magnitude of the load current I<sub>LOAD</sub>). Since both the sense resistor R332 and the operational amplifier circuit 318 are referenced to circuit common, the operational amplifier circuit 318 may be responsive to (*e.g.*, only responsive to) the magnitude of the load current I<sub>LOAD</sub> and not influenced by the magnitude of the load voltage across the lighting load.

[0060] The gate drive circuit 300 may include a buffer circuit 326. The buffer circuit 326 may be coupled in series between the output of the operational amplifier circuit 318 and the gate of the FET Q330. The buffer circuit 326 may receive the control signal V<sub>GC</sub> from the voltage amplifier circuit 318 and may buffer the control signal V<sub>GC</sub> to generate a gate voltage V<sub>G</sub>. The gate signal V<sub>G</sub> may control conductivity of the FET Q330. For example, the gate signal V<sub>G</sub>, via the gate control signal V<sub>GC</sub>, may render the FET Q330 conductive and non-conductive. In some examples, the gate drive circuit 300 may not include the buffer circuit 326.

The gate drive circuit may include an overcurrent detection circuit 322 and an overcurrent protection circuit 324. The overcurrent detection circuit 322 may detect an overcurrent condition. For example, the overcurrent detection circuit 322 may detect the overcurrent condition when the load current I<sub>LOAD</sub> (*e.g.*, the magnitude of the load current) conducted through the FET Q330 (*e.g.*, and through the electrical load) reaches the maximum current level I<sub>MAX</sub>. Since the magnitude of the gate control signal V<sub>GC</sub> indicates the desired magnitude of the load current I<sub>LOAD</sub>, the overcurrent detection circuit 322 may receive the gate control signal V<sub>GC</sub> and may determine whether an overcurrent condition is occurring in response to the magnitude of the gate control signal V<sub>GC</sub>. The overcurrent detection circuit 322 may receive the step up signal V<sub>STEP</sub> and may begin to monitor for the overcurrent condition in response to the step up signal V<sub>STEP</sub> (*e.g.*, after the step up signal V<sub>STEP</sub> is driven high when rendering the FET Q330 conductive). For example, the overcurrent detection circuit 322 may determine that an overcurrent condition has occurred when the gate control signal V<sub>GC</sub> is at the maximum current magnitude V<sub>I-MAX</sub> for a predetermined period of time.

[0062] The overcurrent detection circuit 322 may generate a signal (*e.g.*, an overcurrent detection signal Vocd) that may be received by the control circuit. When the overcurrent detection circuit 322 detects an overcurrent condition, the overcurrent detection circuit 322 may drive the magnitude of the overcurrent detect signal Vocd high to indicate the overcurrent condition to the control circuit. For example, the overcurrent detection signal Vocd may be coupled to the control circuit via an optocoupler (not shown). The control circuit may use the overcurrent detect signal Vocd to provide feedback to a user regarding the overcurrent condition. For example, the load control device 100 of FIG. 1 may provide feedback to the user about the overcurrent condition via the user interface 130.

[0063] The overcurrent protection circuit 324 may receive the overcurrent detect signal Vocd from the overcurrent detection circuit 322, the drain voltage signal V<sub>DV</sub> from the drain voltage sense circuit 328, and the drive signal V<sub>DR</sub> from the control circuit. The overcurrent protection circuit 324 may control the voltage amplifier circuit 318 to render the FET Q330 non-conductive after a trip time period TTRIP from when the overcurrent condition is detected (e.g., from when the overcurrent detect signal V<sub>OCD</sub> is driven high by the overcurrent protection circuit 324). For example, the overcurrent protection circuit 324 may generate an overcurrent protection signal V<sub>OCP</sub> that may be received by the target voltage set circuit 316. When the overcurrent protection circuit 324 detects that the magnitude of the gate control signal V<sub>GC</sub> is at the maximum current magnitude V<sub>I-MAX</sub> for a trip time period Ttrip after the overcurrent condition is detected, the overcurrent protection circuit 324 may control the overcurrent protection signal V<sub>OCP</sub> to render the FET Q330 non-conductive. The overcurrent protection circuit 324 may render the FET Q330 non-conductive by controlling the target voltage set circuit 316 to set the magnitude of the target voltage V<sub>TRGT</sub> to zero volts to cause the operational amplifier circuit 318 to drive the magnitude of the gate control signal V<sub>GC</sub> to zero volts when the overcurrent condition is detected. After the overcurrent protection circuit 324 has caused the operational amplifier circuit 318 to drive the magnitude of the gate control signal V<sub>GC</sub> to zero volts, the overcurrent protection circuit 324 may remain latched in the overcurrent state. The overcurrent protection circuit 324 may be reset from being latched in the overcurrent state in response to the drive signal V<sub>DR</sub> (e.g., when the drive signal V<sub>DR</sub> is driven low to render the FET Q330 non-conductive).

The overcurrent protection circuit 324 may determine the length of the trip time period based on a parameter of the FET Q330. The length of the trip time period may be associated with a safe operating area of the FET Q330. For example, the parameter of the FET Q330 may include a temperature of the FET, a power dissipation of the FET, a voltage developed across the FET, and/or the like. Based on the parameter, the overcurrent protection circuit 324 may determine the length of trip time period to render the FET Q330 non-conductive after the overcurrent condition is detected. For example, the overcurrent protection circuit 324 may be configured to determine the magnitude of the voltage developed across the FET Q330 in response to drain voltage signal V<sub>DV</sub> from the drain voltage sense circuit 328.

The length of the trip time period may be inversely proportional to the parameter of the FET Q330. For example, the overcurrent protection circuit 324 may have a shorter length of the trip time period when the parameter (*e.g.*, temperature, power, and/or voltage) is high, and may have a longer length of the trip time period when the parameter (*e.g.*, temperature, power, and/or voltage) is low. Accordingly, the overcurrent protection circuit 324 may render the FET Q330 conductive faster by having a shorter length of the trip time period when, for example, an overcurrent condition may be occurring. In addition, the overcurrent protection circuit 324 may render the FET Q330 conductive slower by having a longer length of the trip time period (*e.g.*, to allow for conduction of inrush current for a longer period of time). By allowing the FET Q330 to be conductive in a current half cycle for a longer period of time to conduct inrush current, the gate drive circuit 300 may charge an input capacitance of the electrical load to a greater level and reduce the amount of inrush current that may be conducting during the next half cycle.

The gate drive circuit 300 may include an isolated power supply 320. The isolated power supply 320 may generate an isolated supply voltage V<sub>SUP</sub> (*e.g.*, approximately 15 V) for providing power to the gate drive circuit 300 and drive the FET Q330. The isolated power supply 320 may be independent from a power supply used for the remaining components of the load control device, such as the power supply 140 shown in FIGs. 1 and 2. For example, each of the controllably conductive devices 110, 120 shown in FIGs 1 and 2 may comprise an individual isolated power supply. Alternatively, the load control device may include a single power supply, and as such, the isolated power supply 320 may be omitted.

[0067] When the load control device comprises multiple load control circuits (*e.g.*, such as the first and second load control circuits 110, 120 of the load control device 100), a single lighting load may be connected to two or more the dimmed-hot terminals (*e.g.*, as shown in FIG. 2), such that the load control circuits are coupled in parallel and share the load current (*e.g.*, may each conduct at least a portion of a load current I<sub>LOAD</sub> through the lighting load). This may allow the load control device to control a lighting load having a high power rating than when lighting loads are individually coupled to the dimmed-hot terminals (*e.g.*, as shown in FIG. 1).

[0068]Each of the multiple load control circuit includes respective closed-loop drive circuit for each of the semiconductor switches. The closed-loop drive circuits each operate to limit the magnitude of the portion of the load current being conducted through the respective semiconductor switch to the maximum current level IMAX (e.g., as described above with reference to the gate drive circuit 300 of FIG. 3). The control circuit 115 may generate respective drive signals to control the respective semiconductor switches of each of the load control circuits in unison (e.g., with identical drive signals as described above with reference to FIG. 2). However, due to tolerances of the components of the gate drive circuits, there may be different hardware delays between when the drive signals are driven high to render the semiconductor switches conductive and each of semiconductor switches are rendered conductive. For example, if the first FET Q112 of the first load control circuit 110 becomes conductive before (e.g., even slightly before) the FET Q122 of the second load control circuit 120, the FET Q112 may attempt to conduct (e.g., briefly conduct) all of the load current I<sub>LOAD</sub> (e.g., which may be very large, particularly during an inrush current condition). Because the first closed-loop gate circuit 116 may limit the magnitude of the load current ILOAD conducted through the first FET Q112 to the maximum current level IMAX, the first FET Q112 may not be damaged and may continue to conduct (e.g., briefly conduct) the load current ILOAD at the maximum current level IMAX until the second FET Q112 becomes conductive.

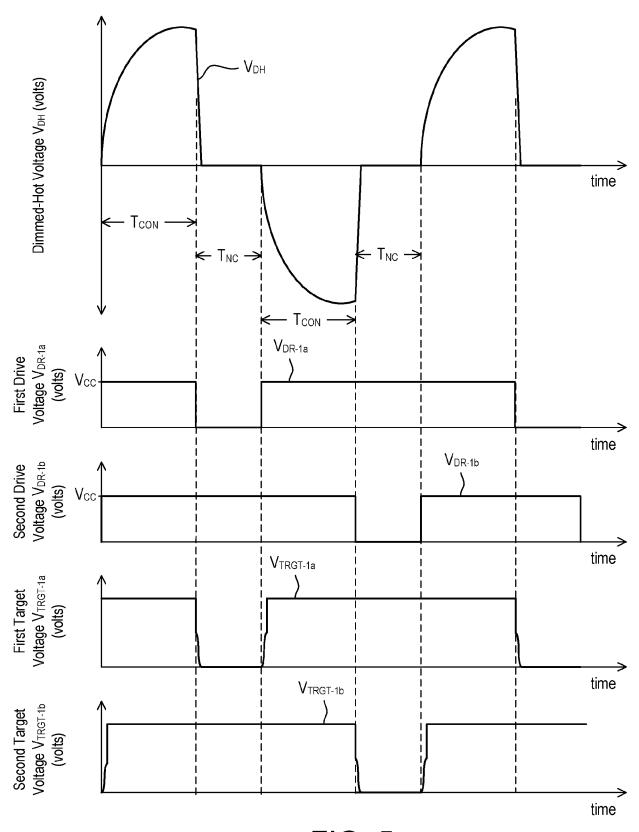

[0069] FIG. 4 shows examples of waveforms that illustrate an operation of a load control device (*e.g.*, the load control device 100 shown in FIGs. 1 and 2) using a forward phase-control dimming technique. As described herein, the load control device may receive an AC voltage from an AC power source and may generate a dimmed-hot voltage V<sub>DH</sub> at a dimmed-hot terminal of the load control device. Using the forward phase-control dimming technique and as shown in FIG. 4, a

control circuit may render a controllably conductive device non-conductive at the beginning of each half cycle (*e.g.*, during a non-conductive period T<sub>NC</sub>), render the controllably conductive device conductive at a firing time during the half cycle, and maintain the controllably conductive device non-conductive until the end of the half cycle (*e.g.*, during a conductive period T<sub>CON</sub>). For example, the controllably conductive device may comprise two semiconductor switches, such as in anti-series connection. Further, it should be appreciated that the slope of the dimmed-hot voltage V<sub>DH1</sub> when transitioning from and to zero volts as shown in FIGs. 4-9 is exaggerated for illustrated purposes.

[0070] The control circuit may generate a drive signal to control the conductivity of the controllably conductive device. For example, the control circuit may generate a first drive signal V<sub>DR-1a</sub> to render a first semiconductor switch (*e.g.*, the first FET Q112 of the first controllably conductive device 110) conductive during the positive half cycles, and may generate a second drive signal V<sub>DR-1b</sub> to render a second semiconductor switch (*e.g.*, the second FET Q114 of the first controllably conductive device 120) conductive during the negative half cycles. The first and second drive signals V<sub>DR-1a</sub>, V<sub>DR-1b</sub> may be pulse-width modulated signals.

The load control device may generate target signals (*e.g.*, a first target signal V<sub>TRGT-1a</sub> and a second target signal V<sub>TRGT-1b</sub>) in response to the control circuit. For example, as described herein, a first gate drive circuit of the load control device (*e.g.*, the first gate drive circuit 116) may receive the first drive signal V<sub>DR-1a</sub>, which may be driven high at a firing time during the positive half cycles of the AC voltage. The first gate drive circuit may start to shape the first target signal V<sub>TRGT-1a</sub> in response to the first drive signal V<sub>DR-1a</sub>, and may shape the first target signal V<sub>TRGT-1a</sub> during a turn-on time period. The first gate drive circuit may use the first target signal V<sub>TRGT-1a</sub> to render the first semiconductor switch conductive and maintain the first semiconductor switch conductive during the remainder of the positive half cycles. Similarly, a second gate drive circuit of the load control device (*e.g.*, the second gate drive circuit 118) may receive the second drive signal V<sub>DR-1b</sub>, which may be driven high at a firing time during the negative half cycles of the AC voltage. The second gate drive circuit may shape the second target signal V<sub>TRGT-1b</sub> in response to the second drive signal V<sub>DR-1b</sub>, and may shape the second target signal V<sub>TRGT-1b</sub> during a turn-on time period. The second gate drive circuit may use the second target signal V<sub>TRGT-1b</sub> to render the second

semiconductor switch conductive and maintain the second semiconductor switch conductive during the remainder of the negative half cycles.

Further, at the end of the negative half cycles of the AC voltage (*e.g.*, near a zero-crossing of the AC voltage), the first drive signal V<sub>DR-1a</sub> may be driven low by the control circuit, and the first gate drive circuit may shape the first target signal V<sub>TRGT-1a</sub> during a turn-off time period. Similarly, at the end of the positive half cycles of the AC voltage (*e.g.*, near a zero-crossing of the AC voltage), the second drive signal V<sub>DR-1b</sub> may be driven low by the control circuit, and the second gate drive circuit may shape the second target signal V<sub>TRGT-1b</sub> during a turn-off time period. Accordingly, the first and second target signals V<sub>TRGT-1a</sub>, V<sub>TRGT-1b</sub> may be shaped on their rising and falling edges. Alternatively, the first and second target signals V<sub>TRGT-1a</sub>, V<sub>TRGT-1b</sub> may only be shaped on their rising edges and not their falling edges when using the forward phase-control dimming technique.

[0073] FIG. 5 shows examples of waveforms that illustrate an operation of a load control device (*e.g.*, the load control device 100 shown in FIGs. 1 and 2) using a reverse phase-control dimming technique. Similar to the operation of the load control device with a forward phase-control dimming technique described herein, the load control device may receive an AC voltage from an AC power source and may generate a dimmed-hot voltage V<sub>DH1</sub> at a dimmed-hot terminal of the load control device. Using the reverse phase-control dimming technique and as shown in FIG. 5, a control circuit may render a controllably conductive device conductive at the beginning of each half cycle (*e.g.*, during a conductive period T<sub>CON</sub>), render the controllably conductive device non-conductive at a firing time (during the half cycle, and maintain the controllably conductive device conductive until the end of the half cycle (*e.g.*, during a non-conductive period T<sub>NC</sub>). For example, the controllably conductive device may comprise two semiconductor switches, such as in anti-series connection.

The control circuit may generate a drive signal to control the conductivity of the controllably conductive device. For example, the control circuit may generate a first drive signal V<sub>DR-1a</sub> to render a first semiconductor switch (*e.g.*, the first FET Q112 of the first controllably conductive device 110) conductive during the positive half cycles. The control circuit may generate a second drive signal V<sub>DR-1b</sub> to render a second semiconductor switch (*e.g.*, the second FET Q114 of

the second controllably conductive device) conductive during the negative half cycles. As noted above, the first and second drive signals  $V_{DR-1a}$ ,  $V_{DR-1b}$  may be pulse-width modulated signals.