### (10) **DE 101 27 950 B4** 2007.04.12

(12)

# **Patentschrift**

(21) Aktenzeichen: 101 27 950.7(22) Anmeldetag: 08.06.2001(43) Offenlegungstag: 19.12.2002

(45) Veröffentlichungstag

der Patenterteilung: 12.04.2007

(51) Int Cl.8: *H01L 29/06* (2006.01)

**H01L 29/78** (2006.01) **H01L 29/861** (2006.01)

Innerhalb von drei Monaten nach Veröffentlichung der Patenterteilung kann nach § 59 Patentgesetz gegen das Patent Einspruch erhoben werden. Der Einspruch ist schriftlich zu erklären und zu begründen. Innerhalb der Einspruchsfrist ist eine Einspruchsgebühr in Höhe von 200 Euro zu entrichten(§ 6 Patentkostengesetz in Verbindung mit der Anlage zu § 2 Abs. 2 Patentkostengesetz).

(73) Patentinhaber:

Infineon Technologies AG, 81669 München, DE

(74) Vertreter:

Westphal, Mussgnug & Partner, 80336 München

(72) Erfinder:

Lehmann, Volker, 80689 München, DE; Schubert, Axel, 81543 München, DE

(56) Für die Beurteilung der Patentfähigkeit in Betracht gezogene Druckschriften:

US-PS 53 59 214 EP 02 96 348 A1

STENGL/TIHANY: Leistungs-MOSFET-Praxis,

Pflaum

Verlag, München 1992, S. 36-39;

### (54) Bezeichnung: Verfahren zur Herstellung eines Halbleiterbauelements und Halbleiterbauelement

- (57) Hauptanspruch: Verfahren zur Herstellung eines Halbleiterbauelements, das folgende Merkmale aufweist:

- Bereitstellen eines Halbleiterkörpers (100) mit einer ersten und einer zweiten Oberfläche (101, 102),

- Herstellen einer Vielzahl von Poren (103) in dem Halbleiterkörper (100), die sich ausgehend von der ersten Oberfläche (101) in den Halbleiterkörper (100) hinein erstrecken und die unterhalb der zweiten Oberfläche (102) enden, gekennzeichnet, durch

- Steigern der elektrischen Leitfähigkeit des Halbleiterkörpers (100) im Bereich der Poren (103) durch Dotieren des Halbleiterkörpers (100) im Bereich der Poren (103) mit Dotierstoffatomen des selben Leitungstyps wie die Grunddotierung und/oder durch wenigstens teilweises Auffüllen der Poren (103) mit einem elektrisch leitfähigen Material.

### **Beschreibung**

[0001] Die vorliegende Erfindung betrifft ein Halbleiterbauelement, das in einem Halbleiterkörper bzw. Chip integriert ist, der eine erste und eine zweite Oberfläche aufweist, wobei Anschlusskontakte an den Oberflächen zur Kontaktierung des Halbleiterbauelements angeordnet sind.

[0002] Ein derartiges Halbleiterbauelement ist beispielsweise ein vertikaler Transistor, wie er in Stengl/Tihanyi: "Leistungs-MOS-FET-Praxis", Pflaum Verlag, München 1992, Seite 37, beschrieben ist. Dieser Transistor weist ein stark n-dotiertes Halbleitersubstrat auf, auf dem eine schwächer n-dotierte Epitaxieschicht aufgebracht ist. In der Epitaxieschicht sind p-dotierte Body-Zonen angeordnet, in denen wiederum n-dotierte Source-Zonen angeordnet sind. Die Source- und die Body-Zonen sind bei diesem Bauelement an einer Vorderseite des durch das Substrat und die Epitaxieschicht gebildeten Halbleiterkörpers kontaktiert. Das Substrat bildet eine Drain-Zone des Transistors, die an einer Rückseite des Halbleiterkörpers kontaktiert ist. Die Dicke und die Dotierung der Epitaxieschicht, die als Driftzone wirkt, bestimmen maßgeblich die elektrischen Eigenschaften des bekannten Bauelements, insbesondere dessen Sperrspannung und dessen Einschaltwiderstand. Das Substrat, auf welchem die Epitaxieschicht aufgebracht ist, ist möglichst hoch dotiert, um den Einschaltwiderstand möglichst wenig zu beeinflussen.

#### Stand der Technik

**[0003]** Die US 5,359,214 beschreibt ein Halbleiterbauelement mit einem Halbleiterkörper, in den eine Vielzahl von Poren eingebracht sind, wobei Seitenwände dieser Poren mit einem Halbleitermaterial bedeckt sind, welches komplementär zu der Dotierung des Halbleiterkörpers dotiert ist, um auf diese Weise zwischen den Seitenwänden der Poren und dem Halbleiterkörper pn-Übergänge zu erzeugen, so dass durch Anlegen einer Spannung an diese pn-Übergänge der das Halbleiterbauelement durchfließende Strom moduliert werden kann.

[0004] Das stark dotierte Substrat dient im wesentlichen als Träger und ist erforderlich, um einen Wafer, in dem eine Vielzahl solcher Transistoren hergestellt werden und aus dem die Chips mit den Transistoren am Ende des Herstellungsverfahrens herausgesägt werden, während des Herstellungsverfahrens handhaben zu können. Ein Wafer, der ausschließlich die Dicke der die elektrischen Eigenschaften bestimmenden Driftzone aufweist ist theoretisch ausreichend, für die Herstellung des Transistors praktisch jedoch nicht handhabbar, da die Dicke der Driftzone üblicherweise so gering ist, dass ein solcher Wafer vollkommen instabil wäre.

[0005] Weitere allgemein bekannte vertikale Halbleiterbauelemente mit Anschlüssen an gegenüberliegenden Oberflächen eines Halbleiterkörpers sind Dioden, die aus Stabilitätsgründen üblicherweise ebenfalls ein gut elektrisch leitendes Substrat aufweisen, auf welches – beispielsweise mittels Epitaxie – Halbleiterschichten aufgebracht sind, die einen pn-Übergang bilden und deren Dotierung und Abmessungen die elektrischen Eigenschaften der Diode bestimmen.

[0006] Um einerseits eine ausreichende mechanische Stabilität des Wafers bei der Herstellung zu gewährleisten, die nur durch eine gewisse Dicke sichergestellt werden kann, und andererseits die Auswirkungen dieser zur Herstellung erforderlichen Dicke auf das Bauelement möglichst gering zu halten, sind neben der genannten Möglichkeit, auf ein gut leitendes Substrat Epitaxie-Schichten aufzubringen, die die elektrischen Eigenschaften bestimmen, weitere Vorgehensweisen allgemein bekannt.

[0007] So ist es allgemein bekannt, einen Wafer vorzusehen, der eine Dotierung aufweist, die den Anforderungen an die Dotierung in Bereichen des Halbleiterbauelements, beispielsweise der Driftzone, genügt und den Wafer anschließend in den Bereichen, die einen Einfluss auf die elektrischen Eigenschaften des Bauelements haben, zu dünnen.

[0008] Des weiteren ist es allgemein bekannt, wenn auf eine Epitaxie verzichtet werden soll, einen schwächer dotierten Wafer zu verwenden und den Wafer von einer Rückseite her mittels einer Tiefdiffusion zu dotieren, um so einen niedrigen Widerstand des Wafers in den Bereichen zu erzeugen, die lediglich zur mechanischen Stabilität beitragen, und das oberhalb dieser Bereiche ausgebildete Halbleiterbauelemente von der Rückseite her niederohmig kontaktieren zu können.

#### Aufgabenstellung

[0009] Ziel der vorliegenden Erfindung ist es, ein Verfahren zur Herstellung eines Halbleiterbauelements zur Verfügung zu stellen, bei dem ein Wafer in dem eine Vielzahl von Bauelementen hergestellt werden, eine für die Handhabung des Wafers während des Herstellungsverfahrens ausreichende Dicke aufweisen darf und bei dem der Bereich des Wafers bzw. des späteren Chips, der keinen aktiven Bereich des Bauelements bildet einen geringen elektrischen Widerstand aufweist und ein durch dieses Verfahren hergestelltes Halbleiterbauelement zur Verfügung zu stellen.

**[0010]** Diese Aufgabe wird durch ein Verfahren gemäß der Merkmale des Anspruchs 1 und ein Halbleiterbauelement gemäß der Merkmale des Anspruchs 4 gelöst.

**[0011]** Vorteilhafte Ausgestaltungen der Erfindung sind Gegenstand der Unteransprüche.

[0012] Das erfindungsgemäße Verfahren zur Herstellung eines Halbleiterbauelements sieht vor, einen Halbleiterkörper mit einer ersten und einer zweiten Oberfläche zur Verfügung zu stellen und eine Vielzahl von Poren zu erzeugen, die sich ausgehend von der ersten Oberflächen in den Halbleiterkörper hinein erstrecken und die unterhalb der zweiten Oberfläche enden. Anschließend wird die elektrische Leitfähigkeit des Halbleiterkörpers im Bereich der Poren gesteigert. Dies erfolgt durch Eindiffundieren von Dotierstoffatomen des selben Leitungstyps wie eine Grunddotierung des Halbleiterkörpers in Bereiche des Halbleiterkörpers, die in den Poren freiliegen und/oder durch Auffüllen der Poren mit einem elektrisch leitenden Material, insbesondere einem Metall oder Polysilizium.

[0013] Der nicht von den Poren durchsetzte Bereich des Halbleiterkörpers unterhalb der zweiten Oberfläche kann zur Realisierung der aktiven Bereiche des eigentlichen Halbleiterbauelements, beispielsweise einer Diode oder eines Transistors, genutzt werden. Diese aktiven Bereiche können vor der Erzeugung der Poren oder nach der Erzeugung der Poren hergestellt werden. Die Tiefe, bis in welche die Poren ausgehend von der ersten Oberfläche in den Halbleiterkörper eingebracht werden, ist so auf die Dicke des Halbleiterkörpers bzw. des Wafers, der eine Vielzahl der späteren Halbleiterkörper/Chips bildet, abgestimmt, dass zwischen dem im Halbleiterkörper liegenden Ende der Poren und der zweiten Oberfläche eine Halbleiterschicht verbleibt, die eine Dicke aufweist, die zur Realisierung des gewünschten Bauelements geeignet ist. Das erfindungsgemäße Verfahren ist dabei insbesondere bei der Herstellung von PIN-Fotodioden geeignet.

[0014] Elektrisch verhält sich der Halbleiterkörper, dessen elektrische Leitfähigkeit im Bereich der Poren gesteigert wurde, annäherungsweise wie ein dünnes Substrat, das lediglich die Dicke der nicht von Poren durchsetzten Schicht des Halbleiterkörpers aufweist und das über den gut elektrisch leitenden porösen Bereich von der zweiten Oberfläche des Halbleiterkörpers her kontaktierbar ist.

**[0015]** Die vorliegende Erfindung wird nachfolgend in Ausführungsbeispielen anhand von Figuren näher erläutert. In den Figuren zeigt

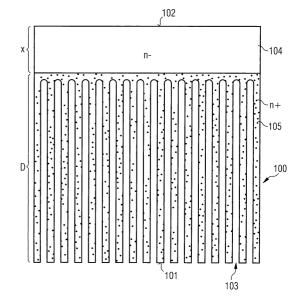

**[0016] Fig.** 1 einen Ausschnitt eines Halbleiterkörpers/Wafers während verschiedener Verfahrensschritte eines erfindungsgemäßen Verfahrens zur Herstellung eines Halbleiterbauelements,

[0017] Fig. 2 einen Ausschnitt eines Halbleiterkörpers/Wafers, bei dem die elektrische Leitfähigkeit im

Bereich der Poren durch Auffüllen der Poren mit einem elektrisch leitenden Material gesteigert wurde,

**[0018]** Fig. 3 ein erfindungsgemäßes Halbleiterbauelement gemäß einer ersten Ausführungsform der Erfindung,

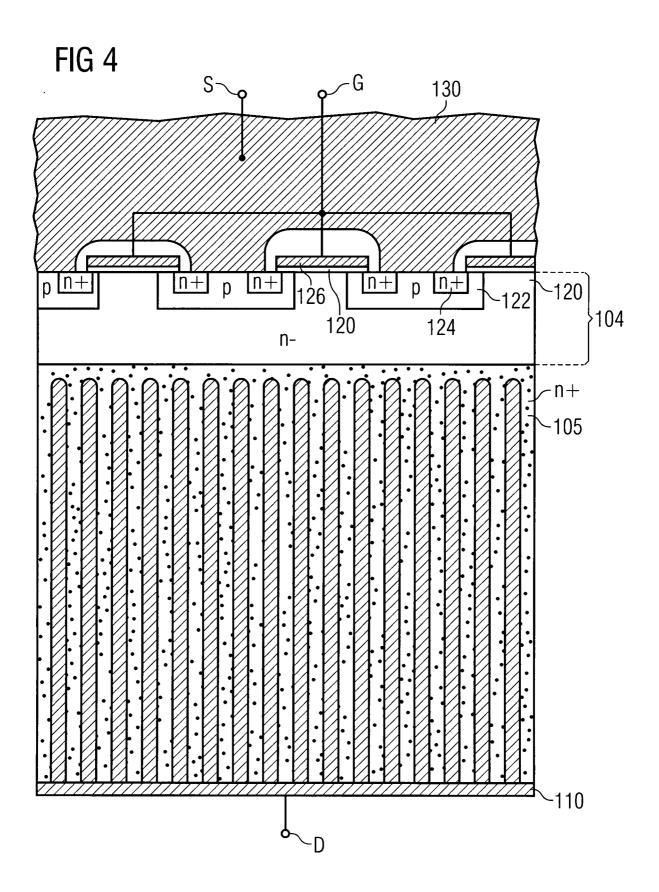

**[0019]** Fig. 4 ein erfindungsgemäßen Halbleiterbauelement gemäß einer zweiten Ausführungsform der Erfindung.

### Ausführungsbeispiel

[0020] Fig. 1 veranschaulicht erfindungsgemäße Verfahrensschritte während der Herstellung eines Halbleiterbauelements, wobei Fig. 1 einen Ausschnitt eines Halbleiterkörpers oder eines Wafers, aus dem eine Vielzahl der späteren Halbleiterkörper/Chips herausgesägt werden, im Querschnitt zeigt.

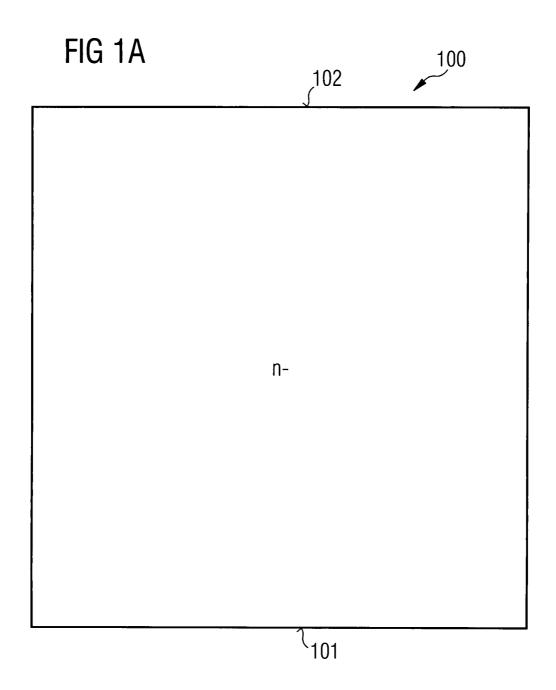

[0021] In einem ersten Verfahrensschritt wird, wie in Fig. 1a dargestellt ist, ein Halbleiterkörper 100 zur Verfügung gestellt, der eine erste Oberfläche 101 und eine zweite Oberfläche 102 aufweist.

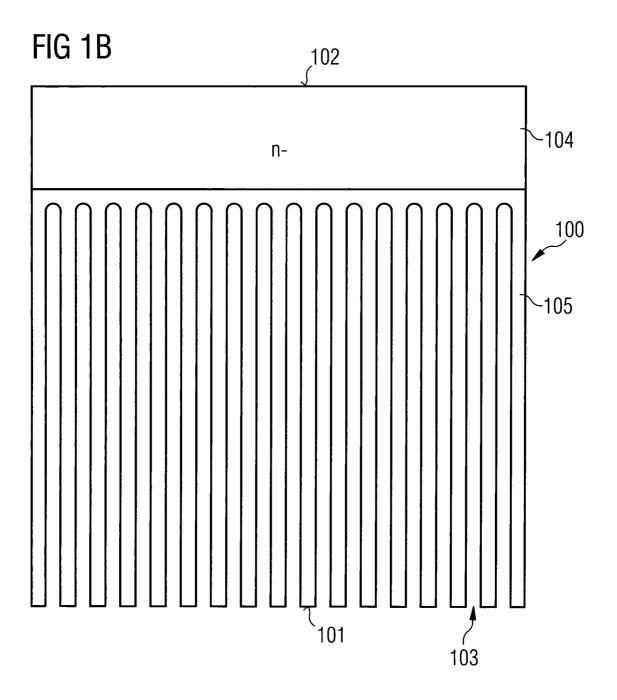

[0022] Anschließend werden ausgehend von der ersten Oberfläche 101 Poren in dem Halbleiterkörper 100 erzeugt, die unterhalb der zweiten Oberfläche 102 des Halbleiterkörpers enden, wie in Fig. 1b dargestellt ist. Zur Herstellung der Poren 103 eignet sich beispielsweise das in der EP 0 296 348 A1 beschriebene elektrochemische makroporöse Ätzverfahren.

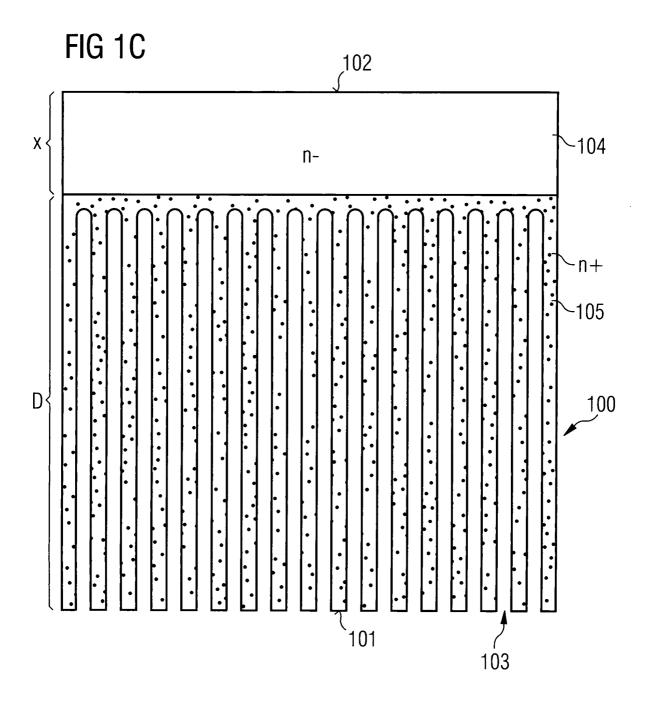

[0023] Zudem wird, wie in Fig. 1c dargestellt ist, die elektrische Leitfähigkeit des Halbleiterkörpers im Bereich der Poren 103 gesteigert. Dazu ist gemäß einer ersten Ausführungsform des Verfahrens vorgesehen, ausgehend von der ersten Oberfläche 101 Dotierstoffatome, insbesondere Donatoratome in Bereiche des Halbleiterkörper 100 einzudotieren, die in den Poren freiliegen, und die Dotierstoffatome anschließend in den Halbleiterkörper mittels eines Temperaturschritts eindiffundieren zu lassen. Die Diffusionstiefe und die Abstände benachbarter Poren 103 sind vorzugsweise so aufeinander abgestimmt, dass die zwischen den Poren liegenden Bereiche vollständig dotiert werden und anschließend eine hohe Dotierung aufweisen. Der in Fig. 1a dargestellte Halbleiterkörper 100 ist in dem Beispiel zu Beginn des Verfahrens schwach n-dotiert, wobei zur Steigerung der elektrischen Leitfähigkeit im Bereich der Poren 103 eine starke n-Dotierung erfolgt.

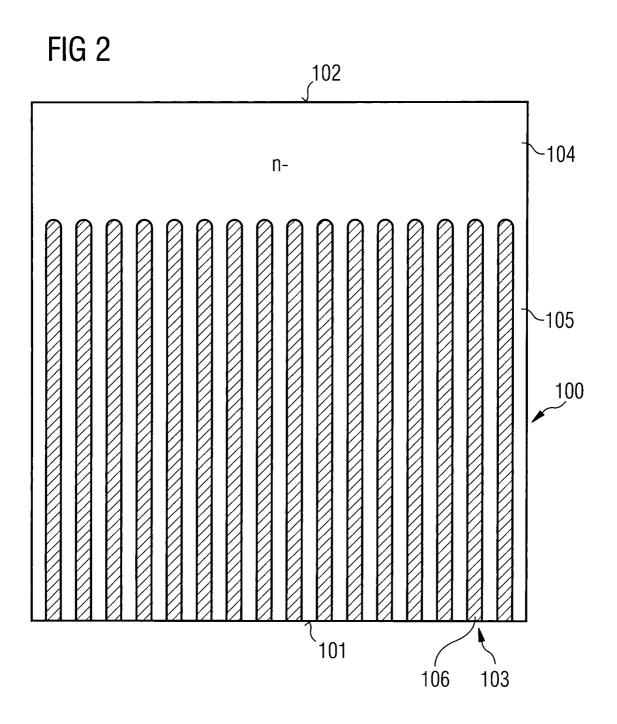

[0024] Zur Steigerung der elektrischen Leitfähigkeit im Bereich der Poren kann zusätzlich oder alternativ vorgesehen werden, die Poren 103 mit einem elektrisch leitenden Material, insbesondere einem Metall, beispielsweise Kupfer, oder Polysilizium aufzufüllen. Fig. 2 zeigt einen Halbleiterkörper 100, dessen Po-

ren 103 mit einem leitenden Material aufgefüllt wurden.

[0025] Bei den in den Fig. 1 und Fig. 2 dargestellten Ausführungsbeispielen nimmt der Bereich mit gesteigerter elektrischer Leitfähigkeit einen Bereich 105 mit einer Dicke D ein. Ein Bereich 104 mit einer Dicke x oberhalb des Bereiches 105 mit gesteigerter elektrischer Leitfähigkeit verbleibt für die Realisierung von aktiven Bereichen von Halbleiterbauelementen.

[0026] Der Bereich 105, trägt im wesentlichen zur mechanischen Stabilität eines Wafers bei der Herstellung von Halbleiterbauelementen in dem Bereich 104 bei, wobei die Ausdehnung des Wafers in lateraler Richtung die Dicke D, bzw. die Summe aus den Dicken D und x, um mehrere Größenordnungen übersteigt. Der Bereich D dient somit im wesentlichen als Trägerschicht für die Schicht 104, in der Halbleiterbauelemente ausgebildet sein können, wie anhand der Fig. 3 und Fig. 4 noch erläutert wird. Des weiteren dient der Bereich 105 als Anschlusszone für diese Halbleiterbauelemente, wobei die Maßnahme, die elektrische Leitfähigkeit des Bereiches 105 durch Dotierung und/oder Auffüllen der Poren 103 mit einem leitenden Material zu steigern, dem Bestreben Rechnung trägt, dass die Anschlusszone 105 möglichst nicht zur Steigerung des elektrischen Widerstandes des Halbleiterbauelementes beitragen soll. Die Zone 104 des Halbleiterkörpers wirkt wie ein dünnes Substrat, das über die Zone 105 von der ersten Oberfläche 101 des Halbleiterkörpers 100 her niederohmig kontaktierbar ist.

**[0027]** Zusätzlich bewirkt diese Dotierung aus den Poren **103** heraus dass in diesem Bereich die Lebensdauer für, beispielsweise durch Licht generierte, Elektron-Loch-Paare sehr niedrig ist. Dadurch lassen sich sehr schnelle PIN-Dioden realisieren.

[0028] Fig. 3 zeigt in Seitenansicht im Querschnitt eine Diode, die in einem mittels einem Verfahren gemäß der Fig. 1 oder Fig. 2 bearbeiteten Halbleiterkörper integriert ist. Der Bereich 105 mit den Poren 103 ist mittels einer auf die erste Oberfläche 101 aufgebrachten Kontaktschicht 110, vorzugsweise einem Metall kontaktiert. Ausgehend von der zweiten Oberfläche 102 wurde mittels hinlänglich bekannter Verfahren eine p-dotierte Zone 104A in dem Bereich 104 erzeugt, die durch eine Kontaktschicht 112 kontaktiert ist. Die p-dotierte Zone 104A bildet die Anodenzone, die n-dotierte Zone 104B bildet die Kathodenzone der Diode. Die ursprüngliche Dotierung des Halbleiterkörpers 100 ist vorzugsweise so gewählt, dass sie zur Bildung der späteren Kathodenzone 104B der Diode geeignet ist.

[0029] Fig. 4 zeigt in Seitenansicht im Querschnitt einen vertikalen MOS-Transistor, der in einem mittels eines Verfahrens gemäß der Fig. 1 oder Fig. 2 bear-

beiteten Halbleiterkörper integriert ist. Zur Herstellung des Transistors wurden in die n-dotierte Zone 104 p-dotierte Body-Zonen eingebracht, in die wiederum stark n-dotierte Source-Zonen 122 eingebracht wurden. Die Source-Zonen 122 und die Body-Zonen 120 sind mittels einer Source-Elektrode 130 kurzgeschlossen, die auf die zweite Oberfläche 102 des Halbleiterkörpers 100 aufgebracht ist. Ein Abschnitt 120 der Zone 104 bildet die Driftzone des MOS-Transistors, die über den porösen Bereich 105 durch eine auf der ersten Oberfläche 101 aufgebrachte Anschlussschicht 110, die die Drain-Elektrode bildet, kontaktiert ist. Oberhalb der zweiten Oberfläche 102 des Halbleiterkörpers 100 sind weiterhin Gate-Elektroden 126 vorgesehen, die mittels Isolationsschichten 128 gegenüber dem Halbleiterkörper 100 und der Source-Elektrode 130 isoliert sind.

[0030] Bei dem MOS-Transistor gemäß Fig. 4 ist eine Dotierung des Halbleiterkörpers im Bereich der Poren 103 vorgesehen und die Poren 103 sind mit einem elektrisch leitenden Material aufgefüllt. Die ursprüngliche Dotierung des Halbleiterkörpers 100 ist so gewählt ist, dass sie zur Bildung der Driftzone 120 geeignet ist.

[0031] Während bei der obigen Beschreibung davon ausgegangen wurde, dass die aktiven Bereiche der Halbleiterbauelemente nach der Herstellung der Poren 103 erzeugt werden, besteht selbstverständlich auch die Möglichkeit, die aktiven Bereiche der Halbleiterbauelemente vor der Erzeugung der Poren 103 in dem Halbleiterkörper 100 herzustellen.

#### **Patentansprüche**

- 1. Verfahren zur Herstellung eines Halbleiterbauelements, das folgende Merkmale aufweist:

- Bereitstellen eines Halbleiterkörpers (100) mit einer ersten und einer zweiten Oberfläche (101, 102),

- Herstellen einer Vielzahl von Poren (103) in dem Halbleiterkörper (100), die sich ausgehend von der ersten Oberfläche (101) in den Halbleiterkörper (100) hinein erstrecken und die unterhalb der zweiten Oberfläche (102) enden,

gekennzeichnet, durch

- Steigern der elektrischen Leitfähigkeit des Halbleiterkörpers (100) im Bereich der Poren (103) durch Dotieren des Halbleiterkörpers (100) im Bereich der Poren (103) mit Dotierstoffatomen des selben Leitungstyps wie die Grunddotierung und/oder durch wenigstens teilweises Auffüllen der Poren (103) mit einem elektrisch leitfähigen Material.

- 2. Verfahren nach Anspruch 1, bei dem sich ein Diffusionsschritt an den Dotierschritt anschließt.

- 3. Verfahren nach Anspruch 1, bei dem das elektrisch leitfähige Material ein Metall oder Polysilizium ist.

- 4. Halbleiterbauelement, das folgende Merkmale aufweist:

- einen Halbleiterkörper (100) mit einer ersten und zweiten Oberfläche (101, 102) die jeweils Anschlusskontakte (110, 112; 110, 130) aufweisen,

- eine Vielzahl von Poren (103), die sich ausgehend von der ersten Oberfläche (101) in den Halbleiterkörper (100) hinein erstrecken und die unterhalb der zweiten Oberfläche (102) enden,

dadurch gekennzeichnet, dass

das Bauelement im Bereich der Poren (103) eine gesteigerte elektrische Leitfähigkeit dadurch aufweist, dass Dotierstoffatome desselben Leitungstyps wie die Grunddotierung des Halbleiterkörpers (100) im Bereich der Poren (103) in dem Halbleiterkörper (100) eingebracht sind und/oder dass die Poren (103) wenigstens teilweise mit einem elektrisch leitfähigen Material aufgefüllt sind.

5. Halbleiterbauelement nach Anspruch 4, bei dem das elektrisch leitende Material ein Metall oder Polysilizium ist.

Es folgen 6 Blatt Zeichnungen

## Anhängende Zeichnungen