## (19) **日本国特許庁(JP)**

# (12) 公 開 特 許 公 報(A)

(11)特許出願公開番号

特開2016-181676 (P2016-181676A)

(43) 公開日 平成28年10月13日(2016.10.13)

(51) Int. Cl. FLテーマコード (参考) HO1L 25/07 (2006, 01) HO1L C 5H770 25/04 HO1L 25/18 (2006, 01) HO2M 7/48  $\mathbf{Z}$

HO2M 7/48 (2007.01)

> 審査請求 未請求 請求項の数 21 OL (全 14 頁)

(21) 出願番号 特願2015-238930 (P2015-238930) (71) 出願人 000003078 (22) 出願日 平成27年12月7日(2015.12.7) 株式会社東芝 (31) 優先権主張番号 特願2015-61797 (P2015-61797) 東京都港区芝浦一丁目1番1号 平成27年3月24日(2015.3.24) (74)代理人 100119035 (32) 優先日 (33) 優先権主張国 日本国(JP) 弁理士 池上 徹真 (74)代理人 100141036 弁理士 須藤 章 (74)代理人 100088487 弁理士 松山 允之 (72) 発明者 高尾 和人 東京都港区芝浦一丁目1番1号 株式会社 東芝内

(72) 発明者 飯島 良介

東芝内

最終頁に続く

東京都港区芝浦一丁目1番1号 株式会社

(54) 【発明の名称】半導体装置、インバータ回路、駆動装置、車両、及び、昇降機

## (57)【要約】

【課題】インダクタンスの低減が可能な半導体装置を提 供する。

【解決手段】実施形態の半導体装置は、第1の電極、第 2の電極、第1の電極と第2の電極との間に電気的に直 列に接続される第1のスイッチング素子と第2のスイッ チング素子を有するスイッチング素子部、第1の電極と 第2の電極との間に第1のスイッチング素子と第2のス イッチング素子に対し電気的に並列に接続されるコンデ ンサを有しスイッチング素子部と積層されるコンデンサ (b) 部、を有する複数の回路ユニット、を備え、隣り合う2 個の回路ユニットにおいて、一方のスイッチング素子部 と他方のコンデンサ部とが隣り合い、一方のコンデンサ 部と他方のスイッチング素子とが隣り合い、一方の第1 の電極と他方の第1の電極とが隣り合い、一方の第2の 電極と他方の第2の電極とが隣り合う。

【選択図】図1

#### 【特許請求の範囲】

## 【請求項1】

第1の電極、第2の電極、前記第1の電極と前記第2の電極との間に電気的に直列に接続される第1のスイッチング素子と第2のスイッチング素子を有するスイッチング素子部、前記第1の電極と前記第2の電極との間に前記第1のスイッチング素子と前記第2のスイッチング素子に対し電気的に並列に接続されるコンデンサを有し前記スイッチング素子部と積層されるコンデンサ部、を有する複数の回路ユニット、を備え、

隣り合う 2 個の前記回路ユニットにおいて、一方の前記スイッチング素子部と他方の前記コンデンサ部とが隣り合い、一方の前記コンデンサ部と他方の前記スイッチング素子とが隣り合い、一方の前記第 1 の電極とが隣り合い、一方の前記第 2 の電極と他方の前記第 2 の電極とが隣り合う半導体装置。

【請求項2】

前記第1の電極が互いに接続され、前記第2の電極が互いに接続される請求項1記載の半導体装置。

#### 【請求項3】

隣り合う2個の前記回路ユニットにおいて、一方の前記スイッチング素子部と他方の前記コンデンサ部との距離が、一方の前記スイッチング素子部と他方の前記スイッチング素子部との距離よりも短い請求項1又は請求項2記載の半導体装置。

## 【請求項4】

前記回路ユニットが、前記第1のスイッチング素子と前記第2のスイッチング素子との間に接続される第3の電極を有する請求項1乃至請求項3いずれか一項記載の半導体装置

【請求項5】

前記スイッチング素子部の、前記コンデンサ部を挟んで反対側に、ヒートシンクを有する請求項1乃至請求項4いずれか一項記載の半導体装置。

【請求項6】

前記回路ユニットが環状に配置される請求項1乃至請求項5いずれか一項記載の半導体装置。

【請求項7】

前記第1のスイッチング素子及び前記第2のスイッチング素子が、MOSFET又はIGBTであることを特徴とする請求項1乃至請求項6いずれか一項記載の半導体装置。

【請求項8】

隣り合う 2 個の前記回路ユニットにおいて、一方の磁束の向きと他方の磁束の向きが反対である請求項 1 乃至請求項 7 いずれか一項記載の半導体装置。

【請求項9】

第1の電極、第2の電極、前記第1の電極と前記第2の電極との間に電気的に直列に接続される第1のスイッチング素子と第2のスイッチング素子を有するスイッチング素子部、前記第1の電極と前記第2の電極との間に前記第1のスイッチング素子と前記第2のスイッチング素子に対し電気的に並列に接続されるコンデンサを有し前記スイッチング素子部と積層されるコンデンサ部、を有する第1の回路用ニットと第2の回路ユニット、を備え、

前記第1の回路ユニットの前記スイッチング素子部と前記第2の回路ユニットの前記コンデンサ部とが隣り合い、前記第1の回路ユニットの前記コンデンサ部と前記第2の回路ユニットの前記第1の電路と前記第2の回路ユニットの前記第1の電極とが隣り合い、前記第1の回路ユニットの前記第2の電極と前記第2の電極と前記第2の電極と前記第2の電極とが隣り合う半導体装置。

【請求項10】

前記第1の電極が互いに接続され、前記第2の電極が互いに接続される請求項9記載の半導体装置。

【請求項11】

10

20

30

40

前 記 第 1 の 回 路 ユニット の 前 記 ス イッ チン グ 素 子 部 と 前 記 第 2 の 回 路 ユニット の 前 記 コ ン デ ン サ 部 と の 距 離 が 、 前 記 第 1 の 回 路 ユ ニ ッ ト の 前 記 ス イ ッ チ ン グ 素 子 部 と 前 記 第 2 の 回路ユニットの前記スイッチング素子部との距離よりも短い請求項9又は請求項10記載 の半導体装置。

## 【請求項12】

前 記 第 1 の ス イ ッ チ ン グ 素 子 と 前 記 第 2 の ス イ ッ チ ン グ 素 子 と の 間 に 接 続 さ れ る 第 3 の 電 極 を 有 す る 請 求 項 9 乃 至 請 求 項 1 1 い ず れ か 一 項 記 載 の 半 導 体 装 置 。

## 【請求項13】

前記スイッチング素子部の、前記コンデンサ部を挟んで反対側に、ヒートシンクを有す る請求項9乃至請求項12いずれか一項記載の半導体装置。

【請求項14】

前記回路ユニットが環状に配置される請求項9乃至請求項13いずれか一項記載の半導 体装置。

## 【請求項15】

前 記 第 1 の ス イ ッ チ ン グ 素 子 及 び 前 記 第 2 の ス イ ッ チ ン グ 素 子 が 、 M O S F E T 又 は I GBTであることを特徴とする請求項9乃至請求項14いずれか一項記載の半導体装置。

## 【請求項16】

前記第1の回路ユニットの磁束の向きと前記第2の回路ユニットの磁束の向きが反対で ある請求項9乃至請求項15いずれか一項記載の半導体装置。

## 【請求項17】

第1の電極、第2の電極、前記第1の電極と前記第2の電極との間に電気的に直列に接 続 さ れ る 第 1 の ス イ ッ チ ン グ 素 子 と 第 2 の ス イ ッ チ ン グ 素 子 を 有 す る ス イ ッ チ ン グ 素 子 部 、前記第1の電極と前記第2の電極との間に前記第1のスイッチング素子と前記第2のス イッチング素子に対し電気的に並列に接続されるコンデンサを有し前記スイッチング素子 部と積層されるコンデンサ部、を有する第1の回路用ニットと第2の回路ユニット、を備 え、

前記第1の回路ユニットの磁束の向きと前記第2の回路ユニットの磁束の向きが反対で ある半導体装置。

## 【請求項18】

請求項1乃至請求項17いずれか一項記載の半導体装置を備えるインバータ回路。

## 【請求項19】

請求項1乃至請求項17いずれか一項記載の半導体装置を備える駆動装置。

#### 【請求項20】

請求項1乃至請求項17いずれか一項記載の半導体装置を備える車両。

## 【請求項21】

請求項1乃至請求項17いずれか一項記載の半導体装置を備える昇降機。

## 【発明の詳細な説明】

## 【技術分野】

## [00001]

本発明の実施形態は、半導体装置、インバータ回路、駆動、車両、及び、昇降機に関す る。

## 【背景技術】

## [00002]

例えば、電力変換モジュールのようなパワー半導体モジュールでは、スイッチング動作 が高速になるにつれ、ターンオフ時の過電圧による素子破壊やノイズの発生が問題となる 。 ターンオフ 時 の 過 電 圧 は 、 回 路 配 線 中 の イ ン ダ ク タ ン ス と パ ワ ー 半 導 体 モ ジ ュ ー ル を 流 れる電流の時間変化率(di/dt)に比例する。

## [00003]

過電圧を抑制するためにスイッチング時間を長くとると、スイッチング動作が遅くなる 。同時に、電流と電圧の積の時間積分で表されるスイッチング損失が大きくなる。過電圧 10

20

30

40

を抑制し、かつ、スイッチング損失を低減するには、パワー半導体モジュールのインダク タンスを低減させることが望ましい。インダクタンスを低減するため、パワー半導体モジ ュールを複数の回路ユニットに分割する方法がある。

【先行技術文献】

【特許文献】

[0004]

【特許文献1】特開2014-67760号公報

【発明の概要】

【発明が解決しようとする課題】

[00005]

本発明が解決しようとする課題は、インダクタンスの低減が可能な半導体装置、インバ 一夕回路、駆動装置、車両、及び、昇降機を提供することにある。

【課題を解決するための手段】

[0006]

実施形態の半導体装置は、第1の電極、第2の電極、前記第1の電極と前記第2の電極 との間に電気的に直列に接続される第1のスイッチング素子と第2のスイッチング素子を 有 す る ス イ ッ チ ン グ 素 子 部 、 前 記 第 1 の 電 極 と 前 記 第 2 の 電 極 と の 間 に 前 記 第 1 の ス イ ッ チング素子と前記第2のスイッチング素子に対し電気的に並列に接続されるコンデンサを 有し前記スイッチング素子部と積層されるコンデンサ部、を有する複数の回路ユニット、 を備え、隣り合う2個の前記回路ユニットにおいて、一方の前記スイッチング素子部と他 方の前記コンデンサ部とが隣り合い、一方の前記コンデンサ部と他方の前記スイッチング 素子とが隣り合い、一方の前記第1の電極と他方の前記第1の電極が隣り合い、一方の前 記第2の電極と他方の前記第2の電極が隣り合う。

【図面の簡単な説明】

[0007]

- 【図1】第1の実施形態の半導体装置の模式図。

- 【図2】第1の実施形態の回路ユニットの等価回路図。

- 【図3】比較形態の半導体装置の模式図。

- 【図4】比較形態及び第1の実施形態の半導体装置の動作時の電流の向きと磁束の向きを 示す図。

- 【図5】第2の実施形態の半導体装置の模式平面図。

- 【図6】第3の実施形態の駆動装置の模式斜視図。

- 【図7】第4の実施形態の車両の模式図。

- 【図8】第5の実施形態の車両の模式図。

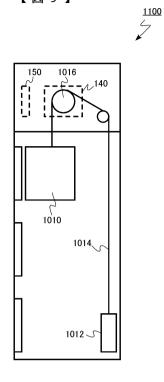

- 【図9】第6の実施形態の昇降機の模式図。

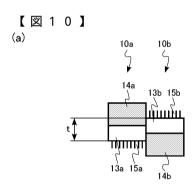

- 【図10】実施例の説明図。

- 【発明を実施するための形態】

- [0008]

以下、図面を参照しつつ本発明の実施形態を説明する。なお、以下の説明では、同一の 部 材 等 に は 同 一 の 符 号 を 付 し 、 一 度 説 明 し た 部 材 等 に つ い て は 適 宜 そ の 説 明 を 省 略 す る 。

[0009]

(第1の実施形態)

本実施形態の半導体装置は、第1の電極、第2の電極、第1の電極と第2の電極との間 に電気的に直列に接続される第1のスイッチング素子と第2のスイッチング素子を有する スイッチング素子部、第1の電極と第2の電極との間に第1のスイッチング素子と第2の ス イ ッ チ ン グ 素 子 に 対 し 電 気 的 に 並 列 に 接 続 さ れ る コ ン デ ン サ を 有 し ス イ ッ チ ン グ 素 子 部 と積層されるコンデンサ部、を有する複数の回路ユニット、を備える。そして、隣り合う 2個の回路ユニットにおいて、一方のスイッチング素子部と他方のコンデンサ部とが隣り 合い、一方のコンデンサ部と他方のスイッチング素子とが隣り合い、一方の第1の電極と 他方の第1の電極が隣り合い、一方の第2の電極と他方の第2の電極が隣り合う。

10

20

30

40

#### [0010]

また、本実施形態の半導体装置は、第1の電極、第2の電極、第1の電極と第2の電極との間に電気的に直列に接続される第1のスイッチング素子と第2のスイッチング素子を有するスイッチング素子部、第1の電極と第2の電極との間に第1のスイッチング素子と第2のスイッチング素子に対し電気的に並列に接続されるコンデンサを有しスイッチング素子部と積層されるコンデンサ部、を有する第1の回路用ニットと第2の回路ユニット、を備える。第1の回路ユニットのスイッチング素子部と第2の回路ユニットのコンデンサ部とが隣り合い、第1の回路ユニットの第1の電極と第2の回路ユニットの第1の電極が隣り合い、第1の回路ユニットの第1の電極と第2の回路ユニットの第1の電極が隣り合い、第1の回路ユニットの第2の電極と第2の回路ユニットの第2の電極が隣り合う

[0011]

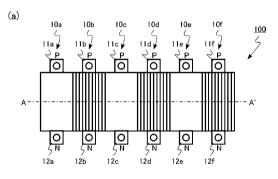

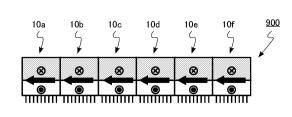

図1は、本実施形態の半導体装置の模式図である。図1(a)が平面図、図1(b)が図1(a)のAA<sup>°</sup>断面図である。本実施形態の半導体装置は、インバータ回路に用いられる半導体モジュールである。

[ 0 0 1 2 ]

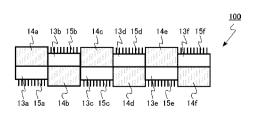

半導体モジュール 1 0 0 は、複数の回路ユニット 1 0 a ~ 1 0 f を備える。また、回路ユニット 1 0 a ~ 1 0 f は、第 1 の電極 1 1 a ~ 1 1 f 、第 2 の電極 1 2 a ~ 1 2 f 、スイッチング素子部 1 3 a ~ 1 3 f 、コンデンサ部 1 4 a ~ 1 4 f 、ヒートシンク 1 5 a ~ 1 5 f を備える。また、回路ユニット 1 0 a ~ 1 0 f は、図示しない交流電極、ゲート信号端子を備える。

[0013]

回路ユニット 1 0 a ~ 1 0 f は、スイッチング素子部 1 3 a ~ 1 3 f とコンデンサ部 1 4 a ~ 1 4 f が上下に積層された構造を備える。コンデンサ部 1 4 a ~ 1 4 f は、それぞれの回路ユニット 1 0 a ~ 1 0 f において、スイッチング素子部 1 3 a ~ 1 3 f の上部又は下部に配置される。ヒートシンク 1 5 a ~ 1 5 f は、スイッチング素子部 1 3 a ~ 1 3 f のコンデンサ部 1 4 a ~ 1 4 f を挟んで反対側に設けられる。

[0014]

複数の回路ユニット10a~10fは、互いに隣り合って横並びに配置される。

[ 0 0 1 5 ]

隣り合う 2 個の回路ユニットにおいて、一方のスイッチング素子部と他方のコンデンサ部とが隣り合い、一方のコンデンサ部と他方のスイッチング素子部とが隣り合う。例えば、隣り合う回路ユニット 1 0 a と回路ユニット 1 0 b に着目する。回路ユニット 1 0 a のスイッチング素子部 1 3 a と、回路ユニット 1 0 b のコンデンサ部 1 4 b とが隣り合う。また、回路ユニット 1 0 b のスイッチング素子部 1 3 b とが隣り合う。

[0016]

言い換えれば、隣り合う2個の回路ユニットにおいて、一方のスイッチング素子部と他方のコンデンサ部との距離が、一方のスイッチング素子部と他方のスイッチング素子部との距離よりも短い。また、言い換えれば、隣り合う2個の回路ユニットが、上下の向きが反転した関係で配置されている。他の、隣り合う2個の回路ユニットにおいても同様である。

[0017]

また、隣り合う2個の回路ユニットにおいて、第1の電極と第1の電極とが隣り合い、第2の電極と第2の電極とが隣り合う。例えば、隣り合う回路ユニット10aと回路ユニット10bに着目する。回路ユニット10aの第1の電極11aと回路ユニット10bの第1の電極11bとが隣り合う。また、回路ユニット10aの第2の電極12aと回路ユニット10bの第2の電極12bとが隣り合う。他の、隣り合う2個の回路ユニットにおいても同様である。

[ 0 0 1 8 ]

10

20

30

40

(6)

第 1 の電極 1 1 a ~ 1 1 f には、共通の電位が印加される。第 2 の電極 1 2 a ~ 1 2 f には、共通の電位が印加される。回路ユニット 1 0 a ~ 1 0 f は並列に接続される。

#### [0019]

第2の電極12a~12fには、第1の電極11a~11fよりも低い電位が印加される。第1の電極11a~11fには、正の電位が印加される。第2の電極12a~12fは、接地されるか、又は、負の電位が与えられる。

#### [0020]

図 2 は、本実施形態の回路ユニットの等価回路図である。回路ユニット 1 0 a ~ 1 0 f の回路に相当する回路図である。

## [0021]

回路ユニット 1 0 は、第 1 の電極 1 1 、第 2 の電極 1 2 、スイッチング素子部 1 3 、コンデンサ部 1 4 、交流電極 ( 第 3 の電極 ) 1 6 を備える。

#### [0022]

スイッチング素子部13は、第1のスイッチング素子18、第2のスイッチング素子2 0、第1のダイオード22、第2のダイオード24を備える。第1のスイッチング素子1 8、第2のスイッチング素子20、第1のダイオード22、第2のダイオード24は、例 えば、図示しない、絶縁性又は導電性の基板上に実装される。

## [0023]

第1のスイッチング素子18と第2のスイッチング素子20は、第1の電極11と第2の電極12との間に電気的に直列に接続される。第1のスイッチング素子18と第2のスイッチング素子20は、例えば、SiC(炭化珪素)のMOSFET(Metal Oxiside Semiconductor Field Effect Transistor)である。

#### [0024]

第1のダイオード22は、第1のスイッチング素子18に並列に接続される。第2のダイオード24は、第2のスイッチング素子20に並列に接続される。第1のダイオード2 2及び第2のダイオード24は、還流ダイオードである。

#### [0025]

コンデンサ部 1 4 は、コンデンサ 2 6 を備える。コンデンサ 2 6 は、第 1 の電極 1 1 と 第 2 の電極 1 2 との間に、第 1 のスイッチング素子 1 8 と第 2 のスイッチング素子 2 0 に 対 し電気的に並列に接続される。

## [0026]

第2の電極12には、第1の電極11よりも低い電位が印加される。第1の電極11には、正の電位が印加される。第2の電極12は、接地されるか、又は、負の電位が与えられる。

## [0027]

交流電極16は、第1のスイッチング素子18と第2のスイッチング素子20との間に接続される。第1のスイッチング素子18及び第2のスイッチング素子20のゲート電圧を制御することにより、交流電極16から交流電圧が出力される。

#### [0028]

第2のスイッチング素子20がオン状態からオフ状態へ変化する間、第1のダイオード22を通して図2中に点線矢印で示す向きに電流が流れる。また、第1のスイッチング素子18がオン状態からオフ状態へ変化する間、第2のダイオード24を通して図2中に点線矢印で示す向きに電流が流れる。

#### [0029]

次に、本実施形態の半導体装置の作用及び効果について説明する。

#### [0030]

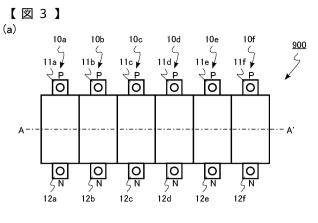

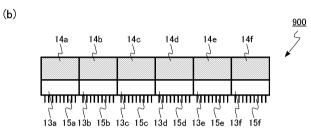

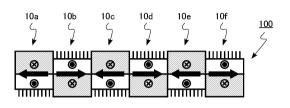

図3は、比較形態の半導体装置の模式図である。図3(a)が平面図、図3(b)が図3(a)のAA、断面図である。比較形態の半導体装置は、インバータ回路に用いられる半導体モジュールである。

10

20

30

50

40

#### [0031]

半導体モジュール900は、隣り合う2個の回路ユニットにおいて、一方のスイッチング素子部と他方のスイッチング素子部とが隣り合い、一方のコンデンサ部と他方のコンデンサ部とが隣り合う点で、本実施形態の半導体モジュール100と異なる。言い換えれば、隣り合う2個の回路ユニットが、上下の向きが同じ関係で配置されている点で、本実施形態の半導体モジュール100と異なる。

#### [0032]

半導体モジュール900は、複数の回路ユニット10a~10fに分割されることによりインダクタンスが低減する。回路ユニット10a~10fの相互インダクタンスを無視すると、半導体モジュール900をN個の回路ユニットに分割することで、半導体モジュール900のインダクタンスは1/Nに低減する。比較形態では、回路ユニットが6個であるため、インダクタンスは1/6に低減する。

#### [0033]

したがって、インダクタンスとパワー半導体モジュールを流れる電流の時間変化率(di/dt)に比例するターンオフ時の過電圧が抑制される。よって、素子破壊やノイズの発生の抑制が可能となる。

## [0034]

図4は、比較形態及び本実施形態の半導体装置の動作時の電流の向きと磁束の向きを示す図である。図4(a)が比較形態の場合、図4(b)が本実施形態の場合である。図中、黒矢印が磁束の向きを示す。

#### [ 0 0 3 5 ]

図4(a)に示すように、比較形態の半導体モジュール900では、回路ユニット10a~10fの磁束の向きは同一であり、互いに強めあうことになる。したがって、相互インダクタンスがインダクタンスに加算され、半導体モジュール900のインダクタンスが増加する。

## [0036]

半導体モジュール100においても、複数の回路ユニット10a~10fに分割されることによりインダクタンスが低減する。更に、図4(b)に示すように、本実施形態の半導体モジュール100では、回路ユニット10a~10fの磁束の向きは反対になり、互いに打消しあうことになる。したがって、相互インダクタンスがインダクタンスから減算され、インダクタンスが更に低減する。よって、更に、素子破壊やノイズの発生の抑制が可能となる。

### [0037]

また、本実施形態の半導体モジュール100では、隣り合う2個の回路ユニットにおいて、第1の電極と第1の電極とが隣り合い、第2の電極と第2の電極とが隣り合う。したがって、複数の第1の電極間の接続、及び、複数の第2の電極間の接続が容易である。

## [0038]

本実施形態によれば、インダクタンスが低減し、素子破壊やノイズの発生の抑制が可能となる半導体モジュールが実現される。

## [0039]

なお、ここでは、回路ユニットが6個の場合を例に説明したが、回路ユニットの数は6個に限定されるものではない。回路ユニットが2個以上であれば、任意の数とすることが可能である。

## [0040]

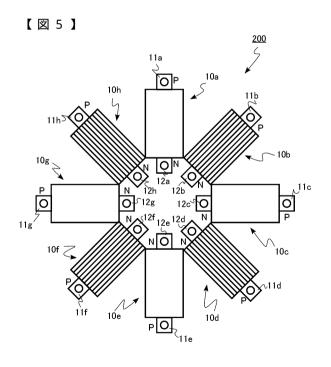

## (第2の実施形態)

本実施形態の半導体装置は、回路ユニットが環状に配置される以外は、第1の実施形態と同様である。したがって、第1の実施形態と重複する内容については、一部記述を省略する。

## [ 0 0 4 1 ]

図5は、本実施形態の半導体装置の模式平面図である。本実施形態の半導体装置は、イ

10

20

30

30

40

ンバータ回路に用いられる半導体モジュールである。

#### [0042]

半導体モジュール200は、複数の回路ユニット10a~10hが、環状に配置される。回路ユニット10a~10hのそれぞれの第1の電極11a~11hと第2の電極12a~12hを結ぶ方向が、放射状になるよう回路ユニット10a~10hが配置される。 言い換えれば、回路ユニット10a~10hはサークル状に配置される。

#### [0043]

例えば、図1に示す第1の実施形態の半導体モジュールでは、両端に位置する回路ユニット10aと回路ユニット10f以外の回路ユニット10b~10eは、隣り合う2個の回路ユニットから磁束の影響を受ける。しかし、両端に位置する回路ユニット10aと回路ユニット10fでは、隣り合う1個の回路ユニットの磁束のみの影響を受ける。したがって、回路ユニット10a~10f間で電流分布が不均一となる。

#### [0044]

回路ユニット10a~10f間で電流分布が不均一となると、半導体モジュールの定格電流に対する設計マージンを大きくとることが必要となる。したがって、半導体モジュールの製造コストが増大する恐れがある。

### [0045]

図 5 に示すように、本実施形態の半導体モジュール 2 0 0 では、すべての回路ユニット 1 0 a ~ 1 0 h が、隣り合う 2 個の回路ユニットから、同様に磁束の影響を受ける。したがって、回路ユニット 1 0 a ~ 1 0 h 間で電流分布の均一性が向上する。

#### [0046]

回路ユニット10a~10h間で電流分布の均一性が向上すると、半導体モジュールの 定格電流に対する設計マージンを小さくすることが可能となる。したがって、半導体モジュールの製造コストを削減することが可能となる。

## [0047]

本実施形態によれば、インダクタンスが低減し、素子破壊やノイズの発生の抑制が可能となる半導体モジュールが実現される。更に、回路ユニット間での電流分布の均一性が向上し、半導体モジュールの製造コストを削減することが可能となる。

## [0048]

なお、ここでは、回路ユニットが8個の場合を例に説明したが、回路ユニットの数は8個に限定されるものではない。回路ユニットが4個以上且つ偶数であれば、隣り合う回路 ユニットの磁束の向きが逆方向となり、任意の数とすることが可能である。

## [0049]

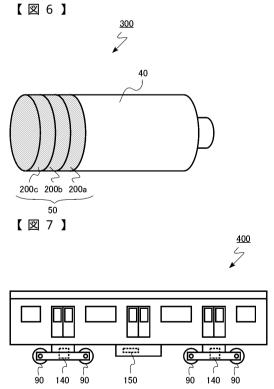

## (第3の実施形態)

本実施形態のインバータ回路及び駆動装置は、第2の実施形態の半導体装置を備える駆動装置である。

## [0050]

図 6 は、本実施形態の半導体装置を備える駆動装置の模式斜視図である。駆動装置 3 0 0 は、モーター 4 0 と、インバータ回路 5 0 を備える。

#### [0051]

インバータ回路50は、モーター40の背面に設けられる。インバータ回路50は、第2の実施形態の半導体モジュール200と同一構成の3個の半導体モジュール200a、200b、200 cを並列に接続することで、3個の交流電圧の出力端子U、V、Wを備える三相のインバータ回路50が実現される。インバータ回路50から出力される交流電圧により、モーター40が駆動する。

## [0052]

本実施形態のインバータ回路50及び駆動装置300においても、素子破壊やノイズの

10

20

30

40

発生の抑制が可能となる。また、製造コストを削減することが可能となる。また、半導体モジュール 2 0 0 a 、 2 0 0 b 、 2 0 0 c のそれぞれが、回路ユニットをサークル状に配置することにより、円盤形状となっている。したがって、モーター 4 0 の背面に設けることが可能となり、駆動装置 3 0 0 の小型化が実現できる。

- [0053]

- (第4の実施形態)

本実施形態の車両は、第1の実施形態の半導体装置を備える車両である。

[0054]

図7は、本実施形態の車両の模式図である。本実施形態の車両400は、鉄道車両である。車両400は、モーター140と、インバータ回路150を備える。

[0055]

インバータ回路 1 5 0 は、第 1 の実施形態の半導体モジュール 1 0 0 と同一構成の 3 個の半導体モジュールで構成される。 3 個の半導体モジュールを並列に接続することで、 3 個の交流電圧の出力端子 U、 V、 Wを備える三相のインバータ回路 1 5 0 が実現される。

[0056]

インバータ回路 1 5 0 から出力される交流電圧により、モーター 1 4 0 が駆動する。モーター 1 4 0 により車両 4 0 0 の車輪 9 0 が回転する。

[0057]

本実施形態の車両400は、素子破壊やノイズの発生の抑制されたインバータ回路15 0を有することにより、高い信頼性を備える。

[0058]

(第5の実施形態)

本実施形態の車両は、第1の実施形態の半導体装置を備える車両である。

[0059]

図8は、本実施形態の車両の模式図である。本実施形態の車両1000は、自動車である。車両1000は、モーター140と、インバータ回路150を備える。

[0060]

インバータ回路 1 5 0 は、第 1 の実施形態の半導体モジュール 1 0 0 と同一構成の 3 個の半導体モジュールで構成される。 3 個の半導体モジュールを並列に接続することで、 3 個の交流電圧の出力端子 U、 V、 Wを備える三相のインバータ回路 1 5 0 が実現される。

[0061]

インバータ回路 1 5 0 から出力される交流電圧により、モーター 1 4 0 が駆動する。モーター 1 4 0 により車両 1 0 0 0 の車輪 9 0 が回転する。

[0062]

本実施形態の車両1000は、素子破壊やノイズの発生の抑制されたインバータ回路1 50を有することにより、高い信頼性を備える。

- [0063]

- (第6の実施形態)

本実施形態の昇降機は、第1の実施形態の半導体装置を備える昇降機である。

[0064]

図9は、本実施形態の昇降機(エレベータ)の模式図である。本実施形態の昇降機1100は、かご1010、カウンターウエイト1012、ワイヤロープ1014、巻上機1016、モーター140と、インバータ回路150を備える。

[0065]

インバータ回路 1 5 0 は、第 1 の実施形態の半導体モジュール 1 0 0 と同一構成の 3 個の半導体モジュールで構成される。 3 個の半導体モジュールを並列に接続することで、 3 個の交流電圧の出力端子 U、 V、 Wを備える三相のインバータ回路 1 5 0 が実現される。

[0066]

インバータ回路 1 5 0 から出力される交流電圧により、モーター 1 4 0 が駆動する。モーター 1 4 0 により巻上機 1 0 1 6 が回転し、かご 1 0 1 0 が昇降する。

10

20

30

40

### [0067]

本実施形態の昇降機1100は、素子破壊やノイズの発生の抑制されたインバータ回路150を有することにより、高い信頼性を備える。

### 【実施例】

[0068]

以下、実施例を説明する。

[0069]

図 1 0 は、実施例の説明図である。図 1 0 ( a ) がシミュレーションを行った構造の説明図である。図 1 0 ( b ) がシミュレーションの結果を示す図である。

[0070]

図10(a)に示すように、反転させた2つの回路ユニット10aと10bを相対的に上下方向に動かし、各回路ユニットの配線基板面のズレ(t)を変化させた。ズレ(t)を変化させて、各回路用ユニット間の結合係数(k)をシミュレーションにより求めた。 【0071】

配線基板面のズレ(t)と結合係数(k)との関係を占めす。配線基板面が一致する位置(t=0)から、tが正の方向(図10(a)中、回路ユニット10bが相対的に上に行く方向)にずれることで結合係数が負になることがわかる。すなわち、隣り合う2個の回路ユニット10aと10bにおいて、一方のスイッチング素子部13aと他方のコンデンサ部14bとが隣り合い、一方のコンデンサ部14aと他方のスイッチング素子部13bとが隣り合うようにすることで、結合係数が負になる。結合係数が負になることにより、相互インダクタンスがインダクタンスから減算されることになり、インダクタンスが低減する。

[0072]

実施例により、実施形態の効果が明らかになった。

[0073]

以上、第1乃至第3の実施形態においては、第1のスイッチング素子及び第2のスイッチング素子について、MOSFETを例に説明したが、IGBT(Insulated Gate Bipolar Transistor)やHEMT(High Electron Mobility Transistor)等を適用することも可能である。

[0074]

また、第1乃至第3の実施形態においては、第1のスイッチング素子及び第2のスイッチング素子の半導体材料としてSiC(炭化珪素)を例に説明したが、Si(シリコン)やGaN(窒化ガリウム)等を適用することも可能である。

[0075]

また、第4乃至第6の実施形態において、本発明の半導体装置を車両やエレベータに適用する場合を例に説明したが、本発明の半導体装置を例えば、太陽光発電システムのパワーコンディショナー等に適用することも可能である。

[0076]

本発明のいくつかの実施形態を説明したが、これらの実施形態は、例として提示したものであり、発明の範囲を限定することは意図していない。これら新規な実施形態は、その他の様々な形態で実施されることが可能であり、発明の要旨を逸脱しない範囲で、種々の省略、置き換え、変更を行うことができる。例えば、一実施形態の構成要素を他の実施形態の構成要素と置き換え又は変更してもよい。これら実施形態やその変形は、発明の範囲や要旨に含まれるとともに、特許請求の範囲に記載された発明とその均等の範囲に含まれる。

## 【符号の説明】

[0077]

1 0回路ユニット1 0 a ~ h回路ユニット1 1第1の電極

10

20

30

40

```

1 1 a ~ h

第1の電極

1 2

第2の電極

1 2 a ~ h

第2の電極

スイッチング素子部

1 3

1 3 a ~ f

スイッチング素子部

コンデンサ部

1 4

コンデンサ部

1 4 a ~ f

1 5 a ~ f

ヒートシンク

交流電極(第3の電極)

1 6

10

第1のスイッチング素子

1 8

2 0

第2のスイッチング素子

第1のダイオード

2 2

2 4

第2のダイオード

2 6

コンデンサ

モーター

4 0

5 0

インバータ回路

1 0 0

半導体モジュール(半導体装置)

1 4 0

モーター

1 5 0

インバータ回路

20

2 0 0

半導体モジュール(半導体装置)

2 0 0 a ~ c

半導体モジュール(半導体装置)

駆動装置

3 0 0

4 0 0

車両

1 0 0 0

車両

1 1 0 0

昇降機

【図2】

【図1】

(a)

Α-

26

-oV<sup>16</sup>

h

12b

電流

12c

12d

12e

AC

(b)

13d 15d

13f 15f

тінтін

14b

13c 15c

14d

13e 15e

```

(a)

(b)

【図4】

【図9】

(b)

0.04 0.02 0 -0.02 -0.04 結合係数 k (-) -0.06 -0.08 -0.1 -0.12 -0.14 -0.16 -0.18 0 3 6 配線基板面のズレ t (mm)

## フロントページの続き

(72)発明者 清水 達雄 東京都港区芝浦一丁目 1 番 1 号 株式会社東芝内

(72)発明者 大橋 輝之 東京都港区芝浦一丁目 1 番 1 号 株式会社東芝内

Fターム(参考) 5H770 AA21 BA02 BA03 DA44 PA22 PA42 QA06 QA08 QA22