### (12) INTERNATIONAL APPLICATION PUBLISHED UNDER THE PATENT COOPERATION TREATY (PCT)

# (19) World Intellectual Property Organization

International Bureau

(10) International Publication Number WO 2019/245931 A1

(51) International Patent Classification: *H04L 27/26* (2006.01) *H04B 7/0456* (2017.01)

(21) International Application Number:

PCT/US2019/037399

(22) International Filing Date:

15 June 2019 (15.06.2019)

(25) Filing Language:

English

(26) Publication Language:

English

(30) Priority Data:

62/686,083

17 June 2018 (17.06,2018)

US

- (71) Applicant: GENGHISCOMM HOLDINGS, LLC [US/US]; PO BOX 17355, Boulder, Colorado 80308 (US).

- (72) Inventor: SHATTIL, Steve; 5002 Phoenix Dr., Cheyenne, Wyoming 82001 (US).

- (74) Agent: SHATTIL, Steven; PO Box 17355, Boulder, Colorado 80308 (US).

- (81) Designated States (unless otherwise indicated, for every kind of national protection available): AE, AG, AL, AM, AO, AT, AU, AZ, BA, BB, BG, BH, BN, BR, BW, BY, BZ, CA, CH, CL, CN, CO, CR, CU, CZ, DE, DJ, DK, DM, DO, DZ, EC, EE, EG, ES, FI, GB, GD, GE, GH, GM, GT, HN, HR, HU, ID, IL, IN, IR, IS, JO, JP, KE, KG, KH, KN, KP, KR, KW, KZ, LA, LC, LK, LR, LS, LU, LY, MA, MD, ME,

MG, MK, MN, MW, MX, MY, MZ, NA, NG, NI, NO, NZ, OM, PA, PE, PG, PH, PL, PT, QA, RO, RS, RU, RW, SA, SC, SD, SE, SG, SK, SL, SM, ST, SV, SY, TH, TJ, TM, TN, TR, TT, TZ, UA, UG, US, UZ, VC, VN, ZA, ZM, ZW.

(84) Designated States (unless otherwise indicated, for every kind of regional protection available): ARIPO (BW, GH, GM, KE, LR, LS, MW, MZ, NA, RW, SD, SL, ST, SZ, TZ, UG, ZM, ZW), Eurasian (AM, AZ, BY, KG, KZ, RU, TJ, TM), European (AL, AT, BE, BG, CH, CY, CZ, DE, DK, EE, ES, FI, FR, GB, GR, HR, HU, IE, IS, IT, LT, LU, LV, MC, MK, MT, NL, NO, PL, PT, RO, RS, SE, SI, SK, SM, TR), OAPI (BF, BJ, CF, CG, CI, CM, GA, GN, GQ, GW, KM, ML, MR, NE, SN, TD, TG).

### **Declarations under Rule 4.17:**

- as to applicant's entitlement to apply for and be granted a patent (Rule 4.17(ii))

- of inventorship (Rule 4.17(iv))

#### **Published:**

with international search report (Art. 21(3))

(54) Title: DISTRIBUTED RADIO SYSTEM

(57) **Abstract:** Systems, methods, and apparatuses for synthesizing a wireless communication signal are provided. A base expanded matrix is generated, wherein a sum of values in each row of the base expanded matrix produces a base signal vector. Values in at least one column of the base expanded matrix are updated to produce an updated expanded matrix. The values in each row of the updated expanded matrix are summed to produce an updated signal vector. The updated signal vector is transmitted over a wireless channel.

### DISTRIBUTED RADIO SYSTEM

### CROSS REFERENCE TO PRIOR APPLICATIONS

[0001] This application claims the priority benefit of United States Patent Application Serial No. 62/686,083, filed on June 17, 2018.

### BACKGROUND

[0002] Aspects of this disclosure relate generally to communication networks, and more particularly, to computationally efficient signal synthesis and signal analysis.

[0003] Wireless communication systems (e.g. wireless networks) provide various telecommunication services, such as telephony, video, data, messaging, and broadcasts. Wireless communication systems may employ multiple-access technologies capable of supporting communication with multiple users by sharing available system resources (e.g., time, frequency, power). Examples of such multiple-access technologies include code division multiple access (CDMA), time division multiple access (TDMA), frequency division multiple access (FDMA), orthogonal frequency division multiple access (OFDMA), single-carrier frequency divisional multiple access (SC-FDMA), and discrete Fourier transform spread orthogonal division multiplexing (DFT-s-OFDM). It should be understood that SC-FDM and DFT-s-OFDM are two names of essentially similar technologies, known as Carrier Interferometry (CI). However, DFT-s-OFDM is the terminology used in 3GPP specifications.

[0004] These multiple access technologies have been adopted in various telecommunication and wireless network standards. For example, fifth generation (5G) (also called New Radio (NR)) wireless access is being developed with three broad use case families in mind: enhanced mobile broadband (eMBB), massive machine-type communications (mMTC) and ultra-reliable low-latency communications (URLLC). Beyond 5G refers to visions for future generations of wireless communications (e.g., 5G-Advanced, 5G-Extreme, 6G) that enable groundbreaking high-bandwidth, low-latency, massive capacity, and massive connectivity.

### **SUMMARY**

[0005] The following presents a simplified summary of one or more aspects in order to provide a basic understanding of such aspects. This summary is not an extensive overview of

all contemplated aspects, and is intended to neither identify key or critical elements of all aspects nor delineate the scope of any or all aspects. Its sole purpose is to present some concepts of one or more aspects in a simplified form as a prelude to the more detailed description that follows.

[0006] To realize 5G and Beyond-5G, new networking technologies are being developed, beginning with Massive multiple-input multiple output (MIMO), Cooperative MIMO, millimeter wave communications, non-orthogonal multiple access (NOMA), and device-to-device (D2D) via proximity services (ProSe). 5G will likely evolve to include mobile and airborne relays. Many infrastructure functions can be pushed to the network's edge to reduce latency, extend coverage, enhance versatility, and exploit the computational resources of the vast number of user devices. New paradigms, such as software-defined networking and fog computing are emerging. Artificial Intelligence (AI), such as deep learning neural networks, can be developed for many network functions, and with access to the vast cloud and fog resources, spawn new industries. Cooperative AI can be developed for situational awareness, security, threat mitigation, navigation, financial services, environmental monitoring.

**[0007]** Network devices commonly perform linear algebra computations. Matrix products are a central operation in computational applications of linear algebra. Their computational complexity is  $O(n^3)$  (for  $n \times n$  matrices) for the basic algorithm. The complexity is  $O(n^{2.373})$  for the asymptotically fastest algorithm. This nonlinear complexity means that the matrix product is often the critical part of many algorithms. Techniques that enable a processor in a network device to more efficiently compute the matrix product can be useful in one or more of the networks, applications, and use case families mentioned in this disclosure, as reduced latency, improved power efficiency, improved computational efficiency, and/or combinations thereof may be desired.

[0008] Aspects of the disclosure can be configured to operate with any of the multiple-access technologies, networking technologies, use case families, and telecommunication and wireless network standards mentioned herein. All techniques can be integrated with disclosed aspects, such as with signal coding/decoding in a modem of a network device. Disclosed aspects can be implemented in a mobile ad hoc network (MANET), peer-to-peer network, vehicular ad hoc network (VANET), smart phone ad hoc network (SPAN), Cloud-relay network, flying ad hoc network (FANET), distributed antenna system (DAS), wireless sensor

network (WSN), wireless personal area network (WPAN), wireless heterogeneous network (HetNet), Internet area network (IAN), near-me area network (NAN), or any combinations thereof.

[0009] A network device can include one or more base stations, one or more user equipment devices (UEs), one or more relay stations, and/or access terminals of various types. A network device may comprise a virtual machine, a virtual antenna array, a distributed software-defined radio, a virtual radio transceiver, a fog, a Cloud, or combinations thereof.

[0010] In some examples, a base station may include or be referred to by those skilled in the art as a base transceiver station, a radio base station, an access point, an access node, a radio transceiver, a NodeB, an eNodeB (eNB), a gNodeB (gNB), a Home NodeB, a Home eNodeB, a Home gNodeB, a relay, or some other suitable terminology. A UE may include or be referred to by those skilled in the art as a mobile station, a subscriber station, a mobile unit, a subscriber unit, a wireless unit, a remote unit, a mobile device, a wireless device, a wireless communications device, a remote device, a mobile subscriber station, an access terminal, a mobile terminal, a wireless terminal, a remote terminal, a handset, a user agent, a mobile client, a client, a modem, or some other suitable terminology. A UE may include or be referred to as an Internet-of-Thing (IoT) device, an Internet of Vehicles (IoV) device, a Machine-to-Machine (M2M) device, or a sensor or a data aggregation point (DAP) in a wireless sensor network.

**[0011]** In an aspect of the disclosure, a method of wireless communication may include synthesizing a communication signal and transmitting the communication signal over a wireless channel. The synthesizing can comprise generating a base expanded matrix having a plurality of rows and a plurality of columns, wherein a sum of values in each row produces a base signal vector; updating values in at least one column of the base expanded matrix to produce an updated expanded matrix; and summing values in each row of the updated expanded matrix to produce an updated signal vector. The updated signal vector may be the communication signal that is transmitted over the wireless channel in a wireless communications network. The method of wireless communication may be performed in combination with any aspects disclosed herein.

[0012] In an aspect of the disclosure, a network device comprises a memory and at least one processor in communication with the memory. The at least one processor may be configured to perform the method of wireless communication above. The at least one processor may be configured to perform the method of wireless communication above in combination with any aspects disclosed herein.

[0013] In an aspect of the disclosure, a computer-readable medium storing computer code executable by a processor for causing a computer to implement the method of wireless communication above. The code may be configured to perform the method of wireless communication above in combination with any aspects disclosed herein. The computer-readable medium and the code may be referred to as a computer program product.

[0014] In an aspect of the disclosure, a network device (e.g., a wireless communication device) may include means for synthesizing a communication signal and means for transmitting the communication signal over a wireless channel. The means for synthesizing may comprise means for generating a base expanded matrix having a plurality of rows and a plurality of columns, wherein a sum of values in each row produces a base signal vector; means for updating values in at least one column of the base expanded matrix to produce an updated expanded matrix; and means for summing values in each row of the updated expanded matrix to produce an updated signal vector. The updated signal vector may be the communication signal that is transmitted over the wireless channel. The wireless communication device may be further configured to perform any of the aspects disclosed herein.

[0015] By way of example, but without limitation, means for generating an expanded matrix can comprise a physical data storage medium, such as (but not limited to) random access memory, hard drive, virtual memory, and the like; and can comprise a data buffer, for example, and a data-processor for organizing and/or manipulating data in the data buffer and optionally provide for managing I/O operations. The means for generating the expanded matrix can provide a data output format and/or memory-access scheme designed to enable or facilitate the computational processing disclosed herein. While summing the elements in each row of the base expanded matrix can produce a base signal vector, the summing describes a characteristic feature of the base expanded matrix, and is therefore not a required step in generating the base expanded matrix.

**[0016]** By way of example, but without limitation, means for updating can comprise circuits, processors, or computer program code (stored in memory as software and/or firmware) in combination with a general-purpose processor configured to perform multiplicative and/or arithmetic update operations on the data values of the expanded matrix. In some aspects, updating can be configured to perform bit operations on the data. Update operations may provide for shifting, swapping, or otherwise rearranging data values in memory.

[0017] Aspects disclosed herein can comprise data-independent updating schedules, data-dependent updating schedules, and combinations thereof. In some aspects, the parameters to be updated in a data-independent updating schedule are chosen at random. Aspects may employ a stochastic partial update algorithm. In one example, parameters to be updated are partitioned into multiple subsets of the total set of parameters, and then the subsets are randomly selected to be updated in each iteration. In some aspects, a predetermined schedule of parameters to be updated in each iteration is provided.

[0018] Update algorithms disclosed herein can be configured to reduce the number of computations needed to generate a transmission signal (such as a signal having one or more desired properties), or to process a received signal. The update algorithms can take into account costs for program and data memory. For example, the reduction in number of execution cycles might be offset by the additional cycles needed for storing data in intermediate steps. Thus, a processing metric to be optimized by the algorithm can comprise any combination of these costs.

**[0019]** A step size used for updating may be determined to provide desirable conditions, such as convergence conditions and/or stability. The step size may be constant or it may be variable based on one or more measurement criteria. In some aspects, conditions on the step size parameter are derived that provide convergence in the mean and the mean square sense.

**[0020]** By way of example, but without limitation, means for summing can include program code that configures a processor to read data from memory such that the read data is grouped into blocks corresponding to the matrix rows, and then the data values in each row are summed. Various computer circuitry and/or logic may be configured with an I/O controller to effect such arithmetic operations. A CPU's accumulator (e.g., general purpose registers that

function as an accumulator) may be employed for such arithmetic operations, and the results can be written to memory to produce the updated vector(s).

[0021] In some aspects, updating comprises an operation developed from a data-symbol matrix and a weight matrix that commute under multiplication, thereby removing the data-symbol matrix and its inverse from the operation. For example, data-symbol values and weight values may be configured functionally to comprise matrix structures that commute at least with each other under multiplication. These matrix structures can be employed as operators and/or operands. In some aspects, the data-symbol matrix commutes with the inverse of the weight matrix. In some aspects, the weight matrix commutes with the inverse of the data-symbol matrix. In some aspects, the inverse of a base weight matrix (which can be an initial weight matrix or a previous update weight matrix) is removed by setting the base weight matrix to an Identity matrix. This can be done implicitly or explicitly. In an aspect, the initial weight matrix is set to the Identity matrix. In an aspect, the current data-symbol matrix is set equal to a product of a previous weight matrix with a previous data-symbol matrix. In an aspect, a previous updated expanded matrix is designated as the current base expanded matrix.

[0022] In some aspects, a computing system learns and/or detects features in base and/or updated data, and/or provides updates based on an application of one or more machine learning algorithms or processes to expanded data.

**[0023]** In an aspect of the disclosure, means for generating, the means for updating, and the means for summing comprises a processor; and the network device further comprises a memory coupled to the processor. The processor may be configured to perform the method of wireless communication above in combination with any aspects disclosed herein.

[0024] To the accomplishment of the foregoing and related ends, the one or more aspects comprise the features hereinafter fully described and particularly pointed out in the claims. The following description and the annexed drawings set forth in detail certain illustrative features of the one or more aspects. These features are indicative, however, of but a few of the various ways in which the principles of various aspects may be employed, and this description is intended to include all such aspects and their equivalents.

## BRIEF DESCRIPTION OF THE DRAWINGS

[0025] The disclosed aspects will hereinafter be described in conjunction with the appended drawings, provided to illustrate and not to limit the disclosed aspects, wherein like designations denote like elements, and in which:

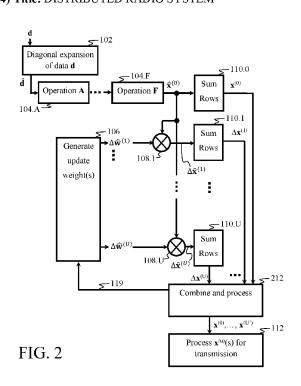

[0026] FIGS. 1A, and 2-8 are flow diagrams of example methods, functional components of an apparatus, and software modules according to aspects of the presents disclosure, which may be used to synthesize at least one signal that is transmitted over a wireless channel in a wireless network.

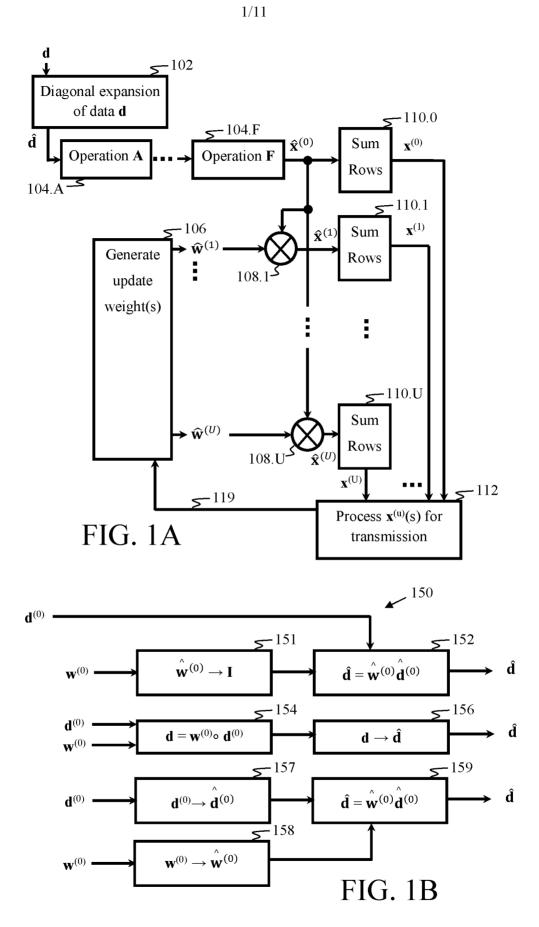

[0027] FIG. 1B is a flow diagram of example methods, functional components of an apparatus, and software modules according to aspects of the presents disclosure, and which may be implemented with any of the aspects disclosed herein.

[0028] FIG. 9 is a schematic diagram of example components of a network device, such as a UE, that can be configured according to aspects of the presents disclosure.

[0029] FIG. 10 is a schematic diagram of example components of a network device, such as a base station, that can be configured according to aspects of the presents disclosure.

[0030] FIG. 11A is a schematic diagram of example components in a computer processor (such as a Graphics Processing Unit (GPU)) architecture that can be configured for signal-processing functions according to aspects of the present disclosure.

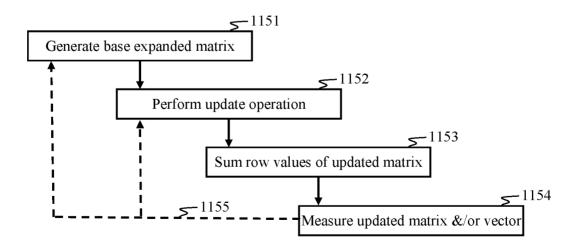

[0031] FIG. 11B is a flow diagram that depicts some aspects of the disclosure.

[0032] It is contemplated that elements described in one aspect may be beneficially utilized on other aspects without specific recitation.

## DETAILED DESCRIPTION

[0033] The description that follows includes exemplary systems, methods, techniques, instruction sequences, and computer program products that embody techniques of this disclosure. However, it is understood that the described aspects may be practiced without these specific details. Apparatuses and methods are described in the following description

and illustrated in the accompanying drawings by various blocks, modules, components, circuits, steps, processes, algorithms, etc. (collectively referred to as "elements"). These elements may be implemented using electronic hardware, computer software, firmware, or any combination thereof.

**[0034]** In accordance with some general aspects of the disclosure, a data sequence (denoted by a length-N vector  $\mathbf{d} = [\mathbf{d}_0, \dots, \mathbf{d}_{N-1}]$ ) is processed in a network device to generate a discrete-time signal (denoted by vector  $\mathbf{x}$ ) of length-N or longer for transmission in a communication network:

### x = FEDCBAd

where **A**, **B**, **C**, **D**, **E**, **F** denote any number of operations performed on **d**. The operations can comprise matrix multiplications, invertible transform operations, and/or other linear operations. The term "matrix" used herein can be understood to include tensors. The operations can comprise spreading, multiple-access encoding, transform precoding, resource unit mapping, layer mapping, selective mapping, filtering, pulse shaping, spatial (and/or frequency) precoding, invertible transforms (e.g., FFT, short-time Fourier transform, fractional Fourier transform, space-time Fourier transform, geometric Fourier transform, discrete cosine transform, Gabor transform, Laplace transform, Mellin transform, Borel transform, wavelet transform, Constant-Q transform, Newland transform, (fast) S transform, Z transform, Chirplet transform, Wigner transform, integral transform, linear canonical transform, and multi-dimensional transforms thereof), and/or others.

[0035] In one aspect, **A** may be a spreading matrix (e.g., one or more spreading code vectors), **B** may be a spread-DFT operator (such as an FFT), **C** may be a pulse-shaping filter, **D** may be a MIMO precoding matrix, **E** may be an OFDM subcarrier mapping, and **F** may be OFDM modulation (e.g., an IFFT). Two or more consecutive ones of the operations (e.g., **A**, **B**, **C**, **D**, **E**, **F**) may be combined into a single operator, thereby exploiting the associative property of matrix multiplication. The number of operations may be greater than or less than the number of operations depicted herein. Furthermore, **d** may comprise transform(s), matrix product(s), and/or encoded version of data.

[0036] Some aspects disclosed herein relate generally to calculating an update to  $\mathbf{x}$  (the update to  $\mathbf{x}$  being denoted as  $\mathbf{x}^{(u)}$ , where update index u > 0) that would result from an update operation performed on  $\mathbf{d}$  (or on a product or transform involving  $\mathbf{d}$ ) by configuring a matrix

expansion of an initial or previous vector  $\mathbf{x}$  (which may be denoted as  $\mathbf{x}^{(0)}$  or  $\mathbf{x}^{(u-1)}$ ) and performing operations on the matrix expansion. This can avoid repeating the computations of one or more of the operations (e.g.,  $\mathbf{A}$ ,  $\mathbf{B}$ ,  $\mathbf{C}$ ,  $\mathbf{D}$ ,  $\mathbf{E}$ ,  $\mathbf{F}$ ), thereby reducing computational complexity (e.g., the number of complex multiplications). Thus, the update can be performed independently of one or more of the operations (e.g.,  $\mathbf{A}$ ,  $\mathbf{B}$ ,  $\mathbf{C}$ ,  $\mathbf{D}$ ,  $\mathbf{E}$ ,  $\mathbf{F}$ ). For example, an update operation on the matrix expansion of  $\mathbf{d}$  can instead be performed on the matrix expansion of  $\mathbf{x}^{(0)}$  or  $\mathbf{x}^{(u-1)}$  without needing to account for how any of the operations (e.g.,  $\mathbf{A}$ ,  $\mathbf{B}$ ,  $\mathbf{C}$ ,  $\mathbf{D}$ ,  $\mathbf{E}$ ,  $\mathbf{F}$ ) affect updates to the vector  $\mathbf{d}$ .

[0037] In one example, an update performed on **d** can be represented as a Hadamard product of a length-N weight vector  $\mathbf{w}^{(u)}$  (=  $\left[\mathbf{w}_{0}^{(u)}, \ldots, \mathbf{w}_{N-1}^{(u)}\right]$ ) with **d**. A weight vector corresponding to the initial or previous **d** is expressed as  $\mathbf{w}^{(0)}$  (u = 0). The Hadamard product (also known as the Schur product or the entrywise product) is a binary operation that takes two matrices of the same dimensions and produces another matrix of the same dimension as the operands, where each element i, j is the product of elements i, j of the original two matrices. For two matrices  $\mathbf{X}$  and  $\mathbf{Y}$  of the same dimension  $m \times n$ , the Hadamard product  $\mathbf{X} \circ \mathbf{Y}$  is a matrix of the same dimension as the operands, with elements given by

$$(X \circ Y)_{i,j} = (X)_{i,j}(Y)_{i,j}$$

The Hadamard product is associative and distributive. Unlike the matrix product, the Hadamard product is commutative. Thus, in some aspects, matrix forms that commute, and operations thereon, can be configured to provide a result that is analogous to the Hadamard product of two vectors. For example, diagonal matrices or Toeplitz matrices may be employed. Disclosed aspects that exploit this and other features can provide advantageous solutions for synthesizing and/or analyzing signals employed in data communications. Such aspects can improve the functioning of a computer processor and related technological processes disclosed herein. Furthermore, data structures disclosed herein can improve the way a computer processor stores and retrieves data in memory for signal-processing applications in wireless communications. Some benefits of the disclosed aspects include faster processing time, improved flexibility for updating signal features, and improvements to how a computer stores and reads data from memory to perform signal processing. In some aspects, a network device comprises a modem having a signal-processing component that includes a signal coding/decoding scheme configured to generate and transmit, or alternatively, to receive a signal in accordance with the figures and description.

[0038] The present disclosure provides examples, and is not limiting of the scope, applicability, or examples set forth in the claims. Changes may be made in the function and arrangement of elements discussed without departing from the scope of the disclosure. Various examples may omit, substitute, or add various procedures or components as appropriate. For instance, the methods described may be performed in an order different from that described, and various steps may be added, omitted, or combined. Also, features described with respect to some examples may be combined in other examples.

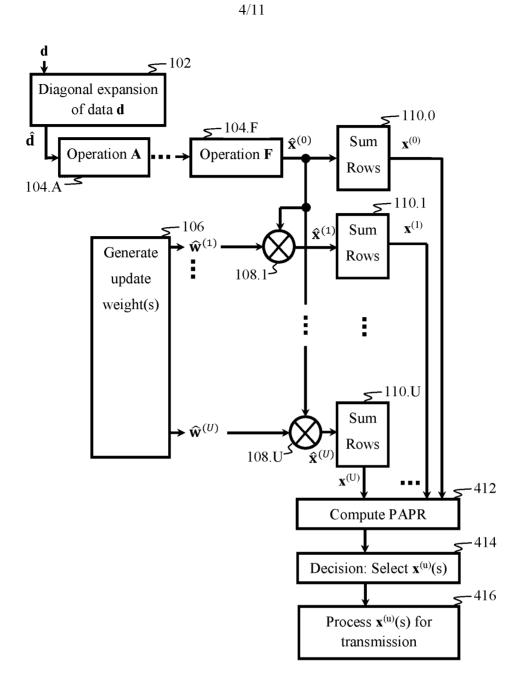

[0039] FIG. 1A depicts some method and apparatus aspects of the disclosure. Input data symbols can be formatted (or otherwise implemented functionally) 102 to generate a diagonal expansion matrix  $\hat{\mathbf{d}}$ . The data symbols may be processed for transmission in a wireless communication network. In accordance with some aspects, the data vector  $\mathbf{d}$  can be implemented functionally as an NXN diagonal matrix  $\hat{\mathbf{d}}$  with diagonal elements set to the elements in  $\mathbf{d}$ :

$$\hat{\mathbf{d}} = \begin{vmatrix} d_0 & 0 & \cdots & 0 \\ 0 & d_1 & \cdots & 0 \\ \vdots & \vdots & \ddots & \vdots \\ 0 & 0 & \cdots & d_{N-1} \end{vmatrix}$$

This is referred to as a diagonal expansion matrix of **d**.

**[0040]** In weight generation 106, one or more (*U*) update weights are computed. The weight vectors can be implemented functionally as NXN diagonal matrix  $\hat{\mathbf{w}}^{(u)}$  with diagonal elements set to the elements in  $\mathbf{w}^{(u)}$ :

$$\hat{\mathbf{w}}^{(u)} = \begin{bmatrix} w_0^{(u)} & 0 & \dots & 0 \\ 0 & w_1^{(u)} & \dots & 0 \\ \vdots & \vdots & \ddots & \vdots \\ 0 & 0 & \dots & w_n^{(u)} \end{bmatrix}$$

One or more operations, such as a plurality of operations  $\mathbf{A}, \dots, \mathbf{F}$  (104.A-104.F), can be performed on the diagonal expansion matrix (or equivalent representation) of  $\mathbf{d}$  to produce an expanded matrix  $\hat{\mathbf{x}}^{(u)}$ , which may be an expanded discrete-time matrix, for example. In some aspects, an initial weighting  $\mathbf{w}^{(0)}$  (not shown) may be performed explicitly on the data. In some aspects, the effects of any previous weighting is incorporated into the data values.

[0041] Operations  $\mathbf{A}, \dots, \mathbf{F}$  (104.A-104.F) can comprise vectors, matrices, and/or tensors, and can be implemented via transform operations, including fast transforms. In one aspect, operator  $\mathbf{A}$  may normally comprise a Hadamard product of vector  $\mathbf{a}$  with vector  $\mathbf{d}$ , but is configured to operate with expanded matrices disclosed herein. For example,  $\mathbf{a}$  can be converted to diagonal expansion matrix  $\hat{\mathbf{a}}$ . Then matrix multiplication  $\hat{\mathbf{a}}\hat{\mathbf{d}}$  produces an NXN diagonal matrix whose diagonal elements are the values of the Hadamard product  $\mathbf{a} \cdot \mathbf{d}$ . One or more subsequent operations (e.g.,  $\mathbf{B}, \dots, \mathbf{F}$ ) are then performed on the diagonal expansion matrix  $\hat{\mathbf{a}}\hat{\mathbf{d}}$  to produce expanded discrete-time matrix  $\hat{\mathbf{x}}^{(u)}$ , which can be an initial (index  $\mathbf{u} = 0$ ) or updated ( $\mathbf{u} > 0$ ) expanded discrete-time matrix.

[0042] The methods and apparatus aspects disclosed herein with respect to mathematical operations and matrix (any matrix, including vectors and tensors) structures can be implemented functionally so as to effect the disclosed operations and structures. Such implementations may not explicitly comprise such structures. For example, expanded matrices, diagonal matrices, and operations thereon may be effected via various data structures and algorithms in computer code, data storage schemes in memory, circuit designs, processor architectures, etc.

**[0043]** In some aspects, an operator (e.g., operation 104.F) can comprise an interpolating function, such as an interpolation filter. In some aspects, the operator can employ a Vandermonde matrix. An NXN (or larger: e.g., MNXMN) expanded updated discrete-time matrix  $\hat{\mathbf{x}}^{(u)}$  can be computed from  $\hat{\mathbf{x}}^{(u)} = \mathbf{FEDCBAw}^{(u)}\hat{\mathbf{d}}$ . Operator  $\mathbf{F}$  can be an M·N-point transform (where M is an integer > 1) configured to operate on an MNXMN matrix constructed, for example, by performing "zero stuffing" or "zero padding" of its input. In one example, each  $n^{th}$  element of discrete-time signal vector  $\mathbf{x}^{(u)}$  can be generated by summing (e.g., row summations 110.0-110.U) the elements of the corresponding  $n^{th}$  row in matrix  $\hat{\mathbf{x}}^{(u)}$ , wherein the  $n^{th}$  row is expressed as:

$$\hat{\mathbf{x}}_n^{(u)} = \frac{1}{MN} \left[ X_0, X_1 e^{i2\pi(1)n/MN}, \dots, X_{MN-1} e^{i2\pi(MN-1)n/MN} \right].$$

Thus, each element in vector  $\hat{\mathbf{x}}_n^{(u)}$  is an addend of the  $n^{\text{th}}$  value of the length-MN discrete-time vector  $\mathbf{x}^{(u)}$ . In one aspect, operator  $\mathbf{F}$  is an MN-point interpolation filter that operates on an MNXMN zero-stuffed operand matrix to produce an MNXMN expanded discrete-time matrix  $\hat{\mathbf{x}}^{(u)}$ , and  $\hat{\mathbf{x}}_n^{(u)}$  is a length-MN vector.

[0044] An expression for **F** can be derived using computations of an initial or previous (e.g., u = 0) candidate expanded discrete-time matrix  $\hat{\mathbf{x}}^{(0)}$ :

$$F = \overset{^{\wedge}}{x^{(0)}}\overset{^{\wedge}}{d^{-1}}\overset{^{\wedge}}{w^{(0)}}^{-1}A^{-1}B^{-1}C^{-1}D^{-1}E^{-1}$$

where (.)-1 denotes a complementary or inverse of operation (.), and which is also typically employed at a corresponding receiver. An updated  $\hat{\mathbf{x}}^{(u)}$  can be expressed using the above substitution for  $\mathbf{F}$ :

$$\hat{\mathbf{x}}^{(u)} = \hat{\mathbf{x}}^{(0)} \hat{\mathbf{d}}^{-1} \hat{\mathbf{w}}^{(0)}^{-1} \mathbf{A}^{-1} \mathbf{B}^{-1} \mathbf{C}^{-1} \mathbf{D}^{-1} \mathbf{E}^{-1} \mathbf{E} \mathbf{D} \mathbf{C} \mathbf{B} \mathbf{A} \hat{\mathbf{w}}^{(u)} \hat{\mathbf{d}}$$

where (u = 0) denotes initial  $\hat{\mathbf{x}}^{(u)}$  and  $\hat{\mathbf{w}}^{(u)}$ , and (u > 0) denotes a  $u^{\text{th}}$  update. The term  $\hat{\mathbf{w}}^{(0)}$  is an optional weight matrix (not explicitly shown in FIG. 1A, but could be implemented in or prior to operator  $\mathbf{A}$ ), which can be a diagonal expansion matrix that multiplies  $\hat{\mathbf{d}}$ . In some aspects,  $\hat{\mathbf{d}}$  can be an operator that operates on an update weight matrix.

[0045] The operator terms ( $\mathbf{E}^{-1}\mathbf{E}$  to  $\mathbf{A}^{-1}\mathbf{A}$ ) drop out, and because the weight and data matrices are diagonal (and therefore commute under multiplication), the terms can be rearranged to remove the explicit operations involving  $\hat{\mathbf{d}}$  and  $\hat{\mathbf{d}}^{-1}$  in the update, resulting in updated expanded matrix,  $\hat{\mathbf{x}}^{(u)}$  expressed as:

$$\mathbf{x}^{(u)} = \mathbf{x}^{(0)} \mathbf{w}^{(0)}^{-1} \mathbf{w}^{(u)}$$

The values of  $\widehat{\mathbf{w}}^{(0)}$  may be selected so that its matrix inverse is easily computed. For example, values of  $\pm 1$  are not changed by inversion. The expression is further simplified when  $\widehat{\mathbf{w}}^{(0)}$  (and thus,  $\widehat{\mathbf{w}}^{(0)}^{-1}$ ) is an Identity matrix, which results in the multiplicative update:

$$\mathbf{x}^{(u)} = \mathbf{x}^{(0)} \mathbf{w}^{(u)}$$

This might be accomplished by using  $\hat{\mathbf{w}}^{(u-1)}\hat{\mathbf{d}}$  as the current expanded data matrix  $\hat{\mathbf{d}}$  in the expression for  $\mathbf{F}$ . In some aspects, this is effected by designating a previous expanded discrete-time matrix (e.g.,  $\hat{\mathbf{x}}^{(u-1)}$ ) to be the base expanded discrete-time matrix,  $\hat{\mathbf{x}}^{(0)}$ .

[0046] FIG. 1B shows some aspects wherein the inverse of the base weight matrix  $(\hat{\mathbf{w}}^{(0)})^{-1}$ , which may be the inverse of an initial weight matrix,  $\hat{\mathbf{w}}^{(0)}$ , or the inverse of a previous update weight matrix,  $\hat{\mathbf{w}}^{(u-1)}$ ) may be removed from the computation for  $\hat{\mathbf{x}}^{(u)}$  (or  $\Delta \hat{\mathbf{x}}^{(u)}$ ). In an aspect, the base weight matrix is set to an Identity matrix 151, and the current expanded data matrix  $\hat{\mathbf{d}}$  may be provided via a matrix expansion (e.g., in 152) of previous data  $\mathbf{d}^{(0)}$

(e.g., an initial or previous data vector). For example, the previous data  $\mathbf{d}^{(0)}$  may be designated as the current data  $\mathbf{d}$ . In an aspect, a Hadamard product 154 (or equivalent operation) is performed with initial or previous weights and data ( $\mathbf{w}^{(0)}$  and  $\mathbf{d}^{(0)}$ ), followed by matrix expansion 156, which effectively incorporates the weights  $\mathbf{w}^{(0)}$  into the current expanded data  $\hat{\mathbf{d}}$ . In an aspect, previous data  $\mathbf{d}^{(0)}$  and previous weights  $\mathbf{w}^{(0)}$  are expanded (157 and 158, respectively), and the expanded matrices are multiplied together 159. In some aspects, a new  $\hat{\mathbf{x}}^{(0)}$  is selected from an updated expanded matrix from a previous iteration, In an aspect, subsequent update computations may be made to this new base  $\hat{\mathbf{x}}^{(0)}$  without employing inverse weights applied to any previous base. Aspects disclosed herein can be configured for multiplicative and additive updates.

[0047] Updates 108.1-108.U to  $\hat{\mathbf{x}}^{(0)}$  are depicted as each comprising a matrix multiplication of  $\hat{\mathbf{x}}^{(0)}$  with one of the  $\hat{\mathbf{w}}^{(u)}$  ( $u=1,\ldots,U$ ) to produce  $\hat{\mathbf{x}}^{(u)}$ . However, updates 108.1-108.U should be understood to comprise equivalent operations on  $\hat{\mathbf{x}}^{(0)}$ . Some aspects provide for advantageously simple updates 108.1-108.U to the values in  $\hat{\mathbf{x}}^{(0)}$ . For example, values in  $\hat{\mathbf{w}}^{(u)}$  that equal one require no update to corresponding  $\hat{\mathbf{x}}^{(0)}$  values, diagonal values in  $\hat{\mathbf{w}}^{(u)}$  that equal zero (i.e., the diagonal matrix  $\hat{\mathbf{w}}^{(u)}$  is sparse) can provide for deleting values or skipping subsequent calculations involving corresponding  $\hat{\mathbf{x}}^{(0)}$  values, values in  $\hat{\mathbf{w}}^{(u)}$  that equal minus-one change the signs of corresponding  $\hat{\mathbf{x}}^{(0)}$  values, and  $\pi/2$  phase shifts can comprise sign updates to the Real and Imaginary values in  $\hat{\mathbf{x}}^{(0)}$ . In some aspects, updates can be implemented as bit operations (e.g., bit shifts, bit permutations, etc.).

**[0048]** Each expanded matrix  $\hat{\mathbf{x}}^{(u)}$  ( $u=0,\ldots,U$ ) is operated upon with a row summing operation (110.0-110.U), wherein the values in each row of an  $\hat{\mathbf{x}}^{(u)}$  are summed, thus reducing the number of columns (i.e., row elements) from MN to one to produce a corresponding discrete-time signal vector  $\mathbf{x}^{(u)}$  ( $u=0,\ldots,U$ ). In an aspect, the elements  $\hat{x}_{n',n''}^{(u)}$  in each row ( $n'=0,\ldots,N'$ -1) of an N'XN'' matrix  $\hat{\mathbf{x}}^{(u)}$  are summed to convert  $\hat{\mathbf{x}}^{(u)}$  to an N'X1 matrix (i.e., vector)  $\mathbf{x}^{(u)}$ . For example,  $\hat{\mathbf{x}}^{(u)}$  can be expressed as:

$$\hat{\mathbf{x}}^{(u)} = \begin{vmatrix} \hat{x}_{0,0}^{(u)} & \hat{x}_{0,1}^{(u)} & \cdots & \hat{x}_{0,N''-1}^{(u)} \\ \hat{x}_{1,0}^{(u)} & \hat{x}_{1,1}^{(u)} & \cdots & \hat{x}_{1,N''-1}^{(u)} \\ \vdots & \vdots & \ddots & \vdots \\ \hat{x}_{N'-1,0}^{(u)} & \hat{x}_{N'-1,1}^{(u)} & \cdots & \hat{x}_{N'-1,N''-1}^{(u)} \end{vmatrix}$$

and a discrete-time signal vector resulting from this conversion can be expressed as:

$$\mathbf{x}^{(u)} = \begin{vmatrix} x_0^{(u)} \\ x_1^{(u)} \\ \vdots \\ x_{N'-1}^{(u)} \end{vmatrix} = \begin{vmatrix} \hat{x}_{0,0}^{(u)} + \hat{x}_{0,1}^{(u)} + \dots + \hat{x}_{0,N-1}^{(u)} \\ \hat{x}_{1,0}^{(u)} + \hat{x}_{1,1}^{(u)} + \dots + \hat{x}_{1,N-1}^{(u)} \\ \vdots \\ \hat{x}_{N'-1,0}^{(u)} + \hat{x}_{N'-1,1}^{(u)} + \dots + \hat{x}_{N'-1,N-1}^{(u)} \end{vmatrix}$$

This conversion can be regarded as a transformation of the data from a high-dimensional space to a space with fewer dimensions. This can be referred to as a feature projection or feature extraction, and can be implemented in various ways. This approach can be implemented with higher-dimensional data structures (such as tensors), and can reduce the dimensionality to a lower-dimension tensor (including a matrix or a vector, for example). The transformation can be linear or non-linear.

[0049] In some aspects,  $\mathbf{x}^{(u)}$  is a signal vector, such as a discrete-time signal, a frequencydomain signal, or an antenna-array (e.g., spatial-domain) signal vector. Signal vector(s)  $\mathbf{x}^{(u)}$ may be synthesized and one or more signals  $\mathbf{x}^{(u)}$  selected to be transmitted over a wireless channel in a wireless network. Disclosed aspects can perform updates to the expanded-matrix form of the signal vectors to adjust or select some predetermined measurable signal parameter in the resulting signal vector(s). Such signal parameters can include signal amplitude pattern, sparsity pattern, etc. Updates to an expanded matrix can be configured to change the signal parameters in the signal vector corresponding to the expanded matrix, such as the signal vector's data symbol value(s) (such as user data, control data, reference signal data, etc.), dynamic range, spreading code, precoding, resource element mapping, layer mapping, and/or pulse shape, for example. In some aspects, the vector  $\mathbf{x}^{(u)}$  might be a set of signal values transmitted or received by an antenna array in a given time interval. A corresponding measurable parameter(s) might be derived from an analysis (e.g., Principal Component, Independent Component, etc.) of the corresponding expanded matrix that indicates MIMO performance. Updates to the expanded matrix may provide for selecting and/or de-selecting transmit and/or receive antennas, such as to improve MIMO performance for a fixed subset of candidate MIMO antennas. MIMO performance can be characterized by sum rate, mean per-user rate, spectral efficiency, energy efficiency (e.g., ratio of sum rate to total energy consumption of the system), eigenvalue-based condition number, bit error probability, signal to interference plus noise ratio (SINR), outage probability, measures of correlation between spatial subchannels, Minimum Variance index, and may further account for CSI estimation overhead, computational complexity of spatial multiplexing, and inherent limitations due to the variability of the propagation channels.

[0050] In some aspects, the various updates can be performed via any of the techniques disclosed herein to generate U candidate data sets in a high-dimensional space. By way of example, the update weights can effect a selection of transmit antennas and/or receive antennas in a MIMO array, although other examples that employ other mixing matrices may alternatively be employed. Dimensionality reduction may be performed on the data matrix, or on a covariance or correlation of the data matrix for each update. Principal component analysis (PCA) may be employed, such as to reduce the original space to a space spanned by a few eigenvectors. In the MIMO example, this can be used to select MIMO array parameters. In an aspect, the objective is to reduce the number of active antennas, thereby reducing computational complexity for spatial multiplexing and/or reducing transmitted power. PCA can be performed via Singular Value Decomposition (SVD) on the updated expanded matrices or Eigenvalue Decomposition (ED) on a covariance or correlation matrix generated from the updated expanded matrices or updated vectors. Some aspects can employ kernel PCA. For example, a kernel method can be implemented for pattern analysis. Algorithms that can be implemented herein include the kernel perceptron, support vector machines (SVM), Gaussian processes, PCA, canonical correlation analysis, ridge regression, spectral clustering, and linear adaptive filters. Some aspects perform pattern analysis on the updated data, such as to determine types of relations (for example clusters, rankings, principal components, correlations, classifications) in datasets. Subsequent updates to the data may be based on such relations, and are referred to as data-driven updates. Various non-linear techniques that can be employed include manifold learning, such as Isomap, locally linear embedding (LLE), Hessian LLE, Laplacian eigenmaps, and methods based on tangent space analysis.

**[0051]** In one aspect, each vector  $\mathbf{x}^{(u)}$  can be processed for transmission 112. Transmission processing 112 can include coupling the signal to at least one antenna and transmitting the signal over a wireless channel. The plurality of vectors  $\mathbf{x}^{(u)}$  (u = 0, ..., U; or u = 1, ..., U) can be processed 112 concurrently or sequentially. In some aspects, processing 112 is communicatively coupled 119 to the weight generator 106 such that processing 112 of at least a first set of one or more vectors  $\mathbf{x}^{(u)}$  may also select or adapt the update(s) (e.g., weight generation 106) to produce a subsequent set of one or more vectors  $\mathbf{x}^{(u)}$ . This can involve iterative updates to the weights, and thus, the vectors  $\mathbf{x}^{(u)}$ . Accordingly, logical and physical

implementations of aspects depicted by the figures can comprise parallel and/or pipelined processing configurations. In some aspects, extrinsic data configures weight generation 106.

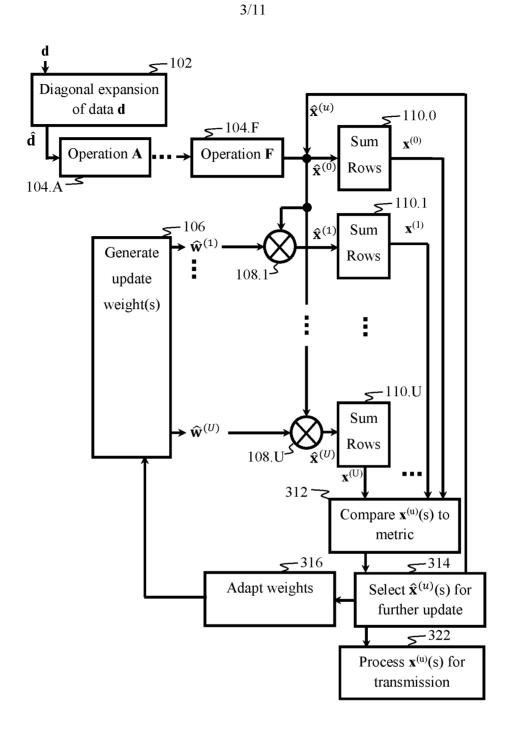

**[0052]** As depicted in FIG. 2, in some aspects, the update weight matrix  $\hat{\mathbf{w}}^{(u)}$  comprises an additive update  $\Delta \hat{\mathbf{w}}^{(u)}$  to a previous weight matrix: e.g.,  $\hat{\mathbf{w}}^{(0)}$ :  $\hat{\mathbf{w}}^{(u)} = \hat{\mathbf{w}}^{(0)} + \Delta \hat{\mathbf{w}}^{(u)}$ . The additive update  $\Delta \hat{\mathbf{w}}^{(u)}$  may be a sparse matrix in the diagonal sense, wherein one or more of the diagonal values are zero. The additive update can change and, in some aspects, even erase values. It should be appreciated that an operation that erases data is not invertible in the usual sense. In some aspects, the erased data can be reconstructed using a constructor operator. In some aspects that employ an expression in which its derivation depends on the inverse of a singular matrix, a matrix pseudo-inverse may be employed. The Moore-Penrose method is an exemplary technique. In the case of a sparse diagonal matrix, each diagonal zero value can be replaced with a non-zero variable  $\gamma_k$ , followed by deriving the expression that involves the matrix inverse, and then computing the expression for the limit as each  $\gamma_k$  approaches zero. This approach mimics the Residue Theorem used for integrating around singularities.

[0053] In an aspect, the elements in each row of  $\hat{\mathbf{x}}^{(0)}$  and  $\Delta \hat{\mathbf{x}}^{(u)}$  may be summed 110.0-110.U, wherein  $\Delta \hat{\mathbf{x}}^{(u)} = \hat{\mathbf{x}}^{(0)} \Delta \hat{\mathbf{w}}^{(u)}$  is an update expanded matrix, and the resulting base vector  $\mathbf{x}^{(0)}$  and update vector(s)  $\Delta \mathbf{x}^{(u)}$  added together in a combining process 212 and then may be processed for further updating 119 or processed for transmission 112. The combining 212 may produce multiple (U') different combinations of the vectors  $\mathbf{x}^{(0)}$  and  $\Delta \mathbf{x}^{(u)}$ , and/or may combine multiple ones of the  $\Delta \mathbf{x}^{(u)}$  vectors together to generate the multiple U' candidates  $\mathbf{x}^{(u)}$ . In another aspect, the order of combining 212 and summing 110.0-110.U may be switched. The update may be implemented as  $\hat{\mathbf{x}}^{(u)} = \hat{\mathbf{x}}^{(0)} + \Delta \hat{\mathbf{x}}^{(u)}$  in a process that combines 212 expanded matrices, where  $\hat{\mathbf{x}}^{(u)}$  is the  $u^{th}$  updated expanded matrix. The elements in each row of each  $\hat{\mathbf{x}}^{(u)}$  can be summed 110.0-110.U to produce vector  $\mathbf{x}^{(u)}$ .

[0054] Updates disclosed herein, such as multiplicative updates and additive updates, can be implemented in transmitters and/or receivers. For example, **d** can comprise a received signal vector (e.g., digital samples of a received signal). Various operations (such as decoding, transforms, etc.) might be performed on the received signal to produce **d**. One or more operations 104.A-104.F are performed on the diagonal expansion matrix  $\hat{\mathbf{d}}$  to produce base expanded matrix  $\hat{\mathbf{x}}^{(0)}$ , which, when operated upon by row summation 110.0, provides a data

sequence  $\mathbf{x}^{(0)}$ . Thus,  $\mathbf{\hat{x}}^{(0)}$  can be referred to as a base expanded data-sequence matrix, or a base expanded data matrix. Multiplicative and/or additive updates (e.g., employing weights  $\mathbf{\hat{w}}^{(u)}$  and/or  $\Delta \mathbf{\hat{w}}^{(u)}$ ) can be made to  $\mathbf{\hat{x}}^{(0)}$  to effect one or more updates to the data sequence  $\mathbf{x}^{(0)}$  (e.g.,  $\mathbf{x}^{(u)}$ ,  $u=1,\ldots,U$ ) without repeating the one or more operations 104.A-104.F. In some aspects, the weights (e.g.,  $\mathbf{\hat{w}}^{(u)}$  and/or  $\Delta \mathbf{\hat{w}}^{(u)}$ ) can comprise filter weights, decoding weights, or combinations thereof.

[0055] FIG. 3 depicts method and apparatus aspects wherein multiple iterations or multiple stages can be employed to produce a discrete-time signal for transmission. The plurality of vectors  $\mathbf{x}^{(u)}$  ( $u = 0, \dots, U$ ; or  $u = 1, \dots, U$ ) are compared 312 to some metric that is based on at least one desired feature of the signal which is improved by the update process. This can comprise measuring or computing each vector's  $\mathbf{x}^{(u)}$  feature(s), and comparing the features to the metric. The metric may be updated based on the features. Based on the feature(s), one or more of the  $\mathbf{x}^{(u)}$ s can be selected 314 for further updates, whereupon the corresponding  $\hat{\mathbf{x}}^{(u)}(s)$  can be updated in the same manner as  $\hat{\mathbf{x}}^{(0)}$ . For example, a processing system can have memory configured to store data, such as expanded matrices  $\hat{\mathbf{x}}^{(u)}$ , vector  $\mathbf{x}^{(u)}$ , weights  $\hat{\mathbf{w}}^{(u)}$ , the features, and/or the metric; and this data may be read from the memory and used for additional processing. Optionally, adaptation of the weights 316 may be performed for subsequent iterations. The adaptation 316 may be based on  $\mathbf{x}^{(u)}$  features of the current iteration and/or a history of feature measurements, weights, and/or changes to the weights. Upon satisfying at least one criterion (e.g., a threshold feature measurement, a predetermined number of iterations, etc.), at least one of the  $\mathbf{x}^{(u)}(s)$  is selected, whereupon the  $\mathbf{x}^{(u)}(s)$  may be further processed for transmission.

[0056] In one example, a computing system operating within a computing environment may receive a signal that includes current data about at least one of the base expanded discrete-time matrix, the base discrete-time signal vector, the updated expanded discrete-time matrix, and the updated discrete-time signal vector. In response to the received signal, the computing system may load, from a storage unit, historical data characterizing prior base expanded discrete-time matrices, base discrete-time signal vectors, updated expanded discrete-time matrices, and/or updated discrete-time signal vectors. For example, the above current data and/or historical data may comprise features of the matrices and/or vectors. Further, based on the current data, and on portions of the historical data, the computing system may compute

updates that produce or improve one or more features in the updated matrices and/or vectors. The system may employ supervised learning, unsupervised learning, or both to determine the feature(s) that correspond to one or more desired signal properties in the wireless network, such as low MIMO condition number, a number of eigenvalues above a threshold value, low peak-to-average-power ratio (PAPR), low bit-error-rate, high bandwidth efficiency, low computational complexity, etc.. The system may learn which update schemes enhance the features (and thus, the corresponding desired signal properties). Disclosed aspects can configure data into expanded matrices, and provide updates thereto for the purpose of adaptive filtering and/or classification.

[0057] In some aspects, the computing system may learn and/or detect the features, and/or provide the update based on an application of one or more machine learning algorithms or processes to input data that includes, but is not limited to, the current data and portions of the historical data. Examples of the one or more machine learning algorithms or processes include, but are not limited to, an association-rule algorithm (such as an Apriori algorithm, an Eclat algorithm, or an FP-growth algorithm), a clustering algorithm (such as a hierarchical clustering module, a k-means algorithm, or other statistical clustering algorithms), a collaborative filtering algorithm (such as a memory- or model-based algorithm), or an artificial intelligence algorithm (such as an artificial neural network).

**[0058]** In FIG. 4, one of the operations, such as Operation **F** (104.F), may be an IFFT, for example. In some aspects, the input to 104.F may comprise precoded data symbols, such as data symbols  $\mathbf{d} = [\mathbf{d}_0 \ \mathbf{d}_1...\ \mathbf{d}_{N-1}]^T$  precoded with an NXN precoding operator **S**, which can comprise transform precoding, CDMA precoding, Zadoff-Chu coding, space-time block coding, spatial multiplexing (e.g., MIMO) precoding, SVD MIMO precoding, transmit diversity precoding, space-time block coding, or any combinations thereof. The output of the IFFT (e.g., 104.F) is an expanded discrete-time matrix  $\hat{\mathbf{x}}^{(0)}$ . The weights updates to  $\hat{\mathbf{x}}^{(0)}$ , provide for a set of updated expanded discrete-time matrices  $\hat{\mathbf{x}}^{(u)}$  from which candidate discrete-time signals  $\mathbf{x}^{(u)}$  can be produced. In some aspects the weights  $\hat{\mathbf{w}}^{(u)}$  can provide for any combination of selective mapping, partial transmit sequence (PTS) scheme, dummy symbol insertion (e.g., in any resource units, such as tones, MIMO channels, multiple-access codes, etc.), data-symbol swapping, changing the order of data symbols, symbol constellation offset (such as dithering, perturbing, scaling, mapping, offsetting, transforming, deforming,

phase-shifting, and/or rotating symbol constellations). Peak-to-Average-Power Ratio (PAPR) measurements 412 are computed for each candidate, and the candidate signal  $\mathbf{x}^{(u)}$  with the best PAPR metric (e.g., lowest PAPR) can be selected 414 for processing 416 to generate the discrete-time transmission signals.

[0059] The PAPR of a signal  $x_n(t)$  can be computed from

$$PAPR = \frac{\max\limits_{0 \leq t \leq NT} |x_n(t)|^2}{E[|x_n(t)^2|]} = \frac{\max\limits_{0 \leq t \leq NT} |x_n(t)|^2}{\frac{1}{NT} \int_0^{NT} |x_n(t)|^2 dt}$$

where  $E[\cdot]$  denotes the expected value. The complementary cumulative distribution function (CCDF) is a frequently used performance measure for PAPR, which is the probability that the PAPR of a signal exceeds a given threshold, PAPR<sub>0</sub>, which is denoted as CCDF = Pr(PAPR > PAPR<sub>0</sub>). Other PAPR performance measures may be used, such as peak amplitude, crest factor, or PAPR normalized with respect to shaping gain. PAPR, as used herein, can refer to any of the PAPR performance measures or PAPR-based metrics disclosed herein. The reduction in PAPR results in a system that can either transmit more bits per second with the same hardware, or transmit the same bits per second with lower power and/or less-expensive hardware. Some aspects, for example, can produce a greater number of candidate discrete-time signals for given processing constraints, thus increasing the likelihood that a signal with low PAPR can be found.

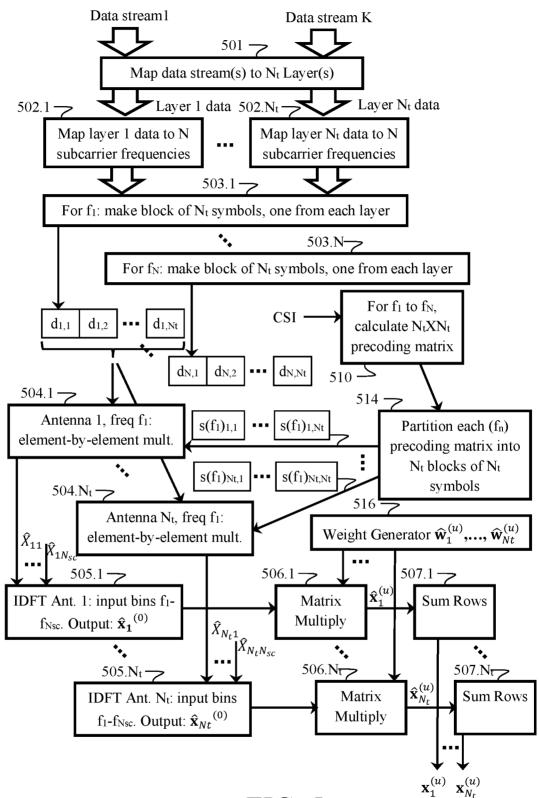

[0060] In FIG. 5, a MIMO-OFDM transmitter maps 501 one or more (K) data streams to as many as N<sub>t</sub> layers. The MIMO-OFDM transmitter may comprise a single-terminal device with multiple antennas thereon, a distributed antenna system residing on multiple terminals, or some combination thereof. The MIMO-OFDM transmitter may comprise UEs (e.g., UEs with multiple antennas and/or UEs configured as a cooperative array, wherein the UEs can be networked together and/or to a hub, such as via D2D, near-field, and/or other links), network infrastructure terminals (e.g., base stations, gNodeB's, remote radio heads, relays, repeaters, hubs, gateways, and/or other server-side and/or intermediate network devices), or some combination thereof.

**[0061]** Data in each layer is mapped 502.1-502.N<sub>t</sub> to N<sub>SC</sub> subcarrier frequencies (such as OFDM tones). For each frequency  $(f_1, ..., f_{N_{SC}})$ , data is arranged 503.1-503.N<sub>t</sub> in blocks of N<sub>t</sub> symbols. The transmitter may employ channel state information (CSI) to calculate precoding

matrices. For example, for each of the N<sub>SC</sub> frequencies  $(f_n)$ , an N<sub>t</sub>XN<sub>t</sub> precoding matrix  $s(f_n)$ can be computed 510. These precoding matrices can multiply 504.1-504.Nt data blocks from each of the processes 503.1-503.N<sub>t</sub>, and may include a step of partitioning 514 each of the Nsc precoding matrices into Nt blocks of Nt symbols. The multiplication 504.1-504.Nt comprises an element-by-element multiplication of the data and precoding values to generate expanded precoded data values  $\hat{X}_{11}, \dots, \hat{X}_{1Nsc}, \dots, \hat{X}_{N_t1}, \dots, \hat{X}_{N_tNsc}$ . The expanded precoded data (comprising Nsc rows) corresponding to antenna 1 is operated on by a first M·Nsc-point IDFT 505.1 to generate an initial expanded matrix  $\hat{\mathbf{x}}_1^{(0)}$ , which is an expansion of the length-M·N<sub>SC</sub> discrete-time vector corresponding to antenna 1. Similar operations are performed for the other  $N_{t}$ -1 antennas. For example, initial expanded matrix  $\hat{\boldsymbol{x}}_{Nt}^{(0)}$  is generated for antenna  $N_t$ . Weight generator 516 generates candidate weight sets  $\widehat{\mathbf{w}}_1^{(u)}, \dots, \widehat{\mathbf{w}}_{Nt}^{(u)}$  for each antenna, and a multiplication 506.1-506.Nt of the corresponding weights and initial expanded matrices for each antenna generates an updated (candidate) expanded matrix  $\hat{\mathbf{x}}_1^{(u)}, \dots, \hat{\mathbf{x}}_{N_t}^{(u)}$ . The rows of each of the updated expanded matrices are summed 507.1-507.Nt to produce the candidate sets of discrete-time signals  $\mathbf{x}_1^{(u)}, \dots, \mathbf{x}_{N_t}^{(u)}$ . The processing described herein can be adapted for parallel, sequential, and/or partial update techniques. It should be appreciated that elements of the matrices disclosed herein can each comprise a matrix (i.e., a submatrix).

[0062] The update MIMO-OFDM signal for each antenna (e.g., antenna 1) has the form:

$$\hat{\mathbf{x}}_{1}^{(u)} = \hat{\mathbf{x}}_{1}^{(0)} \hat{\mathbf{d}}_{1}^{-1} \hat{\mathbf{w}}_{1}^{(u)} \hat{\mathbf{d}}_{1}$$

The associative property of matrix multiplication along with the commutative property of multiplication for diagonal matrices of the same size (i.e., for  $\hat{\mathbf{d}}_1^{-1}$ ,  $\widehat{\mathbf{w}}_1^{(u)}$ , and  $\hat{\mathbf{d}}_1$ ) can be exploited to further simplify the above expression to:

$$\widehat{\mathbf{x}}_1^{(u)} = \widehat{\mathbf{x}}_1^{(0)} \widehat{\mathbf{w}}_1^{(u)}$$

This is enabled by the formatting of data symbols and weights into matrices ( $\hat{\mathbf{d}}_1$  and  $\hat{\mathbf{w}}_1^{(u)}$ , respectively) that commute under multiplication. These matrices might be diagonal matrices or Toeplitz matrices (e.g., Circulant matrices). Row summation is performed relative to each antenna to produce each updated discrete-time (MIMO-)OFDM signal  $\mathbf{x}^{(u)}$ . For each updated (candidate) weight matrix set, there is a corresponding set of updated (candidate) MIMO-OFDM signals that can be transmitted from the N<sub>t</sub> antennas. Properties of the signals (e.g., MIMO performance, PAPR, etc.) may be measured or computed, compared to a threshold value(s), and candidate signals may be selected based on the comparison.

[0063] In an aspect, PAPR of the discrete-time MIMO-OFDM signal  $\mathbf{x}^{(u)}$  is computed for at least one of the  $N_t$  antennas. A PAPR-based metric may be computed from the PAPR measurements. Either the PAPRs or the PAPR-based metrics may be compared for multiple weight matrix sets, and the weight matrix set (and/or discrete-time signal  $\mathbf{x}^{(u)}$ ) having the best PAPR or PAPR-based metric can be selected. PAPR reduction may be performed for certain ones of the antennas. In some aspects, the metric might be a function (e.g., maximum, mean, average, etc.) of PAPR for multiple ones of the antennas. Based on the selection, a transmit MIMO-OFDM signal is synthesized and transmitted from the  $N_t$  antennas.

**[0064]** In some aspects, the weighting matrices can provide for additive updates (including techniques that employ sparse matrices). Thus, the weighting matrices can be configured in a partial update method for generating candidate MIMO-OFDM signals. The weight matrices may provide updates to precoding, the data symbols, or both. The weight matrices may update layer mapping and/or resource mapping. For example, a weight matrix may update how data symbols are mapped to a predetermined set of resource units and/or layers. Update techniques can include updating an antenna selection, such as selecting which antennas in an antenna array (e.g., a MIMO array) are activated.

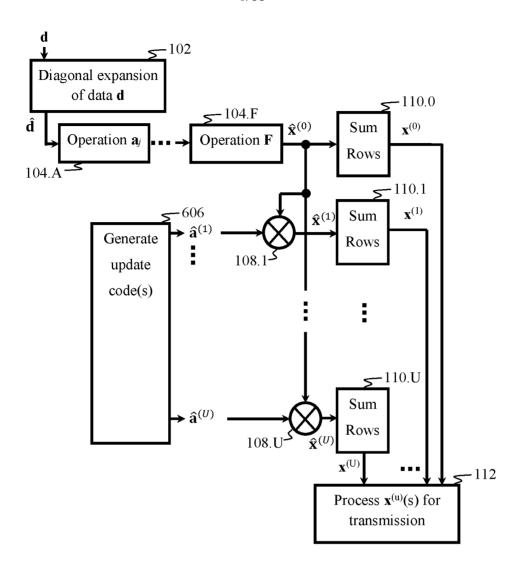

[0065] In FIG. 6, a method and apparatus are provided for updating a coding operation 104.A performed on input data **d**. In one example, a data symbol  $d_i$  is encoded (e.g., spread) with a length-N code vector  $\mathbf{a}_i$  by the coding operation 104.A in a manner that is functionally equivalent to the following mathematical operations. Data symbol  $d_i$  is repeated N times to produce length-N data vector **d**. Operation 104.A can perform a Hadamard product  $\mathbf{x}_a^{(0)} = \mathbf{a}_i \circ \mathbf{d}$ , followed by a diagonal matrix expansion of the product, wherein the diagonal elements of expanded matrix  $\hat{\mathbf{x}}_a^{(0)}$  are the values of  $\mathbf{x}_a^{(0)}$ .

**[0066]** Additional operation(s) (e.g., 104.F) can be performed on the expanded matrix  $\mathbf{x}_a^{(0)}$  to produce  $\mathbf{\hat{x}}^{(0)}$ , which is an expanded matrix of the encoded data. One or more (U) code updates  $\mathbf{\hat{a}}^{(u)}$  are provided 606 (e.g., generated or retrieved from memory), and employed to update the base or previous expanded matrix ( $\mathbf{\hat{x}}^{(0)}$ ), which is generated and/or retrieved from memory:

$$\mathbf{x}^{(u)} = \mathbf{x}^{(0)} \mathbf{a}^{(u)}$$

It should be appreciated that code updates  $\hat{\mathbf{a}}^{(u)}$  can be referred to as weights. In some aspects, a code update  $\hat{\mathbf{a}}^{(u)}$  can comprise a scalar multiplier that effects an update to data symbol  $d_i$ , such as to change  $d_i$  from one symbol value to another symbol value. In other aspects, updates to the data can be performed independently from the code updates. Disclosed aspects related to code updates can be implemented in a transmitter that employs code index modulation. In an aspect, the codes  $\mathbf{a}_i$  have a frequency-domain signature characterized by a sparsity pattern of OFDM tones (subcarrier frequencies), and the updates  $\hat{\mathbf{a}}^{(u)}$  can be configured to update the frequency-domain signature of the transmission. This aspect may be employed to effect OFDM index modulation.

[0067] By way of example, binary codes are efficiently updated, since -1 code values result in only a sign change to corresponding values in the expanded matrix  $\hat{\mathbf{x}}^{(0)}$ , and +1 values result in no changes. In some aspects, code update 606 can be implemented in an additive update system, such as depicted in FIG. 2. Thus, code updates  $\hat{\mathbf{a}}^{(u)}$  can comprise sparse diagonal matrices, wherein one or more of the diagonal values are zero. In the case of ternary codes, for example, additive or multiplicative updates  $\hat{\mathbf{a}}^{(u)}$  can be sparse diagonal matrices.

[0068] Aspects disclosed herein can employ Gray codes, Inverse Gray codes, Walsh codes, Gold codes, Golay codes, CI codes, maximal-length sequences, Barker codes, Kasami codes, Zadoff-Chu codes, chirp codes, Reed-Muller codes, quadratic residue codes, twin prime, ternary codes, quaternary codes, higher-order codes, vector signaling codes, polar codes, and adaptations thereof, such as concatenating, truncating, cyclic shifting, superimposing, combining via element-wise multiplication, and/or inserting zeros into any of the aforementioned codes. Sparse codes can have non-zero elements that are drawn from orthogonal or non-orthogonal code dictionaries, which can include any of the codes mentioned herein.

**[0069]** In some aspects, operation 104.A is followed by DFT-spreading, which outputs frequency-domain symbols. These symbols are mapped to input frequency bins of an IFFT, which generates expanded discrete-time matrix  $\hat{\mathbf{x}}^{(0)}$ . In this case,  $\mathbf{x}_a^{(0)}$  is a time-domain sequence. In some aspects, it is advantageous to perform an operation in one domain (e.g.,

time domain) to effect an operation in another domain (e.g., frequency domain), the relationship between the domain operations being defined by the transform properties. For example, a frequency shift may be implemented by multiplying an encoded sequence x[n] (or a code sequence) with a phase shift:

$$e^{i\phi n}x[n] \stackrel{DTFT}{\to} X(e^{i(\omega-\phi)})$$

wherein  $\omega$  is the frequency of the corresponding frequency-domain samples of X(), and  $\varphi$  indicates a phase shift applied to a code sequence or coded sequence x[n], which results in a frequency offset of the X() samples. The phase shift can be a code update. In disclosed aspects, the code update can operate on the expanded discrete-time matrix  $\hat{\mathbf{x}}^{(0)}$  to effect a desired frequency-domain operation, thus avoiding the need to repeat DFT-spreading, resource-element mapping, and the IFFT. This reduces computational complexity.

**[0070]** In one aspect, a phase-shift update to  $\hat{\mathbf{x}}^{(0)}$  can provide a cyclic shift in the corresponding frequency-domain symbols. This can be useful in systems that employ receivers that perform decoding in the frequency domain, as some disclosed aspects can efficiently change the transmitted frequency-domain codes via updates to the expanded discrete-time signal  $\hat{\mathbf{x}}^{(0)}$ , additive updates in the expanded discrete-time signal space, and other operations in the expanded discrete-time signal space. In some aspects, code sequence  $\mathbf{a}_i$  has a corresponding frequency-domain code space  $\mathbf{a}_i$  that is sparse (i.e., one or more values of  $\mathbf{a}_i$  are zero), and the code updates to  $\hat{\mathbf{x}}^{(0)}$  provide for updates to the sparse frequency-domain code  $\mathbf{a}_i$ . The code sequence  $\mathbf{a}_i$  can be configured to have a first predetermined sparsity pattern (i.e., a pattern of non-zero elements) in the frequency domain, and updates to  $\hat{\mathbf{x}}^{(0)}$  can be configured to provide an updated sequence (e.g.,  $\mathbf{x}^{(u)}$ ) having a second frequency-domain sparsity pattern. The sparsity patterns may be the same or different. A phase-shift update to  $\hat{\mathbf{x}}^{(0)}$  can be operable to remap (i.e., change the mapping of) the DFT-spread symbols to the IFFT inputs, which effectively updates resource unit (e.g., resource element) mapping.

[0071] Other transform properties can be exploited in a similar manner as disclosed herein, including, but not limited to transform properties associated with time shifting, convolution, correlation, multiplication, modulation, scaling, and filtering. Aspects disclosed herein can be configured with respect to any of the Fourier transforms and/or other transforms mentioned herein.

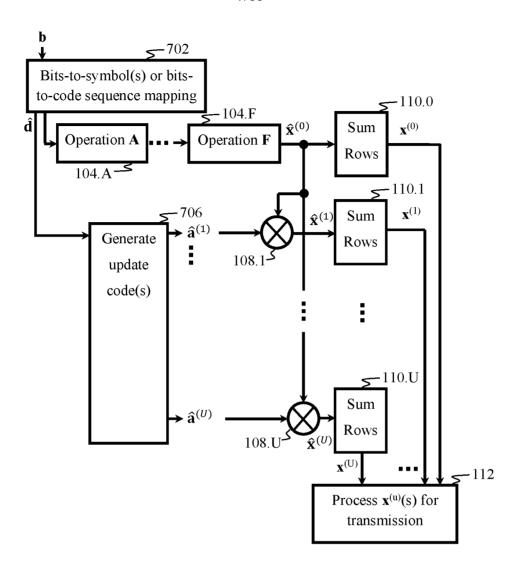

[0072] In FIG. 7, a NOMA scheme, such as sparse code multiple access (SCMA) can be performed. A plurality of data bits **b** in each layer are mapped 702 to data symbols or to one or more code sequences  $\mathbf{a}_i$ , wherein the output can be formatted as a diagonal matrix expansion  $\hat{\mathbf{d}}$ . The mapping 702 can employ one or more codebooks. For example, each layer may have its own codebook. The data  $\hat{\mathbf{d}}$  can comprise one or more data symbols spread with the one or more code sequences. Operations A-F (104.A-104.F) can comprise DFT spreading, followed by resource element mapping, followed by an IFFT. Code sequence  $\mathbf{a}_i$  can be selected such that its frequency-domain code space  $\alpha_i$  is effectively an SCMA codeword. The output of the IFFT, for example, Operation F (104.F), is an expanded discrete-time matrix  $\hat{\mathbf{x}}^{(0)}$  of a discrete-time SCMA signal. Updates to the code sequence(s)  $\mathbf{a}_{j}$ , and thus the corresponding SCMA codeword(s)  $\alpha_i$ , may be generated or read from memory (706). Multiplicative update(s) 108.1-108.U (or additive updates 212) performed on  $\hat{\mathbf{x}}^{(0)}$  in disclosed aspects can effectively change the SCMA codeword(s). An SCMA receiver can demodulate the received OFDM-SCMA signals (e.g., with an FFT) and decode the frequency-domain symbols based on a message-passing algorithm, successive interference cancellation, or other advanced-receiver design. UE codebooks can assist the receiver in decoding received signals. Disclosed aspects can be configured for decoding operations in a NOMA receiver.

**[0073]** In one aspect, codewords employed by each layer have a layer-specific sparsity pattern, which may differ from sparsity patterns associated with other layers. Code sequence  $\mathbf{a}_{i}$  can be selected to provide  $\mathbf{x}^{(0)}$  with an SCMA sparsity pattern corresponding to a first layer (e.g., a first code book), and code updates 706 to the base expanded discrete-time matrix  $\mathbf{\hat{x}}^{(0)}$  can provide for updated discrete-time sequences  $\mathbf{x}^{(u)}$  with the same SCMA sparsity pattern. In one aspect, a base code sequence  $\mathbf{a}_{0}$  having a predetermined SCMA sparsity pattern (such as corresponding to a codebook for layer 1) is provided to Operation(s) 104.A-104.F to produce the base expanded discrete-time matrix  $\mathbf{\hat{x}}^{(0)}$ . As the transmitter receives layer 1's data bits, it arranges the bits into blocks, and the bits-to-code sequence mapping 702 regulates the generation (or selection) 706 of matrix-expansion updates  $\mathbf{\hat{a}}^{(u)}$  for each block, which produce discrete-time sequences  $\mathbf{x}^{(u)}$  with the same sparsity pattern as  $\mathbf{a}_{0}$ . This can constitute codeword mapping. This can be performed in serial and/or in parallel. In some aspects, each block is mapped to more than one codeword. In some aspects, codewords may be summed,

which can be implemented by summing two or more of the discrete-time sequences  $\mathbf{x}^{(u)}$ . Updates 108.1-108.U can be made:  $\hat{\mathbf{x}}^{(u)} = \hat{\mathbf{x}}^{(0)} \hat{\mathbf{a}}^{(u)}$ , followed by row summing 110.1-110.U and processing 112. The transmitter can be configured to generate SCMA signals for multiple layers. In some aspects, symbol-to-codeword mapping effected by 702 and 706 can comprise providing for updates that cause the updated sparsity pattern(s) (e.g., for  $\mathbf{x}^{(u)}$ ) to differ from the base sparsity pattern (e.g., for  $\mathbf{x}^{(0)}$ ). This might be done to configure a transmitter to process different layers, when there is a codebook change, or when a codebook calls for changing the layer's sparsity pattern.

[0074] In some aspects, FIG. 7 can be configured to implement code-sequence index modulation, wherein the code sequences are configured to have SCMA frequency-domain signatures. In some aspects, FIG. 7 can be configured to implement OFDM index modulation (OFDM-IM) by providing for code sequence index modulation, wherein the code sequences are designed to have different frequency-domain sparsity patterns. These sparsity patterns can include different active OFDM tone patterns, including different numbers of active OFDM tone patterns (subcarrier number index modulation). By way of example, mapping 702 can perform a bits-to-code-index mapping, and each code index is then input to update 706 to generate the code update(s). The update(s) can have the form of a code-sequence update, which indirectly effects an SCMA code update or sparsity pattern update without repeating the IFFT (and possibly other functions). This can significantly improve computational efficiency. The updates can be implemented via multiplicative and/or additive updates disclosed herein. In some aspects, some of the data bits are mapped to data symbols (e.g., in 702), which are then effectively modulated onto index-modulation selections of SCMA codewords or individual ones of the OFDM-IM tones via the generation or selection of update codes 706. For example, data symbol modulation and code index modulation can be combined in 706 by configuring the generation or selection of updates  $\hat{\mathbf{a}}^{(u)}$  that result in discrete time sequences  $\mathbf{x}^{(u)}$  having the desired frequency-domain signature (i.e., SCMA) codewords or OFDM-IM tones with data symbols modulated thereon). In other aspects, data symbol modulation may be performed separately from (e.g., following) index modulation.

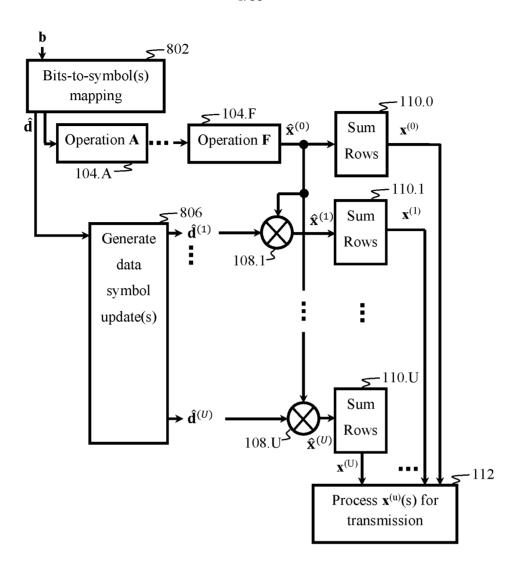

[0075] FIG. 8 illustrates method and apparatus aspects that can be configured to generate data-modulated waveforms for transmission, and/or possibly other uses. By way of example, bits-to-symbol(s) mapping 802 can map an initial block of data bits **b** to one or more data

symbols that are processed by one or more processing blocks 104.A-104.F to produce at least one base expanded matrix  $\hat{\mathbf{x}}^{(0)}$ , such as a base expanded discrete-time matrix. Bits-to-symbol(s) mapping 802 can map one or more subsequent blocks of data bits  $\mathbf{b}$  to one or more subsequent data symbols, which symbol update module 806 can use to generate one or more symbol updates  $\hat{\mathbf{d}}^{(u)}$  (which can be referred to as weights). In some aspects, bits-to-symbol(s) mapping 802 directly maps bits to the symbol update(s)  $\hat{\mathbf{d}}^{(u)}$ . The symbol updates  $\hat{\mathbf{d}}^{(u)}$  can be employed in one or more multiplicative updates 108.1-108.U (and/or additive update(s)) to produce one or more updated expanded matrices  $\hat{\mathbf{x}}^{(u)}$ . Row summation 110.0-110.U can precede additional processing, such as processing for transmission 112.

[0076] Disclosed aspects can be combined. For example, updates disclosed herein can effect updates (referred to generally as update weights  $\widehat{\mathbf{w}}^{(u)}$ ) to multiple signal parameters of the discrete-time signal  $\mathbf{x}^{(0)}$ , including updates to data symbol values modulated thereon and at least one of the Operations 104.A-104.F, and updates to multiple ones of the Operations 104.A-104.F. In some aspects, multiple updates can be made concurrently via application of an update weight  $\widehat{\mathbf{w}}^{(u)}$  to an expanded matrix (e.g.,  $\widehat{\mathbf{x}}^{(0)}$ ). In other aspects, multiple updates can be made iteratively or serially, such as by employing a first (multiplicative and/or additive) update to a first expanded matrix to produce a first updated expanded matrix, followed by employing at least a second (multiplicative and/or additive) update to the first updated expanded matrix to produce at least a second updated expanded matrix. In some aspects, the order of disclosed operations may be rearranged. In one aspect, data modulation follows waveform generation.

[0077] In some aspects, a network device (e.g., a UE, base station, relay, or group thereof) employs an operating signal processing component with a signal coding/decoding component (in conjunction with one or more processors, memories, transceivers, RF front ends, and antennas) to generate a base expanded matrix based on data to be transmitted in a wireless communication network, or based on samples of a received signal in the network; update values in at least one column of the base expanded matrix to produce an updated matrix; and sum values in each row of the updated matrix to produce a signal vector. In a transmit mode, the signal vector may be processed for transmission as a discrete-time signal. Alternatively, in a receive mode, the signal vector may be further processed, such as to provide for demultiplexing, decoding, filtering, etc.

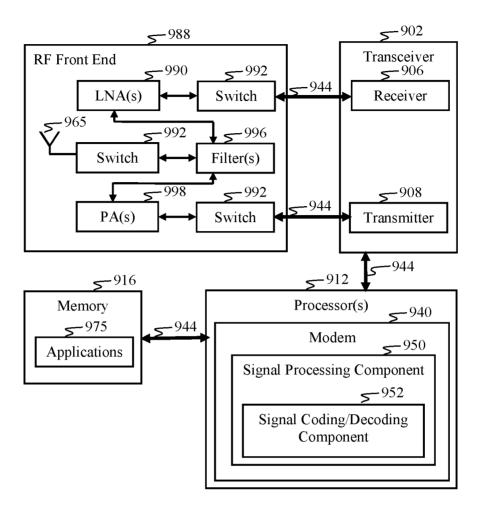

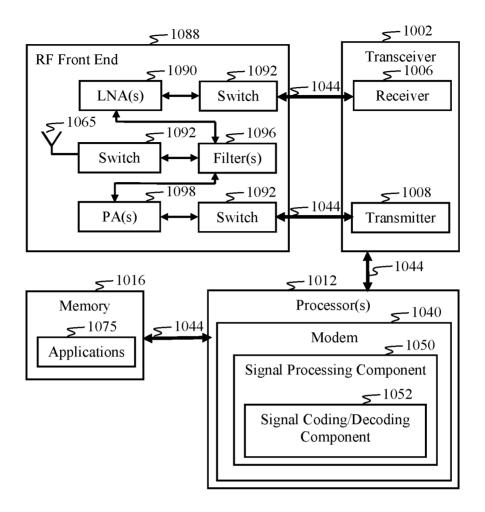

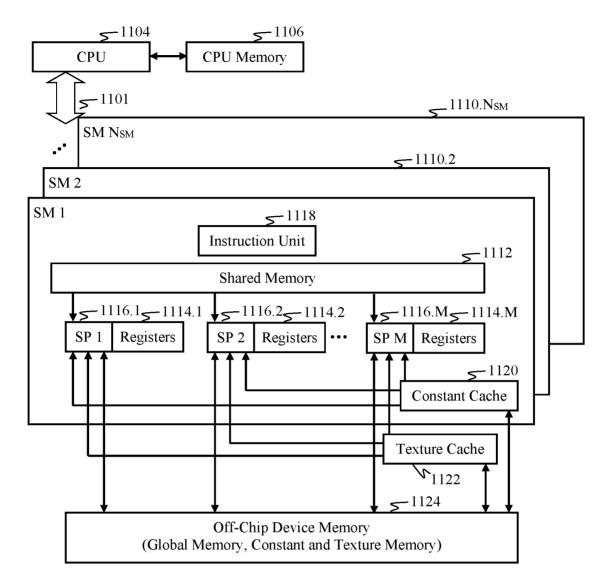

[0078] FIG. 9 is an example implementation of a UE, which may include a variety of components, such as one or more processors 912, memory 916, and transceiver 902 in communication via one or more buses 944, which may operate in conjunction with modem 940, signal processing component 950, and signal coding/decoding component 952 to enable one or more of the functions described herein. The one or more processors 912, modem 914, memory 916, transceiver 902, RF front end 988, and one or more antennas 986 may be configured to support communications (simultaneously or non-simultaneously) in one or more radio access technologies. In some implementations, at least one of the RF front end 988, transmitter 908, and modem 940 may comprise or form at least a portion of means for transmitting a communication signal. In some implementations, at least one of the RF front end 988, receiver 968, and modem 940 may comprise or form at least a portion of means for receiving a communication signal.

[0079] In an aspect, the one or more processors 912 can include a modem 914 that uses one or more modem processors. The various functions related to signal processing component 950 and signal coding/decoding component 952 may be included in modem 140 and/or processors 1212 and, in an aspect, can be executed by a single processor. In other aspects, different ones of the functions may be executed by a combination of two or more different processors. For example, in an aspect, the one or more processors 912 may include any one or any combination of a modem processor, a baseband processor, a digital signal processor, a transmit processor, a receiver processor, or a transceiver processor associated with transceiver 902. In other aspects, some of the features of the one or more processors 912 and/or modem 940 associated with signal processing component 950 and signal coding/decoding component 952 may be performed by transceiver 902.

[0080] Memory 916 may be configured to store data used herein and/or local versions of applications 975 or signal processing component 950 and/or one or more of its subcomponents being executed by at least one processor 912. Memory 916 can include any type of computer-readable medium usable by a computer or at least one processor 912, such as random access memory (RAM), read only memory (ROM), tapes, magnetic discs, optical discs, volatile memory, non-volatile memory, and any combination thereof. In an aspect, for example, memory 916 may be a non-transitory computer-readable storage medium that stores one or more computer-executable codes defining signal processing component 950 and/or

one or more of its subcomponents, and/or data associated therewith, when the UE is operating at least one processor 912 to execute signal processing component 950 and/or one or more of its subcomponents.

[0081] Transceiver 902 may include at least one receiver 906 and at least one transmitter 908. Receiver 906 may include hardware, firmware, and/or software code executable by a processor for receiving data, the code comprising instructions and being stored in a memory (e.g., computer-readable medium). Receiver 906 may be, for example, a radio frequency (RF) receiver. In an aspect, receiver 906 may receive signals transmitted by at least one base station. Additionally, receiver 906 may process such received signals, and also may obtain measurements of the signals, such as, but not limited to, Ec/Io, SNR, RSRP, RSSI, etc. Transmitter 908 may include hardware, firmware, and/or software code executable by a processor for transmitting data, the code comprising instructions and being stored in a memory (e.g., computer-readable medium). A suitable example of transmitter 908 may including, but is not limited to, an RF transmitter.

[0082] Moreover, in an aspect, the UE may include RF front end 988, which may operate in communication with one or more antennas 965 and transceiver 902 for receiving and transmitting radio transmissions. RF front end 988 may be connected to one or more antennas 965 and can include one or more low-noise amplifiers (LNAs) 990, one or more switches 992, one or more power amplifiers (PAs) 998, and one or more filters 996 for transmitting and receiving RF signals.