#### (12) INTERNATIONAL APPLICATION PUBLISHED UNDER THE PATENT COOPERATION TREATY (PCT)

(19) World Intellectual Property Organization

International Bureau

(10) International Publication Number WO 2014/142972 A1

(43) International Publication Date 18 September 2014 (18.09.2014)

(51) International Patent Classification: G06F 9/06 (2006.01) G06F 9/44 (2006.01) G06F 9/30 (2006.01)

(21) International Application Number:

PCT/US2013/032111

(22) International Filing Date:

15 March 2013 (15.03.2013)

(25) Filing Language:

English

(26) Publication Language:

English

- (71) Applicant (for all designated States except US): INTEL CORPORATION [US/US]; 2200 Mission College Boulevard, Santa Clara, California 95052 (US).

- (72) Inventors; and

- (71) Applicants (for US only): BHARADWAJ, Jayashankar [US/US]; 19553 Brockton Ln, Saratoga, California 95070 (US). VASUDEVAN, Nalini [IN/US]; 644 Picasso Ter, Sunnyvale, California 94087 (US). HARTONO, Albert [ID/US]; 496 Mansion Park Drive #304, Santa Clara, California 95054 (US). BAGHSORKHI, Sara S. [IR/US]; 135 Rio Robles E., Unit 241, San Jose, California 95134 (US).

- (74) Agent: JACKLIN, Kim A.; Hanley, Flight & Zimmerman, LLC, 150 S. Wacker Drive, Suite 2100, Chicago, Illinois 60606 (US).

- (81) Designated States (unless otherwise indicated, for every kind of national protection available): AE, AG, AL, AM, AO, AT, AU, AZ, BA, BB, BG, BH, BN, BR, BW, BY, BZ, CA, CH, CL, CN, CO, CR, CU, CZ, DE, DK, DM, DO, DZ, EC, EE, EG, ES, FI, GB, GD, GE, GH, GM, GT, HN, HR, HU, ID, IL, IN, IS, JP, KE, KG, KM, KN, KP, KR, KZ, LA, LC, LK, LR, LS, LT, LU, LY, MA, MD, ME, MG, MK, MN, MW, MX, MY, MZ, NA, NG, NI, NO, NZ, OM, PA, PE, PG, PH, PL, PT, QA, RO, RS, RU, RW, SC, SD, SE, SG, SK, SL, SM, ST, SV, SY, TH, TJ, TM, TN, TR, TT, TZ, UA, UG, US, UZ, VC, VN, ZA, ZM, ZW.

- (84) Designated States (unless otherwise indicated, for every kind of regional protection available): ARIPO (BW, GH, GM, KE, LR, LS, MW, MZ, NA, RW, SD, SL, SZ, TZ, UG, ZM, ZW), Eurasian (AM, AZ, BY, KG, KZ, RU, TJ, TM), European (AL, AT, BE, BG, CH, CY, CZ, DE, DK, EE, ES, FI, FR, GB, GR, HR, HU, IE, IS, IT, LT, LU, LV, MC, MK, MT, NL, NO, PL, PT, RO, RS, SE, SI, SK, SM, TR), OAPI (BF, BJ, CF, CG, CI, CM, GA, GN, GQ, GW, ML, MR, NE, SN, TD, TG).

#### Published:

with international search report (Art. 21(3))

(54) Title: METHODS AND SYSTEMS TO VECTORIZE SCALAR COMPUTER PROGRAM LOOPS HAVING LOOP-CARRIED DEPENDENCES

(57) Abstract: Methods and systems to convert scalar computer program loops having loop carried dependences to vector computer program loops are disclosed. One example method and system generates a first predicate set associated with a first conditionally executed statement. The first predicate set contains a first set of predicates that cause a variable to be defined in a scalar computer program loop at or before the variable is defined by the first conditionally executed statement. The method and system also generates a second predicate set associated with the first conditionally executed statement. The second predicate set contains a second set of predicates that cause the variable to be used in the scalar computer program loop at or before the variable is defined by the first conditionally executed statement. The method and system determines whether the second predicate set is a subset of the first predicate set and, based on the determination, propagates a vector value in an element of a vector of the variable to a subsequent element of the vector.

### METHODS AND SYSTEMS TO VECTORIZE SCALAR COMPUTER PROGRAM LOOPS HAVING LOOP-CARRIED DEPENDENCES

#### FIELD OF THE DISCLOSURE

[0001] This disclosure relates generally to computer systems and, and more specifically, to methods and system to vectorize scalar computer program loops having loop-carried dependences.

#### BACKGROUND

[0002] Many modern day computer systems employ computer program vectorization technologies, such as optimizing computer program code compilers to vectorize scalar computer programs. Vectorization involves converting scalar computer program loops that operate on a scalar variable(s)/operand(s) representing a single numerical value to vector computer program loops that operate on a vector variable(s)/operand(s) representing a set of numerical values (e.g., a vector of "k" elements includes "k" values). Conventional compilers use simple variable expansion (i.e., replacing scalar program variables with vector program variables) to perform vectorization on scalar computer program loops that do not have loop-carried dependences.

#### BRIEF DESCRIPTION OF THE DRAWINGS

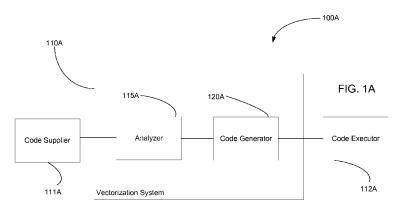

- [0003] FIG. 1A illustrates a block diagram of an example vectorization system capable of vectorizing a scalar computer program loop.

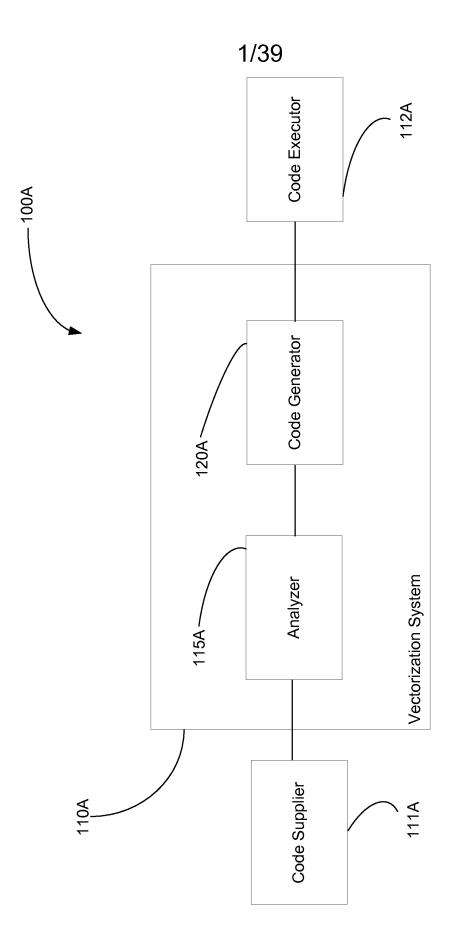

- [0004] FIG. 1B illustrates a block diagram of an example vectorization system capable of vectorizing a scalar computer program loop having lexically backward loop-carried dependences.

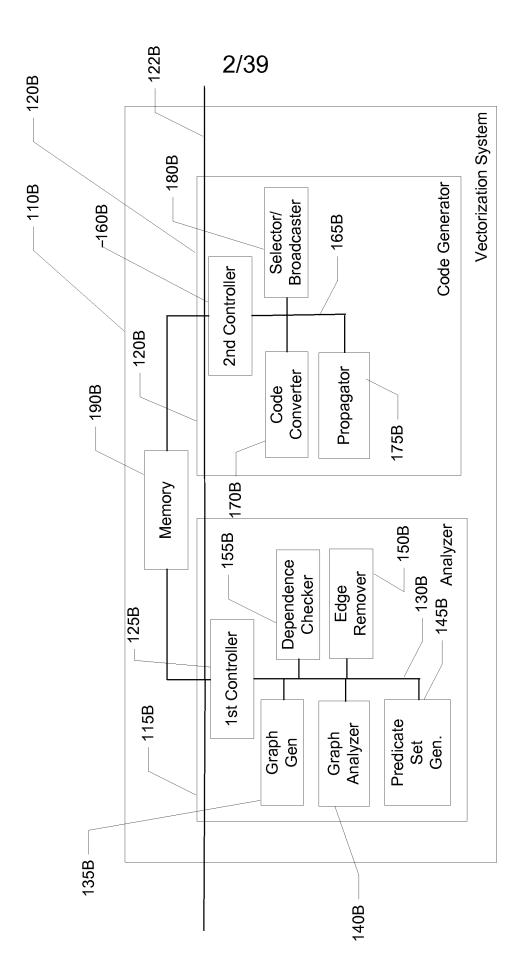

- [0005] FIG. 1C illustrates a block diagram of an example vectorization system capable of vectorizing a scalar computer program loop having loop dependences that arise from recurrence loop operations.

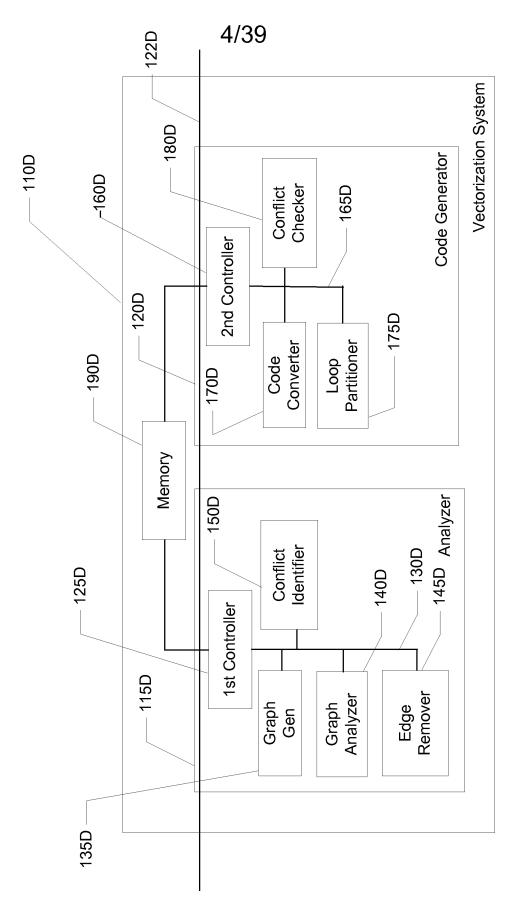

- [0006] FIG. 1D illustrates a block diagram of an example vectorization system capable of vectorizing a scalar computer program loop having cross iteration memory dependences.

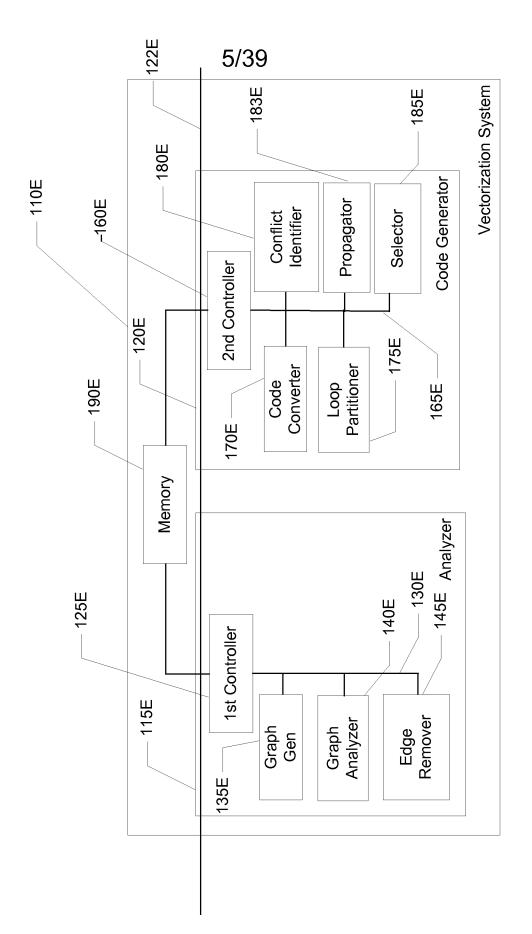

- [0007] FIG. 1E illustrates a block diagram of an example vectorization system capable of

vectorizing a scalar computer program loop having loop-carried dependences arising from conditionally executed statements.

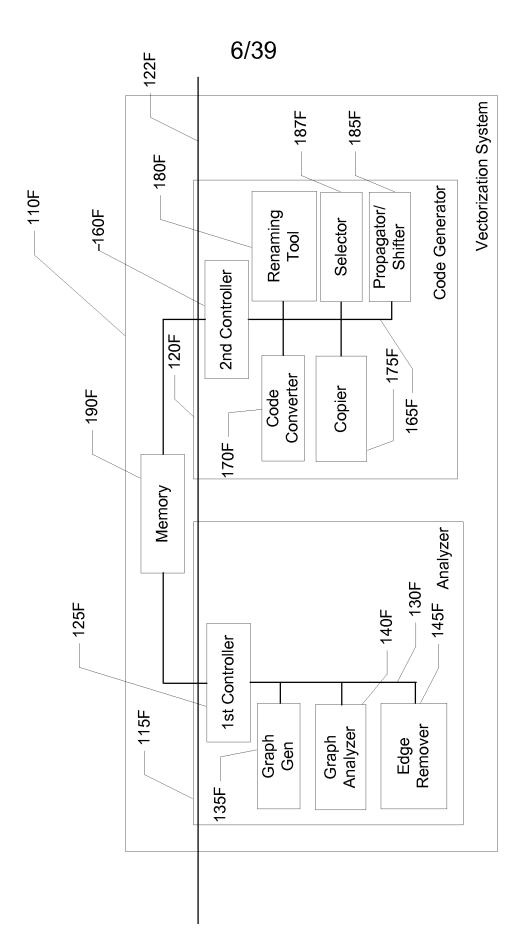

- [0008] FIG. 1F illustrates a block diagram of an example vectorization system capable of vectorizing a scalar computer program loop having loop-carried dependences arising from scalar references.

- [0009] FIG. 2 illustrates example pseudo code representing an example computer program having a scalar computer program loop containing lexically backward loop-carried dependences.

- [0010] FIG. 3 illustrates example pseudo code representing an example vectorized version of the example scalar computer program loop of FIG. 2 created using the example vectorization system of FIG. 1B.

- [0011] FIG. 4 illustrates example pseudo code representing an example scalar computer program loop having loop-carried dependences that arise from recurrence loop operations.

- [0012] FIG. 5 illustrates example pseudo code used by the example code generator to vectorize a computer program loop having loop-carried dependences that arise from recurrence loop operations.

- [0013] FIG. 6 illustrates example pseudo code representing an example vectorized version of the scalar computer program loop of FIG. 4 created using the example vectorization system of FIG. 1C.

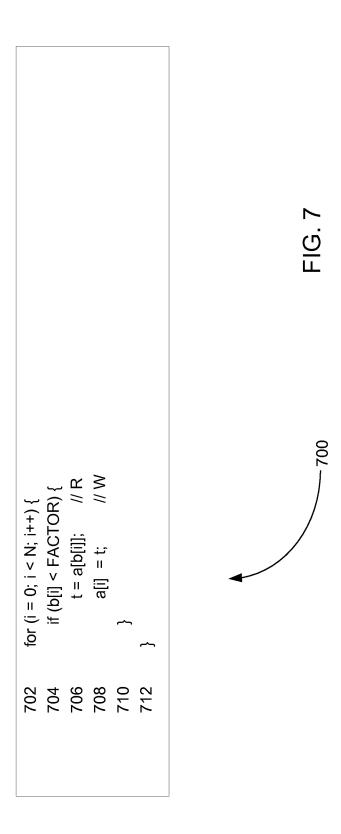

- [0014] FIG. 7 illustrates example pseudo code representing an example scalar computer program having loop-carried cross iteration memory dependences.

- [0015] FIG. 8 illustrates example pseudo code representing an example vectorized version of the example scalar computer program loop of FIG. 7 created using the example vectorization system of FIG. 1D.

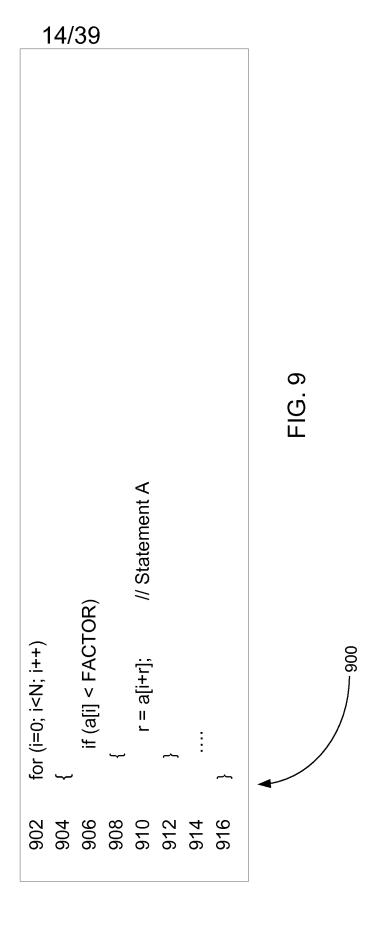

- [0016] FIG. 9 illustrates example pseudo code representing an example scalar computer program having loop-carried dependences arising from conditionally executed statements.

[0017] FIG. 10 illustrates example pseudo code representing an example vectorized version of the example scalar computer program loop of FIG. 9 created using the example vectorization system of FIG. 1E.

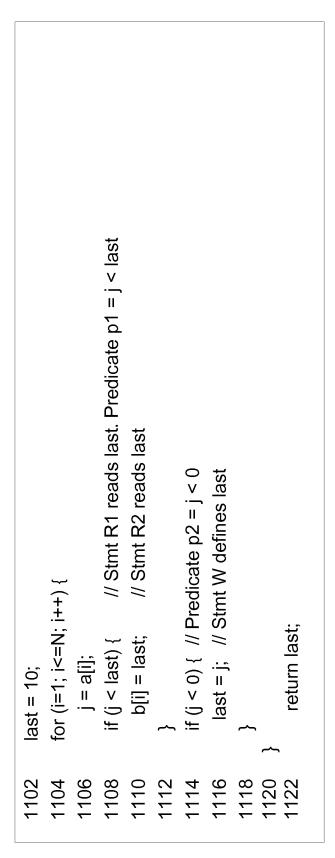

- [0018] FIG. 11 illustrates example pseudo code representing an example scalar computer program having loop-carried dependences arising from scalar references.

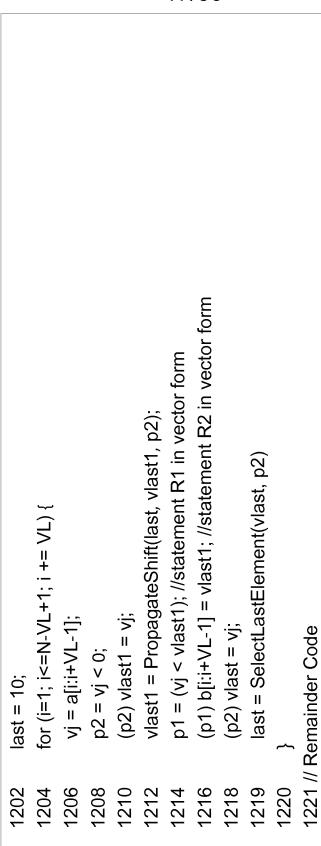

- [0019] FIG. 12 illustrates example pseudo code representing an example vectorized version of the computer program loop of FIG. 11 created using the example vectorization system of FIG. 1F.

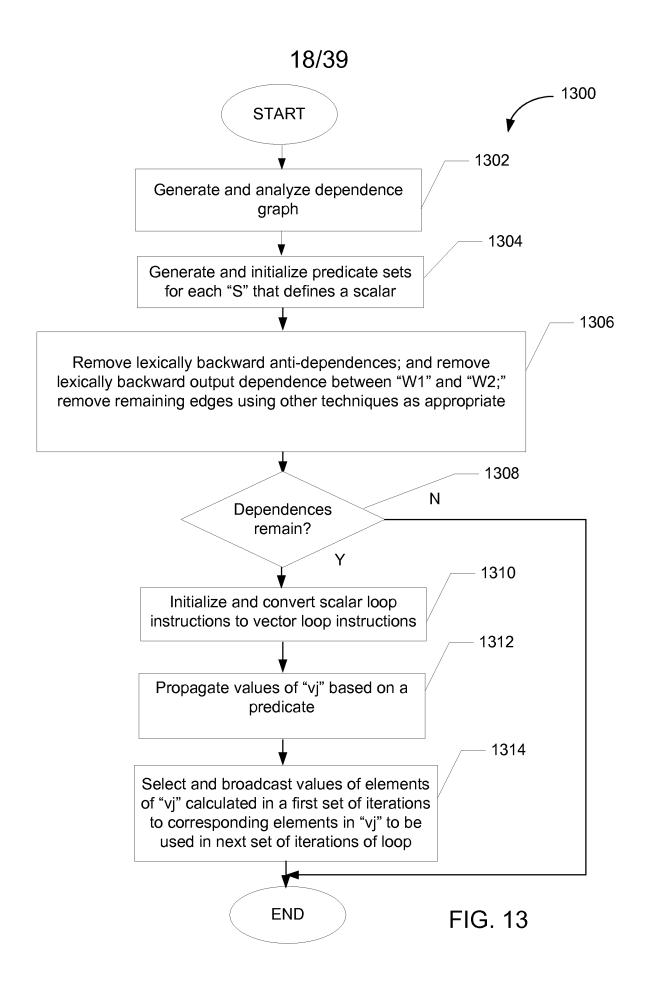

- [0020] FIG. 13 illustrates an example flowchart representing example machine readable instructions executed by the example vectorization system of FIG. 1B to vectorize a scalar computer program loop having lexically backward loop-carried dependences.

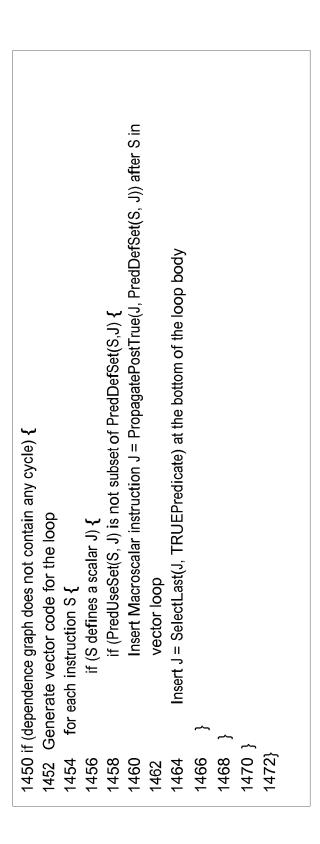

- [0021] FIGS. 14A and 14B illustrate example pseudo code representing example machine readable instructions executed by the example vectorization system of FIG. 1B to vectorize a scalar computer program loop having lexically backward loop-carried dependences.

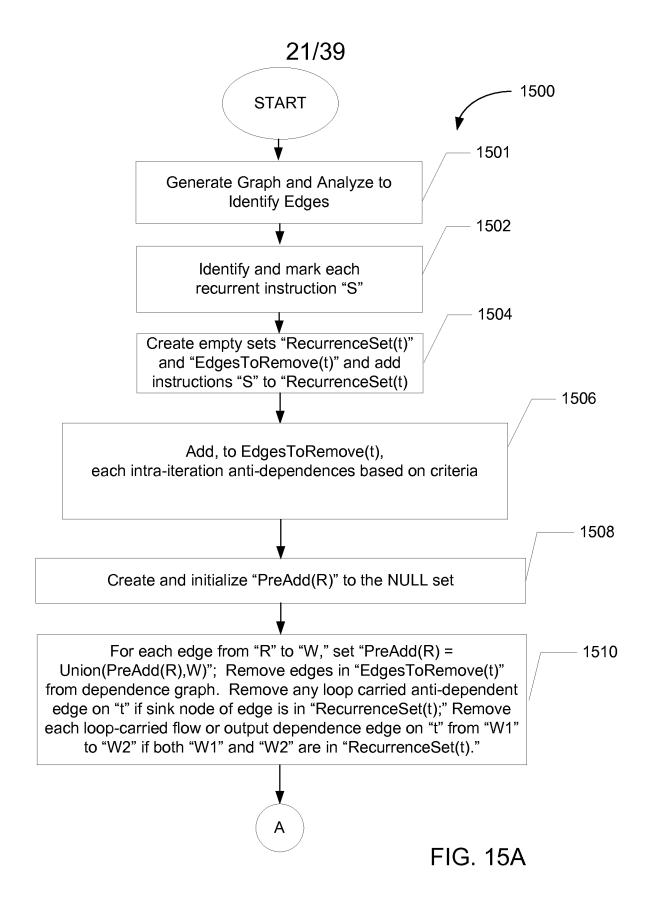

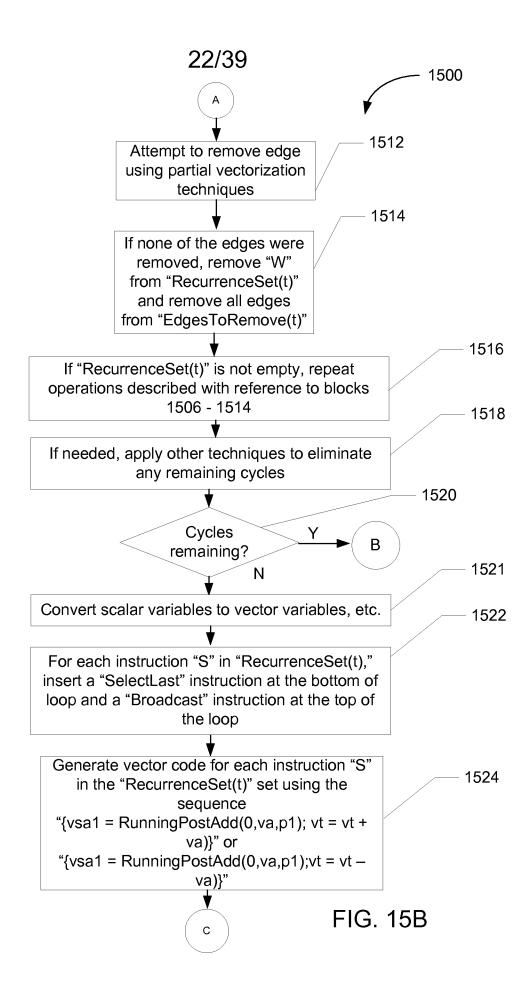

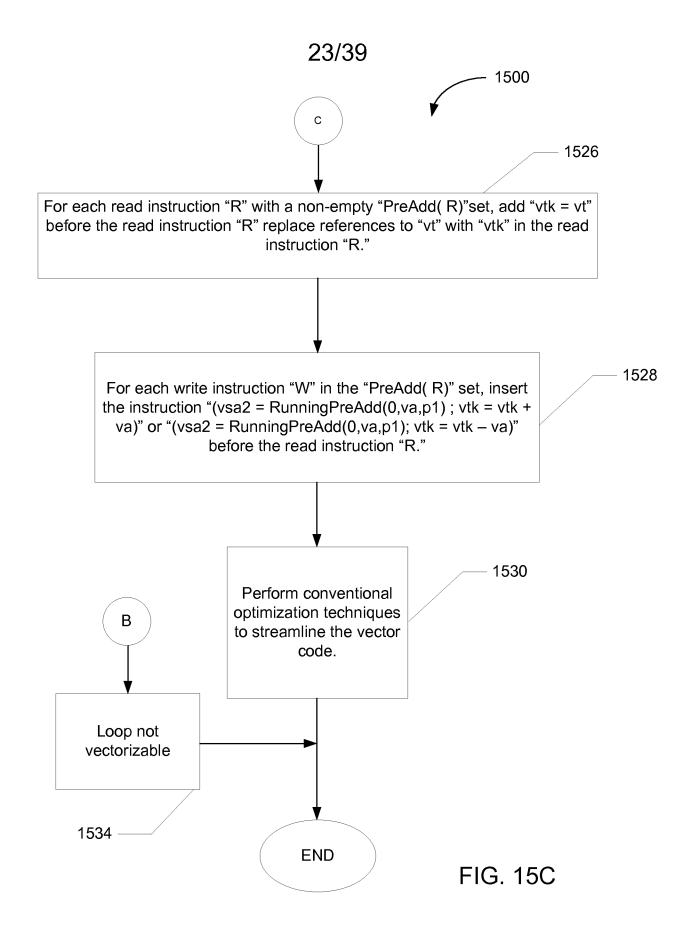

- [0022] FIGS. 15A 15C illustrate an example flowchart representing example machine readable instructions executed by the example vectorization system of FIG. 1C to vectorize a scalar computer program loop having loop-carried dependences that arise from recurrence loop operations.

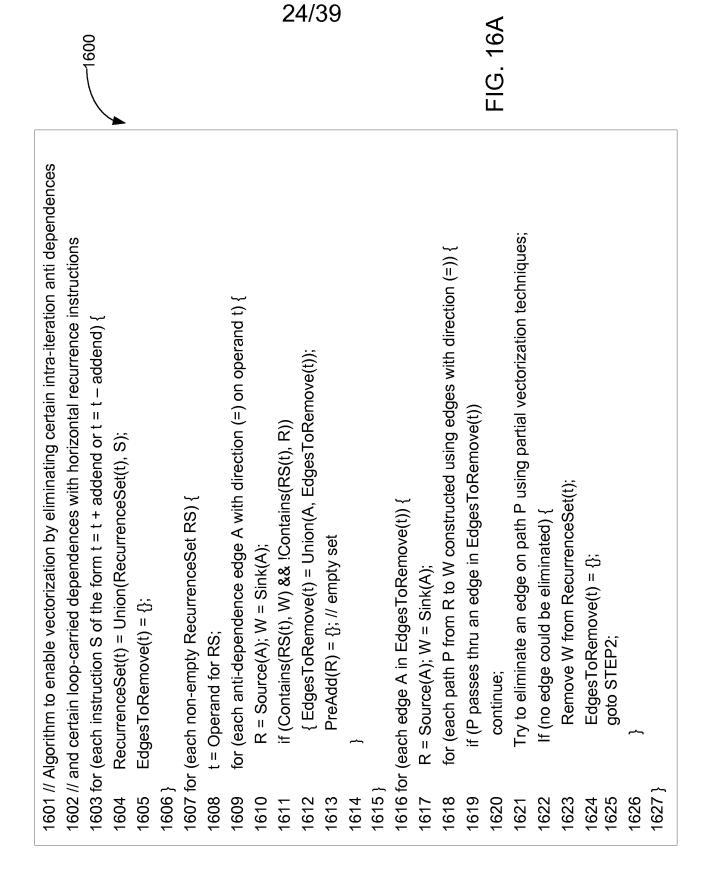

- [0023] FIGS. 16A 16C illustrate an example pseudo code representing example machine readable instructions executed by the example vectorization system of FIG. 1C to vectorize a scalar computer program loop having loop-carried dependences that arise from recurrence loop operations.

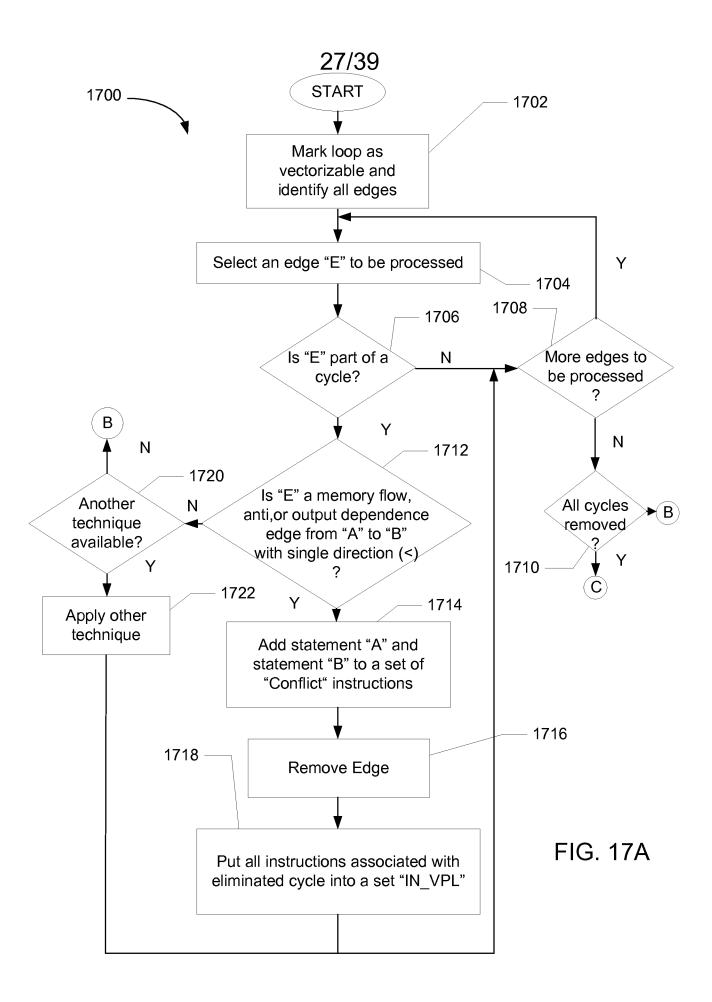

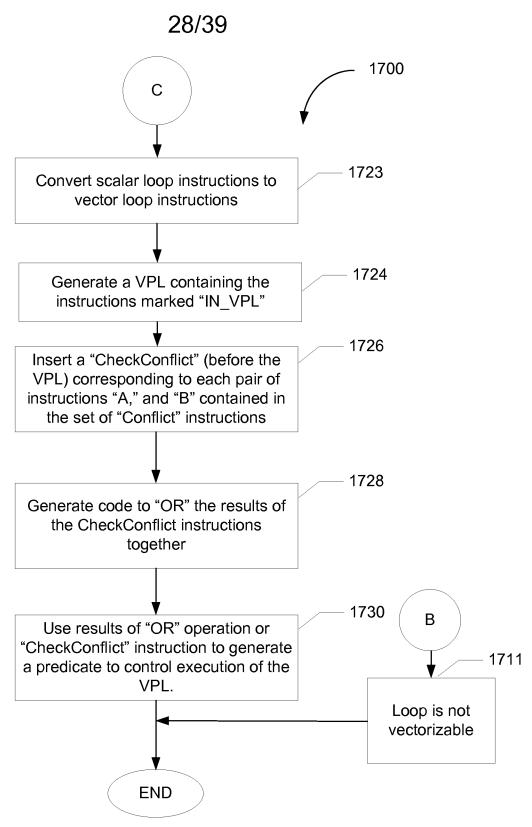

- [0024] FIGS. 17A and 17B illustrate an example flowchart representing example machine readable instructions executed by the example vectorization system of FIG. 1D to vectorize a scalar computer program loop having loop-carried cross iteration memory dependences.

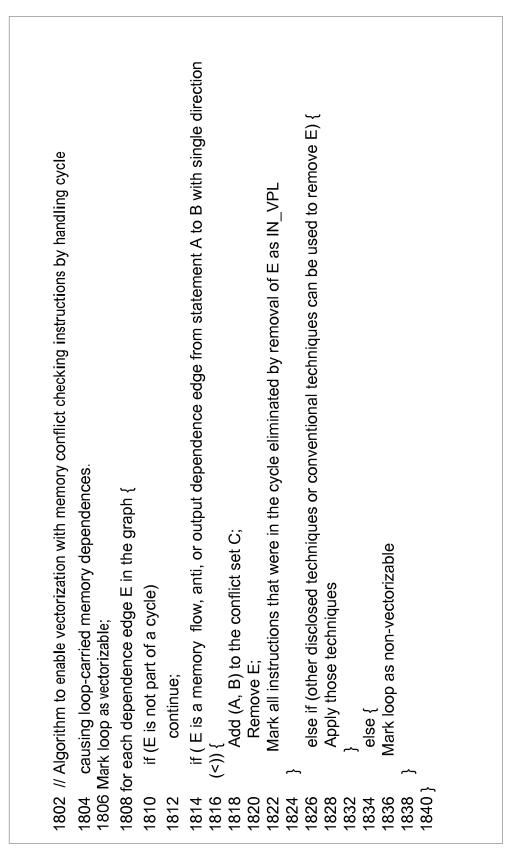

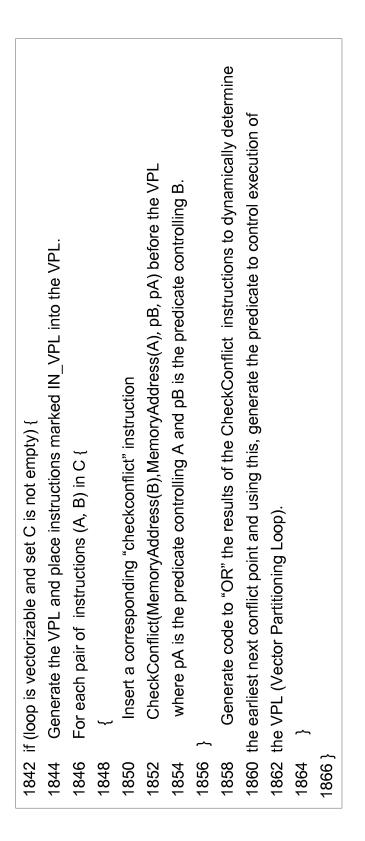

- [0025] FIG. 18A and 18B illustrate example pseudo code representing example machine readable instructions executed by the example vectorization system of FIG. 1D to vectorize a scalar computer program loop having loop-carried cross iteration memory dependences.

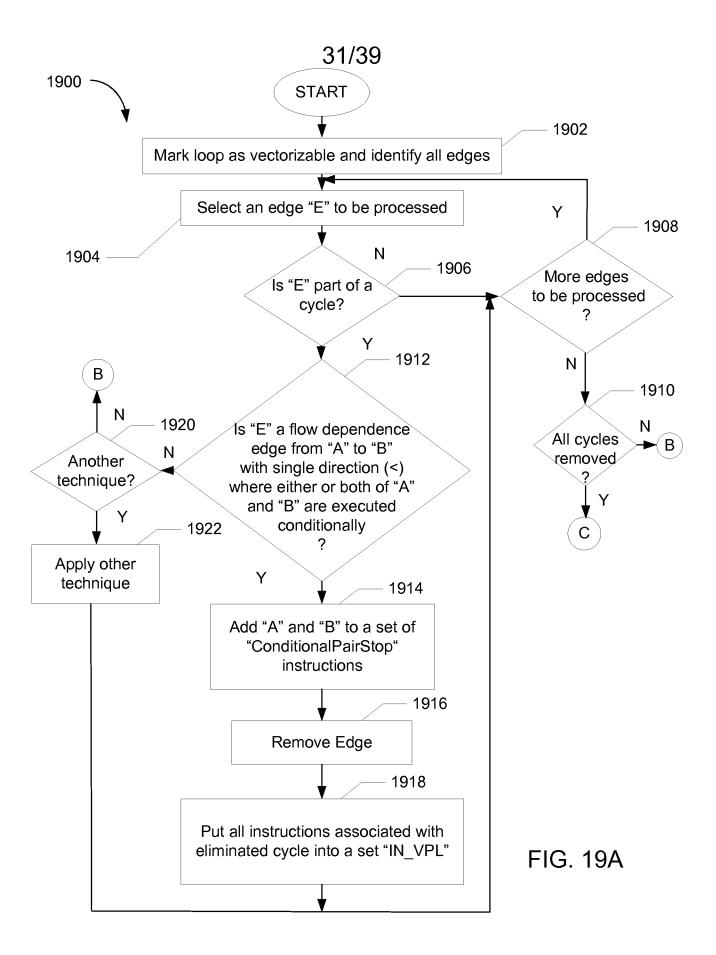

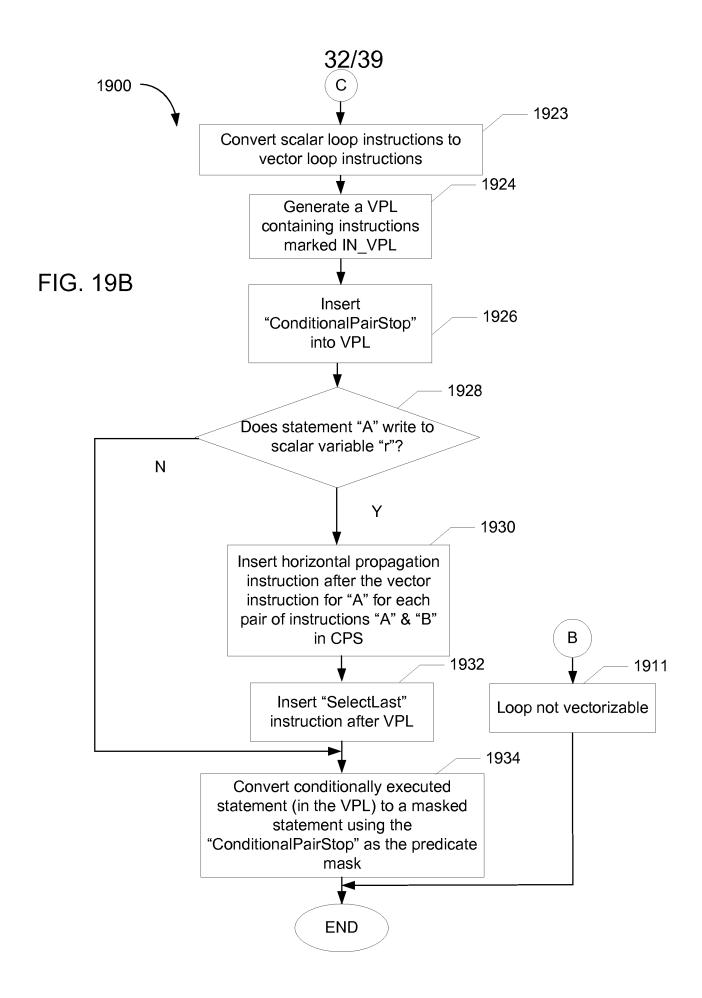

[0026] FIGS. 19A and 19B illustrate an example flowchart representing example machine readable instructions executed by the example vectorization system of FIG. 1E to vectorize a scalar computer program loop having loop-carried dependences arising from conditionally executed statements.

- [0027] FIGS. 20A and 20B illustrate example pseudo code representing example machine readable instructions executed by the example vectorization system of FIG. 1E to vectorize a scalar computer program loop having loop-carried dependences arising from conditionally executed statements.

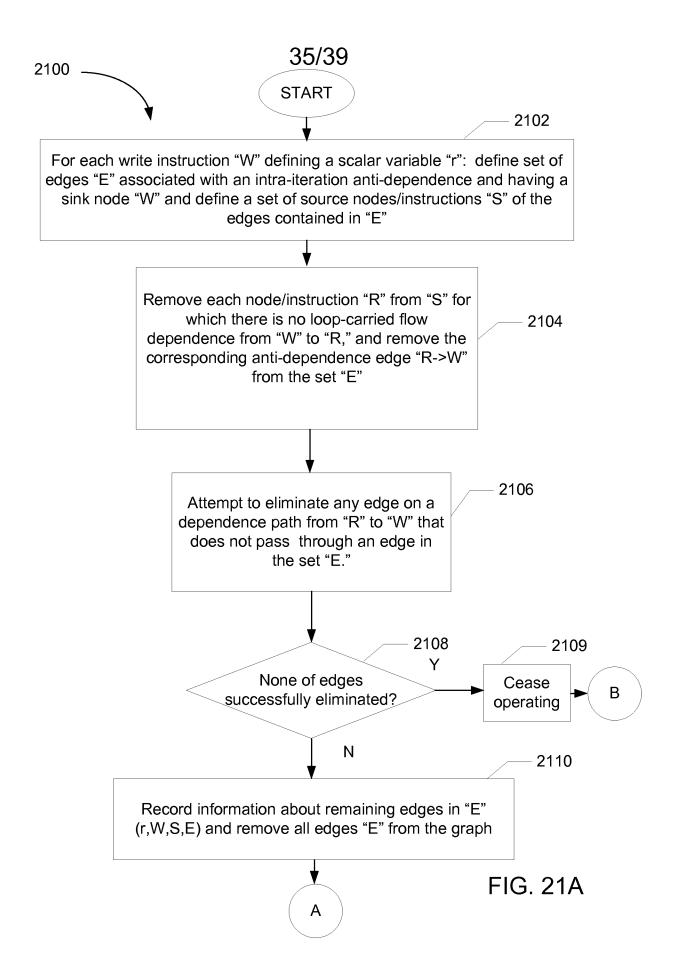

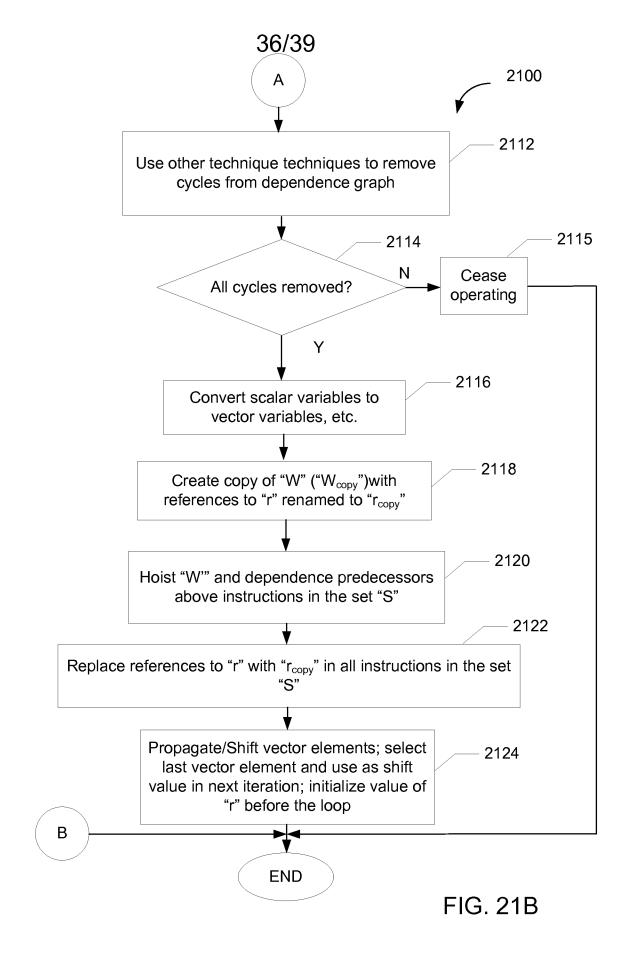

- [0028] FIGS. 21A and 21B illustrate an example flowchart representing example machine readable instructions executed by the example vectorization system of FIG. 1F to vectorize a computer program loop having loop-carried dependences arising from scalar references.

- [0029] FIGS. 22A and 22B illustrate example pseudo code representing example machine readable instructions executed by the example vectorization system of FIG. 1F to vectorize a computer program loop having loop-carried dependences arising from scalar references.

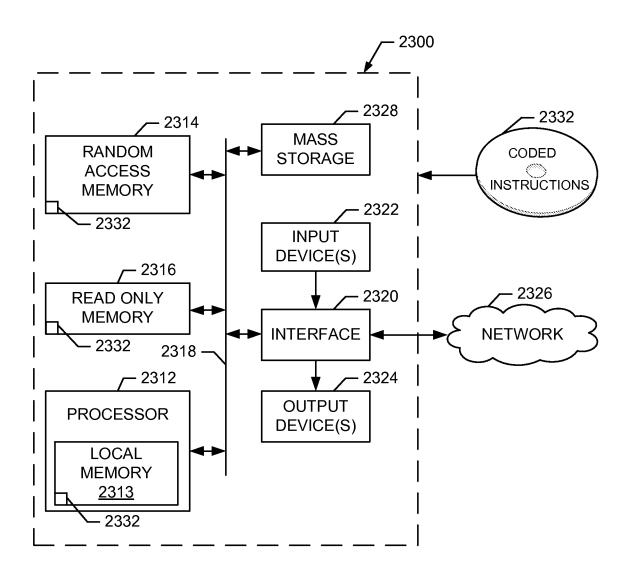

- [0030] FIG. 23 is a block diagram of an example processing system that may execute the example machine readable instructions of FIGS. 13, 14A-14B, 15A 15C, 16A- 16B, 17A 17B, 18A 18B, 19A 19B, 20A 20B., 21A 21B, and 22A 22B to implement the example vectorization systems of FIGS. 1A, 1B, 1C, 1D, 1E and 1F.

- [0031] Wherever possible, the same reference numbers will be used throughout the drawing(s) and accompany written description to refer to the same or like parts.

#### **DETAILED DESCRIPTION**

**[0032]** Example apparatus, methods, systems and articles of manufacture disclosed herein permit vectorization of scalar computer loops having loop-carried dependences. In some examples, the methods and systems enable such vectorization by using computer program code, applications and/or services, including computer code associated with computer languages available in architectures having hardware/software that support speculative vectorization of loops with runtime data dependences, (*e.g.*, Macroscalar<sup>TM</sup> or similar architectures).

[0033] Vectorization allows multiple iterations of a scalar computer program loop to be executed at a same time to thereby improve speed and operating efficiency. To enable parallel loop iteration, each scalar variable in a scalar computer program loop is converted to a vector variable representing a set of numerical values that are each stored in a different vector element (e.g., a vector having "k" elements stores "k" numerical values). (Converting the variables in this manner is sometimes referred to as scalar expansion.) Each vector element of a vector variable corresponds to a different loop iteration such that a first vector element contains a first value calculated during a first iteration, a second vector element contains a second value calculated during a second iteration, etc. Generally, scalar computer program loops can be iterated in parallel (i.e., vectorized) provided that one or more of the instructions in the loop are not dependent on or more other instructions in the loop in a manner that causes a cycle to arise. For example, a dependence between two instructions or variables of a computer program loop exists when the value of a variable calculated in one iteration of the loop depends on a value of the variable calculated in another or the same iteration of the loop. In the case when the variable value calculated in one iteration is dependent on the variable value calculated in a previous, different iteration the dependence is described as "crossing" loop iterations (also referred to as a loop-carried cross-iteration dependence). In the case when the variable value calculated in one iteration is dependent on the variable value calculated in the same iteration the dependence is referred to as a loop-carried intra-iteration dependence.

[0034] In addition to being characterized as either a cross iteration or an intra iteration, dependences can be characterized as being one of two general types: 1) control dependences and 2) data dependences. A control dependence (also referred to as a conditional dependence) exists when a statement is executed based on one or more conditions. For example, a computer program loop containing a scalar that is conditionally defined in one loop iteration and then used either unconditionally or guarded by a different condition in the same or a different loop iteration is one type of conditional dependence.

[0035] In contrast, data dependences between two loop iterations may occur when one statement or instruction (used interchangeably herein) of the loop must be executed in a particular order relative to another statement in the loop. If the statements are not executed in that particular order, the value of a scalar variable used by the loop may be erroneously calculated. For example, a

scalar variable used in a computer program loop should be defined by a write statement before the variable is read by a read statement. Flow dependence, anti-dependence, output dependence, memory dependence and input dependence are all types of data dependences. The following examples of such loop dependences are described with respect to a program code loop having dependences between a first statement "A" and a second statement "B" wherein the statement "A" lexically precedes the statement "B." Note that the adverb "lexically" as used herein refers to the order in which instructions appear in the actual program code of the loop but not necessarily to the order in which the statements are executed based on loop operation (e.g., a loop condition may alter the order in which loop statements are executed while the lexical order of the statements remains unchanged.) For example, a flow dependence between statements "A" and "B" occurs if statement "B" modifies a memory location that statement "A" reads and statement "B" is executed before statement "A" (e.g., "read after write"). Statement "A" is anti-dependent on statement "B" if statement "A" modifies a resource (e.g., memory location) that statement "B" reads and statement "B" is executed before statement "A" (e.g., "write after read"). Statement "A" is output dependent on statement "B" if statement "B" and statement "A" modify the same resource and statement "B" precedes the statement "A" in execution (e.g., "write after write"). Statement "A" is input dependent on a statement "B" if statement "B" and statement "A" read the same memory location and statement "B" is executed before statement "A" (e.g., Read-After-Read). Memory-based dependences arise when a single memory location is read and/or written to by different instructions/statements (e.g., statement "A" and statement "B") in the computer program loop. As used herein, the terms instruction and statement are equivalent and both refer to computer language constructs that are designed/configured to cause a computer to perform one or more operations. As used herein, instructions/statements are tools that are used to perform operations.

[0036] Loop-carried dependences are also described as having directions. For example, if the statement "B" is executed in an iteration subsequent to an iteration in which the statement "A" is executed, the loop dependence between that statement "B" and the statement "A" flows in a forward direction and is represented using the symbol (<). If the statement "B" is executed in an iteration previous to the iteration in which statement "A" is executed, the loop dependence between the statement "B" and the statement "A" flows in a backward direction and is represented using the

symbol (>). If the dependent statements "A" and "B" are both executed in the same iteration of the loop, the dependence between the statement "A" and the statement "B" is referred to an intra-iteration dependence and the direction is represented using the symbol (=).

[0037] One technique for vectorizing a scalar computer program loop includes the use of dependence graphs which are generated using, for example, conventional techniques that are not described herein. A dependence graph represents a computer program loop and is used to identify the loop-carried dependences and cycles present in the computer program loop. The dependent statements or instructions (used interchangeably herein) in the loop are represented in the dependence graph as source nodes and/or sink nodes and nodes that are dependent on one another are connected by a connector referred to as an edge. A source node of an edge is dependent on a corresponding sink node. Therefore, each edge (also referred to herein as a dependence edge) represents a dependence. In some instances, an "edge" is referred to herein as a "dependence edge" and, in these cases, is to be understood to be equivalent to an "edge." As used herein, a dependence edge An edge is represented herein using the following format "(E\_R,W)" where "E" is the edge name, "R" is a read statement representing the source node, and "W" is a write statement representing the sink node. An edge from a source node to a sink node is also represented herein using the following example format "(X\_R,W) where "X" represents the type of dependence associated with the edge and the read and write statements "R" and "W" are source and sink nodes of the edge, respectively. The variable "X" may be represented using an "A" when the edge is associated with an anti-dependence edge, or represented using an "F" when the edge is associated with a flow dependence, etc.

[0038] In some cases, the dependence edges connect to form a path. If the paths form a cycle, the corresponding scalar computer program loop(s) is not vectorizable using conventional techniques (e.g., replacing scalar loop variables with vector loop variables) because the cycle causes one or more outcomes of the scalar loop to be erroneous when executed in parallel iterations. Instead, cycles/path(s) present in scalar loops must be removed/broken from the scalar computer program loop before the scalar computer program loop can be vectorized. Removing/breaking a loop-carried cycle/path from a computer program loop involves eliminating one or more of the edges that connect to form the cycle/path. Edge elimination refers to the performance of operations

that permit the loop to be vectorized. If all cycles can be and have been eliminated from a loop, the loop is vectorizable. In contrast, if all cycles of a graph representing a scalar computer program loop cannot be eliminated, then the loop is not vectorizable.

[0039] A distance vector is used to describe how loop dependences are related with respect to different iterations of a loop. For example, a dependence distance indicates the number of loop iterations that can be performed in parallel. For example, a loop dependence having a distance value of 2 indicates that the dependence occurs two iterations forward (*i.e.*, when the distance value of a loop dependence is 2, two consecutive iterations can be performed in parallel). In contrast, no iterations of a loop having a dependence distance of 1 can iterated in parallel. As a result, the larger the value of the dependence distance, the easier it is to vectorize the loop (*i.e.*, the greater the number of loop iterations that can be executed in parallel without sacrificing loop integrity).

[0040] In some examples, the apparatus, systems, methods and articles of manufacture disclosed herein are performed by a computer system having a vectorization system, a code supplier and a code executer. The example vectorization system includes an analyzer, and a code generator. In some examples, the analyzer creates a list of cycles and/or associated edges in a dependence graph associated with a computer program loop to be vectorized. In some examples, the analyzer performs various operations to process information associated with the edges that form the identified cycles. The analyzer removes cycles and associated edges that have been successfully processed from the list of edges/cycles identified from the dependence graph. If the list of identified edges/cycles is empty, (i.e., all of the edges have been successfully processed), the analyzer supplies the edge-related information to the code generator which operates to compensate for the edges/cycles in a manner that renders the computer program loop vectorizable. In some examples, the code generator inserts instructions, such as hardware instructions into the loop using the information supplied by the edge analyzer. The inserted instructions compensate for cycles caused by the removed edges in a manner that allows multiple iterations of the loop to be iterated in parallel without adversely affecting loop integrity (e.g., the loop outcome). The loop-carried dependences processed by the code vectorization apparatus, systems, methods and articles of manufacture disclosed herein include, for example: 1) lexically backward loop-carried dependences, 2) loopcarried dependences that arise from recurrence loop operations, 3) loop-carried dependences that

arise from cross-iteration memory conflicts, 4) loop-carried dependences arising from conditionally executed statements, and 5) loop-carried dependences arising from scalar references, *etc*.

[0041] As described above, a vectorized loop operates on vector operands and permits multiple iterations of a scalar loop to be executed in parallel. Each vector operand (*e.g.*, vector variable) comprises a vector having a length of, for example, 8 or 16 bits, depending on the processing capabilities of the processor. Each element of the vector variable represents a loop iteration. For example, in a vector having eight elements, the first element contains a value calculated in first iteration of the scalar computer program loop, the second element contains a value calculated in a second iteration of the scalar loop and so on. As used herein, an iteration of a vectorized loop is referred to as a vector iteration and includes the parallel execution of multiple scalar loop iterations and a loop iteration refers to an individual one of the iterations represented by one of the positions in the vector(s) used in the vectorized loop. Thus, a loop control variable of a scalar loop (*e.g.*, loop variable "i") controls the number of loop iterations (*e.g.*, "N") executed by the scalar loop and is incremented by one each time a loop is executed. A loop control variable of a vectorized loop controls the number of vector iterations (*e.g.*, "N – VL") executed by the vectorized loop and is incremented by the vector length each time a vector iteration is executed.

[0042] A block diagram of an example computer system 100A that vectorizes computer program loops containing dependences is illustrated in FIG. 1A. The example computer system 100A of FIG. 1 includes an example vectorization system 110A coupled to an example code supplier 111A and an example code executor 112A. The vectorization system 110A includes an example analyzer 115A and an example code generator 120A. In some examples, the analyzer 115A analyzes computer program code/instructions supplied by the example code supplier 111A to identify instructions that cause loop-carried dependences.

[0043] If the example analyzer 115A determines that the loop contains one or more types of loop-carried dependences/cycles, the example analyzer 115A performs one or more operations to collect information regarding the cycles that is later supplied to the code generator for use in compensating for edges associated with the cycles in a manner that permits vectorization of the scalar computer program loop. In some examples, the analyzer 115A generates a dependence graph

corresponding to the scalar computer program loop being processed and then analyzes the graph to identify the dependence edges present in the graph. The analyzer 115A then processes the edges to collect information about instructions associated with the edges. Because the edges are of a type that can later be compensated for by the code generator, the edges are removed from the list of edges identified by the analyzer. Provided that all edges causing a cycle to arise in the scalar computer program loop have been removed from the list of edges, the collected instruction information regarding the removed edges is supplied to the code generator 120A. The scalar computer program loop and the corresponding edge-related instruction information are transmitted to the example code generator 120A which uses the edge-related information to vectorize the loop. In some examples, the code generator 120A vectorizes the loop by inserting hardware instructions based on the edge-related information to thereby compensate for the edges removed from the list of edges. Iterations of the vectorized loop can then be executed in parallel by the example code executer 112A. In the examples disclosed herein, an edge removal operation performed by the analyzers refers to the removal of an edge from a list of edges associated with a corresponding dependence graph. The code generators disclosed herein then convert the corresponding scalar computer program loop in a manner that compensates for the cycles caused by the removed edges such that multiple iterations of the scalar computer program code can be executed in parallel (i.e., the scalar computer program loop can be vectorized).

# Vectorization of Loops Having Loop-Carried Lexically Backward Dependences that Arise From A Conditionally Defined Scalar Variable

[0044] FIG. 1B is a block diagram of an example vectorization system 110B configured to vectorize loops having loop-carried lexically backward dependences that arise from defining a conditional scalar variable and then using the scalar unconditionally or guarded by a different, second condition. Such a dependence is present in a scalar computer program loop when, for example, a read statement reads a scalar variable and a write statement subsequently write the scalar variable. In addition, the read statement is executed based on a first condition and the write statement is executed based on a second condition. A loop configured to include a read and a write statement that are ordered in this manner and that are based on two different conditions, will have a different outcome when iterated in parallel than when each loop iteration is executed in a serial

fashion. Thus, the loop includes an edge/cycle that must be successfully processed by the analyzer (*i.e.*, removed from the list of edges created by the analyzer) before the loop can be vectorized.

[0045] The vectorization system 110B includes an example analyzer 115B in communication with an example code generator 120B via a communication bus 122B. In some examples, the example analyzer 115B includes a first example controller 125B coupled via a communication bus 130B to an example dependence graph generator 135B, an example graph analyzer 140B, an example predicate set generator 145B, an example edge remover 150B, and an example dependence checker 155B. The example code generator 120B includes a second example controller 160B coupled via a communication bus 165B to an example code converter 170B, an example propagator 175B and an example selector/broadcaster 180B. In some examples, the first controller 125B and the second controller 160B can access a memory 190B as needed to store and/or retrieve information during operation.

[0046] In some examples, the example analyzer 115B receives the program code representing the scalar loop to be vectorized from the example code supplier 111A (see FIG. 1A). The example graph generator 135B then generates a dependence graph representing the scalar loop. The graph generator 135B supplies the graph to the example graph analyzer 140B which uses the graph to identify dependences/edges present in the graph. For example, the graph analyzer 140B creates a list of the edges that were identified based on the dependence graph.

[0047] The example predicate set generator 145B then creates sets that will be populated with vector predicates. A vector predicate includes a set of vector values each corresponding to different loop iteration and each controlling whether a vector loop statement is to be executed in the corresponding iteration. The vector predicate is defined to be a condition that controls execution of a corresponding loop statement in the scalar loop. The example predicate vector sets created by the predicate set generator 145B are later used, as described below, to identify loop statements that cause a loop cycle to arise (*e.g.*, statements that use/read a conditionally defined scalar variable before that same scalar variable has been defined such that the outcome of the loop would be adversely affected if multiple iterations of the loop were to be executed in parallel).

[0048] As used herein, a predicate "p" placed before a vector statement (and enclosed in

parentheses when shown in pseudo code) indicates that the vector statement is to be performed as a masked vector operation. A masked vector operation is an operation that is performed in an iteration only when a value in a vector element of the predicate vector "p," corresponding to the iteration, are TRUE, otherwise the operation is not performed. Thus, for example, a predicate vector "p" used to mask a first vector statement will cause the first vector statement to be executed for the loop iteration only when the value in the predicate vector element corresponding to the same loop iteration is TRUE. The term predicates is also referred to herein as a condition upon which a statement is to be executed. When a condition/predicate appears in a scalar computer program it is a scalar predicate and when a condition/predicate appears in a predicate vector it is referred to as a vector predicate. When describing the operation of a predicate within a vector computer program, it is to be understood that the predicate is a vector. Likewise, when describing the operation of a predicate within a scalar computer program, it is to be understood that the predicate is a scalar. In some instances, when needed for clarity, a predicate that takes the form of a vector is referred to herein as a predicate vector.

[0049] In some examples, the predicate set generator 145B associates two example predicate sets (e.g., a "PredDefSet(W,J)" and a "PredUseSet(W,J)" with each write statement "W" that defines a scalar. The "PredDefSet(W,J)" contains each predicate that, when true, causes the scalar "J" to be defined within the same scalar iteration at or before the write statement, "W." The "PredUseSet(W,J)" contains each predicate that, when true, causes the scalar "J" to be used within the same scalar iteration at or before the write statement, "W." The "PredDefSet(W,J)" is initialized to contain "pW" where "pW" controls execution of the write statement "W," and "PredUseSet(W,J)" is initialized as a NULL set.

[0050] The example edge remover 150B next removes each loop-carried lexically backward anti-dependence edge between a read statement "R" that reads the scalar variable "J" and a write statement "W" that writes the scalar variable "J" from the list of edges generated by the edge analyzer 135B and then adds the predicate "pR" to the set "PredUseSet(W,J)" (i.e., sets PredUseSet(W,J) equal to the union of "PredUseSet(W,J)" and the predicate, "pR"), where "pR" controls the execution of the read statement "R."

[0051] The edge remover 150B also removes, from the list of edges generated by the edge analyzer 135B, each lexically backward output-dependence edge between, for example, two write statements "W1," and "W2" (e.g., a dependence from a second write statement, "W2," to a first write statement, "W1" of a scalar, "J,") provided that the second write statement "W2" is not a recurrence operation. Upon removing the dependences, the edge remover 150B adds the predicate "pW1" to the set "PredDefSet(W2,J)", where "pW1" controls execution of the write statement "W1" (e.g., sets "PredDefSet(W2,J)" equal to the union of "(PredDefSet(W2,J)" and "pW1." (Note that recurrence operations may take the form "T=fn(T,Z)" where the input and output "T" is either a scalar or an array reference to a same memory location. Techniques to vectorize loops having recurrence operations, though not described here, are described in detail below with respect to FIGS. 4, 5, 6, 15A, 15B, 15C, 16A, 16B and 16C.) As described below, the edges associated with the types of dependences described above are processed to permit removal of the edge from the list of edges generated by the edge analyzer 140B because the information related to the removed edges (e.g., the Sets "PredDefSet" and "PredUseSet") is later processed by the code generator 120B to compensate for any of the edges that cause a cycle/path to be present in the loop.

[0052] In addition to performing the operations described above, the edge remover 150B also attempts to use other techniques (including any of the techniques disclosed herein) to process any other edges remaining in the list of edges identified by the edge analyzer 135B. For example, an edge processing technique(s) applicable to the type of edge being processed is attempted (*i.e.*, any technique that will enable vectorization of the loop by the code generator). After the edge remover 150B is done operating, the example dependence checker 155B determines whether any edges remain in the list of edges identified by the edge analyzer 135B. If any cycles remain, then the loop is not vectorizable and the vectorization system 110B stops operating. If the dependence checker 155B determines that no edges remain in the computer program loop being vectorized, the example analyzer 115B supplies the now vectorizable computer program loop to the code converter 170B of the code generator 120B.

[0053] When the vectorizable code is received at the example code generator 120B, the example code converter 170B converts the scalar computer program statements supplied by the example analyzer 115B to vector statements by, for example: 1) replacing references to scalar

variable(s) with references to vector version(s) of the scalar variable(s), 2) replacing conditional statements in the scalar computer program loop to predicate statements "p," 3) converting statements that are executed conditionally to masked predicate operations, 4) replacing the scalar iteration control variable with a vector iteration control variable, *etc*. As used herein, a prefix of "v" is added to a scalar variable to indicate the vector form (scalar expansion) of the scalar variable. For example, "vj" is used to represent the vector form of the scalar variable, "J."

[0054] Next, the propagator 175B determines whether there any vector predicates contained in the "PredUseSet(W,J)" that are not contained in the corresponding "PredDefSet(W,J)." If the vector predicates contained in the "PredUseSet(W,J)" are not a subset of the predicates contained in the corresponding "PredDefSet(W,J)," the write statement, "W" is associated with a dependence cycle. In response, the example propagator 175B performs a propagation operation to compensate for the dependence cycle in a manner that effectively causes the cycle to be broken/eliminated.

[0055] For example, the propagator 175B causes the elements of a conditionally defined vector "vj" of the scalar variable, "J," to propagate from one loop iteration to subsequently executed loop iterations to thereby prevent the execution of an iteration in which the scalar is used but not defined. In operation, the propagator 175B propagates values from the vector elements of the vector "vj" where a corresponding predicate vector element is TRUE to subsequent vector elements of the vector "vj" where a corresponding predicate vector element is FALSE. In some examples, the propagator 175B performs this propagation operation by, for example, inserting instructions (*e.g.*, propagate instructions) after the identified, conditionally executed write statements (*e.g.*, W1, W2...*etc.*).

[0056] In some examples, the selector/broadcaster 180B then selects and broadcasts a last value of a vector "j" computed in a current vector iteration to all elements of a vector "vj." The example selector/broadcaster 180B and broadcaster 170B can do this by, for example, inserting an instruction(s) (e.g., select and/or broadcast instructions) at the bottom of the loop being vectorized. Generally, the select and/or broadcast instructions operate to select and broadcast the value residing at a last vector element of the vector "vj" computed in a first vector iteration to all elements of the

vector "vj" to be used when executing the second vector iteration. For example, and as described above, if each vector is sixteen elements long, then a first set of sixteen iterations are executed in parallel and then a second set of sixteen iterations are executed in parallel and so on, until a desirable number of iterations. When the select and/or broadcast instruction is used, the value calculated for the last vector element of "vj[i]" during the first set of iterations is propagated to each element of the vector "vj[i+1]" to be used when executing the second set of iterations and so on. Thus, selecting and broadcasting the last element of "vj" calculated in the first iterated vector "vj[i]" to the elements of the vector "vj[i+1]" to be used in the second iterated vector "vj[i+1]" ensures that the vector "vj[i+1]" is properly initialized before execution.

[0057] In some examples, the graph generator 135B, the graph analyzer 140B, the predicate set generator 145B, the edge remover 150B and dependence checker 155B operate under the control of the first controller 125B. Likewise, in some examples, the code converter 170B, the propagator 175B, and the selector/broadcaster 180B operate under control of the controller 160B.

[0058] The operation of the example vectorization system 110B of FIG. 1B can be further understood with reference to an example scalar computer program loop 200 illustrated using the pseudo code shown in FIG. 2. The computer program loop 200 contains loop-carried lexically backward anti and output dependences (as described below) arising from conditionally defined scalar variables. A description of the operation of the example loop 200 is followed by a description of how the example vectorization system 110B operates to vectorize the loop 200.

[0059] The example computer program loop 200 begins when a scalar "j" is initialized to equal "a[0]." (See line 202). Next, a loop controlled by a counter "i" is entered (see line 204) and a test for a first condition or first predicate "p1" is performed where p1 is equal to "a[i] < b[i]." (See line 206). If the first predicate, "p1," is met, a first write statement, "W1," is executed by setting the scalar "j" equal to "a[i]" (See line 208). If the first predicate, "p1," is not met, a test for a second condition or predicate, "p2," is performed where "p2" is "c[i] < b[i]." (See line 212). If the second predicate, "p2," is met, a second write statement "W2" is executed by setting "j = c[i]." (See line 214). If the second predicate, "p2," is not met, the program 200 tests for a fourth condition or predicate, "p4," where "p4" is "b[i] > 0." (See line 218). If the fourth predicate, "p4," is met, a read statement, "R1" is executed at which the value of "b[i]" is read as the value of the scalar "j." (See

line 220). If the fourth predicate, "p4," is not met, the value of "j" is returned. (See line 226). (Note that a third predicate "p3" is defined and described with respect to vectorized computer program loop 300 shown in FIG. 3.)

[0060] Thus, the example computer program loop 200 contains two conditional write statements, "W1" and "W2" (see Il. 208, 214) to the scalar variable "j" and one conditional read statement, "R1," (see line 220) of the scalar variable "j." The order in which these instructions are executed creates: 1) lexically backward anti-dependences from "R1" to "W1" and "W2," 2) an output dependence from the first write statement "W1" to the second write statement "W2" and 3) a lexically backward output-dependence from the second write statement "W2" to the first write statement "W1."

[0061] The write statement "W1" defines the variable "j" based on the predicate "p1" and the write statement "W2" defines the variable "j" based on "p2." If either or both "p1" and "p2" are true in a current iteration, then the variable "j" will be defined in the same iteration before the read statement "R" is executed. However, if neither "p1" nor "p2" is true in the current iteration, then the variable "j" will be undefined when the read statement "R" is executed in the same iteration. When the read statement "R" executes before the variable "j" has been defined in the current iteration, the value of the "j" variable set in the preceding iteration will be read in the current iteration. Thus, when neither "p1" nor "p2" is true, an outcome of the current iteration is dependent on the preceding iteration (*i.e.*, the conditional write statements cause a loop dependence) such that iterating the scalar computer program loop in parallel will cause an error in the outcome of one or more of the iterations.

[0062] FIG. 3 illustrates example computer program code 300 representing a vectorized version of the example scalar computer program code 200 (see FIG. 2). In some examples, the vectorization system 110B of FIG. 1 is used to vectorize the scalar computer program loop 200 of FIG. 2 to thereby generate the vectorized computer program loop 300 of FIG. 3. The example analyzer 115B first identifies and processes the edges of the scalar computer program loop 200 to enable vectorization of the loop To perform the conversion, the graph generator 135B generates a dependence graph of the loop 200 (see FIG. 2). The graph analyzer 140B then uses the graph to

identify and create a list of the edges present in the scalar computer program loop 200 (see FIG. 2). The edges present in the computer program loop 200 (see FIG. 2) are associated with 1) lexically backward anti-dependences from "R1" to "W1" and "W2," 2) an output dependence from the first write statement "W1" to the second write statement "W2" and 3) a lexically backward output-dependence from the second write statement "W2" to the first write statement "W1."

[0063] Next, the predicate set generator 145B associates two predicate sets "PredDefSet(W,J)" and "PredUseSet(W,J)" with each of the write statements "W1" and "W2" such that the predicate set generator 145B creates the following four sets: 1) "PredDefSet(W1,j) = {p1}," 2) "PredUseSet(W1,j)={}," 3) "PredDefSet(W2,j)={p2}," and 4) "PredUseSet(W2,j)={}." The example edge remover 150B removes the cross-iteration backward anti-dependence edges between "R1" and "W1" from the list of edges identified by the graph analyzer 140B and sets "PredUseSet(W1,j)" equal to "{p3}," removes the cross-iteration backward anti-dependence edge between "R1" and "W2" from the list of edges identified by the graph analyzer 140B and sets "PredUseSet(W2,j)" equal to "{p3}." The edge remover 150B also removes the cross-iteration output dependence edge of "W2" to "W1" and sets "PredDefSet(W2,j)" equal to "{p2 | p1}." In this example, the "PredUseSet (W1,j)" is not a subset of the "PredDefSet(W1,j)" thereby indicating that the write statement "W1" is associated with a cycle. Likewise, the "PredUseSet (W2,j)" is not a subset of the "PredDefSet(W2,j)" is associated with a cycle.

[0064] After the edge remover 150B stops operating, the example dependence checker 155B determines that all the loop dependence edges have been removed from the list of edges identified by the example graph analyzer 140B and causes the vectorizable loop to be supplied to the example code generator 120B. The example code generator 120B then begins operating to create the vectorized code 300 of FIG. 3 by causing the code converter 170B to convert the conditionally executed statements of scalar loop 200 of FIG. 2 into conditionally executed vector statements in the loop 300 of FIG. 3. For example, to convert the write statement "W1" in loop 2 (see line 208 of FIG. 2) the code converter 170B replaces the conditional statement "if (a[i]<b[i])" (line 206 of FIG. 2) with a statement that defines the condition as a predicate, "p1=a[i:i+VL-1]<b[i:i+VL-1]" (see line 306 of FIG. 3). Here, the first predicate, "p1," (see line 308) is used as a mask vector for performing

the first write statement, "W1" and the second predicate, "p2," (see line 312) is used as a mask vector for performing the second write statement "W2." (See line 314). The predicate "p" enclosed in parenthesis before a statement indicates that the statement is to be performed as a masked vector operation. A masked vector operation is an operation that is performed only when elements of the predicate "p" used as the vector mask are TRUE, otherwise the operation is not performed. Thus, for example, with respect to line 308 of FIG. 3, the first predicate "p1" is used to mask the operation of the first write statement "W1" such that the first write operation "W1" is performed on a particular element of the vector "vj" depending on whether a corresponding vector element of the predicate mask is true.

[0065] In the example of loop 200 and, as described above, the read instruction "R" is only executed when both "p1" and "p2" are true (*i.e.*, the union of "p1" and "p2"). Thus, the example code converter also defines a third predicate "p3" equal to the union of "p1" and "p2" (*e.g.*, "p1|p2") (see line 316) to control execution of the read statement "R."

As described above, the "PredUseSet (W1,j)" is not a subset of the [0066] "PredDefSet(W1,j)" and the "PredUseSet (W2,j)" is not a subset of the "PredDefSet(W2,j)." As a result, the example propagator 175B inserts a first example propagate instruction (e.g., "PropagatePostTrue" instruction) after the first write statement "W1" masked by the predicate "p1" (See line 310) and a second example propagate instruction ("PropagatePostTrue" instruction) after the second write statement "W2" (See line 318) masked by the predicate "p2." As described above, the "PropagatePostTrue" instruction of line 318 causes the values of the vector elements of "vj" calculated in loop iterations in which "p3" is true to be propagated to vector elements calculated in subsequent loop iterations in which "p3" is false. This operation causes the value of the variable "j" calculated in any iteration in which neither "p1" nor "p2" is TRUE (i.e., the iterations in which "j" is not defined before being read) to be equal to the value of the variable "j" calculated in the iteration in which the value of "j" was last defined. In this example, the value of "j" was last defined in the nearest preceding iteration in which either "p1" and/or "p2" were TRUE. Thus, the propagation instruction (see line 318) compensates for the loop dependence(s) caused by the loop statements that use a loop variable in a given iteration before that loop variable has been defined in the same iteration to thereby allow multiple iterations of the loop to be executed in parallel (i.e., vectorized).

[0067] The selector/broadcaster 170B then inserts an example select instruction (e.g., "SelectLast" operation) at the bottom (i.e., end) of the loop to select and broadcast the last value of "j" computed in each loop iteration to all elements of the vector "vj" based on a predicate "TRUE\_Predicate" where all of the values in the "TRUE\_Predicate" are true. (See line 324).

[0068] It is noted that the "PropagatePostTrue" instruction of line 310 is intended to compensate for the loop dependence caused by the conditionally executed write statement "W1." However, by defining the predicate "p3" to account for the circumstances in which neither "p1" nor "p2" is true, the "PropagatePostTrue" instruction at the line 318 of FIG. 3 compensates for both instances in which the read instruction "R" attempts to read a "j" value that has not been previously defined in the same loop iteration. As a result, the "PropagatePostTrue" instruction of line 310 never operates and can be removed without consequence to loop operation.

## Vectorization of Loops Having Loop Dependences Arising From Recurrence Operations

[0069] FIG. 1C is a block diagram of an example vectorization system 110C configured to vectorize loops having loop dependences arising from use of a recurrence operation. Recurrence operations may take the form "T=fn(T,Z) where the input and output "T" is either a scalar or an array reference to a same memory location. One example recurrence instruction can take the form of a write statement "W" where "W" is equal to "t=t+a[i]" such that the value of "t" is set equal to a previously defined value of "t" plus the addend "a[i]." In cases where the value of "t" to be added to "a[i]" was defined in an earlier-executed iteration, (e.g., "t=t[i-1]+a[i]"), the outcome of a current iteration "i" is dependent on an outcome of an earlier executed loop iteration thereby causing a loop dependence to arise.

**[0070]** In some examples, a computer program loop contains a read statement "R" that operates on the variable "t" and precedes execution of the recurrent write statement "W" where the execution of "W" depends on a condition "p." In such examples, assuming that the value of "t" is initialized to "t<sub>initial</sub>" before the computer program loop is entered, after execution of the write statement "W" at a fourth loop iteration, the value of "t" will equal "t<sub>initial</sub>+a[1]+a[2]+a[3]+a[4]" provided that the predicate condition "p" was met in each of the four loop iterations. If, instead, the

predicate condition "p" was met in the first three loop iterations but not the fourth loop iteration, the value of "t" at the fourth loop iteration will equal "t<sub>initial</sub>+a[1]+a[2]+a[3]." Thus, the value of "t" read in each loop iteration will equal "t<sub>initial</sub>" plus the values of "a" associated with earlier loop iterations in which the corresponding predicate condition "p," is met.

[0071] In the illustrated example of FIG. 1C, the vectorization system 110C includes an example analyzer 115C in communication with an example code generator 120C via an example communication bus 122C. The example analyzer 115C operates to identify and process loop dependence edges arising from recurrence operations thereby rendering the computer program loop vectorizable, and the example code generator 120C operates to vectorize the code. In some examples, the example analyzer 115C performs the dependence edge removal operations by creating a dependence graph of the loop, using the graph to identify loop dependences and then removing edges from the graph as described below. The code generator 120C operates to vectorize recurrence instructions included in the computer program loop by causing one or more elements of a first vector to be added to one or more elements of a second vector depending on the value of a predicate vector. In some examples, the elements of the first and second vectors are added using an instruction that creates a running sum of the elements of a vector representing the "addend" of the recurrence instruction as described in greater detail below.

[0072] In some examples, the analyzer 115C includes a first example controller 125C coupled via a communication bus 130C to an example graph generator 135C, an example graph analyzer 140C, an example recurrence instruction identifier 145C, an example edge identifier 150C, an example edge remover 152C, and an example partial vectorization tool 155C. In some examples, the code generator 120C of FIG. 1C includes a second example controller 160C coupled via a communication bus 165C to an example vector code converter 170C, an example selector/broadcaster 175C, an example vector renaming tool 180C, and an example recurrence adder 185C. The example first controller 125C and the example second controller 160C access a memory 190C as needed to store and/or retrieve information during operation.

[0073] In some examples, the example analyzer 115C receives the program code representing the scalar loop to be vectorized from the example code supplier 111A (see FIG. 1A). The example graph generator 135C then generates a dependence graph representing the scalar loop.

The graph generator 135C supplies the graph to the example graph analyzer 140C which uses the graph to identify and create a list of edges present in the dependence graph. .

[0074] The recurrence instruction identifier 145C then marks each recurrence instruction(s) that operates on, for example, a variable "t," with an "S." In some examples, the recurrence instruction "S" are write statement(s) "W" that takes the form "t = t + addend" or the form "t = t - addend" (provided that the variable "addend" is a constant or is a variable expression that is not dependent on the variable "t"). If the addend is not a constant or is a variable expression dependent on the variable "t," then the code is not vectorizable and the vectorization system 110C ceases operating. Here, the variable "t" may be a scalar variable, an array variable or memory accesses where the loop-carried flow-dependence distance in the recurrence operation is 1. A flow dependence distance of 1 indicates that a value written in a previous iteration of the loop is read in the current iteration of the loop. As described above, iterations of a loop having a dependence distance of 1 cannot be iterated in parallel.

[0075] In addition to marking the recurrence instructions/statements with an "S," the example recurrence instruction identifier 145C creates an example set of instructions to store the recurrence instructions/statements, referred to as, for example, "RecurrenceSet(t)" and populates the set with the instructions marked with an "S."

[0076] The example edge identifier 150C of the example analyzer 115C then creates an initially empty set, referred to as "EdgesToRemove(t)," that is later populated with edges that are to be removed from the list of edges generated by the graph analyzer 140C. The example edge identifier 150C adds each intra-iteration anti-dependence edge (e.g., "A") on the operand "t" that extends from a read statement(s) "R" in the loop to one of the write statements "W" in the loop to the "EdgesToRemove(t)" set provided that the write statement "W" is a recurrence instruction "S" and the read statement "R" is not a recurrence instruction "S" (e.g., "RecurrenceSet(t)" set contains the write statement "W" but not the read statement "R"). (If this condition is not met, the vectorization system 110C cannot vectorize the code and ceases operating.) In some examples, the recurrence instruction identifier 145C also creates an initially empty set of instructions, referred to as, for example, "PreAdd(R)," corresponding to each read instruction "R." As described below, the "PreAdd(R)" set corresponding to each read statement "R" will later be populated with the

recurrence write instruction(s) "W" that operate on a same variable (e.g., "t") operated on by the read statement "R."

[0077] Next, the example partial vectorization tool 155C selects an anti-dependence edge remaining in "EdgesToRemove(t)" (*e.g.*, "A") extending from a read instruction "R" to a write instruction "W" with direction (=) and applies partial vectorization techniques to compensate for the edge in a manner that will permit vectorization of the loop. The example partial vectorization tool 155C applies the partial vectorization techniques when the application of the technique will enable vectorization of the loop (*e.g.*, will result in the elimination of one or more cycles in the dependence graph from the read statement "R" to the write statement "W") and further provided that there are paths from the read statement "R" to the write statement "W" that are constructed using intra-iteration dependence edges that do not pass through an edge in the "EdgesToRemove(t)" set. The partial vectorization techniques may include, for example, the partial vectorization techniques described below with respect to FIGS. 11, 14 and 21.

[0078] If one or more of the edges cannot be processed using the partial vectorization technique (e.g., applying partial vectorization will not enable vectorization of the loop by the code generator 120C), the example edge remover 152C removes the recurrence instruction "W" from the "RecurrentSet(t)" set and then removes all edges from the "EdgesToRemove(t)" set. As described below, when the partial vectorization techniques are unsuccessful in removing one or more of the edges from the list of edges generated by the example graph analyzer 140C (i.e., application of partial vectorization will not enable vectorization), other edge processing techniques are later applied in an attempt to remove the cycles created by the edges and thereby enable loop vectorization.

[0079] Provided that the "RecurrenceSet(t)" set is not empty (i.e., "RecurrenceSet(t)" set contains one or more other recurrence write instructions/statements such as a second write statement "W2"), the partial vectorization tool 155C selects the second write statement "W2," adds the associated anti-dependent edges to "EdgesToRemove(t)" and proceeds to operate in the manner described above in an attempt to process the edge dependence graph using partial vectorization techniques. In some examples, the partial vectorization tool 155C is associated with the code

generator 120C instead of the code analyzer 115C.

[0080] If the example partial vectorization tool 155C is successful in permitting removing one or more such edges associated with the recurrence instruction(s) (e.g., "W"), the example recurrence instruction identifier 145C adds the write instruction "W1" to the "PreAdd(R)" set created for each corresponding read statement "R" (e.g., "PreAdd(R)"). In some examples, the example recurrence instruction identifier 145C adds the write statement "W1" to the "PreAdd(R)" set by setting "PreAdd(R)" equal to the union of "PreAdd(R)" and "W." Next, the example edge remover 152C removes loop-carried anti-dependence edges having a sink node contained in the "RecurrenceSet(t)" set from the dependence graph (i.e., from the list of edges created by the edge analyzer 135C) and removes the loop-carried flow or output dependence edges occurring between two recurrence instructions/statements from the dependence graph, (e.g., from the first write statement "W1" to the second write statement "W2), where both the recurrence instruction/statements are contained in the "RecurrenceSet(t)." If, additional recurrence instruction(s) remain in "RecurrenceSet(t)," the operations described above are repeated for each of the remaining recurrence instruction(s).

[0081] If one or more of the edges remaining in the dependence graph connect to form a dependence cycle, one or more other techniques performed by, for example, the analyzers of FIGS. 1B, 1D, 1E and 1F may be deployed to attempt to process the remaining edges. For example, a technique applicable to the type of edge to be processed is attempted (*i.e.*, a technique that will permit vectorization of the loop by the code generator is attempted). If such edges and associated cycles are not successfully processed, the loop cannot be vectorized and the compiler 110A ceases operating. If, instead, such edges and associated cycles are successfully processed/removed from the list edges created by the graph analyzer 140B the loop is now vectorizable and is supplied by the example analyzer 115B to the example code generator 160C for vectorization.

[0082] When the vectorizable code is received at the example code generator 120C, the example code converter 170C converts the scalar computer program loop instructions supplied by the example analyzer 115C to vector program instruction by, for example: 1) replacing references to the scalar variable(s) with references to vector version(s) of the variable(s) 2) replacing conditional

statements in the scalar code with predicate statements "p," 3) converting statements that are executed conditionally to masked predicate operations, 4) replacing the scalar iteration control variable with a vector iteration control variable, *etc*.

[0083] Next, the example recurrence adder 185C recurrently uses a first running sum operation and/or a second running sum operation to add the "addend(s)" values corresponding to each loop iteration (*e.g.*, "a[i], a[i+1], a[i+2], a[i+3], *etc.*") and thereby form a first vector of a first running sum of the addend values (*e.g.*, "vsa1") and a second vector of a second running sum of the addend values (*e.g.*, "vsa2"). Each element in the first and second running sums (*e.g.*, "vsa1" and "vsa2") represents a running sum of the addend values gathered up to a desired loop iteration (*e.g.*, "[i]" or "[i-1]"). In some examples, the recurrence adder 185C forms the first and second running sum vectors (*e.g.*, "vsa1" and "vsa2") by: 1) causing elements of a vector of the addend values (*e.g.*, "va") to be added to elements of another vector (*e.g.*, the vector "v1"), 2) causing elements of the addend vector "va" to be added together, and/or 3) propagating elements of addend vector "va" to subsequent elements of "vsa." The adding and propagating operations performed by the recurrence adder 185C are executed based on a predicate mask condition vector "p." The predicate mask condition "p" corresponds to a condition in the scalar loop used to control operation of the corresponding scalar recurrence instruction "t=t+v[a]."

[0084] In some examples, the example recurrence adder 185C generates the first and second running sums using an example set of propagation instructions (*e.g.*, a "RunningPostAdd" instruction and a "RunningPreAdd" instruction, respectively). The "Running PostAdd" instruction, for example, operates on "v1," "va," and "p" to calculate the first running sum (*e.g.*, "vsa1") and takes the form "vsa1 = RunningPostAdd(v1, va, p)." The "RunningPreAdd" instruction, for example, also operates on the vector, "v1," the vector "va" and the predicate mask vector "p" to calculate a second running sum (*e.g.*, vector "vsa2") and takes the form "vsa2 = RunningPreAdd(v1, va, p)." Both instructions traverse the vector elements of the predicate mask vector "p" starting from the vector element residing at the vector element position "0" of the predicate mask vector. Each vector element value contained in the first vector "v1" is copied to a corresponding element position "k" in the first and second running sum vectors (*e.g.*, "vsa1" and "vsa2") until the first TRUE predicate element of the predicate mask vector "p" is encountered. When the first TRUE

predicate element of the predicate mask vector "p" is encountered, a running sum (*i.e.*, partial sum) of the mask enabled elements of the vector "va" is added to the first mask enabled element of the vector "v1" and stored as the element residing in the corresponding position "k" of the first running sum vector and the second running sum vector (*e.g.*, "vsa1" or "vsa2"). When using the "RunningPostAdd," instruction, the value recorded at the vector element position "k" of the vector "vsa1" (*i.e.*, "vsa1[k]") includes the addition of the element residing at the vector element position "k" of the vector "va," (*i.e.*, the first running sum is gathered up to and include the element of the vector "va" located at the position "k"). In contrast, for "RunningPreAdd" the vector value recorded at the vector element position "k" of the vector "vsa2" includes the partial sum of the elements of the vector "va" gathered up but not including the element residing at the vector element position "k" (*i.e.*, the second running sum is gathered up to the element of the vector "va" located at the position "k-1"). Note that the vector "v1" represents an initial value to be added to the partial sum (*e.g.*, "vsa1" or "vsa2"). In some examples, the recurrence adder 185C initializes the elements of the vector "v1" at the top of the loop.

[0085] Using the example of FIG. 4 to demonstrate the operation of the "RunningPostAdd" and "RunningPreAdd" instructions when using the predicate "p" to operate on the illustrated eight element vectors "v1" and "va," the vector value of "vsa1" residing at the vector element position "k=0" is equal to the vector value of "v1" residing at the vector element position "k=0" (e.g., "vsa1[0]" = "v1[0]." Likewise, "vsa1[1]" = "v1[1]" because the first two elements of the predicate vector "p" residing at the vector element positions "k=0" and "k=1" are FALSE. The first TRUE value of "p" resides at the vector element position "k=2." Hence, the running sum is computed starting at the vector element position "k=2. Thus, the value of "vsa1" at vector element position "k=2" is equal to "v1[2] + va[2]" and the value of "vsa2" at vector element position "k=2" is equal to "v1[2]." Likewise, because "p[3]" is TRUE, the value of "vsa1" at "k=3" is equal to "v1[2] + v2[2] + v2[3]" and the "vsa2" at "k=3" is equal to "v1[2] + v2[2]." The values of "vsa1" remain unchanged at k = 4, 5 and 6 because the predicate "p" is FALSE at these vector element positions is FALSE and the value of "vsa1" includes the addition of "v2[7]" at "k=7." The values of "vsa2" remain unchanged at k = 4, 5, 6 and 7 because the predicate "p" is FALSE at these vector element positions is FALSE and the value of "vsa2" does not include the addition of "v2[7]" at

"k=7."

[0086] Referring again to FIG. 1C, after inserting the instructions that generate the first running sum (e.g., "vsa1"), the example recurrence adder 185C re-defines the vector "vt" by inserting a vector recurrence operation that adds the first running sum to the vector "vt." Thus, in some examples, the example recurrence adder 185C inserts the sequence of vector instructions "{vsa1 = RunningPostAdd(v1,va,p}; vt = vt+vsa1}," where "S" is of the form "t=t+a" or the instruction sequence "{vsa1 = RunningPostAdd(v0,va,p}; vt = vt-vsa1}," where the instruction "S" is of the form "t = t-a").

[0087] Next, to distinguish the vector "vt" being written by a recurrence write instruction "W" and then read by a read instruction "R" from other forms of the vector "vt" that are used elsewhere in the computer program loop, the example renaming tool 180C renames the vector "vt" before each read instruction "R" that operates on the vector "vt." In some examples, the example renaming tool 180C renames the vector, "vt," operated on by the read instruction "R" to "vtk" and replaces references to the vector "vt" in the read instruction "R" with references to the vector "vtk."

**[0088]** In some examples, for each recurrence instruction "S" (*e.g.*, each write instruction "W") included in a "PreAdd(R)" set, the recurrence adder 185C uses a second summing operation to generate a second running sum of the addend associated with the corresponding recurrence instruction "S" gathered up to the previous iteration. The second summing operation, in some examples, is implemented using the instruction "vsa2 = RunningPreAdd(0,va,p1)." In addition, the recurrence adder 185C inserts a second recurrence instruction that defines the vector "vt" as being equal to the sum of the vector "vt" and the second running sum (*e.g.*, "vtk = vtk + vya" or "vtk = vtk – vya" depending on whether the corresponding scalar recurrence operation takes the form "t = t + a" or "t = t – a," respectively). Thus, the example recurrence adder 185C generates the second running sum and the second recurrence instruction using the sequence of vector instructions {"vya=RunningPreAdd(0,vz,p1); vtk = vtk + vya" or "vya=RunningPreAdd(0,vz,p1); vtk = vtk - vya"}.

[0089] The sequences of instructions inserted by the recurrence adder 185C compensate for the cycles created by the edges removed from the list of edges created by the graph analyzer

140C (see FIG. 1C) such that the code generator 120C can vectorize the loop (*i.e.*, convert the scalar loop to a loop that can be iterated in parallel without adverse effect on loop integrity).

[0090] At this point, one or more optimization techniques, such as copy propagation and common sub-expression elimination or partial redundancy elimination can be performed to further fine tune/optimize the vectorized code.

[0091] The example selector/broadcaster 175C initializes every element in the vector "vt" (before the vector loop is entered) using an initial value of the scalar variable "t." In some examples, the selector/broadcaster 175 C performs this operation by inserting, for example, a "broadcast" instruction (e.g., "vt = Broadcast(t)"). The selector/broadcaster 175C performs this initializing operation on each scalar variable that is subject to a recurrence instruction "S" included in the computer program loop. The example selector/broadcaster 175C also inserts the last mask-enabled element of the vector "vt" (calculated at the bottom of the first loop iteration) to be inserted into each element of the vector "vt" at the start of the succeeding vector iteration. Thus, the value in the last element of "vt" calculated in the initial vector iteration is used at the input of the succeeding vector iteration (e.g., the last element of the vector "vt" calculated at the bottom of a vector iteration is used to populate each element of the vector "vt" at the top of the next loop iteration). In some examples, the example selector/broadcaster 175C selects the last value of the vector "vt" by inserting a "SelectLast" instruction (e.g., "vt= SelectLast(vt, p0)") where "p0" is a predicate mask vector having all elements set to TRUE. In some examples, the selector/broadcaster 175C also inserts a broadcast instruction before the loop is entered to set the elements of the predicate mask vector "p0." In addition, in some examples, the selector broadcaster 175C sets or clears the elements of the vector "v1" before the loop is entered.

[0092] In some examples, the example graph generator 135C, the example graph generator 135C, the example graph analyzer 140C, the example recurrence instruction identifier 145C, the example edge identifier 150C, the example edge remover 152C, and the example partial vectorization tool 155C operate under the control of the first example controller 125C. Likewise, in some examples, the example vector code converter 170C, the example selector/broadcaster 175C, the example vector renaming tool 180C, and the example recurrence adder 190C operate under the

control of the second controller 160C.

[0093] An example computer program loop 500 illustrated using the pseudo code shown in FIG. 5 is described to provide one example of a loop having loop dependences that arise from recurrence operations/statements. The description of the loop operation is followed by a description of how the example vectorization system 110C operates to vectorize the computer program loop 500 of FIG. 5.

[0094] The example computer program loop 500 sets a variable "sum" equal to "0." (See line 502) and defines a loop iteration control variable "i." (See line 504). Upon entering the loop, a first read instruction "R1" is executed on a variable "sum." (See line 506). If a condition (e.g., predicate "p1") equal to "a[i] < K" returns TRUE (see line 508), then a first write statement "W1" operates as a recurrence operation to read and write to the variable "sum." (See line 510). (Note that the variable "K" used in the conditional "p1" is not related to the "k" variable used earlier to represent the vector elements.) Otherwise, a second read statement "R2" reads the variable "sum." (See line 514). Next, if a predicate "p2" equal to "b[i] < K2" returns TRUE (see line 516), then a second write statement "W2" operates as a recurrence operation to read and write the variable "sum." (See line 518). Lastly, a third read statement "R3" reads the variable sum. (See line 522). Thus, as described, the loop 500 of FIG. 5 reads the variable sum at the statement "R1" and then conditionally adds a first value "a[i]" to the variable "sum" based on the predicate "p1" at the write statement "W1" and/or adds a second value "b[i]" based on the predicate "p2" at the write statement "W2." The loop 500 also reads the results of the write statement "W1," and the write statement "W2." Thus, the variable "sum" calculated in one iteration of the loop 500 is used in subsequent iteration(s) of the loop 500 and the method used to calculate the variable "sum" changes in each loop based on the conditions "p1" and "p2."

[0095] An example computer program loop 600 representing a vectorized version of the loop 500 of FIG. 5 is illustrated using the pseudo code of FIG. 6. Before the code generator 120D creates the vectorized code, the example analyzer 115D operates to the convert the code in the manner described above. For example, the graph generator generates a graph of the computer program loop of FIG. 6 and the graph analyzer analyzes the graph to identify and create a list of loop edges.

[0096] As described above, the loop 500 conditionally adds a value to the scalar variable "sum" at the statement "W1" which is then read in the same and/or subsequent loop iterations by one or more statements "R1," "W1," "R2," "W2," and "R3." Thus, when operating on the program loop 500 of FIG. 5, the graph analyzer 140C identifies an intra-iteration anti-dependence edge "A1\_R1W1" on the variable "sum" from the read statement "R1" to the write statement "W1" that requires that the statement "R1" lexically precede the write statement "W1." As a result, a flow dependence edge "F1\_W1R1" from the write statement "W1" to the read statement "R1" on the variable "sum" is a loop-carried lexically backward flow dependence. Similarly there are intraiteration anti-dependences edges, "A2\_R1W2," A3\_W1W2, A4\_R2W2 on the variable "sum" from the read statement "R1," to the write statement "W1," and from the read statement "R2" to the write statement "W2" that require that the read statement "R1," the write statement "W1", and the read statement "R2" lexically precede the write statement "W2." Hence a set of flow dependence edges "F2\_W2R1," "F3\_W2W1," and "F4\_W2R2" from the write statement "W2" to "R1," "W1," and "R2" on the variable "sum" are loop-carried lexically backward flow dependences/edges. Together, these flow and anti-dependences "F1\_W1R1," "F2\_W2R1," "F3\_W2W1," and "F4\_W2R2" and "A1 R1W1," "A2 R1W2," "A3 W1W2," and "A4 R2W2" create cycles in the dependence graph. There are also cycles created by self flow dependences as well as flow dependences between the recurrence operations "W1" and "W2." In addition there are cycles created by output dependences between "W1" and "W2" (referred to as "O1 W2W1", O2 W1W1," O3 W2,W2"). A conventional compiler would not be able to vectorize this loop.

[0097] After the graph analyzer 140C has identified and created a list of the dependences of the computer program loop 500, the example recurrence instruction identifier 145C creates the "RecurrenceSet(sum)" set and defines the set to contain the recurrence instructions/statements "{W1,W2}." The example edge identifier 150C creates the initially empty set of edges to be removed, "EdgesToRemove(sum)". The example edge identifier 150C then adds each intraiteration anti-dependence edge "A" on the operand "sum" from a read instruction to a write statement to the "EdgesToRemove(t)" set provided that the "RecurrenceSet(sum)" set contains the corresponding write statements "W1" and "W2" but not the corresponding read statements "R1" and "R2." In the loop 500, the intra iteration edges "A1," "A2," and "A4" correspond to the edges from

"R1" to "W1," from "R1" to "W2" and from "R2" to "W2," respectively, and "RecurrenceSet(sum)" contains "W1" and "W2" but not "R1" and not "R2." As a result, the edges "A1," "A2," and "A4" are each added to the "EdgesToRemove(t)" set.

- [0098] As described above, in some examples, the edge identifier 150C creates an initially empty set of instructions, "PreAdd(R)." to contain read statements "R." A different "PreAdd(R)" set is created for each read instruction "R" in the loop 500 (i.e., "PreAdd(R1)" and "PreAdd(R2)." The example edge identifier 150C adds "W1" and "W2" to "PreAdd(R1)" because the anti-dependent intra-iteration edge "A1\_R1,W1" extends from "R1" to "W1" and the anti-dependence intra-iteration edge "(A2\_R1,W2)" extends from "R1" to "W2." The example edge identifier 150C also adds the write statement "W2" to "PreAdd(R2)" because the anti-dependence intra-iteration edge "A4\_R2,W2" extends from "R2" to "W2."

- [0099] In the scalar computer program loop 500 of FIG. 5, every path formed using intra-iteration dependence edges "A1," "A2" and "A4" passes through an edge in the "EdgesToRemove(sum)" set such that the partial vectorization tool 155C does not apply partial vectorization techniques to remove these edges.

- [00100] Next, the edge identifier 150C removes the edges contained in the "EdgesToRemove(t)" set from the dependence graph/list of edges and removes any loop-carried anti-dependence edges on the variable "sum" if the sink node of the edge is in the "RecurrenceSet(t)." This operation results in the removal of the edges "A1," "A2," "A3," and "A4" from "EdgesToRemove(sum)" and from the list of edges.