Office de la Propriété Intellectuelle du Canada

Un organisme d'Industrie Canada Canadian

Intellectual Property

Office

An agency of

Industry Canada

CA 2357236 C 2011/09/06

(11)(21) 2 357 236

(12) BREVET CANADIEN CANADIAN PATENT

(13) **C**

- (22) Date de dépôt/Filing Date: 2001/09/12

- (41) Mise à la disp. pub./Open to Public Insp.: 2002/04/17

- (45) Date de délivrance/Issue Date: 2011/09/06

- (30) Priorité/Priority: 2000/10/17 (US60/240,859)

- (51) Cl.Int./Int.Cl. *H05K 5/02* (2006.01), *G06F 1/18* (2006.01)

- (72) Inventeurs/Inventors:

RIBEIRO, DURVAL S., US;

RAICHLE, KURT R., US

- (73) Propriétaire/Owner: SPX CORPORATION, US

- (74) Agent: ROBIC

(54) Titre: MODULE ENFICHABLE POUR DISPOSITIF D'INFORMATIQUE PORTATIF

(54) Title: PLUG-IN MODULE FOR PORTABLE COMPUTING DEVICE

#### (57) Abrégé/Abstract:

A plug-in module adds functionality to a portable electronic device. The module includes a housing that is accepted by a housing port of the portable electronic device. The module includes at least one latch to secure the module to the electronic device. Each

CA 2357236 C 2011/09/06

(11)(21) 2 357 236

(13) **C**

#### (57) Abrégé(suite)/Abstract(continued):

latch includes a first member, a second member, and a third member. The housing includes at least one receptacle corresponding to each latch. The receptacles are sized and positioned to accept a member of the latch and direct the latch to a groove located on the portable electronic device. Optionally, the latch includes a slip-resistant surface sized to accept a human finger or thumb. The module also preferably includes a hardware interface connector sized and positioned within the housing to engage a 120-pin hardware interface port on the portable electronic device when the module housing is positioned on the housing port of the portable electronic device. Receptacles of the electric connector have certain functionality corresponding to the pins on the port.

## ABSTRACT OF THE DISCLOSURE

A plug-in module adds functionality to a portable electronic device. The module includes a housing that is accepted by a housing port of the portable electronic device. The module includes at least one latch to secure the module to the electronic device. Each latch includes a first member, a second member, and a third member. The housing includes at least one receptacle corresponding to each latch. The receptacles are sized and positioned to accept a member of the latch and direct the latch to a groove located on the portable electronic device. Optionally, the latch includes a slip-resistant surface sized to accept a human finger or thumb. The module also preferably includes a hardware interface connector sized and positioned within the housing to engage a 120-pin hardware interface port on the portable electronic device when the module housing is positioned on the housing port of the portable electronic device. Receptacles of the electric connector have certain functionality corresponding to the pins on the port.

# PLUG-IN MODULE FOR PORTABLE COMPUTING DEVICE

#### FIELD OF THE INVENTION

The present invention relates generally to an apparatus for adding functionality to a portable computing device. More particularly, the present invention relates to a plug-in module for use with a portable computing device. The module may include a latching mechanism to secure the module to the apparatus, a pin or hole connector designed to transfer data, signals, or other communications between the plug-in module and the portable computing device, and optionally other functionality.

#### BACKGROUND OF THE INVENTION

10

20

Computing devices, such as personal computers, main frames, lap top computers, pocket PCs, personal digital assistants, portable analog or digital analyzers, and the like provide users with specific functionality based on the design and features of the device. As technology, usage patterns, and user requirements change, users may desire to add additional functionality to a portable computing device. Such devices are particularly desirable in connection with portable diagnostic equipment, such as analog or digital analyzers. For example, a diagnostic device such as an engine analyzer may serve to collect and analyze multiple aspects of an engine or vehicle, including aspects of vehicle operation such as emissions component, system pressure, fluid pressure, system temperature, and other aspects of conditions.

However, the prior art plug-in modules do not provide functionality to all types of electronic devices. For example, a plug-in module is not available that security attaches to, and interfaces with, certain portable electronic devices having a 120-pin or 120-receptacle hardware

TO THE POST OF THE

interface port.

10

15

20

25

If a module were available that could interface with such a portable electronic or computing device, the device could receive additional memory, software, features, hardware and functionality. Such a module may also facilitate the use of software, features and functionality for other portable computing devices, as well as previous versions of portable computing devices. In addition, it is desirable that such a module latch onto the portable computing device so that it does not fall off of the device when transported, but that the module also be easily removable when it is not needed, or when a replacement module is desired.

It is therefore desirable to provide an improved plug-in module for a portable electronic or computing device.

## SUMMARY OF THE INVENTION

It is therefore a feature and advantage of the present invention to provide an improved plug-in module for a portable electronic or computing device.

The above and other features and advantages are achieved through the use of a novel plug-in module as herein disclosed. In accordance with one embodiment of the invention, a plug-in module adds functionality to a portable electronic device. The module includes a housing that is of a size appropriate to be accepted by a housing port of the portable electronic device. The module includes at least one latch to secure the module to the electronic device. Each latch includes a first member, a second member, and a third member, and each member has a first end and a second end. The first end of the first member is connected to the first end of the second member such that the first and second members also form an angle of between 60° and 130°. The second end of the first member is connected to the first end of the third member such that the first and third members form an angle of between 60° and 130°. The housing includes at least one receptacle corresponding to each latch. The receptacles are sized and positioned to accept a latch and direct the latch to a groove, such as a notch, located on the portable electronic device

so that the third member of the latch mates with the groove or notch and secures the housing to the portable electronic device.

Optionally, the latch includes a slip-resistant surface, sized to accept a human finger or thumb. Such a slip-resistant surface may be connected to the second end of the second member of the latch. Also optionally, the latch includes a notch positioned substantially at the point where the first member connects to the second member. The notch of the latch is sized and positioned to engage a raised portion or rib located on the interior surface of the housing when the latch is inserted into the receptacle and positioned to mate with the groove or notch of the housing.

The embodiment also optionally includes a hardware interface connector sized and positioned within the housing to engage a hardware interface port on the portable electronic device when the module housing is positioned on the housing port of the portable electronic device. The hardware interface port and hardware interface connector comprise 120-pin or 120-receptacle connectors or ports.

In accordance with another embodiment of the present invention, an apparatus for adding functionality to a portable electronic device comprises:

a housing having an interior portion, the housing sized to be received by a housing port of a portable electronic device, the housing port disposed within an interior portion of the portable electronic device; and

a hardware interface connector disposed within the interior portion of the housing and in connection with a hardware interface port disposed within the housing port of the portable electronic device, wherein at least a portion of the housing is disposed within the interior portion of the portable electronic device when the hardware interface connector is in connection with the hardware interface port,

the hardware interface connector having between 1 and 120 receptacles, the hardware interface port having 120 pins, the receptacles configured to correspond to a pin in the hardware interface port, the receptacles further forming two rows in parallel such that each receptacle is positioned to be numbered corresponding to its

10

position in one of the rows, wherein one of the two rows includes receptacle positions 1 through 60, the other of the two rows includes receptacle positions 61 through 120, receptacle positions 1 and 61 being located at corresponding ends of each row, receptacle positions 60 and 120 being located at opposite ends of each row, receptacle positions 1 and 120 being located at opposite ends of each row, and receptacle positions 60 and 61 being located at opposite ends of each row; and

securing means for securing the portable electronic device to the housing.

In accordance with one embodiment of the present apparatus, at least one of the receptacles on the connector corresponds to at least one of positions 50, 56, 57, 58, 60, 61, 62, 64, 65, 66, 68, 69, 70, 72, 73, 74, 76, 77, 78, 80, 81, 82, 84, 85, 86, 88, 89, 105, 106, 108, and 110, and such receptacle or receptacles also correspond to a bus, such as a microprocessor interface bus, located within the portable electronic device.

In accordance with another embodiment of the present invention, at least one of the receptacles corresponds to at least one of positions 111, 112, 113, 114, 116, 118, and 120, and such receptacle or receptacles relate to power.

In accordance with another embodiment of the present invention, at least one of the receptacles corresponds to at least one of positions 3, 5, 7, 9, 11, 15, 19, 23, 27, 31, 35, 39, 47, 51, 55, 59, 63, 67, 71, 75, 79, 83, 87, 91, 95, 99, 103, 107, 109, 115, 117, and 119, and such receptacle or receptacles correspond to an electrical ground.

In accordance with another embodiment of the present invention at least one of the receptacles corresponds to at least one of positions 90, 92, 93, 96, 97, 100, 101, 102, 104, and 105, and such receptacle or receptacles correspond to a microprocessor discrete input/output.

In accordance with another embodiment of the present invention at least one of the receptacles corresponds to at least one of positions 2, 4, 6, 8, 10, 12-14, 16-18, 20-22, 24-26, 28-30, 32-34, 36-38 and 40, and such receptacle or receptacles correspond to a field programmable gate array (FPGA) discrete input/output.

The analysis of the analysis o

In accordance with another embodiment of the present invention, a method of adding functionality to a portable electronic device comprises the steps of:

sizing a housing to be accepted by a housing port of a portable electronic device, the housing having an interior portion;

providing a hardware interface connector disposed within the interior portion of the housing, the hardware interface connector having between 1 and 120 receptacles, wherein the receptacles are arranged in two parallel rows such that each receptacle is positioned to be numbered corresponding to its position in one of the rows, wherein one of the two rows includes receptacle positions 1 through 60, the other of the two rows includes receptacle positions 61 and 120, receptacle positions 1 and 61 being located at corresponding ends or each row, receptacle positions 1 and 120 being located at corresponding ends of each row, receptacle positions 1 and 120 being located at opposite ends of each row, and receptacle positions 60 and 61 being located at opposite ends of each row;

10

20

providing a hardware interface port disposed within the housing port, the hardware interface port having 120 pins;

connecting the hardware interface port to the hardware interface connector within the interior portion of the housing;

configuring the receptacles to correspond to a pin in the hardware interface port; and securing the portable electronic device to the housing.

In accordance with another embodiment of the present invention, an apparatus for adding functionality to a portable electronic device comprises:

a housing having an interior portion, the housing sized to be received by a housing port of a portable electronic device, the housing port disposed within an interior portion of the portable electronic device;

a hardware interface connector disposed within the interior portion of the housing and connected to a hardware interface port disposed within the housing port of the portable electronic device, the hardware interface connector having a plurality of receptacles, the hardware interface port having a plurality of pins wherein the

receptacles are configured to correspond to a pin in the hardware interface port, wherein at least a portion of the housing is disposed within the interior portion of the portable electronic device when the hardware interface connector is in connection with the hardware interface port; and

securing means for securing the portable electronic device to the housing;

wherein the hardware interface connector has between 1 and 120 receptacles and the hardware interface port has 120 pins,

wherein the receptacles are arranged in two parallel rows such that each receptacle is positioned to be numbered corresponding to its position in one of the rows, wherein one of the two rows includes receptacle positions 1 through 60, the other of the two rows includes receptacle positions 61 and 120, receptacle positions 1 and 61 being located at corresponding ends of each row, receptacle positions 60 and 120 being located at corresponding ends of each row, receptacle positions 1 and 120 being located at opposite ends of each row, and receptacle positions 60 and 61 being located at opposite ends of each row.

10

There has thus been outlined, rather broadly, the more important features of the invention in order that the detailed description thereof that follows may be better understood, and in order that the present contribution to the art may be better appreciated. There are, of course, additional features of the invention that will be described below and which will form the subject matter of the claims appended hereto.

The second control of the second control of

In this respect, before explaining at least one embodiment of the invention in detail, it is to be understood that the invention is not limited in its application to the details of construction and to the arrangements of the components set forth in the following description or illustrated in the drawings. The invention is capable of other embodiments and of being practiced and carried out in various ways. Also, it is to be understood that the phraseology and terminology employed herein, and the abstract set forth below, are for the purpose of description and should not be regarded as limiting.

As such, those skilled in the art will appreciate that the conception upon which this disclosure is based may readily be utilized as a basis for the designing of other structures, methods and systems for carrying out the several purposes of the present invention. It is important, therefore, that the claims be regarded as including such equivalent constructions insofar as they do not depart from the spirit and scope of the present invention.

10

15

#### BRIEF DESCRIPTION OF THE DRAWINGS

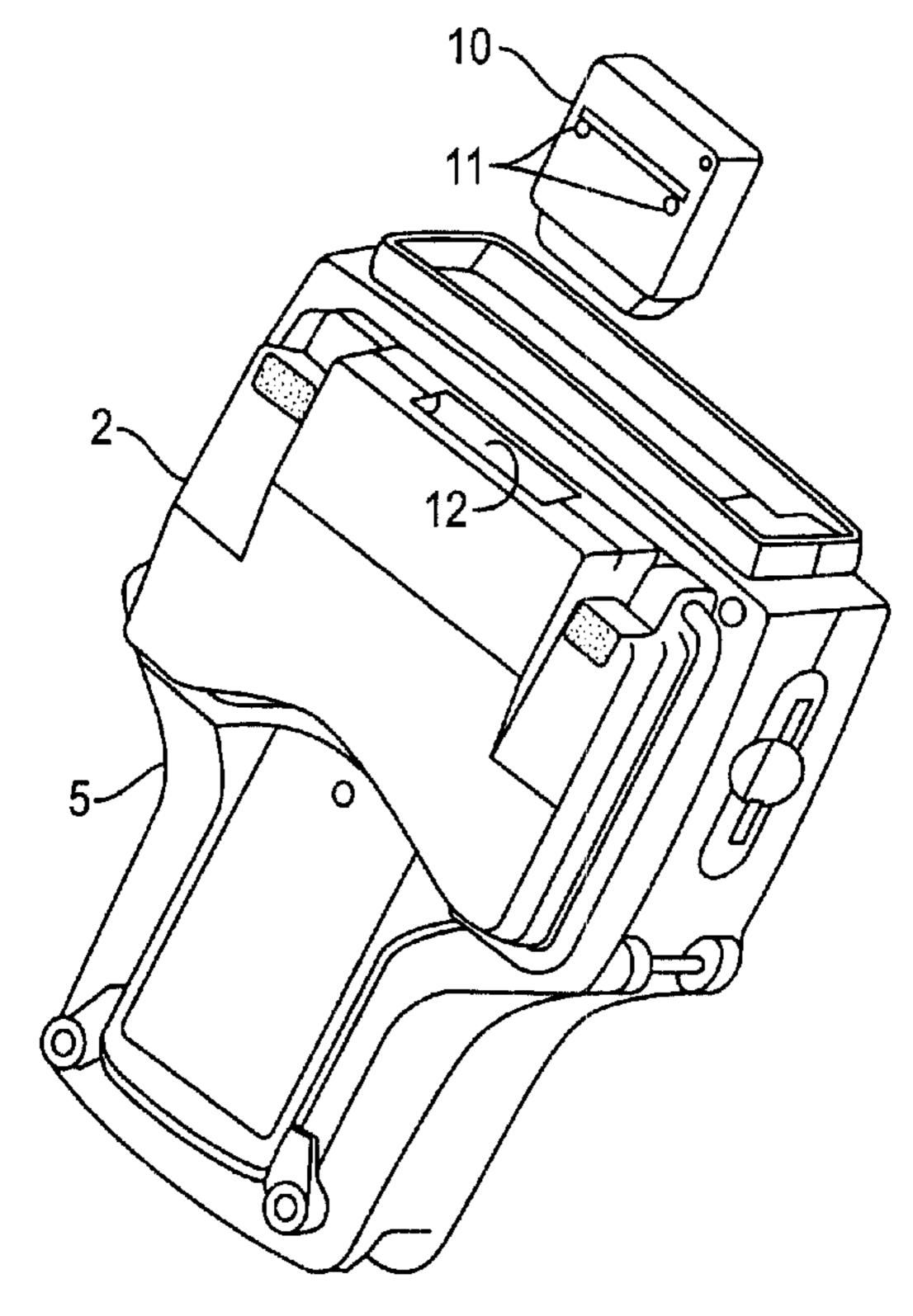

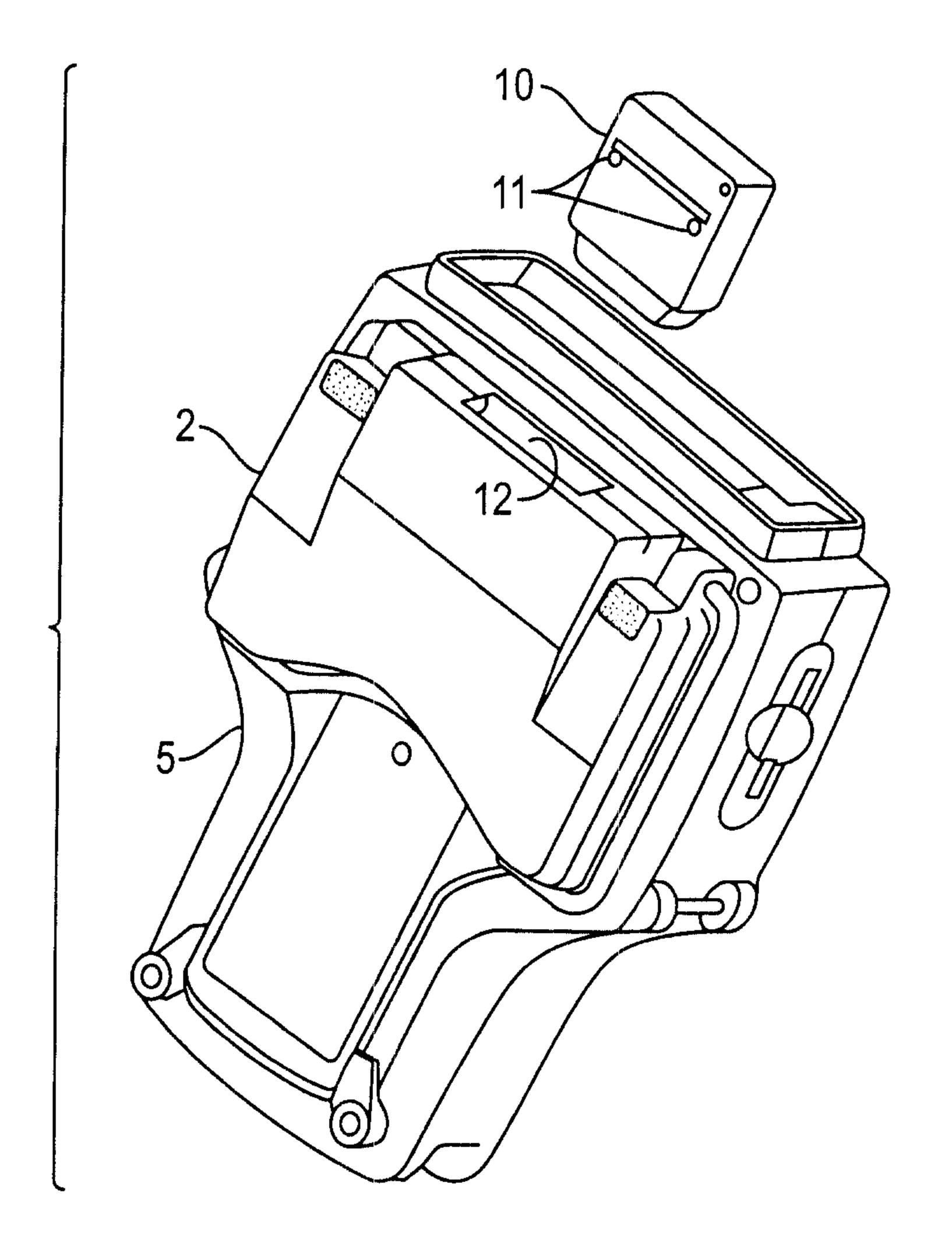

- FIG. 1 illustrates an exemplary portable electronic device and plug-in module in accordance with the present invention.

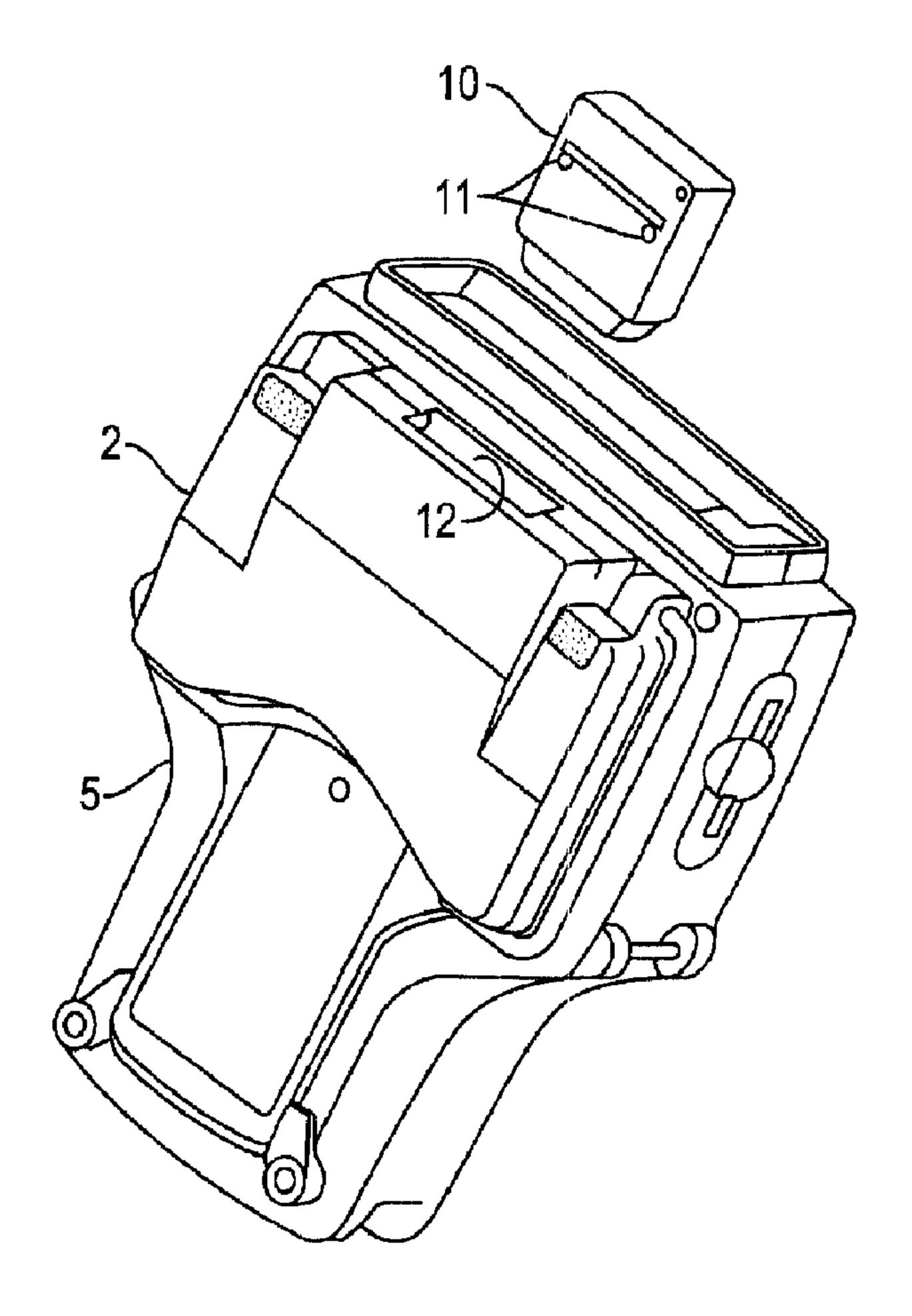

- FIG. 2 illustrates the portable electronic device in FIG. 1 with an alternate embodiment of the plug-in module.

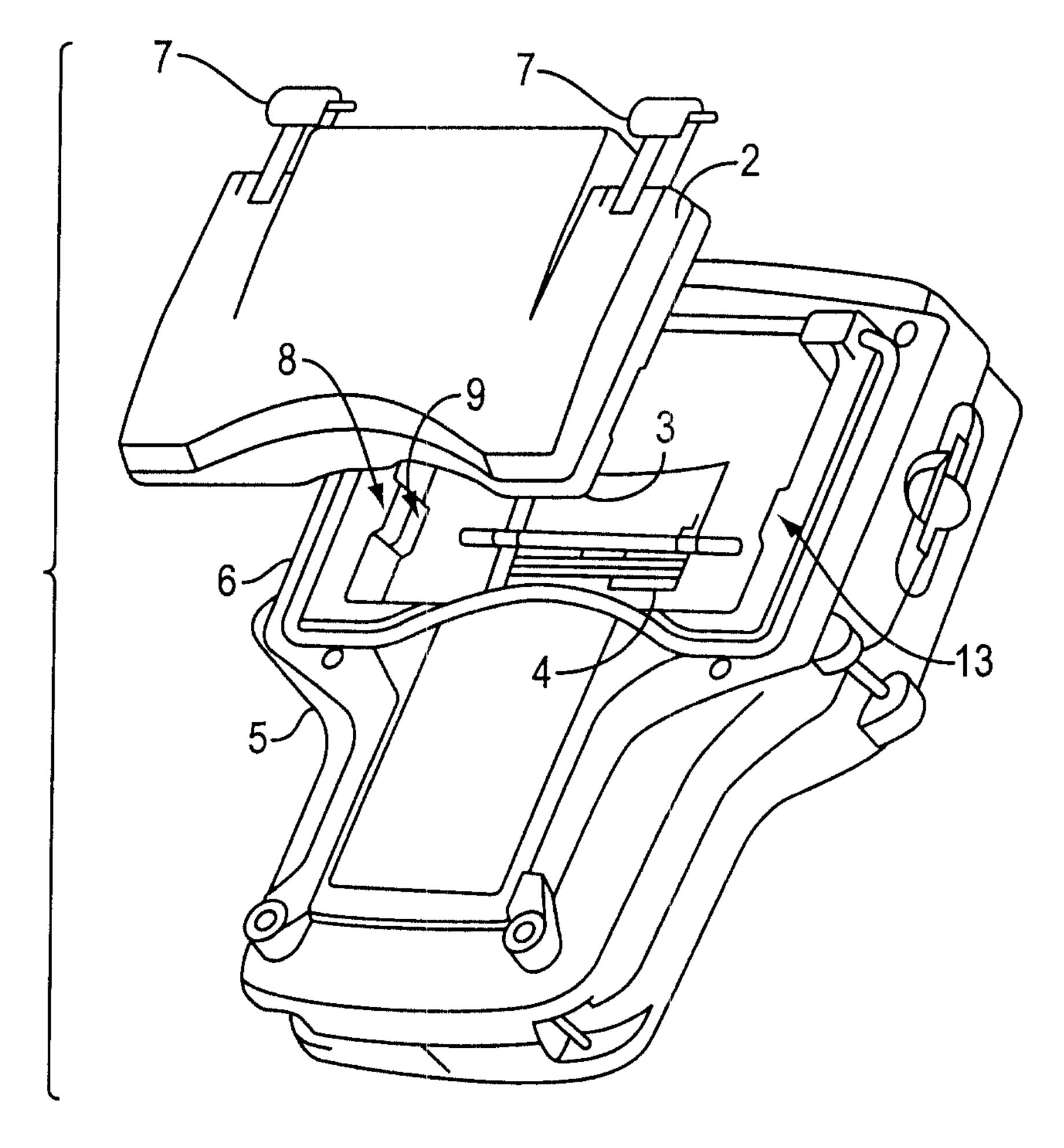

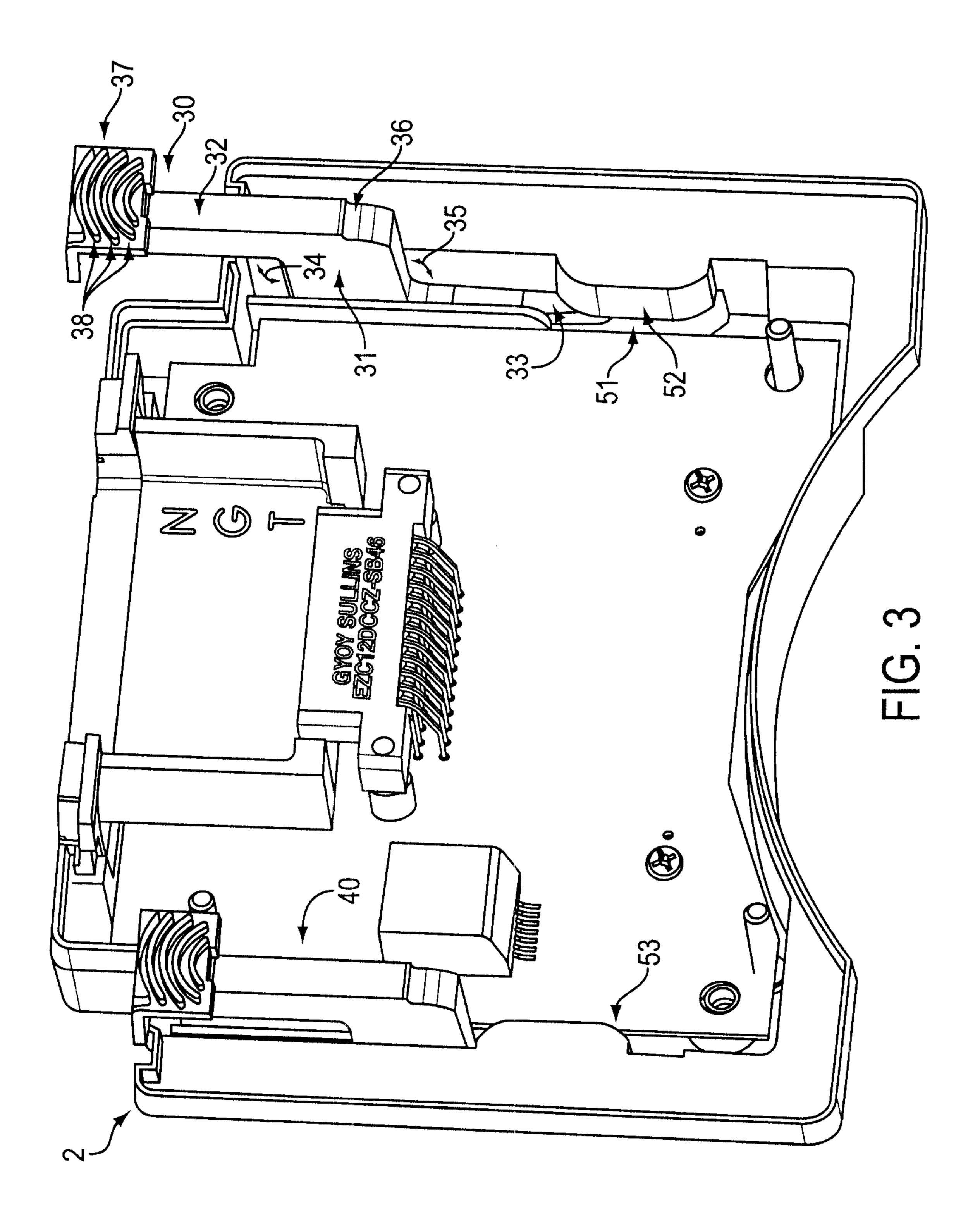

- FIG. 3 is a cut-away perspective view illustrating a preferred embodiment of the latching of the plug-in module to an electronic device.

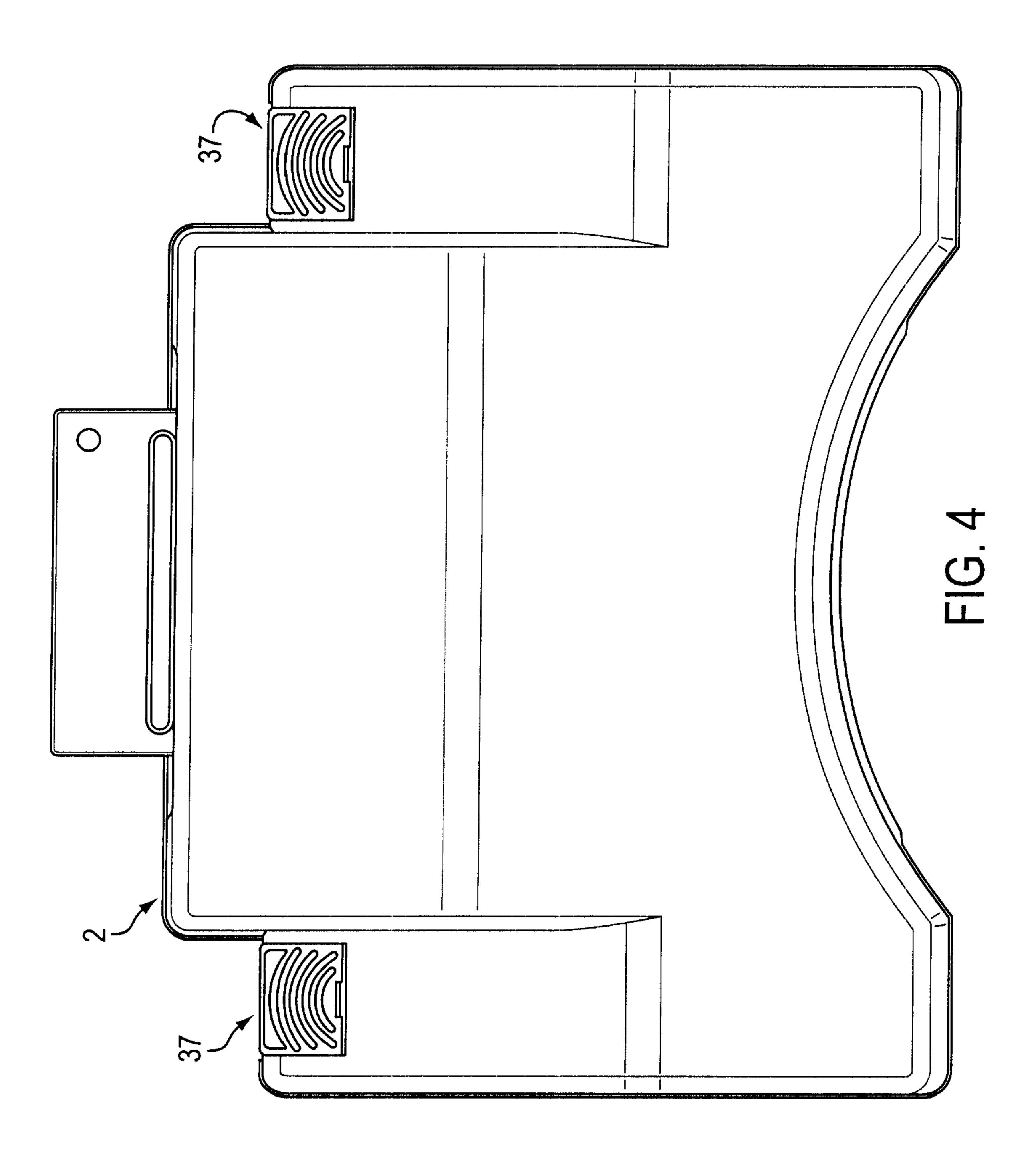

- FIG. 4 is a planar view of a preferred embodiment of the present inventive module.

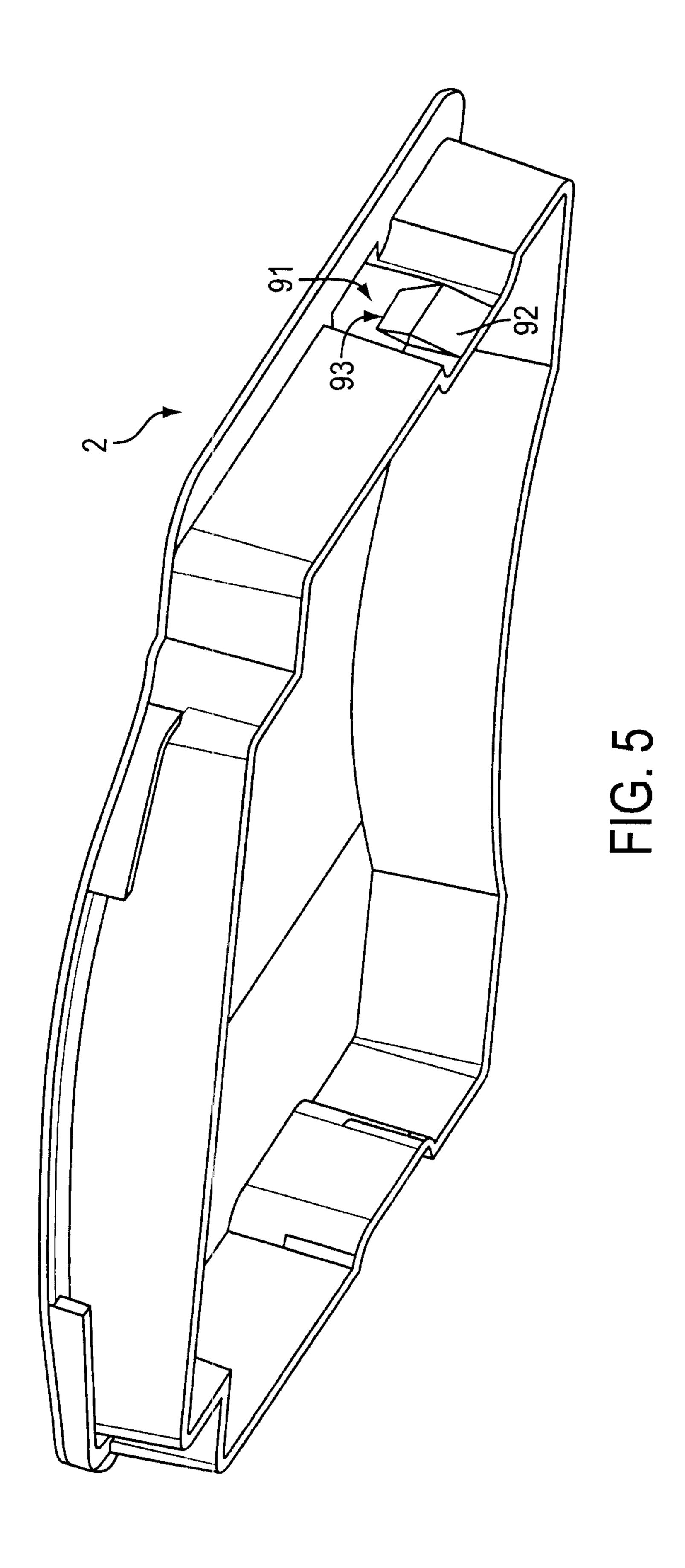

- FIG. 5 is a perspective view of an alternate embodiment of the present inventive module illustrating an alternate latch.

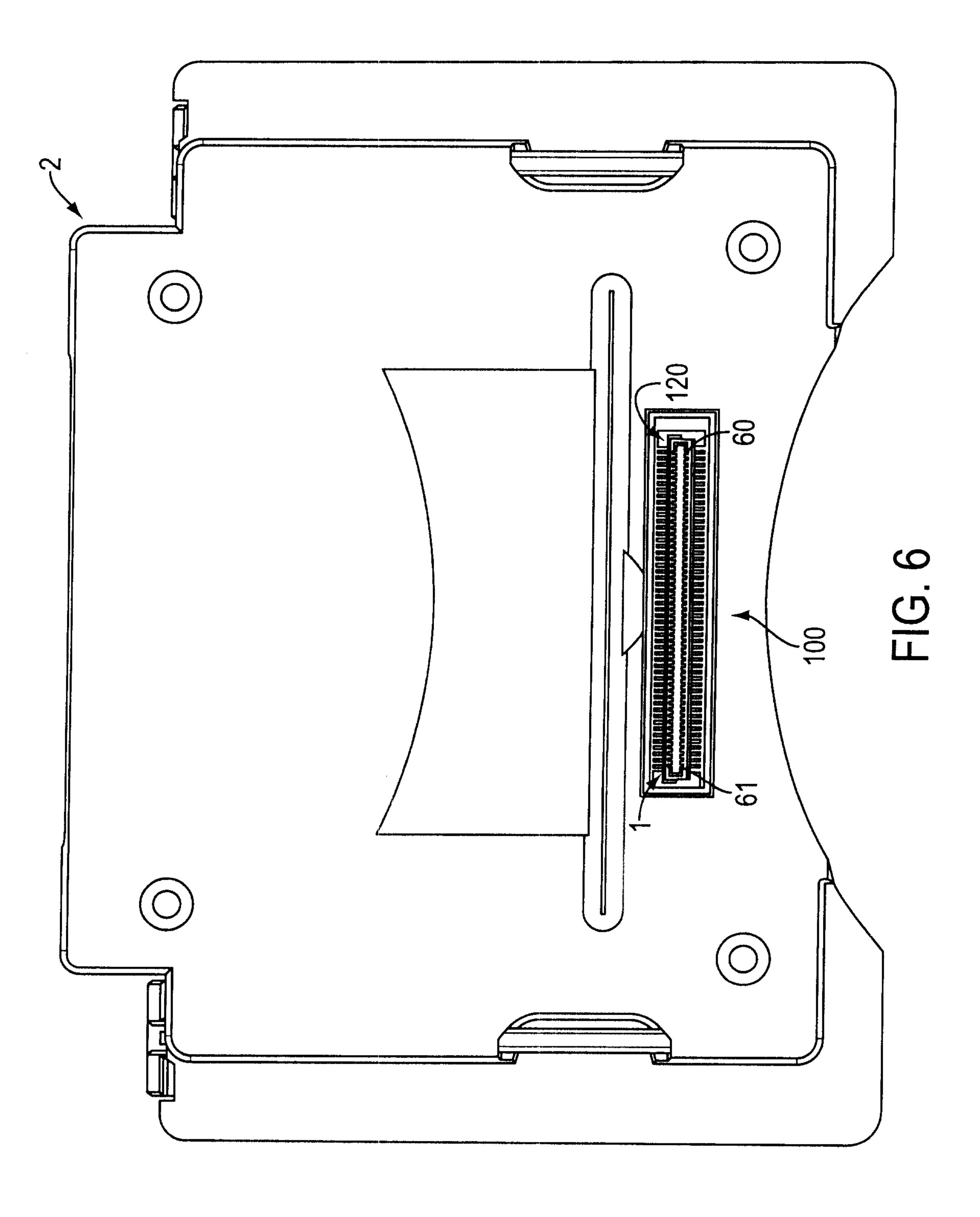

- FIG. 6 is a planar view of a preferred embodiment of the present inventive module, illustrating a preferred electric connector.

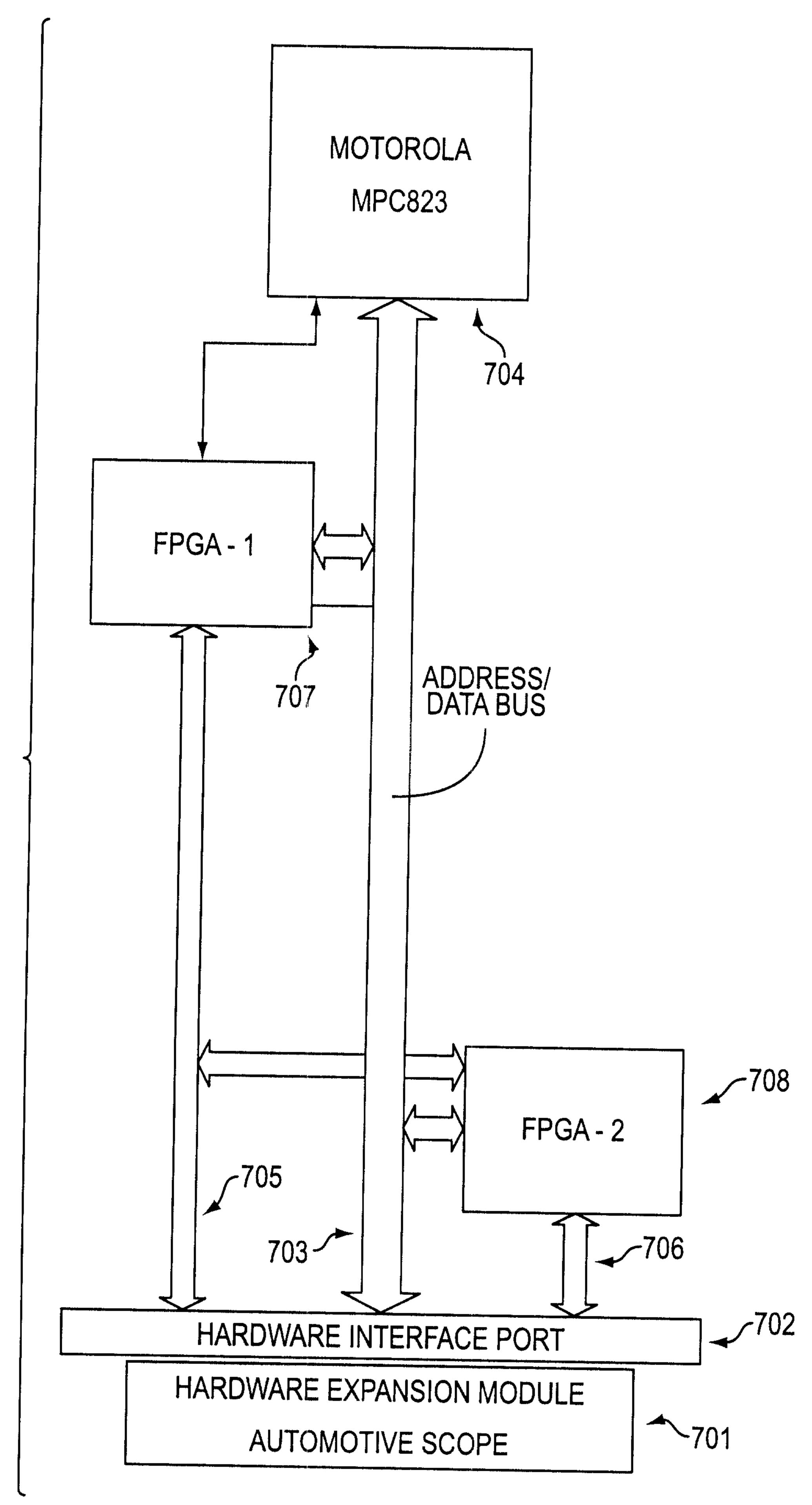

FIG. 7 is a block diagram illustrating the exemplary hardware of an electronic device with which the present inventive module may interface.

# DETAILED DESCRIPTION OF PREFERRED EMBODIMENTS OF THE INVENTION

The present invention provides an improved plug-in module for a portable electronic device, such as a portable computer, pocket PC, personal digital assistant, analog or digital analyzer, electronic game, or other electronic device. The module may include a computer processor or memory storing program instructions for adding functionality to the electronic apparatus, or the module may include hardware to accept a computer memory containing computer program instructions and deliver such instructions to the electronic device or to add processing capability to the device.

10

15

20

25

FIG. 1 illustrates an exemplary embodiment of the present inventive plug-in module for a portable electronic device. Referring to FIG. 1, a portable electronic device 5 includes a module port 6 that may accept a plug-in module 2. The electronic device illustrated in FIG. 1 is a portable engine analyzer, such as that which may be used to measure and analyze various aspects of the operation of a vehicle. However, the electronic device may in fact be any type of analyzer or other type of portable electronic or computing device such as a pocket PC or a personal digital assistant, a remote control, an electronic game, or any other portable electronic device. The electronic apparatus includes a hardware interface port 4 such as a 120-pin or 120-receptacle connector to provide an interface between the plug-in module and the electronic device. The plug-in module 2 mates with the module port 6 of the electronic device. The module port 6 includes one or more extensions such as 8 and 13 that form grooves or notches such as 9 within the port. The module includes a means to secure the module 2 to the device 5 such as one or more latches 7 that secure the module 2 to the electronic device 5 during normal operation.

The electronic device illustrated in FIG. 1 is a vehicle engine analyzer. Such an analyzer may serve to collect and analyze multiple aspects of an engine or vehicle, including aspects of the vehicle operations such as emissions components, system pressure, fluid pressure, system temperature, and other aspects or conditions. However, if the analyzer cannot provide all of the above functions, or if it is desirable to add a different type of functionality to the analyzer such as the ability to measure amps, vibration, or other aspects, the plug-in module may include a computer program memory containing computer program instructions that instruct the electronic apparatus to perform such functions. The module may also provide processing hardware that can be used by the electronic device when performing such functions. Such memory and/or processing hardware may be included in the module itself, or the module may simply contain communications hardware that provides an interface between the hardware interface port of the portable electronic device and an external memory or processor.

10

15

20

25

FIG. 2 illustrates an exemplary embodiment of an arrangement where the module serves as an interface between a separate memory or processing cartridge and the electronic device. Referring to FIG. 2, plug-in module 2 is connected to portable electronic device 5. The module 2 includes a port 12 that accepts an external cartridge 10. Cartridge 10 includes a computer processor and/or computer memory that adds functionality to the electronic device 5.

FIG. 3 illustrates an exemplary latch and its use to secure the plug-in module to an electronic device. Referring to FIG. 3, one end of a first member 31 is connected to an end of a second member 32, and the other end of the first member 31 is connected to an end of a third member 33 to form the latch 30. The members are connected such that the angles 34 and 35 made by the connection of the members are between 60° and 130°. Preferably, first member 31 is substantially perpendicular to the second member 32 and third member 33. Also preferably, the second member 32 and third member 33 are substantially parallel to each other. The latch 30 may include a notch 36 positioned to mate with a raised surface or rib located within the housing of the plug-in module. The third member 33 is sized to fit within a groove 51 located on the

plug-in module. Latch 30 optionally includes a finger rest 37 sized to receive a human finger or thumb to facilitate insertion of the latch 30 into the plug-in module. Preferably and optionally, the finger rest 37 includes a slip resistant portion such as one or more ribs 38 that reduce the likelihood that a finger will slip on the finger rest 37 when engaging the latch 30.

FIG. 3 is a cut-away illustration, illustrating two latches 30 and 40 and a portion of the module 2 so that the position of the latches within the module and in reference to the electronic device may be understood. Referring again to FIG. 3, at least one latch such as 30 and/or 40 is inserted into a plug-in module 2 to secure the module 2 to a portable electronic device such as that identified as 5 in FIG. 1. Referring to FIG. 3, the module includes at least one receptacle or groove 51 formed by a cap such as 52 or 53. The groove 51 is sized and positioned to receive the third member 33 of a latch 30 when the latch 30 is inserted into the plug in module. Referring to FIGs. 1 and 3, when the module 2 is attached to the device 5 the groove or grooves 51 in the module 2 receive the latch 30, and the third member 33 of the latch is directed to the notch or notches 9 of the device 5 to secure the module 2 to the device 5. FIG. 3 illustrates latch 30 before it is fully inserted into the module and groove 51, and latch 40 after it is inserted into the groove formed by cap 53.

10

15

20

25

FIG. 4 provides a planar illustration of the present inventive module when two latches are inserted into the module. In the embodiment illustrated in FIG. 4, when the latch is completely inserted into the module 2 and engaged with the electronic device, the finger rest 37 portion of the latch is the only portion that is externally visible, while other portions of the latch are hidden or substantially hidden within the module 2.

FIG. 5 illustrates an alternate embodiment of a means to latch the housing to the electronic apparatus. Referring to FIG. 5, the housing to includes a locking finger 92 positioned at a point to mate with the notch (as illustrated by 9 of FIG. 1) of the portable electronic device when the housing is placed into the housing port of the electronic device. In this embodiment, the housing includes a space 91 to provide flexibility of the finger 92 so that the finger 92 may

be squeezed and locked into the notch or receptacle of the electronic device. The finger 92 is preferably angled to come to a point 93 such that the housing may be removed from the electronic device with moderate force.

5

10

15

20

25

The plug in module includes a memory or computer processor that adds functionality to the portable electronic device, or a means to connect such a memory or processor to the device. This functionality is delivered to the device through an electrical connector. An exemplary electrical connector is illustrated in FIG. 6. Referring to FIG. 6, electrical connector 100 is positioned within the module 2 and mates with the hardware interface port of the portable electronic device when the module 2 is attached to the electronic device. The electrical connector 100 includes up to 120 receptacles positioned to mate with the pins of the hardware interface port. The location and functionality of the receptacles of connector 100 are positioned to correspond to the functions of pins of the hardware interface port. In an alternate embodiment, the connector 100 includes pins and the hardware interface port of the electronic device includes receptacles.

FIG. 6 illustrates the numbering system for each receptacle. The interface connector has between 1 and 120 receptacles sized and positioned to receive and correspond to one or more pins of a hardware interface port on the portable electronic device. The receptacles on the connector form two rows in parallel such that each receptacle is positioned to be numbered corresponding to its position in one of the rows. One of the two rows includes receptacle positions 1 through 60, and the other of the two rows includes receptacle positions 61 through 120. Receptacle positions 1 and 61 are located at corresponding ends of each row, and receptacle positions 60 and 120 are located at the other corresponding ends of each row. Receptacle positions 1 and 120 are located at opposite ends of each row, and receptacle positions 60 and 61 are also located at opposite ends of each row. It is not necessary that the connector 100 contain all 120 receptacles. Rather, at least one receptacle must have corresponding functionality as follows:

In accordance with one embodiment of the present apparatus, at least one of the receptacles on the connector corresponds to at least one of positions 50, 56, 57, 58, 60, 61, 62, 64, 65, 66, 68, 69, 70, 72, 73, 74, 76, 77, 78, 80, 81, 82, 84, 85, 86, 88, 89, 105, 106, 108, and 110, and such receptacle or receptacles also correspond to a bus, such as a microprocessor interface bus, located within the portable electronic device.

In accordance with another embodiment of the present invention, at least one of the receptacles corresponds to at least one of positions 111, 112, 113, 114, 116, 118, and 120, and such receptacle or receptacles relate to power.

In accordance with another embodiment of the present invention, at least one of the receptacles corresponds to at least one of positions 3, 5, 7, 9, 11, 15, 19, 23, 27, 31, 35, 39, 47, 51, 55, 59, 63, 67, 71, 75, 79, 83, 87, 91, 95, 99, 103, 107, 109, 115, 117, and 119, and such receptacle or receptacles correspond to an electrical ground.

In accordance with another embodiment of the present invention at least one of the receptacles corresponds to at least one of positions 90, 92, 93, 96, 97, 100, 101, 102, 104, and 105, and such receptacle or receptacles correspond to a microprocessor discrete input/output.

In accordance with another embodiment of the present invention at least one of the receptacles corresponds to at least one of positions 2, 4, 6, 8, 10, 12-14, 16-18, 20-22, 24-26, 28-30, 32-34, 36-38 and 40, and such receptacle or receptacles correspond to a field programmable gate array (FPGA) discrete input/output.

The following chart illustrates the possible functionality of each pin and corresponding receptacle on the hardware interface port and electronic connector.

| Pin | Function               | Pin | Function              | 28.418                                    | Pin | Function | Pin | Function |

|-----|------------------------|-----|-----------------------|-------------------------------------------|-----|----------|-----|----------|

| 1   | NC                     | 31  | Ground                |                                           | 61  | D(4)     | 91  | Ground   |

| 2   | HIP 1<br>(FPGA<br>I/O) | 32  | NOT A15<br>(FPGA I/O) |                                           | 62  | D(5)     | 92  | PA(7)    |

| 3   | Ground                 | 33  | EN (FPGA<br>I/O)      |                                           | 63  | Ground   | 93  | PA(12)   |

| 4   | HIP 2                  | 34  | WR (FPGA              | - 1975 - WA<br>- 1975 - WA<br>- 1975 - WA | 64  | D(6)     | 94  | NC       |

10

15

20

|         |                 | (FPGA            |                                             |           | I/O)                    |                                                                    |                 |            |                                                           |                |              |

|---------|-----------------|------------------|---------------------------------------------|-----------|-------------------------|--------------------------------------------------------------------|-----------------|------------|-----------------------------------------------------------|----------------|--------------|

|         |                 | I/O)             |                                             |           |                         |                                                                    |                 |            |                                                           |                | 7            |

|         | 5               | Ground           |                                             | 35        | Ground                  |                                                                    | 65              | D(7)       |                                                           | 95             | Ground       |

|         | 6               | HIP 3            |                                             | 36        | NOT AS                  |                                                                    | 66              | D(8)       |                                                           | 96             | PC(8)        |

|         |                 | (FPGA            |                                             |           | (FPGA I/O)              |                                                                    |                 |            | 100 0000<br>100 0000<br>100 0000<br>100 0000<br>100 0000  |                |              |

|         |                 | I/O)             |                                             |           |                         |                                                                    | ~ "7            | Cround     |                                                           | 97             | PC(9)        |

|         | 7               | Ground           |                                             | 37        | NOT CS4                 |                                                                    | 67              | Ground     |                                                           | 97             |              |

|         |                 | TTTD             |                                             | 30        | (FPGA I/O)<br>NOT CSRAM |                                                                    | 68              | D(9)       | 2 - 1 - 2 - 2 - 2 - 2 - 2 - 2 - 2 - 2 -                   | 98             | NC           |

|         | 8               | HIP 4<br>(FPGA   |                                             | 38        | (FPGA I/O)              |                                                                    |                 |            |                                                           |                |              |

|         |                 | I/O)             |                                             |           |                         |                                                                    |                 |            |                                                           |                |              |

|         | 9               | Ground           |                                             | 39        | Ground                  | 8 8 8 8 8 8 8 8 8 8 8 8 8 8 8 8 8 8 8                              | 69              | D(10)      |                                                           | 99             | Ground       |

|         | 10              | IRQ6A            |                                             | 40        | CARIN FPGA              |                                                                    | 70              | D(11)      |                                                           | 100            | PB(18)       |

|         |                 | (FPGA            |                                             |           | I/O                     | A2 55 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1                          |                 |            |                                                           |                |              |

|         |                 | I/O)             |                                             |           |                         | 10 Atom                                                            | 71              | Ground     | 1.23                                                      | 101            | PB(30)       |

|         | 11              | Ground           |                                             | 41        | NC                      | N.X. STATE                                                         | $\frac{71}{72}$ | D(12)      |                                                           | 102            | PB(29)       |

|         | 12              | DO (FPGA         |                                             | 42        | NC                      |                                                                    | , 4             | \ /        |                                                           |                |              |

|         | 13              | D1 (FPGA         |                                             | 43        | Ground                  | 24 (26)<br>24 (27)<br>24 (27)                                      | 73              | D(13)      | 10 00 00 00 00 00 00 00 00 00 00 00 00 0                  | 103            | Ground       |

|         | 1 1             | I/O)             | 148                                         | 0         |                         | 18 20 20 1<br>18 20 20 20 20 20 20 20 20 20 20 20 20 20            |                 |            | 10 10 85<br>10 10 85<br>10 10 88<br>10 10 88              |                | 55 (00)      |

| <u></u> | 14              | D2 (FPGA         | J. A.                                       | 44        | NC                      |                                                                    | 74              | D(14)      | 10 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0                    | 104            | PB(28)       |

| )       |                 | I/O)             |                                             |           |                         |                                                                    | 75              | Ground     |                                                           | 105            | NOT          |

|         | 15              | Ground           |                                             | 45        | $\mathbf{T}\mathbf{D}0$ |                                                                    | /5              | Ground     | 10.00 mg                                                  | 1.00           | CSISI        |

|         | 1.              | D3 (FPGA         |                                             | 46        | TD1                     |                                                                    | 76              | D(15)      |                                                           | 106            | READ/NOT     |

|         | 16              | D3 (FPGA<br>I/O) |                                             |           |                         | (F) (F)                                                            |                 |            |                                                           |                | WRIGHT       |

|         | 17              | D4 (FPGA         | **************************************      | 47        | Ground                  |                                                                    | 77              | A(22)      |                                                           | 107            | Ground       |

|         |                 | I/O)             | 100000000000000000000000000000000000000     |           | > 7 /~                  |                                                                    | 78              | A(23)      |                                                           | 108            | NOT          |

|         | 18              | D5 (FPGA         |                                             | 48        | NC                      |                                                                    | 7.0             | A (23)     |                                                           |                | SRESET       |

| 1 0     | 10              | Ground           |                                             | 49        | TCK                     |                                                                    | 79              | Ground     | 100 100 100 100 100 100 100 100 100 100                   | 109            | Ground       |

| 10      | <u>19</u><br>20 | D6 (FPGA         |                                             | 50        |                         | COACH CALL<br>OFFICE PING<br>DELLE CALL<br>TOCK CALL               | 80              | A(24)      | 1 V 100,000<br>3 100,000<br>100,000<br>100,000<br>100,000 | 110            | NOT TA       |

|         | 2.0             | I/O)             |                                             |           |                         | 900 100 100 100 100 100 100 100 100 100                            |                 |            |                                                           | 4 1 1          | +3.3 V       |

|         | 21              | D7 (FPGA         |                                             | 51        | Ground                  |                                                                    | 81              | A(25)      |                                                           | 111            | DC +3.3 v    |

|         |                 | I/O)             |                                             |           | אלי איני איני           | 284 (26)<br>200 (20)<br>200 (20)<br>200 (20)<br>200 (20)           | 82              | A(26)      |                                                           | 112            | +3.3 V       |

|         | 22              | D8 (FPGA         |                                             | 52        | ENETRXD                 |                                                                    | 02              | 11 ( 2 0 ) |                                                           | <del></del>    | DC           |

|         | 23              | I/O)<br>Ground   |                                             | 53        | IC1                     | 700 5 7 7 7 7 7 7 7 7 7 7 7 7 7 7 7 7 7                            | 83              | Ground     |                                                           | 113            | +5 V DC      |

|         | $\frac{23}{24}$ | D9 (FPGA         |                                             | 54        | IC2                     | 100 km 100<br>100 km 100<br>100 km 100<br>100 km 100<br>100 km 100 | 84              | A(27)      | 2 1 1 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2                   | 114            | +5 V DC      |

| 15      | 2               | 1/0)             |                                             |           |                         |                                                                    |                 | - (00)     |                                                           |                | Czecuzad     |

|         | 25              | D10 (FPGA        |                                             | 55        | Ground                  |                                                                    | 85              | A(28)      |                                                           | 115            | Ground       |

|         |                 | I/O)             | 2 6 2 7 8 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 |           | T) ( () \               | 451.51                                                             | 86              | A(29)      | 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1                     | 116            | BATTERY      |

|         | 26              | D11 (FPGA        |                                             | 56        | D(0)                    | 70 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0                             |                 |            | 7, 77 (9) (3<br>1, 1, 2) (1,<br>2, 1)<br>1, 1, 2)         |                | B+           |

|         | 27              | I/O)<br>Ground   |                                             | 57        | D(1)                    |                                                                    | 87              | Ground     |                                                           | 117            | Ground       |

|         | 28              | A12 (FPGA        |                                             | 58        | D(2)                    |                                                                    | 88              | A(30)      |                                                           | 118            | BATTERY      |

|         | ب بے            | I/O)             |                                             |           |                         | 200 20 B                                                           |                 | * / ^ 1 \  | 1, 10, 1<br>1, 1, 1, 1, 1, 1, 1, 1, 1, 1, 1, 1, 1, 1      | 110            | B+<br>Ground |

| 20      | 29              | A13 (FPGA        |                                             | 59        | Ground                  |                                                                    | 89              | A(31)      | 100 K                                                     | 119            | GIOUIIU      |

| 40      |                 | I/O)             | **************************************      |           | T) / 2 \                | 5 4 5 4<br>2 4 4 5<br>1 5 1 5 5                                    | 90              | PA(6)      | 11 10 10 10 10 10 10 10 10 10 10 10 10 1                  | 120            | EXT +12V     |

|         | 30              | A14 (FPGA        |                                             | 60        | D(3)                    |                                                                    |                 | 111(0)     |                                                           | <del></del> •- | DC           |

| į       |                 | 1/0)             |                                             | <u></u> . |                         | 4 (* 18 <u> </u>                                                   | <u>1</u>        | <u>,</u>   | <u>, , ,</u>                                              |                |              |

FIG. 7 illustrates the internal components of an exemplary electronic device. Such components may interface with the module through the hardware interface port. Referring to FIG 7, a hardware expansion module 701 such as that in an automotive scope interfaces with a hardware interface port 702. Certain pins or receptacles on the hardware interface port 702 provide communication to and from the controller 704 via interface bus 703 within the portable electronic device. The hardware interface port 702 may also serve to communicate discrete input/output signals via interface bus 703 to the expansion module, and the expansion module may share input/output signals 705 and/or 706 with one or more FPGA components within the electronic device such as 707 and/or 708.

In order to provide a shock-resistant plug-in module, it may be desirable to incorporate an elastomeric member to absorb or reduce shock when the unit is dropped or otherwise subjected to an impact. At least one such member is described in U.S. Patent No. 6,454,250 B1, entitled "Shock Absorbing Apparatus", which is hereby incorporated herein by reference.

The many features and advantages of the invention are apparent from the detailed specification, and thus, it is intended by the appended claims to cover all such features and advantages of the invention which fall within the true spirits and scope of the invention. Further, since numerous modifications and variations will readily occur to those skilled in the art, it is not desired to limit the invention to the exact construction and operation illustrated and described, and accordingly, all suitable modifications and equivalents may be resorted to, falling within the scope of the invention.

10

E CONTROL OF THE CONT

#### WHAT IS CLAIMED IS:

10

20

1. An apparatus for adding functionality to a portable electronic device, comprising:

a housing having an interior portion, said housing sized to be received by a housing port of a portable electronic device, said housing port disposed within an interior portion of the portable electronic device; and

a hardware interface connector disposed within the interior portion of the housing and in connection with a hardware interface port disposed within the housing port of the portable electronic device, wherein at least a portion of the housing is disposed within the interior portion of the portable electronic device when the hardware interface connector is in connection with the hardware interface port,

the hardware interface connector having between 1 and 120 receptacles, the hardware interface port having 120 pins, said receptacles configured to correspond to a pin in the hardware interface port, said receptacles further forming two rows in parallel such that each receptacle is positioned to be numbered corresponding to its position in one of the rows, wherein one of the two rows includes receptacle positions 1 through 60, the other of the two rows includes receptacle positions 61 through 120, receptacle positions 1 and 61 being located at corresponding ends of each row, receptacle positions 60 and 120 being located at opposite ends of each row, and receptacle positions 60 and 61 being located at opposite ends of each row; and

securing means for securing said portable electronic device to said housing.

2. The apparatus of claim 1, wherein at least one of the receptacles corresponding to at least one of positions 50, 56, 57, 58, 60, 61, 62, 64, 65, 66, 68, 69, 70, 72, 73, 74, 76, 77, 80, 81, 82, 84, 85, 86, 88, 89, 105, 106, 108, and 110 corresponds to a bus located within the portable electronic device.

- 3. The apparatus of claim 1, wherein at least one of the receptacles corresponding to at least one of positions 111, 112, 113, 114, 116, 118, and 120 corresponds to power.

- 4. The apparatus of claim 1, wherein at least one of the receptacles corresponding to at least one of positions 3, 5, 7, 9, 11, 15, 19, 23, 27, 31, 35, 39, 47, 51, 55, 59, 63, 67, 71, 75, 79, 83, 87, 91, 95, 99, 103, 107, 109, 115, 117 and 119 corresponds to an electrical ground.

- 5. The apparatus of claim 1, wherein at least one of the receptacles corresponding to at least one of positions 90, 92, 93, 96, 97, 100, 101, 102, 104, and 105 corresponds to discrete input to or output from a microprocessor within the portable electronic device.

10

20

- 6. The apparatus of claim 1, wherein at least one of the receptacles corresponding to at least one of positions 2, 4, 6, 8, 10, 12-14, 16-18, 20-22, 24-26, 28-30, 32-34, 36-38 and 40, corresponds to discrete input to or output from a field programmable gate array within the portable electronic device.

- 7. A method of adding functionality to a portable electronic device, comprising the steps of:

sizing a housing to be accepted by a housing port of a portable electronic device, the housing having an interior portion;

providing a hardware interface connector disposed within the interior portion of the housing, said hardware interface connector having between 1 and 120 receptacles, wherein said receptacles are arranged in two parallel rows such that each receptacle is positioned to be numbered corresponding to its position in one of the rows, wherein one of the two rows includes receptacle positions 1 through 60, the other of the two rows includes receptacle positions 61 and 120, receptacle positions 1 and 61 being located at corresponding ends or each row, receptacle positions 60

and 120 being located at corresponding ends of each row, receptacle positions 1 and 120 being located at opposite ends of each row, and receptacle positions 60 and 61 being located at opposite ends of each row;

providing a hardware interface port disposed within the housing port, the hardware interface port having 120 pins;

connecting the hardware interface port to the hardware interface connector within the interior portion of the housing;

configuring said receptacles to correspond to a pin in the hardware interface port; and securing the portable electronic device to said housing.

10 8. An apparatus for adding functionality to a portable electronic device, comprising:

a housing having an interior portion, said housing sized to be received by a housing port of a portable electronic device, said housing port disposed within an interior portion of the portable electronic device;

a hardware interface connector disposed within the interior portion of the housing and connected to a hardware interface port disposed within the housing port of the portable electronic device, the hardware interface connector having a plurality of receptacles, the hardware interface port having a plurality of pins wherein said receptacles are configured to correspond to a pin in the hardware interface port, wherein at least a portion of the housing is disposed within the interior portion of the portable electronic device when the hardware interface connector is in connection with the hardware interface port; and

20

securing means for securing said portable electronic device to said housing;

wherein the hardware interface connector has between 1 and 120 receptacles and the hardware interface port has 120 pins,

wherein said receptacles are arranged in two parallel rows such that each receptacle is positioned to be numbered corresponding to its position in one of the rows, wherein one of the two rows includes receptacle positions 1 through 60, the

other of the two rows includes receptacle positions 61 and 120, receptacle positions 1 and 61 being located at corresponding ends of each row, receptacle positions 60 and 120 being located at corresponding ends of each row, receptacle positions 1 and 120 being located at opposite ends of each row, and receptacle positions 60 and 61 being located at opposite ends of each row.

The contraction of the contracti

FIG. 1

FIG. 2

FIG. 7