# (19) 대한민국특허청(KR)

# (12) 등록특허공보(B1)

(51) 국제특허분류(Int. Cl.) **G06F 12/02** (2018.01)

(52) CPC특허분류

GO6F 12/0292 (2013.01)

(21) 출원번호 **10-2017-0174083**

(22) 출원일자 **2017년12월18일** 심사청구일자 **2020년11월05일**

(65) 공개번호 10-2019-0072922

(43) 공개일자 2019년06월26일

(56) 선행기술조사문헌 US20100199024 A1 (뒷면에 계속)

전체 청구항 수 : 총 17 항

(45) 공고일자 2023년08월14일

(11) 등록번호 10-2566635

(24) 등록일자 2023년08월09일

(73) 특허권자

#### 삼성전자주식회사

경기도 수워시 영통구 삼성로 129 (매탄동)

(72) 발명자

#### 김정훈

경기도 용인시 기흥구 동백7로 56,1106동 203호 이영식

서울특별시 서초구 바우뫼로41길 31,1동 109호

노강호

서울특별시 관악구 인헌12길 46-1, 205동 203호

(74) 대리인 **박영우**

심사관: 박미정

#### (54) 발명의 명칭 비휘발성 메모리 시스템 및 그 동작 방법

#### (57) 요 약

비휘발성 메모리 장치 및 메모리 콘트롤러를 포함하는 비휘발성 메모리 시스템에서, 호스트 장치의 논리적 어드레스 및 상기 비휘발성 메모리 장치의 물리적 어드레스 사이의 맵핑 관계를 나타내는 맵핑 데이터를 저장하기 위한 맵핑 메모리를 복수의 맵핑 메모리 영역들로 분할한다. 상기 복수의 맵핑 메모리 영역들의 각각에 대하여 상기 맵핑 데이터가 저장되었는지를 나타내는 점유 정보를 제공한다. 상기 점유 정보에 기초하여 상기 복수의 맵핑 메모리 영역들 중 상기 맵핑 데이터가 저장되지 않은 맵핑 메모리 영역들에 유저 데이터를 저장한다. 맵핑 메모리의 일부를 캐시 메모리로 이용함으로써 점유 면적의 증가 없이 비휘발성 메모리 시스템의 성능을 향상시킬 수있다.

### 대 표 도 - 도1

(56) 선행기술조사문헌

US20170337212 A1\*

US20150324284 A1\*

US20140156964 A1\*

US20140006681 A1\*

US20150347026 A1\*

KR101663667 B1\*

US08880845 B2\*

\*는 심사관에 의하여 인용된 문헌

### 명세서

### 청구범위

#### 청구항 1

비휘발성 메모리 장치 및 상기 비휘발성 메모리 장치에 연결되는 메모리 콘트롤러를 포함하는 비휘발성 메모리 시스템의 동작 방법으로서.

호스트 장치의 논리적 어드레스 및 상기 비휘발성 메모리 장치의 물리적 어드레스 사이의 맵핑 관계를 나타내는 맵핑 데이터를 저장하고 상기 메모리 콘트롤러에 포함되는 맵핑 메모리를 복수의 맵핑 메모리 영역들로 분할하 는 단계;

상기 메모리 콘트롤러에 포함되는 버퍼 메모리를 복수의 버퍼 영역들로 분할하는 단계;

상기 복수의 버퍼 영역들에 유저 데이터를 저장하는 단계;

상기 복수의 맵핑 메모리 영역들의 각각에 대하여 상기 맵핑 데이터가 저장되었는지를 나타내는 점유 정보를 제 공하는 단계;

상기 점유 정보에 기초하여 상기 복수의 맵핑 메모리 영역들 중 상기 맵핑 데이터가 저장되지 않은 맵핑 메모리 영역들에 상기 유저 데이터를 저장하는 단계; 및

상기 유저 데이터가 저장된 데이터 맵핑 메모리 영역을 나타내는 캐싱 어드레스 및 상기 데이터 맵핑 메모리 영역에 저장된 상기 유저 데이터에 상응하는 상기 논리적 어드레스를 각각 포함하는 복수의 캐싱 엔트리들을 포함하는 캐싱 테이블을 제공하는 단계를 포함하는 비휘발성 메모리 시스템의 동작 방법.

#### 청구항 2

제1 항에 있어서,

상기 복수의 맵핑 메모리 영역들의 각각에 대한 점유 정보를 제공하는 단계는,

상기 복수의 맵핑 메모리 영역들의 각각에 상응하고, 각각의 맵핑 메모리 영역이 상기 맵핑 데이터가 저장된 점유 맵핑 메모리 영역인지 또는 상기 맵핑 데이터가 저장되지 않은 비점유 맵핑 메모리 영역인지를 나타내는 값을 각각 저장하는 복수의 상태 표시 영역들을 포함하는 점유 상태 매니저를 제공하는 단계를 포함하는 것을 특징으로 하는 비휘발성 메모리 시스템의 동작 방법.

#### 청구항 3

제2 항에 있어서.

상기 복수의 상태 표시 영역들의 각각은,

1개의 비트 또는 2개의 비트들을 저장하는 것을 특징으로 하는 비휘발성 메모리 시스템의 동작 방법.

#### 청구항 4

제2 항에 있어서,

상기 복수의 상태 표시 영역들의 각각은,

상기 상응하는 맵핑 메모리 영역이 상기 점유 맵핑 메모리 영역임을 나타내는 제1 값 및 상기 상응하는 맵핑 메모리 영역이 상기 비점유 맵핑 메모리 영역임을 나타내는 제2 값 중 하나를 저장하는 것을 특징으로 하는 비휘발성 메모리 시스템의 동작 방법.

### 청구항 5

제4 항에 있어서,

상기 복수의 맵핑 메모리 영역들의 각각에 대한 점유 정보를 제공하는 단계는,

상기 비점유 맵핑 메모리 영역에 상기 맵핑 데이터가 저장된 경우 상기 상응하는 상태 표시 영역의 값을 상기 제2 값에서 상기 제1 값으로 변경하는 단계; 및

상기 점유 맵핑 메모리 영역에 저장된 상기 맵핑 데이터가 폐기된 경우 상기 상응하는 상태 표시 영역의 값을 상기 제1 값에서 상기 제2 값으로 변경하는 단계를 더 포함하는 것을 특징으로 하는 비휘발성 메모리 시스템의 동작 방법.

#### 청구항 6

제2 항에 있어서,

상기 복수의 상태 표시 영역들의 각각은,

상기 상응하는 맵핑 메모리 영역이 상기 점유 맵핑 메모리 영역임을 나타내는 제1 값, 상기 상응하는 맵핑 메모리 영역이 상기 유저 데이터가 저장된 데이터 맵핑 메모리 영역임을 나타내는 제2 값 및 상기 상응하는 맵핑 메모리 영역이 상기 맵핑 데이터 및 상기 유저 데이터가 모두 저장되지 않은 엠프티 맵핑 메모리 영역임을 나타내는 제3 값 중 하나를 저장하는 것을 특징으로 하는 비휘발성 메모리 시스템의 동작 방법.

### 청구항 7

제6 항에 있어서,

상기 복수의 맵핑 메모리 영역들의 각각에 대한 점유 정보를 제공하는 단계는,

상기 엠프티 맵핑 메모리 영역 또는 상기 데이터 맵핑 메모리 영역 에 상기 맵핑 데이터가 저장된 경우 상기 상 응하는 상태 표시 영역의 값을 상기 제3 값 또는 상기 제2 값에서 상기 제1 값으로 변경하는 단계;

상기 점유 맵핑 메모리 영역에 저장된 상기 맵핑 데이터가 폐기된 경우 상기 상응하는 상태 표시 영역의 값을 상기 제1 값에서 상기 제3 값으로 변경하는 단계; 및

상기 데이터 맵핑 메모리 영역에 저장된 상기 유저 데이터가 폐기된 경우 상기 상응하는 상태 표시 영역의 값을 상기 제2 값에서 상기 제3 값으로 변경하는 단계를 더 포함하는 것을 특징으로 하는 비휘발성 메모리 시스템의 동작 방법.

#### 청구항 8

삭제

### 청구항 9

삭제

#### 청구항 10

비휘발성 메모리 장치 및 상기 비휘발성 메모리 장치에 연결되는 메모리 콘트롤러를 포함하는 비휘발성 메모리 시스템의 동작 방법으로서,

호스트 장치의 논리적 어드레스 및 상기 비휘발성 메모리 장치의 물리적 어드레스 사이의 맵핑 관계를 나타내는 맵핑 데이터를 저장하고 상기 메모리 콘트롤러에 포함되는 맵핑 메모리를 복수의 맵핑 메모리 영역들로 분할하 는 단계;

상기 맵핑 메모리와 물리적으로 분리되고 상기 메모리 콘트롤러에 포함되는 버퍼 메모리를 복수의 버퍼 영역들로 분할하는 단계;

상기 복수의 버퍼 영역들에 유저 데이터를 저장하는 단계;

상기 복수의 맵핑 메모리 영역들의 각각에 대하여 상기 맵핑 데이터가 저장되었는지를 나타내는 점유 정보를 제공하는 단계;

상기 점유 정보에 기초하여 상기 복수의 맵핑 메모리 영역들 중 상기 맵핑 데이터가 저장되지 않은 맵핑 메모리 영역들에 상기 유저 데이터를 저장하는 단계; 상기 버퍼 메모리에 저장된 상기 유저 데이터의 캐싱 정보를 포함하는 메인 캐싱 테이블을 제공하는 단계; 및 상기 맵핑 메모리에 저장된 상기 유저 데이터의 캐싱 정보를 포함하는 서브 캐싱 테이블을 제공하는 단계를 포함하는 것을 특징으로 하는 비휘발성 메모리 시스템의 동작 방법.

#### 청구항 11

제10 항에 있어서

상기 메인 캐싱 테이블은,

상기 버퍼 영역에 저장된 상기 유저 데이터에 상응하는 상기 논리적 어드레스를 각각 포함하는 복수의 메인 캐 싱 엔트리들을 포함하고,

상기 서브 캐싱 테이블은,

상기 유저 데이터가 저장된 데이터 맵핑 메모리 영역의 어드레스 및 상기 데이터 맵핑 메모리 영역에 저장된 상기 유저 데이터에 상응하는 상기 논리적 어드레스를 각각 포함하는 복수의 서브 캐싱 엔트리들을 포함하는 것을 특징으로 하는 비휘발성 메모리 시스템의 동작 방법.

#### 청구항 12

제10 항에 있어서

상기 메인 캐싱 테이블에 기초하여 상기 버퍼 메모리를 L1 캐시로 사용하고 상기 서브 캐싱 테이블에 기초하여 상기 맵핑 메모리를 L2 캐시로 사용하는 것을 특징으로 하는 비휘발성 메모리 시스템의 동작 방법.

#### 청구항 13

제1 항에 있어서,

데이터 맵핑 메모리 영역 또는 상기 버퍼 영역에 저장된 상기 유저 데이터에 상응하는 상기 논리적 어드레스를 각각 포함하는 복수의 통합 캐싱 엔트리들을 포함하는 통합 캐싱 테이블을 제공하는 단계를 더 포함하는 것을 특징으로 하는 비휘발성 메모리 시스템의 동작 방법.

### 청구항 14

제2 항에 있어서,

상기 호스트 장치로부터 액세스 명령 및 논리적 액세스 어드레스를 수신하는 단계;

상기 논리적 액세스 어드레스에 상응하는 맵핑 데이터가 상기 점유 맵핑 메모리 영역에 저장되어 있지 않은 경우, 상기 비휘발성 메모리 장치로부터 상기 논리적 액세스 어드레스에 상응하는 맵핑 데이터를 독출하는 단계; 및

상기 독출된 맵핑 데이터를 상기 비점유 맵핑 메모리 영역에 저장하는 경우, 상기 점유 상태 매니저의 상기 상응하는 상태 표시 영역의 값을 갱신하는 단계를 더 포함하는 것을 특징으로 하는 비휘발성 메모리 시스템의 동작 방법.

## 청구항 15

제2 항에 있어서,

상기 호스트 장치로부터 독출 명령 및 논리적 독출 어드레스를 수신하는 단계;

상기 논리적 독출 어드레스에 상응하는 유저 데이터가 상기 맵핑 메모리에 저장되어 있지 않은 경우, 상기 비휘 발성 메모리 장치로부터 상기 논리적 독출 어드레스에 상응하는 유저 데이터를 독출하는 단계; 및

상기 독출된 유저 데이터를 상기 비점유 맵핑 메모리 영역에 저장하는 경우, 상기 점유 상태 매니저의 상기 상 응하는 상태 표시 영역의 값을 갱신하는 단계를 더 포함하는 것을 특징으로 하는 비휘발성 메모리 시스템의 동 작 방법.

### 청구항 16

제2 항에 있어서,

상기 호스트 장치로부터 기입 명령, 논리적 기입 어드레스 및 기입 데이터를 수신하는 단계; 및

상기 기입 데이터를 상기 비점유 맵핑 메모리 영역에 저장하는 경우, 상기 점유 상태 매니저의 상기 상응하는 상태 표시 영역의 값을 갱신하는 단계를 더 포함하는 것을 특징으로 하는 비휘발성 메모리 시스템의 동작 방법.

#### 청구항 17

제1 항에 있어서,

상기 복수의 맵핑 메모리 영역들의 각각의 사이즈는 상기 비휘발성 메모리 장치 및 상기 메모리 콘트롤러 사이에서 전송되는 데이터 유닛의 사이즈와 동일한 것을 특징으로 하는 비휘발성 메모리 시스템의 동작 방법

#### 청구항 18

비휘발성 메모리 장치; 및

상기 비휘발성 메모리 장치에 연결되고, 맵핑 메모리, 버퍼 메모리, 점유 상태 매니저 및 제어부를 포함하는 메 모리 콘트롤러를 포함하고,

상기 맵핑 메모리는 호스트 장치의 논리적 어드레스 및 상기 비휘발성 메모리 장치의 물리적 어드레스 사이의 맵핑 관계를 나타내는 맵핑 데이터를 저장하고, 복수의 맵핑 메모리 영역들로 분할되고,

상기 버퍼 메모리는 유저 데이터를 저장하는 복수의 버퍼 영역들로 분할되고,

상기 점유 상태 매니저는 상기 복수의 맵핑 메모리 영역들의 각각에 대하여 상기 맵핑 데이터가 저장되었는지를 나타내는 점유 정보를 제공하고,

상기 제어부는, 상기 점유 상태 매니저의 상기 점유 정보에 기초하여 상기 복수의 맵핑 메모리 영역들 중 상기 맵핑 데이터가 저장되지 않은 맵핑 메모리 영역들에 유저 데이터를 저장하고, 상기 유저 데이터가 저장된 데이 터 맵핑 메모리 영역을 나타내는 캐싱 어드레스 및 상기 데이터 맵핑 메모리 영역에 저장된 상기 유저 데이터에 상응하는 상기 논리적 어드레스를 각각 포함하는 복수의 캐싱 엔트리들을 포함하는 캐싱 테이블을 제공하는 비 휘발성 메모리 시스템.

### 청구항 19

제18 항에 있어서,

상기 점유 상태 매니저는,

상기 복수의 맵핑 메모리 영역들의 각각에 상응하고, 각각의 맵핑 메모리 영역이 상기 맵핑 데이터가 저장된 점 유 맵핑 메모리 영역인지 또는 상기 맵핑 데이터가 저장되지 않은 비점유 맵핑 메모리 영역인지를 나타내는 값 을 각각 저장하는 복수의 상태 표시 영역들을 포함하는 것을 특징으로 하는 비휘발성 메모리 시스템.

#### 청구항 20

삭제

### 발명의 설명

### 기술분야

[0001] 본 발명은 반도체 집적 회로에 관한 것으로서, 더욱 상세하게는 비휘발성 메모리 시스템 및 상기 비휘발성 메모 리 시스템의 동작 방법에 관한 것이다.

### 배경기술

[0002] 데이터를 저장하기 위한 반도체 메모리 장치는 크게 휘발성(volatile) 메모리 장치와 비휘발성(non-volatile) 메모리 장치로 대별될 수 있다. 셀 커패시터의 충전 또는 방전에 의해 데이터가 저장되는 디램(DRAM: Dynamic Random Access Memory) 등의 휘발성 메모리 장치는 전원이 인가되는 동안에는 저장된 데이터가 유지되지만 전원이 차단되면 저장된 데이터가 손실된다. 한편, 비휘발성 메모리 장치는 전원이 차단되어도 데이터를 저장할 수

있다. 휘발성 메모리 장치는 주로 컴퓨터 등의 메인 메모리로 사용되고, 비휘발성 메모리 장치는 컴퓨터, 휴대용 통신기기 등 넓은 범위의 응용 기기에서 프로그램 및 데이터를 저장하는 대용량 메모리로 사용되고 있다. 비휘발성 메모리 장치의 메모리 용량이 증가할수록 상기 비휘발성 메모리 장치의 제어를 위한 회로의 면적 및 비용이 증가한다.

## 발명의 내용

### 해결하려는 과제

- [0003] 상기와 같은 문제점을 해결하기 위한 본 발명의 일 목적은, 비휘발성 메모리 장치를 제어하는 메모리 콘트롤러의 메모리 자원을 효율적으로 이용할 수 있는 비휘발성 메모리 시스템을 제공하는 것이다.

- [0004] 또한 본 발명의 일 목적은, 비휘발성 메모리 장치를 제어하는 메모리 콘트롤러의 메모리 자원을 효율적으로 이용할 수 있는 비휘발성 메모리 시스템의 동작 방법을 제공하는 것이다.

## 과제의 해결 수단

- [0005] 상기 일 목적을 달성하기 위해, 본 발명의 실시예들에 따른 비휘발성 메모리 시스템의 동작 방법에서, 호스트 장치의 논리적 어드레스 및 상기 비휘발성 메모리 장치의 물리적 어드레스 사이의 맵핑 관계를 나타내는 맵핑 데이터를 저장하기 위한 맵핑 메모리를 복수의 맵핑 메모리 영역들로 분할한다. 상기 복수의 맵핑 메모리 영역들의 각각에 대하여 상기 맵핑 데이터가 저장되었는지를 나타내는 점유 정보를 제공한다. 상기 점유 정보에 기초하여 상기 복수의 맵핑 메모리 영역들 중 상기 맵핑 데이터가 저장되지 않은 맵핑 메모리 영역들에 유저 데이터를 저장한다.

- [0006] 상기 일 목적을 달성하기 위해, 본 발명의 실시예들에 따른 비휘발성 메모리 시스템은 비휘발성 메모리 장치, 맵핑 메모리, 점유 상태 매니저 및 제어부를 포함한다.

- [0007] 상기 맵핑 메모리는 호스트 장치의 논리적 어드레스 및 상기 비휘발성 메모리 장치의 물리적 어드레스 사이의 맵핑 관계를 나타내는 맵핑 데이터를 저장하고, 복수의 맵핑 메모리 영역들로 분할된다.

- [0008] 상기 점유 상태 매니저는 상기 복수의 맵핑 메모리 영역들의 각각에 대하여 상기 맵핑 데이터가 저장되었는지를 나타내는 점유 정보를 제공한다.

- [0009] 상기 제어부는 상기 점유 상태 매니저의 상기 점유 정보에 기초하여 상기 복수의 맵핑 메모리 영역들 중 상기 맵핑 데이터가 저장되지 않은 맵핑 메모리 영역들에 유저 데이터를 저장한다.

- [0010] 상기 일 목적을 달성하기 위해, 본 발명의 실시예들에 따른 비휘발성 메모리 시스템은, 비휘발성 메모리 장치, 호스트 장치의 논리적 어드레스 및 상기 비휘발성 메모리 장치의 물리적 어드레스 사이의 맵핑 관계를 나타내는 맵핑 데이터를 저장하고, 복수의 맵핑 메모리 영역들로 분할되는 맵핑 메모리, 상기 맵핑 메모리와 물리적으로 분리되고, 유저 데이터를 저장하는 복수의 버퍼 영역들로 분할하는 버퍼 메모리, 상기 복수의 맵핑 메모리 영역들의 각각에 대하여 상기 맵핑 데이터가 저장되었는지를 나타내는 점유 정보를 제공하는 점유 상태 매니저 및 상기 점유 상태 매니저의 상기 점유 정보에 기초하여 상기 복수의 맵핑 메모리 영역들 중 상기 맵핑 데이터가 저장되지 않은 맵핑 메모리 영역들 또는 상기 복수의 버퍼 영역들에 상기 유저 데이터를 저장하는 제어부를 포함하다.

### 발명의 효과

[0011] 본 발명의 실시예들에 따른 비휘발성 메모리 시스템 및 상기 비휘발성 메모리 시스템의 동작 방법은 맵핑 메모리의 일부를 캐시 메모리로 이용함으로써 점유 면적의 증가 없이 비휘발성 메모리 시스템의 성능을 향상시킬 수 있다.

### 도면의 간단한 설명

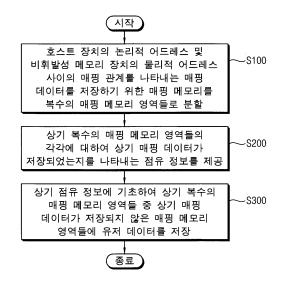

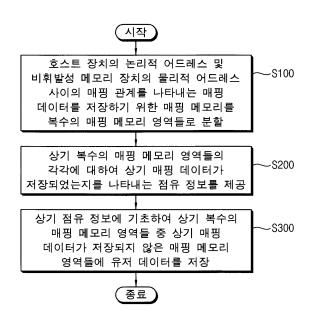

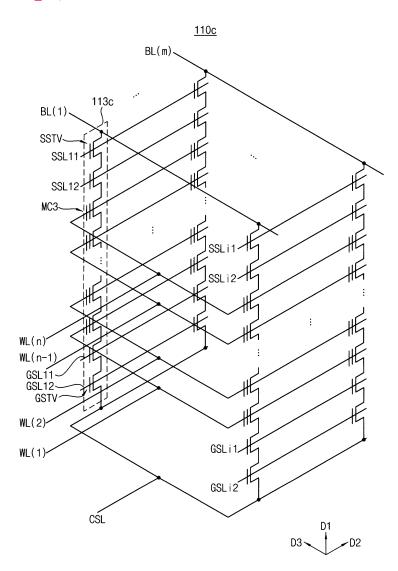

[0012] 도 1은 본 발명의 실시예들에 따른 비휘발성 메모리 시스템의 동작 방법을 나타내는 순서도이다.

도 2는 본 발명의 실시예들에 따른 비휘발성 메모리 시스템을 나타내는 블록도이다.

도 3은 도 2의 비휘발성 메모리 시스템에 포함되는 맵핑 메모리의 분할 방법의 일 예를 나타내는 도면이다.

도 4는 도 2의 비휘발성 메모리 시스템에 포함되는 점유 상태 매니저의 일 실시예를 나타내는 도면이다.

도 5a 및 5b는 본 발명의 실시예들에 따른 맵핑 메모리에 저장되는 맵핑 엔트리의 실시예들을 나타내는 도면들이다.

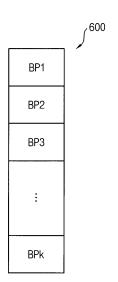

도 6은 본 발명의 실시예들에 따른 맵핑 메모리의 점유 상태의 일 예를 나타내는 도면이다.

도 7은 도 6의 맵핑 메모리의 점유 상태에 상응하는 점유 상태 매니저의 상태 표시 영역들의 저장 값들을 나타내는 도면이다.

도 8은 본 발명의 실시예들에 따른 맵핑 메모리의 점유 상태의 다른 예를 나타내는 도면이다.

도 9는 도 8의 점유 상태에 상응하는 점유 상태 매니저의 상태 표시 영역들의 저장 값들을 나타내는 도면이다.

도 10은 본 발명의 일 실시예에 따른 비휘발성 메모리 시스템의 동작 방법을 나타내는 순서도이다.

도 11은 본 발명의 실시예들에 따른 스토리지 장치를 포함하는 시스템을 나타내는 블록도이다.

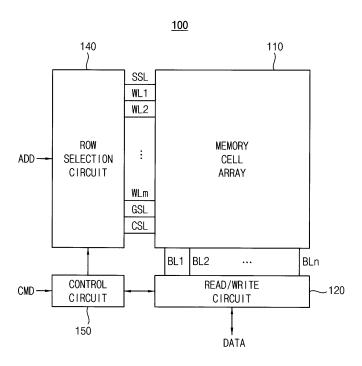

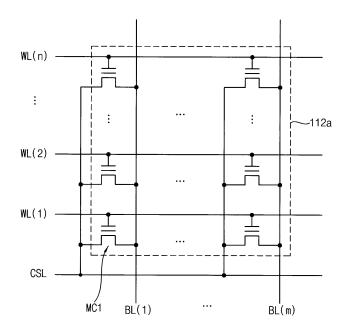

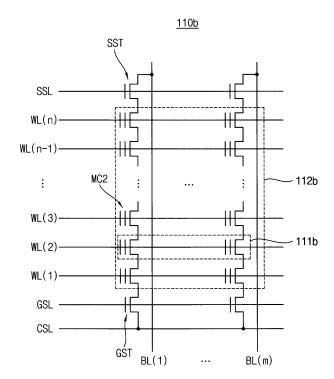

도 12는 도 11의 스토리지 장치에 포함되는 메모리 장치를 나타내는 블록도이다.

도 13a, 도 13b 및 13c는 도 12의 메모리 장치에 포함되는 메모리 셀 어레이의 예들을 나타내는 도면들이다.

도 14는 도 2의 비휘발성 메모리 시스템에 포함되는 맵핑 메모리의 분할 방법의 일 예를 나타내는 도면이다.

도 15a 및 15b는 본 발명의 실시예들에 따른 비휘발성 메모리 시스템의 동작 방법에 이용되는 캐싱 테이블의 일실시예를 나타내는 도면들이다.

도 16a 및 16b는 본 발명의 실시예들에 따른 비휘발성 메모리 시스템의 동작 방법에 이용되는 캐싱 테이블의 다른 실시예를 나타내는 도면들이다.

도 17은 본 발명의 실시예들에 따른 비휘발성 메모리 시스템의 독출 방법을 나타내는 순서도이다.

도 18은 본 발명의 실시예들에 따른 비휘발성 메모리 시스템의 기입 방법을 나타내는 순서도이다.

도 19는 본 발명의 실시예들에 따른 모바일 장치를 나타내는 블록도이다.

#### 발명을 실시하기 위한 구체적인 내용

- [0013] 이하, 첨부한 도면들을 참조하여, 본 발명의 바람직한 실시예를 보다 상세하게 설명하고자 한다. 도면상의 동일 한 구성요소에 대해서는 동일한 참조부호를 사용하고 동일한 구성요소에 대해서 중복된 설명은 생략한다.

- [0014] 도 1은 본 발명의 실시예들에 따른 비휘발성 메모리 시스템의 동작 방법을 나타내는 순서도이고, 도 2는 본 발명의 실시예들에 따른 비휘발성 메모리 시스템을 나타내는 블록도이다.

- [0015] 도 1을 참조하면, 호스트 장치의 논리적 어드레스 및 비휘발성 메모리 장치의 물리적 어드레스 사이의 맵핑 관계를 나타내는 맵핑 데이터를 저장하기 위한 맵핑 메모리를 복수의 맵핑 메모리 영역들로 분할한다(S100). 맵핑 메모리의 분할에 대해서는 도 3을 참조하여 후술한다.

- [0016] 상기 복수의 맵핑 메모리 영역들의 각각에 대하여 상기 맵핑 데이터가 저장되었는지를 나타내는 점유 정보를 제공한다(S200). 도 4 내지 9를 참조하여 후술하는 바와 같이, 상기 점유 정보는 점유 상태 매니저의 상태 표시 영역들에 저장된 값들로서 제공될 수 있다.

- [0017] 상기 점유 정보에 기초하여 상기 복수의 맵핑 메모리 영역들 중 상기 맵핑 데이터가 저장되지 않은 맵핑 메모리 영역들에 유저 데이터를 저장한다(S300).

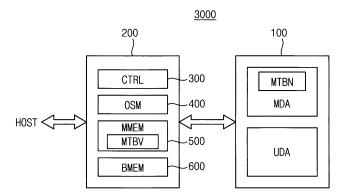

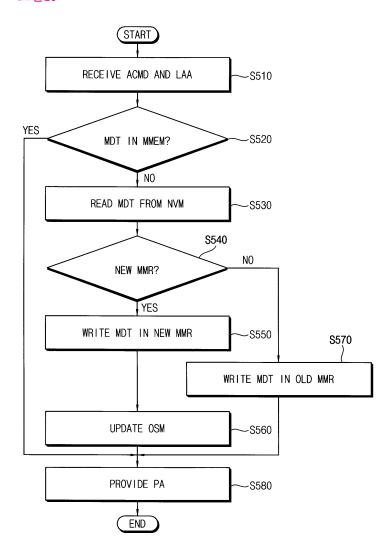

- [0018] 도 2를 참조하면, 메모리 시스템(3000)은 비휘발성 메모리 장치(100) 및 상기 비휘발성 메모리 장치(100)의 동 작을 제어하는 메모리 콘트롤러(200)를 포함할 수 있다.

- [0019] 비휘발성 메모리 장치(100)는 복수의 메모리 셀들이 배열된 메모리 셀 어레이를 포함할 수 있으며, 상기 메모리 셀 어레이는 메타 데이터 영역(MDA) 및 유저 데이터 영역(UDA)을 포함할 수 있다. 메타 데이터 영역과 유저 데이터 영역의 상대적인 크기 또는 메모리 용량은 다양하게 결정될 수 있다. 메타 데이터 영역에는 비휘발성 메모리 장치(100)의 동작에 요구되는 다양한 데이터가 포함될 수 있으며, 이를 메타 데이터라고 한다. 예를 들어, 비휘발성 메모리 장치가 플래시 메모리 장치인 경우, 초기 독출 전압 레벨, P/E 사이클(Program/Erase cycle) 및 논리적 어드레스와 물리적 어드레스간의 맵핑(mapping) 정보를 포함하는 맵핑 테이블(MTBN) 등이 메타 데이

터로서 메타 데이터 영역(MDA)에 저장될 수 있다. 유저 데이터 영역(UDA)에는 유저의 요청에 따라 프로그램 된 유저 데이터가 저장될 수 있다.

- [0020] 메모리 콘트롤러(200)는 제어부(CTRL)(300), 점유 상태 매니저(occupation status manager)(OSM)(400), 맵핑 메모리(mapping memory)(MMEM)(500) 및 버퍼 메모리(buffer memory)(BMEM)(600)를 포함할 수 있다.

- [0021] 맵핑 메모리(500)는 호스트 장치의 논리적 어드레스 및 비휘발성 메모리 장치(100)의 물리적 어드레스 사이의 맵핑 관계를 나타내는 맵핑 데이터, 즉 맵핑 테이블(MTBV)을 저장하고, 도 3을 참조하여 후술하는 바와 같이 복수의 맵핑 메모리 영역들로 분할된다.

- [0022] 버퍼 메모리(600)는 맵핑 메모리(500)와 물리적으로 분리되고, 도 14를 참조하여 후술하는 바와 같이, 유저 데이터를 저장하는 복수의 버퍼 영역들로 분할된다. 실시예들에 따라서, 버퍼 메모리(600)는 생략되거나 맵핑 메모리(500)에 병합될 수 있다. 일 실시예에서, 맵핑 메모리(500) 및/또는 버퍼 메모리(600)는 SRAM(static random access memory), DRAM(dynamic random access memory)와 같이 비교적 작은 단위로 입출력되고 동작 속도가 빠른 휘발성 메모리로 구현될 수 있다. 또한 맵핑 메모리(500) 및/또는 버퍼 메모리(600)는 MRAM(magnetic random access memory), PRAM(phase change random access memory)과 같이 동작 속도가 빠른 비휘발성 메모리로 구현될 수도 있다.

- [0023] 점유 상태 매니저(400)는 맵핑 메모리(500)의 복수의 맵핑 메모리 영역들의 각각에 대하여 상기 맵핑 데이터가 저장되었는지를 나타내는 점유 정보를 제공한다.

- [0024] 제어부(300)는 점유 상태 매니저(400)의 상기 점유 정보에 기초하여 상기 복수의 맵핑 메모리 영역들 중 상기 맵핑 데이터가 저장되지 않은 맵핑 메모리 영역들 또는 상기 복수의 버퍼 영역들에 상기 유저 데이터를 저장한 다.

- [0025] 비휘발성 메모리 장치(100), 예를 들어, 플래시 메모리 장치는 데이터 덮어 쓰기(over write)에 제약이 따른다. 플래시 메모리에 데이터를 덮어 쓰기 위해서는 먼저 이미 기입된 데이터를 소거해야 한다. 이를 기입 전 소거 동작(EBW, erase-before-write)이라 한다. 플래시 메모리의 소거 동작은 기입 동작에 비해 긴 시간이 소요된다. 또한, 플래시 메모리는 일반적으로 페이지 단위로 기입/독출이 이루어지는데, 소거 단위는 기입 단위보다 훨씬 큰 메모리 블록 단위로 수행되어야 한다. 이러한 특징은 다른 저장장치와 다른 특성으로 기존 파일시스템과의 호환성을 가지기 위하여 플래시 메모리의 메모리 콘트롤러는 FTL(flash translation layer)이라는 가상 파일 시스템을 이용하여 플래시 메모리를 관리함으로써 기존의 파일시스템과의 호환성을 제공할 수 있다.

- [0026] FTL은 맵핑 기법을 이용하여, 호스트 장치로부터 입력되는 논리적 어드레스(logical address)를 물리적 어드레스(physical address)로 맵핑하고, 상기 어드레스 맵핑 정보를 포함하는 맵핑 데이터를 생성한다. 맵핑 데이터는 비휘발성 메모리 장치의 메모리 셀 어레이에 맵핑 테이블(MTBN)로서 저장될 수 있다.

- [0027] 논리적 어드레스는 호스트 장치가 인식하는 유저 데이터에 대한 어드레스로서, 호스트 장치는 유저 데이터가 비휘발성 메모리 장치에서 실제로 저장되는 공간에 대한 어드레스인 물리적 어드레스 대신 논리적 어드레스를 지정하여 유저 데이터를 기록하거나 독출할 수 있다. 물리적 어드레스는 비휘발성 메모리 장치에서 실제 유저 데이터가 저장되는 공간에 대한 어드레스이다. 메모리 콘트롤러는 호스트로부터 유저 데이터에 대한 엑세스 명령 및 논리적 어드레스를 수신할 수 있고 논리적 어드레스에 대응하는 물리적 어드레스가 지정하는 공간에 유저 데이터를 기록하거나 그 공간에 저장된 유저 데이터를 독출할 수 있다.

- [0028] 비휘발성 메모리 시스템(3000)의 동작 속도 향상을 위해 비휘발성 메모리 장치(100)에 저장된 맵핑 데이터의 적어도 일부는 맵핑 메모리(500)에 맵핑 테이블(MTBV)로서 로딩될 수 있다. 또한 비휘발성 메모리 시스템(3000)의 동작 속도 향상을 위해 호스트 장치와 비휘발성 메모리 장치(100) 사이에 교환되는 유저 데이터는 버퍼 메모리(600)에 로딩 또는 캐싱될 수 있다. 비휘발성 메모리 장치(100)의 메모리 용량이 증가할수록 이에 상응하는 메모리 용량을 갖는 맵핑 메모리(500)가 요구된다. 그러나, 비휘발성 메모리 장치(100)에 저장된 유저 데이터의양에 따라서 맵핑 메모리(500)의 상당 부분이 비점유 상태 또는 비사용 상태로 남게 된다.

- [0029] 본 발명의 실시예들에 따른 비휘발성 메모리 시스템 및 상기 비휘발성 메모리 시스템의 동작 방법은 맵핑 메모리 일부를 캐시 메모리로 이용함으로써 점유 면적의 증가 없이 비휘발성 메모리 시스템의 성능을 향상시킬 수 있다.

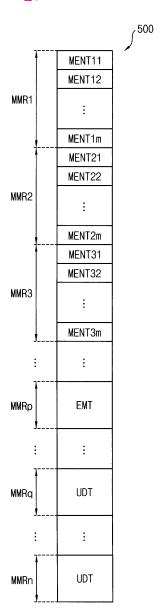

- [0030] 도 3은 도 2의 비휘발성 메모리 시스템에 포함되는 맵핑 메모리의 분할 방법의 일 예를 나타내는 도면이다.

- [0031] 도 3을 참조하면, 맵핑 메모리(500)는 복수의 맵핑 메모리 영역들(MMR1~MMRn)로 분할될 수 있다. 맵핑 메모리

영역들(MMR1~MMRn)의 각각의 사이즈는 비휘발성 메모리 장치(100) 및 메모리 콘트롤러(200) 사이에서 전송되는 데이터 유닛의 사이즈와 동일할 수 있다. 예를 들어, 맵핑 메모리 영역들(MMR1~MMRn)의 각각의 사이즈는 비휘발성 메모리 장치(100)의 독출 및 기입의 단위가 되는 페이지의 사이즈에 상응할 수 있으며, 이에 한정되는 것은 아니다.

- [0032] 맵핑 메모리 영역들(MMR1~MMRn)의 각각은 복수의 맵핑 엔트리들을 저장할 수 있다. 예를 들어, 제1 맵핑 메모리 영역(MMR1)은 m개의 맵핑 엔트리들(MENT11~MENT1m)을 저장하고, 제2 맵핑 메모리 영역(MMR2)은 m개의 맵핑 엔트리들(MENT21~MENT2m)을 저장하고, 제3 맵핑 메모리 영역(MMR3)은 m개의 맵핑 엔트리들(MENT31~MENT3m)을 저장하고, 제p 맵핑 메모리 영역(MMRp)은 빈 상태(EMT)이고 제q 내지 제n 맵핑 메모리 영역들(MMRq~MMRn)은 본 발명의 실시예들에 따라서 유저 데이터(UDT)를 저장할 수 있다.

- [0033] 예를 들어, 맵핑 메모리 영역들(MMR1~MMRn)의 각각의 사이즈는 4K 바이트이고 각 맵핑 엔트리의 사이즈는 4 바이트일 수 있다. 이 경우 맵핑 메모리 영역들(MMR1~MMRn)의 각각에는 약 1000개의 맵핑 엔트리들이 저장될 수 있다.

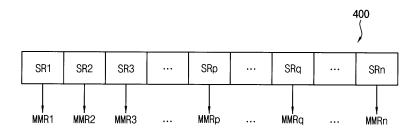

- [0034] 도 4는 도 2의 비휘발성 메모리 시스템에 포함되는 점유 상태 매니저의 일 실시예를 나타내는 도면이다.

- [0035] 도 4를 참조하면, 점유 상태 매니저(400)는 복수의 상태 표시 영역들(SR1~SRn)을 포함할 수 있다.

- [0036] 복수의 상태 표시 영역들(SR1~SRn)은 도 3의 복수의 맵핑 메모리 영역들(MMR1~MMRn)의 각각에 상응한다. 다시 말해, 제1 상태 표시 영역(SR1)은 제1 맵핑 메모리 영역(MMR1)에 상응하고, 제2 상태 표시 영역(SR2)은 제2 맵핑 메모리 영역(MMR2)에 상응하고, 이와 같이, 제n 상태 표시 영역(SRn)은 제n 맵핑 메모리 영역(MMRn)에 상응한다.

- [0037] 복수의 상태 표시 영역들(SR1~SRn)의 각각은 복수의 맵핑 메모리 영역들(MMR1~MMRn)의 각각이 맵핑 데이터가 저장된 점유 맵핑 메모리 영역인지 또는 상기 맵핑 데이터가 저장되지 않은 비점유 맵핑 메모리 영역인지를 나타 내는 값을 저장한다. 다시 말해, 제1 상태 표시 영역(SR1)에 저장된 값은 제1 맵핑 메모리 영역(MMR1)이 점유 맵핑 메모리 영역인지 또는 비점유 맵핑 메모리 영역인지를 나타내고, 제2 상태 표시 영역(SR2)에 저장된 값은 제2 맵핑 메모리 영역(MMR2)이 점유 맵핑 메모리 영역인지 또는 비점유 맵핑 메모리 영역인지를 나타내고, 이와 같이, 제n 상태 표시 영역(SRn)에 저장된 값은 제n 맵핑 메모리 영역(MMRn)이 점유 맵핑 메모리 영역인지 또는 비점유 맵핑 메모리 영역인지를 나타내다.

- [0038] 도 7 및 9를 참조하여 후술하는 바와 같이, 복수의 상태 표시 영역들(SR1~SRn)의 각각은, 1개의 비트 또는 2개의 비트들을 저장할 수 있다.

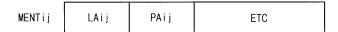

- [0039] 도 5a 및 5b는 본 발명의 실시예들에 따른 맵핑 메모리에 저장되는 맵핑 엔트리의 실시예들을 나타내는 도면들이다.

- [0040] 도 5a를 참조하면, 맵핑 메모리(500)에 저장되는 각각의 맵핑 엔트리(MENTij)는 물리적 어드레스(PAji) 및 기타 값들(ETC)을 포함할 수 있다. 이 경우, 맵핑 엔트리(MENTij)의 인텍스(ij) 자체가 논리적 어드레스를 나타내고 상기 논리적 어드레스는 물리적 어드레스(PAij)에 맵핑된다. 상기 논리적 어드레스는 맵핑 테이블의 시작 주소 및 맵핑 엔트리의 사이즈에 해당하는 오프셋 값 등을 이용하여 계산될 수 있다. 기타 값들(ETC)은 맵핑 엔트리 (MENTij)의 유효 여부를 나타내는 값, 물리적 어드레스(PAij)의 소거 상태를 나타내는 값 등을 포함할 수 있다.

- [0041] 도 5b를 참조하면, 맵핑 메모리(500)에 저장되는 각각의 맵핑 엔트리(MENTij)는 논리적 어드레스(LAij), 물리적 어드레스(PAji) 및 기타 값들(ETC)을 포함할 수 있다. 이 경우, 논리적 어드레스(LAij)는 물리적 어드레스 (PAij)에 맵핑된다. 기타 값들(ETC)은 맵핑 엔트리(MENTij)의 유효 여부를 나타내는 값, 물리적 어드레스(PAij)의 소거 상태를 나타내는 값 등을 포함할 수 있다.

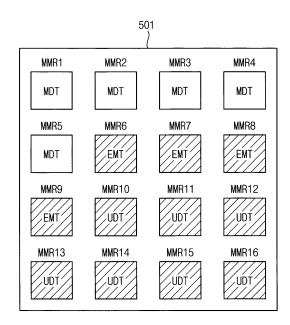

- [0042] 도 6은 본 발명의 실시예들에 따른 맵핑 메모리의 점유 상태의 일 예를 나타내는 도면이고, 도 7은 도 6의 맵핑 메모리의 점유 상태에 상응하는 점유 상태 매니저의 상태 표시 영역들의 저장 값들을 나타내는 도면이다.

- [0043] 도 6에는 설명 및 도시의 편의를 위하여 예시적으로 16개의 맵핑 메모리 영역들을 포함하는 맵핑 메모리의 점유 상태(501)의 일 예가 도시되어 있다. 도 6을 참조하면, 제1 내지 제5 맵핑 메모리 영역들(MMR1~MMR5)은 맵핑 데이터(MDT)가 저장된 점유 맵핑 메모리 영역(OMMR)에 해당하고 제6 내지 제16 맵핑 메모리 영역들(MMR6~MMR16)은 맵핑 데이터(MDT)가 저장되지 않은 비점유 맵핑 메모리 영역(UMMR)에 해당한다. 비점유 메모리 영역에 해당하는 제6 내지 제16 맵핑 메모리 영역들(MMR6~MMR16)은 본 발명의 실시예들에 따라서 유저 데이터(UDT)가 저장된 데이터 맵핑 메모리 영역에 해당하고 제6 내지 제9 맵

핑 메모리 영역들(MMR6~MMR9)은 맵핑 데이터(MDT) 및 유저 데이터(UDT)가 모두 저장되지 않은 엠프티 맵핑 메모리 영역(EMT)일 수 있다.

- [0044] 도 7에는 도 6의 맵핑 메모리의 점유 상태(501)에 상응하는 점유 상태 매니저의 2가지 실시예들(401a, 401b)이 도시되어 있다.

- [0045] 제1 실시예에 따른 점유 상태 매니저(401a)는 복수의 상태 표시 영역들(SR1~SR16)의 각각이 1개의 비트를 저장할 수 있다. 복수의 상태 표시 영역들(SR1~SR16)의 각각은 상응하는 맵핑 메모리 영역이 맵핑 데이터(MDT)가 저장된 점유 맵핑 메모리 영역임을 나타내는 제1 값(예를 들어, 1) 및 상응하는 맵핑 메모리 영역이 맵핑 데이터(MDT)가 저장되지 않은 비점유 맵핑 메모리 영역임을 나타내는 제2 값(예를 들어, 0) 중 하나를 저장할 수 있다. 도 6의 맵핑 메모리의 점유 상태(501)의 경우, 제1 내지 제5 상태 표시 영역들(SR1~SR5)은 제1 값(1)을 갖고 제6 내지 제16 상태 표시 영역들(SR6~SR16)은 제2 값(0)을 가질 수 있다.

- [0046] 맵핑 메모리의 점유 상태(501)는 가변적이고, 이러한 맵핑 메모리의 점유 상태(501)의 변경에 따라서, 상태 표시 영역들(SR1~SR16)의 값들이 갱신될 수 있다.

- [0047] 비점유 맵핑 메모리 영역에 맵핑 데이터(MDT)가 저장된 경우, 상응하는 상태 표시 영역의 값을 제2 값(0)에서 제1 값(1)으로 변경할 수 있다. 예를 들어, 빈 상태의 제6 맵핑 메모리 영역(MMR6)에 맵핑 데이터(MDT)가 저장된 경우, 이에 상응하는 제6 상태 표시 영역(SR6)의 값을 제2 값(0)에서 제1 값(1)으로 변경할 수 있다.

- [0048] 한편, 점유 맵핑 메모리 영역에 저장된 맵핑 데이터(MDT)가 폐기된 경우, 상응하는 상태 표시 영역의 값을 제1 값(1)에서 제2 값(0)으로 변경할 수 있다. 예를 들어, 제5 맵핑 메모리 영역(MMR5)에 저장된 맵핑 데이터(MDT) 가 폐기된 경우, 제5 상태 표시 영역(SR5)의 값을 제1 값(1)에서 제2 값(0)으로 변경할 수 있다.

- [0049] 제2 실시예에 따른 점유 상태 매니저(401b)는 복수의 상태 표시 영역들(SR1~SR16)의 각각이 2개의 비트들을 저장할 수 있다. 복수의 상태 표시 영역들(SR1~SR16)의 각각은 상응하는 맵핑 메모리 영역이 맵핑 데이터(MDT)가 저장된 점유 맵핑 메모리 영역임을 나타내는 제1 값(예를 들어, 11), 상응하는 맵핑 메모리 영역이 유저 데이터(UDT)가 저장된 데이터 맵핑 메모리 영역임을 나타내는 제2 값(예를 들어, 01) 및 상응하는 맵핑 메모리 영역이 맵핑 데이터(MDT) 및 유저 데이터(UDT)가 모두 저장되지 않은 엠프티 맵핑 메모리 영역임을 나타내는 제3 값(예를 들어, 00) 중 하나를 저장할 수 있다. 도 6의 맵핑 메모리의 점유 상태(501)의 경우, 제1 내지 제5 상태 표시 영역들(SR1~SR5)은 제1 값(11)을 갖고 제10 내지 제16 상태 표시 영역들(SR10~SR16)은 제2 값(01)을 갖고 제6 내지 제9 상태 표시 영역들(SR6~SR9)은 제3 값(00)을 가질 수 있다.

- [0050] 엠프티 맵핑 메모리 영역 또는 데이터 맵핑 메모리 영역에 맵핑 데이터(MDT)가 저장되는 경우, 상응하는 상태 표시 영역의 값을 제3 값(00) 또는 제2 값(01)에서 제1 값(11)으로 변경할 수 있다. 예를 들어, 빈 상태의 제6 맵핑 메모리 영역(MMR6)에 맵핑 데이터(MDT)가 저장된 경우, 이에 상응하는 제6 상태 표시 영역(SR6)의 값을 제3 값(00)에서 제1 값(11)으로 변경할 수 있다. 또한, 데이터 맵핑 메모리 영역에 해당하는 제10 맵핑 메모리 영역(MMR10)에 맵핑 데이터(MDT)가 저장된 경우, 이에 상응하는 제10 상태 표시 영역(SR10)의 값을 제2 값(01)에서 제1 값(11)으로 변경할 수 있다.

- [0051] 한편, 점유 맵핑 메모리 영역에 저장된 맵핑 테이터(MDT)가 폐기된 경우, 상응하는 상태 표시 영역의 값을 상기 제1 값(11)에서 제3 값(00으로 변경할 수 있다. 예를 들어, 제5 맵핑 메모리 영역(MMR6)에 저장된 맵핑 테이터 (MDT)가 폐기된 경우, 제5 상태 표시 영역(SR5)의 값을 제1 값(11)에서 제3 값(00)으로 변경할 수 있다.

- [0052] 또한, 데이터 맵핑 메모리 영역에 저장된 유저 데이터(UDT)가 페기된 경우, 상응하는 상태 표시 영역의 값을 상기 제2 값(01)에서 제3 값(00)으로 변경할 수 있다. 예를 들어, 제12 맵핑 메모리 영역(MMR12)에 저장된 유저데이터(UDT)가 페기된 경우, 제12 상태 표시 영역(SR12)의 값을 제2 값(01)에서 제3 값(00)으로 변경할 수있다.

- [0053] 이와 같이, 점유 상태 매니저를 이용하여 맵핑 메모리의 적어도 일부를 캐시 메모리로 이용하는 것을 관리하여 점유 면적의 증가 없이 캐시 용량을 증가시킴으로써 비휘발성 메모리 시스템의 성능을 향상시킬 수 있다.

- [0054] 도 8은 본 발명의 실시예들에 따른 맵핑 메모리의 점유 상태의 다른 예를 나타내는 도면이고, 도 9는 도 8의 점유 상태에 상응하는 점유 상태 매니저의 상태 표시 영역들의 저장 값들을 나타내는 도면이다. 이하 도 6 및 7과 중복되는 설명은 생략한다.

- [0055] 도 6의 맵핑 메모리의 점유 상태(501)와 비교하여, 도 8의 맵핑 메모리의 점유 상태(502)는 점유 맵핑 메모리 영역들의 개수가 증가한 것을 알 수 있다. 도 8을 참조하면, 제1 내지 제9 맵핑 메모리 영역들(MMR1~MMR9)은 맵

핑 데이터(MDT)가 저장된 점유 맵핑 메모리 영역(OMMR)에 해당하고 제10 내지 제16 맵핑 메모리 영역들 (MMR10~MMR16)은 맵핑 데이터(MDT)가 저장되지 않은 비점유 맵핑 메모리 영역(UMMR)에 해당한다. 비점유 메모리 영역에 해당하는 제10 내지 제16 맵핑 메모리 영역들(MMR6~MMR16) 중에서, 제11 내지 제16 맵핑 메모리 영역들(MMR11~MMR16)은 본 발명의 실시예들에 따라서 유저 데이터(UDT)가 저장된 데이터 맵핑 메모리 영역에 해당하고 제10 맵핑 메모리 영역(MMR10)은 맵핑 데이터(MDT) 및 유저 데이터(UDT)가 모두 저장되지 않은 앰프티 맵핑 메모리 영역(EMT)일 수 있다.

- [0056] 도 9에는 도 8의 맵핑 메모리의 점유 상태(502)에 상응하는 점유 상태 매니저의 2가지 실시예들(402a, 402b)이 도시되어 있다. 도 9에 도시된 상태 표시 영역들(SR1~SR16)에 저장된 값들은 도 7을 설명한 바와 같이 결정되고 갱신될 수 있다.

- [0057] 제1 실시예에 따른 점유 상태 매니저(402a)는 복수의 상태 표시 영역들(SR1~SR16)의 각각이 1개의 비트를 저장할 수 있다. 복수의 상태 표시 영역들(SR1~SR16)의 각각은 상응하는 맵핑 메모리 영역이 맵핑 데이터(MDT)가 저장된 점유 맵핑 메모리 영역임을 나타내는 제1 값(예를 들어, 1) 및 상응하는 맵핑 메모리 영역이 맵핑 데이터(MDT)가 저장되지 않은 비점유 맵핑 메모리 영역임을 나타내는 제2 값(예를 들어, 0) 중 하나를 저장할 수 있다. 도 8의 맵핑 메모리의 점유 상태(502)의 경우, 제1 내지 제9 상태 표시 영역들(SR1~SR9)은 제1 값(1)을 갖고 제10 내지 제16 상태 표시 영역들(SR10~SR16)은 제2 값(0)을 가질 수 있다.

- [0058] 제2 실시예에 따른 점유 상태 매니저(402b)는 복수의 상태 표시 영역들(SR1~SR16)의 각각이 2개의 비트들을 저장할 수 있다. 복수의 상태 표시 영역들(SR1~SR16)의 각각은 상응하는 맵핑 메모리 영역이 맵핑 데이터(MDT)가 저장된 점유 맵핑 메모리 영역임을 나타내는 제1 값(예를 들어, 11), 상응하는 맵핑 메모리 영역이 유저 데이터(UDT)가 저장된 데이터 맵핑 메모리 영역임을 나타내는 제2 값(예를 들어, 01) 및 상응하는 맵핑 메모리 영역이 맵핑 데이터(MDT) 및 유저 데이터(UDT)가 모두 저장되지 않은 엠프티 맵핑 메모리 영역임을 나타내는 제3 값(예를 들어, 00) 중 하나를 저장할 수 있다. 도 8의 맵핑 메모리의 점유 상태(502)의 경우, 제1 내지 제9 상태 표시 영역들(SR11~SR9)은 제1 값(11)을 갖고 제11 내지 제16 상태 표시 영역들(SR11~SR16)은 제2 값(01)을 갖고 제10 상태 표시 영역(SR10)은 제3 값(00)을 가질 수 있다.

- [0059] 도 6 내지 9를 참조하여 설명한 바와 같이, 비휘발성 메모리 시스템의 동작 상태에 따라서 맵핑 데이터(MDT)가 저장되는 점유 맵핑 메모리 영역들의 개수 및 유저 데이터(UDT)가 저장되는 데이터 맵핑 메모리 영역들의 개수는 동적으로(dynamically) 변경될 수 있다.

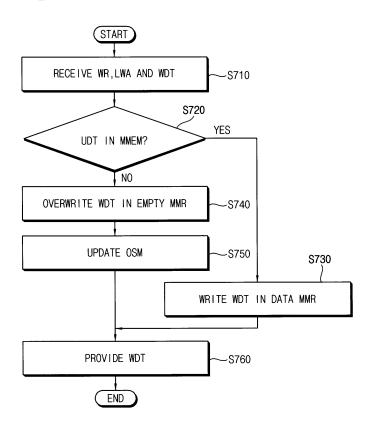

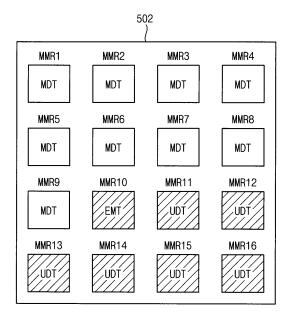

- [0060] 도 10은 본 발명의 일 실시예에 따른 비휘발성 메모리 시스템의 동작 방법을 나타내는 순서도이다.

- [0061] 도 10을 참조하면, 독출 동작 또는 기입 동작을 위해, 메모리 콘트롤러는 호스트 장치로부터 액세스 명령(ACMD) 및 논리적 액세스 어드레스(LAA)를 수신한다(S510). 액세스 명령(ACMD)은 독출 명령 및 기입 명령을 포함할 수 있다.

- [0062] 논리적 액세스 어드레스(LAA)에 상응하는 맵핑 데이터(MDT)가 맵핑 메모리(MMEM)의 점유 맵핑 메모리 영역에 저장되어 있지 않은 경우(S520: NO), 메모리 콘트롤러는 비휘발성 메모리 장치로부터 논리적 액세스 어드레스 (LAA)에 상응하는 맵핑 데이터(MDT)를 독출한다(S530).

- [0063] 메모리 콘트롤러는 독출된 맵핑 데이터(MDT)를 비점유 맵핑 메모리 영역(NEW MMR)에 저장할 것을 결정한 경우 (S540: YES), 맵핑 메모리는 독출된 맵핑 데이터(MDT)를 비점유 맵핑 메모리 영역(NEW MMR)에 저장하고(S550), 점유 상태 매니저(OSM)의 상응하는 상태 표시 영역의 값을 갱신한다(S560). 상태 표시 영역의 값의 갱신은 도 6 내지 9를 참조하여 설명한 바와 같다. 맵핑 메모리는 논리적 액세스 어드레스(LAA)에 상응하는 물리적 어드레스 (PA)를 제공한다(S580). 메모리 콘트롤러가 독출된 맵핑 데이터(MDT)를 점유 맵핑 메모리 영역(OLD MMR)에 저장한 것을 결정한 경우(S540: NO), 맵핑 메모리는 독출된 맵핑 데이터(MDT)를 점유 맵핑 메모리 영역(OLD MMR)에 저장한다(S570).

- [0064] 논리적 액세스 어드레스(LAA)에 상응하는 맵핑 데이터(MDT)가 맵핑 메모리(MMEM)의 점유 맵핑 메모리 영역에 저장되어 있는 경우(S520: YES), 메모리 콘트롤러가 비휘발성 메모리 장치를 액세스할 필요 없이, 맵핑 메모리는 논리적 액세스 어드레스(LAA)에 상응하는 물리적 어드레스(PA)를 제공한다(S580).

- [0065] 도 11은 본 발명의 실시예들에 따른 스토리지 장치를 포함하는 시스템을 나타내는 블록도이다.

- [0066] 도 11을 참조하면, 시스템(1000)은 호스트 장치(2000) 및 스토리지 장치(3000)를 포함한다. 스토리지 장치 (3000)는 도 2의 메모리 시스템(3000)의 일 예로서, 예를 들어, 스토리지 장치(3000)는 임베디드 멀티미디어 카

드(eMMC, embedded multimedia card)일 수 있다.

- [0067] 호스트 장치(2000)는 스토리지 장치(3000)의 데이터 처리 동작, 예를 들어, 데이터 독출 동작 또는 데이터 기입 동작 등을 제어할 수 있다. 호스트 장치(2000)는 애플리케이션 프로세서(application processor) 등과 같이 데이터를 처리할 수 있는 데이터 처리 장치일 수 있고, 상기 데이터 처리 장치(2000) 및 스토리지 장치(3000)는 전자 장치에 내장(embedded) 또는 구현될 수 있다.

- [0068] 스토리지 장치(3000)는 호스트 장치(2000)와 데이터 통신을 위해 접속 수단들, 예컨대, 패드들(pads), 핀들 (pins), 버스(bus), 또는 통신 라인들을 통하여 전기적으로 서로 접속될 수 있다.

- [0069] 호스트 장치(2000)는 버스(20)를 통하여 연결된 프로세서(CPU)(2100), 메모리(MEM)(2200) 및 호스트 콘트롤러인터페이스(HCI)(2300)를 포함할 수 있다. 프로세서(2100)에 의해 운영 체제(OS) 및/또는 호스트 펌웨어(FW)(2110)가 구동될 수 있다. 도시된 구성 요소 이외에도 호스트 장치(2000)는 클록 생성기(미도시), 상태 제어 유닛(미도시) 등을 더 포함할 수 있다.

- [0070] 프로세서(2100)는 코맨드(CMD)의 생성, 응답(RES)의 해석, 스토리지 장치(3000)의 레지스터, 예를 들어, Extended(EXT)\_CSD 레지스터(미도시)에 저장된 데이터 및/또는 데이터 처리 동작을 제어할 수 있는 하드웨어를 의미할 수 있다. 프로세서(2100)는 운영 체제/호스트 펌웨어(2110)를 구동하여 상기와 같은 동작들을 수행할 수 있다.

- [0071] 호스트 콘트롤러 인터페이스(2300)는 스토리지 장치(3000)와 인터페이스하기 위한 구성요소이다. 호스트 콘트롤러 인터페이스(2300)는 스토리지 장치(3000)로 코맨드 및 논리적 어드레스를 발급하고(issuing), 코맨드(CMD)에 대한 응답을 스토리지 장치(3000)로부터 수신하고, 스토리지 장치(3000)에 저장될 기입 데이터를 전송하고, 스토리지 장치(3000)로부터 독출한 독출 데이터를 수신한다.

- [0072] 스토리지 장치(3000)는 복수의 비휘발성 메모리 장치들(NVM)(100) 및 메모리 콘트롤러(200) 또는 스토리지 콘트롤러를 포함한다.

- [0073] 비휘발성 메모리 장치들(100)은 옵션적으로 외부 고전압(VPP)을 제공받도록 구현될 수 있다. 비휘발성 메모리 장치들(100)은 플래시 메모리, 에프램(FRAM, ferroelectric random access memory), 피램(PRAM, phase-change random access memory), 엠램(MRAM, magnetic random access memory) 등으로 구현될 수 있다.

- [0074] 스토리지 콘트롤러(200)는 복수의 채널들(CH1~CHi)을 통하여 비휘발성 메모리 장치들(100)에 연결된다. 스토리지 콘트롤러(200)는 버스(30)를 통하여 연결된 적어도 하나의 프로세서(210), 에러 정정 회로(ECC)(220), 호스트 인터페이스(230), 맵핑 메모리(500), 버퍼 메모리(600), 비휘발성 메모리 인터페이스(250) 및 태스크 큐 (TQ)(260)를 포함한다.

- [0075] 맵핑 메모리(500)는 전술한 바와 같이 호스트 장치(2000)의 논리적 어드레스 및 비휘발성 메모리 장치들(100)의 물리적 어드레스 사이의 맵핑 관계를 나타내는 맵핑 데이터를 저장하고, 복수의 맵핑 메모리 영역들로 분할된다. 버퍼 메모리(600)는 맵핑 메모리(500)와 물리적으로 분리되고, 도 14를 참조하여 후술하는 바와 같이 유저 데이터를 저장하는 복수의 버퍼 영역들로 분할된다.

- [0076] 에러 정정 회로(220)는 기입 동작에서 프로그램될 데이터의 에러 정정 코드 값을 계산하고, 읽기 동작에서 읽혀 진 데이터를 에러 정정 코드 값에 근거로 하여 에러 정정하고, 데이터 복구 동작에서 비휘발성 메모리 장치 (100)로부터 복구된 데이터의 에러를 정정할 수 있다. 도 11에 도시되지는 않았지만, 스토리지 콘트롤러(200)는 펌웨어(FW)(212)를 저장하는 코드 메모리를 더 포함할 수 있다. 상기 코드 메모리는 비휘발성 메모리 장치로 구현될 수 있다.

- [0077] 프로세서(210)는 스토리지 콘트롤러(200)의 전반적인 동작을 제어하도록 구성된다. 예를 들면, 프로세서(210)는 플래시 변환 계층(FTL, Flash Translation Layer) 등을 포함하는 펌웨어(212)를 운용하도록 구성된다. 플래시 변환 계층(FTL)은 다양한 기능들을 수행할 수 있다. 예를 들면, 플래시 변환 계층(FTL)은 어드레스 맵핑 동작, 읽기 교정 동작, 에러 정정 동작, 등을 수행하는 다양한 계층들을 포함할 수 있다.

- [0078] 태스크 큐(260)는 호스트 장치(2000)로부터 제공되는 독출 태스크, 기입 태스크와 같은 태스크들 및 상기 태스크들의 상태 정보를 저장한다.

- [0079] 호스트 인터페이스(230)는 호스트 장치(2000)와의 인터페이스 기능을 제공할 수 있다. 비휘발성 메모리 인터페이스(250)는 비휘발성 메모리 장치(100)와의 인터페이스 기능을 제공할 수 있다. 호스트 장치(2000)와 스토리지

장치(3000)는 버스(10)를 통하여 상호 연결될 수 있다.

- [0080] 도 12는 도 11의 스토리지 장치에 포함되는 메모리 장치를 나타내는 블록도이고, 도 13a, 도 13b 및 13c는 도 12의 메모리 장치에 포함되는 메모리 셀 어레이의 예들을 나타내는 도면들이다.

- [0081] 도 12, 도 13a, 도 13b 및 도 13c에는 설명의 편의를 위하여 도 11의 스토리지 장치(3000)에 포함되는 비휘발성 메모리 장치(100)의 일 예로서 플래시 메모리 장치가 도시되어 있다.

- [0082] 도 12를 참조하면, 플래시 메모리 장치(100)는 1-비트 데이터 정보 또는 N-비트 데이터 정보(N은 1 보다 큰 정수)를 각각 저장하는 복수의 메모리 셀들을 포함하는 메모리 셀 어레이(110), 기입 독출 회로(120), 행 선택회로(140) 및 제어 회로(150)를 포함할 수 있다.

- [0083] 셀 당 1-비트 데이터 정보를 저장하는 메모리 셀을 싱글 레벨 셀(single-level cell; SLC)이라 하고 셀 당 N-비트 데이터 정보를 저장하는 메모리 셀을 멀티 레벨 셀(multi-level cell; MLC)이라 한다.

- [0084] 셀 어레이(110)는 복수의 행들(또는 워드라인들)과 복수의 열들(또는 비트 라인들)의 교차점들에 배열된 메모리 셀들을 포함할 수 있다. 셀 어레이(110)에 포함된 복수의 메모리 셀들은 복수의 메모리 블록들(Memory Blocks)을 구성할 수 있다.

- [0085] 제어 회로(150)는 플래시 메모리 장치(100)의 기입, 소거, 및 독출 동작과 관련된 제반 동작을 제어할 수 있다. 프로그램될 데이터는 제어 회로(150)의 제어에 따라 버퍼를 통해 기입 독출 회로(120)로 로딩될 수 있다. 프로그램이 실행되는 구간 동안 제어 회로(150)는 행 선택회로(140), 기입 독출 회로(120)를 제어하여, 선택된 워드라인으로 프로그램 전압이, 비선택된 워드라인들로 패스 전압이, 그리고 메모리 셀들이 형성된 벌크에 벌크 전압(예를 들어, 0V)이 인가되도록 할 수 있다.

- [0086] 프로그램 전압(Vpgm)은 증가형 스텝 펄스 프로그래밍(incremental step pulse programming: ISPP) 방식에 따라 발생될 수 있다. 프로그램 전압의 레벨은 프로그램 루프들이 반복됨에 따라 소정의 전압 증가분만큼 단계적으로 증가 또는 감소할 수 있다. 각각의 프로그램 루프에서 사용되는 프로그램 전압들의 인가 횟수, 전압 레벨, 그리고 전압 인가 시간 등은 외부(예를 들면, 메모리 콘트롤러) 또는 내부(예를 들면, 제어회로(3150))의 제어에 따라 다양한 형태로 결정될 수 있다.

- [0087] 도 12에서, 제어 회로(150)는 동작 모드에 따라서 각각의 워드라인들로 공급될 워드라인 전압들(프로그램 전압, 패스 전압, 검증 전압, 독출 전압)과, 메모리 셀들이 형성된 벌크로 공급될 벌크 전압을 발생할 수 있다. 행 선택회로(140)는 제어 회로(150)의 제어에 응답해서 메모리 셀 어레이(3110)의 메모리 블록들(또는 섹터들) 중 하나를 선택하고, 선택된 메모리 블록의 워드라인들 중 하나를 선택할 수 있다. 행 선택회로(140)는 제어 회로 (150)의 제어에 응답해서 상응하는 워드라인 전압을 선택된 워드라인 및 비선택된 워드라인들로 각각 제공할 수 있다.

- [0088] 기입 독출 회로(120)는 제어 회로(150)에 의해서 제어되며, 동작 모드에 따라 감지 증폭기(sense amplifier)로 서 또는 기입 드라이버(write driver)로서 동작할 수 있다. 예를 들면, 검증 독출 동작 및 정상 독출 동작의 경우 기입 독출 회로(120)는 메모리 셀 어레이(3110)로부터 데이터를 독출하기 위한 감지 증폭기로서 동작할 수 있다. 정상 독출 동작시 기입 독출 회로(120)로부터 위혀진 데이터는 버퍼를 통해 외부(예를 들면, 메모리 콘트롤러 또는 호스트)로 출력되는 반면, 검증 독출 동작시 위혀진 데이터는 패스/패일 검증 회로로 제공될 수 있다.

- [0089] 기입 동작의 경우, 기입 독출 회로(120)는 메모리 셀 어레이(110)에 저장될 데이터에 따라 비트 라인들을 구동하는 기입 드라이버로서 동작할 수 있다. 기입 독출 회로(120)는 기입 동작시 메모리 셀 어레이(110)에 쓰일 데이터를 버퍼로부터 입력받고, 입력된 데이터에 따라 비트라인들을 구동할 수 있다. 이를 위해 기입 독출 회로 (120)는 열들(또는 비트 라인들) 또는 열 쌍들(또는 비트 라인 쌍들)에 각각 대응되는 복수 개의 페이지 버퍼들로 구성될 수 있다.

- [0090] 선택된 워드라인에 접속된 메모리 셀들을 프로그램할 때, 선택된 워드라인으로는 프로그램 전압과 검증 전압이 교대로 제공될 수 있다. 검증 동작시 선택된 메모리 셀들 각각에 접속된 비트 라인들이 프리차지될 수 있다. 그리고 프리차지된 비트 라인의 전압 변화가 대응되는 페이지 버퍼를 통해 감지될 수 있다. 검증 독출 동작시 감지된 데이터는 패스/패일 검증 회로로 제공되어, 메모리 셀들의 프로그램 성공 여부가 판단될 수 있다.

- [0091] 도 13a, 도 13b 및 도 13c는 도 12의 비휘발성 메모리 장치에 포함되는 메모리 셀 어레이의 예들을 나타내는 도

면들이다.

- [0092] 도 13a는 NOR형 플래시 메모리 장치에 포함되는 메모리 셀 어레이의 일 예를 나타내는 회로도이고, 도 13b는 NAND형 플래시 메모리 장치에 포함되는 메모리 셀 어레이의 일 예를 나타내는 회로도이며, 도 13c는 수직형 플래시 메모리 장치에 포함되는 메모리 셀 어레이의 일 예를 나타내는 회로도이다.

- [0093] 도 13a를 참조하면, 메모리 셀 어레이(110a)는 복수의 메모리 셀(MC1)들을 포함할 수 있다. 동일한 열에 배열된 메모리 셀(MC1)들은 비트 라인들(BL(1), ..., BL(m)) 중 하나와 공통 소스 라인(CSL) 사이에 병렬로 배치될 수 있으며, 동일한 행에 배열된 메모리 셀(MC1)들은 워드 라인들(WL(1), WL(2), ..., WL(n)) 중 하나에 공통으로 연결될 수 있다. 예를 들어, 제1열에 배열된 메모리 셀들은 제1 비트 라인(WL(1))과 공통 소스 라인(CSL) 사이에 병렬로 배치될 수 있다. 제1행에 배열된 메모리 셀들의 게이트 전극들은 제1 워드 라인(WL(1))에 공통으로 연결될 수 있다. 메모리 셀(MC1)들은 워드 라인들(WL(1), ..., WL(n))에 인가되는 전압의 레벨에 따라 제어될 수 있다.

- [0094] NOR형 플래시 메모리 장치는 바이트(byte) 단위 또는 워드(word) 단위로 기입 동작 및 독출 동작을 수행하며, 블록 단위로 소거 동작을 수행한다. 기입 동작이 수행되는 경우에, 상기 NOR형 플래시 메모리 장치의 벌크 기판에는 약 -0.1V 내지 약 -0.7V의 벌크 전압이 인가될 수 있다.

- [0095] 도 13b를 참조하면, 메모리 셀 어레이(110b)는 스트링 선택 트랜지스터(SST)들, 접지 선택 트랜지스터(GST)들 및 메모리 셀(MC2)들을 포함할 수 있다. 스트링 선택 트랜지스터(SST)들은 비트 라인들(BL(1), ..., BL(m))에 연결되고, 접지 선택 트랜지스터(GST)들은 공통 소스 라인(CSL)에 연결될 수 있다. 동일한 열에 배열된 메모리 셀(MC2)들은 비트 라인들(BL(1), ..., BL(m)) 중 하나와 공통 소스 라인(CSL) 사이에 직렬로 배치될 수 있으며, 동일한 행에 배열된 메모리 셀(MC2)들은 워드 라인들(WL(1), WL(2), WL(3), ..., WL(n-1), WL(n)) 중 하나에 공통으로 연결될 수 있다. 즉, 스트링 선택 트랜지스터(SST)들과 접지 선택 트랜지스터(GST)들 사이에 메모리 셀(MC2)들이 직렬로 연결될 수 있으며, 스트링 선택 라인(SSL)과 접지 선택 라인(GSL) 사이에는 16개, 32개 또는 64개의 복수의 워드 라인들이 배열될 수 있다.

- [0096] 스트링 선택 트랜지스터(SST)들은 스트링 선택 라인(SSL)에 연결되어, 스트링 선택 라인(SSL)으로부터 인가되는 전압의 레벨에 따라 제어될 수 있고, 접지 선택 트랜지스터(GST)들은 접지 선택 라인(GSL)에 연결되어, 접지 선택 라인(GSL)으로부터 인가되는 전압의 레벨에 따라 제어될 수 있다. 메모리 셀(MC2)들은 워드 라인들(WL(1), ..., ₩L(n))에 인가되는 전압의 레벨에 따라 제어될 수 있다.

- [0097] NAND형 플래시 메모리 장치는 페이지(page, 111b) 단위로 기입 동작 및 독출 동작을 수행하며, 블록(block, 112b) 단위로 소거 동작을 수행한다. 기입 동작이 수행되는 경우에, 상기 NAND형 플래시 메모리 장치의 벌크 기 판에는 약 0V의 벌크 전압이 인가될 수 있다. 한편, 실시예에 따라서, 페이지 버퍼 회로들은 각각 짝수 비트 라인과 홀수 비트 라인이 하나씩 연결될 수 있다. 이 경우, 짝수 비트 라인들은 짝수 페이지를 형성하고, 홀수 비트 라인들은 홀수 페이지를 형성하며, 메모리 셀(MC2)들에 대한 기입 동작은 짝수 페이지와 홀수 페이지가 번갈 아가며 순차적으로 수행될 수 있다.

- [0098] 도 13c를 참조하면, 메모리 셀 어레이(110c)는 수직 구조를 가지는 복수의 스트링(113c)들을 포함할 수 있다. 스트링(113c)은 제2 방향(D2)을 따라 복수 개로 형성되어 스트링 열을 형성할 수 있으며, 상기 스트링 열은 제3 방향(D3)을 따라 복수 개로 형성되어 스트링 어레이를 형성할 수 있다. 복수의 스트링(3113c)들은 비트 라인들 (BL(1), ..., BL(m))과 공통 소스 라인(CSL) 사이에 제1 방향(D1)을 따라 직렬로 배치되는 접지 선택 트랜지스터(GSTV)들, 메모리 셀(MC3)들 및 스트링 선택 트랜지스터(SSTV)들을 각각 포함할 수 있다.

- [0099] 접지 선택 트랜지스터(GSTV)들은 접지 선택 라인들(GSL11, GSL12, ..., GSLi1, GSLi2)에 각각 연결되고, 스트링 선택 트랜지스터(SSTV)들은 스트링 선택 라인들(SSL11, SSL12, ..., SSLi1, SSLi2)에 각각 연결될 수 있다. 동일한 층에 배열되는 메모리 셀(MC3)들은 워드 라인들(WL(1), WL(2), ..., WL(n-1), WL(n)) 중 하나에 공통으로 연결될 수 있다. 접지 선택 라인들(GSL11, ..., GSLi2) 및 스트링 선택 라인들(SSL11, ..., SSLi2)은 상기제2 방향(D2)으로 연장되며 상기 제3 방향(D3)을 따라 복수 개로 형성될 수 있다. 워드 라인들(WL(1), ..., WL(n))은 상기 제2 방향(D2)으로 연장되며 상기 제1 방향(D1) 및 상기 제3 방향(D3)을 따라 복수 개로 형성될수 있다. 비트 라인들(BL(1), ..., BL(m))은 상기 제3 방향으로 연장되며 상기 제2 방향을 따라 복수 개로 형성될수 있다. 메모리 셀(MC3)들은 워드 라인들(WL(1), ..., WL(n))에 인가되는 전압의 레벨에 따라 제어될수 있다.

- [0100] 도 13c의 메모리 셀 어레이(110c)를 포함하는 수직형 플래시 메모리 장치는 NAND 플래시 메모리 셀들을 포함하

므로, NAND형 플래시 메모리 장치와 마찬가지로 페이지 단위로 기입 동작 및 독출 동작을 수행하며, 블록 단위로 소거 동작을 수행한다.

- [0101] 실시예에 따라서, 하나의 스트링(113c)에 포함되는 두 개의 스트링 선택 트랜지스터들은 하나의 스트링 선택 라인에 연결되고 하나의 스트링에 포함되는 두 개의 접지 선택 트랜지스터들은 하나의 접지 선택 라인에 연결되도록 구현될 수도 있다. 또한, 실시예에 따라서, 하나의 스트링은 하나의 스트링 선택 트랜지스터 및 하나의 접지 선택 트랜지스터를 포함하여 구현될 수도 있다.

- [0102] 도 14는 도 2의 비휘발성 메모리 시스템에 포함되는 맵핑 메모리의 분할 방법의 일 예를 나타내는 도면이다.

- [0103] 도 14를 참조하면, 버퍼 메모리(600)는 복수의 버퍼 영역들(BP1~BPk)로 분할될 수 있다. 복수의 버퍼 영역들 (BP1~BPk)에는 유저 데이터가 저장될 수 있다. 복수의 버퍼 영역들(BP1~BPk)의 각각의 사이즈는 비휘발성 메모리 장치 및 메모리 콘트롤러 사이에서 전송되는 데이터 유닛의 사이즈와 동일할 수 있다. 결과적으로, 도 3의 맵핑 메모리(500)의 분할된 맵핑 메모리 영역들(MMR1~MMRn)의 각각의 사이즈 및 도 14의 버퍼 메모리(600)의 분할된 버퍼 영역들(BP1~BPk)의 사이즈는 상기 데이터 유닛의 사이즈로 동일할 수 있다.

- [0104] 이와 같은, 사이즈를 일원화한 방식의 메모리 운용을 통해 맵핑 메모리(500)의 적어도 일부를 버퍼 메모리(600), 즉 캐싱 메모리로 이용할 수 있다.

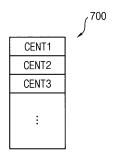

- [0105] 도 15a 및 15b는 본 발명의 실시예들에 따른 비휘발성 메모리 시스템의 동작 방법에 이용되는 캐싱 테이블의 일 실시예를 나타내는 도면들이다.

- [0106] 도 15a에는 버퍼 메모리(600) 및 맵핑 메모리(500)가 물리적으로 분리되는 경우에, 버퍼 메모리(600) 및 맵핑 메모리(500)에 저장된 유저 데이터의 캐싱 정보를 저장하는 통합 캐싱 테이블(700)이 도시되어 있고, 도 15b에는 상응하는 캐싱 엔트리의 일 예가 도시되어 있다.

- [0107] 도 15a를 참조하면, 통합 캐싱 테이블(700)은 맵핑 메모리(500)의 맵핑 메모리 영역들 중에서 데이터 맵핑 메모리 영역 또는 버퍼 메모리(600)의 버퍼 영역에 저장된 유저 데이터에 상응하는 캐싱 정보를 포함하는 복수의 통합 캐싱 엔트리들(CENT1, CENT2, CENT3)을 포함한다. 통합 캐싱 엔트리들(CENT1, CENT2, CENT3)의 개수는 데이터 맵핑 메모리 영역 및 버퍼 영역에 저장된 유저 데이터의 양에 따라서 가변될 수 있다.

- [0108] 도 15b를 참조하면, 통합 캐싱 테이블(700)에 저장되는 각각의 통합 캐싱 엔트리(CENTi)는 메모리 지정 필드 (MB), 논리적 어드레스(LAi), 논리적 어드레스(LAi)에 상응하는 유저 테이터의 어드레스 및 기타 값들(ETC)을 포함할 수 있다. 논리적 어드레스(LAi)에 상응하는 유저 테이터의 어드레스는 맵핑 메모리 영역의 어드레스 (MRAi) 또는 버퍼 영역의 어드레스(BRAi)일 수 있다. 메모리 지정 필드(MB)는 저장된 유저 테이터의 어드레스가 맵핑 메모리 영역의 어드레스(MRAi)인 경우에는 제1 값을 갖고 버퍼 영역의 어드레스(BRAi)인 경우에는 제2 값을 가질 수 있다. 기타 값들(ETC)은 통합 캐싱 엔트리(CENTi)의 유효 여부를 나타내는 값 등을 포함할 수 있다. 버퍼 메모리(600)가 생략되거나 맵핑 메모리(500)에 병합된 경우에는 메모리 지정 필드(MB)는 생략될 수 있다.

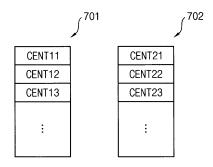

- [0109] 도 16a 및 16b는 본 발명의 실시예들에 따른 비휘발성 메모리 시스템의 동작 방법에 이용되는 캐싱 테이블의 다른 실시예를 나타내는 도면들이다.

- [0110] 도 16a에는 버퍼 메모리(600) 및 맵핑 메모리(500)가 물리적으로 분리되는 경우에 버퍼 메모리(600)에 저장된 캐싱 정보를 저장하는 메인 캐싱 테이블(701) 및 맵핑 메모리(500)에 저장된 유저 데이터의 캐싱 정보를 서브 캐싱 테이블(702)이 도시되어 있고, 도 16b에는 상응하는 캐싱 엔트리의 일 예가 도시되어 있다.

- [0111] 도 16a를 참조하면, 메인 캐싱 테이블(701)은 버퍼 메모리(600)의 버퍼 영역에 저장된 유저 데이터에 상응하는 캐싱 정보를 포함하는 복수의 메인 캐싱 엔트리들(CEN11, CEN12, CEN13)을 포함하고, 서브 캐싱 테이블(702)은 맵핑 메모리(500)의 맵핑 메모리 영역들 중에서 데이터 맵핑 메모리 영역에 저장된 유저 데이터에 상응하는 캐싱 정보를 포함하는 복수의 서브 캐싱 엔트리들(CEN21, CEN22, CEN23)을 포함한다. 메인 캐싱 엔트리들(CEN11, CEN12, CEN13) 및 서브 캐싱 엔트리들(CEN21, CEN22, CEN23)의 개수는 버퍼 영역 및 데이터 맵핑 메모리 영역에 저장된 유저 데이터의 양에 따라서 가변될 수 있다.

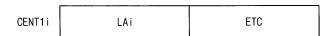

- [0112] 도 16b를 참조하면, 메인 캐싱 테이블(701)에 저장되는 각각의 메인 캐싱 엔트리(CENT1i)는 버퍼 영역에 저장된 유저 데이터에 상응하는 논리적 어드레스(LAi) 및 기타 값들(ETC)을 포함할 수 있다. 이 경우, 메인 캐싱 엔트리(MENT1i)의 인텍스(i) 자체가 유저 데이터가 저장된 버퍼 영역의 어드레스를 나타내고 상기 버퍼 영역의 어드레스는 논리적 어드레스(LAi)에 맵핑된다. 상기 버퍼 영역의 어드레스는 버퍼 메모리의 시작 주소 및 메인 캐싱 엔트리의 사이즈에 해당하는 오프셋 값 등을 이용하여 계산될 수 있다. 기타 값들(ETC)은 메인 캐싱 엔트리

(CENT1i)의 유효 여부를 나타내는 값 등을 포함할 수 있다.

- [0113] 서브 캐싱 테이블(702)에 저장되는 각각의 서브 캐싱 엔트리(CENT2j)는 유저 데이터가 저장된 데이터 맵핑 메모리 영역의 어드레스(MRAj) 및 상기 데이터 맵핑 메모리 영역에 저장된 유저 데이터에 상응하는 상기 논리적 어드레스(LAj) 및 기타 값들(ETC)을 포함할 수 있다. 이 경우, 논리적 어드레스(LA2j)는 맵핑 메모리 영역의 어드레스(MRAj)에 맵핑된다. 기타 값들(ETC)은 서브 캐싱 엔트리(CENT2j)의 유효 여부를 나타내는 값 등을 포함할 수 있다.

- [0114] 메모리 콘트롤러는 메인 캐싱 테이블(701)을 기초하여 버퍼 메모리(600)를 L1 캐시로 사용하고 서브 캐싱 테이블(702)에 기초하여 맵핑 메모리(500)를 L2 캐시로 사용할 수 있다. 다시 말해, 메모리 콘트롤러는 먼저 메인 캐싱 테이블(701)을 검색하고, 메인 캐싱 테이블(701)에 호스트 장치로부터의 논리적 어드레스에 상응하는 캐싱 정보가 없는 경우에만 서브 캐싱 테이블(702)을 검색할 수 있다.

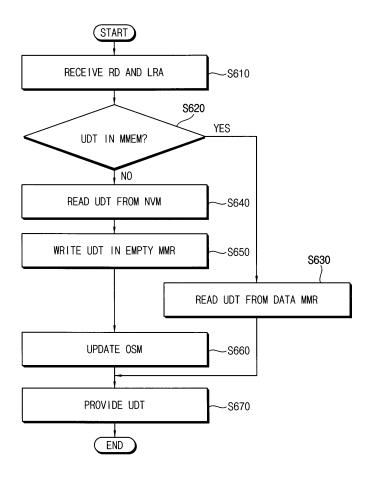

- [0115] 도 17은 본 발명의 실시예들에 따른 비휘발성 메모리 시스템의 독출 방법을 나타내는 순서도이다.

- [0116] 도 17을 참조하면, 독출 동작을 위해, 메모리 콘트롤러는 호스트 장치로부터 독출 명령(RD) 및 논리적 독출 어드레스(LRA)를 수신한다(S610).

- [0117] 논리적 독출 어드레스(LRA)에 상응하는 유저 데이터(UDT)가 맵핑 메모리(MMEM)의 데이터 맵핑 메모리 영역에 저장되어 있지 않은 경우(S620: NO), 메모리 콘트롤러는 비휘발성 메모리 장치로부터 논리적 독출 어드레스(LRA)에 상응하는 유저 데이터(UDT)를 독출한다(S640).

- [0118] 맵핑 메모리는 독출된 유저 데이터(UDT)를 빈 상태의 맵핑 메모리 영역(EMPTY MMR)에 저장하고(S650), 점유 상태 매니저(OSM)의 상응하는 상태 표시 영역의 값을 갱신한다(S660). 상태 표시 영역의 값의 갱신은 도 6 내지 9를 참조하여 설명한 바와 같다. 메모리 콘트롤러는 독출된 유저 데이터(UDT)를 호스트 장치로 제공한다(670).

- [0119] 논리적 독출 어드레스(LRA)에 상응하는 유저 데이터(UDT)가 맵핑 메모리(MMEM)의 데이터 맵핑 메모리 영역에 저장되어 있는 경우(S620: YES), 메모리 콘트롤러가 비휘발성 메모리 장치를 액세스할 필요 없이, 메모리 콘트롤러는 유저 데이터(UDT)를 매핑 메모리의 데이터 매핑 메모리 영역(DATA MMR)로부터 독출하고(S630), 독출된 유저 데이터(UDT)를 호스트 장치로 제공한다(670).

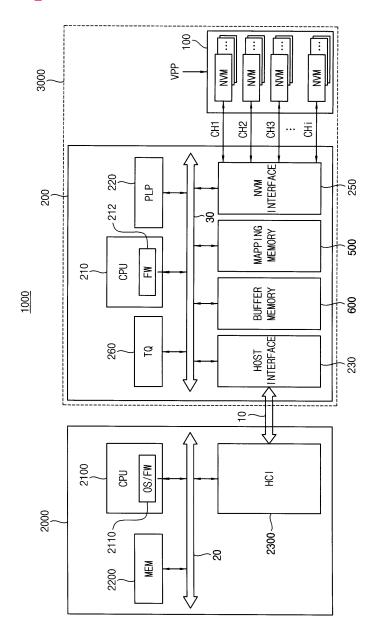

- [0120] 도 18은 본 발명의 실시예들에 따른 비휘발성 메모리 시스템의 기입 방법을 나타내는 순서도이다.

- [0121] 도 18을 참조하면, 기입 동작을 위해, 호스트 장치로부터 기입 명령(WR), 논리적 기입 어드레스(LWA) 및 기입 데이터(WDT)를 수신한다(S710).

- [0122] 논리적 기입 어드레스(LWA)에 상응하는 유저 데이터(UDT)가 맵핑 메모리(MMEM)의 데이터 맵핑 메모리 영역 (DMMR)에 저장되어 있지 않은 경우(S720: NO), 기입 데이터(WDT)를 빈 상태의 맵핑 메모리 영역(EMPTY MMR)에 저장하고(S740), 점유 상태 매니저(OSM)의 상응하는 상태 표시 영역의 값을 갱신한다(S750). 상태 표시 영역의 값의 갱신은 도 6 내지 9를 참조하여 설명한 바와 같다. 메모리 콘트롤러는 기입 데이터(WDT)를 비휘발성 메모리 장치로 제공한다(760).

- [0123] 논리적 기입 어드레스(LWA)에 상응하는 유저 데이터(UDT)가 맵핑 메모리(MMEM)의 데이터 맵핑 메모리 영역 (DMMR)에 저장되어 있는 경우(S720: YES), 맵핑 메모리는 기입 데이터(WDT)를 데이터 맵핑 메모리 영역(DMMR)에 덮어쓰기하고(S730), 메모리 콘트롤러는 기입 데이터(WDT)를 비휘발성 메모리 장치로 제공한다(760).

- [0124] 도 10, 17 및 18을 참조하여 설명한 바와 같이, 맵핑 메모리의 새로운 맵핑 메모리 영역에 맵핑 데이터를 저장하는 하거나 유저 데이터를 저장하는 경우에는 점유 상태 매니저의 값을 갱신할 수 있다. 또한, 맵핑 메모리에 저장된 맵핑 데이터 또는 유저 데이터를 폐기하는 경우에도 점유 상태 매니저의 값을 갱신할 수 있다. 이와 같은 점유 상태 매니저의 갱신을 통하여 본 발명의 실시예들에 따른 비휘발성 메모리 시스템의 동작 방법을 효율적으로수행할 수 있다.

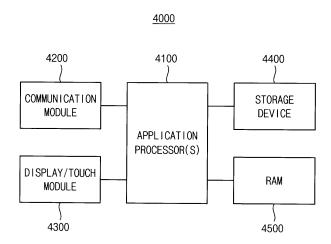

- [0125] 도 19는 본 발명의 실시예들에 따른 모바일 장치를 나타내는 블록도이다.

- [0126] 도 19를 참조하면, 모바일 장치(4000)는 어플리케이션 프로세서(4100), 통신 모듈(4200), 디스플레이/터치 모듈(4300), 저장 장치(4400), 및 모바일 램(4500)을 포함한다.

- [0127] 어플리케이션 프로세서(4100)는 모바일 장치(4000)의 전반적인 동작을 제어한다. 어플리케이션 프로세서(4100)는 인터넷 브라우저, 게임, 동영상 등을 제공하는 어플리케이션들을 실행할 수 있다. 통신 모듈(4200)은 외부와

의 유선 통신 및/또는 무선 통신을 제어하도록 구현될 수 있다. 디스플레이/터치 모듈(4300)은 어플리케이션 프로세서(4100)에서 처리된 데이터를 디스플레이 하거나, 터치 패널로부터 데이터를 입력 받도록 구현될 수 있다. 저장 장치(4400)는 유저 데이터를 저장하도록 구현될 수 있다.

- [0128] 저장 장치(4400)는 임베디드 멀티미디어 카드(eMMC, embedded multimedia card), 솔리드 스테이트 드라이브 (SSD, solid state drive), 유니버셜 플래시 스토리지(UFS, universal flash storage) 장치일 수 있다. 저장 장치(4400)는 전술한 바와 같이 본 발명의 실시예들에 따른 맵핑 데이터 및 유저 데이터의 효율적인 캐싱을 수 행할 수 있다.

- [0129] 모바일 램(4500)은 모바일 장치(4000)의 처리 동작 시 필요한 데이터를 임시로 저장하도록 구현될 수 있다. 예를 들어, 모바일 램(4500)은 DDR SDRAM, LPDDR SDRAM, GDDR SDRAM, RDRAM 등과 같은 동적 랜덤 액세스 메모리일 수 있다. 모바일 램(4500)은 전술한 맵핑 메모리및/또는 버퍼 메모리를 포함할 수 있다.

- [0130] 이상 설명한 바와 같이, 본 발명의 실시예들에 따른 비휘발성 메모리 시스템 및 상기 비휘발성 메모리 시스템의 동작 방법은 맵핑 메모리의 일부를 캐시 메모리로 이용함으로써 점유 면적의 증가 없이 비휘발성 메모리 시스템의 성능을 향상시킬 수 있다.

### 산업상 이용가능성

- [0131] 본 발명의 실시예들은 임의의 전자 장치 및 이를 포함하는 시스템에 유용하게 이용될 수 있다. 특히 본 발명의 실시예들은 메모리 카드, 솔리드 스테이트 드라이브(Solid State Drive; SSD), 임베디드 멀티미디어 카드(eMMC, embedded multimedia card), 컴퓨터(computer), 노트북(laptop), 핸드폰(cellular phone), 스마트폰(smart phone), MP3 플레이어, 피디에이(Personal Digital Assistants; PDA), 피엠피(Portable Multimedia Player; PMP), 디지털 TV, 디지털 카메라, 포터블 게임 콘솔(portable game console), 네비게이션(navigation) 기기, 웨어러블(wearable) 기기, IoT(internet of things;) 기기, IoE(internet of everything:) 기기, e-북(e-book), VR(virtual reality) 기기, AR(augmented reality) 기기 등과 같은 전자 기기에 더욱 유용하게 적용될 수 있다.

- [0132] 상기에서는 본 발명이 바람직한 실시예를 참조하여 설명하였지만, 해당 기술분야의 숙련된 당업자는 하기의 특 허청구범위에 기재된 본 발명의 사상 및 영역으로부터 벗어나지 않는 범위 내에서 본 발명을 다양하게 수정 및 변경시킬 수 있음을 이해할 것이다.

### 도면

## 도면5a

| MENTij | PAij | ETC |

|--------|------|-----|

|--------|------|-----|

## 도면5b

## 도면6

| SR16                                   | 0 | SR16                                   | 10                                       |

|----------------------------------------|---|----------------------------------------|------------------------------------------|

| SR15                                   | 0 | SR15                                   | 10                                       |

| SR14                                   | 0 | SR14                                   | 10                                       |

| SR13                                   | 0 | SR13                                   | 01                                       |

| SR9 SR10 SR11 SR12 SR13 SR14 SR15 SR16 | 0 | SR9 SR10 SR11 SR12 SR13 SR14 SR15 SR16 | 01                                       |

| SR11                                   | 0 | SR11                                   | 10                                       |

| SR10                                   | 0 | SR10                                   | 10                                       |

| SR9                                    | 0 | SR9                                    | 00                                       |

| SR8                                    | 0 | SR8                                    | 00                                       |

| SR7                                    | 0 | SR7                                    | 00                                       |

| SR6                                    | 0 | SR6                                    | 11 11 11 11 00 00 00 00 01 01 01 01 01 0 |

| SR5                                    | 1 | SR5                                    | 11                                       |

| SR4                                    | 1 | SR4                                    | 1                                        |

| SR3                                    | 1 | SR3                                    | 1                                        |

| SR2                                    | 1 | SR2                                    | 11                                       |

| SR1                                    | 1 | SR1                                    | 1                                        |

| 401a                                   |   | 401b                                   |                                          |

MDT:MAPPING DATA :OMMR UDT:USER DATA EMT:EMPTY :UMMR

| SR16                                   | 0 | SR16                                   | 01                   |

|----------------------------------------|---|----------------------------------------|----------------------|

| SR15                                   | 0 | SR15                                   | 10                   |

| SR14                                   | 0 | SR14                                   | 10                   |

| SR13                                   | 0 | SR13                                   | 10                   |

| SR9 SR10 SR11 SR12 SR13 SR14 SR15 SR16 | 0 | SR9 SR10 SR11 SR12 SR13 SR14 SR15 SR16 | 01 01 01             |

| SR11                                   | 0 | SR11                                   | 01                   |

| SR10                                   | 0 | SR10                                   | 11 00                |

| SR9                                    | 1 | SR9                                    | 11                   |

| SR8                                    | - | SR8                                    | 1                    |

| SR7                                    | 1 | SR7                                    | 11                   |

| SR6                                    | 1 | SR6                                    | 11 11 11 11 11 11 11 |

| SR5                                    | 1 | SR5                                    | =                    |

| SR4                                    | 1 | SR4                                    | Ξ                    |

| SR3                                    | 1 | SR3                                    | Ξ                    |

| SR2                                    | 1 | SR2                                    | 11                   |

| SR1                                    | - | SR1                                    | 11                   |

| 402a                                   |   | 402b                                   |                      |

# 도면13a

<u>110a</u>

# 도면13b

# 도면13c

# 도면15a

## 도면15b

| CENTI MB LAI MRAI OR BRAI ETC |

|-------------------------------|

|-------------------------------|

# 도면16a

# 도면16b

도면18