(19) **日本国特許庁(JP)**

# (12) 公表特許公報(A)

(11)特許出願公表番号

特表2015-510277 (P2015-510277A)

(43) 公表日 平成27年4月2日 (2015. 4. 2)

(51) Int.Cl.

FI

テーマコード (参考)

HO1S 5/022 (2006.01)

HO1S 5/022

5F173

## 審査請求 未請求 予備審査請求 未請求 (全 16 頁)

(21) 出願番号 特願2014-559986 (P2014-559986) (86) (22) 出願日 平成25年2月27日 (2013.2.27) (85) 翻訳文提出日 平成26年10月8日 (2014.10.8)

(86) 国際出願番号PCT/US2013/027987(87) 国際公開番号W02013/130580

(87) 国際公開日 平成25年9月6日 (2013.9.6)

(31) 優先権主張番号 13/411,275

(32) 優先日 平成24年3月2日 (2012.3.2)

(33) 優先権主張国 米国(US)

(71) 出願人 512086149

エクセリタス カナダ, インコーポレイテ

ッド

カナダ国, ケベック州 ジェイ7ヴィ 8 ピー7, ヴォードルイユードリオン, ダン

バリー ロード 22001

(74)代理人 100079108

弁理士 稲葉 良幸

(74) 代理人 100109346

弁理士 大貫 敏史

(74)代理人 100117189

弁理士 江口 昭彦

(74)代理人 100134120

弁理士 内藤 和彦

最終頁に続く

(54) 【発明の名称】 基板上で成形されたカプセル化くぼみを有する半導体レーザチップパッケージ及びこれを形成するための方法

## (57)【要約】

## 【課題】

【解決手段】積層リードレスキャリアパッケージは半導体チップを有し、このチップは、これを支持する基板におけるくぼみ領域の縁部に実装されている。基板は、複数の導電層及び誘電層と、光電子チップに結合されたワイヤボンドと、基板の上面の上に位置付けられたワイヤボンドパッドと、を有する。カプセル化封止は、レーザチップ、ワイヤボンド、及びくぼみ領域を含む基板の上面の少なくとも一部を覆う。カプセル化封止は光学的に透明な石英材料である。パッケージはサイドルッカー及び/又はトップルッカーとして実装されるように構成されている。

【選択図】 図1

#### 【特許請求の範囲】

## 【請求項1】

積層リードレスキャリアパッケージであって、

半導体レーザチップと、

前記半導体レーザチップを支持する基板であって、積層された複数の導電層及び誘電層と、前記基板の縁部にくぼんで配置された縁部くぼみ領域と、を備え、前記縁部くぼみ領域に隣接して前記半導体レーザチップが実装される、基板と、

前記基板の上面の上に位置付けられたワイヤボンドパッドと、

前記半導体レーザチップ及び前記ワイヤボンドパッドに結合されたワイヤボンドと、

前記半導体レーザチップ、前記縁部くぼみ領域、前記ワイヤボンド、及び前記基板の前記上面の少なくとも一部を覆うカプセル化封止であって、成形材料であるカプセル化封止と、

を備える、積層リードレスキャリアパッケージ。

## 【請求項2】

前記半導体レーザチップが端面発光レーザである、請求項 1 に記載の積層リードレスキャリアパッケージ。

## 【請求項3】

前記積層リードレスキャリアパッケージが、プリント回路基板上にサイドルッカー構成で実装されるように構成され、前記半導体レーザチップのアクティブエリアが前記プリント回路基板に垂直である、請求項2に記載の積層リードレスキャリアパッケージ。

【請求項4】

前記積層リードレスキャリアパッケージが、プリント回路基板上にトップルッカー構成で実装されるように構成され、前記半導体レーザチップのアクティブエリアが前記プリント回路基板に平行である、請求項2に記載の積層リードレスキャリアパッケージ。

#### 【請求項5】

前記複数の導電層及び誘電層が、下部導電層と、上部導電層と、前記上部及び下部導電層間の誘電層と、を備える、請求項1に記載の積層リードレスキャリアパッケージ。

#### 【請求項6】

前記上部導電層と前記下部導電層との間の電気的接続及び熱導管を与える複数の導電バイアを更に備える、請求項5に記載の積層リードレスキャリアパッケージ。

【請求項7】

前記成形材料が光学的に透明である、請求項1に記載の積層リードレスキャリアパッケージ。

## 【請求項8】

積層リードレスキャリアパッケージであって、

半導体レーザチップと、

前記半導体レーザチップを支持する基板であって、積層された複数の導電層及び誘電層と、前記基板の縁部におけるくぼみ内に配置された縁部くぼみ領域と、を備え、前記縁部くぼみ領域に隣接して前記半導体レーザチップが実装される、基板と、

前記基板の上面の上に位置付けられたワイヤボンドパッドと、

前記光電子チップ及び前記ワイヤボンドパッドに結合されたワイヤボンドと、

前記光電子チップ、前記ワイヤボンド、及び前記基板の前記上面の少なくとも一部を覆うカプセル化封止であって、成形材料であるカプセル化封止と、

を備え、前記積層リードレスキャリアパッケージが、前記光電子チップのアクティブエリアがプリント回路基板に垂直である前記プリント回路基板上のサイドルッカー構成、及び前記光電子チップの前記アクティブエリアがプリント回路基板に平行である前記プリント回路基板上のトップルッカー構成から成る群からの構成で実装されるように構成されている、積層リードレスキャリアパッケージ。

## 【請求項9】

複数の積層リードレス半導体レーザキャリアパッケージを製造するための方法であって

10

20

30

40

基板を準備するステップであって、

前記基板に複数のくぼみ領域を形成することと、

上部導電層と、下部導電層と、前記上部及び下部導電層間の誘電層と、を積層することであって、前記上部導電層が、ダイ取り付けパッド、ワイヤボンドパッド、及び2つのスロットバイアを備える、ことと、

を備える、ステップと、

前記ダイ取り付けパッドにエポキシ接着剤を塗布するステップと、

前記ダイ取り付けパッド上に半導体レーザチップを搭載するステップと、

ワイヤボンドを用いて前記ワイヤボンドパッドに前記半導体レーザチップをワイヤボン ディングするステップと、

成形材料を成形して、前記複数のくぼみ領域を充填すると共に前記光電子チップ、前記ワイヤボンド、及び前記基板の上面の少なくとも一部を覆うカプセル化封止を形成するステップと、

前記基板を個別の積層リードレスキャリアパッケージにダイシングするステップと、 を備える、方法。

## 【請求項10】

前記基板を準備するステップが、前記上部導電層と前記下部導電層との間の電気的接続及び熱導管を与える複数の導電バイアを準備するステップを更に備える、請求項9に記載の方法。

#### 【請求項11】

前記基板を準備するステップが、前記上部導電層をプリント回路基板上の実装パッドにはんだ付けするための前記上部導電層上の複数のスロットバイアを設けることを更に備える、請求項9に記載の方法。

#### 【請求項12】

前記成形材料を成形するステップが、前記ワイヤボンド又は前記半導体レーザチップに高い応力を与えない、請求項9に記載の方法。

#### 【請求項13】

前記成形材料を成形するステップが、前記カプセル化封止の上面を平坦な表面として成形することを更に備える、請求項9に記載の方法。

### 【請求項14】

前記成形材料を成形するステップが、サイドルッカーとして実装された場合に前記半導体レーザパッケージを安定化させるための基部を成形することを更に備える、請求項9に記載の方法。

## 【請求項15】

前記複数のくぼみ領域を充填する前記成形材料を研磨するステップを更に備える、請求項9に記載の方法。

## 【請求項16】

前記複数のくぼみ領域が少なくとも1つの行に配置され、前記ダイシングの完了前に前記複数のくぼみ領域が前記少なくとも1つの行に配置されている間に前記研磨が実行される、請求項15に記載の方法。

【発明の詳細な説明】

## 【技術分野】

## [0001]

本発明は回路コンポーネントに関し、更に特定すれば半導体レーザチップに関する。

#### 【背景技術】

## [0002]

表面実装技術(SMT:surface mount technology)は、電子回路を構築するために用いられるものであり、プリント回路基板(PCB)の表面上に直接コンポーネント(表面実装コンポーネント/SMC)が搭載される。そのように生成された電子デバイスは表面

20

10

30

40

実装部品(SMD:surface mount device)と呼ばれる。SMTは、回路基板のホール内にワイヤリードを挿入してコンポーネントを装着するスルーホール技術構築方法の大部分に取って代わっている。

#### [0003]

SMTコンポーネントは通常、スルーホール・コンポーネントに比べ、リードが小さいか又はリードを全く有しないので小型である。SMTは、コンポーネントのボディ上に、様々な形式の短いピン又はリード、平坦なコンタクト、はんだボール(BGA)の行列、又は終端を有する場合がある。

## [0004]

端面発光レーザ(edge emitting laser)は、実装表面に対して直角な方向に極めて急 速に広がるビームを有する。端面発光レーザは、メインドライバ基板に対して垂直にレー ザを方向付けるリードを有するパッケージ内に搭載することができる。パッケージは、パ ッケージベースのリードフレーム又は基台の縁部に配置されたレーザを保護するためのウ ィンドウキャップ又はカプセル化封止(encapsulation)を有しなければならない。メイ ンドライバ基板上に直接、又はPCB、セラミックもしくは他の基板とすることができメ インドライバ基板上に搭載される二次基板上等、大きい平坦な表面上に実装された場合、 ビームの少なくとも一部が表面と交差することがある。この制約を克服するため、端面発 光 レ ー ザ は 、 多 く の 場 合 ド ラ イ バ 基 板 又 は 二 次 基 板 の 縁 部 に 搭 載 さ れ 、 レ ー ザ の 縁 部 が こ れらの基板の縁部に隣接するか又はほぼ隣接するので、ビームが基板の外側の領域に広が るようになっている。かかる構成はいくつかの欠点を有する。例えば、レーザ面は典型的 に、 様々な 感 度 の 中 で も と り わ け 汚 染 及 び 湿 度 に 対 す る 感 度 が 高 く 、 基 板 の 縁 部 に 近 接 す ると面の脆弱性が高くなる恐れがある。更に、基板の縁部にレーザを位置付ける必要性の ために基板設計の柔軟性が制限され、例えば積層リードレスキャリア(LLC:laminate leadless carrier)等のチップキャリアのようないくつかのパッケージングの選択肢が 実用不可能になることがある。積層リードレスキャリアは、プリント回路基板に接触する 平坦な金属パッドを用いる。パッケージの外部に延出するピンは存在せず、プリント回路 基板上に直接実装することができる。積層リードレスキャリアは、積層された多層の導電 層及び誘電層を含む。

## [0005]

SMTは、製造及び回路レイアウトにおいて利点を有するが、SMTレーザでは、半導体端面発光レーザチップの制約によって問題が生じる。表面実装パッケージの縁部に半導体レーザチップを位置付けることに関するロジスティックな問題の他に、放熱に関する検討事項が表面実装特性と相反することがある。特に、SMTでは一般に、半導体レーザチップによって発生した熱を、例えばヒートシンク又は対流法を用いて更に放散することができるパッケージの表面へと伝えることが難しい。

## 【発明の概要】

【発明が解決しようとする課題】

## [0006]

従って、上述の欠点のいくつか又は全てを克服することが業界において求められている

## 【課題を解決するための手段】

#### [0007]

本発明の実施形態は、基板上に成形された半導体レーザ及びこれを製造するための方法を提供する。簡単に述べると、本発明は、積層リードレスキャリアパッケージを対象とする。パッケージは、半導体レーザチップ及びこの半導体レーザチップを支持する基板を含む。基板は、積層された複数の導電層及び誘電層と、基板の縁部にくぼんで配置された縁部くぼみ領域と、を有し、縁部くぼみ領域に隣接して半導体レーザチップが実装される。パッケージは更に、基板の上面の上に位置付けられたワイヤボンドパッドと、半導体レーザチップ及びワイヤボンドパッドに結合されたワイヤボンドと、半導体レーザチップ、縁部くぼみ領域、ワイヤボンド、及び基板の上面の少なくとも一部を覆うカプセル化封止で

10

20

30

40

あって、成形材料であるカプセル化封止と、を含む。

## [0008]

半導体レーザチップは端面発光レーザとすることができる。積層リードレスキャリアパッケージは、プリント回路基板上にサイドルッカー構成で実装されるように構成することができ、半導体レーザチップのアクティブエリアはプリント回路基板に垂直である。又は、積層リードレスキャリアパッケージは、プリント回路基板上にトップルッカー構成で実装されるように構成することができ、半導体レーザチップのアクティブエリアはプリント回路基板に平行である。複数の導電層及び誘電層は、下部導電層と、上部導電層と、上部導電層と、下部導電層と、上部導電層と下部導電層との間の電気的接続及び熱導管を与える複数の導電バイアを含むことができる。成形材料は光学的に透明である。

## [0009]

アーキテクチャにおいて簡単に述べると、本発明の第2の態様は、半導体レーザチップ及びこの半導体レーザチップを支持する基板を含む積層リードレスキャリアパッケージを対象とする。基板は、積層された複数の導電層及び誘電層と、基板の縁部におけるくぼみ内に配置された縁部くぼみ領域と、を有し、縁部くぼみ領域に隣接して半導体レーザチップが実装される。パッケージは、基板の上面の上に位置付けられたワイヤボンドパッドと、光電子チップ及びワイヤボンドパッドに結合されたワイヤボンドと、光電子チップ、ワイヤボンド、及び基板の上面の少なくとも一部を覆うカプセル化封止と、を含む。カプセル化封止は成形材料である。積層リードレスキャリアパッケージは、光電子チップのアクティブエリアがプリント回路基板に垂直であるプリント回路基板に平行であるプリント回路基板上のトップルッカー(a top-looker)構成から成る群からの構成で実装されるように構成されている。

#### [0010]

簡単に述べると、本発明の第3の態様は、複数の積層リードレス半導体レーザキャリアパッケージを製造するための方法を対象とする。この方法は、基板を準備するステップを含み、このステップは、基板に複数のくぼみ領域を形成することと、上部導電層と、下部導電層と、上部及び下部導電層間の誘電層と、を積層することであって、上部導電層が、ダイ取り付けパッド、ワイヤボンドパッド、及び2つのスロットバイアを含むことと、を含む。他のステップは、ダイ取り付けパッドにエポキシ接着剤を塗布するステップと、をイ取り付けパッド上に半導体レーザチップを搭載するステップと、ワイヤボンドを用いてワイヤボンドパッドに半導体レーザチップをワイヤボンディングするステップと、成形材料を成形して、複数のくぼみ領域を充填すると共に光電子チップ、ワイヤボンド、及び基板の上面の少なくとも一部を覆うカプセル化封止を形成するステップと、基板を個別の積層リードレスキャリアパッケージにダイシングするステップと、を含む。

## [0011]

第3の態様は、上部導電層と下部導電層との間の電気的接続及び熱導管を与える複数の 導電バイアを準備することを更に含むことができる。また、第3の態様は、複数のくぼみ 領域を充填する成形材料を研磨するステップを更に含むことができる。複数のくぼみ領域 は少なくとも1つの行に配置することができ、ダイシングの完了前に複数のくぼみ領域が 行に配置されている間に研磨を実行することができる。

## [0012]

本発明の他のシステム、方法、及び特性は、以下の図面及び詳細な説明を考察することで当業者には明らかとなろう。全てのそのようなシステム、方法、及び特性は、この説明に含まれ、本発明の範囲内であり、添付図面によって保護されることが意図される。

#### [0013]

添付図面は本発明をいっそう理解するために含まれ、本明細書に組み込まれてその一部を構成する。図面は記載と共に本発明の実施形態を例示して、本発明の原理を説明するように機能する。

10

20

30

#### 【図面の簡単な説明】

[0014]

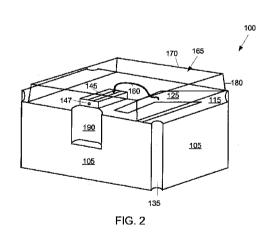

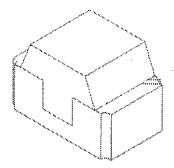

- 【 図 1 】 本 発 明 に 従 っ た 例 示 的 な 半 導 体 レ ー ザ パ ッ ケ ー ジ の 概 略 図 で あ る 。

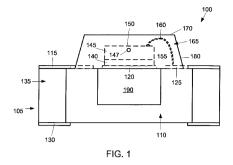

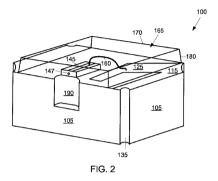

- 【図2】例示的な半導体レーザパッケージの概略斜視図である。

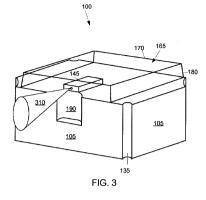

- 【 図 3 】 レーザビームの 経 路 を 示 す 例 示 的 な 半 導 体 レー ザ パ ッ ケ ー ジ の 概 略 斜 視 図 で あ る 。

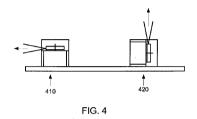

- 【図4】プリント回路基板上にサイドルッカー又はトップルッカーとして実装された例示 的な半導体レーザパッケージを示す。

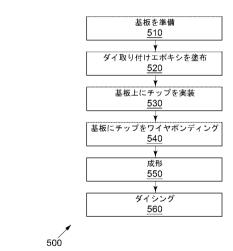

- 【図 5 】本出願に記載する半導体レーザパッケージを製造するための例示的なマトリックス組立プロセスのフローチャートである。

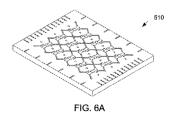

- 【図6A】例示的なマトリックス組立プロセスの異なる段階中の1枚の基板を示す。

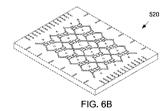

- 【 図 6 B 】 例 示 的 な マ ト リ ッ ク ス 組 立 プ ロ セ ス の 異 な る 段 階 中 の 1 枚 の 基 板 を 示 す 。

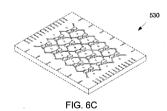

- 【 図 6 C 】 例 示 的 な マ ト リ ッ ク ス 組 立 プ ロ セ ス の 異 な る 段 階 中 の 1 枚 の 基 板 を 示 す 。

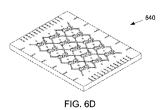

- 【図 6 D】例示的なマトリックス組立プロセスの異なる段階中の 1 枚の基板を示す。

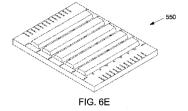

- 【図6E】例示的なマトリックス組立プロセスの異なる段階中の1枚の基板を示す。

- 【 図 6 F 】 例 示 的 な マ ト リ ッ ク ス 組 立 プ ロ セ ス の 異 な る 段 階 中 の 1 枚 の 基 板 を 示 す 。

- 【図 6 G 】図 5 の例示的なマトリックス組立プロセスの製品である個別の光電子パッケージを示す。

【発明を実施するための形態】

## [0015]

これより本発明の実施形態について詳細に参照する。添付図面にその例が図示されている。可能な場合、図面及び記載において同一の参照番号を用いて同一又は同様の部分を示す。

#### [0016]

半導体レーザパッケージを製造するための装置及び方法の例示的な実施形態を提示する。レーザチップは、基板の縁部から引っ込んだくぼみ領域に隣接して実装される。レーザチップは、レーザチップ面がくぼみ領域を見下ろすような向きに配置される。複数の導電バイアが、基板の上部導電層と下部導電層との間の電気的接続及び/又は熱導管(thermal conduit)を与える。オーバーモールド光エポキシ材料が、基板の上面の少なくとも一部、レーザチップ、及びくぼみ領域をカプセル化する。半導体レーザパッケージはプリント回路基板上に実装されて、レーザビームがプリント回路基板に対して平行であるか又はレーザビームがプリント回路基板に対して垂直であるようになっている。

#### [0017]

図1は、本発明に従った半導体レーザパッケージ100の例示的な実施形態の断面図を示す。半導体レーザパッケージ100は、基板105、チップ145、及びカプセル化封止165を含む。

## [0018]

チップ145は、端面発光レーザ等を含むいずれかのレーザデバイスとすることができる。例えばチップ145は、IV族(シリコン)半導体及びIII - V族半導体等のいずれかの適切な材料で形成されたレーザチップとすることができる。レーザチップ145は、エピタキシャルウェハ(EPI)又はリーチスルー(reach-through)構造等のいずれかの構造を有することができる。

## [0019]

半導体レーザパッケージ100は、LLCとすることができる。リードレスキャリアは、プリント回路基板に接触する平坦な金属パッドを用いる。パッケージの外部に延出するピンは存在せず、プリント回路基板上に直接実装することができる。積層チップキャリアは、積層された多層の導電層及び誘電層を含む。一例において積層リードレスキャリアは、以下で詳述するように、誘電層を間に挟んだ上部導電層及び下部導電層を含む。設計の複雑さに応じて、積層チップキャリアは、多くの異なる導電層及び/又は誘電層を有する場合がある。

10

20

30

-

40

10

20

30

40

50

### [0020]

半導体レーザパッケージ100は、チップ145を支持するための基板105を含む。基板105は、いずれかの薄膜セラミック基板、厚膜セラミック基板、及び異なる種類のプリント回路基板(PCB)とすることができるが、これに限られない。1つの好適な実施形態において、半導体レーザパッケージ100はリードフレームを含まない。基板105は、誘電層110の上及び下にそれぞれ設けられた上部導電層115と下部導電層130と、上部及び下部導電層115及び130間の電気的接続及び/又は熱導管を与える複数の導電バイア135と、を含むことができる。導電バイア135は、トップルッカー又はサイドルッカーデバイス方位のいずれかで用いることができる(これら2つの方位については以下で詳述する)。導電バイア135は、電気及び/又は熱伝達のための導管として機能することができる。かかる熱伝達は、レーザチップによって発生した熱を拡散させるために重要である。これがない場合はチップの性能及び信頼性が損なわれることがわかっている。

## [0021]

上部導電層115は、基板105上にチップ145を取り付けるためのダイ取り付けパッド120を含む。具体的には、接着層140を用いてチップ145を基板105の上のダイ取り付けパッド120に取り付けることができる。また、上部導電層115は、ワイヤボンド160を取り付けるためのワイヤボンドパッド125を含む。ワイヤボンド160は、チップ145と上部導電層115との間の電気的接続を与える。この実施形態では単一のワイヤボンド160を用いるが、代替的な実施形態では適宜2つ以上のワイヤボンドを用いても差し支えない。各導電バイア135は、小さい丸い開口等、異なるスロット形状の小さい開口とすることができる。

## [ 0 0 2 2 ]

図2に示すように、基板 1 0 5 はくぼみ領域 1 9 0 を有し、ここでは基板材料が除去されて基板 1 0 5 の縁部に後退領域(pull-back area)を形成している。好ましくは、図2に示すように、チップ 1 4 5 のレーザ発光縁部がくぼみ領域 1 9 0 に隣接するか又はほぼ隣接するようにチップ 1 4 5 を実装する。くぼみ領域の縁部にチップ 1 4 5 を位置付けることによって、光ビーム 3 1 0 (図3)は、基板 1 0 5 と交差することなくチップ 1 4 5 から外側に向かって投射することができる。同様に、光ビームプロファイルを歪ませる可能性のある基板反射なしで全ての光ビームをレーザチップ 1 4 5 の面から出力することができるように、くぼみ領域 1 9 0 によって、光ビーム 3 1 0 (図3)を基板 1 0 5 と交差させることなく、パッケージ 1 0 0 の縁部から引っ込んだ位置にレーザチップ 1 4 5 を位置付けることができる。

## [ 0 0 2 3 ]

カプセル化封止165は、チップ145、ワイヤボンド160、くぼみ領域190、及び基板105又は基板105の一部をカプセル化して保護するために設けられる。 1 つセル化する。 第 面発光レーザチップは、典型的に高電圧で動作するのできる。 カプセル化封止165電圧で動作するのできる。 カプセル化封止165はイオン含有量が少なく耐湿性が高い成形材料とすることができる。 カプセル化 カカル は光エポキシ材料とすることができる。いくつかの例示的なまにでは、カカルとすることができる。いくかの例示的ななく、カカルとはカル化対ボンド160に保護を与える成形材料とすることができる。いくカリングスは APTEK6100・1A が別として例えば APTEK6100・1A が別として例えば APTEK6100・1A を使用可能である。 APTEK6100・1A / Bは、2 成分、無充填、無色透明にあり、光電子パッケージにおけるLEDチップのカプセル化用に設計されている。 であり、光電子パッケージにおけるLEDチップのカンズ部として機能して、優れた透明度及び光透過率を示すことができる。

#### [0024]

図1に示すカプセル化封止165は、基板105の上面の一部のみを覆うが、カプセル

化封止165は、最終用途による必要に応じて基板105の上面全体を覆うことも可能である。カプセル化封止165の側面180は、垂直であるか、傾斜するか、又はカプセル化封止の異なる部分において異なる角度で傾斜することができる。カプセル化封止165の上面170(光界面)は、平坦面として、又は円筒形、球形、非球形、ドーム形、環状レンズ等として成形することができる。

#### [0025]

カプセル化封止165内にレーザチップ145の縁部を収容する利点は、例えば製造後の部品の組み立て又は処理中及びPCB上での組み立ての前に、レーザチップ145のアクティブエリア又は面147を保護することである。くぼみ領域190が存在しない基板105の縁部にチップ145が実装された場合、レーザチップ145の面147はカプセル化封止165によって保護されない。

[0026]

図3は半導体レーザパッケージ100の簡略化した図であり、半導体レーザパッケージ100内のチップ145からのレーザビーム310の投射を示す。ビーム310は、投射された方向に発散角で急速に広がる。くぼみ190が存在しない場合、及びくぼみ190が位置する領域に基板材料が充填されている場合は、ビーム310は基板105と交差する。かかる交差はいくつかの理由で問題となる。第1に、この交差はビーム310の経路を遮って、送信されるはずであったエネルギの一部を吸収する。第2に、基板105はビーム310から吸収されたエネルギによって加熱される。第3に、この交差領域はビームの一部を反射して望ましくない結果を生じる恐れがある。

[0027]

くぼみ領域190のサイズは、チップ145がくぼみ領域190に隣接して又はほぼ隣接して位置付けられるようなものにすることができる。くぼみ領域190は、最終用途により必要に応じて様々な幅及び奥行きを有することができる。例えばビームが広く拡散する用途では、ビームがもっと狭く拡散する用途よりも奥行きの深いくぼみ領域190を有することができる。この実施形態におけるくぼみ領域190は矩形として図示するが、くぼみ領域190は、例えば半円形、扇形、又は他の形状のような他の形状であっても差し支えない。図3に示すように、くぼみ領域190は基板105の上面と交差し、基板105の底面と交差するまでは延出しない場合がある。しかしながら、くぼみ領域190が基板105の底面まで延出する半導体レーザパッケージ100の実施形態であっても差し支えない。

[0028]

図4に示すように、半導体レーザパッケージ100はサイドルッカー410又はトップルッカー420としてプリント回路基板上に実装することができる。一般に、この向きは、プリント回路基板表面に対するレーザチップのアクティブエリアからの光の方向又は放出に基づいて選択することができる。例えばレーザのアクティブエリアからの放出がプリント回路基板に垂直である場合、トップルッカーの向き420を用いることができる。この構成においては、レーザチップのアクティブエリアはプリント回路基板に対して垂直である。これに対して、光がプリント回路基板に平行である場合、サイドルッカー構成410を用いることができる。この構成では、光電子チップのアクティブエリアはプリント回路基板に平行である。

[0029]

図2に示す例示的な実施形態は単一のチップ145及び単一のくぼみ領域190を有するが、代替的な実施形態において2つ以上のチップ145を有することも差し支えない。2つ以上のチップ145は、例えば平行ビームを投射するように位置合わせし、単一のくぼみ領域190を共有することができる。又は、基板105の単一の縁部に沿って多数のくぼみ領域190を形成することも可能である。同様に、半導体レーザパッケージ100は、基板105の2つ以上の縁部に沿ってくぼみ領域190を有して、異なる方向に向けられたビーム310を投射する多数のチップ145を収容することができる。いくつかの実施形態においては、2つ以上のレーザチップ、ワイヤボンド、又はタイボンドパッドを

10

20

30

40

単一の半導体レーザパッケージに配置可能であることは認められよう。

## [0030]

熱に関する検討事項

基板設計では、多種多様な熱伝導性材料が考えられる。更に、バイア135は、レーザチップ145が発生した熱を表面実装パッケージの縁部に伝達する熱導管を与え、熱はその縁部で、当業者に周知の方法によって半導体レーザパッケージから拡散させることができる。例えば銅から成るバイア135は、レーザチップから最終PCAまでの熱インピーダンスを低下させるような熱伝導特性を有することができる。

## [0031]

実装基板は、例えば25 のような閾値温度未満に確実に維持することが有利である場合がある。温度を閾値温度未満に維持することは、例えばチップ145を基板105に取り付ける導電性接着剤の熱特性によって支援することができる。導電性接着剤140は例えば導電性エポキシ又ははんだとすることができる。

## [0032]

方法

図5は、本出願において記載する半導体レーザパッケージを製造するためのマトリックス組立プロセス500の例示的な実施形態のフローチャートである。フローチャートにおけるいかなるプロセス記述又はブロックも、プロセスにおける具体的な論理機能を実施するための1つ以上の命令を含むコードのモジュール、セグメント、一部、又はステップを表すものとして理解されることに留意すべきである。本発明の範囲内に含まれる代替的な実施では、関与する機能性に応じて、機能の実行は、実質的に同時又は逆の順序を含めて、図示又は記載する順序通りでなくても可能である。これは当業者には理解されよう。

## [ 0 0 3 3 ]

マトリックス組立プロセスは、低コスト、大量、小型、及びSMTコンパチブルの製品を求める市場の需要に応えるように設計される。プロック510で示すように、基板内にくぼみ領域を形成することを含めて、当技術分野において既知の方法によって基板を準備する。例えばウェットエッチング又はドライエッチングで基板をエッチングすることにはつて、レーザアブレーションによって、又は当業者に周知の他の方法によって、くぼみ領域を形成することができる。基板は、限定ではないが、薄膜セラミック基板、厚膜セラミック基板、及びいずれかの種類のプリント回路基板とすることができる。基板材料は、例えば耐熱範囲が約10W/ / m から100W/ / m である適切な熱特性を有しなければならない。プロック520で示すように、ダイ取り付けエポキシを塗布する。エポキシ接着剤を、分注、スタンピング、又は印刷手法によって塗布することができる。ダイ取り付けエポキシの代わりに、例えばはんだのような他の導電性及び熱伝導性媒体を使用可能であることに留意すべきである。

## [0034]

ブロック 5 3 0 で示すように、手作業で又は半自動もしくは自動ダイ取り付けマシンを用いて、基板にレーザチップを実装する。ブロック 5 4 0 で示すように、手作業で又は半自動もしくは自動ダイ取り付けマシンを用いて、基板にワイヤボンドを加える。用途に応じて、ワイヤボンドは、アルミナ又は金等の異なる材料、直径が 0 . 7 ミル及び 1 ミル等の異なるサイズ、又はボール・ウェッジ及びウェッジ・ウェッジ等の異なる構成を用いる場合がある。ブロック 5 5 0 で示すように、成形によってカプセル化封止として基板に成形材料を加える。成形材料は液体として流した後に硬化させることができる。硬化の温度及び時間は成形材料に応じて異なり、その情報は典型的に材料データシートから得ることができる。ブロック 5 6 0 で示すように、基板を個別の半導体レーザパッケージにダイシングする。ダイシングは例えば、のこ刃又はレーザビームによって実行することができる

## [0035]

図6Aから図6Fは、上述の例示的なマトリックス組立プロセス500の異なる段階中の1枚の基板を示し、図6Gは例示的なマトリックス組立プロセスから得られた個別の半

10

20

30

40

10

20

30

導体レーザパッケージを示す。図6Aは、くぼみ領域の形成を含む準備を行った後の1枚の基板を示す。しかしながら、基板の残りを準備する前又は後にくぼみ領域を形成しても差し支えない。図6Bは、ダイ取り付けエポキシを塗布した後の組立品を示す。図6Cは、基板上にレーザチップを実装した後の組立品を示す。図6Dは、基板にワイヤボンドを加えた後の組立品を示す。図6Eは、基板に成形材料をカプセル化封止として加えた後の組立品を示す。図6Fは、個別の半導体レーザパッケージにダイシングした後の組立品を示す。1つの組立品は、2つ以上の材料が一体化されたものであり、1つのパッケージ又は複数のパッケージのアレイとすることができる。

## [0036]

プロセス 5 0 0 の前に、組立プロセスの一部として実行されるいずれかの数のプロセスがあり得ることは認められよう。例えば 1 つの前プロセスにおいて、基板に、チップを載せる空洞及び / 又は浮き出しを加工することができる。また、組立プロセスの一部としてプロセス 5 0 0 の後にいずれかの数のプロセスを実行することも可能である。例えば 1 つの後プロセスにおいて、ダイシングしたデバイスをマトリックス形態で又は個別に試験することができる。

## [0037]

プロセス 5 0 0 が追加のステップ及び / 又はサブステップを含み得ることは認められよう。例えば、図 6 Fに示すようにダイシングを開始した後であるがダイシングを完了する前に、LLCから光が発するカプセル化封止材の前面の研磨を行うことができる。例えば、多数のくぼみ領域の前面が複数の行又は帯に配置されている場合に研磨を実行可能であるので、1つの帯の多数のくぼみ領域を覆っているカプセル化封止材を最終ダイシング前に同時に研磨することができる。これは、最終ダイシング後に各くぼみ領域上のカプセル化封止材を個別に研磨するよりも効率的であり得る。

#### [0038]

まとめると、半導体レーザパッケージを製造するための装置及び方法のための例示的な実施形態を提示した。LLC SMD半導体レーザは、光コンポーネントの実装面積が小さく、機械的位置合わせが良好で、コンポーネントアレイ組立プロセスを通してコストが低く、レーザ光軸の向きにおいて柔軟性が高い。本発明の範囲又は精神から逸脱することなく、本発明の構造に様々な変更及び変形を実施可能であることは当業者には明らかであるう。前述のことに鑑み、本発明は、本発明の変更及び変形が以下の特許請求の範囲及びそれらの均等物の範囲内に該当するならば、それらを包含することが意図される。

# 【図1】

# 【図2】

# 【図3】

# 【図4】

# 【図5】

# 【図 6 B】

【図 6 C】

【図6D】

# 【図6A】

# 【図6E】

【図 6 F】

FIG. 6F

# 【図 6 G】

FIG. 6G

## International application No PCT/US2013/027987 A. CLASSIFICATION OF SUBJECT MATTER INV. H01S5/022 ADD. According to International Patent Classification (IPC) or to both national classification and IPC B. FIELDS SEARCHED Minimum documentation searched (classification system followed by classification symbols) H01S H01L Documentation searched other than minimum documentation to the extent that such documents are included in the fields searched Electronic data base consulted during the international search (name of data base and, where practicable, search terms used) EPO-Internal, WPI Data, INSPEC C. DOCUMENTS CONSIDERED TO BE RELEVANT Citation of document, with indication, where appropriate, of the relevant passages Relevant to claim No. JP S61 272987 A (HITACHI LTD) 3 December 1986 (1986-12-03) χ 1-16 abstract; figures 1-3 US 5 627 851 A (TAKAHASHI TAKASHI [JP]) 6 May 1997 (1997-05-06) abstract; figures 3,6 1-16 Х the whole document χ US 2004/233950 A1 (FURUKAWA YOSHIHIKO [JP] 1-16 ET AL) 25 November 2004 (2004-11-25) abstract; figure 1A JP S59 193083 A (HITACHI LTD) 1 November 1984 (1984-11-01) abstract; figure 2 χ 1-16 -/--X See patent family annex. X Further documents are listed in the continuation of Box C. Special categories of cited documents : "I" later document published after the international filing date or priority date and not in conflict with the application but cited to understand the principle or theory underlying the invention "A" document defining the general state of the art which is not considered to be of particular relevance "E" earlier application or patent but published on or after the international filing date "X" document of particular relevance; the claimed invention cannot be considered novel or cannot be considered to involve an inventive step when the document is taken alone "V" document of particular relevance; the claimed invention cannot be considered to involve an inventive step when the document is combined with one or more other such documents, such combination being obvious to a person skilled in the art "L" document which may throw doubts on priority claim(s) or which is cited to establish the publication date of another citation or other special reason (as specified) "O" document referring to an oral disclosure, use, exhibition or other "P" document published prior to the international filing date but later than the priority date claimed "&" document member of the same patent family Date of the actual completion of the international search Date of mailing of the international search report 23/09/2013 13 August 2013 Name and mailing address of the ISA/ Authorized officer European Patent Office, P.B. 5818 Patentlaan 2 NL - 2280 HV Rijswijk Tel. (+31-70) 340-2040, Fax: (+31-70) 340-3016 Lendroit, Stéphane

(13)

INTERNATIONAL SEARCH REPORT

## **INTERNATIONAL SEARCH REPORT**

International application No PCT/US2013/027987

|         | Continuation). DOCUMENTS CONSIDERED TO BE RELEVANT                                                                                               |                       |  |  |  |  |

|---------|--------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|--|--|--|--|

| tegory" | Citation of document, with indication, where appropriate, of the relevant passages                                                               | Relevant to olaim No. |  |  |  |  |

|         | WO 96/00918 A1 (BRITISH TELECOMM [GB];<br>COLLINS JOHN VINCENT [GB]; PAYNE ROGER<br>ALYN [GB] 11 January 1996 (1996-01-11)<br>abstract; figure 7 | 1-16                  |  |  |  |  |

| , P     | US 2012/213239 A1 (JU JIN HAN [CA] ET AL)<br>23 August 2012 (2012-08-23)<br>the whole document                                                   | 1-16                  |  |  |  |  |

|         | US 2011/079801 A1 (ZHANG XIANZHU [CA] ET AL) 7 April 2011 (2011-04-07) the whole document                                                        | 1-16                  |  |  |  |  |

|         |                                                                                                                                                  |                       |  |  |  |  |

|         |                                                                                                                                                  |                       |  |  |  |  |

|         |                                                                                                                                                  |                       |  |  |  |  |

|         |                                                                                                                                                  |                       |  |  |  |  |

|         |                                                                                                                                                  |                       |  |  |  |  |

|         |                                                                                                                                                  |                       |  |  |  |  |

Form PCT/ISA/210 (continuation of second sheet) (April 2005)

## INTERNATIONAL SEARCH REPORT

Information on patent family members

International application No PCT/US2013/027987

|                                           | information on patent family members |                     |                                                                                        | PCT/US                            | 2013/027987                                                                      |

|-------------------------------------------|--------------------------------------|---------------------|----------------------------------------------------------------------------------------|-----------------------------------|----------------------------------------------------------------------------------|

| Patent document<br>cited in search report |                                      | Publication<br>date | Patent family<br>member(s)                                                             |                                   | Publication<br>date                                                              |

| JP S61272987                              | A                                    | 03-12-1986          | NONE                                                                                   |                                   |                                                                                  |

| US <b>5627851</b>                         | Α                                    | 06-05-1997          | NONE                                                                                   |                                   |                                                                                  |

| US 2004233950                             | A1                                   | 25-11-2004          | CN 150950<br>JP 394547<br>US 200423395<br>WO 0210386<br>WO 0210386                     | 9 B2<br>0 A1<br>5 A1              | 30-06-2004<br>18-07-2007<br>25-11-2004<br>27-12-2002<br>27-12-2002               |

| JP S <b>59</b> 193083                     | Α                                    | 01-11-1984          | NONE                                                                                   |                                   |                                                                                  |

| WO 9600918                                | A1                                   | 11-01-1996          | CA 219309<br>DE 6951435<br>DE 6951435<br>JP H1050543<br>US 585269<br>WO 960091         | 8 D1<br>8 T2<br>3 A<br>6 A        | 11-01-1996<br>10-02-2006<br>24-08-2006<br>26-05-1998<br>22-12-1998<br>11-01-1996 |

| US 2012213239                             | A1                                   | 23-08-2012          | NONE                                                                                   |                                   |                                                                                  |

| US 2011079801                             | A1                                   | 07-04-2011          | CN 10263035 EP 248393 JP 201350698 KR 2012010137 TW 20121652 US 201107980 WO 201103950 | 9 A1<br>5 A<br>4 A<br>3 A<br>1 A1 | 08-08-2012<br>08-08-2012<br>28-02-2013<br>13-09-2012<br>16-04-2013<br>07-04-2011 |

Form PCT/ISA/210 (patent family annex) (April 2005)

## フロントページの続き

(81)指定国 AP(BW,GH,GM,KE,LR,LS,MW,MZ,NA,RW,SD,SL,SZ,TZ,UG,ZM,ZW),EA(AM,AZ,BY,KG,KZ,RU,TJ,TM),EP(AL,AT,BE,BG,CH,CY,CZ,DE,DK,EE,ES,FI,FR,GB,GR,HR,HU,IE,IS,IT,LT,LU,LV,MC,MK,MT,NL,NO,PL,PT,RO,RS,SE,SI,SK,SM,TR),OA(BF,BJ,CF,CG,CI,CM,GA,GN,GQ,GW,ML,MR,NE,SN,TD,TG),AE,AG,AL,AM,AO,AT,AU,AZ,BA,BB,BG,BH,BN,BR,BW,BY,BZ,CA,CH,CL,CN,CO,CR,CU,CZ,DE,DK,DM,DO,DZ,EC,EE,EG,ES,FI,GB,GD,GE,GH,GM,GT,HN,HR,HU,ID,IL,IN,IS,JP,KE,KG,KM,KN,KP,KR,KZ,LA,LC,LK,LR,LS,LT,LU,LY,MA,MD,ME,MG,MK,MN,MW,MX,MY,MZ,NA,NG,NI,NO,NZ,OM,PA,PE,PG,PH,PL,PT,QA,RO,RS,RU,RW,SC,SD,SE,SG,SK,SL,SM,ST,SV,SY,TH,TJ,TM,TN,TR,TT,TZ,UA,UG,US,UZ,VC

(72)発明者 ジュ,ジン,ハン

カナダ国,ケベック州 エイチ9ジェイ 3ワイ6,カークランド,リュ オーデュボン 6

(72)発明者 ブルマン,ロバート

カナダ国,ケベック州 ジェイ7ブイ 8ビー8,ヴォードルイユ-ドリオン,カルティエ 61 ナンバー2

(72)発明者 デレオン,ジェリー

フィリピン国, ラグナ, 4027, カランバ シティ, カンリューバン, アヴィダ ヴィレッジ ニューヴァリ, ロト4, ブロック 40, フェーズ 1

F ターム(参考) 5F173 MB02 MC12 MD04 MD16 MD23 MD27 MD83 ME06 ME22 ME32 ME42