# (12) UK Patent Application (19) GB (11) 2 187 889 (13) A

(43) Application published 16 Sep 1987

(21) Application No 8705079

(22) Date of filing 4 Mar 1987

(30) Priority data

(31) 839848

(32) 14 Mar 1986

(33) US

(71) Applicant Motorola Inc.

(Incorporated in USA-Delaware),

1303 East Algonquin Road, Schaumburg, Illinois 60196, **United States of America**

(72) Inventors Clarence A. Lund, Richard R. Hamzik

(74) Agent and/or Address for Service C. S. Hirsz, Patent & Licensing Operations—Europe, Jays Close, Viables Ind. Est., Basingstoke, Hants. RG22 4PD

(51) INT CL4 H01L 21/82 29/78

(52) Domestic classification (Edition I) H1K 11B4 11D 1CA 3E1M 3E5A 3P5 4C14 4H1A 4H1C 4H3A 9D1 9E 9N2 CAX MWA

(56) Documents cited

1594562 US GB 1502668 GB

4435896

(58) Field of search

Selected US specifications from IPC sub-class H01L

### (54) Providing contact separation in silicided devices

(57) Platinum or tungsten silicide contacts (17a-e) are provided to source (152), drain (151), gate (15b) and tub (12a) regions of a dielectrically isolated MOSFET (10). A "false" gate (15a) is used to provide automatic self-aligned separation of the source-drain contact (152) and the tub contact (16). An intermetallic forming material (17) is uniformly coated over the doped substrate (11) on which the gate (15b) and false gate (15a) region have been formed which upon heating reacts with the substrate (11) and the polysilicon gates (15a—b) to form intermetallic regions (17a-e).

Doping of source (152) drain (151) and tub contact (16) areas is carried out by implantation of P-type impurity using the gate and false gate as masks and masking out the tub contact area, followed by implantation of n-type impurity at a lower dose than the p-type implantation in all three areas, (Figs. 3 and 4).

7 18/ 889 /

## 3/4

# 4/4

FIG. 11

GB 2 187 889 A

#### **SPECIFICATION**

### Means and Method for Providing Contact Separation in Silicided Devices

5 Background of the Invention Field of the Invention

This invention relates in general to means and methods for providing closely spaced contacts in semiconductor devices and, more particularly, to 10 means and methods for providing closely spaced contacts in semiconductor devices which employ intermetallic contact regions.

### Background Art

It is desirable in the semiconductor art to be able to use intermetallic contact regions. These intermetallic contact regions can provide very low resistance ohmic contacts or, alternatively, can provide high quality Schottky contacts.

Intermetallics are generally formed by reacting one or more metallic elements with the semiconductor of choice. For example, in the case of silicon semiconductors, a wide variety of metals such as Pt, Mo, W, Ni, Ti, and Ta are but a few of the 25 many silicide forming materials which are known. Platinum is a particularly convenient intermetallic

forming element and is widely used. A need that often arises in connection with high density integrated circuit structures employing 30 dielectrically isolated semiconductor tubs, is to simultaneousy make contact to the device regions within the tub and the tub itself. In the prior art, when silicides or silicide forming materials were employed as a part of the contact structured, 35 additional masking steps were required in order to make separate, non-shorting contacts to the tub and

the device regions contained therein. These extra masking steps add to the cost and complexity of the devices. In addition, each masking step requires that 40 provision be made in the device layout for the necessary mask-to-mask alignment tolerance. This

increases the area occupied for a given circuit function and further increases the cost. Thus, a need continues to exist for improved processes and

45 structures in dielectrically isolated circuits employing intermetallic contacts which utilize minimum surface area and which can be fabricated with the fewest possible masking operations.

Accordingly, it is an objective of the present 50 invention to provide an improved means and method for forming intermetallic contacts to semiconductor regions wherein separate masking operations for contacting the N and P regions are

55 means and method for contacting semiconductor devices employing intermetallic contacts wherein N and P-type contacts may be brought as close as the minimum layout line width without requiring any 60 provision for alignment tolerance.

It is also desirable to provide an improved means and method for forming intermetallic contacts to semiconductor devices wherein the contacts to the N and P regions are self-aligned.

#### Summary of the Invention

and advantages is achieved through the present invention wherein there is provided a means and 70 method for forming semiconductor devices, comprising: providing a semiconductor substrate having a first surface; forming on the first surface at least first and second dopant blocking regions having respectively first and second lateral

The attainment of the foregoing and other objects

75 dimensions, wherein the first and second dopant blocking regions are separated by a first region of the substrate, and wherein a second region of the substrate is separated from the first region of the substrate by the second blocking region; providing

80 a mask on the first surface which covers at least the second region of the substrate and which has an opening exposing at least the first region of the substrate; doping through this opening at least the first region of the substrate with a first dopant to a

85 first predetermined dopant concentration, without substantially doping the second region of the substrate; removing the mask and doping the first and second regions of the substrate with a second dopant different than the first dopant, to a second

90 concentration less than the first concentration; depositing an intermetallic forming layer simultaneously on the first and second regions of the substrate; and heating the intermetallic forming layer for a time sufficient to produce an intermetallic 95 compound by reaction with the substrate.

Although generally useful, the means and method of the present invention are particularly well suited to the formation of MOS devices where the first blocking region is the gate of the MOS device, the first region of the substrate is the source and/or drain of the MOS device, and the second region of the substrate is the contact to the isolated tub in which the MOS device is being built. The second blocking region prevents the intermetallic forming 105 layer from shorting together the source (or drain) contact and the tub contact. The second blocking region or "false gate" is conveniently formed at the same time and in the same manner as the gate of the MOS device. A lateral dielectric isolation wall 110 can be provided surrounding the active device region to cut off lateral continuity with other

semiconductor areas. The second blocking region or "false gate" runs laterally across the tub between the isolation walls. 115 A particular feature of the present invention is that the source and drain contacts are self-aligned to the

gate and to each other, and to the tub contact. A further feature of the present invention is that no intermediate mask alignment steps are required to It is furthermore desirable to provide an improved 120 locate the tub contact region with respect to the source, drain, or gate. A further feature of the present invention is that the intermetallic forming layer may be deposited simultaneously on the source, drain, gate, and tub contact regions without

125 shorting them together. Sidewall oxides are desirably used on the first and second blocking regions in order to increase the lateral separation of the intermetallic regions.

An additional feature of the present invention is 130 that the source (or drain) and tub contacts may be

65

<sup>2</sup> GB 2 187 889 A 2

brought extremely close together without shorting since the minimum separation is determined by the minimum line width layout rule being used. For example, the false gate can have the same lateral dimensions as the minimum active gate length.

The details of the present invention are more completely described in the figures and description which follow.

10 Brief Description of the Drawings

Figs. 1—10 show simplified schematic crosssectional elevation views of a portion of a semiconductor device fabricated according to the means and method of the present invention.

15 Fig. 11 shows a simplified schematic crosssectional plan view of the portion of the semiconductor device shown in Fig. 10, at a particular location.

20 Detailed Description of the Drawings

For purposes of explanation, the device structures and methods presented herein are described for the case of silicon-based semiconductor devices and silicide intermetallic layers. However, those of skill

- 25 in the art will understand that these means and methods apply to other semiconductor substrates and other intermetallic forming materials, and that the examples presented herein are shown merely as an aid to understanding and not intended to be

- 30 limiting. Other semiconductor materials and intermetallics may also be used.

In Figs. 1—11, unless otherwise noted, dielectric layers or regions are shown hatched, polycrystalline semiconductor regions are shown lightly stippled,

- 35 intermetallic regions are shown heavily stippled, and single crystal regions, mask layers, and metal regions are shown clear. Arrows are used to indicate the implantation of various dopant species, however, those of skill in the art will understand that

40 other doping methods could equally well be

- 40 other doping methods could equally well be applied.

Figs. 1—10 show, in simplified schematic crosssectional form, elevation views of a portion of a semiconductor device formed according to the

45 method of the present invention. The device structure illustrated is particularly suited to function as a MOS device having source, drain, and gate electrodes formed in a dielectrically isolated semiconductor tub to which a separate contact is

50 provided. For ease of understanding, particular combinations of semiconductor conductivity types are illustrated. However, those of skill in the art will

understand that different conductivity types could

also be used.

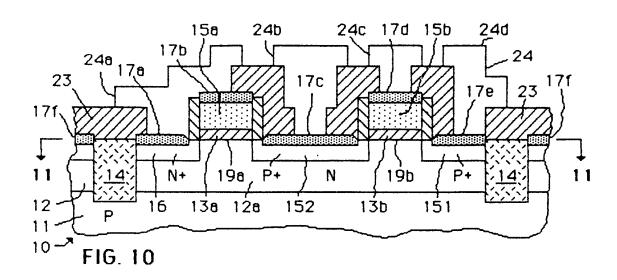

- 55 Fig. 1 shows semiconductor device portion 10 comprising P-type substrate 11 with surface layer or portion 12 in which have been formed dielectric isolation walls 14. Layer or portion 12 may be a separately formed epi-layer or merely the near

- surface region of substrate 11. For the purposes of this invention, layer or region 12 may be considered a part of substrate 11. N-type central region 12a has been provided within lateral isolation walls 14. Portions 12d of region 12 outside of isolation walls

14 may be doped N or P-type and may contain

devices similar to or different than those intended to be formed in portion 12a. Surface layer or portion 12 is covered by dielectric layer 13 and conductor layer 15. Conductor layer 15 is conveniently formed of

- 70 polycrystalline semiconductor material, e.g., polycrystalline silicon, but other conductive materials may also be used. Dielectric layer 13 is conveniently formed of silicon oxide or silicon nitride, but other dielectric materials may be used

- 75 provided that they are compatible with the underlying semiconductor material. Surface layer or portion 12, doped region 12a, lateral dielectric isolation walls 14, and layers 13 and 15 are formed by means well known in the art. Layer 15 is

- 80 conveniently about 0.1—1.0 microns thick with about 0.4 microns being typical. Layer 13 is conveniently about 0.01—1.0 microns thick with about 0.015 microns being typical where it is desired to use part of layer 13 as the gate of an MOS device.

85 Mask regions 30 are provided on layer 15. Photoresist is an example of a suitable material for mask region 30 but other material may also be used. Means for forming masking layers having particular open and protected regions are well known in the

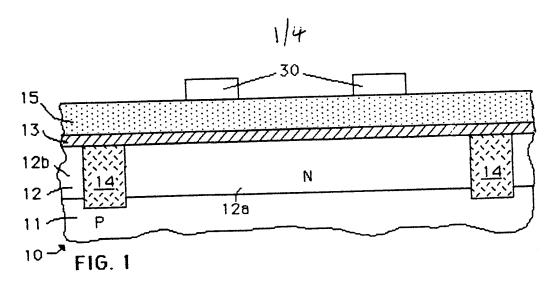

- 90 art. Layers 15 and 13 are etched through the openings in mask 30 so as to remove those portions of layers 13 and 15 not protected by mask 30. This leaves behind this structure illustrated in Fig. 2 wherein portions 13a—b and 15a—b remain on the 95 surface of semiconductor substrate 11—12. Mask 30

- 95 surface of semiconductor substrate 11—12. Mask 30 is then conveniently removed.

For the example given, conductor portion 15b and dielectric portion 13b can serve as the gate conductor and gate dielectric of an MOS transistor.

100 Conductor portion 15a and dielectric portion 13a,

- which may have the same lateral dimensions as gate 15b serve as a "false" gate to provide for separation of the contacts to tub 12a and the semiconductor device regions therein. For a small 105 MOS device suitable for use in VLSI circuits, regions

- 15a—b are typically about 0.5 microns in lateral extent and separated by, typically, 1.5—2.5 microns, with about 1.0—2.0 microns between regions 15a—b and isolation walls 14. These dimensions are 110 measured in the horizontal direction in Figs. 2—11.

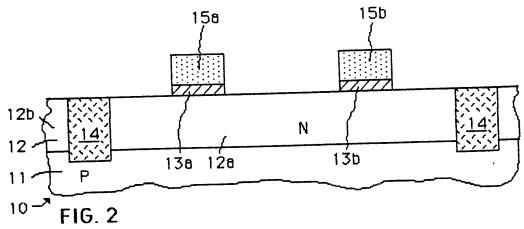

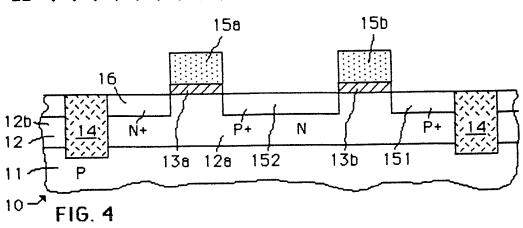

Source-drain regions 151, 152 and tub contact region 16 are provided as illustrated in Figs. 3—4. The steps illustrated in Figs. 3 and 4 may be performed in either order, that is, in the order shown 115 by Fig. 3 followed by Fig. 4 or in the order shown in Fig. 4, followed by the steps shown in Fig. 3. Those of skill in the art will understand how the order of these steps may be interchanged. For purposes of

further explanation herein, it is assumed that the 120 steps of Fig. 3 are performed first.

In Fig. 3, mask 20 having opening 20a is applied.

Opening 20a should encompass the desired location of source-drain regions 151, 152 on either side of gate region 15b. Mask 20 must cover region 161 in substrate 11—12 where the contact to tub 12a will subsequently be formed. Ions 21 are provided in Fig. 3 to dope regions 151—152. In the example shown wherein tub 12a is N-type, regions 151—152 are doped P-type. Polycrystalline semiconductor gate region 15b is doped at the same time, although this

3 GB 2 187 889 A 3

is not essential for the purposes of this invention.

Some portion of false gate 15 may also be doped but this is not essential. It will be noted that regions 151, 152, 15a, 15b, and 161 are all self-aligned. Mask opening 20a need not be precision aligned since it is only necessary that it cover region 161. Where substrate 11—12 is of silicon, boron is a typical P-type dopant impurity. Regions 151—152 are conveniently formed by implanting boron to a concentration of about 1×10<sup>15</sup> ions/cm<sup>2</sup> at an energy of about 30 keV. Other does and energies may also

be used. If ion implantation is used as a means for providing doped regions 151—152, the implant energy must be sufficiently low so as not to cause penetration of ions 21 through gate region 15b.

Those of skill in the art will understand how to choose the dose and energy to obtain the desired device characteristics. Alternatively, other doping techniques can also be used.

Any portion of mask 20 which remains after doping regions 151—152 is then removed. As shown in Fig. 4, dopant ions 22 are conveniently applied uniformly across substrate 11—12 so as to form N+ doped region 16 in portion 161 which had

been previously covered by mask 20. At the same time that N+ region 16 is being formed, ions 22 are also being introduced in regions 151, 152 and 15b. Accordingly, the dose of ions 22 must be smaller than the dopant concentration used to form regions

151—152 so as to not counter-dope these regions.

30 151—152 so as to not counter-dope these regions. Where substrate 11—12 is silicon, typical implant conditions for forming regions 151—152 and 16 are, boron implant doses in the range 5×10<sup>14</sup> to 1×10<sup>16</sup> ions/cm² for regions 151—152 and arsenic or

5 phosphorous ions implanted to a dose of a range 1×10<sup>14</sup> to 5×10<sup>15</sup> ions/cm<sup>2</sup> to form N+ region 16. Region 16 is typically doped to about one half or less of the concentration in P-region 151—152. The implant energy is selected to provide the desired

40 doping depth. Those of skill in the art will understand how to do this. For the lateral device dimensions illustrated herein, regions 151, 152 and 16 conveniently have a depth less than or equal to about 0.2 microns. Generally, it is desirable that the 45 junction depth of these regions be small compared

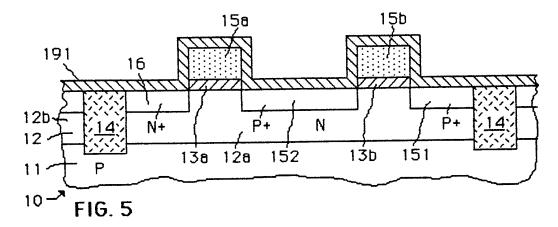

5 junction depth of these regions be small compared to the lateral dimensions of regions 15a—b, so that the side diffusion from regions 151, 152, and 16 is a small fraction of the lateral width of regions 15a—b. Doped substrate 11—12 and gate regions 15a—b

are then conveniently covered with thin dielectric layer 191 (Fig. 5). Dielectric layer 191 should conformally coat the surface since it is intended to be used to form lateral oxide spacers on either side of gates 15a—b. The thickness of layer 191 is chosen to provide the desired lateral oxide sidewall spacing. Layer 191 may be of any convenient dielectric material. Silicon dioxide and silicon nitride are examples of suitable dielectric materials.

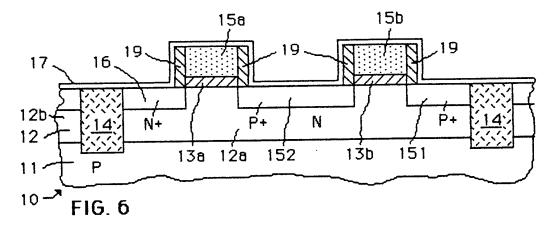

Layer 191 is then anisotropically etched so as to remove those portions of the layer which lie on the upper surface of substrate 11—12 and on the upper surface of gates 15a—b so that these upper surfaces are exposed. If the anisotropic etching process has a high vertical to horizontal etch ratio then the result of the anisotropic etching process will be to leave

sidewall oxide portions 19 (Fig. 6) in place after the upper surfaces of substrate 11—12 and gates 15a—b are exposed. Suitable anisotropic etching techniques are well known in the art. Layer 191 is 70 conveniently in the range of about 0.05—0.5 microns thick with about 0.1 microns being typical.

As shown in Fig. 6, the resulting structure is then covered with a thin intermetallic forming material. Platinum is an example of a material which is suitable for forming intermetallic compounds with silicon. Other materials are also known. When platinum is used, layer 17 is conveniently of a thickness in the range 0.01—0.1 microns with 0.03—0.06 microns being preferred and 0.05 microns being typical.

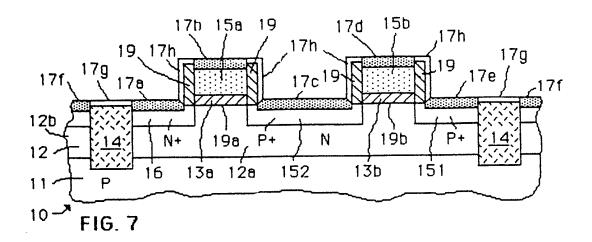

The structure shown in Fig. 6 is then heated to produce the structure shown in Fig. 7 wherein intermetallic forming layer 17 has reacted with the underlying semiconductor substrate 11—12 so as to 85 form intermetallic regions 17a, 17c, 17e, and 17f on substrate 11—12, and has also reacted with polycrystalline semiconductor regions 15a—b to form intermetallic region 17b and 17d. Portions 17g and 17h of layer 17 which are in contact with 90 dielectric isolation walls 14 and sidewall isolation regions 19 do not substantially react during this process.

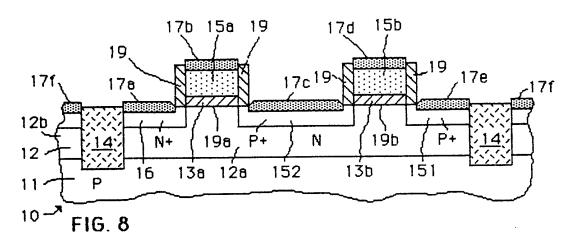

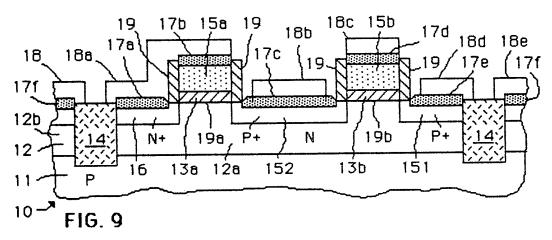

A convenient property associated with many intermetallic compounds, of which platinum silicide 95 is an example, is that their etch chemistry is significantly different than the etch chemistry of the original metal. This means that unreacted portions 17g—17h of layer 17 may be dissolved away, as shown in Fig. 8, while leaving intermetallic regions 17a—f substantially undisturbed. It may be seen by inspecting Fig. 8, that even though intermetallic forming layer 17 was applied as a continuous sheet over the entire device, and initially shorts all the device regions together, following the previously described reaction and etching steps, isolated intermetallic contacts have been formed on each of the device regions of interest. For example, regions 17c and 17e provide contacts to source-drain regions 151, 152, region 17d provides contact to 110 gate region 15b and region 17a provides tub contact 16. It will further be apparent, that false gate 15a prevents regions 152 and 16 from being shorted Fig. 9 illustrates the situation when conductor

layer 18 has been provided and, using the masking techniques (not shown) well known in the art, patterned to provide contact 18a to intermetallic regions 17a and 17b, contact 18b to intermetallic region 17c, contact 18c to intermetallic region 17d

and contact 18d to intermetallic region 17e.

Conductor regions 18e may also contact intermetallic regions 17f which are laterally exterior to isolation walls 14, but that is not essential to the present invention.

125 Region 19b aligned between source-drain regions

151—152 can serve as the channel of an MOS

transistor controlled by gate conductor 15b. The

channel length corresponds to the lateral separation

between regions 151—152, and the gate length

130 corresponds to the width of region 15a, measured

horizontally in the plane of Figs. 2—10. Portion 19a of substrate 12 between regions 152 and 16 may be prevented from acting as a parasitic transitor by

connecting false gate 15a to tub contact 16.

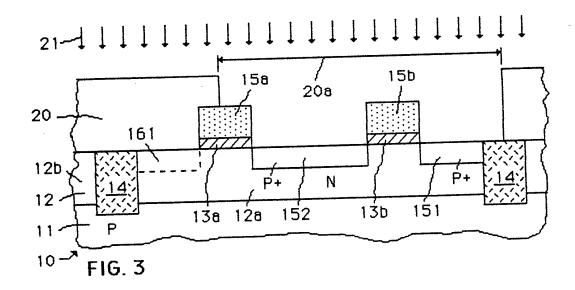

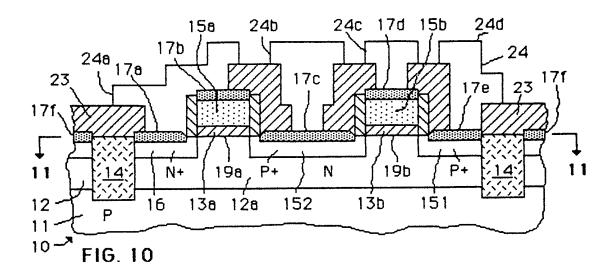

Fig. 10 illustrates an alternative embodiment in which dielectric layer 23 is applied over the structure of Fig. 8 and then patterned using means well

known in the art to provide contact holes prior to the application of a surface conductor layer. As shown 10 in Fig. 10, conductor layer 24 is then applied and patterned using means well known in the art to provide contact 24a to intermetallic regions 17a and 17d, contact 24d to intermetallic region 17c, contact 24c to intermetallic region 17d, and contact 24d to intermetallic region 17f exterior to dielectric isolation walls 14 may or may

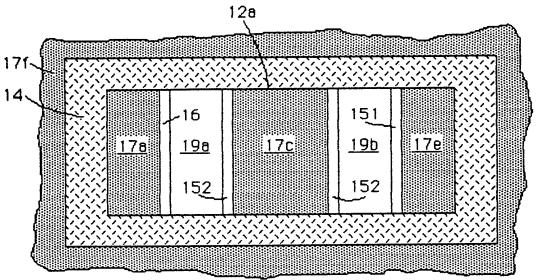

not be connected at the option of the user. Fig. 11 is a plan cross-sectional view of the device of Fig. 10 approximately at the level of the surface of 20 semiconductor substrate 11—12. Dielectric isolation wall 14 desirably has a closed shape so that tub 12a is laterally separated from the remainder of the device structure. It is convenient to have doped region 151 and intermetallic contact 17e, doped 25 region 152 and intermetallic contact 17c, doped region 16 and intermetallic contact 17a extend across the width of tub 12a from isolation wall to isolation wall, i.e., in the vertical direction in Fig. 11. Device channel 19b under active gate 15b is visible 30 in the right half of Fig. 11 and inactive region 19a under false gate 15a is visible in the left half of Fig. 11. It will be readily apparent from Figs. 10—11 that false gate 15a prevents doped regions 152 and 16

and intermetallic regions 17c and 17a from shorting

together. Further, since false gate 15a and active

gate 15b are fabricated at the same time, they both

can have minimum gate length, i.e., the lateral

dimension of regions 15a—b measured in the

horizontal direction in Figs. 10—11. Accordingly,

region 19a may be made as small as region 19b.

Also, no alignment tolerance is required in order to

Also, no alignment tolerance is required in order to place contact 16 in tub 12a while still avoiding shorts between contact 16 and region 152. Thus, the device may be built in a smaller area.

45 As those of skill in the art will appreciate, being

As those of skill in the art will appreciate, being able to make a separate low resistance contact (e.g., contact 17a, 16) to tub 12a is an important and convenient device feature. It is particularly useful where the device formed by regions 151, 152, 15b

and 19b is intended to act as a transmission gate, that is, a device in which none of the terminals is grounded. In this situation, it is essential that region 152 not be shorted to tub contact 16. Such floating devices are also extremely useful in memory

applications wherein it is desired to separately bias tub 12a with respect to channel 19b so as to be able to modulate the characteristics of the active device.

While the means and methods of the present invention have been illustrated for the case in which sidewall dielectric regions 19 have been included, they are not essential, and intermetallic forming layer 17 could equally well be placed directly upon substrate 11—12. In this case however, lateral isolation of, for example, intermetallic regions 17a and 17b is limited only to the thickness of dielectric

region 13a. Where dielectric region 13a is particularly thin, this may be insufficient.

In a further embodiment of the invention, regions 17a—f may be formed by selective deposition of a conductive material. As will be further explained, tungsten is an example of such a material. Fabrication proceeds as has already been described in connection with Figs. 1—6 through formation of side-wall dielectric regions 19. Silicon oxide is

75 preferably used to form regions 19. Then, rather than depositing layer 17 (Fig. 6), reacting layer 17 with the underlying semiconductor to form intermetallic regions 17a—f (Fig. 7), and etching away unreacted regions 17g—h (Fig. 8), conductor

80 regions 17a—f are formed by direct selective deposition, that is, deposition only on exposed semiconductor surfaces of regions 16, 151—152, and 15a—b, and not on side-wall oxide 19 or isolation walls 14. The structure of Fig. 8 is obtained directly by selective deposition of the conductive material without need for an intervening etching step. An intervening heating step may also not be necessary depending upon the desired amount of metal versus intermetallic desired in regions 17a—f.

90 Tungsten is an example of a conductor material known to selectively deposit on silicon and not on silicon oxide. The conditions necessary to obtain such selective deposition are well known in the art and are described for example by E. K. Broadbent in 95 "Selective Chemical Vapor Deposition of Tungsten", J. Electrochem. Soc., Vol. 131, #6, June 1984, page 1427. A portion of the deposition tungsten will react with underlying silicon regions 16, 151—152, and 15a—b. Unreacted tungsten will 100 also be present in regions 17a—f. Those of skill in the art will understand that the relative proportions of tungsten and tungsten silicide in regions 17a-f will depend upon the temperature and duration of heating during and/or after deposition. Compared to 105 silicon, both tungsten and tungsten silicide are highly conducting. Tungsten silicide is a known intermetallic. The surfaces of dielectric regions 19

and isolation walls 14 will remain substantially free of tungsten or tungsten silicide. Fabrication then

110 proceeds as described in connection with Figs.

9—10.

While the invented means and method has been

While the invented means and method has been illustrated in terms of silicon semiconductor substrates and polycrystalline silicon conductors,

115 those of skill in the art will understand that other semiconductor materials could be used for substrate 11—12 and other conductors could be used for layer 15 and regions 15a—b. Further, those of skill in the art will understand that the particular device regions labelled P-type or N-type may be interchanged or otherwise modified. Additionally, those of skill in the art will understand that other intermetallic forming materials besides platinum or tungsten may also be used, provided that they do not react with the dielectric regions from which they must ultimately be removed so as to avoid shorting,

must ultimately be removed so as to avoid shorting, or else react in such a way as to not provide a conductor layer on those regions. Also, other selectively depositing conductors could be used, such as for example, doped silicon. Further, those of

5

skill in the art will appreciate that even though a MOS device was illustrated by way of example in describing the invention and that particular examples were given for various thicknesses and dimensions, that other device configurations, thicknesses and dimensions could be equally well be used, and that the means and methods of the present invention apply whenever it is desired to simultaneously make self-aligned intermetallic 10 contacts to one or more active device regions and the semiconductor region or tub in which they are located, and that the false gate structure and method employed herein is equally applicable to such other device configurations. Accordingly, it is 15 intended to include all such variations in the claims which follow.

#### **CLAIMS**

A process for forming a semiconductor device,

comprising:

providing a substrate having a first surface; forming on said first surface at least first and second blocking regions having respectively first and second lateral dimensions, wherein said first and second blocking regions are separated by a first region of said substrate, and wherein a second region of said substrate is separated from said first region of said substrate by said blocking region;

providing a mask on said first surface and 30 extending at least partially onto said second blocking region, and having an opening exposing at least said first region of said substrate;

doping through said opening in said mask at least said first region of said substrate with a first dopant 35 to a first predetermined dopant concentration, without substantially doping said second region of said substrate;

removing said mask and doping said first and second regions of said substrate with a second dopant different than said first dopant to a second predetermined dopant concentration; and

depositing an intermetallic forming layer simultaneously on said first and second regions of said substrate.

- 45 2. The process of claim 1 wherein said second dopant concentration is less than said first dopant concentration.

- 3. The process of claim 1 further comprising prior to said depositing step, the step of forming sidewall

50 dielectric regions on lateral sides of said first and second blocking regions.

- 4. The process of claim 1 further comprising prior to said depositing step, the step of providing a lateral isolation wall circumscribing at least a

55 portion of the regions doped during said doping steps.

- The process in claim 1 further comprising providing a lateral isolation wall circumscribing the regions doped during said doping steps and

wherein at least said second blocking region between said first and second regions of said substrate extends laterally from one portion of said isolation wall to an opposed portion of said isolation wall.

- 65 6. The process of claim 1 further comprising after

said depositing step, the step of removing portions of said intermetallic forming layer which have not reacted to form an intermetallic with the material of said substrate.

- 70 7. The process of claim 1 further comprising during or after said depositing step, the step of heating said intermetallic forming layer to form an intermetallic compound with said substrate.

- 8. The process of claim 1 wherein said step of providing said mask comprises providing a mask having an opening exposing at least said first blocking region said first region of said substrate and a third region of said substrate laterally separated from said first region of said substrate by said first blocking region.

- 9. A process for forming a semiconductor device, comprising:

providing a substrate having a first surface; forming on said first surface at least first and second blocking regions having respectively first and second lateral dimensions, wherein said first and second blocking regions are separated by a first region of said substrate, and wherein a second region of said substrate is separated from said first region of said substrate by said blocking region;

doping said first and second regions of said substrate to a first predetermined dopant concentration;

providing a mask on said first surface covering at 95 least said second regions of said substrate, and having an opening exposing at least said first region of said substrate;

doping through said opening in said mask at least said first region of said substrate with a second 100 dopant to a second predetermined dopant concentration;

removing said mask; and selectively depositing a conductive layer simultaneously on said first and second regions of said substrate.

10. The process of claim 9 wherein said first dopant concentration exceeds said second dopant concentration.

11. The process of claim 10 wherein said second 110 dopant concentration exceeds said first dopant concentration.

12. An MOS device structure comprising: a semiconductor substrate;

a tub region located in said substrate;

115 a lateral isolation means substantially surrounding said tub region, wherein said tub region contains a source, drain, and tub contact; an active gate located above said substrate

an active gate located above said substrate between said source and drain; and

- 120 an inactive gate located above said substrate between one of said source or drain and said tub contact.

- 13. The device of claim 12 further comprising shorting means electrically connecting said inactivegate and said tub contact.

- 14. A semiconductor device structure comprising: a semiconductor substrate;

- a tub region located in said substrate; a lateral isolation means substantially surrounding said tub region, wherein said tub region contains

130

GB 2 187 889 A 6

- a first device region and a tub contact; and an electrically inactive conductor region located above said substrate between said first device region and

- 5 said tub contact and self-aligned therewith, and extending laterally across said tub region from one portion of said isolation means to another portion of

- said isolation means.

- 15. A process for forming a semiconductor device10 substantially as hereinbefore described with reference to the drawings.

- 16. A semiconductor device substantially as hereinbefore described with reference to the drawings.

Printed for Her Majesty's Stationery Office by Courier Press, Learnington Spa, 9/1987. Demand No. 8991685. Published by the Patent Office, 25 Southampton Buildings, London, WC2A 1AY, from which copies may be obtained.