#### (19) **日本国特許庁(JP)**

# (12) 公 開 特 許 公 報(A)

(11)特許出願公開番号

特開2017-224763 (P2017-224763A)

(43) 公開日 平成29年12月21日(2017, 12, 21)

(51) Int.Cl. HO1S 5/227 (2006.01)

5/323

FI

HO1S 5/227 HO1S 5/323 テーマコード (参考)

5F173

審査請求 未請求 請求項の数 5 OL (全8頁)

(21) 出願番号 (22) 出願日

HO1S

特願2016-120151 (P2016-120151) 平成28年6月16日 (2016.6.16)

(2006, 01)

(71) 出願人 000006013

三菱電機株式会社

東京都千代田区丸の内二丁目7番3号

(74)代理人 100082175

弁理士 高田 守

(74)代理人 100106150

弁理士 高橋 英樹

(74)代理人 100148057

弁理士 久野 淑己

(72) 発明者 土屋 裕彰

東京都千代田区丸の内二丁目7番3号 三

菱電機株式会社内

(72) 発明者 山口 晴央

東京都千代田区丸の内二丁目7番3号 三

菱電機株式会社内

最終頁に続く

(54) 【発明の名称】半導体素子の製造方法、半導体素子

## (57)【要約】

【課題】本発明は、弊害なくnつながりを抑制できる半 導体素子の製造方法と、その方法で製造された半導体素 子を提供することを目的とする。

【解決手段】基板の上方に、p型層と、該p型層の上方の活性層と、該活性層の上方のn型層と、を有するメサ部を形成するメサ部形成工程と、該メサ部の左右に、p型電流ブロック層と、該p型電流ブロック層の上方のn型電流ブロック層と、該n型電流ブロック層と、を有する電流狭窄部を形成する電流狭窄部形成工程と、該i型又はp型の電流ブロック層と、該n型層の左右の部分にp型不純物を気相拡散又は固相拡散させて、該n型電流ブロック層の上側の部分と、該n型層の左右の部分を、p型半導体とするp型化工程と、を備える。

【選択図】図1

#### 【特許請求の範囲】

### 【請求項1】

基板の上方に、p型層と、前記p型層の上方の活性層と、前記活性層の上方のn型層と を有するメサ部を形成するメサ部形成工程と、

前記メサ部の左右に、p型電流ブロック層と、前記p型電流ブロック層の上方のn型電流ブロック層と、前記n型電流ブロック層の上方のi型又はp型の電流ブロック層と、を有する電流狭窄部を形成する電流狭窄部形成工程と、

前記i型又はp型の電流ブロック層と、前記n型電流ブロック層の上側の部分と、前記n型層の左右の部分にp型不純物を気相拡散又は固相拡散させて、前記n型電流ブロック層の上側の部分と、前記n型層の左右の部分を、p型半導体とするp型化工程と、を備えたことを特徴とする半導体素子の製造方法。

【請求項2】

前記基板はInPであり、

前記p型層はZnがドープされたInPであり、

前記n型層はSがドープされたInPであり、

前記p型電流ブロック層はZnがドープされたInPであり、

前記n型電流ブロック層はSがドープされたInPであり、

前記p型不純物はZnであることを特徴とする請求項1に記載の半導体素子の製造方法

【請求項3】

前記p型化工程では、前記p型不純物の拡散源となる膜を電流狭窄部の上に形成し、前記p型不純物を固相拡散させることを特徴とする請求項1又は2に記載の半導体素子の製造方法。

### 【請求項4】

基板と、

前記基板の上方に形成されたp型層と、前記p型層の上方に形成された活性層と、前記活性層の上方に形成されたn型層と、を有するメサ部と、

前記メサ部の左右にp型電流ブロック層とn型電流ブロック層とを有する電流狭窄部と、を備え、

前記n型層は前記活性層よりも幅が小さいことを特徴とする半導体素子。

【請求項5】

前記n型層の幅は前記活性層の幅より100nm以上小さいことを特徴とする請求項4 に記載の半導体素子。

【発明の詳細な説明】

## 【技術分野】

[0001]

本発明は、例えば光通信などに用いられる半導体素子の製造方法と、その製造方法で製造された半導体素子に関する。

### 【背景技術】

[0002]

通信系レーザはサイリスタ構造の電流狭窄層を備える。この電流狭窄層はBH構造と呼ばれたり、電流プロック層と呼ばれたりすることがある。電流狭窄層を形成したことによってn型クラッド層と電流狭窄層のn型領域がつながらないようにすべきである。n型クラッド層と電流狭窄層のn型領域がつながることを、「nつながり」という。nつながりを抑制するために、電流狭窄層中の不純物濃度を最適化したり、成長中にエッチング性ガスを導入して電流狭窄層の形状を制御したりすることがある。

## [0003]

特許文献1には、p型の電流ブロック層中の高濃度不純物をn型の電流ブロック層に拡散させることによって、n型の電流ブロック層のメサ部近傍の一部領域をp型に反転させる技術が開示されている。

10

20

30

40

#### 【先行技術文献】

【特許文献】

[0004]

【特許文献1】特開昭63-202985号公報

【発明の概要】

【発明が解決しようとする課題】

[00005]

電流狭窄層の成長中のエッチングが不十分である場合、又はメサ部若しくは選択成長マスク近傍にて結晶の異常成長が生じた場合、「nつながり」が発生することがある。電流狭窄層の形成中にエッチング性ガスを導入する場合、エッチング性ガスの導入量がばらついたり、エッチングが困難な部分が生じたりすると、nつながりを確実に解消できない。また、電流ブロック層のp型不純物濃度を高くする場合、p型不純物が活性層に拡散して素子特性を悪化させたり、p型不純物がn型電流ブロック層に拡散して電流リークの抑制効果を損なったりする。弊害なくnつながりを抑制する方法は見出されていなかった。

[0006]

本発明は、上述のような課題を解決するためになされたもので、弊害なくnつながりを抑制できる半導体素子の製造方法と、その方法で製造された半導体素子を提供することを目的とする。

【課題を解決するための手段】

[0007]

本願の発明に係る半導体素子の製造方法は、基板の上方に、p型層と、該p型層の上方の活性層と、該活性層の上方のn型層と、を有するメサ部を形成するメサ部形成工程と、該メサ部の左右に、p型電流ブロック層と、該p型電流ブロック層の上方のn型電流ブロック層と、該n型電流ブロック層と、を有する電流狭窄部を形成する電流狭窄部形成工程と、該i型又はp型の電流ブロック層と、該n型電流ブロック層の上側の部分と、該n型層の左右の部分にp型不純物を気相拡散又は固相拡散させて、該n型電流ブロック層の上側の部分と、該n型クラッド層の左右の部分を、p型半導体とするp型化工程と、を備えたことを特徴とする。

[0008]

本願の発明に係る半導体素子は、基板と、該基板の上方に形成されたp型層と、該p型層の上方に形成された活性層と、該活性層の上方に形成されたn型層と、を有するメサ部と、該メサ部の左右にp型電流ブロック層とn型電流ブロック層とを有する電流狭窄部と、を備え、該n型層は該活性層よりも幅が小さいことを特徴とする。

【発明の効果】

[0009]

本発明によれば、 p 型不純物を気相拡散又は固相拡散させて n つながりを解消するので、弊害なく n つながりを抑制できる。

【図面の簡単な説明】

[0010]

【図1】実施の形態に係る半導体素子の断面図である。

【図2】基板の上に複数の層を形成したことを示す図である。

【図3】メサ部を形成したことを示す図である。

【図4】電流狭窄部を形成したことを示す図である。

【図5】nつながりを解消したことを示す図である。

【図6】コンタクト層を形成したことを示す図である。

【発明を実施するための形態】

[0011]

本発明の実施の形態に係る半導体素子の製造方法と半導体素子について図面を参照して説明する。同じ又は対応する構成要素には同じ符号を付し、説明の繰り返しを省略する場合がある。

10

20

30

- -

40

. .

### [0012]

実施の形態.

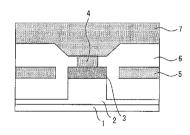

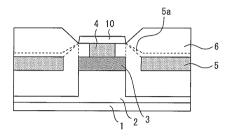

図1は、実施の形態に係る半導体素子の断面図である。この半導体素子は、Znがドープされたp型InPを材料とする基板1の上に、メサ部と、メサ部を埋め込む電流狭窄部とを形成した半導体レーザ素子である。メサ部は、基板1の上方に形成されたp型層2と、p型層2の上方に形成された活性層3と、活性層3の上方に形成されたn型層4と、を有する。メサ部は、リッジ導波路を提供する。

### [0013]

p型層 2 は例えば p 型クラッド層であるが、バッファ層又は光ガイド層などを備えても良い。 n 型層 4 は例えば n 型クラッド層であるが、バッファ層又は光ガイド層などを備えても良い。 n 型層 4 は活性層 3 よりも幅が小さい。 n 型層 4 の幅は活性層 3 の幅より例えば 1 0 0 n m以上小さい。

[0014]

電流狭窄部は、メサ部の左右にp型電流ブロック層 6 と n 型電流ブロック層 5 とを有する。p型電流ブロック層 6 はメサ部に接するが、n 型電流ブロック層 5 はメサ部に接しない。n 型電流ブロック層 5 とメサ部の間にはp型電流ブロック層 6 がある。メサ部と電流狭窄部の上にはコンタクト層 7 が形成されている。

[0015]

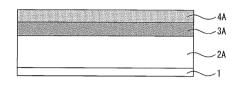

図 2 - 6 を参照して、本発明の実施の形態に係る半導体素子の製造方法を説明する。半導体素子を構成する各半導体層は有機金属気相成長法又は分子線エピタキシャル成長法などを用いて形成することができる。

[0016]

1. メサ部形成工程

[0017]

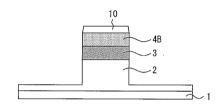

活性層 3 A は、例えば厚み 0 . 0 5 ~ 0 . 2 μ m の I n G a A s P である。 n 型層 4 A は、例えば、 S がドープされた厚みが 0 . 5 ~ 2 μ m の n 型 I n P クラッド層である。 n 型層 4 A のキャリア濃度は例えば 0 . 0 5 ~ 5 . 0 E 1 8 c m <sup>- 3</sup> とする。

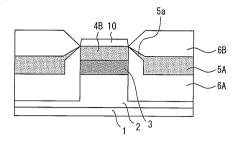

[0018]

次いで、エッチングにより図3に示すメサ部を形成する。メサ部を形成するとき、まずは、スパッタ装置を用いてn型層 4 A の上にS i O  $_2$  マスク 1 O を形成する。そして、I C P 装置によるエッチングで、基板 1 が露出する程度までエッチングし、高さ 1 . 5 ~ 4 . 0  $\mu$  m のメサ部を形成する。メサ部は、基板 1 の上方に、p型層 2 と、p型層 2 の上方の活性層 3 と、活性層 3 の上方の n 型層 4 B とを有する。メサ部を形成する工程をメサ部形成工程という。

[0019]

2.電流狭窄部形成工程

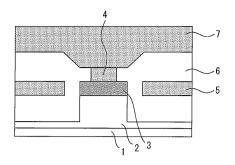

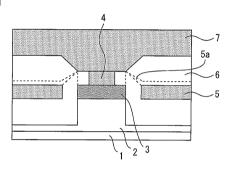

次いで、図4に示す電流狭窄部を形成する。この工程では、メサ部の左右に、有機金属気相成長法により、p型電流ブロック層6Aと、p型電流ブロック層6Aの上方のn型電流ブロック層5Aの上方のi型の電流ブロック層6Bと、を有する電流狭窄部を形成する。成長温度は例えば550~700 程度である。なおi型とはアンドープということである。

[0020]

p 型電流ブロック層 6 A は、例えば、厚さが 0 . 1 ~ 0 . 5 μ m であり、キャリア濃度を 0 . 5 ~ 2 . 0 Ε 1 8 c m  $^{-3}$  に設定した、 Z n がドープされた p 型 I n P 層である。 n 型電流ブロック層 5 A は、例えば、厚さが 0 . 5 ~ 2 . 0 μ m で、キャリア濃度を 5 .

10

20

30

40

## [0021]

電流狭窄部形成工程の直後においては、図4に示されるように、n型電流ブロック層5Aが薄い延長部5aを含んでいる。この延長部5aはメサ部の近くに形成される不必要な部分である。この延長部5aにより、n型電流ブロック層5Aとn型層4Bがつながっている。このような現象を「nつながり」という。

## [0022]

3 . p型化工程

次いで、有機金属気相成長装置にて例えば Z n などの p 型不純物を気相拡散させ、 i 型の電流プロック層 6 B と、 n 型電流プロック層 5 A の上側の部分と、 n 型層 4 B の左右の部分を、 p 型半導体とする。より具体的に言えば、 i 型の電流プロック層 6 B と、 n 型電流プロック層 5 A の上側の部分と、 n 型層 4 B の左右の部分に p 型不純物を気相拡散させて、少なくとも n 型電流プロック層 5 A の上側の部分と、 n 型層 4 B の左右の部分を、 p 型化工程後の半導体素子の断面図が示されている。 n 型電流プロック層 5 A の上側の部分は、 p 型化工程後の半導体素子の断面図が示されている。 n 型電流プロック層 5 A の上側の部分は、 p 型化され、 p 型化た部分は図 5 では破線で示されている。 n 型層 4 B の左右の部分は p 型化された結果、 n 型層 4 C し「n つながり」は解消する。また、 n 型層 4 B の左右が p 型化された結果、 n 型層 4 C の幅は活性層 3 の幅より小さくなる。

### [ 0 0 2 3 ]

p型化工程では、気相拡散に代えて、固相拡散でp型不純物を拡散させてもよい。固相拡散の場合、p型不純物の拡散源となる膜を電流狭窄部の上に形成し、p型不純物を固相拡散させる。拡散源となる膜は、例えばZnOなどの酸化膜である。

## [0024]

4 . コンタクト層形成工程

# [0025]

上述した各工程を実施することで、図1に示す半導体素子が完成する。本発明の実施の 形態に係る半導体素子の製造方法によれば、「nつながり」を抑制するために、p型化工程で、図4の延長部5aをp型化させる。これによりnつながりを解消することができる

## [0026]

ところで、図4の構造を形成した段階又はn型電流プロック層5Aを形成した段階で、nつながりを解消するために、HClなどのエッチングガスを導入し延長部5aを除去することも考えられる。しかし、エッチング性ガスの導入量のばらつき及びメサ加工時の表面荒れによりエッチングが困難な成長面が現れることにより、nつながりを解消できないことがある。また、エッチング性ガスによりSiO₂マスク10がダメージを受けると、電流狭窄層の成長異常などの問題があった。

# [0027]

また、図4のp型電流ブロック層6A又はi型の電流ブロック層6Bに、n型電流ブロック層5Aの不純物濃度より十分高いp型不純物をドープしておくことも考えられる。この場合、p型電流ブロック層6A又はi型の電流ブロック層6Bのp型不純物が、n型電流ブロック層5Aに拡散することで延長部5aの解消が期待できる。しかし、この場合、

10

20

30

40

10

20

後続のコンタクト層形成工程において印加される熱により、p型電流ブロック層6A又はi型の電流ブロック層6Bのp型不純物が活性層3に拡散してレーザ発光効率を低下させるおそれがある。また、p型電流ブロック層6A又はi型の電流ブロック層6Bのp型不純物濃度を、n型電流ブロック層5Aの不純物濃度より十分高くすると、n型電流ブロック層5Aのn型キャリアが補償されて、電流狭窄部における電流リーク抑制効果が損なわれてしまう。

#### [0028]

これに対し、本発明の実施の形態に係る半導体素子の製造方法では、 p 型不純物の気相拡散又は固相拡散により n つながりを解消するので、エッチングガスで延長部 5 a を除去する場合に生じる弊害はない。また、 p 型電流ブロック層 6 A 又は i 型の電流ブロック層 6 B の p 型不純物濃度を、 n 型電流ブロック層 5 A の不純物濃度より十分高くする必要もないので、レーザ発光効率の低下及び電流リーク抑制効果の毀損はない。

#### [0029]

このように本発明の実施の形態に係る半導体素子の製造方法によれば、弊害なくnつながりを抑制することができる。さらに、p型化工程では、n型層4Bの左右の部分をp型化させるので、電流狭窄効果を向上する効果を得ることができる。

### [0030]

本発明の実施の形態に係る半導体素子の製造方法は、その特徴を失わない範囲で様々な変形をなし得る。例えば、SiO₂膜の形成には熱CVDなどの酸化膜形成装置を用いてもよいし、メサ部の形成にRIE装置でのドライエッチング又は薬液によるウェットエッチングを用いることも可能である。 p型化工程におけるZnの不純物拡散には熱拡散炉を用いてもよいし固相拡散を用いることも可能である。

### 【符号の説明】

#### [ 0 0 3 1 ]

1 基板、 2 p型層、 3 活性層、 4 n型層、 5 n型電流ブロック層、

6 p型電流ブロック層

【図1】

【図4】

【図2】

【図5】

【図3】

【図6】

# 【手続補正書】

【提出日】平成29年8月2日(2017.8.2)

【手続補正1】

【補正対象書類名】明細書

【補正対象項目名】0007

【補正方法】変更

【補正の内容】

[0007]

本願の発明に係る半導体素子の製造方法は、基板の上方に、p型層と、該p型層の上方の活性層と、該活性層の上方のn型層と、を有するメサ部を形成するメサ部形成工程と、該メサ部の左右に、p型電流ブロック層と、該p型電流ブロック層の上方のn型電流ブロック層と、該n型電流ブロック層と、を有する電流狭窄部を形成する電流狭窄部形成工程と、該ェ型又はp型の電流ブロック層と、該n型電流ブロック層の上側の部分と、該n型層の左右の部分にp型不純物を気相拡散又は固相拡散させて、該n型電流ブロック層の上側の部分と、該n型層の左右の部分を、p型半導体とするp型化工程と、を備えたことを特徴とする。

# フロントページの続き

# (72)発明者 中井 栄治

東京都千代田区丸の内二丁目 7 番 3 号 三菱電機株式会社内 F ターム(参考) 5F173 AA26 AA48 AF92 AF98 AH14 AP33 AP52 AP53 AP60 AR24