(19) **日本国特許庁(JP)**

# (12) 特 許 公 報(B2)

(11)特許番号

特許第6888122号 (P6888122)

(45) 発行日 令和3年6月16日(2021.6.16)

(24) 登録日 令和3年5月21日 (2021.5.21)

(51) Int.Cl. F I **HO4L 9/32 (2006.01)** HO4L

HO4L

9/32

(2006.01)

HO4L

9/00

675A

GO9C

1/00

(2006.01)

GO9C

1/00

64OD

GO6F

21/57

(2013.01)

GO6F

21/57

32O

請求項の数 20 (全 35 頁)

(21) 出願番号 特願2019-565643 (P2019-565643)

(86) (22) 出願日 平成30年1月19日 (2018.1.19)

(86) 国際出願番号 PCT/JP2018/001521

(87) 国際公開番号 W02019/142307 (87) 国際公開日 令和1年7月25日 (2019.7.25)

審査請求日 令和2年4月30日(2020.4.30)

||(73)特許権者 302062931

ルネサスエレクトロニクス株式会社 東京都江東区豊洲三丁目2番24号

|(73)特許権者 000006013

三菱電機株式会社

東京都千代田区丸の内二丁目7番3号

|(74)代理人 100103894

弁理士 家入 健

|(72)発明者 森山 大輔

東京都江東区豊洲三丁目2番24号 ルネ

サスエレクトロニクス株式会社内

|(72)発明者 鈴木 大輔

東京都千代田区丸の内二丁目7番3号 三

菱電機株式会社内

最終頁に続く

(54) 【発明の名称】半導体装置、更新データ提供方法、更新データ受取方法およびプログラム

## (57)【特許請求の範囲】

## 【請求項1】

メモリと、乱数生成回路と、制御回路と、を有し、外部端末装置に更新データを提供する半導体装置であって、

前記メモリは、鍵情報を記憶し、

前記乱数生成回路は、第1乱数信号および第2乱数信号を生成し、

前記制御回路は、

前記第1乱数信号および前記鍵情報から第6乱数信号および第7乱数信号を生成し、

前記更新データに対して第7乱数信号を用いて暗号化更新データを生成し、

前記外部端末装置に送信する要求信号として前記第1乱数信号および前記第2乱数信号 を生成し、

前記要求信号に対する応答信号として前記外部端末装置から第 1 応答信号および第 2 応答信号を受け取り、

前記第1応答信号と前記第2乱数信号と前記第6乱数信号とを入力信号として、第8乱数信号を生成し、

前記第 2 応答信号と前記第 8 乱数信号とが一致している場合に、前記暗号化更新データを前記外部端末装置に提供する、半導体装置。

## 【請求項2】

前記制御回路は、

前記第6乱数信号、前記第7乱数信号、および前記第8乱数信号を、

予め設定された同一の擬似ランダム関数に入力することよりそれぞれ演算する、 請求項1に記載の半導体装置。

#### 【請求項3】

前記制御回路は、前記第2応答信号と前記第8乱数信号とが一致していない場合に、前記暗号化更新データに代えて、前記暗号化更新データと同じ桁数の乱数信号を前記外部端末装置に提供する、

請求項1に記載の半導体装置。

## 【請求項4】

前記制御回路は、前記外部端末装置から、提供した前記暗号化更新データに対する応答信号である第3応答信号を受け取った場合に、前記第3応答信号が、前記第1応答信号と前記第2乱数信号と前記第6乱数信号とを入力信号として生成された第10乱数信号と一致するか否かを判定し、一致する場合にデータが更新されたことを登録し、一致しない場合には、データが更新されなかったことを登録する、

請求項1に記載の半導体装置。

## 【請求項5】

メモリと、制御回路と、を有し、外部サーバ装置から暗号化更新データを受け取る半導体装置であって、

前記メモリは、更新前データと、鍵情報を記憶し、

前記制御回路は、

前記外部サーバ装置から第1乱数信号および第2乱数信号を要求信号として受け取り、前記第1乱数信号および前記鍵情報から第6乱数信号および第7乱数信号を生成し、

前記第2乱数信号と前記第6乱数信号とを入力信号として、第9乱数信号および第10 乱数信号を生成し、

予め設定された信号を含むチャレンジコードを生成し、

前記要求信号に対する応答信号として前記第9乱数信号および前記チャレンジコードを 前記外部サーバ装置へ出力し、

出力した前記応答信号に基づいて前記外部サーバ装置から認証信号と前記暗号化更新データとを受け取り、

受け取った前記認証信号と、前記第10乱数信号とが一致している場合に、前記外部サーバ装置から受け取った前記暗号化更新データの復号処理を行う、

半導体装置。

## 【請求項6】

前記制御回路は、

前記第6乱数信号、前記第7乱数信号、前記第9乱数信号、および前記第10乱数信号を

予め設定された同一の擬似ランダム関数に入力することよりそれぞれ演算する、 請求項5に記載の半導体装置。

## 【請求項7】

前記制御回路は、受け取った前記認証信号と、前記第10乱数信号とが一致していない場合に、前記外部サーバ装置から受け取った前記暗号化更新データの復号処理を行わない

請求項5に記載の半導体装置。

## 【請求項8】

前記制御回路は、予め設定された桁数の数値を順次インクリメントすることにより前記 チャレンジコードを生成する、

請求項5に記載の半導体装置。

## 【請求項9】

前記制御回路は、前記第2乱数信号と前記第6乱数信号とを入力信号として、第12乱数信号を生成することにより前記チャレンジコードを生成する、

請求項5に記載の半導体装置。

10

20

30

40

#### 【請求項10】

第3乱数信号を生成する乱数生成回路をさらに備え、

前記制御回路は、前記第9乱数信号および前記第10乱数信号を生成する際に、前記第2乱数信号と前記第6乱数信号に加えて前記第3乱数信号も入力信号として入力し、

前記チャレンジコードとして第3乱数信号を前記外部サーバ装置へ出力する、

請求項5に記載の半導体装置。

#### 【請求項11】

前記制御回路は、少なくとも前記第2乱数信号と前記第6乱数信号とを入力信号として含む擬似ランダム関数の出力として第13乱数信号を生成し、

前記暗号化更新データの復号処理が成功した場合に、前記第13乱数信号を前記外部サーバ装置へ出力する、

請求項5に記載の半導体装置。

## 【請求項12】

前記制御回路は、前記暗号化更新データの復号処理が成功しなかった場合に、前記第 1 3 乱数信号に代えて、乱数信号を前記外部サーバ装置へ出力する、

請求項11に記載の半導体装置。

## 【請求項13】

直性乱数生成回路をさらに備え、

前記乱数信号は、真性乱数信号である、

請求項12に記載の半導体装置。

## 【請求項14】

外部端末装置に更新データを提供する方法であって、

鍵情報を記憶し、

第1乱数信号および第2乱数信号を生成し、

前記第1乱数信号および前記鍵情報から第6乱数信号および第7乱数信号を生成し、 前記更新データに対して第7乱数信号を用いて暗号化更新データを生成し、

前記外部端末装置に送信する要求信号として前記第1乱数信号および前記第2乱数信号 を生成し、

前記要求信号に対する応答信号として前記外部端末装置から第 1 応答信号および第 2 応答信号を受け取り、

前記第1応答信号と前記第2乱数信号と前記第6乱数信号とを入力信号として、第8乱数信号を生成し、

前記第2応答信号と前記第8乱数信号とが一致している場合に、前記暗号化更新データを前記外部端末装置に提供する、

更新データ提供方法。

## 【請求項15】

外部サーバ装置から暗号化更新データである暗号化更新データを受け取る方法であって

更新前データと、鍵情報を記憶し、

前記外部サーバ装置から第1乱数信号および第2乱数信号を要求信号として受け取り、前記第1乱数信号および前記鍵情報から第6乱数信号および第7乱数信号を生成し、

前記第2乱数信号と前記第6乱数信号とを入力信号として、第9乱数信号および第10 乱数信号を生成し、

予め設定された信号を含むチャレンジコードを生成し、

前記要求信号に対する応答信号として前記第9乱数信号および前記チャレンジコードを 前記外部サーバ装置へ出力し、

出力した前記応答信号に基づいて前記外部サーバ装置から認証信号と前記暗号化更新データとを受け取り、

受け取った前記認証信号と、前記第 1 0 乱数信号とが一致している場合に、前記外部サ ーバ装置から受け取った前記暗号化更新データの復号処理を行う、

10

20

30

40

更新データ受取方法。

#### 【請求項16】

コンピュータに以下の方法を実行させるプログラムであって、前記方法は、

外部端末装置に更新データを提供する方法であって、

鍵情報を記憶し、

第1乱数信号および第2乱数信号を生成し、

前記第1乱数信号および前記鍵情報から第6乱数信号および第7乱数信号を生成し、

前記更新データに対して第7乱数信号を用いて暗号化更新データを生成し、

前記外部端末装置に送信する要求信号として前記第1乱数信号および前記第2乱数信号を生成し、

前記要求信号に対する応答信号として前記外部端末装置から第1応答信号および第2応 答信号を受け取り、

前記第 1 応答信号と前記第 2 乱数信号と前記第 6 乱数信号とを入力信号として、第 8 乱数信号を生成し、

前記第 2 応答信号と前記第 8 乱数信号とが一致している場合に、前記暗号化更新データを前記外部端末装置に提供する、

プログラム。

## 【請求項17】

コンピュータに以下の方法を実行させるためのプログラムであって、前記方法は、 外部サーバ装置から暗号化更新データである暗号化更新データを受け取る方法であって

更新前データと、鍵情報を記憶し、

前記外部サーバ装置から第1乱数信号および第2乱数信号を要求信号として受け取り、 前記第1乱数信号および前記鍵情報から第6乱数信号および第7乱数信号を生成し、

前記第2乱数信号と前記第6乱数信号とを入力信号として、第9乱数信号および第10 乱数信号を生成し、

予め設定された信号を含むチャレンジコードを生成し、

前記要求信号に対する応答信号として前記第9乱数信号および前記チャレンジコードを 前記外部サーバ装置へ出力し、

出力した前記応答信号に基づいて前記外部サーバ装置から認証信号と前記暗号化更新データとを受け取り、

受け取った前記認証信号と、前記第10乱数信号とが一致している場合に、前記外部サ ーバ装置から受け取った前記暗号化更新データの復号処理を行う、

プログラム。

## 【請求項18】

メモリと、乱数生成回路と、制御回路と、を有し、外部サーバ装置から暗号化更新データを受け取り、受け取った暗号化更新データを外部端末装置に提供する半導体装置であって、

前記メモリは、前記外部サーバ装置との間で使用可能な共通鍵を記憶し、

前記制御回路は、

前記外部サーバ装置から、第1乱数信号、第2乱数信号、前記共通鍵により暗号化された第6乱数信号を含む暗号化鍵データ、および暗号化更新データを受け取り、

前記暗号化鍵データを前記共通鍵により復号して第6乱数信号を生成し、

前記外部端末装置に送信する要求信号として前記第1乱数信号および前記第2乱数信号を出力し、

前記要求信号に対する応答信号として前記外部端末装置から第 1 応答信号および第 2 応答信号を受け取り、

前記第 1 応答信号と前記第 2 乱数信号と前記第 6 乱数信号とを入力信号として、第 8 乱数信号を生成し、

前記第2応答信号と前記第8乱数信号とが一致している場合に、前記暗号化更新データ

10

20

30

40

を前記外部端末装置に提供する、半導体装置。

## 【請求項19】

前記第6乱数信号および前記第8乱数信号は、

予め設定された同一の擬似ランダム関数に入力することよりそれぞれ演算される、

請求項18に記載の半導体装置。

## 【請求項20】

前記制御回路は、

前記第 2 応答信号と前記第 8 乱数信号とが一致していない場合に、前記暗号化更新データに代えて、前記暗号化更新データと同じ桁数の乱数信号を前記外部端末装置に提供する

10

請求項18に記載の半導体装置。

#### 【発明の詳細な説明】

#### 【技術分野】

#### [00001]

本発明は、半導体装置、更新データ提供方法、更新データ受取方法およびプログラムに関する。

## 【背景技術】

## [0002]

I o T (Internet of Things)機器が広く普及している。これらの機器に含まれるマイコン等の半導体装置に対して高いセキュリティを確保した状態でファームウェアアップデート等を行うことが期待されている。

20

## [0003]

特許文献1に記載の車外装置は、更新制御プログラム、当該プログラムに係るダイジェスト値の算出手段、更新後の動作が正常であるか否かを判定する手段、および判定結果を返答する手段を実現するプログラムを含む更新データを記憶している。そして、制御装置は、車外装置から送信される更新データを中継装置を介して受信する。さらに、制御装置は、受信した更新データに含まれる更新制御プログラムにより制御プログラムを更新すると共に、前記プログラムを実行して更新後の動作が正常であるか否かを判定して、その判定結果を中継装置に返答する。

## [0004]

30

特許文献 2 に記載の電子機器は、アプリケーションソフトウェアの動作に係るアプリケーションファイルを有し、ネットワークを介して前記アプリケーションファイルを更新する。かかる電子機器は、1つ以上のデータからなるアプリケーションファイルを記憶し、更新データと、前記アプリケーションファイルにおいて前記更新データによって更新する位置を示す位置情報とを、前記ネットワークを介して外部装置から受け取る。さらに、電子機器は、前記位置情報が示す位置に存在するデータを前記更新データに書き換えて、前記アプリケーションファイルの一部のみを更新し、更新された前記アプリケーションファイルが改竄されているか否かの確認を行う。

## [0005]

特許文献 3 に記載のプログラム書換えシステムは、マルチプロトコルに対応した車載中継装置において新プログラムと旧プログラムとの差分データを検索し、新プログラムにおける差分データを E C U に送信して記憶する。

40

## [0006]

特許文献 4 に記載の組込機器は、ソフトウェアを更新する更新データが複数に分割された各セクションについて順に検証処理を行う。組込機器は、検証処理の途中で得られる中間値を記憶しておく。組込機器は、全てのセクションに対して検証処理が完了すると、検証処理で得られた値と、検証データとを比較して、改ざんがないことを確認する。改ざんがないことが確認できると、組込機器は、再び各セクションについて順に検証処理を行う。組込機器は、検証処理で得られた中間値と記憶しておいた中間値とを比較して、一致すると、そのセクションによってソフトウェアを更新する。

#### 【先行技術文献】

【特許文献】

[0007]

【特許文献 1 】特開 2 0 1 5 - 1 0 3 1 6 3 号公報

【特許文献2】国際公開第2006/129654号

【特許文献3】特開2014-182571号公報

【特許文献4】国際公開第2006/129654号

【発明の概要】

【発明が解決しようとする課題】

[ 0 0 0 8 ]

特許文献1に記載の技術は、中継機が更新データに対して電子署名演算を行うことが可能でなければならない。また、特許文献1は、更新データの暗号化が行われないため、更新データの秘匿性を担保できていない。また、特許文献2に記載の技術は、部分的な検証を行う一方で、全体としての検証を行わない。そのため、ブロックごとに改ざん検出の管理を行うこととなり、保存データ量が多くなるおそれがある。また、特許文献3に記載の技術は、中継装置が更新データの電子署名や復号演算を行わなければならないため、中継装置に更新データの中身を開示する必要がある一方、中継装置とECUとの通信においても、中間値を記憶しておく必要があり保存データ量が多くなるおそれがある。また、各セクションに対して各2回の検証処理が必要であるために計算に時間がかかるおそれがある。さらに、上記特許文献のいずれにおいても、正当な更新対象機器との通信が行われていることを確認する手段についての提案はなされていない。

[0009]

その他の課題と新規な特徴は、本明細書の記述および添付図面から明らかになるであろう。

【課題を解決するための手段】

[0010]

一実施の形態によれば、半導体装置は、メモリと、乱数生成回路と、制御回路と、を有し、外部端末装置に更新データを提供する。前記メモリは、鍵情報を記憶し、前記乱数生成回路は、第1乱数信号および第2乱数信号を生成する。前記制御回路は、前記第1乱数信号および前記鍵情報から第6乱数信号および第7乱数信号を生成し、前記更新データに対して第7乱数信号を用いて暗号化更新データを生成する。前記制御回路は、前記外部端末装置に送信する要求信号として前記第1乱数信号および前記第2乱数信号を生成し、前記要求信号に対する応答信号として前記外部端末装置から第1応答信号とおよび第2応答信号を受け取る。前記制御回路は、前記第1応答信号と前記第2乱数信号と前記第6乱数信号と入力信号として、第8乱数信号を生成し、前記第2応答信号と前記第8乱数信号とが一致している場合に、前記暗号化更新データを前記外部端末装置に提供する。

[0011]

一実施の形態によれば、半導体装置は、メモリと、制御回路と、を有し、外部サーバ装置から暗号化更新データを受け取る。前記メモリは、更新前データと、鍵情報を記憶している。前記制御回路は、前記外部サーバ装置から第1乱数信号および第2乱数信号を要求信号として受け取り、前記第1乱数信号および前記鍵情報から第6乱数信号および第7乱数信号を生成する。前記制御回路は、前記第2乱数信号と前記第6乱数信号とを入力信号として、第9乱数信号および第10乱数信号を生成する。また、前記制御回路は、予め設定された信号を含むチャレンジコードを生成し、前記要求信号に対する応答信号として前記第9乱数信号および前記チャレンジコードを前記外部サーバ装置へ出力する。前記制御回路は、出力した前記応答信号に基づいて前記外部サーバ装置から認証信号と前記暗号化更新データとを受け取り、受け取った前記認証信号と、前記第10乱数信号とが一致している場合に、前記暗号化更新データの復号処理を行う。

【発明の効果】

10

20

30

40

#### [0012]

前記一実施の形態によれば、半導体装置は、効率的かつ安全に更新プログラムの授受を行い、プログラムの更新を実現することができる。

## 【図面の簡単な説明】

## [0013]

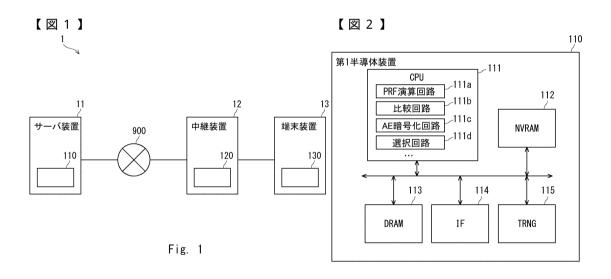

- 【図1】実施の形態1にかかる送受信システムの概略図である。

- 【図2】実施の形態1にかかる第1半導体装置のハードウェア構成図である。

- 【図3】実施の形態1にかかる第2半導体装置のハードウェア構成図である。

- 【図4】実施の形態1にかかる第3半導体装置のハードウェア構成図である。

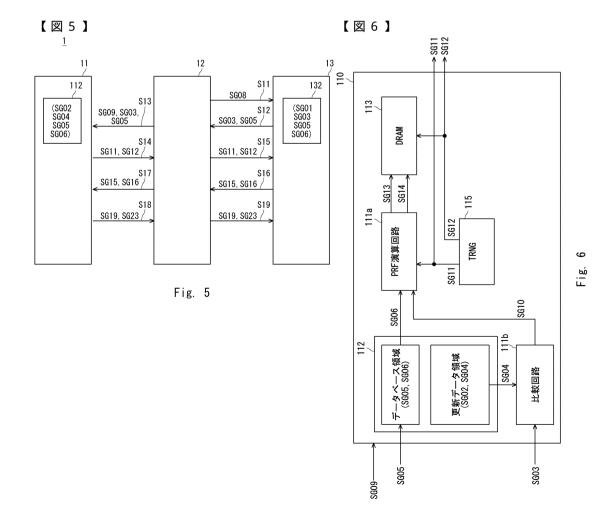

- 【図5】実施の形態1にかかる送受信システムの送受信信号を示した図である。

- 【図6】実施の形態1にかかる第1半導体装置110の機能ブロック図である。

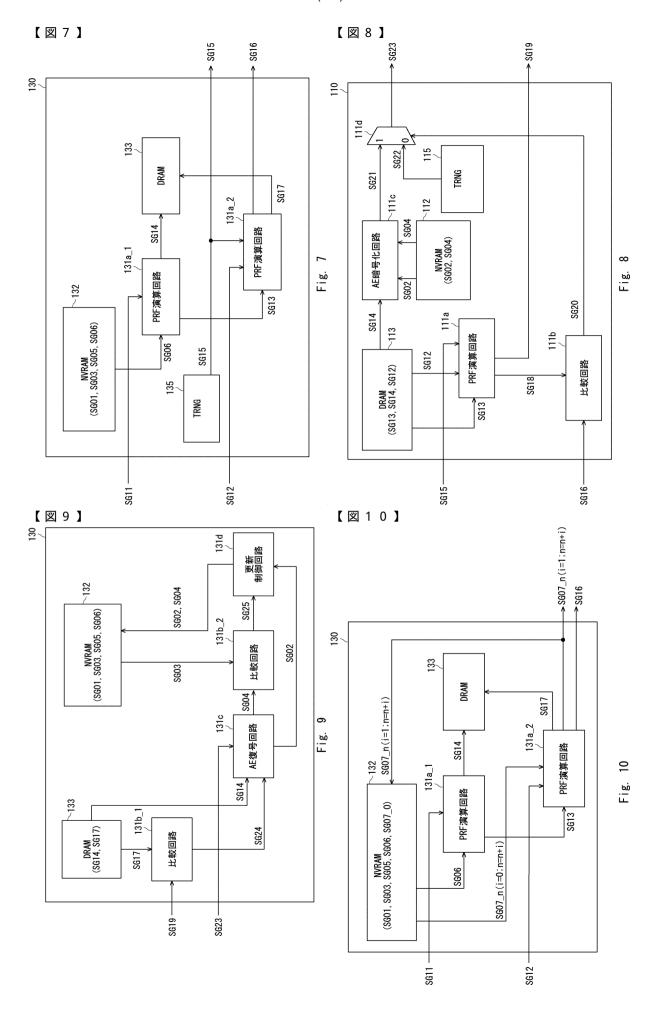

- 【図7】実施の形態1にかかる第3半導体装置の機能ブロック図である。

- 【図8】実施の形態1にかかる第1半導体装置の機能プロック図である。

- 【図9】実施の形態1にかかる第3半導体装置の機能ブロック図である。

- 【図10】実施の形態1の変形例にかかる第3半導体装置の機能ブロック図である。

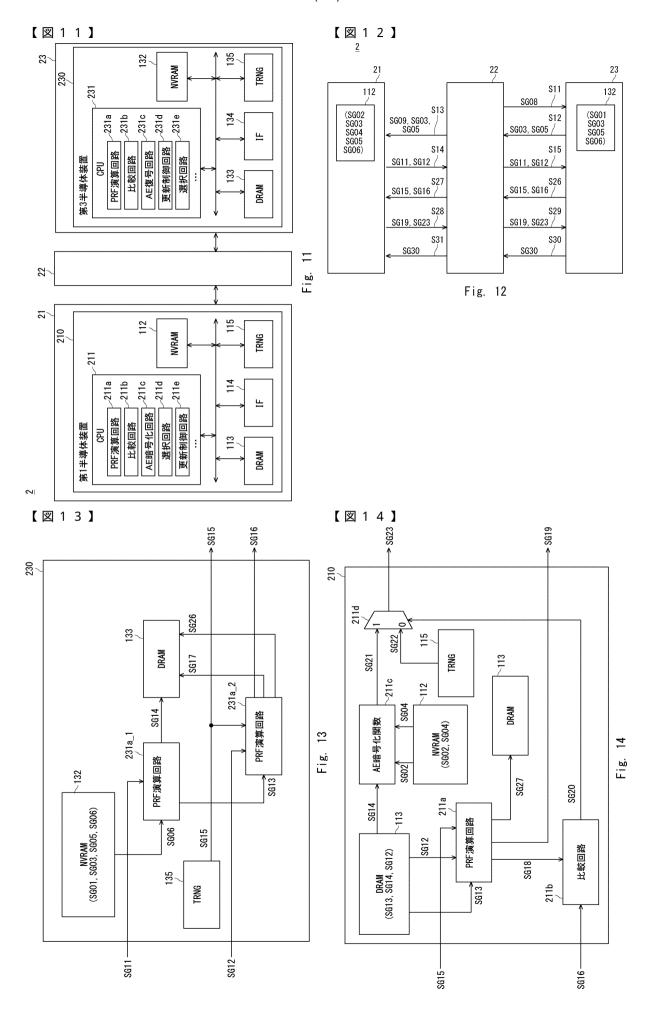

- 【図11】実施の形態2にかかる送受信システムのハードウェア構成図である。

- 【図12】実施の形態2にかかる送受信システムの送受信信号を示した図である。

- 【図13】実施の形態2にかかる第3半導体装置の機能ブロック図である。

- 【図14】実施の形態2にかかる第1半導体装置の機能ブロック図である。

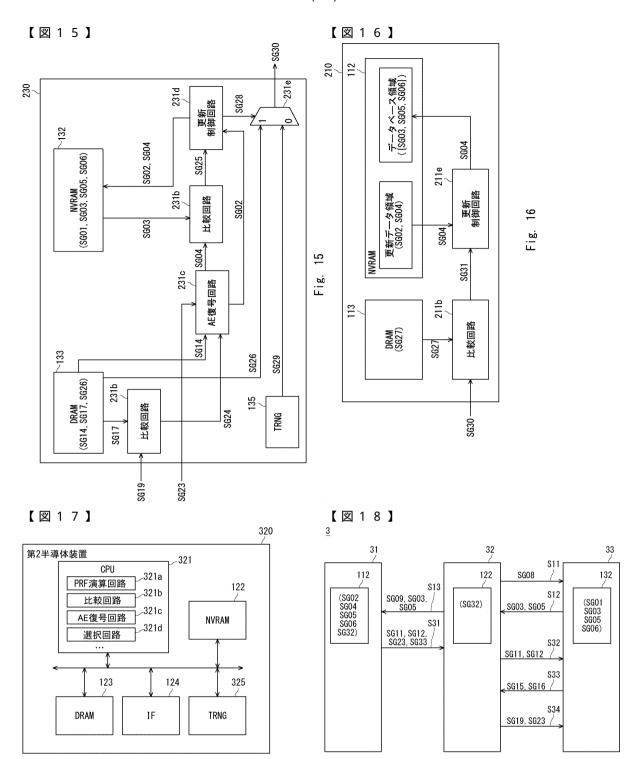

- 【図15】実施の形態2にかかる第3半導体装置の機能ブロック図である。

- 【図16】実施の形態2にかかる第1半導体装置の機能ブロック図である。

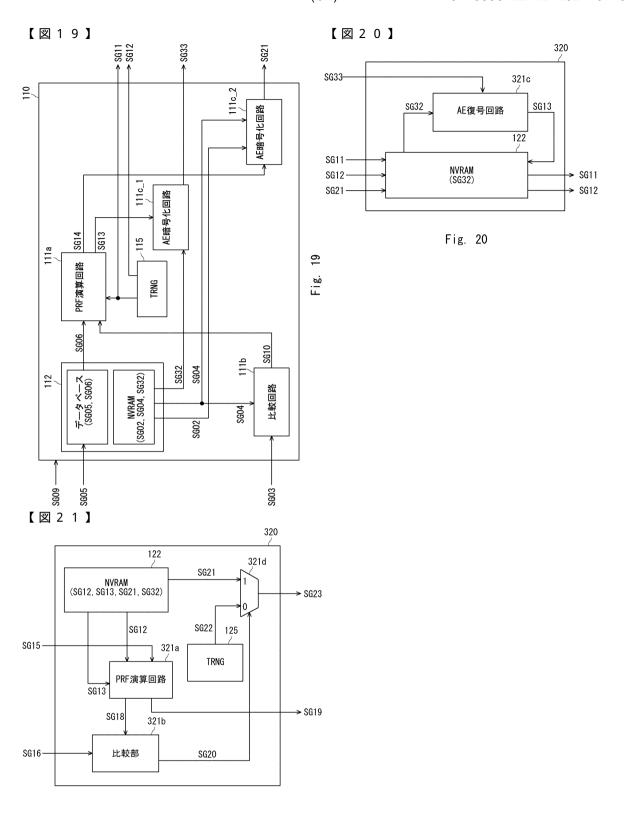

- 【図17】実施の形態3にかかる第2半導体装置のハードウェア構成図である。

- 【図18】実施の形態3にかかる送受信システムの送受信信号を示した図である。

- 【図19】実施の形態3にかかる第1半導体装置の機能ブロック図である。

- 【図20】実施の形態3にかかる第2半導体装置の機能ブロック図である。

- 【図21】実施の形態3にかかる第2半導体装置の機能ブロック図である。

## 【発明を実施するための形態】

# [0014]

説明の明確化のため、以下の記載および図面は、適宜、省略、および簡略化がなされている。また、様々な処理を行う機能プロックとして図面に記載される各要素は、ハードウェア的には、CPU (Central Processing Unit)、メモリ、その他の回路で構成することができ、ソフトウェア的には、メモリにロードされたプログラムなどによって実現される。したがって、これらの機能ブロックがハードウェアのみ、ソフトウェアのみ、またはそれらの組合せによっているいろな形で実現できることは当業者には理解されるところであり、いずれかに限定されるものではない。よって、以下の説明に回路として例示した構成は、ハードウェアまたはソフトウェアのいずれかまたはその両方によって実現することが可能であり、ある機能を実現する回路として示された構成は、同様の機能を実現するソフトウェアの一部としても示され得る。例えば、制御回路と記載された構成は、制御部として記載され得る。なお、各図面において、同一の要素には同一の符号が付されており、必要に応じて重複説明は省略されている。

# [0015]

また、上述したプログラムは、様々なタイプの非一時的なコンピュータ可読媒体を用いて格納され、コンピュータに供給することができる。非一時的なコンピュータ可読媒体は、様々なタイプの実体のある記録媒体を含む。非一時的なコンピュータ可読媒体の例は、磁気記録媒体(例えばフレキシブルディスク、磁気テープ、ハードディスクドライブ)、光磁気記録媒体(例えば光磁気ディスク)、CD-ROM(Read Only Memory)CD-R CD-R/W、半導体メモリ(例えば、マスクROM、PROM(Programmable ROM)、EPROM(Erasable PROM)、フラッシュROM、RAM(Random Access Memory))を含む。また、プログラムは、様々なタイプの一時的なコンピュータ可読媒体によってコンピュータに供給されてもよい。一時的なコンピュータ可読媒体の例は、電気信号、光

10

20

30

40

信号、および電磁波を含む。一時的なコンピュータ可読媒体は、電線および光ファイバ等の有線通信路、又は無線通信路を介して、プログラムをコンピュータに供給できる。

## [0016]

## < 実施の形態 1 >

まず、図1を参照しながら、実施の形態1について概略を説明する。図1は、実施の形態1にかかる送受信システムの概略図である。送受信システム1は、端末装置13が有する更新前データを、サーバ装置11が有している更新データに更新するためのシステムである。送受信システム1は、サーバ装置11において更新データを暗号化し、暗号化した更新データである暗号化更新データを端末装置13に送信する。端末装置13は、暗号化更新データを復号してデータを更新する。送受信システム1は、サーバ装置11、中継装置12、および端末装置13を構成とする。サーバ装置11と中継装置12とは、通信可能に接続している。また、中継装置12と端末装置13とは、通信可能に接続している。また、中継装置12とはネットワーク900を介して通信可能に接続されている。なお、各構成を通信可能にする接続手段は有線、無線を問わず、インターネットを介しているか否かを問わない。

#### [0017]

サーバ装置11は、例えばパーソナルコンピュータやブレードサーバであって、情報処理を司る第1半導体装置110を有している。中継装置12は、例えばスマートフォンやタブレット端末等であって、情報処理を司る第2半導体装置120を有している。また、端末装置13は、IoT機器と呼ばれるインターネット接続可能な機器や、その他通信機能を有する機器である。端末装置13は、情報処理を司る第3半導体装置130を有している。

## [0018]

図 2 は、実施の形態 1 にかかる第 1 半導体装置 1 1 0 のハードウェア構成図である。情報処理を司る第 1 半導体装置 1 1 0 は、主な構成として、C P U 1 1 1、N V R A M 1 1 2 (Non-Volatile Random Access Memory)、D R A M 1 1 3 (Dynamic Random Access Memory)、I F 1 1 4 (Interface)、および T R N G 1 1 5 (True Random Number Generator: 真性乱数生成回路)を有しており、これらの構成は通信バスにより接続されている

## [0019]

なお、以降の説明において、特別に説明を加えた場合を除き、名称が同一で符号が異なる構成は同様の機能を有するものとする。そのため、このような構成についての説明は省略する。

## [0020]

CPU1111は、第1半導体装置110において後述する演算処理等を行うための演算装置である。CPU111は、PRF演算回路111a、比較回路111b、AE暗号化回路111c、選択回路111dを主な構成として有している。なお、CPU1111は、ハードウェアとしてのこれらの構成を複数有していてもよいし、ソフトウェアとして並列処理可能に構成されていてもよい。また、本実施の形態において説明するCPUは、CPUコア以外の周辺回路を含んでもよい。

## [ 0 0 2 1 ]

PRF演算回路111aは、任意の入力信号を予め設定された擬似ランダム関数(PRF=Pseudorandom function)により演算し、演算結果を出力する。擬似ランダム関数は、暗号学的には乱数として識別できない値であって、直感的には十分ランダムに見える出力を返す関数であり、真のランダム関数との間で両者を識別するような多項式時間のアルゴリズムが存在しないものを指す。また、PRF演算回路111aは、同じ入力に対しては同じ結果を出力する。PRF演算回路111aは、入力として出力変数の数を指定してもよい。なお、PRF演算回路111aは、上述のような出力がなされ、且つ安全性が担保できるのであれば、共通鍵暗号やハッシュ関数に基づいた関数など他の関数を用いたものであってもよい。

10

20

30

## [0022]

比較回路 1 1 1 b は、入力として 2 つの信号を受け取り、受け取った 2 つの信号を比較し、比較結果としてこれらの信号が一致するか否かを出力する。比較結果の出力信号の例としては、 2 つの信号が一致しない場合の出力信号は「 0 」であり、 2 つの信号が一致する場合の出力信号は「 1 」である。ただし、比較結果の出力信号はこれに限られない。

## [0023]

A E 暗号化回路 1 1 1 c (AE=Authenticated Encryption)は、任意の平文と鍵情報とを入力信号として、入力信号に対して認証付き暗号化処理を行う。鍵情報は、復号処理をする際にも使用される。認証付き暗号化処理を行うことにより、A E 暗号化回路 1 1 1 c は、暗号文、認証タグ、およびヘッダ信号を出力する。

## [0024]

選択回路111dは、複数の入力信号の内いずれか選択した信号を出力する機能を有している。選択回路111dは、比較回路111bから供給される比較結果信号SG20の値によって、複数の入力信号の内からどの信号を出力するかを選択する。つまり、比較結果信号SG20は、選択回路111dの選択制御信号である。選択回路111dは、ハードウェア構成の例としてはマルチプレクサである。

## [0025]

NVRAM112は、例えばフラッシュメモリのような読み書き可能な不揮発性の記憶装置である。NVRAM112は、更新データや通信セキュリティを担保するための鍵情報等を記憶している。

## [0026]

DRAM113は、揮発性の記憶装置であって、種々のデータを一時的に記憶する。なお、本実施の形態におけるDRAM113のハードウェア構成は一例であって、DRAM113は、SRAM(Static Random Access Memory)によって構成されてもよく、揮発性メモリに代えて、MRAM(Magnetoresistive Random Access Memory)、またはフラッシュメモリ等の不揮発性メモリによって構成されてもよい。

## [0027]

TRNG115は、真性乱数生成回路である。TRNG115は、例えば、ダイオードの生成するノイズや熱雑音、放射性物質の崩壊による放射線をセンサで検出する等、ランダムな物理現象を用い、その信号を元に乱数を生成する。CPU111は、各構成の信号を処理し、処理に応じた信号を、IF114を介して中継装置12に送信し、または、中継装置12から受信した信号を、IF114を介して受け取り、受け取った信号を処理する。

## [0028]

図3は、実施の形態1にかかる第2半導体装置120のハードウェア構成図である。情報処理を司る第2半導体装置120は、主な構成として、CPU121、NVRAM122、DRAM123、およびIF124を有しており、これらの構成は通信バスにより接続されている。第2半導体装置120は、これらの構成により、サーバ装置11と通信し、サーバ装置11から信号を受け取り、受け取った信号を必要に応じて処理し、端末装置13から信号を受け取り、受け取った信号を必要に応じて処理し、サーバ装置11に送信する。

#### [0029]

図4は、実施の形態1にかかる第3半導体装置130のハードウェア構成図である。情報処理を司る第3半導体装置130は、主な構成として、CPU131、NVRAM132、DRAM133、IF134、およびTRNG135を有しており、これらの構成は通信バスにより接続されている。端末装置13は、中継装置12から信号を受け取り、受け取った信号を処理する。また、端末装置13は、処理した信号を中継装置12に送信する。

# [0030]

CPU131は、第3半導体装置130において演算処理等を行うための演算装置であ

10

20

30

40

10

20

30

40

50

る。 C P U 1 3 1 は、 P R F 演算回路 1 3 1 a 、比較回路 1 3 1 b 、 A E 復号回路 1 3 1 c を主な構成として有している。

## [0031]

AE復号回路131cは、認証付き暗号化された信号に対して、復号処理および認証タグの検証を行う。すなわち、AE復号回路131cは、AE暗号化回路111cが出力した暗号文、認証タグ、およびヘッダ信号、ならびにAE暗号化回路111cが使用した鍵情報を入力信号とする。AE復号回路131cは、暗号文を復号し、復号した結果生成された認証タグと、入力信号として受け取った認証タグが一致するか検証を行う。検証の結果、これらの認証タグが一致すると、AE復号回路131cは、復号した平文を出力する。一方、これらの認証タグが一致しないと、AE復号回路131cは、認証結果不一致を示す信号を出力する。

[0032]

更新制御回路131dは、ファームウェアの更新を行うための信号制御を行う。更新制御回路131dは、入力信号として、フラグ信号と更新データ信号を受け取る。更新制御回路131dは、受け取ったフラグ信号がファームウェアの更新を実行するための値であれば、入力信号として受け取った更新データを更新前データと置き換える処理を実行する。また、更新制御回路131dは、ファームウェアの更新処理が成功したか否かを出力する機能を有していてもよい。

[0033]

なお、実施の形態1の変形例として後述するように、端末装置13は、TRNG135 を有していない構成としてもよい。

[0034]

次に、図5~図10を参照しながら、送受信システム1の動作について詳細を説明する。まず、図5を参照しながら、送受信システム1にかかるそれぞれの装置が有する信号と、それぞれの装置が送受信する信号について説明する。図5は、実施の形態1にかかる送受信システム1の送受信信号を示した図である。

[0035]

サーバ装置11は、NVRAM112に、更新データSG02、更新バージョンデータSG04、識別子SG05、およびマスタ鍵SG06を記憶している。更新データSG02は、例えば、端末装置13のための新しいバージョンのファームウェアである。更新バージョンデータSG04は、更新データSG02のバージョン情報を含むデータである。識別子SG05は、端末装置13に固有に付与されている識別情報であって、例えば端末装置13のMacアドレス(Media Access Control address)や製品固有の識別番号等である。

[0036]

端末装置13は、NVRAM132に、更新前データSG01、更新前バージョンデータSG03、識別子SG05、およびマスタ鍵SG06を記憶している。更新前データSG01は、例えば、端末装置13が現在利用しているファームウェアである。更新前バージョンデータSG03は、更新前データSG01のバージョン情報を含むデータである。

以降は、送受信システム1にかかるそれぞれの装置が送受信する信号と、それぞれの装置が行う処理について信号の処理の流れに沿って説明する。ここに示す例では、送受信システム1は、端末装置13のファームウェアのバージョンアップデート処理を行う。

[0038]

[0037]

まず、中継装置12は、バージョンチェック要求信号SG08を端末装置13に送信する(ステップS11)。バージョンチェック要求信号SG08は、端末装置13に対してファームウェアのバージョンを応答するように要求する信号である。

[0039]

端末装置13は、中継装置12からバージョンチェック要求信号SG08を受け取ると、受け取った要求信号に応じて、端末装置13の現在のファームウェアのバージョンであ

10

20

30

40

50

る更新前バージョンデータSG03と、識別子SG05とを中継装置12に送信する(ステップS12)。

## [0040]

中継装置12は、端末装置13から更新前バージョンデータSG03と、識別子SG05とを受け取ると、これらのデータにバージョンアップ要求信号SG09を加えて、サーバ装置11に送信する(ステップS13)。

#### [0041]

図6を参照しながら、サーバ装置11が中継装置12から受け取った信号を処理して、要求信号を出力するまでの処理について説明する。図6において、サーバ装置11が有する第1半導体装置110は、ファームウェアのバージョンアップデート処理を行うために、端末装置13に対してかかる処理を行うか否かを判定する。かかる処理を行う場合、第1半導体装置110は、暗号化された更新データを復号する際に使用する鍵を生成するための信号と、端末装置13を認証するためのチャレンジコードとを出力する。

## [0042]

図6は、実施の形態1にかかるサーバ装置11における第1半導体装置110の機能ブロック図である。図6において、第1半導体装置110は中継装置12からのバージョンアップ要求信号SG09を受け付ける。次に、第1半導体装置110は、NVRAM112のデータベース領域にアクセスして、NVRAM112が記憶している識別子SG05と、中継装置12から受け取った識別子SG05とが一致するか否かを照合する。

## [0043]

サーバ装置11は、識別子に関するこれらの信号が一致した場合、中継装置12から受け取った端末装置13のファームウェアバージョンである更新前バージョンデータSG03と、NVRAM112に記憶している更新バージョンデータSG04とを照合する。すなわち、第1半導体装置110は、NVRAM112の更新データ領域にアクセスし、更新バージョンデータSG04をCPU111の比較回路111bに送信する。また、第1半導体装置110は、中継装置12から受け取った更新前バージョンデータSG03を比較回路111bに供給する。そして、比較回路111bは、これらのデータを比較し、比較結果信号SG10をPRF演算回路111aに出力する。

## [0044]

ここでは、比較回路111bがデータを比較した結果、バージョンデータが一致した場合、比較回路111bは、比較結果信号SG10として「0」を出力する。この場合、端末装置13のファームウェアは最新であり更新の必要はない。そのため、PRF演算回路111aは、ファームウェア更新のための処理を実行しない。一方、比較した結果、バージョンデータが一致しない場合、比較回路111bは、比較結果信号SG10として「1」を出力する。この場合、サーバ装置11は、後述する端末装置13のファームウェアを更新するための処理を実行する。

## [0045]

比較回路111bから比較結果信号SG10として「1」を受け取った場合、PRF演算回路111aは、NVRAM112のデータベース領域にアクセスし、マスタ鍵SG06を受け取る。また、PRF演算回路111aは、TRNG115から、第1乱数信号SG11を受け取る。PRF演算回路111aは、マスタ鍵SG06と、第1乱数信号SG11とを入力として、第6乱数信号SG13および第7乱数信号SG14を生成し、生成したこれらの信号を、DRAM113に記憶させる。

## [0046]

TRNG115は、PRF演算回路111aに対して第1乱数信号SG11を供給すると共に、第2乱数信号SG12を生成し、生成した第2乱数信号SG12をDRAM113に記憶させる。TRNG115は、生成した第1乱数信号SG11を、端末装置13が更新データを復号するための鍵を生成するための情報として出力する。また、TRNG115は、生成した第2乱数信号SG12を、端末装置13に対する要求信号であるチャレンジコードとして出力する。

#### [0047]

図 5 に戻る。サーバ装置 1 1 は、TRNG 1 1 5 が出力した第 1 乱数信号 S G 1 1 および第 2 乱数信号 S G 1 2 を、中継装置 1 2 に送信する(ステップ S 1 4)。

## [0048]

中継装置12は、サーバ装置11から受け取った第1乱数信号SG11および第2乱数信号SG12を、端末装置13に送信する(ステップS15)。

#### [0049]

図7を参照しながら、第1乱数信号SG11および第2乱数信号SG12を受け取った端末装置13が行う処理の概要について説明する。図7において、端末装置13が有する第3半導体装置130は、サーバ装置11から受け取った、鍵を生成するための信号(第1乱数信号SG11)を使用して、暗号化された更新データを復号する際に使用する鍵(第7乱数信号SG114)を生成する。また、第3半導体装置130は、サーバ装置11から受け取った、チャレンジコード(第2乱数信号SG12)に対する応答信号としてレスポンスコード(第9乱数信号SG16)を出力する。さらに、第3半導体装置130は、応答する際にサーバ装置11を認証するためのチャレンジコード(第3乱数信号SG15)を出力する。

## [0050]

図7は、実施の形態1にかかる端末装置の機能ブロック図である。図7において、PRF演算回路が2つ存在するため、ここでは説明の便宜上一方をPRF演算回路131a\_1、もう一方をPRF演算回路131a\_2と称する。当然ながら、PRF演算回路131a\_1とPRF演算回路131a\_2とは、別の構成であっても構わないし、一個の構成であって、異なる演算を行うものであってよい。また、以降の説明においても1つのブロック図において同じ種類の構成が複数存在する場合には、同様の符号をつけることがある。

## [0051]

端末装置13が有する第3半導体装置130は、受け取った第1乱数信号SG11をCPU131が有するPRF演算回路131aに入力する。また、PRF演算回路131aは、NVRAM132が記憶しているマスタ鍵SG06を入力信号として読み出す。

## [0052]

PRF演算回路131a\_1は、マスタ鍵SG06と、第1乱数信号SG11とを入力として、第6乱数信号SG13および第7乱数信号SG14を生成する。PRF演算回路131a\_1は、生成した信号のうち、第6乱数信号SG13をPRF演算回路131a\_2に入力する。また、PRF演算回路131a\_1は、生成した信号のうち、第7乱数信号SG14をDRAM133に記憶させる。

# [0053]

第6乱数信号SG13が入力されたPRF演算回路131a\_2は、さらに中継装置12から受け取った第2乱数信号SG12を、入力信号として受け取る。また、PRF演算回路131a\_2は、もう一つの入力信号として、TRNG135から第3乱数信号SG15を受け取る。

## [0054]

PRF演算回路131a\_2は、第6乱数信号SG13、第2乱数信号SG12、および第3乱数信号SG15を入力信号として、第9乱数信号SG16および第10乱数信号SG17を生成する。PRF演算回路131a\_2は、生成したこれらの信号のうち、第9乱数信号SG16を、サーバ装置11から受け取った要求信号に対する応答信号として出力する。また、PRF演算回路131a\_2は、生成したこれらの信号のうち、第10乱数信号SG17を、DRAM133に記憶させる。

## [0055]

TRNG135は、PRF演算回路131a\_2の入力信号として生成した第3乱数信号SG15を、サーバ装置11から受け取った要求信号に対する応答信号として出力する。すなわち、第3半導体装置130は、第9乱数信号SG16と、第3乱数信号SG15

10

20

30

40

とを、サーバ装置11から受け取った要求信号に対する応答信号として出力する。

## [0056]

図 5 に戻る。端末装置 1 3 は、第 3 半導体装置 1 3 0 が出力した第 3 乱数信号 S G 1 5 および第 9 乱数信号 S G 1 6 を、中継装置 1 2 に送信する(ステップ S 1 6 )。

#### [0057]

中継装置12は、サーバ装置11から受け取った第3乱数信号SG15および第9乱数信号SG16を、サーバ装置11に送信する(ステップS17)。

## [0058]

図8を参照しながら、第3乱数信号SG15および第9乱数信号SG16を受け取ったサーバ装置11が行う処理について説明する。図8において、サーバ装置11が有する第1半導体装置110は、端末装置13から受け取った、チャレンジコード(第3乱数信号SG15)に対する応答信号としてレスポンスコード(第11乱数信号SG19)を出力する。また、第1半導体装置110は、端末装置13から受け取った、レスポンスコード(第9乱数信号SG16)が期待値と一致するか否かを比較し、比較結果に応じた暗号文SG23を出力する。

#### [0059]

図8は、実施の形態1にかかる第1半導体装置の機能ブロック図である。第1半導体装置110は、受け取った第3乱数信号SG15をPRF演算回路111aに入力する。PRF演算回路111aは、さらに入力信号として、DRAM113から第6乱数信号SG13および第2乱数信号SG12を受け取る。

## [0060]

PRF演算回路111aは、第6乱数信号SG13、第2乱数信号SG12、および第3乱数信号SG15を入力信号として、第8乱数信号SG18と、第11乱数信号SG19とを生成する。PRF演算回路111aは、生成した第8乱数信号SG18を比較回路111bに送信する。また、PRF演算回路111aは、生成した第11乱数信号SG19を端末装置13から受け取ったチャレンジコードに応答するレスポンスコードとして出力する。

## [0061]

第1半導体装置110は、受け取った第9乱数信号SG16を、比較回路111bに入力する。比較回路111bは、入力信号として、PRF演算回路111aが出力した第8乱数信号SG18と、端末装置13が出力した第9乱数信号SG16とをそれぞれ受け取り、受け取ったこれらの信号を比較する。すなわち、サーバ装置11は、サーバ装置11が送信したチャレンジコードに対して端末装置13が応答したレスポンスコードが期待値と一致するか否かを比較する。比較回路111bがデータを比較した結果、これらの信号が一致しない場合、比較回路111bは、比較結果信号SG20として「0」を出力する。一方、比較した結果、これらの信号が一致する場合、比較回路111bは、比較結果信号SG20を、選択回路111dに供給する。

## [0062]

AE暗号化回路111cは、NVRAM112から入力信号として更新データSG02と、更新バージョンデータSG04を受け取る。また、AE暗号化回路111cは、更新データSG02および更新バージョンデータSG04を暗号化するための鍵情報である第7乱数信号SG14をDRAM113から受け取る。AE暗号化回路111cは、これらの入力信号に基づいて、暗号化更新データSG21を出力し、出力した暗号化更新データSG21を選択回路111dに入力する。

# [0063]

TRNG115は、第4乱数信号SG22を生成し、生成した信号を、選択回路111 dに入力する。TRNG115が出力する第4乱数信号SG22は、真性乱数であって、 信号の桁数が暗号化更新データSG21と同じになるように設定されている。すなわち、 復号できない場合、暗号化更新データSG21と第4乱数信号SG22との区別は容易で 10

20

30

40

はない。

## [0064]

選択回路111dは、入力信号として、上述した暗号化更新データSG21と第4乱数信号SG22とを受け取るとともに、選択制御信号として、比較結果信号SG20を受け取る。選択回路111dは、比較結果信号SG20の値が「1」の場合、出力信号である暗号文SG23として暗号化更新データSG21を選択する。一方、選択回路111dは、比較結果信号SG20の値が「0」の場合、出力信号である暗号文SG23として暗号化更新データSG21に代えて第4乱数信号SG22を選択する。選択回路111dは、このようにして信号を選択し、選択した信号を暗号文SG23として出力する。

## [0065]

このように、第1半導体装置110は、端末装置13の認証が正しく行われた場合には 更新データを含む暗号化信号を出力し、端末装置13の認証が正しく行われなかった場合 には、正しく認証されない送信先にとって暗号化更新データSG21との区別が容易では ない乱数信号を送信する。このように、正しく認証されない相手に対して形式的に正しい 信号と区別が容易ではない信号を送信することにより、第三者からの不要な攻撃を抑制す ることができる。

## [0066]

図8の構成により、第1半導体装置110は、チャレンジコードである第3乱数信号SG15に対するレスポンスコードとして第11乱数信号SG19を出力し、端末装置13から受け取ったレスポンスコードである第9乱数信号SG16に応じて暗号文SG23を出力する。

#### [0067]

図5に戻る。サーバ装置11は、第1半導体装置110が出力した第11乱数信号SG 19および暗号文SG23を、中継装置12に送信する(ステップS18)。

#### [0068]

中継装置12は、サーバ装置11から受け取った第11乱数信号SG19および暗号文SG23を、端末装置13に送信する(ステップS19)。

#### [0069]

図9を参照しながら、第11乱数信号SG19および暗号文SG23を受け取った端末装置13が行う処理について説明する。図9において、端末装置13が有する第3半導体装置13のは、サーバ装置11から受け取った、レスポンスコード(第11乱数信号SG19)を使用して、サーバ装置11に対する認証を行う。また、第3半導体装置130は、サーバ装置11に対する認証結果に応じて、サーバ装置11から受け取った暗号文SG23を復号するか否かを判定し、判定結果に応じた処理を行う。

# [0070]

図9は、実施の形態1にかかる第3半導体装置の機能ブロック図である。図9において、端末装置13の第3半導体装置130は、サーバ装置11から受け取った第11乱数信号SG19と、DRAM133が記憶している第10乱数信号SG17とを比較回路131b\_1に入力し、これらの信号を比較する。比較回路131b\_1は、これらの信号が一致していない場合には比較結果信号SG24として「0」を出力し、これらの信号が一致している場合には比較結果信号SG24として「1」を出力し、出力した信号を、AE復号回路131cに供給する。

## [0071]

また、第3半導体装置130は、サーバ装置11から受け取った、暗号文SG23を、AE暗号化回路111cは、さらに入力信号として、DRAM133が記憶している第7乱数信号SG14を受け取る。

## [0072]

10

20

30

40

ーバ装置11の認証が正しく行われたことを意味している。この場合、AE復号回路13 1cは、暗号文SG23を復号する以下の処理を実行する。

## [0073]

このように、認証が正しく行われなかった場合に受け取った暗号文の復号処理を実行しないことにより、悪意ある第三者等からのアップデート要求を防止することが出来る。

## [0074]

A E 復号回路 1 3 1 c は、暗号文 S G 2 3 と、暗号文 S G 2 3 を復号するための鍵情報である第 7 乱数信号 S G 1 4 とを入力信号として、暗号文 S G 2 3 を復号する。暗号文 S G 2 3 が復号されると、A E 復号回路 1 3 1 c は、出力信号に含まれている更新バージョンデータ S G 0 4 を比較回路 1 3 1 b 2 に供給する。比較回路 1 3 1 b 2 2 は、NVRAM 1 3 2 から第 3 半導体装置 1 3 0 が記憶する現在のファームウェアのバージョン情報である更新前バージョンデータ S G 0 3 を受け取る。比較回路 1 3 1 b 2 2 は、更新バージョンデータ S G 0 4 が更新前バージョンデータ S G 0 3 より大きいか否かを比較し、比較結果信号 S G 2 5 を更新制御回路 1 3 1 d に供給する。

## [0075]

更新制御回路131dは、比較回路131b \_\_ 2から比較結果信号SG25を受け取ると共に、AE復号回路131cから復号された更新データSG02を受け取る。更新制御回路131dは、NVRAM132が記憶するファームウェアのバージョンよりも、復号されたファームウェアのバージョンが大きい場合には、NVRAM132が記憶するファームウェアを更新する処理を行う。ファームウェアを更新する処理として、更新制御回路131dは、更新前データSG01に代えて、更新データSG02をNVRAM132に記憶させ、更新前バージョンデータSG03に代えて更新バージョンデータSG04をNVRAM132に記憶させる。

#### [0076]

実施の形態 1 にかかる送受信システムは、以上のような構成となっている。上述した説明から、送受信システム 1 の処理をまとめると、以下のように説明することが出来る。すなわち、サーバ装置と、前記サーバ装置から更新データを受け取る端末装置とを含む送受信システム 1 は、以下のように処理を実行する。

## [0077]

まず、サーバ装置11は、認証付き暗号を復号するための鍵を生成するための信号(1 11)および端末装置13を認証するためのチャレンジコード(112)を端末装置13 へ送信する。

#### [0078]

端末装置13は、チャレンジコード(112)に対するレスポンスコードと、サーバ装置11を認証するためのチャレンジコードをサーバ装置11へ送信する。

## [0079]

サーバ装置は、レスポンスコードの検証を行い、検証結果に応じて、予め設定された暗号を送信するとともに、端末装置13から受け取ったチャレンジコードに対するレスポンスコードを端末装置13へ送信する。

## [0800]

端末装置13は、サーバ装置11から受け取ったレスポンスコードの検証を行い、検証結果に応じて、レスポンスコードと共に受け取った暗号に対する処理を決定する。

## [0081]

また、送受信システム1は、サーバ装置11と端末装置13との間に中継装置12が介在し、サーバ装置11と中継装置12とが通信し、中継装置12と端末装置13とが通信する。

## [0082]

送受信システム1は、サーバ装置11と端末装置13とが有する共通鍵を用いて更新データを送受信する。また、送受信システム1は、サーバ装置11と端末装置13とが有する共通の擬似ランダム関数を用いて信号をそれぞれ演算する。そのため、送受信システム

10

20

30

40

1は、更新データの秘匿性を維持し、第三者への情報漏えいを防ぐことが出来る。

## [0083]

送受信システム1は、認証付き暗号化技術を利用して更新データの送受信をおこなう。 そのため、仮に、端末装置13に改ざんされた更新データが供給された場合、送受信システム1は、認証タグを検証することにより、正しくないデータによる更新を防止できる。

## [0084]

また、送受信システム1は、サーバ装置11と端末装置13との間に中継装置12が介在する。これにより、送受信システム1は、サーバ装置11の通信方式と、端末装置13の通信方式が異なる場合にも、サーバ装置11と端末装置13との信号の送受信が可能となる。したがって、送受信システム1は、例えば、端末装置13が直接インターネットに接続していない場合においても、ファームウェアの更新を行うことが出来、運用コストを低減することができる。

#### [0085]

また、送受信システム1は、サーバ装置11と端末装置13とがそれぞれ共通の鍵を有している。このような構成により、送受信システム1は、高速に処理をおこなうことができる。例えば、一般的な公開鍵を利用したシステムと比較すると、本実施の形態にかかるシステムの処理速度は100倍程度速い。

#### [0086]

< 実施の形態1の変形例>

以下に、図10を参照しながら、実施の形態1の変形例について説明する。実施の形態 1の変形例に係る送受信システム1は、端末装置13がTRNG135を有していない点 において、上述した端末装置13の構成と異なる。

## [0087]

図10は、実施の形態1の変形例にかかる第3半導体装置の機能ブロック図である。図10の機能ブロック図は、図5におけるステップS15において第1乱数信号SG11および第2乱数信号SG12を受け取った端末装置13が行う処理について説明するものであって、実施の形態1の図7に対応する。

#### [0088]

図10は、実施の形態1にかかる端末装置の機能ブロック図である。図10を参照しながら、第1乱数信号SG11および第2乱数信号SG12を受け取った端末装置13が行う処理について上述した実施の形態1と異なる点について概要を説明する。図10において、端末装置13が有する第3半導体装置130は、サーバ装置11を認証するためのチャレンジコードとして、第3乱数信号SG15に代えてPRF演算回路131a\_2が第12乱数信号SG07\_nを生成する。第3半導体装置130は、PRF演算回路131a\_2が生成した第12乱数信号SG07\_nを、NVRAM132に記憶させる。また、第3半導体装置130は、第9乱数信号SG16をレスポンスコードとして出力すると共に、第12乱数信号SG07\_nをチャレンジコードとして出力する。

## [0089]

以下に、第12乱数信号SG07\_nについて詳細を説明する。図10において、第3半導体装置130は、NVRAM132に予め第12乱数信号SG07\_nの初期値として、乱数である第12乱数信号SG07\_0を記憶している。第3半導体装置130が最初に処理を行う場合、PRF演算回路131aは、NVRAM132にアクセスし、第12乱数信号SG07\_0を受け取る。また、PRF演算回路131a\_2は、第2乱数信号SG12と、PRF演算回路131a\_1が出力した第6乱数信号SG13を同じく入力信号として受け取る。PRF演算回路131a\_2は、これらを入力信号として演算を行い、出力信号として、第9乱数信号SG16、第10乱数信号SG17、および第12乱数信号SG07\_1を生成する。PRF演算回路131a\_2は、これらの出力信号のうち、第12乱数信号SG07\_1を、サーバ装置11を認証するためのチャレンジコードとして外部に出力するとともに、第12乱数信号SG07\_1を、NVRAM132に記憶させる。PRF演算回路131a\_2は、演算の度に第12乱数信号SG07\_nを

10

20

30

40

新しい値に順次更新し、更新した信号をNVRAM132に記憶する。

## [0090]

これにより、端末装置13は、TRNG135を有さず、サーバ装置11の認証を行うことが出来る。したがって、送受信システム1は、端末装置13を簡便な構成とすることができる。したがって、実施の形態1変形例において、送受信システム1は、簡便な構成により、効率的かつ安全に更新プログラムの授受を行い、プログラムの更新を実現することができる。

## [0091]

なお、実施の形態 1 の変形例としては、これに限らず、例えば、チャレンジコードとして、上述した第 3 乱数信号 S G 1 5 や第 1 2 乱数信号 S G 0 7 \_\_ n に代えて、外部に出力する度にインクリメントする数値を用いてもよい。このような構成にすることにより、実施の形態 1 変形例において、送受信システム 1 は、簡便な構成により、効率的かつ安全に更新プログラムの授受を行い、プログラムの更新を実現することができる。

## [0092]

## < 実施の形態 2 >

次に、図11~図16を参照して本発明の実施の形態について説明する。実施の形態2にかかる送受信システム2は、サーバ装置のCPUの構成、および、端末装置のCPUの構成が実施の形態1と異なる。また、実施の形態2にかかる送受信システム2は、サーバ装置において端末装置が有するファームウェアのバージョンを管理する点において、実施の形態1にかかる送受信システム1と異なる。

## [0093]

図11は、実施の形態2にかかる送受信システムのハードウェア構成図である。送受信システム2は、サーバ装置21、中継装置22、および端末装置23を有している。サーバ装置21は、第1半導体装置210を有しており、第1半導体装置210は、CPU211を含んでいる。CPU211は、更新制御回路211eを含む点において、実施の形態1にかかるCPU1111と異なる。端末装置23は、第3半導体装置230を有しており、第3半導体装置230は、CPU231を含んでいる。CPU231は、選択回路231eを含む点において、実施の形態1にかかるCPU231と異なる。

## [0094]

次に、図12を参照しながら、送受信システム2にかかるそれぞれの装置が有する信号と、それぞれの装置が送受信する信号について説明する。図12は、実施の形態2にかかる送受信システムの送受信信号を示した図である。

#### [0095]

サーバ装置 2 1 は、N V R A M 1 1 2 に、更新前バージョンデータ S G 0 3 を記憶している点において、実施の形態 1 にかかるサーバ装置 1 1 と異なる。すなわち、サーバ装置 2 1 は、端末装置 2 3 の現在のファームウェアのバージョンが何であるかを管理している。なお、端末装置 2 3 は、実施の形態 1 にかかる端末装置 1 3 と同様の信号を記憶している。

## [0096]

以降は、送受信システム 2 にかかるそれぞれの装置が送受信する信号と、それぞれの装置が行う処理について、実施の形態 1 と異なる点について説明する。図 1 2 に示すように、送受信システム 2 は、ステップ S 1 1 からステップ S 1 5 までの処理は、実施の形態 1 と同様である。

## [0097]

次に、図13を参照しながら、第1乱数信号SG11および第2乱数信号SG12を受け取った端末装置23が行う処理について、図7に示した実施の形態1と異なる点について説明する。図13において、端末装置23が有する第3半導体装置230は、PRF演算回路231a\_2が出力する信号が、実施の形態1と異なる。すなわち、PRF演算回路231a\_2は、第6乱数信号SG13、第2乱数信号SG12、および第3乱数信号SG15を入力信号とした演算において、第9乱数信号SG16と第10乱数信号SG1

10

20

30

40

7に加え、第13乱数信号SG26も出力する。第13乱数信号SG26は、ファームウェアの更新が正しく行われたことを示すための信号として用いられる。PRF演算回路231a\_2は、出力した第13乱数信号SG26をDRAM133に記憶させる。図13において、上述の処理を実行した第3半導体装置230は、実施の形態1と同様に、第3乱数信号SG16を出力する。

## [0098]

図12に戻る。端末装置23は、第3乱数信号SG15および第9乱数信号SG16を中継装置22に送信し(ステップS26)、中継装置22はこれらの信号をサーバ装置21に送信する(ステップS27)。

## [0099]

次に、図14を参照しながら、第3乱数信号SG15および第9乱数信号SG16を受け取ったサーバ装置21が行う処理について、図8に示した実施の形態1と異なる点について説明する。図14は、実施の形態2にかかるサーバ装置の機能ブロック図である。

## [0100]

図14において、サーバ装置21が有する第1半導体装置210は、PRF演算回路211a出力する信号が、実施の形態1と異なる。すなわち、PRF演算回路211aは、第2乱数信号SG12、第6乱数信号SG13、および第3乱数信号SG15を入力信号とした演算において、第8乱数信号SG18と第11乱数信号SG19に加え、第14乱数信号SG27も出力する。第14乱数信号SG27は、端末装置23から受け取るファームウェア更新結果信号を検証するための信号として用いられる。PRF演算回路211aは、出力した第14乱数信号SG27をDRAM113に記憶させる。図14において、上述の処理を実行した第1半導体装置210は、実施の形態1と同様に、第11乱数信号SG19および暗号文SG23を出力する。

#### [0101]

図12に戻る。サーバ装置21は、第11乱数信号SG19および暗号文SG23を中継装置22に送信し(ステップS28)、中継装置22はこれらの信号を端末装置23に送信する(ステップS29)。

#### [0102]

次に、図15を参照しながら、第11乱数信号SG19および暗号文SG23を受け取った端末装置23が行う処理について、図9に示した実施の形態1と異なる点について説明する。図15において、端末装置23が有する第3半導体装置230は、更新制御回路231dが更新結果を出力し、更新制御回路231dが出力した更新結果に基づいて、第3半導体装置230が更新結果信号をサーバ装置21に送信する点が、実施の形態1と異なる。

## [0103]

図15は、実施の形態2にかかる端末装置の機能ブロック図である。図15において、更新制御回路231dは、比較回路231bから比較結果信号SG25を受け取ると共に、AE復号回路231cから復号された更新データSG02を受け取る。更新制御回路231dは、NVRAM132が記憶するファームウェアのバージョンよりも、復号されたファームウェアのバージョンが大きい場合には、NVRAM132が記憶するファームウェアを更新する処理を行う。

#### [0104]

更新制御回路231 d は、ファームウェアを更新する処理が完了すると、かかる処理が成功したか否かを示す第1更新結果信号SG28を生成し、生成した第1更新結果信号SG28を、選択回路231eに選択制御信号として供給する。ファームウェアを更新する処理が成功した場合、更新制御回路231 d は、第1更新結果信号SG28として「1」を出力する。一方、ファームウェアを更新する処理が成功しなかった場合、更新制御回路231 d は、第1更新結果信号SG28として「0」を出力する。

#### [0105]

選択回路231eは、入力信号として、DRAM133から第13乱数信号SG26を

10

20

30

40

受け取り、さらに、TRNG135から第5乱数信号SG29を受け取る。第5乱数信号SG29は、第13乱数信号SG26と同じ桁数の真性乱数である。選択回路231eは、更新制御回路231dから第1更新結果信号SG28として「1」を受け取った場合、出力する信号として第13乱数信号SG26を選択する。一方、選択回路231eは、更新制御回路231dから第1更新結果信号SG28として「0」を受け取った場合、出力する信号として第5乱数信号SG29を選択する。選択回路231eは、選択した信号を、第2更新結果信号SG30として出力する。第3半導体装置230は、選択回路231eが出力した第2更新結果信号SG30を出力する。

#### [0106]

ファームウェアを更新する処理が成功したか否かを示すための信号をこのように出力することにより、かかる信号は秘匿性を維持し、第三者への情報漏えいを防ぐことが出来る

[0107]

図 1 2 に戻る。端末装置 2 3 は、第 2 更新結果信号 S G 3 0 を中継装置 2 2 に送信し(ステップ S 3 0 )、中継装置 2 2 はこれをサーバ装置 2 1 に送信する(ステップ S 3 1 )

## [0108]

次に、図16を参照しながら、サーバ装置21が行う処理について説明する。図16は、実施の形態2にかかるサーバ装置の機能ブロック図である。図16において、サーバ装置21が有する第1半導体装置210は、第2更新結果信号SG30を受け取ると、受け取った第2更新結果信号SG30を比較回路211bは、DRAM113から第14乱数信号SG27を受け取る。すなわち、比較回路211bは、第2更新結果信号SG30と第14乱数信号SG27とを比較し、比較結果信号SG31を更新制御回路211eに出力する。

#### [0109]

比較回路 2 1 1 b は、第 2 更新結果信号 S G 3 0 と第 1 4 乱数信号 S G 2 7 とが一致していた場合は、比較結果信号 S G 3 1 として「1」を出力する。一方、比較回路 2 1 1 b は、第 2 更新結果信号 S G 3 0 と第 1 4 乱数信号 S G 2 7 とが一致していない場合は、比較結果信号 S G 3 1 として「0」を出力する。

## [0110]

更新制御回路211eは、比較結果信号SG31として「0」を受け取った場合、NVRAM112のデータを更新する処理を実行しない。この場合、端末装置23が更新処理に失敗したと判断し比較結果信号SG31をNVRAM112に保存してもよい。一方、更新制御回路211eは、比較結果信号SG31として「1」を受け取った場合、NVRAM112のデータを更新する処理を実行する。すなわち、更新制御回路211eは、NVRAM112の更新データ領域にアクセスし、端末装置23に送信した更新データにかかる更新バージョンデータSG04を受け取る。そして、更新制御回路211eは、NVRAM112のデータベース領域に記憶されている更新前バージョンデータSG03に代えて、更新バージョンデータSG04を記憶させる処理を行う。

## [0111]

以上に説明した構成を有することにより、実施の形態 2 にかかる送受信システムは、端末装置の更新データを容易に管理できる。したがって、例えばサーバ装置が複数の端末装置を管理する場合に、それぞれの有するデータの更新状況を管理することができ、ネットワーク脆弱性等を把握することが可能となる。

## [0112]

# <実施の形態3>

次に、図17から図21を参照して、実施の形態3について説明する。実施の形態3にかかる送受信システム3は、端末装置間の通信処理が実施の形態1と異なる。すなわち、実施の形態3にかかる送受信システム3は、まず、サーバ装置31と中継装置32との通信を行い、次に、サーバ装置31と中継装置32との通信を行うことがない状況において

10

20

30

40

、中継装置32と端末装置33との間の通信を行う。また、実施の形態3にかかる送受信システム3は、中継装置32の構成が実施の形態1と異なる。

## [0113]

図17は、実施の形態3にかかる第2半導体装置のハードウェア構成図である。送受信システム3において、中継装置32と端末装置が有する第2半導体装置320は、および、CPU321の構成が、実施の形態1にかかるCPU121と異なる。CPU321は、PRF演算回路321a、比較回路321b、AE復号回路321c、および選択回路321dを主な構成として有している。また、第2半導体装置320は、TRNG325を有している点が実施の形態1と異なる。

## [0114]

次に、図18を参照しながら、送受信システム3にかかるそれぞれの装置が有する信号と、それぞれの装置が送受信する信号について説明する。図18は、実施の形態3にかかる送受信システムの送受信信号を示した図である。

## [ 0 1 1 5 ]

図18に示す送受信システム3は、サーバ装置31のNVRAM112が共通鍵SG32を記憶している点、および中継装置32のNVRAM122が共通鍵SG32を記憶している点において、実施の形態1と異なる。なお、端末装置33のNVRAM132が記憶するデータは、実施の形態1と同様である。

#### [ 0 1 1 6 ]

以降は、送受信システム3にかかるそれぞれの装置が送受信する信号と、それぞれの装置が行う処理について、実施の形態1と異なる点について説明する。図18に示すように、送受信システム3は、ステップS11からステップS13までの処理は、実施の形態1と同様である。

#### [0117]

次に、図19を参照しながら、サーバ装置11が行う処理について実施の形態1と異なる点について説明する。図19は、実施の形態3にかかるサーバ装置の機能ブロック図である。図19において、サーバ装置11の第1半導体装置110は、暗号化された更新データを復号する際に使用する鍵を生成するための信号(第1乱数信号SG11)と、端末装置13を認証するためのチャレンジコード(第2乱数信号SG12)とを出力する。第1乱数信号SG11および第2乱数信号SG12を出力するまでの処理については実施の形態1と同様であるため説明を省略する。

## [0118]

第1半導体装置110は、共通鍵SG32と、第6乱数信号SG13とをAE暗号化回路111c\_1に入力する。AE暗号化回路111c\_1は、これらの信号を受け取り、受け取った信号に対して認証付き暗号化処理を行い、暗号文SG33を生成する。

## [0119]

また、第1半導体装置110は、更新データSG02、更新バージョンデータSG04、および第7乱数信号SG14をAE暗号化回路111c\_2に入力する。AE暗号化回路111c\_2は、これらの信号を受け取り、受け取った信号に対して認証付き暗号化処理を行い、暗号化更新データSG21を生成する。

## [0120]

以上の処理により、第1半導体装置110は、第1乱数信号SG11、第2乱数信号SG12、暗号文SG33、および暗号化更新データSG21を外部へ出力する。そして、サーバ装置11は、これらの信号を中継装置32に送信する(図18のステップS31)

# [0121]

次に、図20を参照しながら、上述の信号を受け取った中継装置が行う処理について説明する。図20は、実施の形態3にかかる中継装置の機能ブロック図である。図20において、中継装置32の第2半導体装置320は、以下の処理を行う。

## [0122]

50

40

10

20

まず、AE復号回路321cは、暗号文SG33を入力信号として受け取り、さらにNVRAM122に記憶されている共通鍵SG32を入力信号として受け取る。そして、AE復号回路321cは、これらを入力信号として、暗号文SG33に含まれていた第6乱数信号SG13をNVRAM122に記憶させる。

## [0123]

次に、第2半導体装置320は、第1乱数信号SG11、第2乱数信号SG12、および暗号化更新データSG21をNVRAM122に記憶させるとともに、第1乱数信号SG11および第2乱数信号SG12を端末装置33へ出力する処理を行う。中継装置32は、これらの信号を端末装置33に送信する(図18のステップS32)。

## [0124]

次に、端末装置33は、中継装置32から受け取った第1乱数信号SG11および第2乱数信号SG12を処理し、中継装置32に対して第3乱数信号SG15および第9乱数信号SG16を送信する(図18のステップS33)。端末装置33が第1乱数信号SG11および第2乱数信号SG12を処理し、中継装置32に対して第3乱数信号SG15および第9乱数信号SG16を送信する処理は、実施の形態1において図7を参照しながら説明したものと同様である。

## [0125]

次に、図21を参照しながら、第3乱数信号SG15および第9乱数信号SG16を受け取った中継装置32が行う処理について説明する。図21は、図19は、実施の形態3にかかる中継装置の機能ブロック図である。

## [0126]

第2半導体装置320において、PRF演算回路321aは、入力信号として、端末装置33が送信した第3乱数信号SG15を受け取る。また、PRF演算回路321aは、入力信号として、NVRAM122に記憶している第6乱数信号SG13、および第2乱数信号SG12を受け取る。PRF演算回路321aは、これらの信号を入力信号として演算処理を行い、第8乱数信号SG18、および第11乱数信号SG19を生成する。

#### [0127]

第2半導体装置320は、PRF演算回路321aが生成した第11乱数信号SG19を、端末装置33のチャレンジコード(第3乱数信号SG15)に対するレスポンスコードとして出力する。

## [0128]

比較回路321 b は、PRF演算回路321 a が生成した第8乱数信号SG18と、中継装置32からレスポンスコードとして受け取った第9乱数信号SG16とをそれぞれ受け取り、受け取ったこれらの信号を比較する。

## [0129]

比較回路 3 2 1 b がデータを比較した結果、これらの信号が一致しない場合、比較回路 3 2 1 b は、比較結果信号 S G 2 0 として「0」を出力する。一方、比較した結果、これらの信号が一致する場合、比較回路 3 2 1 b は、比較結果信号 S G 2 0 として「1」を出力する。比較回路 3 2 1 b は出力した比較結果信号 S G 2 0 を、選択回路 3 2 1 d に供給する。

#### [0130]

TRNG125は、第4乱数信号SG22を生成し、生成した信号を、選択回路321 dに入力する。TRNG125が出力する第4乱数信号SG22は、信号の桁数が暗号化 更新データSG21と同じである真性乱数である。

# [0131]

選択回路321dは、入力信号として、NVRAM122に記憶されている暗号化更新データSG21と第4乱数信号SG22とを受け取るとともに、選択制御信号として、比較結果信号SG20を受け取る。選択回路321dは、比較結果信号SG20の値が「1」の場合、出力信号である暗号文SG23として暗号化更新データSG21を選択する。

10

20

30

40

一方、選択回路321dは、比較結果信号SG20の値が「0」の場合、出力信号である暗号文SG23として暗号化更新データSG21に代えて第4乱数信号SG22を選択する。選択回路321dは、このようにして信号を選択し、選択した信号を暗号文SG23として出力する。

## [0132]

中継装置32は、第2半導体装置320が出力した第11乱数信号SG19および暗号文SG23を、端末装置33に送信する(図18のステップS34)。以降の端末装置33における処理は、実施の形態1において図9を参照しながら説明したものと同様である

[0133]

なお、図18のステップS11およびステップS12において中継装置32と端末装置33とが送受信するデータは、秘匿性があるものではない。そのため、端末装置33にかかる更新前バージョンデータSG03および識別子SG05を、中継装置32が予め記憶しておいてもよい。

## [0134]

このような構成により、実施の形態3にかかる送受信システム3は、サーバ装置31と中継装置32との通信と、中継装置32と端末装置33との通信と、を分離してデータの更新処理を行うことが出来る。例えば、送受信システム3は、端末装置33が遠隔の地にある場合や、近距離通信のみを備えている場合であって、サーバ装置31と中継装置32との通信を行うことが出来ない環境であっても、端末装置33に対して更新データを提供することができる。

[0135]

なお、本発明は上記実施の形態に限られたものではなく、趣旨を逸脱しない範囲で適宜 変更することが可能である。

#### [0136]

例えば、上記の実施形態の一部又は全部は、以下の付記のようにも記載され得るが、以下には限られない。

## [0137]

(付記1)

メモリと、乱数生成回路と、制御回路と、を有し、外部端末装置に更新データを提供する半導体装置であって、

前記メモリは、鍵情報を記憶し、

前記乱数生成回路は、第1乱数信号および第2乱数信号を生成し、

前記制御回路は、

前記第1乱数信号および前記鍵情報から第6乱数信号および第7乱数信号を生成し、

前記更新データに対して第7乱数信号を用いて暗号化更新データを生成し、

前記外部端末装置に送信する要求信号として前記第1乱数信号および前記第2乱数信号 を生成し、

前記要求信号に対する応答信号として前記外部端末装置から第 1 応答信号および第 2 応答信号を受け取り、

前記第1応答信号と前記第2乱数信号と前記第6乱数信号とを入力信号として、第8乱数信号を生成し、

前記第2応答信号と前記第8乱数信号とが一致している場合に、前記暗号化更新データを前記外部端末装置に提供する、半導体装置。

#### [0138]

(付記2)

前記制御回路は、

前記第6乱数信号、前記第7乱数信号、および前記第8乱数信号を、

予め設定された同一の擬似ランダム関数に入力することよりそれぞれ演算する、

付記1に記載の半導体装置。

10

20

30

40

## [0139]

(付記3)

前記制御回路は、前記第2応答信号と前記第8乱数信号とが一致していない場合に、前記暗号化更新データに代えて、前記暗号化更新データと同じ桁数の乱数信号を前記外部端末装置に提供する、

付記1に記載の半導体装置。

#### [0140]

(付記4)

前記制御回路は、前記外部端末装置から、提供した前記暗号化更新データに対する応答信号である第3応答信号を受け取った場合に、前記第3応答信号が、前記第1応答信号と前記第2乱数信号と前記第6乱数信号とを入力信号として生成された第10乱数信号と一致するか否かを判定し、一致する場合には、データが更新されたことを登録し、一致しない場合には、データが更新されなかったことを登録する、

付記1に記載の半導体装置。

## [0141]

(付記5)

メモリと、制御回路と、を有し、外部サーバ装置から暗号化更新データを受け取る半導体装置であって、

前記メモリは、更新前データと、鍵情報を記憶し、

前記制御回路は、

前記外部サーバ装置から第1乱数信号および第2乱数信号を要求信号として受け取り、 前記第1乱数信号および前記鍵情報から第6乱数信号および第7乱数信号を生成し、

前記第2乱数信号と前記第6乱数信号とを入力信号として、第9乱数信号および第10 乱数信号を生成し、

予め設定された信号を含むチャレンジコードを生成し、

前記要求信号に対する応答信号として前記第9乱数信号および前記チャレンジコードを前記外部サーバ装置へ出力し、

出力した前記応答信号に基づいて前記外部サーバ装置から認証信号と前記暗号化更新データとを受け取り、

受け取った前記認証信号と、前記第10乱数信号とが一致している場合に、前記外部サーバ装置から受け取った前記暗号化更新データの復号処理を行う、

半導体装置。

## [0142]

(付記6)

前記制御回路は、

前記第6乱数信号、前記第7乱数信号、前記第9乱数信号、および前記第10乱数信号を

予め設定された同一の擬似ランダム関数に入力することよりそれぞれ演算する、 付記 5 に記載の半導体装置。

## [0143]

(付記7)

前記制御回路は、受け取った前記認証信号と、前記第10乱数信号とが一致していない場合に、前記外部サーバ装置から受け取った前記暗号化更新データの復号処理を行わない

付記5に記載の半導体装置。

# [0144]

(付記8)

前記制御回路は、予め設定された桁数の数値を順次インクリメントすることにより前記 チャレンジコードを生成する、

付記5に記載の半導体装置。

10

20

30

40

## [0145]

(付記9)

前記制御回路は、前記第2乱数信号と前記第6乱数信号とを入力信号として、第12乱 数信号を生成することにより前記チャレンジコードを生成する、

付記5に記載の半導体装置。

## [0146]

(付記10)

第3乱数信号を生成する乱数生成回路をさらに備え、

前記制御回路は、前記第9乱数信号および前記第10乱数信号を生成する際に、前記第 2 乱数信号と前記第6 乱数信号に加えて前記第3 乱数信号も入力信号として入力し、

前記チャレンジコードとして第3乱数信号を前記外部サーバ装置へ出力する、

付記5に記載の半導体装置。

#### [0147]

(付記11)

前記制御回路は、少なくとも前記第2乱数信号と前記第6乱数信号とを入力信号として 含む擬似ランダム関数の出力として第13乱数信号を生成し、

前記暗号化更新データの復号処理が成功した場合に、前記第13乱数信号を前記外部サ バ装置へ出力する、

付記5に記載の半導体装置。

## [0148]

(付記12)

前記制御回路は、前記暗号化更新データの復号処理が成功しなかった場合に、前記第1 3 乱数信号に代えて、乱数信号を前記外部サーバ装置へ出力する、

付記11に記載の半導体装置。

## [0149]

(付記13)

真性乱数生成回路をさらに備え、

前記乱数信号は、真性乱数信号である、

付記12に記載の半導体装置。

## [0150]

(付記14)

外部端末装置に更新データを提供する方法であって、

鍵情報を記憶し、

第1乱数信号および第2乱数信号を生成し、

前記第1乱数信号および前記鍵情報から第6乱数信号および第7乱数信号を生成し、

前記更新データに対して第7乱数信号を用いて暗号化更新データを生成し、

前記外部端末装置に送信する要求信号として前記第1乱数信号および前記第2乱数信号 を生成し、

前記要求信号に対する応答信号として前記外部端末装置から第1応答信号および第2応 答信号を受け取り、

前記第1応答信号と前記第2乱数信号と前記第6乱数信号とを入力信号として、第8乱 数信号を生成し、

前記第2応答信号と前記第8乱数信号とが一致している場合に、前記暗号化更新データ を前記外部端末装置に提供する、

更新データ提供方法。

# [0151]

(付記15)

外部サーバ装置から暗号化更新データである暗号化更新データを受け取る方法であって

更新前データと、鍵情報を記憶し、

10

20

30

40

前記外部サーバ装置から第1乱数信号および第2乱数信号を要求信号として受け取り、前記第1乱数信号および前記鍵情報から第6乱数信号および第7乱数信号を生成し、

前記第2乱数信号と前記第6乱数信号とを入力信号として、第9乱数信号および第10 乱数信号を生成し、

予め設定された信号を含むチャレンジコードを生成し、

前記要求信号に対する応答信号として前記第9乱数信号および前記チャレンジコードを前記外部サーバ装置へ出力し、

出力した前記応答信号に基づいて前記外部サーバ装置から認証信号と前記暗号化更新データとを受け取り、

受け取った前記認証信号と、前記第10乱数信号とが一致している場合に、前記外部サーバ装置から受け取った前記暗号化更新データの復号処理を行う、

更新データ受取方法。

## [0152]

(付記16)

コンピュータに以下の方法を実行させるプログラムであって、前記方法は、

外部端末装置に更新データを提供する方法であって、

鍵情報を記憶し、

第1乱数信号および第2乱数信号を生成し、

前記第1乱数信号および前記鍵情報から第6乱数信号および第7乱数信号を生成し、

前記更新データに対して第7乱数信号を用いて暗号化更新データを生成し、

前記外部端末装置に送信する要求信号として前記第1乱数信号および前記第2乱数信号 を生成し、

前記要求信号に対する応答信号として前記外部端末装置から第 1 応答信号および第 2 応答信号を受け取り、

前記第 1 応答信号と前記第 2 乱数信号と前記第 6 乱数信号とを入力信号として、第 8 乱数信号を生成し、

前記第 2 応答信号と前記第 8 乱数信号とが一致している場合に、前記暗号化更新データを前記外部端末装置に提供する、

プログラム。

## [0153]

(付記17)

コンピュータに以下の方法を実行させるためのプログラムであって、前記方法は、 外部サーバ装置から暗号化更新データである暗号化更新データを受け取る方法であって

更新前データと、鍵情報を記憶し、

前記外部サーバ装置から第1乱数信号および第2乱数信号を要求信号として受け取り、前記第1乱数信号および前記鍵情報から第6乱数信号および第7乱数信号を生成し、

前記第2乱数信号と前記第6乱数信号とを入力信号として、第9乱数信号および第10 乱数信号を生成し、

予め設定された信号を含むチャレンジコードを生成し、

前記要求信号に対する応答信号として前記第9乱数信号および前記チャレンジコードを 前記外部サーバ装置へ出力し、

出力した前記応答信号に基づいて前記外部サーバ装置から認証信号と前記暗号化更新データとを受け取り、

受け取った前記認証信号と、前記第10乱数信号とが一致している場合に、前記外部サーバ装置から受け取った前記暗号化更新データの復号処理を行う、

プログラム。

## [0154]

(付記18)

メモリと、乱数生成回路と、制御回路と、を有し、外部サーバ装置から暗号化更新デー

20

10

30

40

タを受け取り、受け取った暗号化更新データを外部端末装置に提供する半導体装置であって、

前記メモリは、前記外部サーバ装置との間で使用可能な共通鍵を記憶し、

前記制御回路は、

前記外部サーバ装置から、第1乱数信号、第2乱数信号、前記共通鍵により暗号化された第6乱数信号を含む暗号化鍵データ、および暗号化更新データを受け取り、

前記暗号化鍵データを前記共通鍵により復号して第6乱数信号を生成し、

前記外部端末装置に送信する要求信号として前記第1乱数信号および前記第2乱数信号 を出力し、

前記要求信号に対する応答信号として前記外部端末装置から第1応答信号および第2応 答信号を受け取り、

前記第1応答信号と前記第2乱数信号と前記第6乱数信号とを入力信号として、第8乱数信号を生成し、

前記第2応答信号と前記第8乱数信号とが一致している場合に、前記暗号化更新データを前記外部端末装置に提供する、半導体装置。

#### [0155]

(付記19)

前記第6乱数信号および前記第8乱数信号は、

予め設定された同一の擬似ランダム関数に入力することよりそれぞれ演算される、

付記18に記載の半導体装置。

## [0156]

(付記20)

前記制御回路は、

前記第 2 応答信号と前記第 8 乱数信号とが一致していない場合に、前記暗号化更新データに代えて、前記暗号化更新データと同じ桁数の乱数信号を前記外部端末装置に提供する

付記18に記載の半導体装置。

# [0157]

(付記21)

サーバ装置と、前記サーバ装置から更新データを受け取る端末装置とを含む送受信シス テムであって、

前記サーバ装置と、前記端末装置とは、マスタ鍵情報をそれぞれ予め記憶し、

前記サーバ装置は、前記端末装置に対して、第1乱数信号と、前記端末装置を認証するための第1チャレンジコードと、を前記端末装置へ送信し、

前記端末装置は、サーバ装置に対して、

前記第1乱数信号および前記第1チャレンジコードに基づいて生成した第1レスポンスコードと、前記サーバ装置を認証するための第2チャレンジコードと、を送信し、

前記サーバ装置は、前記端末装置に対して、

前記第1レスポンスコードが期待値と一致する場合に、前記マスタ鍵により暗号化された 暗号化更新データと、前記第2チャレンジコードに対する第2レスポンスコードを送信し

前記端末装置は、

前記第 2 レスポンスコードが期待値と一致する場合に、前記マスタ鍵を用いて受け取った 前記暗号化更新データを復号する、

送受信システム。

## [0158]

(付記22)

前記サーバ装置と、前記端末装置とは、それぞれ共通の擬似ランダム関数を記憶し、前記端末装置は、前記擬似ランダム関数に前記第1チャレンジコードを入力して前記第 1レスポンスコードを生成し、 20

10

30

40

前記サーバ装置は、前記擬似ランダム関数に前記第2チャレンジコードを入力して前記第2レスポンスコードを生成する、

付記21に記載の送受信システム。

## [0159]

(付記23)

前記サーバ装置は、真性乱数生成回路を有しており、

前記第1乱数信号と前記第1チャレンジコードとはそれぞれ真性乱数信号である、付記21に記載の送受信システム。

## [0160]

(付記24)

前記端末装置は、真性乱数生成回路を有しており、

前記第2チャレンジコードは真性乱数信号である、

付記23に記載の送受信システム。

## [0161]

(付記25)

前記端末装置は、受け取った前記暗号化更新データに基づいて更新データの登録が完了 した場合に、前記第1乱数信号および第1チャレンジコードに基づいて生成した更新結果 信号を前記サーバ装置に送信し、

前記サーバ装置は、

前記端末装置から受け取った前記更新結果信号が、期待値と一致する場合には、前記端末装置のデータが前記更新データであることを登録するか、期待値と一致しない場合には、前記端末装置のデータが前記更新データでないことを登録する、

付記21に記載の送受信システム。

#### [ 0 1 6 2 ]

(付記26)

前記サーバ装置は、前記第1チャレンジコードが期待値と一致しない場合に、前記暗号 化更新データに代えて、前記暗号化更新データと同じ桁数の乱数信号を送信する、 付記21に記載の送受信システム。

## [ 0 1 6 3 ]

(付記27)

前記端末装置は、前記レスポンスコードが期待値と一致しない場合に、受け取った前記暗号化更新データを復号しない、

付記21に記載の送受信システム。

## [0164]

(付記28)

前記サーバ装置と前記端末装置との通信を中継する中継装置を更に有し、

前記中継装置は、前記端末装置に対して更新前データのバージョン情報を要求する信号を送信し、前記端末装置から受け取った前記バージョン情報と、前記更新前データを更新する処理を要求する信号と、を前記サーバ装置に送信する、

付記21に記載の送受信システム。

# [0165]

(付記29)

前記サーバ装置と前記端末装置との通信を中継する中継装置を更に有し、

前記サーバ装置と、前記中継装置とは、共通鍵をそれぞれ予め記憶し、

前記サーバ装置は、前記中継装置に対して、

第1乱数信号、前記第1チャレンジコード、前記共通鍵により暗号化された第6乱数信号を含む暗号化鍵データ、および前記暗号化更新データ、を送信し、

前記中継装置は、前記端末装置に対して、

前記第1乱数信号と、第1チャレンジコードと、を送信し、

前記端末装置は、前記中継装置に対して、

30

10

20

前記第1乱数信号と、前記第1レスポンスコードと、前記第2チャレンジコードと、を送 信し、

前記中継装置は、前記端末装置に対して、

前記第1レスポンスコードが期待値と一致する場合に、

前記暗号化更新データと、前記第2レスポンスコードと、を送信し、

前記端末装置は、前記第2レスポンスコードが期待値と一致する場合に、受け取った前 記暗号化更新データを復号する、

付記21に記載の送受信システム。

## 【産業上の利用可能性】

## [0166]

一実施の形態は、更新プログラムの授受を行うサーバ装置、端末装置等に適用可能であ る。

## 【符号の説明】

## [0167]

- 1、2、3 送受信システム

- 11, 21, 31 サーバ装置

- 12、22、32 中継装置

- 13、23、33 端末装置

- 1 1 0 、 2 1 0 第 1 半 導 体 装 置

- 120、320 第2半導体装置

- 130、230 第3半導体装置

- 900 ネットワーク

- S G 0 1 更新前データ

- SG02 更新データ

- SG03 更新前バージョンデータ

- SG04 更新バージョンデータ

- S G 0 5 識別子

- S G 0 6 マスタ鍵

- SG07 第12乱数信号

- S G 0 8 バージョンチェック要求信号

- SG09 バージョンアップ要求信号

- S G 1 0 比較結果信号

- S G 1 1 第1乱数信号

- S G 1 2 第 2 乱数信号

- SG13 第6乱数信号

- SG14 第7乱数信号

- S G 1 5 第 3 乱 数 信 号

- S G 1 6 第9乱数信号

- SG17 第10乱数信号

- S G 1 8 第8乱数信号

- S G 1 9 第11乱数信号

- S G 2 0 比較結果信号

- S G 2 1 暗号化更新データ

- S G 2 2 第4乱数信号

- S G 2 3 暗号文

- S G 2 4 比較結果信号

- S G 2 5 比較結果信号

- S G 2 6 第13乱数信号

- S G 2 7 第 1 4 乱数信号

- SG28 第1更新結果信号

10

20

30

40

- SG29 第5乱数信号

- SG30 第2更新結果信号

- SG31 比較結果信号

- SG32 共通鍵

- SG33 暗号文

Fig. 2

# 第2半導体装置 121 122 123 CPU NVRAM DRAM 1F

【図4】 130 第3半導体装置 -131 CPU PRF演算回路 131a 132 \_131b 比較回路 \_131c AE復号回路 NVRAM 133 134 135 IF TRNG DRAM

Fig. 4

Fig. 3

Fig. 17

Fig. 18

Fig. 21

# フロントページの続き

# 審査官 寺谷 大亮

(56)参考文献 国際公開第2016/020640(WO,A1)

特開2017-22654(JP,A) 特開2003-150453(JP,A) 特開2012-93921(JP,A)

(58)調査した分野(Int.CI., DB名)

H 0 4 L 9 / 3 2 G 0 6 F 2 1 / 5 7 G 0 9 C 1 / 0 0