# (19) 中华人民共和国国家知识产权局

# (12) 发明专利

(10) 授权公告号 CN 108321155 B (45) 授权公告日 2021.02.02

- (21) 申请号 201711352234.2

- (22) 申请日 2017.12.15

- (65) 同一申请的已公布的文献号 申请公布号 CN 108321155 A

- (43) 申请公布日 2018.07.24

- (73) 专利权人 天水电子电器检测试验中心 地址 741000 甘肃省天水市秦州区成纪大 道新华2号楼

- (72) 发明人 王起 刘文新

- (74) 专利代理机构 西安嘉思特知识产权代理事 务所(普通合伙) 61230

代理人 李斌

(51) Int.CI.

H01L 27/02 (2006.01)

H01L 21/762 (2006.01)

#### (56) 对比文件

- CN 104752395 A, 2015.07.01

- JP 特开2007-194509 A,2007.08.02

- CN 1841651 A,2006.10.04

审查员 陈峰

权利要求书1页 说明书5页 附图2页

#### (54) 发明名称

基于BJT的集成电路抗静电转接板

#### (57) 摘要

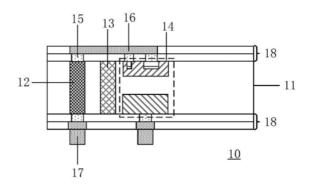

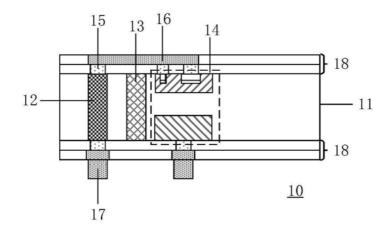

本发明涉及一种基于BJT的集成电路抗静电 转接板,该转接板10包括:硅基衬底11、TSV孔12、 隔离槽13、BJT14、插塞15、金属互连线16、凸点17 及钝化层18:所述TSV孔12、隔离槽13及所述 BJT14沿横向依次间隔地设置于所述硅基衬底11 中:其中,所述TSV孔12中填充多晶硅材料;所述 隔离槽13中填充二氧化硅材料;所述插塞15设置 于所述TSV孔12与所述BJT14上下表面所述金属 互连线16设置于所述TSV孔12与所述BJT14上表 面的所述插塞15上: 所述凸点17设置于所述TSV 孔12与所述BJT14下表面的所述插塞15上;所述 钝化层18设置于所述硅基衬底11上下表面。本发 四 明提供的基于BJT的集成电路抗静电转接板,通 25 过在TSV转接板上加工BJT作为ESD防护器件,增强了层叠封装芯片的抗静电能力。

1.一种基于BJT的集成电路抗静电转接板(10),其特征在于,包括:硅基衬底(11)、TSV孔(12)、隔离槽(13)、BJT(14)、插塞(15)、金属互连线(16)、凸点(17)及钝化层(18);

所述TSV孔(12)、隔离槽(13)及所述BJT(14)沿横向依次间隔地设置于所述硅基衬底(11)中;其中,所述TSV孔(12)中填充多晶硅材料;所述隔离槽(13)中填充二氧化硅材料;

所述插塞(15)设置于所述TSV孔(12)与所述BJT(14)上下表面;

所述金属互连线 (16) 设置于所述TSV孔 (12) 与所述BJT (14) 上表面的所述插塞 (15) 上; 所述凸点 (17) 设置于所述TSV孔 (12) 与所述BJT (14) 下表面的所述插塞 (15) 上; 所述钝化层 (18) 设置于所述硅基衬底 (11) 上下表面;

所述BJT (14) 的基区掺杂浓度为 $6\times10^{17}$ cm<sup>-3</sup> $\sim1\times10^{19}$ cm<sup>-3</sup>;所述BJT (14) 的发射区掺杂浓度为 $6\times10^{20}$ cm<sup>-3</sup> $\sim3\times10^{2}$ ;所述BJT (14) 的集电区的掺杂浓度为 $3\times10^{18}$ cm<sup>-3</sup> $\sim5\times10^{19}$ cm<sup>-3</sup>.

所述金属互连线围绕成螺旋状。

- 2.根据权利要求1所述的转接板 (10),其特征在于,所述硅基衬底 (11) 的掺杂浓度为  $10^{14}\sim10^{17}{\rm cm}^{-3}$ 。

- 3.根据权利要求1所述的转接板 (10), 其特征在于, 在所述TSV孔 (12) 中, 所述多晶硅材料的掺杂浓度为 $3\times10^{20}$ cm<sup>-3</sup> $\sim5\times10^{21}$ cm<sup>-3</sup>。

- 4.根据权利要求1所述的转接板(10),其特征在于,所述插塞(15)为钨材料。

- 5.根据权利要求1所述的转接板(10),其特征在于,所述金属互连线(16)与所述凸点(17)为铜材料。

- 6. 根据权利要求1所述的转接板(10),其特征在于,所述钝化层(18)为二氧化硅材料。

# 基于BJT的集成电路抗静电转接板

#### 技术领域

[0001] 本发明涉及半导体器件设计及制造领域,特别涉及一种基于BJT的集成电路抗静电转接板。

## 背景技术

[0002] 目前为止集成电路的特征尺寸已经低至7nm,在单个芯片上集成的晶体管数量已经到达百亿级别,伴随百亿级别的晶体管数量的要求,片上资源和互连线长度问题成为现今集成电路领域发展的瓶颈,3D集成电路被认为是未来集成电路的发展方向,它原有电路的基础上,在Z轴上层叠,以求在最小的面积上集成更多的功能,这种方法克服了原有集成度的限制,采用新兴技术硅片通孔(Through Silicon Vias,简称TSV),大幅度的提高了集成电路的性能,降低线上延迟,减小芯片功耗。

[0003] 在半导体行业里面,随着集成电路集成度的提高以及器件特征尺寸的减小,集成电路中静电放电引起的潜在性损坏已经变得越来越明显。据有关报道,集成电路领域的故障中有近35%的故障是由静电释放(Electro-Static discharge,简称ESD)所引发的,因此芯片内部都设计有ESD保护结构来提高器件的可靠性。然而不同芯片的的抗静电能力不同,在三维堆叠时抗静电能力弱的芯片会影响到封装后整个系统的抗静电能力,因此如何提高基于TSV工艺的3D集成电路的抗静电能力成为半导体行业亟待解决的问题。

#### 发明内容

[0004] 为解决现有技术存在的技术缺陷和不足,本发明提出一种可以提高集成电路的抗静电能力的转接板。

[0005] 在本发明的一个实施例中提供了一种基于双极结型晶体管 (Bipolar Junction Transistor, 简称BJT) 的集成电路抗静电转接板的转接板。该转接板 (10) 包括: 硅基衬底 (11)、TSV孔 (12)、隔离槽 (13)、BJT (14)、插塞 (15)、金属互连线 (16)、凸点 (17) 及钝化层 (18):

[0006] 所述TSV孔(12)、隔离槽(13)及所述BJT(14)沿横向依次间隔地设置于所述硅基衬底(11)中;其中,所述TSV孔(12)中填充多晶硅材料;所述隔离槽(13)中填充二氧化硅材料;

[0007] 所述插塞(15)设置于所述TSV孔(12)与所述BJT(14)上下表面;

[0008] 所述金属互连线 (16) 设置于所述TSV孔 (12) 与所述BJT (14) 上表面的所述插塞 (15) 上;

[0009] 所述凸点(17)设置于所述TSV孔(12)与所述BJT(14)下表面的所述插塞(15)上;

[0010] 所述钝化层(18)设置于所述硅基衬底(11)上下表面。

[0011] 在本发明的一个实施例中,所述硅基衬底(11)的掺杂浓度为 $10^{14}\sim 10^{17}$ cm<sup>-3</sup>。

[0012] 在本发明的一个实施例中,在所述TSV孔(12)中,所述多晶硅材料的掺杂浓度为 $3\times 10^{20} {\rm cm}^{-3} \sim 5\times 10^{21} {\rm cm}^{-3}$ 。

[0013] 在本发明的一个实施例中,所述BJT (14)的基区掺杂浓度为 $6 \times 10^{17} {\rm cm}^{-3} \sim 1 \times 10^{17}$

$10^{19} \text{cm}^{-3}$  .

[0014] 在本发明的一个实施例中,所述BJT (14) 的发射区掺杂浓度为 $6 \times 10^{20} \text{cm}^{-3} \sim 3 \times 10^{21} \text{cm}^{-3}$ 。

[0015] 在本发明的一个实施例中,所述BJT (14) 的集电区的掺杂浓度为 $3\times10^{18}$ cm<sup>-3</sup> $\sim5\times10^{19}$ cm<sup>-3</sup>。

[0016] 在本发明的一个实施例中,所述插塞(15)为钨材料。

[0017] 在本发明的一个实施例中,所述金属互连线(16)与所述凸点(17)为铜材料。

[0018] 在本发明的一个实施例中,所述钝化层(18)为二氧化硅材料。

[0019] 与现有技术相比,本发明至少具有以下有益效果:

[0020] 1、本发明提供的集成电路抗静电转接板的制备工艺,其工艺步骤简单,可行性高;

[0021] 2、本发明提供的集成电路抗静电转接板,通过在TSV转接板上加工BJT作为ESD防护器件,增强了层叠封装芯片的抗静电能力;此外,上述BJT周围采用上下贯通的隔离沟槽,具有较小的漏电流和寄生电容。

#### 附图说明

[0022] 下面将结合附图,对本发明的具体实施方式进行详细的说明。

[0023] 图1为本发明实施例提供的一种基于BJT的集成电路抗静电转接板的结构示意图;

[0024] 图2a-图2f为本发明实施例提供的一种基于BJT的集成电路抗静电转接板的制备方法示意图。

## 具体实施方式

[0025] 下面结合具体实施例对本发明做进一步详细的描述,但本发明的实施方式不限于此。

[0026] 实施例一

[0027] 请参见图1,图1为本发明实施例提供的一种基于BJT的集成电路抗静电转接板的结构示意图,该转接板10包括:硅基衬底11、TSV孔12、隔离槽13、BJT14、插塞15、金属互连线16、凸点17及钝化层18;

[0028] 所述TSV孔12、隔离槽13及所述BJT14沿横向依次间隔地设置于所述硅基衬底11中;其中,所述TSV孔12中填充多晶硅材料;所述隔离槽13中填充二氧化硅材料;

[0029] 所述插塞15设置于所述TSV孔12与所述BJT14上下表面;

[0030] 所述金属互连线16设置于所述TSV孔12与所述BJT14上表面的所述插塞15上;

[0031] 所述凸点17设置于所述TSV孔12与所述BJT14下表面的所述插塞15上;

[0032] 所述钝化层18设置于所述硅基衬底11上下表面。

[0033] 进一步地,在上述实施例的基础上,所述硅基衬底11的掺杂浓度为 $10^{14} \sim 10^{17}$ cm<sup>-3</sup>。

[0034] 进一步地,在上述实施例的基础上,所述多晶硅材料的掺杂浓度为 $3\times10^{20}$ cm<sup>-3</sup> $\sim5\times10^{21}$ cm<sup>-3</sup>。

[0035] 进一步地,在上述实施例的基础上,所述BJT14的基区掺杂浓度为 $6\times10^{17}$ cm<sup>-3</sup> $\sim1\times10^{19}$ cm<sup>-3</sup>。

[0036] 进一步地,在上述实施例的基础上,所述BJT14的发射区掺杂浓度为 $6 \times 10^{20}$  cm<sup>-3</sup>~

$3 \times 10^{21} \text{cm}^{-3}$

[0037] 进一步地,在上述实施例的基础上,所述BJT14的集电区的掺杂浓度为 $3\times10^{18}$ cm<sup>-3</sup>  $\sim5\times10^{19}$ cm<sup>-3</sup>。

[0038] 进一步地,在上述实施例的基础上,所述插塞15为钨材料。

[0039] 进一步地,在上述实施例的基础上,所述金属互连线(16)与所述凸点(17)为铜材料。

[0040] 进一步地,在上述实施例的基础上,所述钝化层18为二氧化硅材料。

[0041] 本实施例提供的基于BJT的集成电路抗静电转接板,通过在硅基衬底中制作BJT作为ESD防护器件,增强了集成电路的的抗静电能力;此外,通过在BJT周围设置上下贯通的隔离沟槽,可以减小转接板的漏电流和寄生电容。

[0042] 实施例二

[0043] 本实施例是在实施例一的基础上对基于BJT的集成电路抗静电转接板的制备方法进行详细描述。

[0044] 具体的,请参见图2a~图2f,图2a~图2f为本发明实施例提供的一种基于BJT的集成电路抗静电转接板的制备方法示意图,该制备方法包括如下步骤:

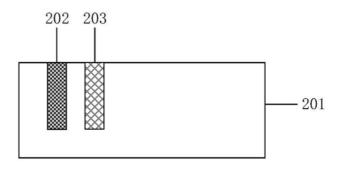

[0045] S1、选取选取硅基衬底201,如图2a所示。

[0046] 其中,硅基衬底201的晶向可以是 (100) 或者 (110) 或者 (111),此处不做任何限制,另外,硅基衬底201的掺杂浓度为 $10^{14}\sim10^{17}$ cm<sup>-3</sup>,掺杂类型为N型,厚度为 $450\sim550$ µm。

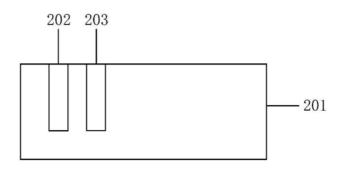

[0047] S2、在所述硅基衬底201中第一指定区域与第二指定区域分别制作TSV孔202与隔离沟槽203,如图2b所示。具体的,S2可以包括如下步骤:

[0048] S21、采用光刻工艺,在所述硅基衬底上制作第一待刻蚀区域与第二待刻蚀区域;

[0049] S22、采用深度反应离子刻蚀工艺,在所述第一待刻蚀区域与所述第二待刻蚀区域刻蚀所述硅基衬底,分别形成所述TSV孔与所述隔离沟槽;其中,所述TSV孔与所述隔离沟槽的深度为300~400μm;

[0050] S23、采用热氧化工艺,在所述TSV孔与所述隔离沟槽的内壁形成氧化层;采用湿法刻蚀工艺,选择性刻蚀所述氧化层以使所述TSV孔与所述隔离沟槽的内壁平整。通过该步骤,可以防止TSV孔侧壁突起形成电场集中区域。

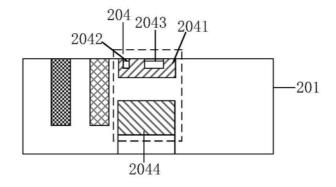

[0051] S3、分别对所述隔离沟槽203与所述TSV孔202进行填充;如图2c所示。具体的,S3可以包括如下步骤:

[0052] S31、采用光刻工艺,在所述硅基衬底201表面形成隔离沟槽填充区域;

[0053] S32、在690℃~710℃的温度下,采用化学气相淀积工艺,通过所述隔离沟槽填充 区域在所述隔离沟槽内淀积二氧化硅材料以完成对所述隔离沟槽的填充;其中,可以采用 未掺杂的多晶硅材料替代二氧化硅材料;

[0054] S33、采用光刻工艺,在所述硅基衬底表面形成TSV孔填充区域;

[0055] S34、在600°C~620°C的温度下,采用化学气相淀积工艺,通过所述TSV孔填充区域在所述TSV孔内淀积多晶硅材料,并引入掺杂气体对所述多晶硅材料进行原位掺杂以完成对所述TSV孔的填充。其中,多晶硅材料的掺杂浓度为 $3\times10^{20}$ cm<sup>-3</sup>~ $5\times10^{21}$ cm<sup>-3</sup>,优选为 $2\times10^{21}$ cm<sup>-3</sup>。在此掺杂条件下,多晶硅材料的电导率较高,有利于减小TSV孔的电阻。

[0056] S4、在所述硅基衬底201中第三指定区域制作BJT204;如图2d所示。具体的,S4可以

包括如下步骤:

[0057] S41、采用光刻工艺,在所述硅基衬底上制作第三待刻蚀区域;

[0058] S42、采用干法刻蚀工艺,在所述第三待刻蚀区域刻蚀所述硅基衬底201,形成器件沟槽;其中,器件沟槽的深度为80~120μm;

[0059] S43、在600 $^{\circ}$ C $^{\circ}$ 950 $^{\circ}$ C温度下,采用低压化学气相淀积工艺,在器件沟槽中淀积硅材料,并对所述硅材料掺杂以形成所述BJT204的基区2041;其中,基区2041的掺杂杂质为硼,掺杂浓度为6 $^{\circ}$ 10 $^{17}$ cm $^{-3}$  $^{\circ}$ 1 $^{\circ}$ 10 $^{19}$ cm $^{-3}$ 3,优选为5 $^{\circ}$ 10 $^{18}$ cm $^{-3}$ 3;

[0060] S44、采用带胶离子注入工艺,在所述基区2041中第一指定区域进行P+离子注入以形成基区接触区2042;其中,基区接触区2042的掺杂杂质为硼,掺杂浓度为 $6\times10^{20}$ cm<sup>-3</sup> $\sim3\times10^{21}$ cm<sup>-3</sup>,优选为 $1\times10^{21}$ cm<sup>-3</sup>;

[0061] S45、采用带胶离子注入工艺,在所述基区中第二指定区域进行N+离子注入以形成所述BJT的发射区2043;其中,发射区2043的掺杂杂质为磷,掺杂浓度为 $6\times10^{20}$ cm<sup>-3</sup> $\sim3\times10^{21}$ cm<sup>-3</sup>,优选为 $1\times10^{21}$ cm<sup>-3</sup>;

[0062] S46、采用带胶离子注入工艺,在所述硅基衬底中的基区下方进行N+离子注入以形成所述BJT的集电区2044;其中,集电区2044的掺杂杂质为磷,掺杂浓度为 $3\times10^{18}$ cm $^{-3}\sim5\times10^{19}$ cm $^{-3}$ ,优选为 $1\times10^{19}$ cm $^{-3}$ 。

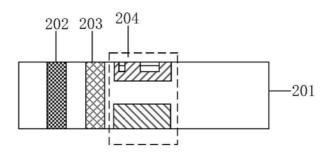

[0063] S5、去除所述硅基衬底201底部部分材料,以在所述硅基衬底201底部露出所述TSV 孔、所述隔离沟槽及所述BJT;如图2e所示。具体的,S5、可以包括如下步骤:

[0064] S51、采用机械磨削工艺,对所述硅基衬底201下表面进行减薄处理;

[0065] S52、采用化学机械抛光工艺,对所述硅基衬底201下表面进行平整化处理,以在所述硅基衬底201底部露出所述TSV孔202、所述隔离沟槽203及所述BJT204。经该步骤处理过后,硅基衬底201厚度的目标尺寸为300~400μm。

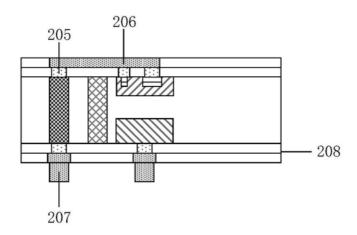

[0066] S6、在所述TSV孔202与所述BJT204表面制作插塞205与金属互连线206以使所述TSV孔202与所述BJT204相连接,如图2f所示。具体的,S5可以包括如下步骤:

[0067] S61、在所述TSV孔202与所述BJT204上下表面淀积二氧化硅材料作为钝化层208, 选择性刻蚀所述钝化层208, 在所述TSV孔202与所述BJT204上下表面分别形成插塞孔; 在所述插塞孔中淀积金属形成插塞205; 其中, 所述插塞205优选为钨材料;

[0068] S62、在所述TSV孔202与所述BJT204上表面的插塞205上制作所述金属互连线206以使所述TSV孔202与所述BJT204相连接;其中,所述金属互连线206优选为铜材料;其中,同时可利用金属互连线围绕成螺旋状而使其具有电感的特性以更好用于射频集成电路的静电防护;

[0069] S63、在所述TSV孔202与所述BJT204下表面的插塞205上淀积金属材料作为凸点207;优选地,所述凸点207优选为铜材料。

[0070] 需要说明的是,隔离沟槽是为了隔断BJT与转接板中其他结构的连接,故隔离沟槽可以制作为封闭结构(例如环状结构)并贯穿衬底材料,BJT位于该封闭结构内部。

[0071] 本实施例提供的基于BJT的集成电路抗静电转接板的制备方法,通过在TSV转接板上制作BJT作为ESD防护器件,增强了集成电路的的抗静电能力;另外,该制备方法相对简单,可行性高。

[0072] 以上内容是结合具体的优选实施方式对本发明所作的进一步详细说明,不能认定

本发明的具体实施只局限于这些说明。对于本发明所属技术领域的普通技术人员来说,在不脱离本发明构思的前提下,还可以做出若干简单推演或替换,都应当视为属于本发明的保护范围。

图1

图2a

图2b

图2c

图2d

图2e

图2f