(19) **日本国特許庁(JP)**

# (12) 特許公報(B2)

(11)特許番号

特許第5650366号 (P5650366)

(45) 発行日 平成27年1月7日(2015.1.7)

(24) 登録日 平成26年11月21日(2014.11.21)

(51) Int. Cl.

FL

G11C 29/00 (2006, 01) G11C 29/00 603L

> (全 19 頁) 請求項の数8

(21) 出願番号 (22) 出願日

特願2007-280822 (P2007-280822)

(65) 公開番号

平成19年10月29日 (2007.10.29) 特開2009-110584 (P2009-110584A)

(43) 公開日

平成21年5月21日 (2009.5.21)

審查請求日

平成22年9月9日(2010.9.9)

(73)特許権者 513192281

ピーエスフォー ルクスコ エスエイアー

ルエル

PS4 Luxco S. a. r. I. ルクセンブルク大公国エルー2121、ル クセンブルク、ヴァル デ ボン マラデ ス208

(74)代理人 100115738

弁理士 鷲頭 光宏

||(74)代理人 100121681

弁理士 緒方 和文

|(74)代理人 100130982

弁理士 黒瀬 泰之

(74)代理人 100127199

弁理士 三谷 拓也

最終頁に続く

(54) 【発明の名称】アンチヒューズ回路及びこれを備える半導体装置、並びに、アンチヒューズ回路へのアドレス書 き込み方法

### (57)【特許請求の範囲】

### 【請求項1】

不揮発的にデータを保持するアンチヒューズ素子を含む複数のヒューズセットを備え、 前記ヒューズセットは、不良アドレスを記憶する複数のビット記憶回路と、前記複数のビ ット記憶回路に記憶された不良アドレスを無効とするディセーブル回路とを含んでおり、

前記複数のヒューズセットのうち、前記不良アドレスの書き込みに失敗したヒューズセ ットの前記ディセーブル回路は活性化されていることを特徴とするアンチヒューズ回路。

#### 【請求項2】

前記ヒューズセットは、前記複数のビット記憶回路に記憶された不良アドレスを有効と するイネーブル回路をさらに含んでいることを特徴とする請求項1に記載のアンチヒュー ズ回路。

10

## 【請求項3】

前記イネーブル回路及び前記ディセーブル回路は、いずれも前記ビット記憶回路と実質 的に同じ回路構成を有していることを特徴とする請求項2に記載のアンチヒューズ回路。

#### 【請求項4】

前記不良アドレスを書き込むべきヒューズセット内の前記イネーブル回路を活性化させ るとともに、前記不良アドレスの書き込みが失敗したヒューズセット内の前記ディセーブ ル回路を活性化させる制御回路をさらに備えることを特徴とする請求項3に記載のアンチ ヒューズ回路。

#### 【請求項5】

請求項1乃至4のいずれか一項に記載のアンチヒューズ回路と、前記不良アドレスが供給されるアドレス端子と、前記ヒューズセットを選択するための救済セットアドレスが供給されるデータ端子とを備えることを特徴とする半導体装置。

## 【請求項6】

請求項4に記載のアンチヒューズ回路に不良アドレスを書き込む方法であって、

前記不良アドレスを書き込むべきヒューズセット内の前記イネーブル回路を活性化させる第 1 のステップと、

前記不良アドレスの書き込みが失敗した場合、該ヒューズセット内の前記ディセーブル 回路を活性化させる第2のステップと、を備えることを特徴とするアンチヒューズ回路へ のアドレス書き込み方法。

### 【請求項7】

前記ディセーブル回路を活性化させたヒューズセットに書き込むべき不良アドレスを、他のヒューズセットに書き込む第3のステップをさらに備えることを特徴とする請求項6に記載のアンチヒューズ回路へのアドレス書き込み方法。

### 【請求項8】

前記第1のステップは、前記不良アドレスを書き込むステップと、前記不良アドレスの書き込みが失敗した場合、前記不良アドレスを再度書き込むステップとを含んでいることを特徴とする請求項6又は7に記載のアンチヒューズ回路へのアドレス書き込み方法。 【発明の詳細な説明】

## 【技術分野】

### [00001]

本発明はアンチヒューズ回路及びこれを備える半導体装置に関し、特に、アンチヒューズ素子への書き込み処理を高速に行うことが可能なアンチヒューズ回路及びこれを有する半導体装置に関する。また、本発明はこのようなアンチヒューズ回路へのアドレス書き込み方法に関する。

## 【背景技術】

#### [0002]

DRAM(Dynamic Random Access Memory)などの半導体装置においては、正常に動作しない不良セルを冗長セルに置換することによって不良アドレスの救済が行われる。不良アドレスの記憶には、通常、ヒューズ素子が用いられる(特許文献 1 , 2 参照)。初期状態のヒューズ素子は電気的に導通状態であり、レーザービームの照射によってこれを切断することにより、不良アドレスを不揮発的に記憶することができる。したがって、このようなヒューズ素子を複数設け、所望のヒューズ素子を切断すれば、所望のアドレスを記憶させることが可能となる。このように、通常のヒューズ素子は、導通状態から絶縁状態に変化させることによって情報を不揮発的に記憶する素子である。

#### [ 0 0 0 3 ]

これに対し、近年、アンチヒューズ素子と呼ばれる素子が注目されている(特許文献3参照)。アンチヒューズ素子とは、通常のヒューズ素子とは逆に、絶縁状態から導通状態に変化させることによって情報を記憶する素子である。アンチヒューズ素子への情報の書き込みは、高電圧の印加による絶縁破壊によって行う。このため、通常のヒューズ素子とは異なり、書き込みに際してレーザービームの照射が不要である。これにより、不良アドレスの書き込みを高速に行うことができるとともに、レーザートリマーなどの装置が不要となる。しかも、レーザービームの照射によるパッシベーション膜の破壊なども生じないことから、製品の信頼性を高めることも可能となる。

## [0004]

しかしながら、絶縁破壊されたアンチヒューズ素子の抵抗値は、絶縁破壊の程度や発生 箇所によって大きくばらつく。このため、場合によっては絶縁破壊後の抵抗値がM オー ダーとなるケースも存在する。このような場合、アンチヒューズ素子が破壊されているの か破壊されていないのか判別が困難となる。しかしながら、一旦不良アドレスの書き込み が実行されたヒューズセットにおいては、使用の有無を示すイネーブルヒューズも破壊さ 10

20

30

40

れていることから、これを不使用状態に戻すことができない。このため、不良アドレスの 書き込みが失敗した場合、チップ全体を廃棄しなければならないという問題があった。

【特許文献1】特開平10-75170号公報

【特許文献2】特開2006-147651号公報

【特許文献3】特開2004-227361号公報

【発明の開示】

【発明が解決しようとする課題】

[0005]

したがって、本発明の目的は、不良アドレスの書き込みが失敗した場合であっても、当該ヒューズセットを無効化可能なアンチヒューズ回路及びこれを有する半導体装置を提供することである。

[0006]

また、本発明の他の目的は、このようなアンチヒューズ回路へのアドレスの書き込み方法を提供することである。

【課題を解決するための手段】

[0007]

本発明によるアンチヒューズ回路は、不揮発的にデータを保持するアンチヒューズ素子を含む複数のヒューズセットを備え、ヒューズセットは、不良アドレスを記憶する複数のビット記憶回路と、複数のビット記憶回路に記憶された不良アドレスを無効とするディセーブル回路とを含んでいることを特徴とする。また、本発明による半導体装置は、このようなアンチヒューズ回路を備えることを特徴とする。さらに、本発明によるアドレスの書き込み方法は、不良アドレスを書き込むべきヒューズセット内のイネーブル回路を活性化させる第1のステップと、不良アドレスの書き込みが失敗した場合、該ヒューズセット内のディセーブル回路を活性化させる第2のステップとを備えることを特徴とする。

[00008]

本発明によれば、各ヒューズセットにディセーブル回路が備えられていることから、一旦不良アドレスの書き込みが実行されたヒューズセットをその後無効化することができる。このため、不良アドレスの書き込みが失敗した場合であっても、チップ全体を廃棄する必要がなくなる。

[0009]

ヒューズセットは、複数のビット記憶回路に記憶された不良アドレスを有効とするイネーブル回路をさらに含んでいることが好ましい。この場合、イネーブル回路及びディセーブル回路は、いずれもビット記憶回路と実質的に同じ回路構成を有していることが好ましい。

【発明の効果】

[0010]

このように、本発明によれば、不良アドレスの書き込みが失敗した場合であっても、当該ヒューズセットを無効化可能することが可能となる。

【発明を実施するための最良の形態】

[0011]

以下、添付図面を参照しながら、本発明の好ましい実施の形態について詳細に説明する

[0012]

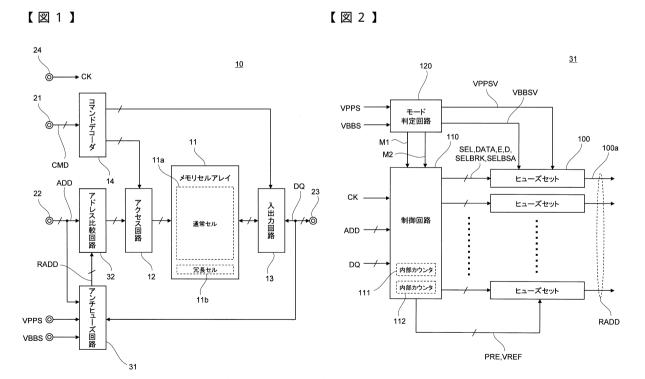

図1は、本発明の好ましい実施形態による半導体装置10の構成を示すプロック図である。

[0013]

本実施形態による半導体装置 1 0 は D R A M などの半導体メモリであり、複数のメモリセルを含むメモリセルアレイ 1 1 と、メモリセルアレイ 1 1 に対するアクセス制御を行うアクセス回路 1 2 と、メモリセルアレイ 1 1 に対するデータの入出力制御を行う入出力回路 1 3 と、コマンド信号 C M Dを受け付けるコマンドデコーダ 1 4 とを備えている。図 1

10

20

30

40

に示すように、メモリセルアレイ11に含まれるメモリセルは、通常セル11aと冗長セル11bに分類される。冗長セル11bは、不良のある通常セル11aを置換することにより不良アドレスを救済するために用いられる。

#### [0014]

本実施形態による半導体装置10は、外部端子として複数のコマンド端子21、複数のアドレス端子22及び複数のデータ端子23を備えている。コマンド端子21はコマンド信号CMDが供給される端子であり、アドレス端子22はアドレス信号ADDが供給される端子である。また、データ端子23は、リードデータDQの出力及びライトデータDQの入力を行う端子である。その他、クロック信号CKが入力されるクロック端子24や、図示しない電源端子なども設けられている。

[0015]

通常動作時における半導体装置10の動作は、コマンド信号CMDの組み合わせによって指定される。例えば、コマンド信号CMDがリード動作を表している場合には、コマンドデコーダ14によってリード信号が内部生成され、コマンド信号CMDがライト動作を表している場合には、コマンドデコーダ14によってライト信号が内部生成される。これらの内部コマンドは、アクセス回路12や入出力回路13に供給される。

[0016]

リード信号が内部生成されると、メモリセルアレイ11に記憶されたデータのうち、アドレス信号 A D D により指定されるアドレスに記憶されたデータにアクセスし、読み出したリードデータ D Q をデータ端子23へ出力する。メモリセルへのアクセスはアクセス回路12によって制御され、リードデータ D Q の出力は入出力回路13によって制御される。一方、ライト信号が内部生成されると、データ端子23に入力されたライトデータ D Q を入出力回路13に取り込み、アクセス回路12の制御により、アドレス信号 A D D によって指定されるアドレスに書き込む。

[0017]

図1に示すように、本実施形態による半導体装置10は、アンチヒューズ回路31及びアドレス比較回路32をさらに備えている。アンチヒューズ回路31は、不良のある通常セル11aのアドレス(不良アドレスRADD)を記憶する回路であり、後述するように、複数のアンチヒューズセットを含んでいる。

[0018]

アドレス比較回路32は、アンチヒューズ回路31記憶された不良アドレスRADDとアドレス端子22を介して供給されたアドレス信号ADDとを比較する回路である。比較の結果はアクセス回路12に供給される。アクセス回路12は、アドレス比較回路32により一致が検出されなかった場合には通常セル11aに対してアクセスを行い、一致が検出された場合には冗長セル11bに対してアクセスを行う。これにより、不良アドレスが救済される。

[0019]

次に、アンチヒューズ回路31の構成について詳細に説明する。

[0020]

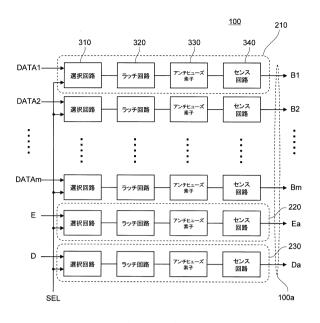

図2は、アンチヒューズ回路31の回路構成を示すブロック図である。

[0021]

図 2 に示すように、アンチヒューズ回路 3 1 は、不良アドレスを記憶する複数のヒューズセット 1 0 0 と、ヒューズセット 1 0 0 の動作を制御する制御回路 1 1 0 と、エントリすべき動作モードを判定するモード判定回路 1 2 0 とを備えている。

[0022]

ヒューズセット100は、それぞれ1アドレスを不揮発的に記憶可能な回路である。したがって、アンチヒューズ回路31は、ヒューズセット100と同数の不良アドレスを記憶することができる。具体的なヒューズセット100の数については製品によって異なるが、例えば1000セット程度設けられることが多い。ヒューズセット100の具体的な回路構成については後述する。

10

20

30

40

### [0023]

モード判定回路120は、外部端子VPPS,VBBSに供給される電圧に基づいてエントリすべき動作モードを判定する。本実施形態では、動作モードとして少なくとも「セットモード」、「書き込みモード」、「センスモード」を備えている。

### [0024]

「セットモード」とは、不良アドレスをヒューズセット100に一時的にラッチさせるためのモードである。このモードでは、アンチヒューズ素子の破壊は行われない。「書き込みモード」とは、実際にアンチヒューズ素子を破壊するためのモードであり、セットモードにて不良アドレスをラッチした後にエントリされる。「センスモード」とは、ヒューズセット100に書き込まれた不良アドレスを読み出すモードであり、実使用状態においては常にこのモードにエントリされる。

### [0025]

特に限定されるものではないが、本実施形態では、外部端子VPPS,VBBSにそれぞれ3V、0Vを印加することにより「セットモード」にエントリすることができ、それぞれ4V、・2Vを印加することにより「書き込みモード」にエントリすることができる。また、外部端子VPPS,VBBSをいずれもオープン状態とすることにより、「センスモード」にエントリすることができる。外部端子VPPS,VBBSは、いずれも実使用状態においては使用されない端子であり、ウェハ状態で行う動作テスト時においてのみ使用される。したがって、実使用状態においては外部端子VPPS,VBBSは常にオープン状態である。

#### [0026]

セットモードにエントリすると、モード判定回路120は、モード信号M1,M2をいずれもハイレベルとし、これに応じて制御回路110はセットモード時における動作を行う。さらに、モード判定回路120は、動作電圧VPPSV,VBBSVのレベルをそれぞれ外部端子VPPS,VBBSへの供給電圧、つまりそれぞれ3V、0Vとし、これを各ヒューズセット100に供給する。

## [0027]

書き込みモードにエントリすると、モード判定回路120は、モード信号M1をハイレベル、モード信号M2をローレベルとし、これに応じて制御回路110は書き込みモード時における動作を行う。さらに、モード判定回路120は、動作電圧VPPSV,VBBSVのレベルをそれぞれ外部端子VPPS,VBBSへの供給電圧、つまりそれぞれ4V、・2Vとし、これを各ヒューズセット100に供給する。

#### [0028]

センスモードにエントリすると、モード判定回路120は、モード信号M1をローレベル、モード信号M2をハイレベルとし、これに応じて制御回路110はセンスモード時における動作を行う。さらに、モード判定回路120は、動作電圧VPPSV,VBBSVのレベルをいずれもVSSレベルとする。

### [0029]

図3は、ヒューズセット100の回路構成を示すブロック図である。

#### [0030]

図3に示すように、1つのヒューズセット100には、m個のビット記憶回路210と、イネーブル回路220と、ディセーブル回路230とが含まれている。ビット記憶回路210は、それぞれ記憶すべき不良アドレスの1ビットに対応する。したがって、1つのヒューズセット100に含まれるビット記憶回路210の数(=m)は、記憶すべきアドレスのビット数と等しい(或いはそれ以上)。

## [0031]

イネーブル回路 2 2 0 は、当該ヒューズセット 1 0 0 を有効化する場合に活性化される回路であり、ディセーブル回路 2 3 0 は、当該ヒューズセット 1 0 0 を無効化する場合に活性化される回路である。ディセーブル回路 2 3 0 は、イネーブル回路 2 2 0 よりも優先順位が高く、したがって、イネーブル回路 2 2 0 とディセーブル回路 2 3 0 の両方が活性

10

20

30

40

化された場合、当該ヒューズセット100は無効化される。尚、イネーブル回路220とディセーブル回路230の両方が非活性である場合も、当該ヒューズセット100は無効とされる。

### [0032]

ビット記憶回路 2 1 0、イネーブル回路 2 2 0 及びディセーブル回路 2 3 0 は、互いに同じ回路構成を有している。具体的には、図 3 に示すように、いずれも選択回路 3 1 0、ラッチ回路 3 2 0、アンチヒューズ素子 3 3 0 及びセンス回路 3 4 0 によって構成されている。選択回路 3 1 0 は、当該ヒューズセット 1 0 0 が選択された場合に活性化される回路であり、それぞれ対応するビット信号 D A T A 1 ~ D A T A m、イネーブル信号 E、ディセーブル信号 D が入力される。また、ラッチ回路 3 2 0 は、アンチヒューズ素子 3 3 0 に書き込むべきデータを一時的に保持する回路である。

[0033]

そして、センス回路340の出力であるビット信号B1~Bmが1つの不良アドレスを示し、イネーブル信号Eaがアクティブであれば当該不良アドレスは有効とされ、ディセーブル信号Daがアクティブであれば当該不良アドレスは無効とされる。このように、一つのヒューズセット100からの出力100aは、ビット信号B1~Bm、イネーブル信号Ea及びディセーブル信号Daによって構成される。図2に示したとおり、これら出力100aの集合が不良アドレスRADDである。

[0034]

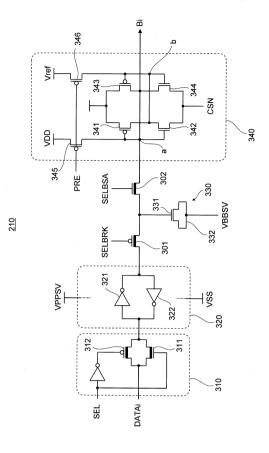

図4は、ビット記憶回路210の具体的な回路図である。

[0035]

図4に示すように、ビット記憶回路210に含まれる選択回路310は、NチャンネルMOSトランジスタ311とPチャンネルMOSトランジスタ312が並列接続されたトランスファゲート構成を有している。これらトランジスタ311,312のゲートには、対応する選択信号SEL及びその反転信号が供給される。選択信号SELは、所望のヒューズセット100を選択するための信号であり、したがって、ヒューズセット100ごとに異なる選択信号SELが割り当てられる。かかる構成により、選択信号SELがハイレベルに活性化すると、対応するビット信号DATAi(i=1~m)がラッチ回路320に供給される。

[0036]

ラッチ回路320は、2つのインバータ321,322が循環接続された、いわゆるフリップフロップ構成を有している。したがって、選択信号SELが活性化すると、ビット信号DATAiがラッチ回路320に一時的に記憶されることになる。当然ながら、ラッチ回路320への書き込みは、アンチヒューズ素子への書き込みとは異なり、非常に高速に行うことが可能である。図4に示すように、ラッチ回路320には、モード判定回路120により生成される動作電圧VPPSVが供給される。

[0037]

ラッチ回路320の出力は、書き込みトランジスタ301を介してアンチヒューズ素子330に供給される。アンチヒューズ素子330は、MOSトランジスタのソースとドレインが短絡された構成を有しており、そのゲート331にはラッチ回路320の出力が供給され、ソース/ドレイン332にはモード判定回路120により生成される動作電圧VBBSVが供給される。

[ 0 0 3 8 ]

初期状態におけるアンチヒューズ素子330は、ゲート絶縁膜を介して、ゲート331とソース/ドレイン332とが絶縁されている。このため、両者間に電流は流れない。しかしながら、ゲート331とソース/ドレイン332との間に高電圧を印加すると、ゲート絶縁膜に絶縁破壊が生じ、両者間に電流パスが形成される。ゲート絶縁膜を絶縁破壊した後は、これを元に戻すことはできず、したがって、不可逆的な不揮発性書き込みが可能となる。アンチヒューズ素子330のゲート331は、読み出しトランジスタ302を介してセンス回路340に接続される。

10

20

30

40

#### [0039]

ここで、選択回路 3 1 0 及びラッチ回路 3 2 0 を構成するトランジスタ、並びに、図 4 に示すトランジスタ 3 0 1 , 3 0 2 は、いずれも他のトランジスタと比べてゲート絶縁膜が厚い耐圧構造を有している。これに対し、アンチヒューズ素子 3 3 0 を構成するトランジスタは、センス回路 3 4 0 や他の内部回路を構成する通常のトランジスタであり、ゲート絶縁膜の膜厚が薄く設定されている。これは、アンチヒューズ素子 3 3 0 の絶縁破壊を行う際に、選択回路 3 1 0 やラッチ回路 3 2 0 が絶縁破壊するのを防止するためである。ゲート絶縁膜を厚くするとトランジスタとしての能力は低下するが、選択回路 3 1 0 やラッチ回路 3 2 0 などの動作速度が若干低下しても、実用上の問題はほぼ皆無である。

#### [0040]

センス回路340は、ラッチ回路320と同様、トランジスタ341,342からなるインバータと、トランジスタ343,344からなるインバータが循環接続された、いわゆるフリップフロップ構成を有している。トランジスタ342,344のソースには、センス信号CSNが供給される。センス信号CSNは、アンチヒューズ素子330の状態を読み出す期間においてはVDDレベルとされ、センス動作を行う際にはVSSレベルとされる。トランジスタ341,342のゲートに接続されるノードaは、読み出しトランジスタ302を介してアンチヒューズ素子330のゲート331に接続されるとともに、ビット記憶回路210の出力端として用いられる。ノードaの代わりに、トランジスタ343,344のゲートに接続されるノードbを出力端として用いても構わない。

## [0041]

ノードa, bには、それぞれトランジスタ345,346を介して電源電圧VDD及び基準電圧Vrefが供給される。トランジスタ345,346は、プリチャージ信号PREがローレベルに活性化するとオンし、ノードa, bをそれぞれ電源電圧VDD及び基準電圧Vrefとの関係は、

VDD > Vref

であり、したがって、プリチャージ直後の状態におけるビット出力  $Bi(i=1 \sim m)$  は ハイレベル(1)である。

#### [0042]

プリチャージを完了した後、読み出しトランジスタ302をオンさせると、ノードaはアンチヒューズ素子330に接続される。このとき、センス信号CSNはVDDレベルとされる。ノードaがアンチヒューズ素子330に接続されると、アンチヒューズ素子330の状態に応じてノードaのレベルが変化する。つまり、アンチヒューズ素子330が総縁破壊されている場合には、ノードaからアンチヒューズ素子330へ電流が流れるため、ノードaの電位は低下し、センス信号CSNをVSSレベルに変化させることによりビット出力Biはローレベル(0)に反転する。これに対し、アンチヒューズ素子330が絶縁破壊されていない場合には、ノードaの電位はVDDに保たれるため、センス信号CSNをVSSレベルに変化させてもビット出力Biはハイレベル(1)を保持する。このようにして、センス回路340は、アンチヒューズ素子330に書き込まれた情報を読み出すことができる。

### [0043]

イネーブル回路 2 2 0 及びディセーブル回路 2 3 0 についても、ビット信号 D A T A i の代わりにイネーブル信号 E 及びディセーブル信号 D が供給され、それぞれイネーブル信号 E a 及びディセーブル信号 D a を出力する他は、図 4 に示したビット記憶回路 2 1 0 と同じ回路構成を有している。

#### [0044]

以上が本実施形態による半導体装置の構成である。次に、本実施形態による半導体装置の動作について、アンチヒューズ回路31に着目して説明する。

#### [0045]

アンチヒューズ回路 3 1 の動作は、不良アドレスを一時的にラッチするセット動作と、 ラッチされた不良アドレスをアンチヒューズ素子に書き込む書き込み動作と、アンチヒュ 10

20

30

40

ーズ素子に書き込まれた不良アドレスを読み出すセンス動作に大別される。これらの動作は、それぞれ上述した「セットモード」、「書き込みモード」及び「センスモード」にエントリすることによって行われる。

[0046]

セット動作及び書き込み動作は、ウェハ状態で行われる一連のテスト工程に含まれる。

[0047]

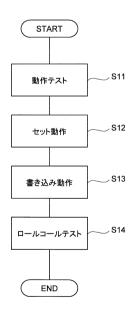

図5は、テスト工程の大まかな流れを示すフローチャートである。

[0048]

テスト工程は図示しないテスタを用いて行われ、図 5 に示すように、まず実際にデータの書き込み及び読み出しを行うことによって、不良アドレスの検出、つまり動作テストを行う(ステップ S 1 1 )。これにより検出された不良アドレスは、テスタの内部に一時的に記憶される。

[0049]

次に、テスタは、記憶した不良アドレスを半導体装置10に転送し、ヒューズセット100内のラッチ回路320にラッチさせる(ステップS12)。この時、アンチヒューズ回路31は「セットモード」にエントリされ、セット動作を行う。次に、テスタは、ラッチ回路320にラッチされた不良アドレスを実際にアンチヒューズ素子330に書き込ませる(ステップS13)。この時、アンチヒューズ回路31は「書き込みモード」にエントリされ、書き込み動作を行う。これにより、複数の不良アドレスがそれぞれヒューズセット100に不揮発的に記憶される。最後に、アンチヒューズ回路31に対してロールコールテストを行う(ステップS14)。各ステップS12~S14における動作の詳細については後述する。

[0050]

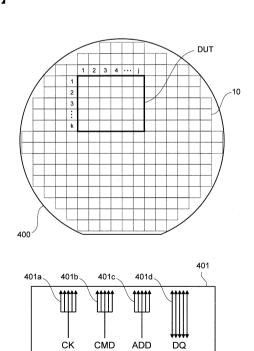

このようなテスト工程は、製造時においてウェハ状態で行われる。つまり、複数の半導体装置(チップ)に対して並列に実行される。具体的には、図 6 に示すように、半導体ウェハ 4 0 0 に含まれる半導体装置のうち、 $j \times k$  個の半導体装置に対して並列に動作テストが行われる。並列にテストされる $j \times k$  個の半導体装置は、いわゆる D U T (Device Under Test) と呼ばれる。D U T の数は、テスタに設けられたプローブカード 4 0 1 の構成に依存し、例えば 2 0 0 個程度の半導体装置が並列にテストされる。

[0051]

プローブカード401は、テスト対象となる半導体装置に設けられた各端子と接触するための多数のプローブを有しているが、図6に示すように、クロック信号CKを供給するためのプローブ401aと、コマンド信号CMDを供給するためのプローブ401bと、アドレス信号ADDを供給するためのプローブ401cは、それぞれチップ間で共通接続されている。これは、不良アドレスを検出するための動作テストにおいては、各チップに個別のクロック信号CK、アドレス信号ADD及びコマンド信号CMDを供給する必要がなく、全てのチップに対してこれら信号を共通に与えればよいからである。

[0052]

これに対し、入出力データDQに関してはチップごとに個別である必要があることから、データDQを授受するためのプローブ401dについては共通接続されず、チップごとに個別接続される。

[0053]

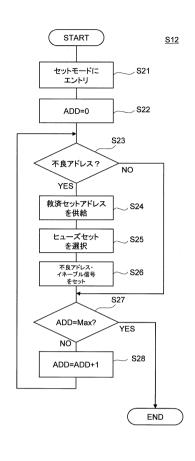

図7は、セット動作(ステップS12)を説明するためのフローチャートである。

[0054]

セット動作とは、検出された不良アドレスをテスタから半導体装置10へ転送し、ヒューズセット100内のラッチ回路320にラッチさせる動作である。上述の通り、テスト 工程は複数のチップに対して並列に実行され、複数のチップに対してアドレス信号ADD が共通に与えられる。つまり、各チップに個別のアドレス信号ADDを供給することはで きない。これに対し、当然ながら不良アドレスはチップごとに異なる。

[0055]

10

20

30

このような問題を解決すべく、本実施形態ではアドレス端子 2 2 を介してアドレス信号 A D D をインクリメント (又はデクリメント)させながら、データ端子 2 3 を用いて不良の有無をチップごとに通知する。以下、具体的に説明する。

### [0056]

## [0057]

制御回路110をセットモードにエントリさせた後、テスタ側においてアドレス信号ADDを最小値(=0)に設定し(ステップS22)、当該アドレスが不良アドレスであるチップに対して「救済セットアドレス」を供給する(ステップS23,S24)。救済セットアドレスとは、当該不良アドレスを記憶させるべきヒューズセット100のアドレスを指す。救済セットアドレスはチップごとに個別である必要があることから、これらの信号の供給にはデータ端子23を介したデータDQを用いる。

### [0058]

救済セットアドレスを受けた制御回路110は、対応する選択信号SELを活性化させ、これによって所定のヒューズセット100を選択する(ステップS25)。これにより、選択されたヒューズセット100内の選択回路310が導通状態となる。この状態で、当該不良アドレスの各ビットDATA1~DATAm及びイネーブル信号Eをヒューズセット100に供給する(ステップS26)。この時、書き込みトランジスタ301は、オフ状態に保持される。これにより、選択されたヒューズセット100内のラッチ回路320には、不良アドレスの各ビットDATA1~DATAm及びイネーブル信号Eがラッチされることになる。

## [0059]

このような動作は、アドレス信号ADDをインクリメントすることにより(ステップS28)、全アドレスに対して行われる。そして、アドレス信号ADDが最大値(ADD=Max)となり、全アドレスのインクリメントが完了すると(ステップS27:YES)、一連のセット動作を完了する。以上の動作により、全ての不良アドレスがヒューズセット100にラッチされることになる。また、不良アドレスがラッチされることになる。

## [0060]

セット動作において1アドレスの処理に要する時間、つまり、図7に示すステップS23~ステップS28までの動作に要する時間は、ナノ秒オーダーである。一例として、1アドレスの処理に要する時間を14nsとし、アドレスの総数を34000アドレスとすると、セット動作を完了するのに必要な時間は約0.48sとなる。つまり、同じDUTに属する全てのチップに対して、0.48秒でセット動作を完了させることができる。

### [0061]

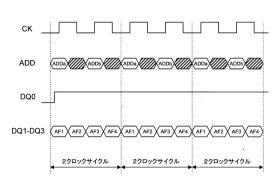

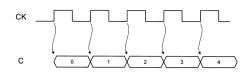

図8は、セット動作時における各信号の変化の一例を示すタイミング図である。

## [0062]

図8に示す例では、2クロックサイクルにてアドレスをインクリメントしている。具体的には、クロック信号 C K の 1 回目の立ち上がりエッジに応答してアドレス信号 A D D の前半部分(A D D a )を入力し、2回目の立ち上がりエッジに応答してアドレス信号 A D D の後半部分(A D D b )を入力している。

## [0063]

一方、救済セットアドレスについては、複数のデータ端子23のうち4つの端子を使用し、このうちビットDQ0をイネーブル信号として用いる。ビットDQ0はハイアクティブであり、対象となる2クロックサイクルの期間中全てハイレベルであれば当該チップの選択が有効となり、アンチヒューズ回路31はイネーブル信号Eを生成する。一方、残り

10

20

30

40

の 3 ビット D Q 1 ~ D Q 3 については、クロック信号 C K の両エッジにて合計 4 回取り込まれる。これら 4 回の取り込み(A F 1 ~ A F 4)によって救済セットアドレスが指定される。上述の通り、ビット D Q 1 ~ D Q 3 により指定される救済セットアドレスは、ヒューズセット 1 0 0 の選択に用いられる。

### [0064]

図9は、セット動作時における各信号の変化の一例を示す表である。

#### [0065]

図9に示す例では、アドレス信号ADDの前半部分ADDa及び後半部分ADDbがいずれも10ビットである。1回目に入力される前半部分ADDaの10ビット(A0~A9)と、2回目に入力される後半部分ADDbの3ビット(A0~A2)からなる13ビットでロウアドレス(又はカラムアドレス)が指定され、後半部分ADDbのビットA4,A5からなる2ビットでバンクアドレスが指定される。後半部分ADDbのビットA3はイネーブルビットであり、セット動作時においては常にハイレベル(1)とされる。残りのビットA6~A9は使用しない。これらのアドレス信号ADDは、同じDUTに属する全てのチップに対して共通に与えられる。

#### [0066]

上述の通り、各アドレスに対応する救済セットアドレスはチップごとに異なり、イネーブル用のビットDQ 0 がハイレベル(1)であれば、他のビットDQ 1 ~DQ 3 が有効となる。図 9 に示す例では、アドレス#2、#5 においてチップ#0 がイネーブルとされ、アドレス#4 においてチップ#1 がイネーブルとされている。

#### [0067]

このように、本実施形態によるセット動作によれば、任意の不良アドレスを個々のチップに対して並列にセットすることができる。

### [0068]

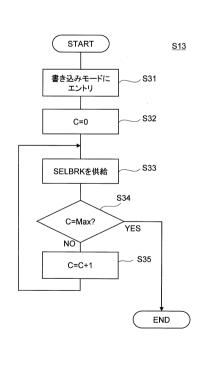

図10は、書き込み動作(ステップS13)を説明するためのフローチャートである。 書き込み動作とは、ラッチ回路320に一時的にラッチされた不良アドレスをアンチヒューズ素子330に書き込む動作である。

#### [0069]

まず、外部端子VPPS,VBBSにそれぞれ4V、-2Vを印加することにより、同じDUTに属する全チップのアンチヒューズ回路31を「書き込みモード」にエントリさせる(ステップS31)。書き込みモードにエントリすると、モード判定回路120はモード信号M1をハイレベル、モード信号M2をローレベルとし、これに応答して制御回路110は書き込みモード時における動作を行う。

### [0070]

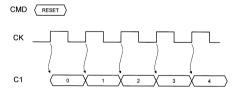

テスタは、制御回路110を書き込みモードにエントリさせた後、図11に示すように、クロック信号CKを周期的に変化させる。書き込みモードにエントリしている場合、制御回路110は、クロック信号CKに同期して内部カウンタ111をインクリメントする。内部カウンタ111のカウント値Cはそれぞれ対応するヒューズセット100を示しており、したがって、カウント値Cが変化する度に異なるヒューズセット100が選択される。カウント値Cは、初期値として0に設定される(ステップS32)。

## [0071]

制御回路110は、カウント値 C により選択されたヒューズセット100に対して、クロック信号 C K がハイレベルの期間に書き込み信号 S E L B R Kを供給する(ステップ S 3 3)。これにより、クロック信号 C K がハイレベルの期間において書き込みトランジスタ 3 0 1 がオンする。この時、読み出しトランジスタ 3 0 2 についてはオフ状態に保持される。

### [0072]

書き込み動作時においては、アンチヒューズ素子330のソース / ドレイン332には、電圧 V B B S V ( - 2 V ) が供給されている。このため、書き込みトランジスタ301 がオンすると、当該ヒューズセット100に含まれるアンチヒューズ素子330のうち、

10

20

30

40

対応するラッチ回路 3 2 0 にハイレベル(1)がラッチされているものについては、ゲート絶縁膜に 6 V(= 4 V + 2 V)の電圧が印加されることになる。これにより、当該アンチヒューズ素子 3 3 0 は絶縁破壊され、非導通状態から導通状態に不可逆的に遷移する。一方、当該ヒューズセット 1 0 0 に含まれるアンチヒューズ素子 3 3 0 のうち、対応するラッチ回路 3 2 0 にローレベル(0)がラッチされているものについては、ゲート絶縁膜に2 V(= 0 V + 2 V)の電圧しか印加されないため、ゲート絶縁膜の破壊は生じない。つまり、当該アンチヒューズ素子 3 3 0 は非導通状態に保たれる。

### [0073]

これにより、ラッチ回路320を用いて一時的に保持されていた不良アドレスがアンチヒューズ素子330に不揮発的に記録されることになる。アンチヒューズ素子330への書き込みは、ラッチ回路320への書き込みに比べて長い時間(例えば5ms)を要する

[0074]

このような動作は、クロック信号 CKに同期して内部カウンタ111をインクリメントすることにより(ステップ S35)、全てのヒューズセット100に対して行われる。そして、内部カウンタ111のカウント値 Cが最大値となり、全てのヒューズセット100に対する書き込み処理が完了すると(ステップ S34:YES)、一連の書き込み動作を完了する。したがって、アンチヒューズ回路 31に含まれるヒューズセット100の数が例えば1000個であるとすれば、約5秒(=5ms×1000)で同じDUTに属する全てのチップに対する書き込み動作が完了する。

[0075]

ここで、書き込み動作をヒューズセット100ごとに行っているのは、テスタが供給可能な電流量に限界があることを考慮したためである。したがって、テスタが供給可能な電流量がある程度大きければ、1つのチップに含まれる複数のヒューズセット100に対して同時に書き込み動作を行っても構わない。これによれば、一連の書き込み動作をより高速に完了させることが可能となる。

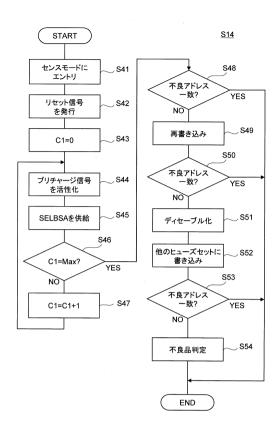

[0076]

図 1 2 は、ロールコールテスト(ステップ S 1 4 )を説明するためのフローチャートである。ロールコールテストとは、各ヒューズセット 1 0 0 に不良アドレスが正しく書き込まれているか否かを判定するテストである。

[0077]

まず、外部端子VPPS,VBBSをオープン状態とすることにより、同じDUTに属する全チップのアンチヒューズ回路31を「センスモード」にエントリさせる(ステップS41)。センスモードにエントリすると、モード判定回路120はモード信号M1をローレベル、モード信号M2をハイレベルとし、これに応答して制御回路110はセンスモード時における動作を行う。

[0078]

テスタは、制御回路110をセンスモードにエントリさせた後、図13に示すように、各チップにリセット信号RESETを供給する(ステップS42)。リセット信号RESETは、コマンド信号CMDの所定の組み合わせであり、したがってコマンド端子21に供給される。

[0079]

センスモードへのエントリ中にリセット信号RESETが供給されると、制御回路110は、クロック信号CKに同期して内部カウンタ112をインクリメントする。内部カウンタ112のカウント値C1は、初期値として0に設定される(ステップS43)。

[080]

内部カウンタ112のカウント値C1はそれぞれ複数のヒューズセット100を指しており、したがって、カウント値C1が変化する度に異なる複数のヒューズセット100が選択されることになる。一つのカウント値C1により選択されるヒューズセット100の数については特に限定されず、例えば32セット程度とすることができる。尚、一つのカ

20

10

30

40

10

20

30

40

50

ウント値 C 1 により選択されるヒューズセット 1 0 0 の数を 2 のべき条に設定すれば、内部カウンタ 1 1 2 を別途設ける必要はなく、内部カウンタ 1 1 1 の上位ビットを使用すれば足りる。

## [0081]

次に、制御回路110は、プリチャージ信号PREを所定期間ローレベルとし、センス回路340をプリチャージする(ステップS44)。上述の通り、電源電圧VDDと基準電圧Vrefとの関係は、

VDD>Vref

であることから、プリチャージ直後の状態におけるビット出力 B i ( i = 1 ~ m ) 及びイネーブル信号 E a はハイレベル(1) である。

[0082]

プリチャージが完了した後、制御回路110は、カウント値C1により選択された複数のヒューズセット100に対してセンス信号SELBSAを供給する(ステップS45)。これにより、選択されたヒューズセット100内の読み出しトランジスタ302がオンし、センス回路340のノードaがアンチヒューズ素子330に接続される。この時、書き込みトランジスタ301についてはオフ状態に保持される。

[0083]

その結果、アンチヒューズ素子330が絶縁破壊されている場合には、ノードaからアンチヒューズ素子330へ電流が流れるため、ノードaの電位は低下し、ビット出力Bi及びイネーブル信号Eaはローレベル(0)に反転する。これに対し、アンチヒューズ素子330が絶縁破壊されていない場合には、ノードaの電位はVDDに保たれるため、ビット出力Bi及びイネーブル信号Eaはハイレベル(1)を保持する。

[0084]

以上により、選択された複数のヒューズセット100に書き込まれた不良アドレス及びイネーブル信号 E a が読み出される。このような動作は、クロック信号 C K に同期して内部カウンタ112をインクリメントすることにより(ステップ S 4 7 )、全てのヒューズセット100に対して行われる。そして、内部カウンタ112のカウント値 C 1 が最大値となり、全てのヒューズセット100に対するセンス動作が完了すると(ステップ S 4 6 : Y E S )、一連のセンス動作を完了する。

[0085]

このようにして読み出された不良アドレスは、図示しないテスタに供給され、動作テスト(ステップS11)にて検出された不良アドレスと比較される。その結果、両者が全て一致していれば(ステップS48:YES)、ロールコールテストを終了する。これに対し、少なくとも一部のアドレスが不一致であれば(ステップS48:NO)、アンチヒューズ素子330の破壊が不十分であることから、同じヒューズセット100に対して再書き込みを実行する(ステップS49)。

[0086]

そして、再度ロールコールを行い、テスタ内に記憶された不良アドレスと比較する。その結果、再書き込みの成功により両者が全て一致していれば(ステップS50:YES)、ロールコールテストを終了する。これに対し、不一致のアドレスが一つでも残存していれば(ステップS50:NO)、当該ヒューズセット100への書き込みを断念し、ディセーブル回路230に含まれるアンチヒューズ素子330への書き込みを行う(ステップS51)。これにより、当該ヒューズセット100は無効化される。

[0087]

次に、無効化したヒューズセット100に書き込むべき不良アドレスを、未使用状態である他のヒューズセット100に対して書き込む(ステップS52)。そして、再々度ロールコールを行い、テスタ内に記憶された不良アドレスと比較する。その結果、代替書き込みの成功により両者が全て一致していれば(ステップS53:YES)、ロールコールテストを終了する。これに対し、不一致のアドレスが一つでも残存していれば(ステップS53:NO)、当該チップを不良品として取り扱う(ステップS54)。

10

20

30

40

#### [0088]

このように、本実施形態では、ヒューズセット100を有効化するイネーブル回路22 0の他に、無効化するディセーブル回路230を備えていることから、再書き込みが失敗 したとしても、直ちに当該チップを廃棄するのではなく、未使用状態である他のヒューズ セット100への代替書き込みが可能となる。これにより、製品の歩留まりを向上させる ことが可能となる。

#### [0089]

以上が一連のテスト工程にて行われる動作である。

## [0090]

このように、本実施形態によれば、セット動作(ステップS12)にて全ての不良アドレスをラッチさせた後、実際にアンチヒューズ素子330に対する書き込み動作(ステップS13)を行っていることから、時間のかかる書き込み動作を複数のチップに対して並列に実行することが可能となる。このため、アンチヒューズ素子330への書き込み時間を大幅に短縮することが可能となる。

#### [0091]

しかも、セット動作(ステップS12)においては、アドレス信号ADDをインクリメントしながら、データDQを用いて救済セットアドレスを供給していることから、異なる不良アドレスを個々のチップに対してセットすることができる。このため、アドレス信号ADDを供給するためのプローブ401cが共通接続された、通常のプローブカード401を用いることが可能となる。

#### [0092]

さらに、ロールコールテスト(ステップS14)において書き込み不良が発見されたヒューズセット100については、ディセーブル回路230を活性化させることによって事後的に無効化することができる。これにより、未使用のヒューズセット100への代替書き込みが可能となることから、製品の歩留まりを向上させることが可能となる。

### [0093]

上述の通り、実使用状態においては、外部端子VPPS,VBBSがオープン状態とされ、したがって、常にセンスモードとなる。したがって、電源投入時やリセット時においてリセット信号RESETを発行すると、図12に示したステップS43~ステップS47の処理が実行され、各ヒューズセット100に書き込まれた不良アドレスRADDが読み出される。そして、読み出された不良アドレスRADDは、図1に示したアドレス比較回路32に供給され、アドレス比較回路32及びアクセス回路12による制御により、不良のある通常セル11aが冗長セル11bに置換される。これにより、不良アドレスが救済される。

## [0094]

以上、本発明の好ましい実施形態について説明したが、本発明は、上記の実施形態に限定されることなく、本発明の主旨を逸脱しない範囲で種々の変更が可能であり、それらも本発明の範囲内に包含されるものであることはいうまでもない。

## [0095]

例えば、上記実施形態では、セット動作(ステップS12)にて全ての不良アドレスをラッチさせた後、実際にアンチヒューズ素子330に対する書き込み動作(ステップS13)を行っているが、本発明がこれに限定されるものではない。したがって、ラッチ回路320を省略し、上述したセット動作時において実際にアンチヒューズ素子330への書き込みを行っても構わない。

## [0096]

また、上記実施形態では、アドレス信号ADDをインクリメントしながら、データDQを用いて救済セットアドレスを供給しているが、本発明がこれに限定されるものではない。したがって、不良アドレス及び救済セットアドレスの供給を別の方法により行っても構わない。

## [0097]

さらに、上記実施形態では、アンチヒューズ素子330として、MOSトランジスタと 同じ構成を有するゲート破壊型のアンチヒューズ素子を用いているが、本発明においてア ンチヒューズ素子の具体的な構成については特に限定されない。したがって、例えば、D RAMのセルキャパシタと同じ構成を有する容量破壊型のアンチヒューズ素子を用いても 構わない。

【図面の簡単な説明】

[0098]

【図1】本発明の好ましい実施形態による半導体装置10の構成を示すブロック図である

- 【図2】アンチヒューズ回路31の回路構成を示すブロック図である。

- 【図3】ヒューズセット100の回路構成を示すブロック図である。

- 【図4】ビット記憶回路210の具体的な回路図である。

- 【図5】テスト工程の大まかな流れを示すフローチャートである。

- 【図6】半導体ウェハ400及びこれをテストするプローブカード401を示す図である

- 【図7】セット動作(ステップS12)を説明するためのフローチャートである。

- 【図8】セット動作時における各信号の変化の一例を示すタイミング図である。

- 【図9】セット動作時における各信号の変化の一例を示す表である。

- 【図10】書き込み動作(ステップS13)を説明するためのフローチャートである。

- 【図11】カウント値Cの変化を示すタイミング図である。

【図12】ロールコールテスト(ステップS14)を説明するためのフローチャートであ

【図13】カウント値C1の変化を示すタイミング図である。

【符号の説明】

[0099]

- 1 0 半導体装置

- 1 1 メモリセルアレイ

- 1 1 a 通常セル

- 1 1 b 冗長セル

- 1 2 アクセス回路

- 1 3 入出力回路

- コマンドデコーダ 1 4

- 2 1 コマンド端子

- 2 2 アドレス端子

- 2 3 データ端子

- 2 4 クロック端子

- 3 1 アンチヒューズ回路

- 3 2 アドレス比較回路

- 1 0 0 ヒューズセット

- 1 1 0 制御回路

111,112 内部カウンタ

- モード判定回路 1 2 0

- 2 1 0 ビット記憶回路

- 2 2 0 イネーブル回路

- 2 3 0 ディセーブル回路

- 3 1 0 選択回路

- 3 2 0 ラッチ回路

- 3 3 0 アンチヒューズ素子

- 3 4 0 センス回路

- 4 0 0 半導体ウェハ

20

10

30

40

4 0 1 プローブカード 4 0 1 a ~ 4 0 1 d プローブ

【図3】

【図4】

【図5】

【図6】

## 【図7】

【図8】

## 【図9】

【図10】

【図11】

【図12】

【図13】

## フロントページの続き

(72)発明者 宮武 伸一

東京都中央区八重洲二丁目2番1号エルピーダメモリ株式会社内

(72)発明者 小川 澄男

東京都中央区八重洲二丁目2番1号エルピーダメモリ株式会社内

審査官 小林 紀和

(56)参考文献 特開平04-123399(JP,A)

特開平08-167298(JP,A)

特開平04-192198 (JP,A)

特開2000-331495(JP,A)

特開2008-97696(JP,A)

特開2002-74980(JP,A)

(58)調査した分野(Int.CI., DB名)

G11C 29/00