#### (19) **日本国特許庁(JP)**

# (12) 特 許 公 報(B2)

(11)特許番号

特許第5612508号 (P5612508)

(45) 発行日 平成26年10月22日(2014.10.22)

(24) 登録日 平成26年9月12日(2014.9.12)

| (51) Int.Cl. |       |           | FΙ      |       |      |

|--------------|-------|-----------|---------|-------|------|

| G11C         | 16/02 | (2006.01) | G11C    | 17/00 | 601C |

| G 1 1 C      | 16/04 | (2006.01) | G 1 1 C | 17/00 | 601E |

| G06F         | 12/16 | (2006.01) | G11C    | 17/00 | 622E |

|              |       |           | G11C    | 17/00 | 641  |

|              |       |           | GO6F    | 12/16 | 310A |

請求項の数 10 (全 17 頁)

特願2011-39857 (P2011-39857) (21) 出願番号 (22) 出願日 平成23年2月25日 (2011.2.25) (65) 公開番号 特開2011-222107 (P2011-222107A) 平成23年11月4日(2011.11.4) (43) 公開日 平成25年12月11日 (2013.12.11) 審査請求日 特願2010-69602 (P2010-69602) (31) 優先権主張番号 平成22年3月25日 (2010.3.25) (32) 優先日 (33) 優先権主張国 日本国(JP)

||(73)特許権者 000005821

パナソニック株式会社

大阪府門真市大字門真1006番地

(74)代理人 100067828

弁理士 小谷 悦司

|(74)代理人 100115381

弁理士 小谷 昌崇

(74)代理人 100109438

弁理士 大月 伸介

|(72)発明者 本多 利行

大阪府門真市大字門真1006番地 パナ

ソニック株式会社内

審査官 後藤 彰

最終頁に続く

# (54) 【発明の名称】不揮発性メモリコントローラ及び不揮発性記憶装置

# (57)【特許請求の範囲】

### 【請求項1】

不揮発性メモリを制御する不揮発性メモリコントローラであって、

前記不揮発性メモリは、複数のブロックを含み、

前記ブロックは、複数のメモリセルを含み、前記不揮発性メモリにおけるデータの消去 単位であり、

前記メモリセルは、<u>書き込み種別として 2 値書き込みと多値書き込みとが可能であり、</u> それぞれ N ビット( N は 1 以上の整数)の情報を記録可能であり、

前記メモリセルの特性の劣化量は、記録する情報量に応じて異なり、

前記不揮発性メモリコントローラは、

前記不揮発性メモリに対してデータの読み出し、書き込み、及び消去の制御を行う制御部と、

前記ブロック単位で前記メモリセルの劣化度合いを記録するためのストレステーブルと を備え、

前記制御部は、<u>前記ストレステーブルの劣化度合いの値に、</u>前記書き込み種別に対応した劣化度合いの加算量を加算することにより、前記ブロックに対する消去のサイクル毎に、前記ストレステーブルに、前記メモリセルに格納する情報量に応じて前記メモリセルの劣化度合いを記録することを特徴とする不揮発性メモリコントローラ。

### 【請求項2】

前記メモリセルに記録する情報量は、前記ブロックの単位で同じビット数であることを

特徴とする請求項1記載の不揮発性メモリコントローラ。

# 【請求項3】

前記制御部は、前記書き込みの制御において、前記ストレステーブルを参照し、前記不揮発性メモリ前記メモリセルの劣化度合いが少ないブロックにデータを書き込むことを特徴とする請求項1記載の不揮発性メモリコントローラ。

#### 【請求項4】

前記制御部は、前記ブロックからデータを消去した後、前記ブロックにデータを書き込む前に、前記ストレステーブルに前記メモリセルの劣化度合いを記録することを特徴とする請求項1記載の不揮発性メモリコントローラ。

#### 【請求項5】

前記不揮発性メモリコントローラの外部から指定されるアドレスを論理アドレスとし、前記不揮発性メモリの前記ブロックのアドレスを物理アドレスとして、前記論理アドレスと前記物理アドレスとの対応情報を格納するアドレス変換テーブルをさらに備えることを特徴とする請求項1記載の不揮発性メモリコントローラ。

### 【請求項6】

前記論理アドレスに対応して、前記メモリセルに記録する情報量を決定するための領域 指定テーブルをさらに備えることを特徴とする請求項 5 記載の不揮発性メモリコントロー ラ。

#### 【請求項7】

前記領域指定テーブルは、前記不揮発性メモリコントローラの外部から書き換え可能なことを特徴とする請求項6記載の不揮発性メモリコントローラ。

#### 【請求項8】

前記メモリセルの劣化度合いは、前記メモリセルに書き込まれたデータの保持期間を基準として決定されることを特徴とした請求項1記載の不揮発性メモリコントローラ。

#### 【請求項9】

請求項1から8のいずれか1項に記載の不揮発性メモリコントローラと、 前記不揮発性メモリとを備えることを特徴とする不揮発性記憶装置。

#### 【請求項10】

前記不揮発性メモリは、NANDタイプのフラッシュメモリを含むことを特徴とする請求項9記載の不揮発性記憶装置。

【発明の詳細な説明】

# 【技術分野】

# [0001]

本発明は、フラッシュメモリ等の不揮発性メモリを制御する不揮発性メモリコントローラ、及び、該不揮発性メモリコントローラを用いた不揮発性記憶装置に関する。

#### 【背景技術】

# [0002]

近年、書き換え可能な不揮発性メモリであるNANDタイプのフラッシュメモリを搭載した不揮発性記憶装置として、メモリーカードがデジタルカメラや携帯電話の記憶媒体に使用され、その市場が拡大している。

#### [0003]

また、不揮発性記憶装置は、半導体プロセスの微細化に伴い、ビット単価が下がり、安価な記憶デバイスとして、メモリーカード以外の市場、例えば、HDD(Hard Disk Drive)と置き換えられるSSD(Solid State Drive)や、ホスト機器に直接搭載するエンベデッドシステムのメモリに用いられ、その適用が拡がっている。

### [0004]

ここで、NANDタイプのフラッシュメモリの特徴として、以下の項目が挙げられる。

#### [0005]

- ・半導体メモリの中で最も容量が大きく、低ビットコストの不揮発性メモリである

- ・半導体プロセスの微細化に伴い、データの信頼性が低下している

10

20

30

40

・2値や多値の複数のタイプのメモリセルがある以下、それぞれについて順に説明する。

#### [0006]

NANDタイプのフラッシュメモリは、半導体プロセスの最小加工寸法をFとすると、(2F)の2乗の大きさで1つのメモリセルを構成できる。このことが、NANDタイプのフラッシュメモリを、半導体メモリの中で最も低ビットコストとし、且つ最も大容量なメモリとしている。

#### [0007]

また、ここ数年は、プロセスドライバーとして、半導体プロセスの最も進んだプロセスルールを使用して、NANDタイプのフラッシュメモリの製造が行なわれている。これにより、NANDタイプのフラッシュメモリは、他のメモリを用いていたシステムにも、使用され始めている。

#### [00008]

例えば、高速なランダムアクセスが要求されるプログラムコードは、NORタイプのフラッシュメモリに格納され、大きな容量が要求されるユーザデータは、NANDタイプのフラッシュメモリに格納されていたシステムが、単一のNANDフラッシュメモリのみに置き換わっている。

### [0009]

これは、搭載するNANDタイプのフラッシュメモリの容量が、必要なNORタイプのフラッシュメモリの容量に比べて十分小さく、また、NORタイプのフラッシュメモリに搭載していたプログラムコードをNANDタイプのフラッシュメモリに格納しても、その影響が少なく、NANDタイプのフラッシュメモリを使用する工夫を盛り込んだとしても、NORタイプのフラッシュメモリをなくすことができるコストメリットが大きいためである。

#### [0010]

また、NANDタイプのフラッシュメモリの大容量化は、半導体プロセスの微細化によるものが大きい。しかし、半導体プロセスの微細化は、メリットばかりではなく、データの信頼性の低下が問題になっている。すなわち、微細化が進むと、データ保持特性は低下し、書き換え処理による特性劣化が進む。

# [0011]

ここで、フラッシュメモリのメモリセルは、MOS (Metal Oxide Semiconductor)タイプトランジスタのコントロールゲートと基盤との間に、電子を不揮発で保持するフローティングゲートを持つ構成をとり、基盤とフローティングゲートとの間で電子をやり取りすることにより、データの消去及び書き込みを行う。また、フラッシュメモリを構成するトランジスタに流れる電流量を判定することにより、フラッシュメモリのメモリセルからデータが読み出される。

# [0012]

上記のように、フラッシュメモリのメモリセルに対して、データの消去及び書き込みを繰り返すと、基盤とフローティングゲートとの間を電子が移動し、基盤とフローティングゲートとの間の絶縁膜(以降、ゲート絶縁膜)が劣化してしまう。ゲート絶縁膜が劣化すると、ゲート絶縁膜中に存在する欠陥を経由してフローティングゲートから基盤に電子が漏れ、ゲート絶縁膜中の欠陥にトラップされた電子の影響で書き込みの効率が低下して、データの信頼性が低下する要因となる。

# [0013]

こういったデメリットはあるが、圧倒的なビット単価を強みとすることができるので、 データの信頼性を向上させる工夫を盛り込んででも、微細化の進んだフラッシュメモリの 用途は拡がっている。

#### [0014]

また、フラッシュメモリのデータの信頼性を検討する上で重要な要素は、データの書き 込みに対するメモリセルの取り扱いである。すなわち、2値のメモリセルとしてデータを 10

20

30

40

書き込んでいるのか、多値のメモリセルとしてデータを書き込んでいるのかによって、データの信頼性は大きく異なり、 2 値のメモリセルとしてデータを書き込む方が、データの信頼性が高くなる。一方、当然であるが、多値のメモリセルとしてデータを書き込む方が、メモリの容量を大きくすることが可能になり、同時にビット単価を低下させることができる。

#### [0015]

以上のようなNANDタイプのフラッシュメモリの特徴から、フラッシュメモリに対してデータを格納する際に書き込み方式の異なる複数の書き込み方式を用いることがある。例えば、信頼性に対する要求が高いプログラムコードを2値のメモリセルとして書き込む2値書き込みを行い、容量に対する要求が高いユーザデータを多値のメモリセルとして書き込む多値書き込みを行うことが考えられる。

[0016]

次に、2値書き込みと多値書き込みとの比較をする。以下、簡単のために、2値書き込みの場合と4値書き込みの場合について、図を用いて説明する。

# [0017]

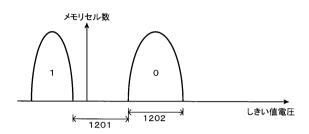

図12は、2値書き込みした場合のメモリセルのしきい値電圧が、どのように分布するかを示す図である。図12の左側の分布が、消去状態のメモリセルのしきい値電圧の分布を示し、図12の右側の分布が、書き込み状態のメモリセルのしきい値電圧の分布を示している。2値書き込みの場合、メモリセルのしきい値電圧が、左の分布にあるか、右の分布にあるかで1ビットの情報を記憶する。

[0018]

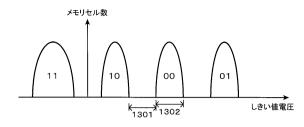

図13は、4値書き込みした場合のメモリセルのしきい値電圧が、どのように分布するかを示す図である。図13の左側の分布が、消去状態のメモリセルのしきい値電圧の分布を示し、図13の右側の3つの分布が、それぞれ異なった書き込み状態のメモリセルのしきい値電圧の分布を示している。4値書き込みの場合、メモリセルのしきい値電圧が4つの分布のどこにあるかで2ビットの情報を記憶する。

#### [0019]

図12及び図13から、2値書き込みの場合のしきい値電圧の分布の間隔1201に比べて、4値書き込みの場合のしきい値電圧の分布の間隔1301は狭くなっている。このように、分布の間隔が狭くなることにより、メモリセルのしきい値電圧の変動に対してのマージンが小さくなる。つまり、4値書き込みの方が、2値書き込みに比べて、データ保持期間が短くなる。

[0020]

また、2値書き込みの場合のしきい値電圧の分布の幅1202に比べて、4値書き込みの場合のしきい値電圧の分布の幅1302を狭くする必要がある。このように、メモリセルのしきい値電圧の分布を狭くするためには、メモリセルへの書き込みにおける細かな制御を繰り返し実行することが必要となる。結果として、メモリセルへの書き込みストレスを印加する回数が多くなったり、印加する期間が長くなることになり、書き換え時におけるゲート絶縁膜の劣化が進み、書き換え回数が少なくなる。

[0021]

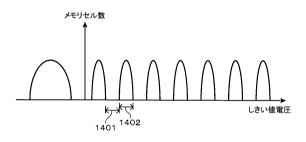

図14は、8値書き込みの場合のメモリセルのしきい値電圧が、どのように分布するかを示す図である。8値書き込みの場合、4値書き込みの場合に比べてさらに、しきい値電圧の分布の間隔1401と、しきい値電圧の分布の幅1402とがそれぞれ狭くなっていることが分かる。つまり、8値書き込みを行った場合には、書き換え回数はさらに少なく、データ保持期間はさらに短くなる。

# [0022]

また、特許文献1には、2値書き込みの領域と、多値書き込みの領域とを持った不揮発性記憶装置において、メモリセルアレイを2値書き込みの領域として使用する領域と、16値(すなわち、多値)書き込みの領域として使用する領域とに物理的に分割して管理することにより、それぞれの領域において最適なブロック管理を行う技術が示されている。

10

20

30

40

#### 【先行技術文献】

【特許文献】

[0023]

【特許文献1】特開2008-257773号公報

【発明の概要】

【発明が解決しようとする課題】

[0024]

しかしながら、上記の特許文献1のような構成においては、2値書き込みの領域として使用する領域と、16値書き込みの領域として使用する領域とを物理的に区別して管理しているために、2値書き込み領域のみを繰り返し使用した場合に、2値書き込み領域の物理ブロックの書き換え回数のみが増えて劣化していくが、多値書き込み領域の物理ブロックは使用されないために劣化しないままであり、結果として、全体の物理ブロックを均等に使用することができないという課題がある。

[0025]

また、それぞれの劣化の程度を書き換え回数のみで管理している。そのために、本来は 劣化度合いが異なる 2 値の書き込みと 1 6 値の書き込みとについて、共通の劣化の尺度を 持ち得ないために、それぞれの領域の相互利用を阻害する要因となる。

[0026]

本発明の目的は、任意に 2 値書き込み領域と多値書き込み領域とを設けた上で、それぞれの領域に対して物理的な領域制限を必要とせず、不揮発性メモリの全てのブロックを有効に利用することが可能な不揮発性メモリコントローラ及び不揮発性記憶装置を提供することである。

【課題を解決するための手段】

[0027]

本発明に係る不揮発性メモリコントローラは、不揮発性メモリを制御する不揮発性メモリコントローラであって、前記不揮発性メモリは、複数のブロックを含み、前記ブロックは、複数のメモリセルを含み、前記不揮発性メモリにおけるデータの消去単位であり、前記メモリセルは、それぞれNビット(Nは1以上の整数)の情報を記録可能であり、前記メモリセルの特性の劣化量は、記録する情報量に応じて異なり、前記不揮発性メモリコントローラは、前記不揮発性メモリに対してデータの読み出し、書き込み、及び消去の制御を行う制御部と、前記ブロック単位で前記メモリセルの劣化度合いを記録するためのストレステーブルとを備え、前記制御部は、前記ブロックに対する消去のサイクル毎に、前記ストレステーブルに、前記メモリセルに格納する情報量に応じて前記メモリセルの劣化度合いを記録する。

[0028]

この不揮発性メモリコントローラにおいては、データの消去単位となる不揮発性メモリのブロック単位で、ブロックに対する消去のサイクル毎に、メモリセルに格納する情報量に応じてメモリセルの劣化度合いをストレステーブルに記録しているので、ブロック別に2値書き込みとが可能な不揮発性記憶装置において、2値書き込みを行った場合の劣化とを共通の尺度で管理する仕組みを導入することにより、不揮発性メモリの劣化の均等化を図り、不揮発性メモリの劣化を抑えることができるとともに、不揮発性メモリの全てのブロックを有効に利用することができる。この結果、任意に2値書き込み領域と多値書き込み領域とを設けた上で、それぞれの領域に対して物理的な領域制限を必要とせず、不揮発性メモリの全てのブロックを有効に利用することができる。

[0029]

前記メモリセルに記録する情報量は、前記ブロックの単位で同じビット数であることが 好ましい。

[0030]

この場合、メモリセルに記録する情報量がブロックの単位で同じビット数であるので、

10

20

30

40

ブロック単位でデータの消去及び書き込みを行う不揮発性メモリにおいて、 2 値書き込みを行った場合の劣化と、多値書き込みを行った場合の劣化とを共通の尺度で管理する仕組みを導入することができる。

#### [0031]

前記制御部は、前記書き込みの制御において、前記ストレステーブルを参照し、前記メモリセルの劣化度合いが少ないブロックにデータを書き込むことが好ましい。

#### [0032]

この場合、書き込みの制御において、ストレステーブルを参照し、メモリセルの劣化度合いが少ないブロックにデータを書き込んでいるので、全てのブロックを均等に使用することができる。

#### [0033]

前記制御部は、前記ブロックからデータを消去した後、前記ブロックにデータを書き込む前に、前記ストレステーブルに前記メモリセルの劣化度合いを記録することが好ましい

### [0034]

この場合、ブロックを消去した後、ブロックにデータを書き込む前に、ストレステーブルにメモリセルの劣化度合いを記録しているので、ブロックに対する消去のサイクル毎に、メモリセルの劣化度合いをストレステーブルに確実に記録することができる。

#### [0035]

前記不揮発性メモリコントローラの外部から指定されるアドレスを論理アドレスとし、 前記不揮発性メモリの前記ブロックのアドレスを物理アドレスとして、前記論理アドレス と前記物理アドレスとの対応情報を格納するアドレス変換テーブルをさらに備えることが 好ましい。

#### [0036]

この場合、不揮発性メモリコントローラの外部から指定されるアドレスを論理アドレスとし、不揮発性メモリのブロックのアドレスを物理アドレスとして、論理アドレスと物理アドレスとの対応情報を格納するアドレス変換テーブルを用いて、2値書き込みを行った場合の劣化と、多値書き込みを行った場合の劣化とを共通の尺度で管理しながら、外部から指定される論理アドレスに対応する物理アドレスを有する不揮発性メモリのブロックにデータを書き込むことができる。

#### [0037]

前記論理アドレスに対応して、前記メモリセルに記録する情報量を決定するための領域 指定テーブルをさらに備えることが好ましい。

#### [0038]

この場合、領域指定テーブルを用いて、不揮発性メモリコントローラの外部から指定される論理アドレスに対するメモリセルに記録する情報量を決定することができるので、決定した情報量に応じた書き込み方式でデータを書き込むことができる。この結果、2値書き込み領域と多値書き込み領域とを設けた上で、それぞれの領域に対して物理的な領域制限を設けることなく、不揮発性メモリの全てのブロックを有効に利用することができる。

#### [0039]

前記領域指定テーブルは、前記不揮発性メモリコントローラの外部から書き換え可能なことが好ましい。

### [0040]

この場合、領域指定テーブルの内容を不揮発性メモリコントローラの外部から書き換えることができるので、任意に 2 値書き込み領域と多値書き込み領域とを設けた上で、それぞれの領域に対して物理的な領域制限を設けることなく、不揮発性メモリの全てのブロックを有効に利用することができる。

#### [0041]

前記メモリセルの劣化度合いは、前記メモリセルに書き込まれたデータの保持期間を基準として決定されることが好ましい。

10

20

30

40

#### [0042]

この場合、メモリセルの劣化度合いが、メモリセルに書き込まれたデータの保持期間を 基準として決定されているので、2値書き込み領域及び多値書き込み領域ともに、データ の信頼性を向上することができる。

#### [0043]

本発明に係る不揮発性記憶装置は、上記いずれかの不揮発性メモリコントローラと、前 記不揮発性メモリとを備える。

#### [0044]

前記不揮発性メモリは、NANDタイプのフラッシュメモリを含むことが好ましい。

この場合、NANDタイプのフラッシュメモリを用いているので、容量が大きく、低ビ ットコストの不揮発性記憶装置を提供することができるとともに、データの信頼性を向上 することができる。

# 【発明の効果】

### [0046]

本発明によれば、任意に2値書き込み領域と多値書き込み領域とを設けた上で、それぞ れの領域に対して物理的な領域制限を必要とせず、不揮発性メモリのブロックを有効に利 用することが可能な不揮発性メモリコントローラ及び不揮発性記憶装置を提供することが できる。

# 【図面の簡単な説明】

[0047]

【図1】本発明の一実施の形態のメモリーカードの構成を示す図である。

【図2】図1に示すメモリーカードのアドレス変換テーブルの構成の一例を示す図である

【図3】図1に示すメモリーカードの無効ブロックテーブルの構成の一例を示す図である

【図4】図1に示すメモリーカードの領域指定テーブルの構成の一例を示す図である。

【図5】図1に示すメモリーカードの劣化度テーブルの構成の一例を示す図である。

【図6】図1に示すメモリーカードの書き込み処理のフローチャートである。

【図7】図1に示すメモリーカードの劣化度テーブルの更新後の状態の一例を示す図であ

【図8】図1に示すメモリーカードのアドレス変換テーブルの更新後の状態の一例を示す 図である。

【 図 9 】図 1 に示すメモリーカードの無効ブロックテーブルの更新後の状態の一例を示す 図である。

【図10】図1に示すメモリーカードの書き込み処理の各処理における各テーブルの参照 及び更新の有無を示す図である。

【図11】図1に示すメモリーカードのフラッシュメモリ部の書き換え回数とデータ保持 期間との関係を示す図である。

【図12】2値書き込みした場合のメモリセルのしきい値電圧の分布を示す図である。

【図13】4値書き込みした場合のメモリセルのしきい値電圧の分布を示す図である。

【図14】8値書き込みした場合のメモリセルのしきい値電圧の分布を示す図である。

### 【発明を実施するための形態】

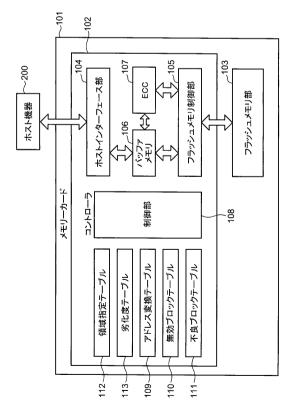

# [0048]

以下、図面を参照して、本発明の一実施の形態のメモリーカードについて説明する。図 1は、本発明の一実施の形態のメモリーカードの構成を示すブロック図である。

#### [0049]

< 1 . メモリーカードの構成 >

メモリーカード101は、外部のホスト機器200と接続され、ホスト機器200と双 方向に通信を行うことにより、ホスト機器200からの指示に応じてデータの読み出し及 10

20

30

40

び/又は書き込みを行う。

# [0050]

メモリーカード 1 0 1 は、コントローラ 1 0 2 と、フラッシュメモリ部 1 0 3 とを備える。コントローラ 1 0 2 は、メモリーカード 1 0 1 とホスト機器 2 0 0 とのインターフェースの制御を行うと共に、フラッシュメモリ部 1 0 3 の制御を行う。

# [0051]

フラッシュメモリ部103は、不揮発性メモリの一例であるフラッシュメモリからなる。図示しないが、フラッシュメモリは、NANDタイプのフラッシュメモリであり、複数の物理ブロックからなる。物理ブロックは、複数のメモリセルからなる。物理ブロックは、フラッシュメモリにおけるデータの消去単位である。メモリセルの各々は、それぞれNビット(Nは1以上の整数)の情報を記録可能であり、メモリセルの特性の劣化量は、記録する情報量に応じて異なる。

#### [0052]

ここで、メモリーカード 1 0 1 が不揮発性記憶装置の一例であり、コントローラ 1 0 2 が不揮発性メモリコントローラの一例であり、フラッシュメモリ部 1 0 3 が不揮発性メモリの一例である。また、ホスト機器 2 0 0 の一例としては、デジタルカメラ、携帯電話、ビデオレコーダ、コンピュータ等が該当する。

#### [0053]

メモリーカード 1 0 1 は、メモリーカード 1 0 1 の外部のホスト機器 2 0 0 からのアドレスを指定したデータの書き込みや読み出しの制御に対応して、フラッシュメモリ部 1 0 3 からデータを読み出す。

#### [0054]

コントローラ102は、ホストインターフェース部104、フラッシュメモリ制御部105、バッファメモリ106、ECC107、制御部108、アドレス変換テーブル10 9、無効ブロックテーブル110、不良ブロックテーブル111、領域指定テーブル11 2、及び劣化度テーブル113を備える。

#### [0055]

ホストインターフェース部104は、ホスト機器200とのインターフェースを制御する。フラッシュメモリ制御部105は、フラッシュメモリ部103の制御を行う。バッファメモリ106は、ホスト機器200からの書き込みデータや、ホスト機器200への読み出しデータをフラッシュメモリ部103との間で転送する際に、一時的にデータを格納するための揮発性のバッファメモリである。

#### [0056]

ECC107は、ECC(エラー検出訂正)回路であり、フラッシュメモリ部103にデータを書き込む際に付加するECC(Error Correcting Code:誤り訂正符号)を生成し、フラッシュメモリ部103からデータを読み出す際に、読み出したデータの訂正を行う。

#### [0057]

制御部108は、図示を省略した配線により各ブロックに接続され、各ブロックの動作を制御することにより、コントローラ102内部全体の制御を行う。また、制御部108は、フラッシュメモリ部103に対してデータの読み出し、書き込み、及び消去の制御を行う。

# [0058]

アドレス変換テーブル109は、ホスト機器200から指定されるアドレス(論理アドレス)と、フラッシュメモリ部103の物理ブロックのアドレス(物理アドレス)との対応を記録する。すなわち、アドレス変換テーブル109は、コントローラ102の外部からの指定されるアドレスを論理アドレスとし、フラッシュメモリ部103の物理ブロックのアドレスを物理アドレスとして、論理アドレスと物理アドレスとの対応情報を格納する

[0059]

50

20

10

30

- -

無効ブロックテーブル 1 1 0 は、フラッシュメモリ部 1 0 3 において有効なデータが書き込まれておらず、且つ、不良ブロックでない(不良ブロックテーブル 1 1 1 で管理されていない)物理ブロックのアドレスのリストを記録する。すなわち、無効ブロックテーブル 1 1 0 は、論理アドレスに対応するデータが格納されておらず、新たなデータの書き込みが可能な物理ブロックの物理アドレスを格納しており、データの書き込みに使用可能な物理ブロックが無効ブロックテーブル 1 1 0 に登録されている。

#### [0060]

不良ブロックテーブル111は、フラッシュメモリ部103における不良ブロックの物理アドレスのリストを記録する。

### [0061]

領域指定テーブル112は、ホスト機器200から指定される論理アドレスを複数の領域に分割し、それぞれの分割された領域のデータに対してデータの書き込み方法を示すテーブルである。領域指定テーブル112は、ホスト機器200から指定される論理アドレスに対応して、フラッシュメモリ部103の物理ブロックのメモリセルに記録する情報量を決定するために使用され、コントローラ102の外部、例えば、ホスト機器200からテーブルの内容を書き換え可能に構成されている。

#### [0062]

ここで、メモリセルに記録する情報量としては、2値、又は3値以上の多値(例えば、4値、8値、16値)があり、書き込み方式を特定するための書き込み種別の情報として、2値書き込みを示す情報又は多値書き込みを示す情報が、任意の論理アドレス範囲毎に領域指定テーブル112に記憶される。

#### [0063]

例えば、領域指定テーブル 1 1 2 は、データを書き換え可能な揮発性メモリ又は不揮発性メモリから構成され、ホスト機器 2 0 0 が、論理アドレス範囲と、当該論理アドレス範囲に適用される書き込み方式を特定するための書き込み種別の情報とを含む領域指定テーブル書き換え命令をメモリーカード 1 0 1 へ送信すると、制御部 1 0 8 は、領域指定テーブル書き換え命令により指定された論理アドレス範囲と、当該論理アドレス範囲に適用される書き込み種別の情報とを領域指定テーブル 1 1 2 に格納する。

### [0064]

なお、複数の多値を使用する場合、多値ごとに当該多値を示す情報を領域指定テーブル 1 1 2 に記録するようにしてもよく、例えば、4 値の場合に、4 値書き込みを示す情報を 記録し、8 値の場合に、8 値書き込みを示す情報を記録するようにしてもよい。

#### [0065]

劣化度テーブル 1 1 3 は、フラッシュメモリ部 1 0 3 に含まれる全ての物理ブロックの劣化度合いを示すテーブルであり、ブロック単位でメモリセルの劣化度合いを記録するためのストレステーブルの一例である。制御部 1 0 8 は、ブロックに対する消去処理のサイクル毎に、劣化度テーブル 1 1 3 に、メモリセルに格納する情報量に応じてメモリセルの劣化度合いを記録する。

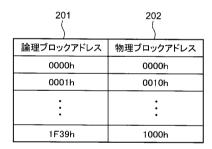

### [0066]

### < 2 . 各種テーブルの構成例 >

図2は、アドレス変換テーブル109の構成の一例を示す図である。アドレス変換テーブル109は、論理ブロックアドレス201の情報と、物理ブロックアドレス202の情報とを対応付けて記憶している。ここで、論理アドレスの範囲を、フラッシュメモリ部103の物理ブロックの容量と等量の単位の論理ブロックに分割し、各論理ブロックを特定するための論理アドレスの情報を、論理ブロックアドレス201の情報とする。一方、物理ブロックアドレス202の情報は、物理ブロックを特定するための物理アドレスの情報である。アドレス変換テーブル109では、1つの論理ブロックアドレス201と、それに対応するフラッシュメモリ部103の物理ブロックアドレス202との組で一つのレコードが構成されている。

### [0067]

10

20

30

10

20

30

40

50

例えば、論理ブロックアドレス「0000h」に対応するデータは、物理ブロックアドレス「0000h」の物理ブロックすなわちフラッシュメモリ部103のアドレス「0000h」の物理ブロックに格納され、論理ブロックアドレス「001h」に対応するデータは、物理ブロックアドレス「0010h」の物理ブロックすなわちフラッシュメモリ部103のアドレス「0010h」の物理ブロックに格納されていることを示す。また、論理ブロックアドレスとして、0000hから1F39hまでの範囲のアドレスが管理されている。

### [0068]

図 3 は、無効ブロックテーブル 1 1 0 の構成の一例を示す図である。無効ブロックテーブル 1 1 0 は、フラッシュメモリ部 1 0 3 における無効なデータを格納する物理ブロックのアドレスである物理ブロックアドレスの情報、例えば、 0 1 2 3 h、 0 4 5 6 h、…を記憶している。なお、フラッシュメモリ部 1 0 3 の物理ブロックのアドレスの範囲は、 0 0 0 h ~ 1 F F F h の範囲とし、 2 0 0 0 h は、無効ブロックテーブル 1 1 0 における無効な値として取り扱う。

### [0069]

不良ブロックテーブル111の構成は、上記の無効ブロックテーブル110と同様であり、フラッシュメモリ部103における不良データの物理ブロックのアドレスを格納する。すなわち、不良ブロックテーブル111は、不良ブロックの物理ブロックアドレスの情報を格納し、2000hを無効値として取り扱う。

# [0070]

図4は、領域指定テーブル112の構成の一例を示す図である。領域指定テーブル112では、先頭論理アドレス401の情報と、最終論理アドレス402の情報と、書き込み種別403の情報との組で1つのレコードが構成される。書き込み種別403は、先頭論理アドレス401から最終論理アドレス402までのアドレス領域に対する書き込み種別を定義する。

#### [0071]

例えば、先頭論理アドレス401の「0000h」から最終論理アドレス402の「0001h」までの論理アドレスに対応するデータの書き込み種別403の情報は、2値書き込みであり、2値書き込みを表す「2値」が格納される。先頭論理アドレス401の「0002h」から最終論理アドレス402の「1F29h」までの論理アドレスに対応するデータの書き込み種別403は、多値書き込みであり、多値書き込みを表す「多値」が格納される。先頭論理アドレス401の「1F30h」から最終論理アドレス402の「1F39h」までの論理アドレスに対応するデータの書き込み種別403は、2値書き込みであり、2値書き込みを表す「2値」が格納される。

# [0072]

なお、領域指定テーブル112の情報は、メモリーカード101の外部、例えば、ホスト機器200から書き換えることにより、任意に設定可能な構成をとる。また、書き込み種別403として記憶される情報は、上記の例に特に限定されず、メモリーカード101が2値書き込みであるか、多値書き込みであるかを判別可能であれば、種々の情報を用いることができる。

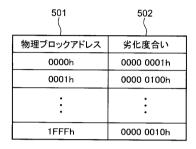

# [0073]

図5は、劣化度テーブル113の構成の一例を示す図である。劣化度テーブル113は、物理プロックアドレス501の情報と、メモリセルの劣化度合いを表す劣化度合い502の情報とを対応付けて記憶している。ここで、劣化度合い502の情報は、フラッシュメモリ部103の全ての物理プロックに対応して、その物理プロックがデータの消去と書き込みとの繰り返しである書き換えストレスによってどの程度劣化しているかを示す値を用いることができる。

#### [0074]

例えば、書き込み種別の劣化度合い502の値としては、全く劣化していない状態を初期値となる「000000h」とし、データの書き換えが行われる毎に、その書き込

みが 2 値書き込みなのか多値書き込みなのかに対応した所定のストレス量(例えば、 2 値書き込みが「1」、多値書き込みが「3」)を前回の劣化度合いの値に加算する。書き込み種別のフラッシュメモリ部 1 0 3 の物理ブロック「0 0 0 0 h」の劣化度合い 5 0 2 の値は、「0 0 0 0 0 0 1 h」であり、物理ブロック「0 0 0 1 h」の劣化度合い 5 0 2 の値は、「0 0 0 0 0 1 0 0 h」であり、物理ブロック「1 FFFh」の劣化度合い 5 0 2 の値は「0 0 0 0 0 0 1 0 h」である。

#### [0075]

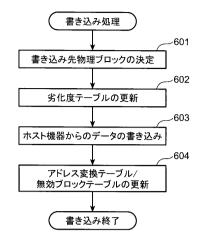

< 3 . 書き込み処理におけるテーブル更新 >

次に、領域指定テーブル112と劣化度テーブル113の使用方法を説明するために、メモリーカード101におけるデータの書き込み処理を説明する。図6は、メモリーカード101に対するデータの書き込み処理における制御部108の動作のフローチャートである。メモリーカード101は、ホスト機器200からの論理アドレスを指定した書き込み命令によって書き込み処理を開始する。

# [0076]

まず、処理601を説明する。制御部108は、書き込み先物理ブロックを決定し、書き込み先物理ブロックの消去を行う。具体的には、制御部108は、無効ブロックテーブル110反び劣化度テーブル113を参照して、無効ブロックテーブル110に登録されている物理ブロックアドレスの中から、劣化度テーブル113に示されている劣化度合いが最も少ない物理ブロックアドレスを選択し、選択した物理ブロックアドレスの物理ブロックを書き込み先物理ブロックとして決定する。次に、制御部108は、フラッシュメモリ部103に対して書き込み先物理ブロックの物理アドレスを指定してデータを消去する消去命令を発行し、書き込み先物理ブロックのデータを消去する。

# [0077]

図3及び図5に示す例では、無効ブロックテーブル110に登録されている物理ブロックアドレスのうち、最も劣化度合いの少ない物理ブロックアドレスは、劣化度合いが「0000010h」の物理ブロックアドレス「1FFFh」となり、物理ブロックアドレス「1FFFh」の物理ブロックが書き込み先物理ブロックとなる。なお、物理ブロックアドレス「0000h」の物理ブロックの方が、物理ブロックアドレス「1FFFh」に比べて、劣化度合いが小さいが、物理ブロックアドレス「0000h」は、無効ブロックテーブル110に登録されていないので、物理ブロックアドレス「0000h」の物理ブロックは、選択対象とはならない。

# [0078]

次に、処理602を説明する。制御部108は、劣化度テーブル113の更新を行う。 具体的には、制御部108は、領域指定テーブル112を参照して、ホスト機器200から指定された論理アドレスがどの先頭論理アドレスから最終論理アドレスまでの範囲に入るかを判断し、ホスト機器200から指定された論理アドレスが入る範囲に対応する書き込み種別を取得し、取得した書き込み種別に応じて、処理601で決定した書き込み先物理ブロックに対応する劣化度テーブル113の劣化度合いの値を更新する。

### [0079]

例えば、ホスト機器 2 0 0 が指定した論理アドレスが「 0 0 0 1 h 」であるとすると、制御部 1 0 8 は、論理アドレス「 0 0 0 1 h 」が含まれる領域の書き込み種別として、 2 値書き込みを得る。従って、制御部 1 0 8 は、劣化度テーブル 1 1 3 の物理ブロックアドレス「 1 F F F h 」に対応する劣化度合いの値に「 1 」を加算する。

# [0800]

図7は、更新後の劣化度テーブル113の状態の一例を示している。図7に示すように、劣化度テーブル113の物理ブロックアドレス「1FFFh」に対応する劣化度合いの値は、前回の値「0000010h」に「1」が加算され、「0000011h」となる。なお、書き込み種別に対応した劣化度合いの加算量(ストレス量)については、後で説明する。

### [0081]

50

10

20

30

次に、処理603を説明する。制御部108は、ホスト機器200からのデータの書き込みを行う。具体的には、制御部108は、ホスト機器200から指定された論理アドレスを基に領域指定テーブル112を参照して、対応する書き込み種別を取得し、取得した書き込み種別を用いて、ホスト機器200から転送される書き込みデータをフラッシュメモリ部103に転送し、処理601で決定した書き込み先物理ブロックアドレス、例えば、「1FFFh」に書き込む。

#### [0082]

このとき、ホスト機器 2 0 0 からの書き込みデータが物理ブロック単位に満たないときには、制御部 1 0 8 は、フラッシュメモリ部 1 0 3 に既書き込みのデータを使用して、物理ブロック単位のデータを作成し、このデータをフラッシュメモリ部 1 0 3 に書き込む。このような処理を行う必要があるのは、フラッシュメモリ部 1 0 3 のデータの消去単位でしか、データを書き換えることができないためである。従って、本実施の形態では、メモリセルに記録する情報量は、データの消去単位である物理ブロックの単位で同じビット数となる。

#### [0083]

次に、処理604を説明する。制御部108は、アドレス変換テーブル109及び無効ブロックテーブル110の更新を行う。具体的には、制御部108は、ホスト機器200から指定された論理アドレスである論理ブロックアドレスに対応するアドレス変換テーブル109の物理ブロックアドレスと、処理601において選択され、処理603においてホスト機器200からの書き込みデータを書き込んだ物理アドレスである無効ブロックテーブル110の物理ブロックアドレスとを入れ替えて、アドレス変換テーブル109及び無効ブロックテーブル110を更新する。

#### [0084]

図8は、更新後のアドレス変換テーブル109の状態の一例を示し、図9は、更新後の無効ブロックテーブル110の状態の一例を示している。図8及び図9に示すように、制御部108は、ホスト機器200が指定した論理ブロックアドレス「0001h」に対応する物理ブロックアドレス「0010h」と、処理601で選択した物理ブロックアドレス「1FFFh」とを交換し、アドレス変換テーブル109の論理ブロックアドレスは、「1FFFh」となり、無効ブロックテーブル110では、「1FFFh」が削除され、新たに「0010h」が追加される。

# [0085]

図10は、図6に示すフローチャートの各処理において、どのテーブルが参照及び更新されるか示している。なお、図10では、テーブルの参照を「R」で示し、テーブルの更新を「W」で示している。

# [0086]

図10に示すように、処理601では、無効ブロックテーブル110及び劣化度テーブル113が参照され、処理602では、領域指定テーブル112が参照され、劣化度テーブル113が更新され、処理603では、領域指定テーブル112が参照され、必要に応じてアドレス変換テーブル109が参照され、処理604では、アドレス変換テーブル109が参照され、アドレス変換テーブル100が更新される。

### [0087]

### < 4. 劣化度合いの算定>

次に、劣化度テーブル113の劣化度合いの更新における、各書き込み種別における加算値について説明する。加算値を決定するためには、メモリーカード101に使用するフラッシュメモリ部103の特性を評価する必要がある。つまり、メモリーカード101に使用するフラッシュメモリ部103の特性によって、加算値は異なってくる。例えば、フラッシュメモリ部103を製造したプロセスルールやフラッシュメモリメーカーによって異なり、また、2値書き込みか、又は、多値書き込みか、さらに、多値書き込みが4値なのか、8値なのか、16値なのかによっ

10

20

30

40

ても異なる。

### [0088]

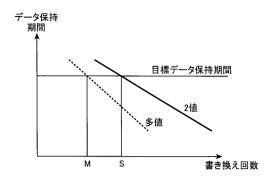

図11は、フラッシュメモリ部103の書き換え回数とデータ保持期間との関係を示す図である。図11では、横軸には書き換え回数を、縦軸にはデータ保持期間をとり、書き換え回数は、2値又は多値を問わず、共通の書き換え回数で示している。また、フラッシュメモリ部103の評価結果として、2値書き込みによる2値書き換えのみを実行した場合を破線で示している。

### [0089]

つまり、2値書き込みで10回、100回、100回、5000回書き換えた後のデータ保持期間をプロットすることにより、2値書き換えの線である実線が引け、また、多値書き込みで10回、100回、100回、5000回書き換えた後のデータ保持期間をプロットすることにより、多値書き換えの線である破線が引ける。また、書き込み種別である2値書き込みや多値書き込みによらず、共通の書き込み方式でデータを書き込んだ後に、フラッシュメモリ部103のフラッシュメモリを放置して、ビットエラーが所定のビット数に達するまでの期間をデータ保持期間とする。このデータ保持期間の評価は、高温環境で実施する加速評価を行うことが一般的である。

#### [0090]

図11に示すように、メモリーカード101の目標とする所定の目標データ保持期間を設定する。次に、2値書き換えの線と多値書き換えの線とが、それぞれ目標データ保持期間と交わる書き換え回数の比を求める。例えば、2値書き込みによる書き換え回数Sが、多値書き込みによる書き換え回数Mの約3倍であるとする。この場合の2値書き換え劣化量及び多値書き換え劣化量を、書き換え回数の逆数の簡単な整数比で設定し、2値書き換え劣化量と多値書き換え劣化量との比に基づいて加算値を決定する。つまり、2値書き換え劣化量:多値書き換え劣化量=1/3:1=1:3となり、2値書き込みを行う場合の加算量として「1」が得られ、多値書き込みを行う場合の加算量として「3」が得られる

### [0091]

なお、加算量は、上記の例に特に限定されず、種々の変更が可能であり、多値ごとに異なる値を用いてもよく、例えば、4値書き込みを行う場合の加算量や8値書き込みを行う場合の加算量をそれぞれ設定してもよい。この場合、2値書き込みを行う場合の加算量は、4値書き込みを行う場合の加算量より小さく、4値書き込みを行う場合の加算量は、8値書き込みを行う場合の加算量より小さく設定することが好ましい。

# [0092]

以上のような構成のメモリーカード101では、2値書き込みにおける劣化と、多値書き込みにおける劣化とを共通の尺度で管理する仕組みを導入している。それによって、2値書き込みと多値書き込みとが可能なメモリーカード101において、それぞれの書き込みに対する領域を個別に設定する必要がなく、メモリーカード101の劣化の均等化を図り、メモリーカード101の劣化を抑えることができるとともに、メモリーカード101の全ての物理ブロックを有効に利用することができる。結果として、2値書き込みと多値書き込みとが可能なメモリーカード101において、任意に2値書き込み領域と多値書き込み領域とを設けた上で、それぞれの領域に対して物理的な領域制限を必要とせず、全ての物理ブロックを双方の書き込みに対して有効に使用することが可能になる。

# 【産業上の利用可能性】

# [0093]

本発明は、書き込み種別によって異なる書き込み方法でデータを記憶する不揮発性記憶装置において、全ての物理ブロックの劣化を均等化することができ、結果として、データの信頼性を実効的に向上することが可能なユーザ利便性の高い不揮発性記憶装置を提供することができるので、不揮発性メモリを用いた不揮発性記憶装置、及び不揮発性メモリを制御する不揮発性メモリコントローラに有用である。

10

20

30

# 【符号の説明】

# [0094]

- 101 メモリーカード

- 102 コントローラ

- 103 フラッシュメモリ部

- 104 ホストインターフェース部

- 105 フラッシュメモリ制御部

- 106 バッファメモリ

- 107 ECC

- 108 制御部

- 109 アドレス変換テーブル

- 110 無効ブロックテーブル

- 111 不良ブロックテーブル

- 1 1 2 領域指定テーブル

- 1 1 3 劣化度テーブル

# 【図1】

# 【図2】

【図3】

| 物理ブロックアドレス |

|------------|

| 0123h      |

| 0456h      |

| •          |

| :          |

| 1FFFh      |

| 2000h      |

| :          |

| :          |

# 【図4】

# 【図5】

# 【図6】

# 【図7】

| 物理ブロックアドレス | 劣化度合い      |

|------------|------------|

| 0000h      | 0000 0001h |

| 0001h      | 0000 0100h |

| •          |            |

| 1FFFh      | 0000 0011h |

# 【図8】

| 論理ブロックアドレス | 物理ブロックアドレス |

|------------|------------|

| 0000h      | 0000h      |

| 0001h      | 1FFFh      |

| :          | :          |

| 1F39h      | 1000h      |

# 【図9】

| 物理ブロックアドレス |

|------------|

| 0010h      |

| 0123h      |

| 0456h      |

| :          |

| 2000h      |

| :          |

# 【図10】

|     |                              | 領域指定テーブル | 劣化度<br>テーブル | アドレス変換<br>テーブル | 無効ブロック<br>テーブル |

|-----|------------------------------|----------|-------------|----------------|----------------|

| 601 | 書き込み先物理ブロックの決定               | l        | œ           | l              | R              |

| 602 | 劣化度テーブルの更新                   | œ        | *           | I              | I              |

| 603 | ホスト機器からの<br>データの書き込み         | œ        | I           | (R)            | I              |

| 304 | アドレス変換テーブル/<br>無効ブロックテーブルの更新 | I        | ı           | R/W            | W              |

|     |                              |          |             |                |                |

# 【図11】

# 【図12】

# 【図13】

【図14】

# フロントページの続き

# (56)参考文献 国際公開第2008/073421(WO,A1)

特開2009-048680(JP,A)

特表2010-512569(JP,A)

特表2010-518546(JP,A)

特表2009-510549(JP,A)

# (58)調査した分野(Int.CI., DB名)

G11C 16/02 - 16/06

G06F 12/16