### (19)中华人民共和国国家知识产权局

### (12)发明专利申请

(10)申请公布号 CN 109462394 A (43)申请公布日 2019.03.12

- (21)申请号 201810814451.7

- (22)申请日 2018.07.23

- (30)优先权数据

10-2017-0114032 2017.09.06 KR

- (71)申请人 三星电子株式会社 地址 韩国京畿道

- (72)发明人 黄铉澈 刘钟奎 金珉修

- (74) **专利代理机构** 北京市立方律师事务所 11330

代理人 李娜

(51) Int.CI.

*H03K* 19/01(2006.01) *H03K* 19/20(2006.01)

权利要求书3页 说明书14页 附图46页

#### (54)发明名称

时序电路

#### (57)摘要

本发明提供了一种时序电路,所述时序电路包括第一门电路、第二门电路和输出电路。所述第一电路基于输入信号、输入时钟信号和第二信号生成第一信号。所述第二电路通过对所述第一信号和与所述输入时钟信号反相的反相时钟信号执行NOR运算来生成内部时钟信号,并且基于所述内部时钟信号和所述输入信号生成所述第二信号。所述输出电路基于所述第二信号生成输出信号。可以通过经由所述第一电路与所述第二电路之间的相互控制来增加负建立时间,从而提高所述时序电路和包括所述时序电路的集成电路的运行速度,所述负建立时间反映在所述输入时钟信号转变之后的所述输入信号的转变。

CN 109462394 A

1.一种时序电路,所述时序电路包括:

第一电路,所述第一电路被配置为基于输入信号、输入时钟信号和第二信号生成第一信号:

第二电路,所述第二电路被配置为通过对所述第一信号和与所述输入时钟信号反相的 反相时钟信号执行NOR运算来生成内部时钟信号,并且被配置为基于所述内部时钟信号和 所述输入信号生成所述第二信号;以及

输出电路,所述输出电路被配置为基于所述第二信号生成输出信号。

- 2.根据权利要求1所述的时序电路,其中,响应于所述输入信号在自所述输入时钟信号 从第一逻辑电平转变到第二逻辑电平的时间点起经过负建立时间之前转变,所述第一信号 和所述第二信号中的一个信号转变。

- 3.根据权利要求2所述的时序电路,其中,当所述输入时钟信号具有所述第一逻辑电平时,所述第一信号具有所述第一逻辑电平,并且所述第二信号具有所述第二逻辑电平,并且

其中,在所述输入时钟信号从所述第一逻辑电平转变到所述第二逻辑电平的时间点, 所述第一信号和所述第二信号中的一个信号根据所述输入信号的逻辑电平而转变。

- 4.根据权利要求2所述的时序电路,其中,响应于所述输入信号在自所述输入时钟信号 从所述第一逻辑电平转变到所述第二逻辑电平的时间点起经过所述负建立时间之后转变, 所述第一信号和所述第二信号均不转变。

- 5.根据权利要求2所述的时序电路,其中,当所述输入信号从所述第一逻辑电平转变到 所述第二逻辑电平时,所述负建立时间对应于从所述输入时钟信号的转变时间点到所述第 一信号的转变时间点的第一延迟时间,以及

其中,当所述输入信号从所述第二逻辑电平转变到所述第一逻辑电平时,所述负建立时间对应于从所述输入时钟信号的转变时间点到所述第二信号的转变时间点的第二延迟时间。

6.根据权利要求1所述的时序电路,其中,所述第二电路包括:

第一门电路,所述第一门电路被配置为通过对所述第一信号和所述反相时钟信号执行 NOR运算来生成所述内部时钟信号;

第二门电路,所述第二门电路被配置为通过对所述内部时钟信号以及所述输入信号和第二反相信号的OR运算结果执行NAND运算来生成所述第二信号;以及

反相器,所述反相器被配置为通过使所述第二信号反相来生成所述第二反相信号。

7.根据权利要求1所述的时序电路,其中,所述第一电路包括:

第一门电路,所述第一门电路被配置为通过对所述输入信号和与所述第二信号反相的 第二反相信号执行NOR运算来生成内部信号;

第二门电路,所述第二门电路被配置为通过对所述输入时钟信号以及所述内部信号和 所述第一信号的OR运算结果执行NAND运算来生成第一反相信号;以及

反相器,所述反相器被配置为通过使所述第一反相信号反相来生成所述第一信号。

8.根据权利要求1所述的时序电路,其中,所述第一电路包括:

第一门电路,所述第一门电路被配置为通过对第一反相信号以及所述输入信号和与所述第二信号反相的第二反相信号的OR运算结果执行第一NAND运算来生成内部信号:

第二门电路,所述第二门电路被配置为通过对所述内部信号和所述输入时钟信号执行

第二NAND运算来生成所述第一反相信号:以及

反相器,所述反相器被配置为通过使所述第一反相信号反相来生成所述第一信号。

9.根据权利要求1所述的时序电路,其中,所述第一电路包括:

门电路,所述门电路被配置为通过对所述输入信号、与所述第二信号反相的第二反相信号、第一反相信号和所述输入时钟信号执行逻辑运算来生成所述第一信号;以及

反相器,所述反相器被配置为通过使所述第一信号反相来生成所述第一反相信号。

10.根据权利要求1所述的时序电路,其中,所述时序电路是被配置为执行以下操作的触发器:接收输入数据信号作为所述输入信号并且生成与所述输入数据信号相对应的输出数据信号作为所述输出信号,以及

其中,所述输出电路包括:

锁存电路,所述锁存电路被配置为锁存所述第二信号;以及

缓冲器,所述缓冲器被配置为通过缓冲所述锁存电路的输出来生成所述输出数据信号。

11.根据权利要求1所述的时序电路,其中,所述时序电路是被配置为执行以下操作的时钟门控电路:接收时钟使能信号作为所述输入信号并且生成响应于所述时钟使能信号的激活而跳转的输出时钟信号作为所述输出信号,以及

其中,所述输出电路包括被配置为通过缓冲所述第二信号来生成所述输出时钟信号的 缓冲器。

- 12.根据权利要求1所述的时序电路,进一步包括多路复用器,所述多路复用器被配置 为响应于扫描使能信号而选择输入数据信号和扫描输入信号中的一个信号,以将所选择的 信号输出为所述输入信号。

- 13.根据权利要求1所述的时序电路,其中,所述第二电路包括:

第一门电路,所述第一门电路被配置为通过对所述第一信号和所述反相时钟信号执行 NOR运算来生成所述内部时钟信号:以及

第二门电路,所述第二门电路被配置为通过对所述内部时钟信号和以下信号的OR运算结果执行NAND运算来生成所述第二信号:所述输入信号、与所述第二信号反相的第二反相信号和扫描使能信号。

14.根据权利要求1所述的时序电路,其中,所述第一电路包括:

第一门电路,所述第一门电路被配置为通过对所述输入信号、扫描使能信号和与所述 第二信号反相的第二反相信号执行NOR运算来生成内部信号;

第二门电路,所述第二门电路被配置为通过对所述第一信号、所述内部信号、所述输入时钟信号、所述第二反相信号、所述扫描使能信号和扫描输入信号执行逻辑运算来生成第一反相信号:以及

输出电路,所述输出电路被配置为通过使所述第一反相信号反相来生成所述第一信号。

15.根据权利要求1所述的时序电路,其中,所述第一电路包括:

第一门电路,所述第一门电路被配置为通过对第一反相信号和以下信号的OR运算结果 执行NAND运算来生成内部信号:扫描使能信号、所述输入信号和与所述第二信号反相的第 二反相信号; 第二门电路,所述第二门电路被配置为通过对所述内部信号、所述输入时钟信号、所述 第二反相信号、所述扫描使能信号和扫描输入信号执行逻辑运算来生成所述第一反相信 号;以及

反相器,所述反相器被配置为通过使所述第一反相信号反相来生成所述第一信号。

16.根据权利要求1所述的时序电路,其中,所述第一电路包括:

第一门电路,所述第一门电路被配置为通过对扫描输入信号和扫描使能信号执行NAND运算来生成内部使能信号;

第二门电路,所述第二门电路被配置为基于所述输入信号、所述扫描使能信号、从所述 第二信号反相的第二反相信号、第一反相信号、所述反相时钟信号和所述内部使能信号生 成所述第一信号:以及

反相器,所述反相器被配置为通过使所述第一信号反相来生成所述第一反相信号。

17.一种时序电路,所述时序电路包括:

第一电路,所述第一电路被配置为基于扫描输入信号、输入数据信号、扫描使能信号、 输入时钟信号和第二信号生成第一信号;

第二电路,所述第二电路被配置为通过对所述第一信号和与所述输入时钟信号反相的 反相时钟信号执行NOR运算来生成内部时钟信号,并且被配置为基于所述内部时钟信号、所 述输入数据信号和所述扫描使能信号生成所述第二信号;以及

输出电路,所述输出电路被配置为基于所述第二信号生成输出信号。

18.根据权利要求17所述的时序电路,其中,在所述扫描使能信号被激活时的扫描测试模式下,与所述扫描输入信号相对应的所述第二信号是通过经由所述第一电路和所述第二电路的扫描测试路径而生成的,以及

其中,在所述扫描使能信号被去激活时的正常模式下,与所述输入数据信号相对应的 所述第二信号是通过经由所述第二电路的正常路径而生成的。

- 19.根据权利要求18所述的时序电路,其中,所述扫描测试路径的延迟时间比所述正常路径的延迟时间长。

- 20.一种时序电路,所述时序电路包括:

第一电路,所述第一电路被配置为基于时钟使能信号、输入时钟信号和第二信号生成第一信号;

第二电路,所述第二电路被配置为通过对所述第一信号和与所述输入时钟信号反相的 反相时钟信号执行NOR运算来生成内部时钟信号,并且被配置为基于所述内部时钟信号和 所述时钟使能信号生成所述第二信号:以及

缓冲器,所述缓冲器被配置为通过缓冲所述第二信号来生成输出时钟信号。

### 时序电路

[0001] 相关申请的交叉引用

[0002] 本申请要求于2017年9月6日在韩国知识产权局提交的韩国专利申请No.10-2017-0114032的优先权,其公开内容通过引用整体地并入在本文中。

#### 技术领域

[0003] 与本发明构思的示例实施例一致的装置总体上涉及半导体集成电路,并且更具体地,涉及一种具有增加的负建立时间的时序电路。

#### 背景技术

[0004] 时序电路包括在半导体集成电路中广泛地使用的触发器、集成时钟门控电路等。因为时序电路的运行速度直接地影响半导体集成电路的运行速度,所以需要开发高速时序电路。

#### 发明内容

[0005] 一些示例实施例可以提供一种具有高运行速度的时序电路。

[0006] 一些示例实施例可以提供一种除了具有高运行速度之外还具有高效扫描测试功能的时序电路。

[0007] 根据示例实施例,提供了一种时序电路,所述时序电路可以包括第一门电路、第二门电路和输出电路。所述第一电路基于输入信号、输入时钟信号和第二信号生成第一信号。所述第二电路通过对所述第一信号和与所述输入时钟信号反相的反相时钟信号执行NOR运算来生成内部时钟信号,并且基于所述内部时钟信号和所述输入信号生成所述第二信号。所述输出电路基于所述第二信号生成输出信号。

[0008] 根据示例实施例,提供了一种时序电路,所述时序电路可以包括第一门电路、第二门电路和输出电路。所述第一电路基于扫描输入信号、输入数据信号、扫描使能信号、输入时钟信号和第二信号生成第一信号。所述第二电路通过对所述第一信号和与所述输入时钟信号反相的反相时钟信号执行NOR运算来生成内部时钟信号,并且基于所述内部时钟信号、所述输入数据信号和所述扫描使能信号生成所述第二信号。所述输出电路基于所述第二信号生成输出信号。

[0009] 根据示例实施例,提供了一种时序电路,所述时序电路可以包括第一门电路、第二门电路和输出电路。所述第一电路基于时钟使能信号、输入时钟信号和第二信号生成第一信号。所述第二电路通过对所述第一信号和与所述输入时钟信号反相的反相时钟信号执行NOR运算来生成内部时钟信号,并且基于所述内部时钟信号和所述时钟使能信号生成所述第二信号。缓冲器通过缓冲所述第二信号来生成输出时钟信号。

[0010] 根据示例实施例的时序电路可以通过所述第一电路与所述第二电路之间的相互控制而具有增加的负建立时间,负建立时间反映在所述输入时钟信号的转变之后的所述输入信号的转变,并且因此,可以提高所述时序电路和包括所述时序电路的集成电路的运行

速度。

[0011] 根据示例实施例的时序电路可以在所述第二电路中的数据传送路径上仅包括单级门电路以减小数据输出延迟,并且因此,可以提高所述时序电路和所述集成电路的运行速度。

[0012] 根据示例实施例的时序电路可以将扫描测试路径的延迟时间设定为比正常路径的延迟时间长,并且因此,可以高效地支持扫描测试。

#### 附图说明

[0013] 从结合附图的以下详细描述中,将更清楚地理解本发明构思的示例实施例。

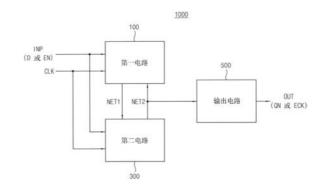

[0014] 图1是例示了根据示例实施例的时序电路的框图。

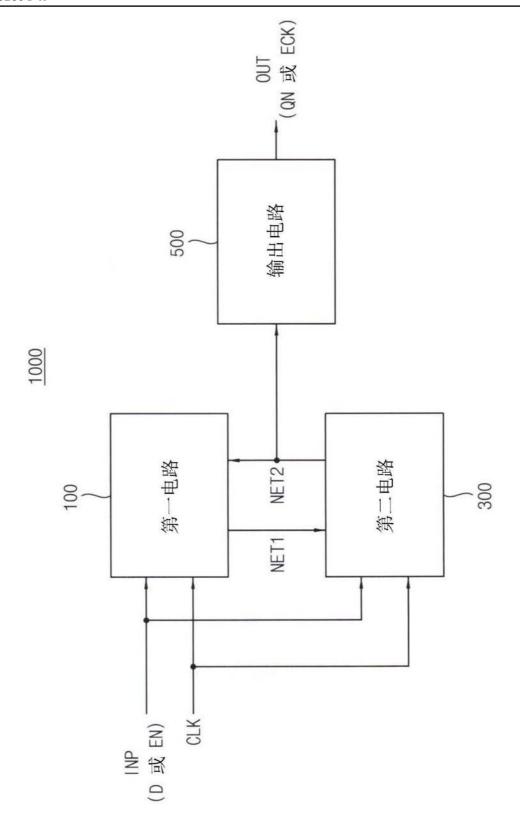

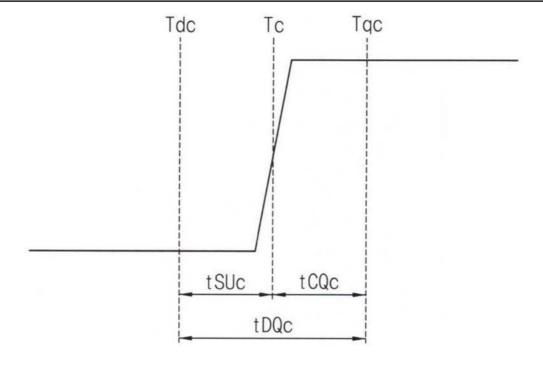

[0015] 图2A和图2B是用于描述根据示例实施例的时序电路的负建立时间的图。

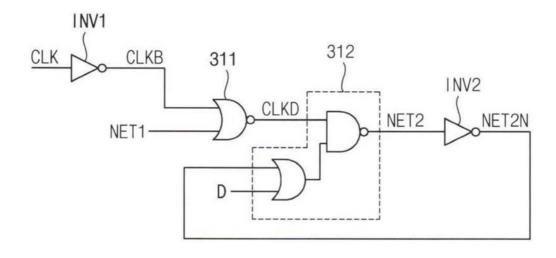

[0016] 图3A是例示了图1的时序电路中所包括的第二电路的示例实施例的框图,并且图3B是例示了图3A的第二电路的示例实施例的电路图。

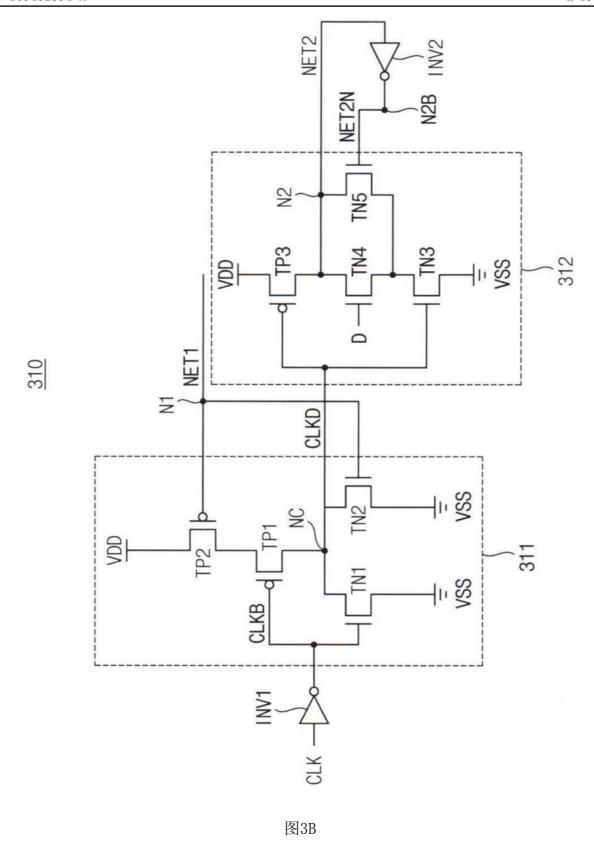

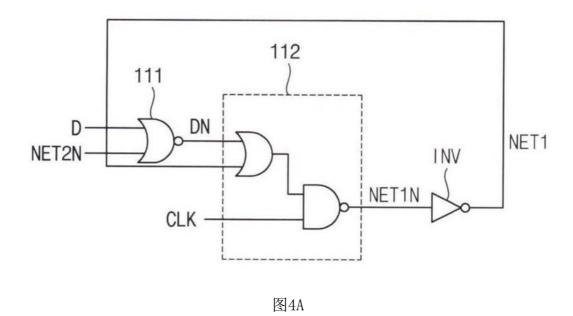

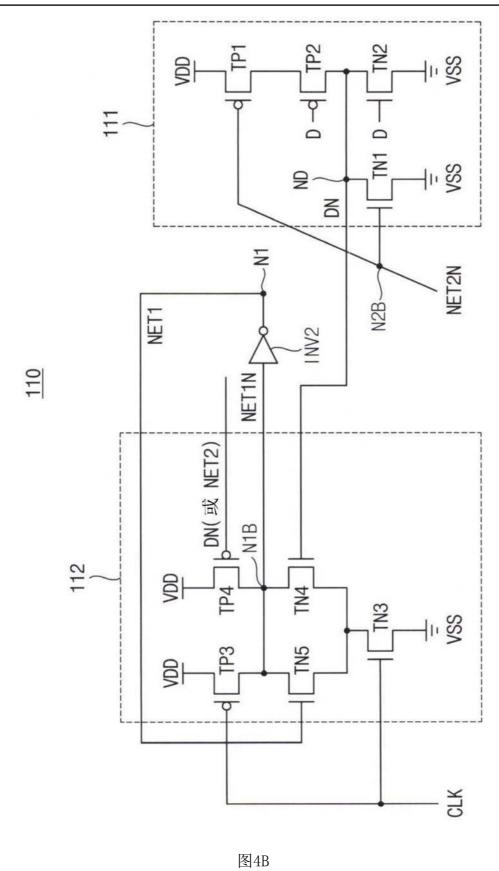

[0017] 图4A是例示了图1的时序电路中所包括的第一电路的示例实施例的框图,并且图4B是例示了图4A的第一电路的示例实施例的电路图。

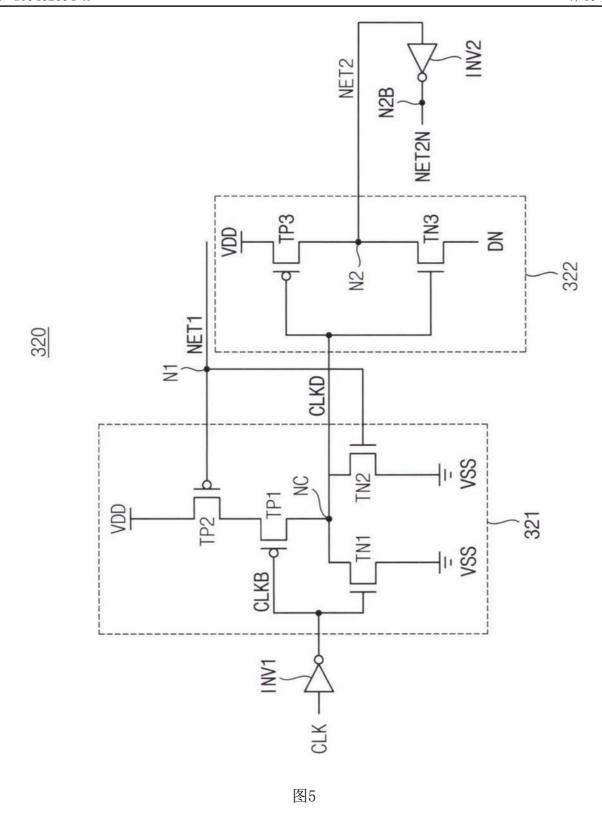

[0018] 图5是例示了图1的时序电路中所包括的第二电路的示例实施例的电路图。

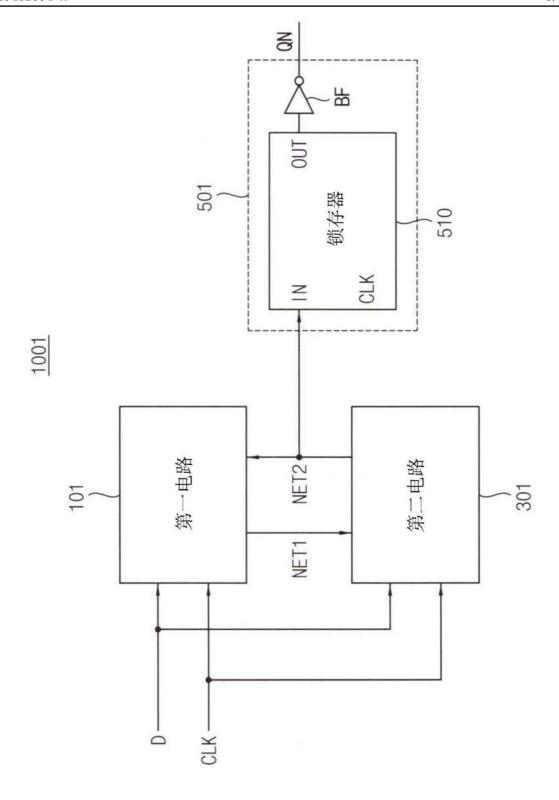

[0019] 图6是例示了根据示例实施例的时序电路的框图。

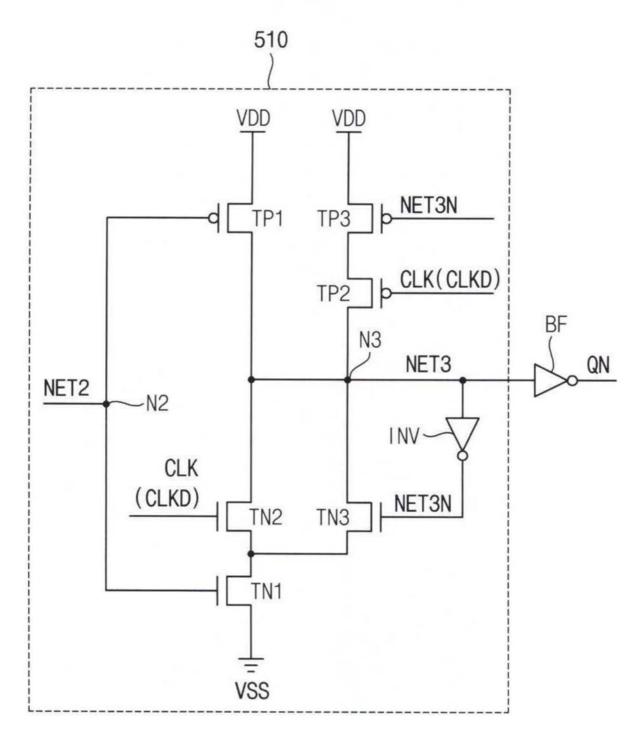

[0020] 图7是例示了图6的时序电路中所包括的输出电路的示例实施例的电路图。

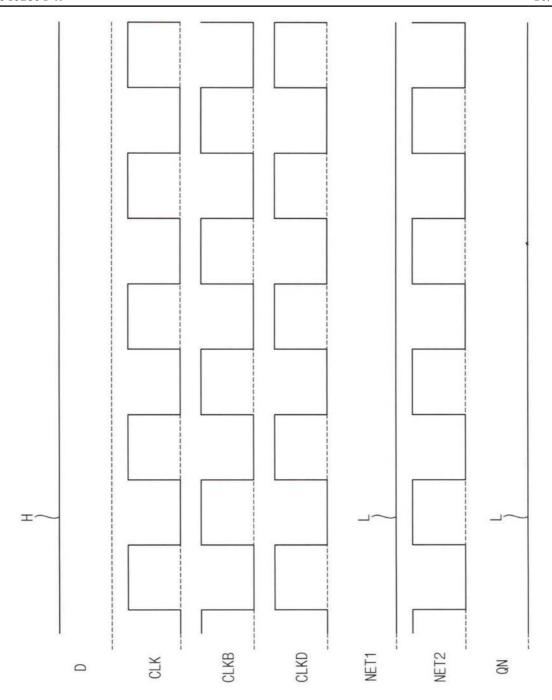

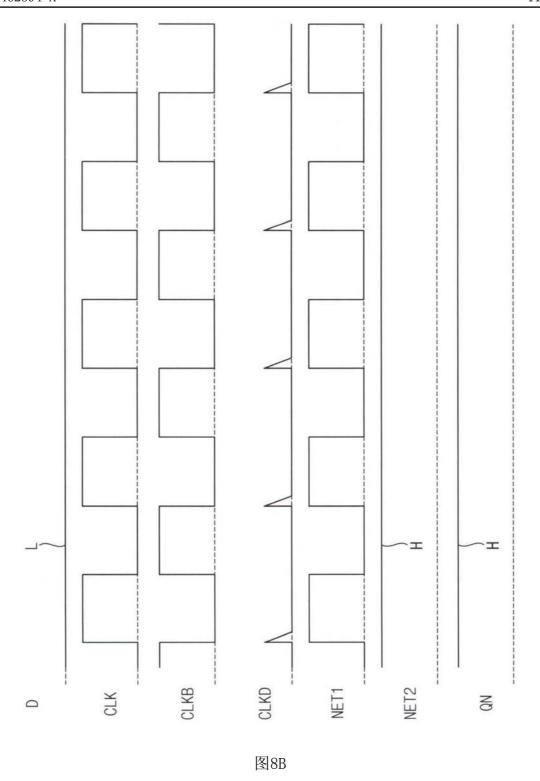

[0021] 图8A和图8B是例示了根据示例实施例的时序电路的操作的时序图。

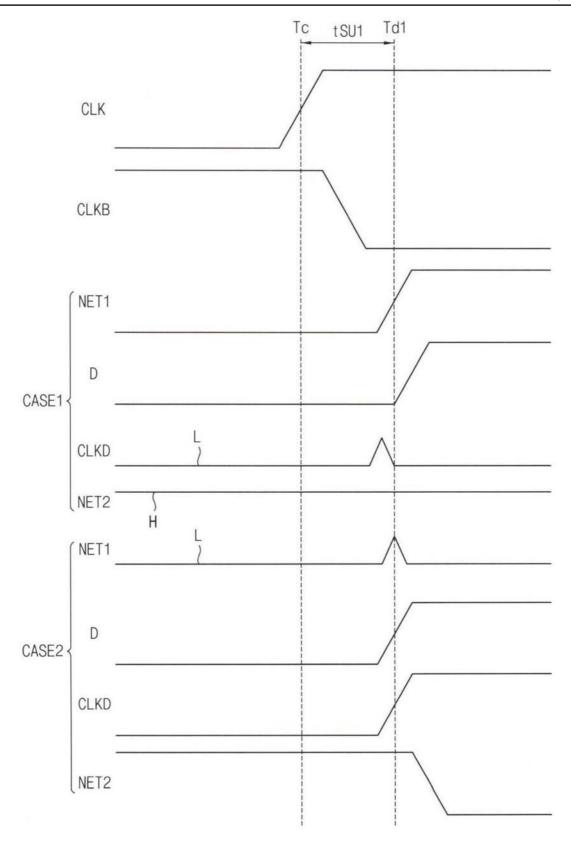

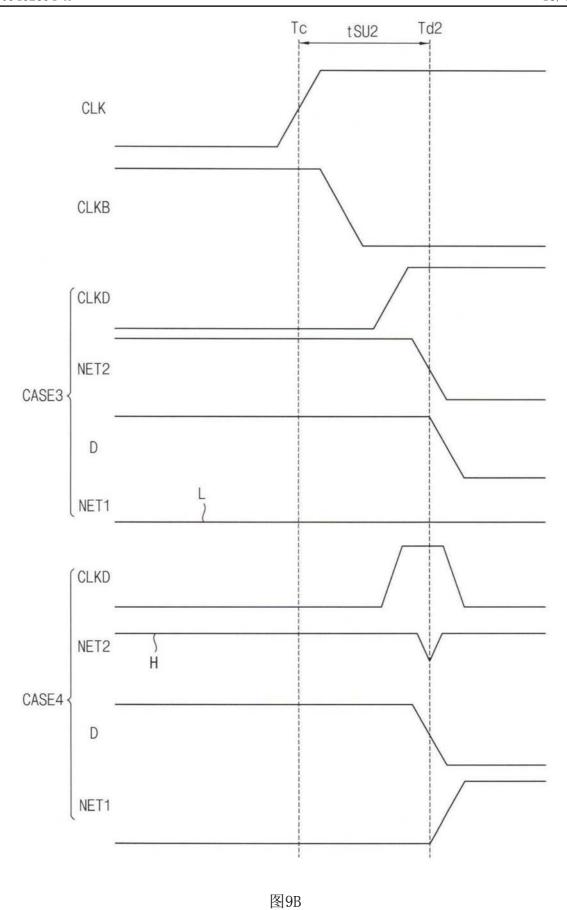

[0022] 图9A和图9B是例示了根据示例实施例的时序电路的负建立时间的时序图。

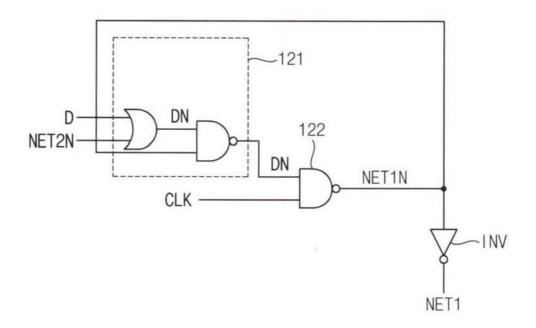

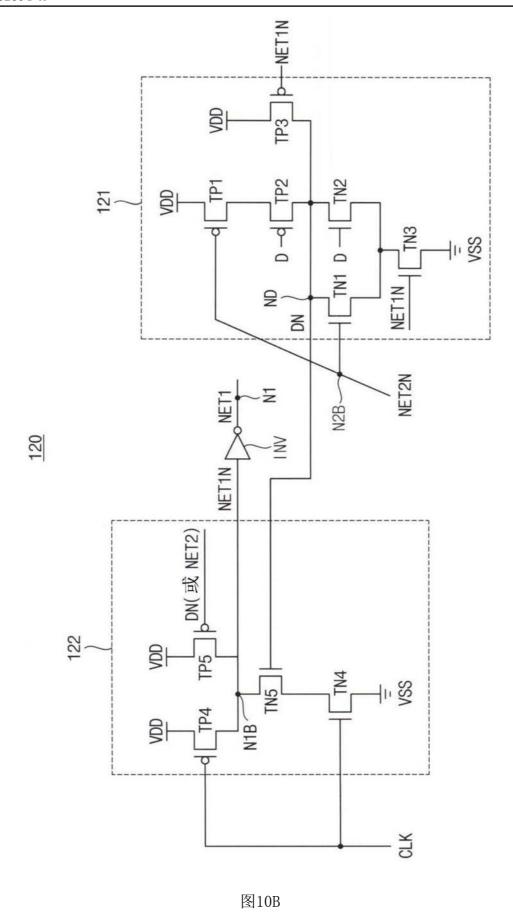

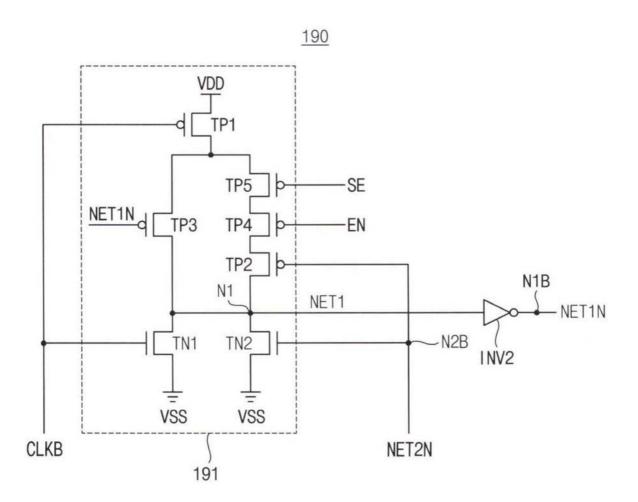

[0023] 图10A是例示了图1的时序电路中所包括的第一电路的示例实施例的框图,并且图 10B是例示了图10A的第一电路的示例实施例的电路图。

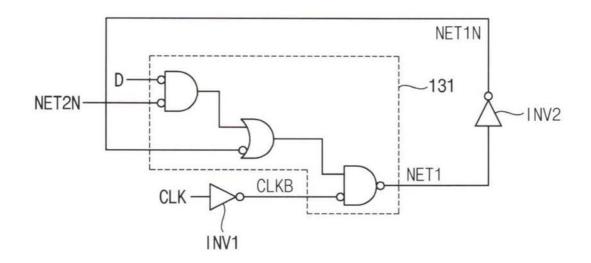

[0024] 图11A是例示了图1的时序电路中所包括的第一电路的示例实施例的框图,并且图 11B是例示了图11A的第一电路的示例实施例的电路图。

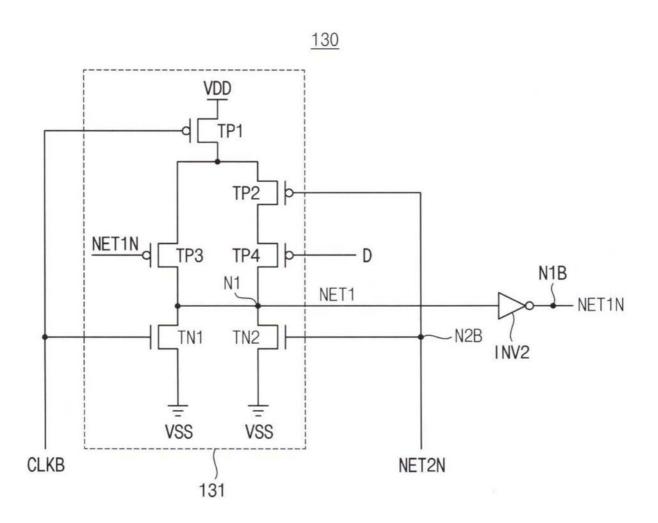

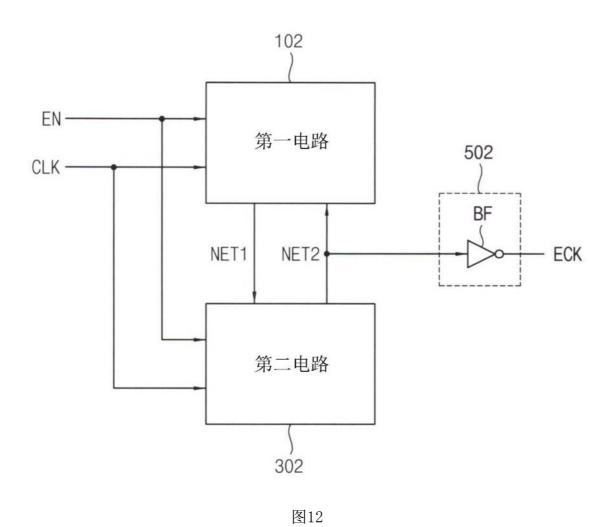

[0025] 图12是例示了根据示例实施例的时序电路的框图。

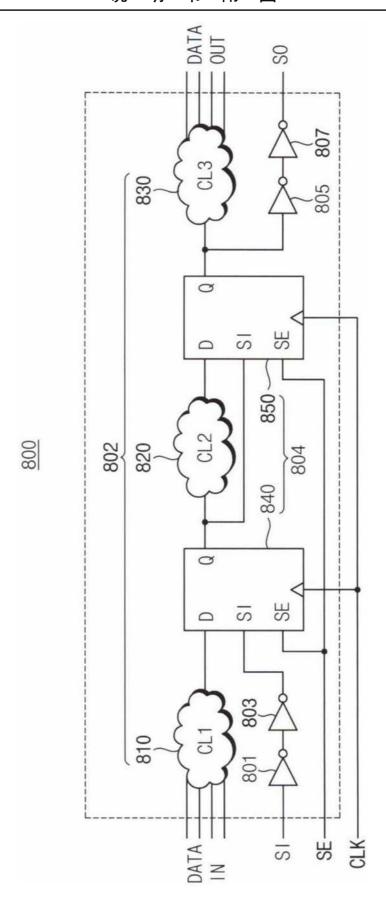

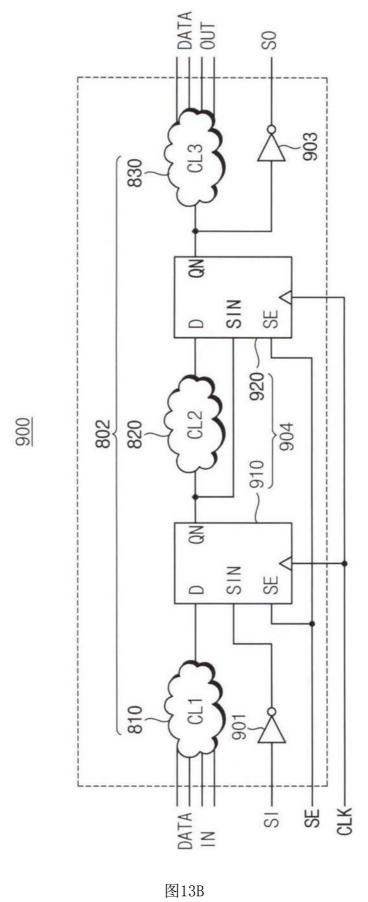

[0026] 图13A和图13B是例示了根据示例实施例的包括时序电路的扫描测试电路的图。

[0027] 图14和图15是例示了根据示例实施例的具有扫描测试功能的时序电路的框图。

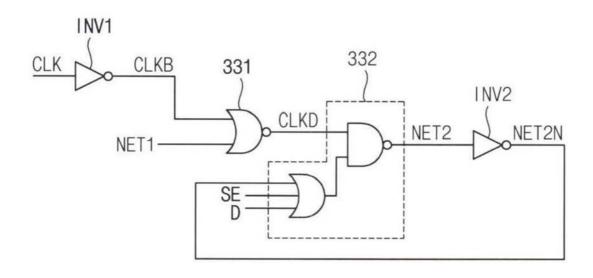

[0028] 图16A是例示了图15的时序电路中所包括的第二电路的示例实施例的框图,并且图16B是例示了图16A的第二电路的示例实施例的电路图。

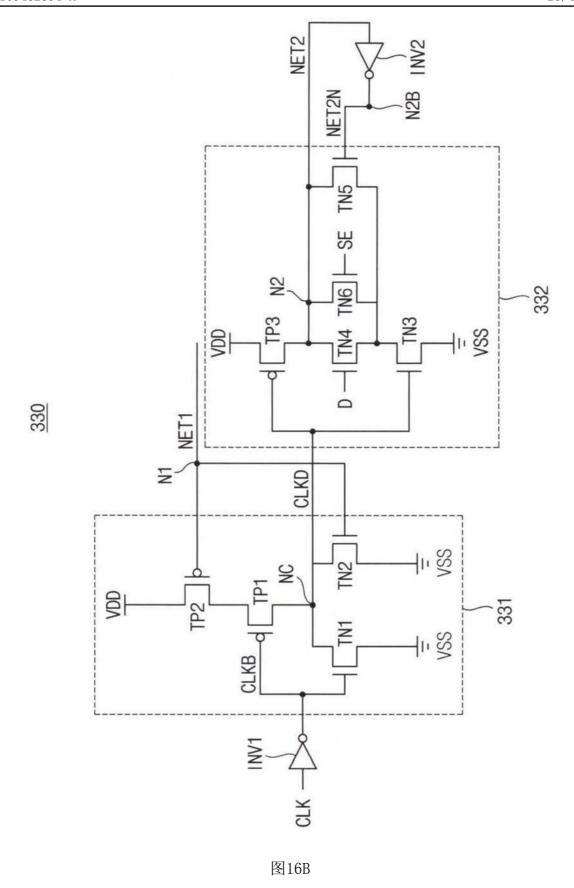

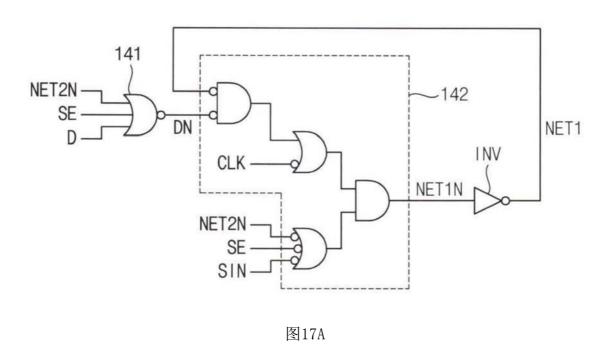

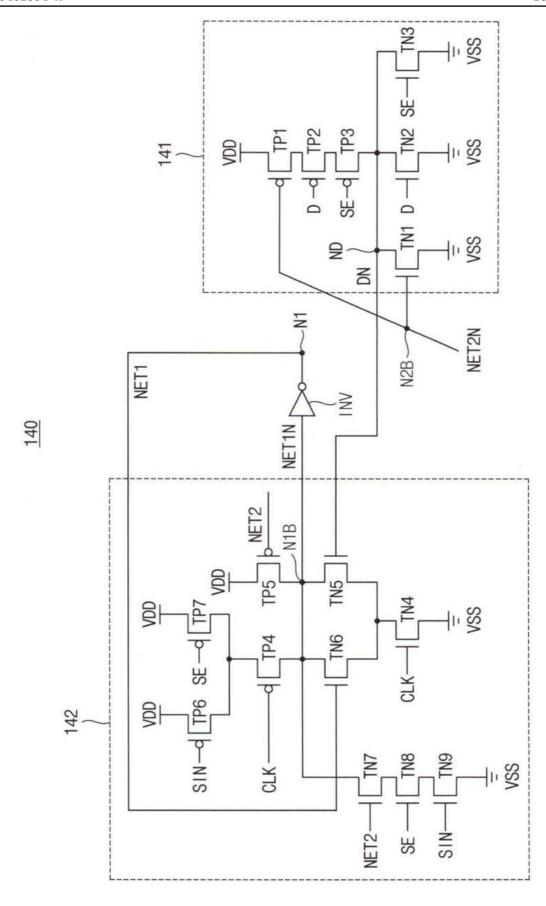

[0029] 图17A是例示了图15的时序电路中所包括的第一电路的示例实施例的框图,并且图17B是例示了图17A的第一电路的示例实施例的电路图。

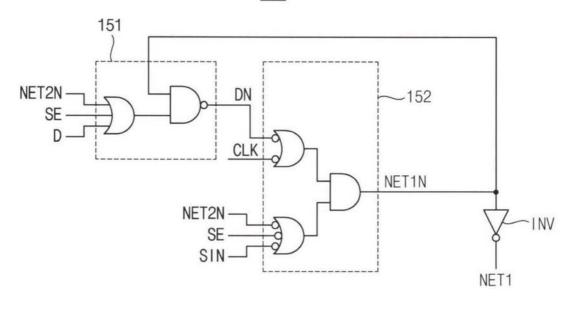

[0030] 图18A是例示了图15的时序电路中所包括的第一电路的示例实施例的框图,并且图18B是例示了图18A的第一电路的示例实施例的电路图。

[0031] 图19A是例示了图15的时序电路中所包括的第一电路的示例实施例的框图,并且图19B是例示了图19A的第一电路的示例实施例的电路图。

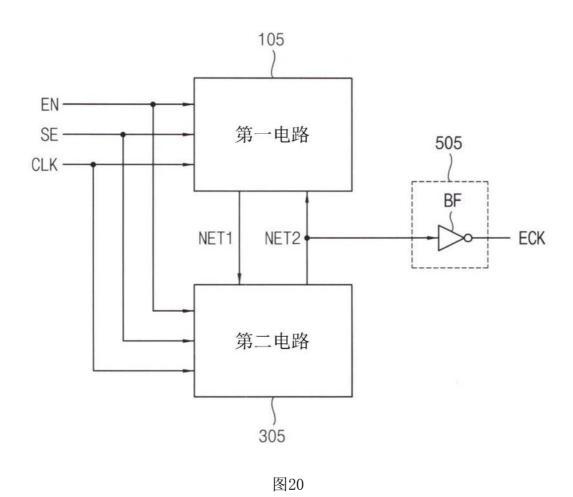

[0032] 图20是例示了根据示例实施例的时序电路的框图。

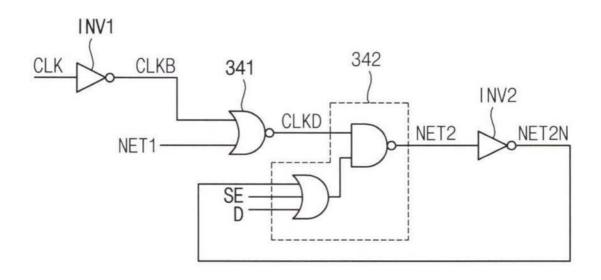

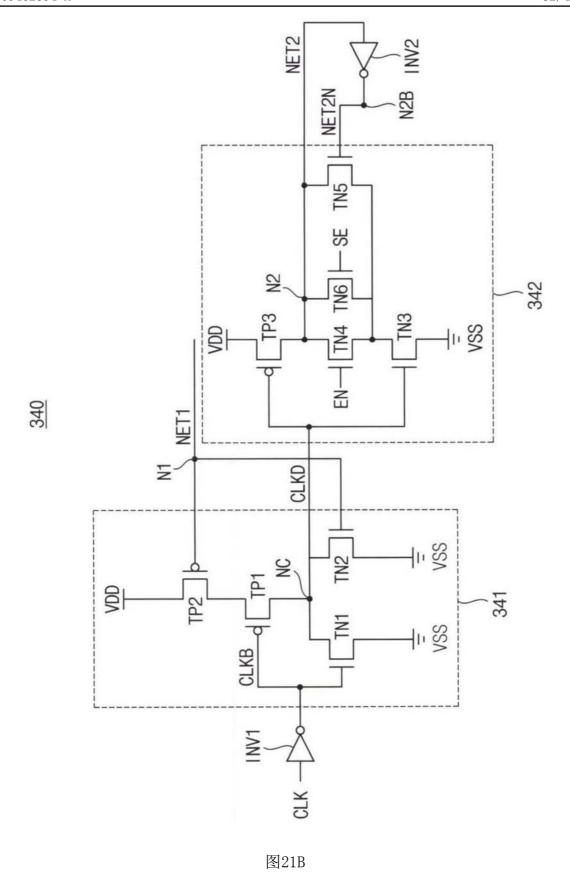

[0033] 图21A是例示了图20的时序电路中所包括的第二电路的示例实施例的框图,并且图21B是例示了图21A的第二电路的示例实施例的电路图。

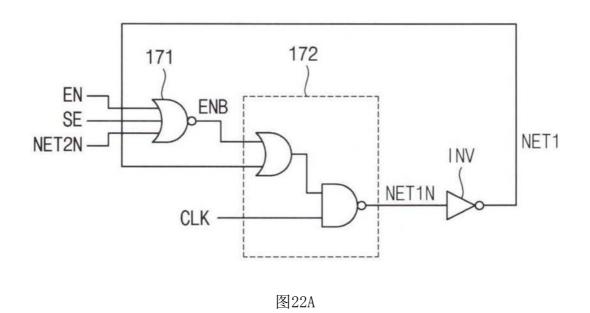

[0034] 图22A是例示了图20的时序电路中所包括的第一电路的示例实施例的框图,并且

图22B是例示了图22A的第一电路的示例实施例的电路图。

[0035] 图23A是例示了图20的时序电路中所包括的第一电路的示例实施例的框图,并且图23B是例示了图23A的第一电路的示例实施例的电路图。

[0036] 图24A是例示了图20的时序电路中所包括的第一电路的示例实施例的框图,并且图24B是例示了图24A的第一电路的示例实施例的电路图。

[0037] 图25是例示了根据示例实施例的时序电路的框图。

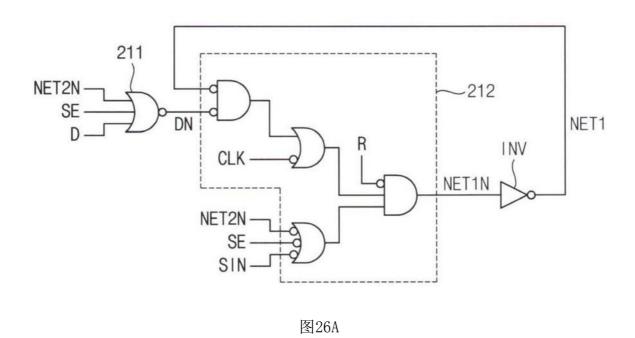

[0038] 图26A是例示了图25的时序电路中所包括的第一电路的示例实施例的框图,并且图26B是例示了图26A的第一电路的示例实施例的电路图。

[0039] 图27A是例示了图25的时序电路中所包括的第一电路的示例实施例的框图,并且图27B是例示了图27A的第一电路的示例实施例的电路图。

[0040] 图28A是例示了图25的时序电路中所包括的第一电路的示例实施例的框图,并且图28B是例示了图28A的第一电路的示例实施例的电路图。

[0041] 图29是例示了图25的时序电路中所包括的输出电路的示例实施例的电路图。

[0042] 图30是例示了根据示例实施例的系统的框图。

#### 具体实施方式

[0043] 将在下文中参考附图更全面地描述本发明构思的各个方面,在附图中示出了一些示例实施例。在附图中,相同的标号始终指代相同的元件。可以省略重复的描述。

[0044] 图1是例示了根据示例实施例的时序电路的框图。

[0045] 参考图1,时序电路1000包括第一电路100、第二电路300和输出电路500。

[0046] 第一电路100基于输入信号INP、输入时钟信号CLK和第二信号NET2生成第一信号NET1。如将参考图3A所描述的,第二电路300通过对第一信号NET1和与输入时钟信号CLK反相的反相时钟信号CLKB执行NOR(或非)运算来生成内部时钟信号CLKD,并且基于内部时钟信号CLKD和输入信号INP生成第二信号NET2。输出电路500基于第二信号NET2生成输出信号OUT。

[0047] 第一电路100和第二电路300可以以与置位复位 (SR) 锁存器类似的方式通过第一信号NET1和第二信号NET2进行相互控制。第二信号NET2可以被传送到输出电路500,并且时序电路1000可以根据输出电路500的配置而用作触发器或时钟门控电路。

[0048] 在一些示例实施例中,时序电路1000可以是执行以下操作的触发器:接收输入数据信号D作为输入信号INP并且生成与输入数据信号D相对应的输出数据信号QN作为输出信号0UT。当由此触发器来实现时序电路1000时,输出电路500可以包括如将参考图6和图7所描述的锁存器和缓冲器。

[0049] 在其它示例实施例中,时序电路1000可以是执行以下操作的时钟门控电路:接收时钟使能信号EN作为输入信号INP并且生成输出时钟信号ECK作为输出信号OUT,所述输出时钟信号ECK响应于时钟使能信号EN的激活而跳转。当由此时钟门控电路来实现时序电路1000时,如将参考图12所描述的,输出电路500可以仅包括缓冲器而不包括锁存器。

[0050] 在根据示例实施例的时序电路1000中,如果输入信号INP在自输入时钟信号CLK从第一逻辑电平转变到第二逻辑电平的时间点起经过负建立时间之前转变,则第一信号NET1和第二信号NET2中的一个信号可以转变。

[0051] 在下文中,主要基于时序电路在输入时钟信号CLK的上升沿对输入信号INP进行采样的情况对示例实施例进行描述。在这种情况下,第一逻辑电平可以是逻辑低电平并且第二逻辑电平可以是逻辑高电平。然而,本发明构思也可以被应用于时序电路在输入时钟信号CLK的下降沿对输入信号INP进行采样的情况。在这种情况下,第一逻辑电平可以是逻辑高电平并且第二逻辑电平可以是逻辑低电平。本领域的技术人员将容易地理解的是,可以通过信号反相、在N型与P型之间交换晶体管类型等,来将所公开的上升沿采样的示例实施例修改为下降沿采样的示例实施例。

[0052] 图2A和图2B是用于描述根据示例实施例的时序电路的负建立时间的图。

[0053] 图2A例示了通用时序电路的建立时间tSUc、时钟到输出延迟时间tCQc和输入到输出延迟时间tDQc,并且图2B例示了根据示例实施例的时序电路的建立时间tSUp、时钟到输出延迟时间tCQp和输入到输出延迟时间tDQp。Tc指示输入时钟信号CLK的转变时间点,Tdc和Tdp指示输入信号INP的转变时间点,并且Tqc和Tqp指示输出信号OUT的转变时间点。

[0054] 触发器的速度通常由输入到输出延迟时间tDQc决定。输入到输出延迟时间tDQc被定义为建立时间tSUc和时钟到输出延迟时间tCQc的和。众所周知,建立时间tSUc是向触发器稳定地提供数据(即,输入信号的数据)所需的时间。换句话说,建立时间tSUc指示在时钟信号的采样沿之前必须提前完成输入信号的转变,并且等于从输入信号的转变到对时钟信号进行采样的时间间隔。时钟到输出延迟时间tCQc指示从对时钟信号进行采样到发出输出数据的延迟时间。输入到输出延迟时间tDQc的减小对于设计高速时序电路是必不可少的。

[0055] 如图2B中所例示的,根据示例实施例的时序电路具有负建立时间tSUp。负建立时间表示时序电路甚至可以反映采样时钟信号转变之后输入信号的转变。根据示例实施例的时序电路可以通过增加的负建立时间tSUp而具有减小的输入-输出延迟时间tDQp,并且因此,可以提高时序电路和包括时序电路的集成电路的运行速度。

[0056] 图3A是例示了图1的时序电路1000中所包括的第二电路300的示例实施例的框图,并且图3B是例示了图3A的第二电路的示例实施例的电路图。

[0057] 参考图3A,第二电路310可以包括第一门电路311、第二门电路312、第一反相器 INV1和第二反相器INV2。

[0058] 第一反相器INV1使输入时钟信号CLK反相以生成反相时钟信号CLKB。第二反相器INV2使第二信号NET2反相以生成第二反相信号NET2N。根据示例实施例,可以省略第一反相器INV1,可以从外部提供反相时钟信号CLKB。

[0059] 第一门电路311可以通过对第一信号NET1和反相时钟信号CLKB执行NOR运算来生成内部时钟信号CLKD。第一门电路311可以被实现为NOR门。

[0060] 第二门电路312可以通过对内部时钟信号CLKD以及与输入信号INP相对应的输入数据信号D和第二反相信号NET2N的OR运算结果执行NAND运算来生成第二信号NET2。第二门电路312可以被实现为0AI(或-与-反相器)门。0AI门是同时执行多个逻辑运算的复合逻辑门。在延迟时间方面,0AI门对应于单个门。

[0061] 因此,第二电路312中的数据传送路径仅包括单个门从而减小了数据输出延迟,并且因此,可以提高时序电路和包括时序电路的集成电路的运行速度。

[0062] 参考图3B,第二电路310的第一门电路311和第二门电路312可以用多个晶体管来实现。

[0063] 第一门电路311可以包括第一PMOS (p型金属氧化物半导体) 晶体管TP1、第二PMOS 晶体管TP2、第一NMOS (n型金属氧化物半导体) 晶体管TN1和第二NMOS晶体管TN2。

[0064] 第一PMOS晶体管TP1连接在电源电压VDD与生成内部时钟信号CLKD的内部时钟节点NC之间,并且接收与输入时钟信号CLK反相的反相时钟信号CLKB。在下文中,如果未提供不同的描述,则"晶体管接收信号"可以表示"晶体管的栅极接收信号"。第一NMOS晶体管TN1连接在地电压VSS与内部时钟节点NC之间,并且接收反相时钟信号CLKB。第二PMOS晶体管TP2与第一PMOS晶体管TP1串联连接在电源电压VDD与内部时钟节点NC之间,并且从第一节点N1接收第一信号NET1。第二NMOS晶体管TN2与第一NMOS晶体管TN1并联连接在地电压VSS与内部时钟节点NC之间。

[0065] 第二门电路312可以包括第三PMOS晶体管TP3、第三NMOS晶体管TN3、第四NMOS晶体管TN4和第五NMOS晶体管TN5。

[0066] 第三PMOS晶体管TP3连接在电源电压VDD与生成第二信号NET2的第二节点N2之间,并且接收内部时钟信号CLKD。第三NMOS晶体管TN3连接在地电压VSS与第二节点N2之间,并且接收内部时钟信号CLKD。第四NMOS晶体管TN4与第三NMOS晶体管TN3串联连接在地电压VSS与第二节点N2之间,并且接收输入数据信号D。第五NMOS晶体管TN5与第四NMOS晶体管TN4并联连接在地电压VSS与第二节点N2之间,并且接收第二反相信号NET2N。第二反相器INV2的输入节点对应于第二节点N2,并且第二反相器INV2的输出节点对应于第二反相节点N2B。

[0067] 图4A是例示了图1的时序电路1000中所包括的第一电路100的示例实施例的框图,并且图4B是例示了图4A的第一电路的示例实施例的电路图。

[0068] 参考图4A,第一电路110可以包括第一门电路111、第二门电路112和反相器INV。

[0069] 第一门电路111通过对与输入信号INP相对应的输入数据信号D和与第二信号NET2 反相的第二反相信号NET2N执行NOR运算来生成内部信号DN。第一门电路111可以被实现为NOR门。

[0070] 第二门电路112可以通过对输入时钟信号CLK以及内部信号DN和第一信号NET1的 OR运算结果执行NAND运算来生成第一反相信号NET1N。反相器INV通过使第一反相信号 NET1N反相来生成第一信号NET1。第二门电路112可以被实现为0AI门。

[0071] 参考图4B,第一电路110的第一门电路111和第二门电路112可以用多个晶体管来实现。

[0072] 第一门电路111可以包括第一PMOS晶体管TP1、第二PMOS晶体管TP2、第一NMOS晶体管TN1和第二NMOS晶体管TN2。

[0073] 第一PMOS晶体管TP1连接在电源电压VDD与生成内部信号DN的内部数据节点ND之间,并且从第二反相节点N2B接收第二反相信号NET2N。第一NMOS晶体管TN1连接在地电压 VSS与内部数据节点ND之间,并且接收第二反相信号NET2N。第二PMOS晶体管TP2与第一PMOS晶体管TP1串联连接在电源电压VDD与内部数据节点ND之间,并且接收输入数据信号D。第二 NMOS晶体管TN2与第一NMOS晶体管TN1并联连接在地电压VSS与内部数据节点ND之间。

[0074] 第二门电路112可以包括第三PMOS晶体管TP3、第四PMOS晶体管TP4、第三NMOS晶体管TN3、第四NMOS晶体管TN4和第五NMOS晶体管TN5。

[0075] 第三PMOS晶体管TP3连接在电源电压VDD与生成第一反相信号NET1N的第一反相节

点N1B之间,并且接收输入时钟信号CLK。第三NMOS晶体管TN3连接在地电压VSS与第一反相节点N1B之间,并且接收输入时钟信号CLK。第四PMOS晶体管TP4与第三PMOS晶体管TP3并联连接在电源电压VDD与第一反相节点N1B之间,并且接收内部信号DN或第二反相信号NET2。第四NMOS晶体管TN4与第三NMOS晶体管TN3串联连接在地电压VSS与第一反相节点N1B之间,并且接收内部信号DN。第五NMOS晶体管TN5与第四NMOS晶体管TN4并联连接在地电压VSS与第一反相节点N1B之间,并且接收有一信号NET1。

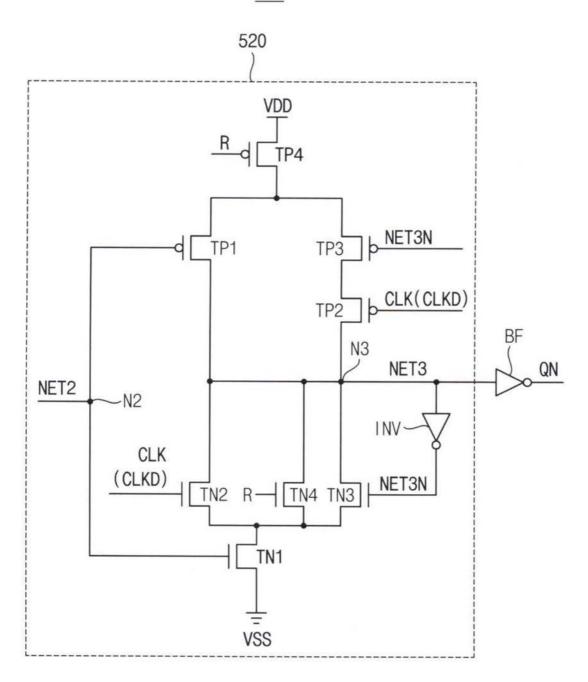

[0076] 图5是例示了图1的时序电路1000中所包括的第二电路300的示例实施例的电路图。

[0077] 参考图5,第二电路320的第一门电路321和第二门电路322可以用多个晶体管来实现。

[0078] 第一门电路321可以包括第一PMOS晶体管TP1、第二PMOS晶体管TP2、第一NMOS晶体管TN1和第二NMOS晶体管TN2。图5中的第一门电路321与图3A中的第一门电路311相同,并且省略重复的描述。

[0079] 第二门电路322可以包括第三PMOS晶体管TP3和第三NMOS晶体管TN3。第三PMOS晶体管TP3连接在电源电压VDD与生成第二信号NET2的第二节点N2之间,并且接收内部时钟信号CLKD。第三NMOS晶体管TN3连接在生成内部信号DN的内部数据节点ND与第二节点N2之间,并且接收内部时钟信号CLKD。

[0080] 在图5的第二门电路322中省略了图3A的第二门电路312中的晶体管TN4和TN5,并且由图4A和图4B的第一电路110生成的内部信号DN被施加到图5中的第三NMOS晶体管TN3的源极。因此,可以通过对数据路径的若干部分进行组合来减小时序电路的大小。

[0081] 图6是例示了根据示例实施例的时序电路的框图。

[0082] 参考图6,时序电路1001包括第一电路101、第二电路301和输出电路501。图6的时序电路1001对应于执行如下操作的触发器:接收输入数据信号D作为输入信号INP并且生成与输入数据信号D相对应的输出数据信号QN作为输出信号OUT。

[0083] 第一电路101基于输入数据信号D、输入时钟信号CLK和第二信号NET2生成第一信号NET1。第二电路301通过对第一信号NET1和与输入时钟信号CLK反相的反相时钟信号CLKB执行NOR运算来生成内部时钟信号CLKD,并且基于该内部时钟信号CLKD和输入数据信号D生成第二信号NET2。输出电路501基于第二信号NET2生成输出数据信号QN。输出电路501可以包括锁存电路510和缓冲器BF。锁存电路510锁存第二信号NET2,并且缓冲器BF通过缓冲锁存电路510的输出信号来生成输出数据信号QN。尽管图6示出了反相器作为缓冲器BF,但是缓冲器BF并不限于反相器而是可以具有各种配置。

[0084] 图7是例示了图6的时序电路1000中所包括的输出电路500的示例实施例的电路图。

[0085] 参考图7,输出电路501的锁存电路510可以用多个晶体管来实现。

[0086] 锁存电路510可以包括第一PMOS晶体管TP1、第二PMOS晶体管TP2、第三PMOS晶体管TP3、第一NMOS晶体管TN1、第二NMOS晶体管TN2、第三NMOS晶体管TN3和反相器INV。

[0087] 第一PMOS晶体管TP1连接在电源电压VDD与生成第三信号NET3的第三节点N3之间,并且接收第二信号NET2。第一NMOS晶体管TN1连接在地电压VSS与第三节点N3之间,并且接收第二信号NET2。第二PMOS晶体管TP2与第一PMOS晶体管TP1并联连接在电源电压VDD与第

三节点N3之间,并且接收输入时钟信号CLK或内部时钟信号CLKD。第二NMOS晶体管TN2与第一NMOS晶体管TN1串联连接在地电压VSS与第三节点N3之间,并且接收输入时钟信号CLK或内部时钟信号CLKD。第三PMOS晶体管TP3与第二PMOS晶体管TP2串联连接在电源电压VDD与第三节点N3之间,并且接收与第三信号NET3反相的第三反相信号NET3N。第三NMOS晶体管TN3与第二NMOS晶体管TN2并联连接在地电压VSS与第三节点N3之间,并且接收第三反相信号NET3N。反相器INV通过使第三信号NET3反相来生成第三反相信号NET3N。

[0088] 图8A和图8B是例示了根据示例实施例的时序电路的操作的时序图。

[0089] 图8A例示了输入数据信号D具有第二逻辑电平(例如,逻辑高电平H)的情况,并且图8B例示了输入数据信号D具有第一逻辑电平(例如,逻辑低电平L)的情况。关于每种情况,均示出了输入时钟信号CLK、反相时钟信号CLKB、内部时钟信号CLKD、第一信号NET1、第二信号NET2和输出信号OUT。在图8A和图8B中,忽略了信号之间的延迟。

[0090] 参考图8A和图8B,当输入时钟信号CLK具有第一逻辑电平L时,第一信号NET1具有第一逻辑电平L并且第二信号NET2具有第二逻辑电平H。换句话说,当输入时钟信号CLK具有第一逻辑电平L时,第一信号NET1可以被放电到第一逻辑电平L并且第二信号NET2可以被充电到第二逻辑电平H。

[0091] 在输入时钟信号CLK从第一逻辑电平L转变到第二逻辑电平H的时间点,第一信号NET1和第二信号NET2中的一个信号可以根据输入数据信号D的逻辑电平而转变。例如,如果输入数据信号D具有第二逻辑电平H,则第二信号NET2可以当输入时钟信号CLK在上升沿处时从第二逻辑电平H向下转变到第一逻辑电平L。相比之下,如果输入数据信号D具有第一逻辑电平L,则第一信号NET1可以当输入时钟信号CLK在上升沿处时从第一逻辑电平L向上转变到第二逻辑电平H。

[0092] 结果,如图8A中所例示的,当输入数据信号具有逻辑高电平H时,第一信号NET1可以维持放电后的逻辑低电平L并且第二信号NET2可以按与输入时钟信号CLK相反的相位跳转。相比之下,如图8B中所例示的,当输入数据信号具有逻辑低电平L时,第二信号NET2可以维持充电后的逻辑高电平H并且第一信号NET1可以按与输入时钟信号CLK相同的相位跳转。

[0093] 图9A和图9B是例示了根据示例实施例的时序电路的负建立时间的时序图。

[0094] 图9A例示了当输入数据信号D从第一逻辑电平或逻辑低电平L转变到第二逻辑电平或逻辑高电平H时的负建立时间tSU1,并且图9B例示了当输入数据信号D从逻辑高电平H转变到逻辑低电平L时的负建立时间tSU2。Tc指示输入时钟信号CLK的转变时间点,Td1指示第一信号NET1的转变时间点并且Td2指示第二信号NET2的转变时间点。

[0095] 当输入数据信号D从逻辑低电平L转变到逻辑高电平H时,负建立时间对应于从输入时钟信号CLK的转变时间点Tc到第一信号NET1的转变时间点Td1的第一延迟时间tSU1。相比之下,当输入数据信号D从逻辑高电平H转变到逻辑低电平L时,负建立时间对应于从输入时钟信号CLK的转变时间点Tc到第二信号NET2的转变时间点Td2的第二延迟时间tSU2。

[0096] 参考图9A,第一种情况CASE1是输入数据信号D在第一信号NET1的转变时间点Td1之后向上转变,而第二种情况CASE2是输入数据信号D在第一信号NET1的转变时间点Td1之前或在第一信号NET1的转变时间点Td1向上转变。参考图9B,第三种情况CASE3是输入数据信号D在第二信号NET2的转变时间点Td2之后向下转变,而第四种情况CASE4是输入数据信号D在第二信号NET2的转变时间点Td2之前或在第二信号NET2的转变时间点Td2向下转变。

[0097] 作为第二种情况CASE2和第四种情况CASE4,如果输入数据信号D在自输入时钟信号CLK从逻辑低电平L转变到逻辑高电平H的时间点Tc起经过负建立时间tSU1或tSU2之前转变,则第一信号NET1和第二信号NET2中的一个信号可以转变。

[0098] 相比之下,作为第一种情况CASE1和第三种情况CASE3,如果输入数据信号D在自时间点Tc(即,采样时间点)起经过负建立时间tSU1或tSU2之后转变,则第一信号NET1和第二信号NET2均不转变。

[0099] 在第一信号NET1被完全充电到逻辑高电平H或者第二信号NET2被完全放电到逻辑低电平L之后,时序电路的输出不受输入数据信号D的变化的影响。相比之下,如果输入数据信号D在第一信号NET1被完全充电到逻辑高电平H或者第二信号NET2被完全放电到逻辑低电平L之前发生改变,则时序电路的输出可能受到影响。

[0100] 因此,根据示例实施例的时序电路可以通过第一电路与第二电路之间的相互控制而具有增加的负建立时间,负建立时间反映在输入时钟信号转变之后的输入信号的转变,并且因此,可以提高时序电路和包括该时序电路的集成电路的运行速度。另外,根据示例实施例的时序电路在第二电路中的数据传输路径上可以仅包括单级门电路以减小数据输出延迟,并且因此,可以提高时序电路和集成电路的运行速度。

[0101] 图10A是例示了图1的时序电路1000中所包括的第一电路100的示例实施例的框图,并且图10B是例示了图10A的第一电路的示例实施例的电路图。

[0102] 参考图10A,第一电路120可以包括第一门电路121、第二门电路122和反相器INV。

[0103] 第一门电路121通过对与输入信号INP相对应的输入数据信号D和与第二信号NET2 反相的第二反相信号NET2N执行NOR运算来生成内部信号DN。第一门电路121可以被实现为0AI门。

[0104] 第二门电路122可以通过对输入时钟信号CLK和内部信号DN执行NAND运算来生成第一反相信号NET1N。反相器INV通过使第一反相信号NET1N反相来生成第一信号NET1。第二门电路122可以被实现为NAND门。

[0105] 参考图10B,第一电路120的第一门电路121和第二门电路122可以用多个晶体管 TP1至TP5和TN1至TN5来实现。图10B例示了与图10A的配置相对应的晶体管级配置的示例。图10B的第一电路120的操作与参考图8A、图8B及图9A和图9B所描述的基本上相同,并且省略重复的描述。

[0106] 图11A是例示了图1的时序电路1000中所包括的第一电路100的示例实施例的框图,并且图11B是例示了图11A的第一电路的示例实施例的电路图。

[0107] 参考图11A,第一电路130可以包括门电路131、第一反相器INV1和第二反相器INV2。

[0108] 门电路131可以通过对以下信号执行逻辑运算来生成第一信号NET1:与输入信号INP相对应的输入数据信号D、与第二信号NET2反相的第二反相信号NET2N、与第一信号NET1反相的第一反相信号NET1N和与输入时钟信号CLK反相的反相时钟信号CLKB。第一反相器INV1通过使输入时钟信号CLK反相来生成反相时钟信号CLKB。第二反相器INV2通过使第一信号NET1反相来生成第一反相信号NET1N。根据示例实施例,可以省略第一反相器INV1,可以从外部提供反相时钟信号CLKB。

[0109] 参考图11B,第一电路130的门电路131可以用多个晶体管TP1至TP4、TN1和TN2来实

现。图11B例示了与图11A的配置相对应的晶体管级配置的示例。图11B的第一电路130的操作与参考图8A、图8B及图9A和图9B所描述的基本上相同,并且省略重复的描述。

[0110] 图12是例示了根据示例实施例的时序电路的框图。

[0111] 参考图12,时序电路1002包括第一电路102、第二电路302和输出电路502。图12的时序电路1002对应于执行如下操作的时钟门控电路:接收时钟使能信号EN作为输入信号INP并且生成响应于时钟使能信号EN的激活而跳转的输出时钟信号ECK作为输出信号OUT。

[0112] 第一电路102基于时钟使能信号EN、输入时钟信号CLK和第二信号NET2生成第一信号NET1。第二电路302通过对第一信号NET1和与输入时钟信号CLK反相的反相时钟信号CLKB执行NOR运算来生成内部时钟信号CLKD,并且基于该内部时钟信号CLKD和时钟使能信号EN生成第二信号NET2。输出电路502基于该第二信号NET2生成输出时钟信号ECK。输出电路502包括缓冲器BF,而不包括图6中的输出电路501中的锁存电路。尽管图12示出了反相器作为缓冲器BF,然而缓冲器BF不限于反相器而是可以具有各种配置。

[0113] 图12的时序电路1002中所包括的第一电路102和第二电路302可以通过用时钟使能信号EN替换输入数据信号D、使用如参考图3A至图11B所描述的第一电路和第二电路来实现。

[0114] 图13A和图13B是例示了根据示例实施例的包括时序电路的扫描测试电路的图。

[0115] DFT (可测试性设计) 方案被广泛地用于测试半导体芯片。在DFT方案中,扫描测试方案被认为是高效地测试半导体集成电路的一个重要的解决方案。具有扫描输入的触发器是为了便于测试逻辑电路而设计的。根据扫描测试方案,逻辑电路中的触发器可以在扫描测试模式下形成移位寄存器,并且可以对移位寄存器施加扫描输入以观察得到的输出。

[0116] 图13A例示了使用扫描输入信号SI的扫描测试电路,并且图13B例示了使用反相扫描输入信号SIN的扫描测试电路。

[0117] 参考图13A,扫描测试电路800可以包括组合电路802、时序电路804以及反相器801、803、805和807。组合电路802可以包括多个逻辑电路810、820和830。时序电路804可以包括多个触发器,该多个触发器包括第一触发器840和第二触发器850。

[0118] 第一逻辑电路810对数据DATA IN执行逻辑运算并且提供第一触发器840的输入数据D。第一触发器840与输入时钟信号CLK同步地工作。扫描使能信号SE的逻辑电平可以表示正常模式或扫描测试模式。第一触发器840在正常模式下提供与输入数据D相对应的输出数据Q,而在扫描测试模式下提供与扫描输入信号SI相对应的输出数据Q。第二逻辑电路820对第一触发器840的输出数据Q执行逻辑运算并且提供第二触发器850的输入数据D。

[0119] 第二触发器850接收第一触发器的输出数据Q作为扫描输入SI并且接收扫描使能信号SE和输入时钟信号CLK。第三逻辑电路830对第二触发器850的输出数据Q执行逻辑运算并且提供输出数据DATA OUT。在扫描测试模式下,可以通过反相器805和807将第二触发器850的输出数据Q提供为扫描输出SO。

[0120] 参考图13B,扫描测试电路900可以包括组合电路802、时序电路904以及反相器901和903。组合电路802可以包括多个逻辑电路810、820和830。时序电路904可以包括多个触发器,该多个触发器包括第一触发器910和第二触发器920。除了图13B的扫描测试电路900中的第一触发器910和第二触发器920接收反相扫描输入信号SIN并且输出反相输出数据QN之外,图13B的扫描测试电路900与图13A的扫描测试电路800类似,并且省略重复的描述。

[0121] 图13A和图13B中的扫描测试电路中所包括的扫描触发器可以在扫描测试模式下提供与扫描输入数据SI相对应的输出数据。另外,图13A和图13B的扫描测试电路可以在正常模式下对输入数据DATA IN执行逻辑运算以提供输出数据DATA OUT,并且形成扫描测试路径以提供用于测试扫描测试电路的操作的、与扫描输入信号SI相对应的扫描输出信号SO。

[0122] 在下文中,提供了可应用于扫描测试电路中的触发器的时序电路的示例实施例。

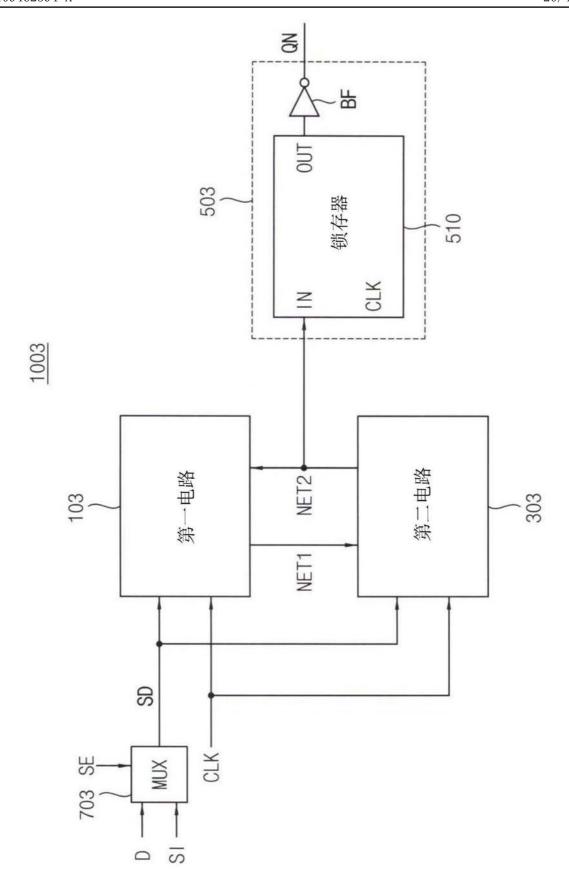

[0123] 图14和图15是例示了根据示例实施例的具有扫描测试功能的时序电路的框图。

[0124] 参考图14,时序电路1003包括第一电路103、第二电路303、输出电路503和多路复用器MUX 703。多路复用器703可以响应于扫描使能信号SE而选择输入数据信号D和扫描输入信号SI中的一个信号,以将所选择的信号SD输出作为上述输入信号INP。图14的时序电路1003对应于执行如下操作的触发器:接收所选择的信号SD作为输入信号INP并且生成与所选择的信号SD相对应的输出数据信号QN作为输出信号OUT。第一电路103、第二电路303和输出电路503与参考图6和图7所描述的基本上相同,并且省略重复的描述。

[0125] 如果通过简单地添加扫描多路复用器来实现扫描测试路径,则可能在时序电路中需要额外的触发器并且通过扫描测试路径的延迟时间可能比所需要的更短。一般而言,期望缩短正常路径的延迟时间,但是扫描测试路径的延迟时间必须比正常路径的延迟时间长。

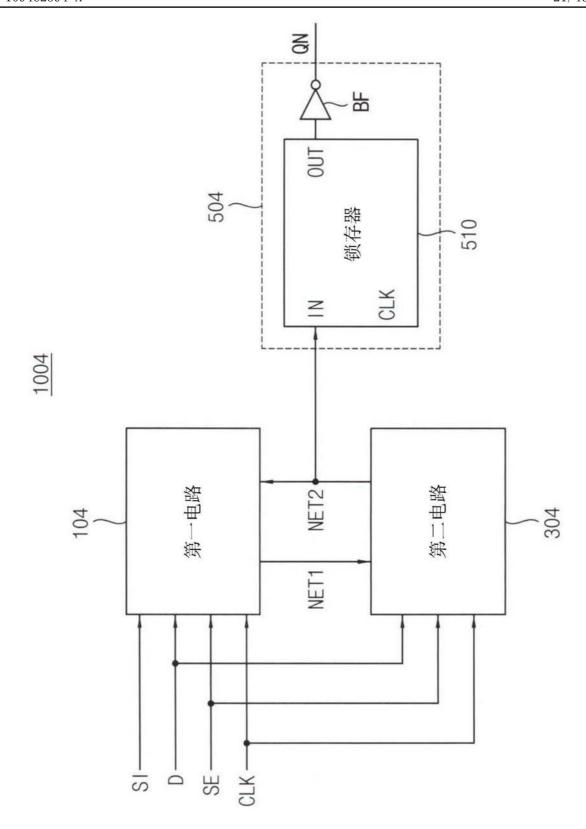

[0126] 可以通过图15的示例实施例来消除扫描多路复用器的缺点。

[0127] 参考图15,时序电路1004包括第一电路104、第二电路304和输出电路504。

[0128] 第一电路104基于扫描输入信号SI、输入数据信号D、扫描使能信号SE、输入时钟信号CLK和第二信号NET2生成第一信号NET1。第二电路304通过对第一信号NET1和与输入时钟信号CLK及相的反相时钟信号CLKB执行NOR运算来生成内部时钟信号CLKD,并且基于内部时钟信号CLKD、输入数据信号D和扫描使能信号SE生成第二信号NET2。输出电路504基于该第二信号NET2生成输出数据信号QN。输出电路504可以包括锁存电路510和缓冲器BF。锁存电路510锁存第二信号NET2并且缓冲器BF通过缓冲锁存电路510的输出信号来生成输出数据信号QN。尽管图15示出了反相器作为缓冲器BF,然而缓冲器BF不限于反相器而是可以具有各种配置。

[0129] 图16A是例示了图15的时序电路1004中所包括的第二电路304的示例实施例的框图,并且图16B是例示了图16A的第二电路的示例实施例的电路图。

[0130] 参考图16A,第二电路330可以包括第一门电路331、第二门电路332、第一反相器 INV1和第二反相器INV2。

[0131] 第一反相器INV1使输入时钟信号CLK反相以生成反相时钟信号CLKB。第二反相器INV2使第二信号NET2反相以生成第二反相信号NET2N。根据示例实施例,可以省略第一反相器INV1,可以从外部提供反相时钟信号CLKB。

[0132] 第一门电路331可以通过对第一信号NET1和反相时钟信号CLKB执行NOR运算来生成内部时钟信号CLKD。第一门电路311可以被实现为NOR门。

[0133] 第二门电路332可以通过对内部时钟信号CLKD和以下信号的OR运算结果执行NAND运算来生成第二信号NET2:与输入信号INP相对应的输入数据信号D、第二反相信号NET2N和扫描使能信号SE。

[0134] 参考图16B,第二电路330的第一门电路331和第二门电路332可以用多个晶体管TP1至TP3和TN1至TN6来实现。图16B例示了与图16A的配置相对应的晶体管级配置的示例。本领域的技术人员通过参照参考图8A、图8B及图9A和图9B所做出的描述,可以容易地理解图16B的第二电路330的操作,并且省略重复的描述。

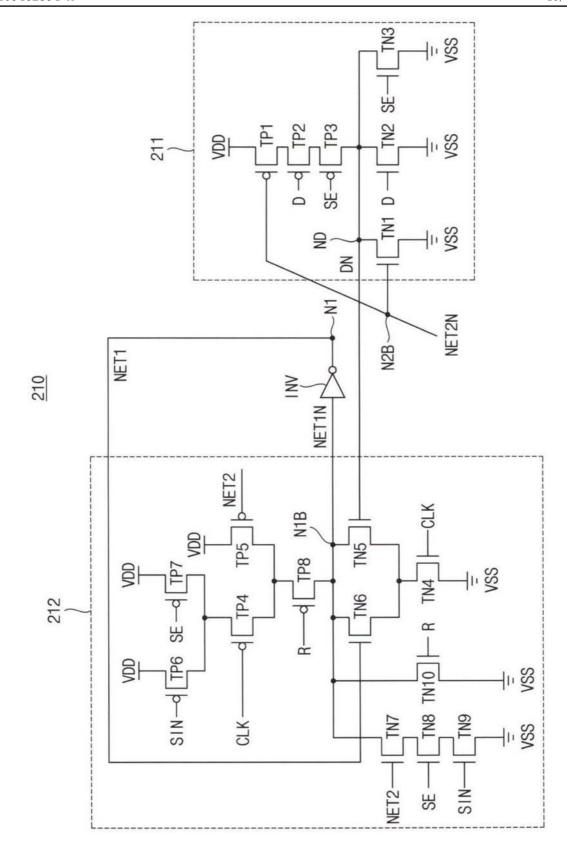

[0135] 图17A是例示了图15的时序电路1004中所包括的第一电路104的示例实施例的框图,并且图17B是例示了图17A的第一电路的示例实施例的电路图。

[0136] 参考图17A,第一电路140可以包括第一门电路141、第二门电路142和反相器INV。

[0137] 第一门电路141可以通过对与输入信号INP相对应的输入数据信号D、扫描使能信号SE和与第二信号NET2反相的第二反相信号NET2N执行NOR运算来生成内部信号DN。第二门电路142可以通过对以下信号执行逻辑运算来生成第一反相信号NET1N信号:第一信号NET1、内部信号DN、输入时钟信号CLK、第二反相信号NET2N、扫描使能信号SE和反相扫描输入信号SIN。反相器INV通过使第一反相信号NET1N反相来生成第一信号NET1。

[0138] 参考图17B,第一电路140的第一门电路141和第二门电路142可以用多个晶体管 TP1至TP7和TN1至TN9来实现。图17B例示了与图17A的配置相对应的晶体管级配置的示例。可以通过本领域的技术人员参考参考图8A、图8B及图9A和图9B的描述容易地理解图17B的第一电路140的操作,并且省略重复的描述。

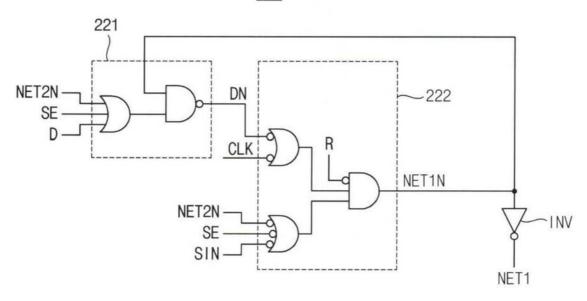

[0139] 图18A是例示了图15的时序电路1004中所包括的第一电路104的示例实施例的框图,并且图18B是例示了图18A的第一电路的示例实施例的电路图。

[0140] 参考图18A,第一电路150可以包括第一门电路151、第二门电路152和反相器INV1。

[0141] 第一门电路151可以通过对与输入信号INP相对应的输入数据信号D、扫描使能信号SE和与第二信号NET2反相的第二反相信号NET2N执行NOR运算来生成内部信号DN。第二门电路152可以通过对以下信号执行逻辑运算来生成第一反相信号NET1N:内部信号DN、输入时钟信号CLK、第二反相信号NET2N、扫描使能信号SE和反相扫描输入信号SIN。反相器INV1通过使第一反相信号NET1N反相来生成第一信号NET1。

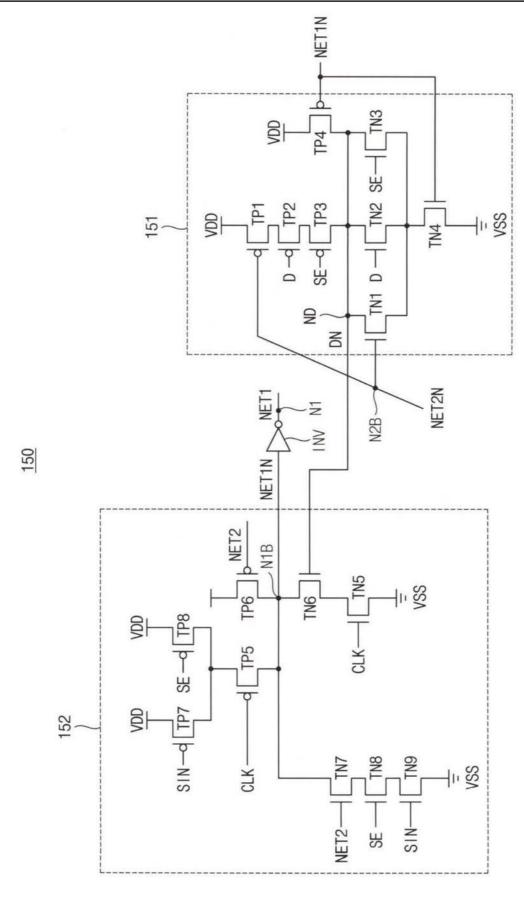

[0142] 参考图18B,第一电路150的第一门电路151和第二门电路152可以用多个晶体管 TP1至TP8和TN1至TN9来实现。图18B例示了与图18A的配置相对应的晶体管级配置的示例。 本领域的技术人员通过参照参考图8A、图8B及图9A和图9B所做出的描述,可以容易地理解图18B的第一电路150的操作,并且省略重复的描述。

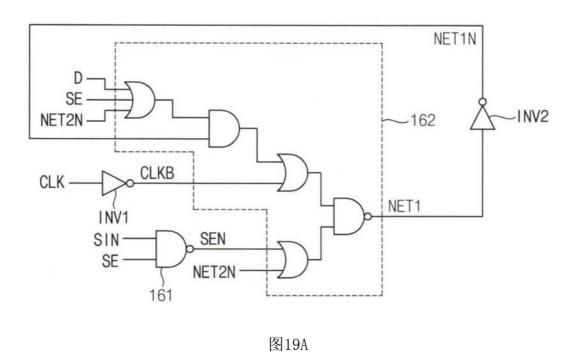

[0143] 图19A是例示了图15的时序电路1004中所包括的第一电路104的示例实施例的框图,并且图19B是例示了图19A的第一电路的示例实施例的电路图。

[0144] 参考图19A,第一电路160可以包括第一门电路161、第二门电路162、第一反相器 INV1和第二反相器INV2。

[0145] 第一门电路161可以通过对反相扫描输入信号SIN和扫描使能信号SE执行NAND运算来生成内部使能信号SEN。第二门电路162可以通过对以下信号执行逻辑运算来生成第一信号NET1:输入数据信号D、扫描使能信号SE、第二反相信号NET2N、第一反相信号NET1N、反相时钟信号CLKB和内部使能信号SEN。第一反相器INV1通过使输入时钟信号CLK反相来生成反相时钟信号CLKB。第二反相器INV2通过使第一信号NET1反相来生成第一反相信号NET1N。 [0146] 参考图19B、第一电路160的第一门电路161和第二门电路162可以用多个晶体管

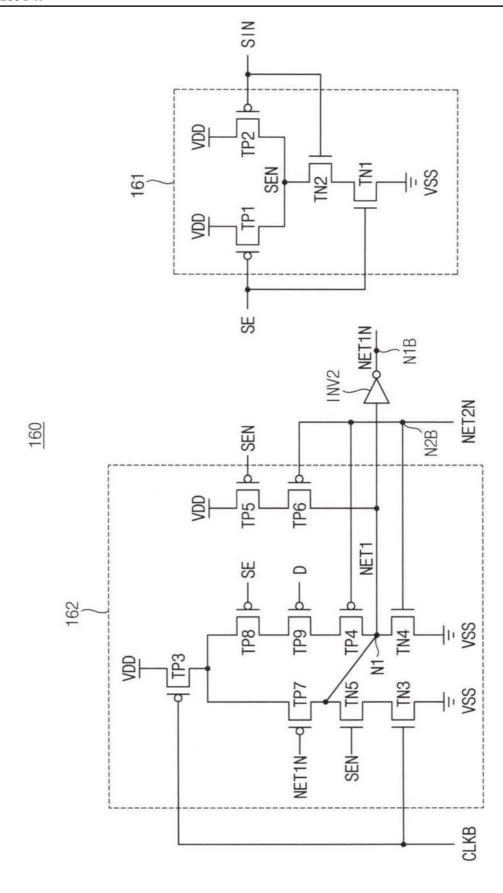

[0146] 参考图19B,第一电路160的第一门电路161和第二门电路162可以用多个晶体管 TP1至TP9和TN1至TN5来实现。图19B例示了与图19A的配置相对应的晶体管级配置的示例。

本领域的技术人员通过参照参考图8A、图8B及图9A和图9B所做出的描述,可以容易地理解图19B的第一电路160的操作,并且省略重复的描述。

[0147] 如参考图15至图19B所描述的,在扫描使能信号SE被激活的扫描测试模式期间,通过经由第一电路和第二电路的扫描测试路径生成与扫描输入信号SI或反相扫描输入信号SIN相对应的第二信号NET2。相比之下,在扫描使能信号SE被去激活的正常模式期间,经由第二电路生成与输入数据信号D相对应的第二信号NET2。通过这种扫描测试路径和正常路径,扫描测试路径的延迟时间可以被设定为比正常路径的延迟时间长。

[0148] 在扫描测试路径中,在触发器之间未插入逻辑电路,并且前一个触发器的输出被直接地输入到下一个触发器。因此前一级的输出可以在经过保持时间之前被传送到下一级。为了扫描测试的成功,在触发器之间传送的数据自输入时钟信号CLK的转变起必须被保持所述的保持时间。如果在扫描测试模式期间触发器之间的数据传送太快,则扫描测试失败。因此在扫描测试模式期间需要增加延迟时间,并且需要减少保持时间。

[0149] 如上所述,根据示例实施例的时序电路可以将扫描测试路径的延迟时间设定为比正常路径的延迟时间长。可以提高正常模式的运行速度并且同时可以高效地支持扫描测试。

[0150] 图20是例示了根据示例实施例的时序电路的框图。

[0151] 参考图20,时序电路1005包括第一电路105、第二电路305和输出电路505。图20的时序电路1005对应于执行以下操作的时钟门控电路:接收时钟使能信号EN作为输入信号INP并且生成响应于时钟使能信号EN的激活而跳转的输出时钟信号ECK作为输出信号OUT。

[0152] 第一电路105基于时钟使能信号EN、扫描使能信号SE、输入时钟信号CLK和第二信号NET2生成第一信号NET1。第二电路305通过对第一信号NET1和与输入时钟信号CLK反相的反相时钟信号CLKB执行NOR运算来生成内部时钟信号CLKD,并且基于该内部时钟信号CLKD、时钟使能信号EN和扫描使能信号SE生成第二信号NET2。输出电路505基于该第二信号NET2生成输出时钟信号ECK。输出电路505包括缓冲器BF,并且不包括图6的输出电路501中的锁存电路。尽管图20示出了反相器作为缓冲器BF,然而缓冲器BF不限于反相器而是可以具有各种配置。

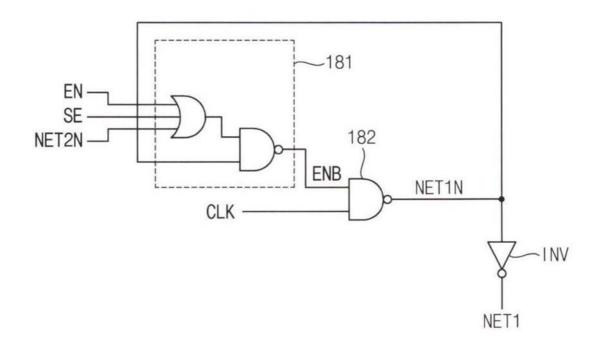

[0153] 图21A是例示了图20的时序电路1005中所包括的第二电路305的示例实施例的框图,并且图21B是例示了图21A的第二电路的示例实施例的电路图。

[0154] 除了第二电路340添加了扫描使能信号SE作为输入之外,图21A和图21B的第二电路340与图3A和图3B的第二电路310基本上相同,并且省略重复的描述。将图21B与图3B相比较,第二电路340进一步包括接收扫描输入信号SE的NMOS晶体管TN6。

[0155] 图22A是例示了图20的时序电路1005中所包括的第一电路105的示例实施例的框图,并且图22B是例示了图22A的第一电路的示例实施例的电路图。

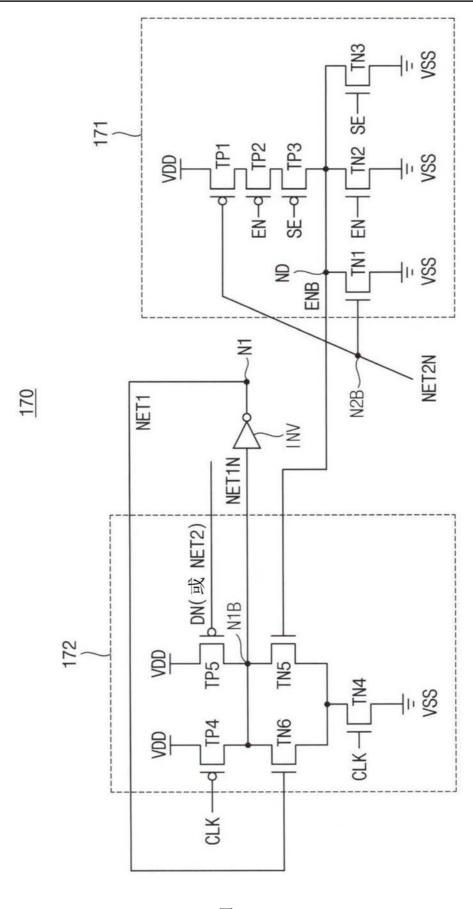

[0156] 除了第一电路170添加了扫描使能信号SE作为输入之外,图22A和图22B的第一电路170与图4A和图4B的第一电路110基本上相同,并且省略重复的描述。将图22B与图4B相比较,第一电路170进一步包括接收扫描输入信号SE的晶体管TP3和TN3,输入数据信号D被时钟使能信号ENB势换,并且内部信号DN被内部使能信号ENB替换。

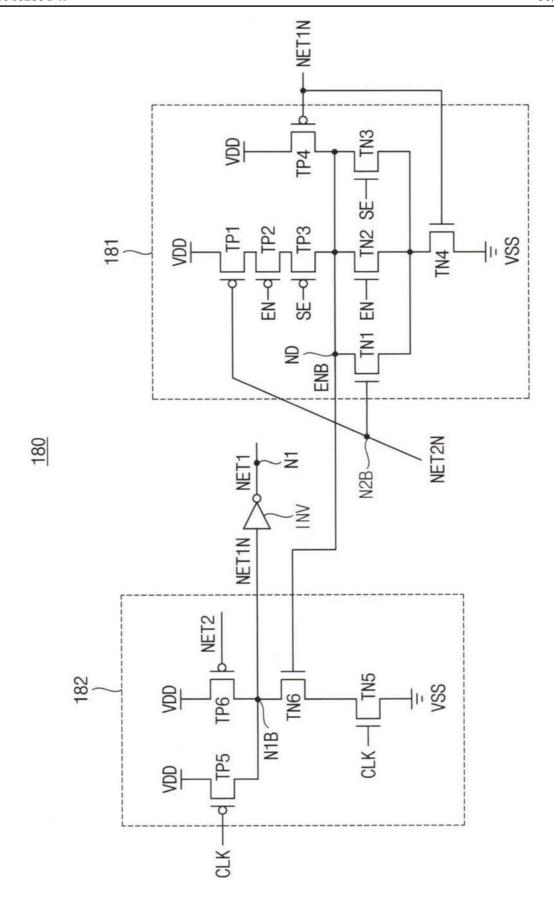

[0157] 图23A是例示了图20的时序电路1005中所包括的第一电路105的示例实施例的框图,并且图23B是例示了图23A的第一电路的示例实施例的电路图。

[0158] 除了第一电路180添加了扫描使能信号SE作为输入之外,图23A和图23B的第一电路180与图10A和图10B的第一电路120基本上相同,并且省略重复的描述。将图23B与图10B相比较,第一电路180进一步包括接收扫描输入信号SE的晶体管TP3和TN3,输入数据信号D被时钟使能信号EN替换,并且内部信号DN被内部使能信号ENB替换。

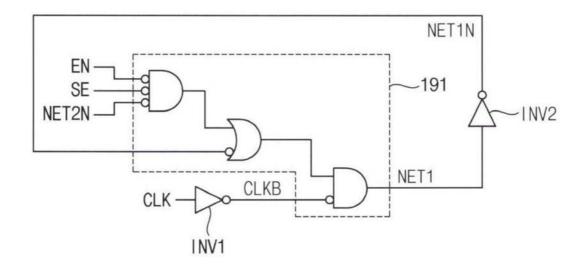

[0159] 图24A是例示了图20的时序电路1005中所包括的第一电路105的示例实施例的框图,并且图24B是例示了图24A的第一电路的示例实施例的电路图。

[0160] 除了第一电路190添加了扫描使能信号SE作为输入之外,图24A和图24B的第一电路190与图11A和图11B的第一电路130基本上相同,并且省略重复的描述。将图24B与图11B相比较,第一电路190进一步包括接收扫描输入信号SE的晶体管TP5,并且输入数据信号D被时钟使能信号EN替换。

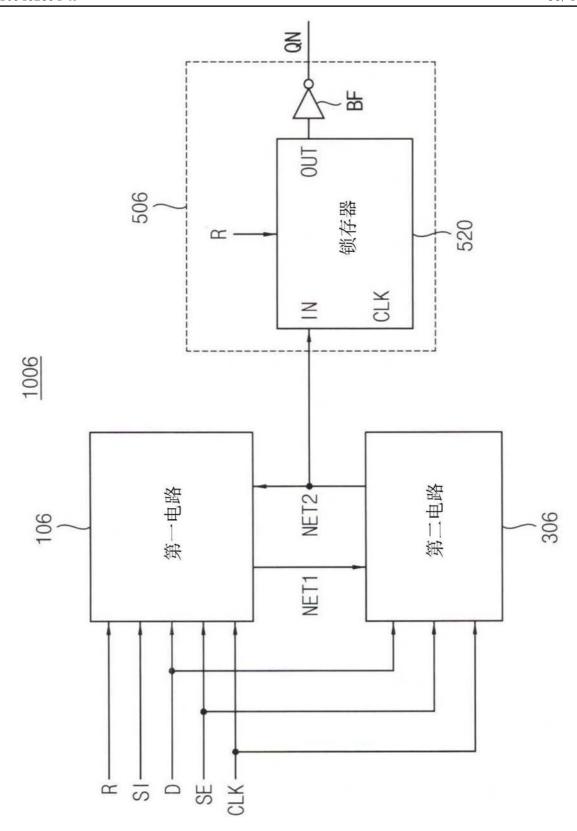

[0161] 图25是例示了根据示例实施例的时序电路的框图。

[0162] 除了时序电路1006添加了复位信号R作为输入之外,图25的时序电路1006与图15的时序电路1004基本上相同,并且省略重复的描述。时序电路1006中的第一电路106和第二电路306可以响应于复位信号R而使内部节点的值复位。

[0163] 图26A是例示了图25的时序电路1006中所包括的第一电路106的示例实施例的框图,并且图26B是例示了图26A的第一电路的示例实施例的电路图。

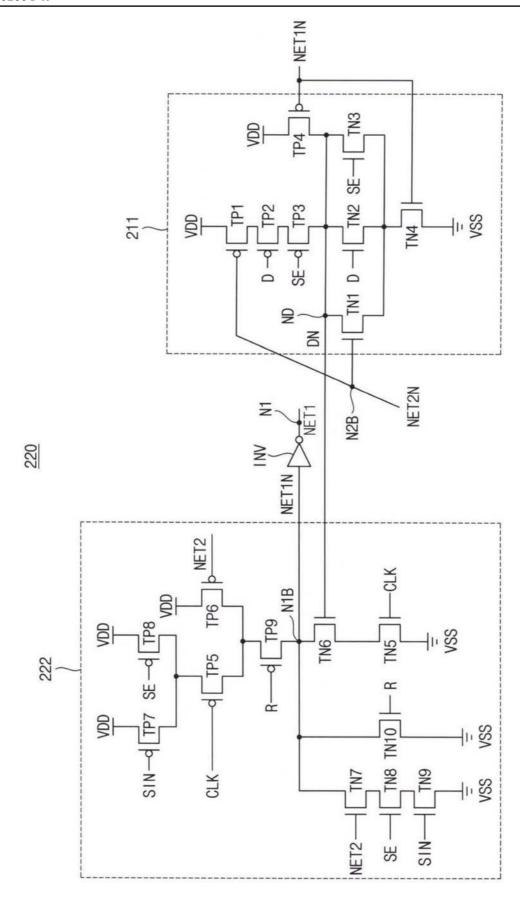

[0164] 除了第一电路210添加了复位信号R作为输入之外,图26A和图26B的第一电路210与图17A和图17B的第一电路140基本上相同,并且省略重复的描述。将图26B与图17B相比较,第一电路210进一步包括接收复位信号R的晶体管TP8和TN10。

[0165] 图27A是例示了图25的时序电路1006中所包括的第一电路106的示例实施例的框图,并且图27B是例示了图27A的第一电路的示例实施例的电路图。

[0166] 除了第一电路220添加了复位信号R作为输入之外,图27A和图27B的第一电路220 与图18A和图18B的第一电路150基本上相同,并且省略重复的描述。将图27B与图18B相比较,第一电路220进一步包括接收复位信号R的晶体管TP9和TN10。

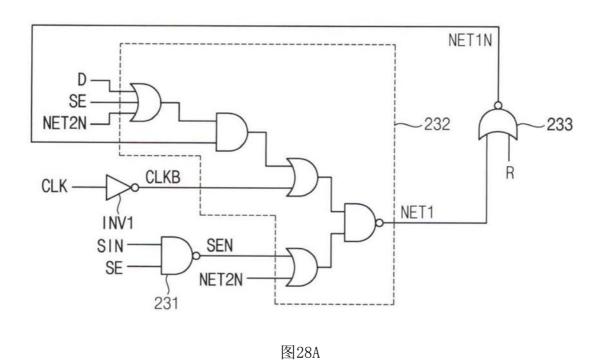

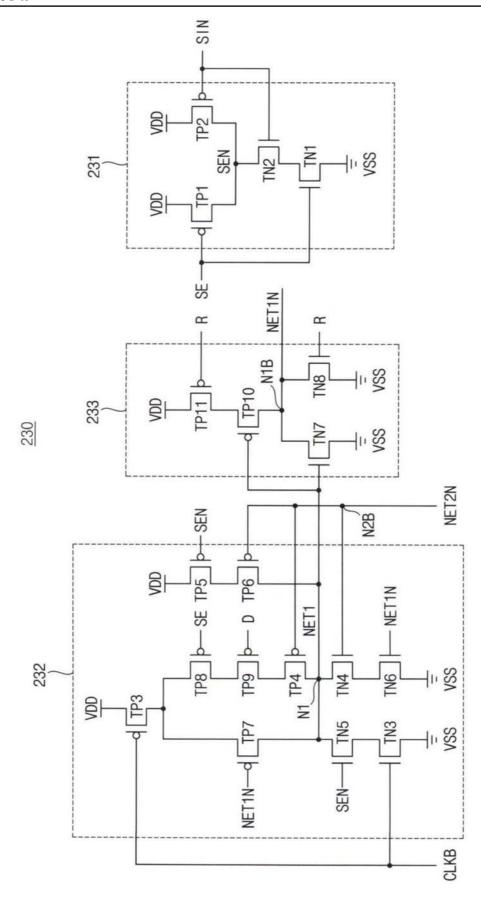

[0167] 图28A是例示了图25的时序电路1006中所包括的第一电路106的示例实施例的框图,并且图28B是例示了图28A的第一电路的示例实施例的电路图。

[0168] 除了第一电路230添加了复位信号R作为输入之外,图28A和图28B的第一电路230与图19A和图19B的第一电路160基本上相同,并且省略重复的描述。将图28B与图19B相比较,图19B中的反相器INV2被图28B中的NOR门233替换。NOR门233包括晶体管TP10、TP11、TN7和TN8,这些晶体管TP10、TP11、TN7和TN8被配置为通过对复位信号R和第一信号NET1执行NOR运算来生成第一反相信号NETIN。

[0169] 图29是例示了图25的时序电路1006中所包括的输出电路506的示例实施例的电路图。

[0170] 除了锁存电路520添加了复位信号R作为输入之外,图29的输出电路506中所包括的锁存电路520与图7的输出电路501中所包括的锁存电路510基本上相同,并且省略重复的描述。将图29与图7相比较,图29中的锁存电路520进一步包括接收复位信号R的晶体管TP4和TN4。

[0171] 已经参考图25和图29描述了具有复位功能的时序电路,但是示例实施例不限于此。本领域的技术人员将容易地理解的是,可以通过信号反相、在N型和P型之间交换晶体管

类型等,将所公开的与复位功能相关联的示例实施例修改为与置位功能相关联的示例实施例。

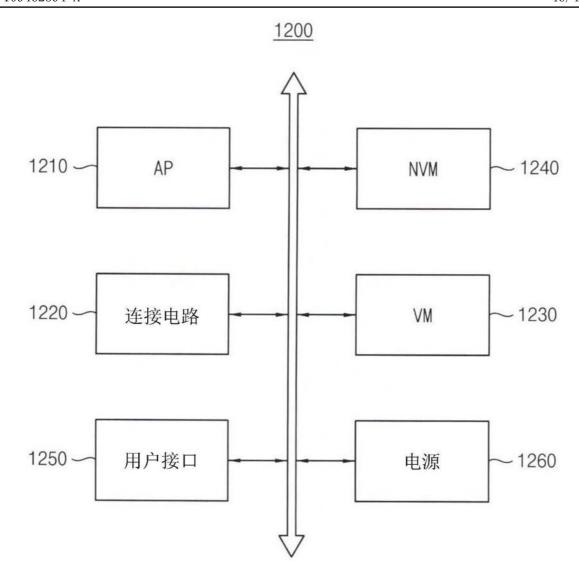

[0172] 图30是例示了根据示例实施例的系统的框图。

[0173] 参考图30,系统1200包括应用处理器1210、连接电路1220、易失性存储器设备(VM) 1230、非易失性存储器设备(NVM) 1240、用户接口1250和电源1260。

[0174] 应用处理器1210可以执行存储在计算机可读介质(例如,存储器设备)中的计算机指令,包括诸如web浏览器、游戏应用、视频播放器等的应用。连接电路1220可以执行与外部设备的有线或无线通信。易失性存储器设备1230可以存储由应用处理器1210处理的数据,或者可以用作工作存储器。例如,易失性存储器设备1230可以是动态随机存取存储器,诸如DDR SDRAM、LPDDR SDRAM、GDDR SDRAM、RDRAM等。非易失性存储器设备1240可以存储用于启动移动系统1200的启动映像。用户接口1250可以包括至少一个输入设备,诸如小键盘、触摸屏等,并且包括至少一个输出设备,诸如扬声器、显示设备等。电源1260可以向移动系统1200供应电源电压。在一些实施例中,移动系统1200可以进一步包括相机图像处理器(CIS)和/或诸如存储卡、固态硬盘(SSD)、硬盘驱动器(HDD)、CD-ROM等的存储设备。

[0175] 系统1200可以包括如参考图1至图29所描述的一个或更多个时序电路。在一些示例实施例中,系统1200可以包括使用根据示例实施例的时序电路的扫描链。

[0176] 如上所述,根据示例实施例的时序电路可以通过第一电路与第二电路之间的相互控制而具有增加的负建立时间,负建立时间反映在输入时钟信号的转变之后的输入信号的转变,并且因此,可以提高时序电路和包括时序电路的集成电路的运行速度。根据示例实施例的时序电路可以在第二电路中的数据传送路径上仅包括单级门电路以减小数据输出延迟,并且因此,可以提高时序电路和包括时序电路的集成电路的运行速度。根据示例实施例的时序电路可以将扫描测试路径的延迟时间设定为比正常路径的延迟时间长,并且因此,可以高效地支持扫描测试。

[0177] 本发明构思可以被应用于任何设备和系统。例如,本发明构思可以被应用于以下系统:诸如存储卡、移动电话、智能电话、个人数字助理(PDA)、便携式多媒体播放器(PMP)、数码相机、摄录像机、个人计算机(PC)、服务器计算机、工作站、膝上型计算机、数字TV、机顶盒、便携式游戏机、导航系统等。

[0178] 本发明构思可以被应用于包括需要刷新操作的存储器设备的任何设备和系统。例如,本发明构思可以被应用于以下系统:诸如为移动电话、智能电话、个人数字助理(PDA)、便携式多媒体播放器(PMP)、数码相机、摄录像机、个人计算机(PC)、服务器计算机、工作站、膝上型计算机、数字TV、机顶盒、便携式游戏机、导航系统等。

[0179] 上文是示例实施例的说明,并且将不被解释为对其进行限制。尽管已经描述了一些示例实施例,然而本领域的技术人员将容易了解的是,在实质上不脱离本发明构思的情况下,许多修改在示例实施例中是可能的。

图1

图2A

图2B

## <u>310</u>

图3A

# <u>110</u>

图7

图8A

图9A

图10A

图11A

图11B

图13A

图14

图15

图16A

<u>140</u>

图17B

<u>150</u>

图18A

图18B

图19B

<u>340</u>

图21A

<u>170</u>

图22B

图23A

图23B

<u>190</u>

图24A

图24B

图25

## <u>210</u>

图26B

图27A

图27B

<u>230</u>

图28B

<u>506</u>

图29

图30