# (19)中华人民共和国国家知识产权局

# (12)发明专利

(10)授权公告号 CN 106649170 B (45)授权公告日 2020.08.14

(21)申请号 201610575809.6

(22)申请日 2016.07.20

(65)同一申请的已公布的文献号 申请公布号 CN 106649170 A

(43)申请公布日 2017.05.10

(30)优先权数据

10-2015-0150661 2015.10.29 KR

(73) **专利权人** 爱思开海力士有限公司 地址 韩国京畿道

(72)发明人 金亨圭 李日勋

(74)专利代理机构 北京弘权知识产权代理事务

所(普通合伙) 11363

代理人 王建国 许伟群

(51) Int.CI.

*G06F* 13/40(2006.01)

(56)对比文件

CN 1694425 A,2005.11.09 US 6034545 A,2000.03.07

审查员 李艳丽

权利要求书2页 说明书5页 附图6页

### (54)发明名称

能够采集高速信号的电子系统和电子设备

#### (57)摘要

一种电子系统可以包括:主机、存储器、数据记录系统和驱动电路。驱动电路可以驱动在主机与存储器之间传送的信号。当信号被监控时,驱动电路可以保持在主机与存储器之间传送的信号的幅度和/或强度。

CN 106649170 B

1.一种电子系统,包括:

主机;

存储器;

数据记录电路:以及

多个驱动电路,被配置为驱动从主机经由多个总线传送的多个信号,并且将驱动的信号提供至存储器和数据记录电路,

其中,所述多个总线之中的至少一个总线是从主机到存储器单向的,并且所述多个总线之中的至少一个总线是双向的。

- 2.根据权利要求1所述的电子系统,其中,驱动电路包括单向转接驱动器和一输入二输出转接驱动器中的一个或多个,转接驱动器被配置为驱动从主机传送的信号,并且将驱动的信号提供至存储器和数据记录电路。

- 3.根据权利要求1所述的电子系统,其中,主机包括训练电路,训练电路被配置为补偿由驱动电路引起的延迟时间。

- 4.根据权利要求1所述的电子系统,其中,驱动电路还被配置为驱动从存储器传送的信号,并且将驱动的信号提供至主机和数据记录电路。

- 5.根据权利要求4所述的电子系统,其中,驱动电路包括:

- 第一转接驱动器,被配置为驱动和输出从主机传送的信号;

- 第二转接驱动器,被配置为驱动从第一转接驱动器输出的信号并且将驱动的信号提供 至存储器,以及驱动和输出从存储器传送的信号;以及

- 第三转接驱动器,被配置为驱动从第一转接驱动器和第二转接驱动器输出的信号,并 且将驱动的信号提供至数据记录电路。

- 6.根据权利要求4所述的电子系统,其中,主机包括训练电路,训练电路被配置为补偿由驱动电路引起的延迟时间。

- 7.一种半导体系统,包括:

主机:

存储器:

数据记录系统:

第一驱动电路,其耦接到第一总线并被配置为驱动从主机经由所述第一总线传送的第一信号,并且将驱动的第一信号提供至存储器和数据记录电路;以及

第二驱动电路,其耦接到第二总线并被配置为驱动从主机经由所述第二总线传送的第二信号,并且将驱动的第二信号提供至存储器和数据记录电路,以及驱动从存储器传送的第二信号,并且将驱动的第二信号提供至主机和数据记录电路;

其中,第一总线是从主机到存储器单向的,并且第二总线是双向的。

- 8.根据权利要求7所述的半导体系统,其中,第一信号包括命令信号、地址信号和时钟信号中的一个或多个。

- 9.根据权利要求7所述的半导体系统,其中,第二信号包括数据信号和数据选通信号中的一个或多个。

- 10.根据权利要求7所述的半导体系统,其中,第一驱动电路包括单向转接驱动器和一输入二输出转接驱动器中的一个或多个,转接驱动器被配置为驱动从主机传送的第一信

- 号,并且将驱动的第一信号提供至存储器和数据记录电路。

- 11.根据权利要求7所述的半导体系统,其中,第二驱动电路包括:

- 第一转接驱动器,被配置为驱动和输出从主机传送的第二信号;

- 第二转接驱动器,被配置为驱动从第一转接驱动器输出的信号并且将驱动的信号提供 至存储器,以及驱动和输出从存储器传送的第二信号;以及

- 第三转接驱动器,被配置为驱动从第一转接驱动器和第二转接驱动器输出的信号,并 且将驱动的信号提供至数据记录电路。

- 12. 根据权利要求7所述的半导体系统,其中,主机包括训练电路,训练电路被配置为补偿由第一驱动电路和第二驱动电路引起的延迟时间。

- 13.一种电子设备,包括:

处理器:

信号采集卡;以及

存储器,安装在信号采集卡上,

其中,信号采集卡包括:

第一驱动电路,其耦接到第一总线并被配置为驱动从处理器经由所述第一总线传送的第一信号,并且将驱动的第一信号提供至存储器和监控终端;以及

第二驱动电路,其耦接到第二总线并被配置为驱动从处理器经由所述第二总线传送的 第二信号并且将驱动的第二信号提供至存储器和监控终端,以及驱动从存储器传送的第二 信号并且将驱动的第二信号提供至处理器和监控终端,

其中,第一总线是从处理器到存储器单向的,并且第二总线是双向的。

- 14.根据权利要求13所述的电子设备,其中,第一信号包括命令信号、地址信号和时钟信号中的一个或多个。

- 15.根据权利要求13所述的电子设备,其中,第二信号包括数据信号和数据选通信号中的一个或多个。

- 16.根据权利要求13所述的电子设备,还包括数据记录电路,数据记录电路经由线缆与监控终端电耦接。

- 17.根据权利要求13所述的电子设备,其中,处理器包括训练电路,训练电路被配置为补偿由第一驱动电路和第二驱动电路引起的延迟时间。

- 18.根据权利要求13所述的电子设备,其中,信号采集卡安装在主板上。

- 19.根据权利要求13所述的电子设备,其中,信号采集卡安装在处理器上。

# 能够采集高速信号的电子系统和电子设备

[0001] 相关申请的交叉引用

[0002] 本申请要求于2015年10月29日向韩国知识产权局提交的申请号为10-2015-0150661的韩国专利申请的优先权,其全部内容通过引用合并于此。

# 技术领域

[0003] 各种实施例总体而言涉及一种电子设备,更具体地,涉及一种能够采集高速信号的电子系统和电子设备。

## 背景技术

[0004] 在计算机系统中,安装在主板上的处理器和存储器可以通过主板的信号总线而彼此通信。近年来,集成有处理器和存储器的电子系统或者电子设备正被应用至个人和便携式电子设备。例如,处理器和存储器可以在单个芯片上制造,或者可以被封闭在单个封装或者模块中。

[0005] 电子系统或者电子设备可以包括:多芯片封装(MCP)、片上系统(S0C)、系统级封装(SIP)、堆叠式封装(P0P)等。电子系统或者电子设备可以用于包括个人计算机(PC)、平板电脑、笔记本电脑、智能电话、便携式多媒体设备等的个人电子设备中。

# 发明内容

[0006] 在本发明的一个实施例中,一种电子系统可以包括:主机、存储器、数据记录电路和驱动电路。驱动电路可以驱动从主机传送的信号,并且可以将驱动的信号提供至存储器和数据记录电路。

[0007] 在本发明的一个实施例中,一种电子系统可以包括:主机、存储器、数据记录电路和驱动电路。驱动电路可以驱动从主机传送的信号,并且将驱动的信号提供至存储器和数据记录电路,以及可以驱动从存储器传送的信号,并且将驱动的信号提供至主机和数据记录电路。

[0008] 在本发明的一个实施例中,一种电子系统可以包括:主机、存储器、数据记录系统、第一驱动电路和第二驱动电路。第一驱动电路可以驱动从主机传送的第一信号,并且可以将驱动的第一信号提供至存储器和数据记录系统。第二驱动电路可以驱动从主机传送的第二信号,并且将驱动的第二信号提供至存储器和数据记录电路,以及可以驱动从存储器传送的第二信号,并且将驱动的第二信号提供至主机和数据记录电路。

[0009] 在本发明的一个实施例中,一种电子设备可以包括:处理器、信号采集卡和存储器。存储器可以安装在信号采集卡上。信号采集卡可以包括第一驱动电路和第二驱动电路。第一驱动电路可以驱动从处理器传送的第一信号,并且可以将驱动的第一信号提供至存储器和监控终端。第二驱动电路可以驱动从处理器传送的第二信号,并且将驱动的第二信号提供至存储器和监控终端,以及可以驱动从存储器传送的第二信号,并且将驱动的第二信号提供至处理器和监控终端。

[0010] 在本发明的一个实施例中,一种电子设备可以包括:主板、安装在主板上的处理器、安装在主板上的信号采集卡以及安装在信号采集卡上的存储模块。信号采集卡可以包括第一驱动电路和第二驱动电路。第一驱动电路可以驱动从处理器传送的第一信号,并且可以将驱动的第一信号提供至存储模块和监控终端。第二驱动电路可以驱动从处理器传送的第二信号,并且将驱动的第二信号提供至存储模块和监控终端,以及可以驱动从存储模块传送的第二信号,并且将驱动的第二信号提供至处理器和监控终端。

[0011] 在本发明的一个实施例中,一种电子设备可以包括:处理器、安装在处理器上的信号采集卡以及安装在信号采集卡上的存储器。信号采集卡可以包括第一驱动电路和第二驱动电路。第一驱动电路可以驱动从处理器传送的第一信号,并且可以将驱动的第一信号提供至存储器和监控终端。第二驱动电路可以驱动从处理器传送的第二信号,并且将驱动的第二信号提供至存储器和监控终端,以及可以驱动从存储器传送的第二信号,并且将驱动的第二信号提供至处理器和监控终端。

### 附图说明

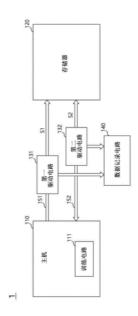

- [0012] 图1为图示了根据本发明的一个实施例的电子系统的示例的示图。

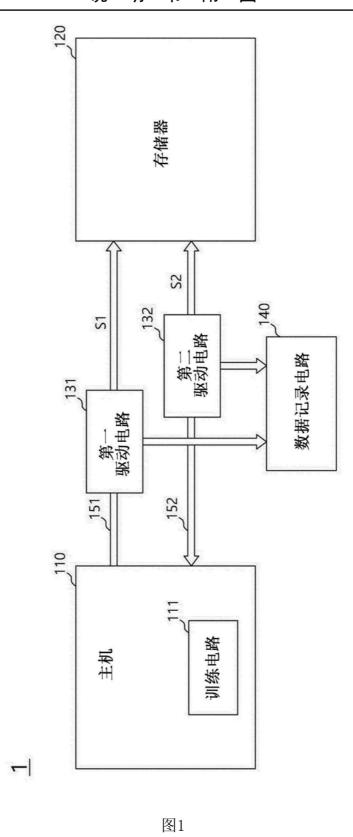

- [0013] 图2为图示了图1中所示的第一驱动电路的示例的示图。

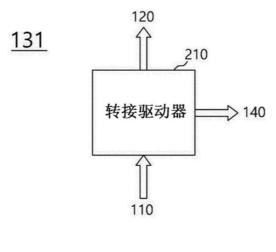

- [0014] 图3A和图3B为图示了图1中所示的第二驱动电路的示例的示图。

- [0015] 图4和图5为图示了根据本发明的一个实施例的电子设备的示例的示图。

- [0016] 图6为图示了根据本发明的一个实施例的电子设备的示例的示图。

- [0017] 图7A和图7B为图示了根据本发明的一个实施例的电子设备的示例的示图。

# 具体实施方式

[0018] 在下文中,将参照附图来描述根据本发明的实施例的半导体设备。

[0019] 图1为图示了根据本发明的一个实施例的电子系统1的示例的示图。参见图1,电子系统1可以包括:主机110、存储器120、多个驱动电路131和132以及数据记录电路140。主机110和存储器120可以执行数据通信。主机110可以包括如下中的一个或多个:中央处理单元(CPU)、图形处理单元(GPU)、多媒体处理器(MMP)和数字信号处理器。主机110可以通过将具有各种功能的处理器,例如应用处理器(AP),组合而以片上系统(SOC)的形式来实施。存储器120可以包括易失性存储器件和非易失性存储器。易失性存储器的示例可以包括:静态RAM(SRAM)、动态RAM(DRAM)和同步DRAM(SDRAM)。非易失性存储器的示例可以包括:只读存储器(ROM)、可编程ROM(PROM)、电可擦除可编程ROM(EEPROM)、电可编程ROM(EPROM)、快闪存储器、相变RAM(PRAM)、磁性RAM(MRAM)、电阻式RAM(RRAM)和铁电RAM(FRAM)。

[0020] 主机110和存储器120可以经由多个总线而彼此电耦接。图1图示了将第一总线151和第二总线152作为使主机110与存储器120耦接的多个总线的示例。第一总线可以传送第一信号S1,而第二总线可以传送第二信号S2。第一信号S1可以从主机110被提供至存储器120。例如,第一信号S1可以包括命令信号、地址信号、时钟信号和请求信号中的一个或多个。第二信号S2可以从主机110被提供至存储器120,或者可以从存储器120被提供至主机110。例如,第二信号S2可以包括数据信号和数据选通信号中的一个或二个。

[0021] 多个驱动电路131和132可以包括第一驱动电路131和第二驱动电路132。第一驱动

电路131可以与第一总线151电耦接,而第二驱动电路132可以与第二总线152电耦接。第一驱动电路131可以驱动从主机110传送的信号,并且可以将驱动的信号提供至存储器120和数据记录电路140。例如,第一驱动电路131可以驱动第一信号S1,并且将驱动的信号提供至存储器120和数据记录电路140。第二驱动电路132可以驱动从主机110传送的信号,并且可以将驱动的信号提供至存储器120和数据记录电路140。第二驱动电路132可以驱动从主机110传送的第二信号S2,并且可以将驱动的信号提供至存储器120和数据记录电路140。第二驱动电路132可以驱动从主机110传送的信号,并且可以将驱动的信号提供至存储器120和数据记录电路140。第二驱动电路132可以驱动从存储器120传送的信号,并且可以将驱动的信号提供至主机110和数据记录电路140。第二驱动电路132可以驱动从主机110提供的第二信号S2,并且将驱动的信号提供至存储器120和数据记录电路140。第二驱动电路132可以驱动从存储器120提供的第二信号S2,并且将驱动的信号提供至主机110和数据记录电路140。

[0022] 主机110和存储器120可以通过高速接口而彼此通信。因此,经由第一总线151和第二总线152传送的第一信号S1和第二信号S2可以具有高频率和低幅度。第一驱动电路131和第二驱动电路132可以驱动经由第一总线151和第二总线152传送的第一信号S1和第二信号S2,并且不仅将驱动的信号提供至主机110和存储器120,还提供至数据记录电路140。因此,可以监控在主机110与存储器120之间传送的第一信号S1和第二信号S2。在一个实施例中,当信号被监控时,可以保持在主机110与存储器120之间传送的第一信号S1和第二信号S2的幅度和/或强度。

[0023] 数据记录电路140可以存储和监控在主机110与存储器120之间传送的信号。数据记录电路140可以通过接收从第一驱动电路131和第二驱动电路132提供的信号,而监控在主机110与存储器120之间传送的第一信号S1和第二信号S2。例如,数据记录电路140可以包括诸如小外形双列直插存储模块(S0DIMM)的数据存储区以及诸如现场可编程门阵列(FPGA)的可编程逻辑器件。数据记录电路140可以将从第一驱动电路131和第二驱动电路132输出的信号存储在数据存储区中(例如,S0DIMM和FPGA)。数据记录电路140可以通过读取来自S0DIMM的信号并且执行算术运算,而监控和/或分析在主机110与存储器120之间传送的信号。

[0024] 参见图1,主机110还可以包括训练电路111。训练电路111可以补偿由第一驱动电路131和第二驱动电路132引起的延迟时间。电耦接在主机110与存储器120之间的第一驱动电路131和第二驱动电路132可以延迟经由第一总线151和第二总线152传送的第一信号S1和第二信号S2。因此,训练电路111可以对主机110和存储器120执行训练操作。例如,训练电路111可以参照从存储器120经由第二总线152提供的第二信号S2而执行时序训练。

[0025] 图2为图示了图1中所示的第一驱动电路131的示例的示图。参见图2,第一驱动电路131可以包括转接驱动器210。转接驱动器210可以驱动从主机110传送的信号,并且将驱动的信号提供至存储器120和数据记录电路140。转接驱动器210可以为单向转发器和一输入二输出转发器。例如,转接驱动器210可以实施为寄存器时钟驱动器(RCD),寄存器时钟驱动器(RCD)可以用于注册双列直插存储模块(RDIMM)或者低负载双列直插存储模块(LRDIMM)。转接驱动器210可以制造成专用集成电路(ASIC)。

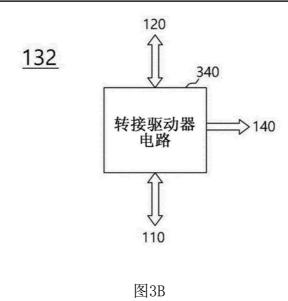

[0026] 图3A和图3B为图示了图1中所示的第二驱动电路132的示例的示图。参见图3A,第二驱动电路132可以包括:第一转接驱动器310、第二转接驱动器320和第三转接驱动器330。

第一转接驱动器310可以电耦接在主机110与第二转接驱动器320和第三转接驱动器330之 间。例如,第一转接驱动器310可以电耦接在主机110与第二转接驱动器320之间,并且电耦 接在主机110与第三转接驱动器330之间。第二转接驱动器320可以电耦接在存储器120与第 一转接驱动器310和第三转接驱动器330之间。例如,第二转接驱动器320可以电耦接在存储 器120与第一转接驱动器310之间,并且电耦接在存储器120与第三转接驱动器330之间。第 三转接驱动器330可以电耦接在第一转接驱动器310和第二转接驱动器320与数据记录电路 140之间。例如,第三转接驱动器330可以电耦接在第一转接驱动器310与数据记录电路140 之间,以及电耦接在第二转接驱动器320与数据记录电路140之间。第一转接驱动器310可以 驱动从主机110传送的信号,并且可以将驱动的信号提供至第二转接驱动器320和第三转接 驱动器330。此外,第一转接驱动器310可以驱动从第二转接驱动器320提供的信号,并且将 驱动的信号提供至主机110。第二转接驱动器320可以驱动从存储器120传送的信号,并且可 以将驱动的信号提供至第一转接驱动器310和第三转接驱动器330。此外,第二转接驱动器 320可以驱动从第一转接驱动器310提供的信号,并且将驱动的信号提供至存储器120。第一 转接驱动器310和第二转接驱动器320中的每个可以为双向转发器。第三转接驱动器330可 以为单向转发器。参见图3B,第二驱动电路132可以包括转接驱动器电路340。转接驱动器电 路340可以制造成耦接在主机110、存储器120和数据记录电路140之间的专用集成电路 (ASIC) 。

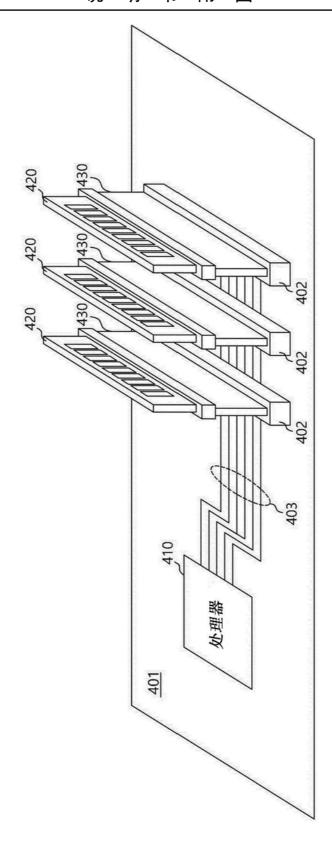

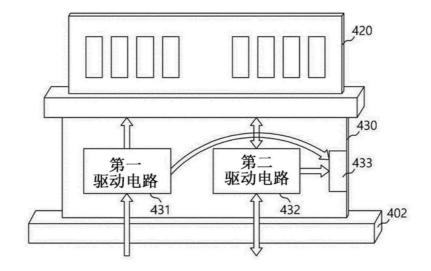

[0027] 图4和图5为图示了根据本发明的一个实施例的电子设备的示例的示图。电子设备可以为计算设备。电子设备可以包括:主板401、处理器410、存储模块420和信号采集卡430。主板401可以为安装有电子设备的部件的基板,并且可以被称为母板。主板401可以包括用于安装处理器410的槽(未示出)和用于安装存储模块420的槽402。主板401可以包括将处理器410与存储模块420电耦接的电线。处理器410可以安装在主板401上。例如,存储模块420可以包括:双列直插存储模块(DIMM)、非注册DIMM(UDIMM)、注册DIMM(RDIMM)、低负载DIMM(LRDIMM)、小外形DIMM(SODIMM)等。

[0028] 通常,存储模块420可以安装入主板401的槽402中。在一个实施例中,信号采集卡430可以取代存储模块420而安装入主板401的槽402中。此外,存储模块420可以安装在信号采集卡430上。存储模块420可以包括在其底端部处的公连接器。信号采集卡430可以包括在其底端部处的公连接器,并且可以通过将信号采集卡430的公连接器插入主板401的槽402中而将信号采集卡430安装在主板401上。信号采集卡430可以包括在其上端部处的母连接器,并且可以通过将存储模块420的公连接器插入信号采集卡430的母连接器中而将存储模块420安装在信号采集卡430上。因此,信号采集卡430可以电耦接在处理器410与存储模块420之间。

[0029] 信号采集卡430可以包括:第一驱动电路431、第二驱动电路432和监控终端433。第一驱动电路431可以驱动从处理器410传送的信号,并且将驱动的信号提供至存储模块420和监控终端433。第二驱动电路432可以驱动从处理器410传送的信号,并且将驱动的信号提供至存储模块420和监控终端433。第二驱动电路432可以驱动从存储模块420传送的信号,并且将驱动的信号提供至处理器410和监控终端433。尽管未示出,但是在实施例中,监控终端433可以经由线缆与数据记录电路电耦接。

[0030] 在电子设备中,信号采集卡430可以电耦接在处理器410与存储模块420之间,并且

监控在处理器410与存储模块420之间传送的信号。第一驱动电路431和第二驱动电路432可以驱动从处理器410传送至存储模块420的信号和从存储模块420传送至处理器410的信号,并且因此能够监控信号。在一个实施例中,当信号被监控时,可以保持在处理器410和存储模块420之间传送的信号的幅度和/或强度。在一个实施例中,处理器410可以包括训练电路(未示出)。为了补偿由第一驱动电路431和第二驱动电路432引起的延迟时间,训练电路可以执行对于处理器410和存储模块420的训练操作(例如,信号时序训练)。

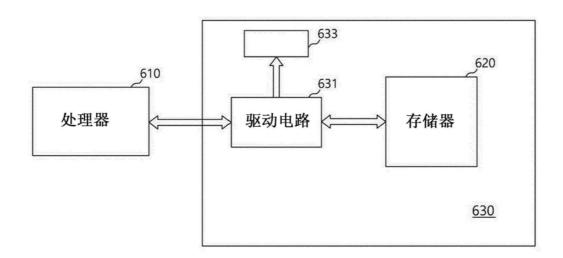

[0031] 图6为图示了根据本发明的一个实施例的电子设备的示例的示图。参见图6,电子设备可以包括:主板601、处理器610、存储器620和信号采集卡630。处理器610可以与存储器620电耦接。在一个实施例中,信号采集卡630可以与处理器610电耦接,并且存储器620可以安装在信号采集卡630上。存储器620可以经由信号采集卡630而与处理器610电耦接。信号采集卡630可以包括驱动电路631和用于安装存储器620的槽。驱动电路631可以包括参照图1至图5所述的驱动电路中的一个或多个。驱动电路631可以驱动从处理器610传送至存储器620的信号,并且将驱动的信号提供至存储器620和监控终端633。驱动电路631可以驱动从存储器620传送至处理器610的信号,并且将驱动的信号提供至处理器610和监控终端633。例如,监控终端633可以经由线缆与数据记录电路电耦接。在一个实施例中,处理器610可以包括训练电路(未示出)。训练电路可以补偿由驱动电路633引起的延迟时间。

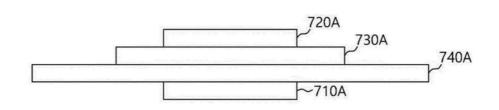

[0032] 图7A和图7B为图示了根据本发明的一个实施例的电子设备的示例的示图。电子设备可以为移动电子设备。参见图7A,电子设备可以包括:处理器710A、存储模块720A、信号采集卡730A和基板740A。处理器710A可以为应用处理器(AP)。例如,存储模块720A可以安装在基板740A的一侧上,并且处理器710A可以安装在基板740A的另一侧上。在一个实施例中,信号采集卡730A可以安装在基板740A的一侧上,而存储模块720A可以安装在信号采集卡730A(其安装在基板740A的另一侧上)上。信号采集卡730A可以包括用于安装存储模块720A的槽。信号采集卡730A可以包括参照图1至图6所述的驱动电路和监控终端。驱动电路可以驱动从处理器710A传送至存储模块720A的信号,并且将驱动的信号提供至存储模块720A和监控终端。驱动电路可以驱动从存储模块720A传送至处理器710A的信号,并且将驱动的信号

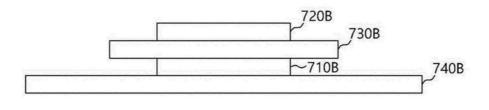

[0033] 如图7B中所示的配置示例与图7A的不同。参见图7B,电子设备可以通过堆叠式封装(P0P)的方式来制造。参见图7B,电子设备可以包括:处理器710B、存储模块720B、信号采集卡730B和基板740B。处理器710B可以安装在基板740B上。信号采集卡730B可以安装在处理器710B上。存储模块720B可以安装在信号采集卡730B上。信号采集卡730B可以包括参照图1至图6所述的驱动电路和监控终端。

[0034] 尽管以上已经描述了某些实施例,但是对于本领域的技术人员将理解的是,所述的实施方案仅仅是示例性的。因此,不应当基于所述的实施例来限定能够采集高速信号的电子系统和电子设备。更确切地说,在结合以上描述和附图时,应当仅根据所附权利要求来限定本文所述的能够采集高速信号的电子系统和电子设备。

9

图2

图3A

图4

图5

图6

图7A

图7B