### (19) **日本国特許庁(JP)**

# (12) 特 許 公 報(B2)

(11)特許番号

特許第6108280号 (P6108280)

(45) 発行日 平成29年4月5日(2017.4.5)

(24) 登録日 平成29年3月17日(2017.3.17)

| (51) Int.Cl. |         |           | FΙ   |       |              |

|--------------|---------|-----------|------|-------|--------------|

| HO1L         | 27/146  | (2006.01) | HO1L | 27/14 | Α            |

| HO4N         | 5/374   | (2011.01) | HO1L | 27/14 | $\mathbf{E}$ |

| HO1L         | 21/8234 | (2006.01) | HO4N | 5/335 | 740          |

| HO1L         | 27/088  | (2006.01) | HO1L | 27/08 | 102C         |

請求項の数 17 (全 12 頁)

(21) 出願番号 特願2014-522369 (P2014-522369) (86) (22) 出願日 平成25年3月8日 (2013.3.8) (86) 国際出願番号 PCT/JP2013/001510 (87) 国際公開番号 W02014/002330 (87) 国際公開日 平成26年1月3日 (2014.1.3) 審査請求日 平成27年12月1日 (2015.12.1) (31) 優先権主張番号 特願2012-144763 (P2012-144763)

(32) 優先日 平成24年6月27日 (2012-14476

(33) 優先権主張国 日本国(JP)

||(73)特許権者 314012076

パナソニック I P マネジメント株式会社 大阪府大阪市中央区城見2丁目1番61号

|(74)代理人 100109210

弁理士 新居 広守

|(74)代理人 100137235

弁理士 寺谷 英作

||(74)代理人 100131417

弁理士 道坂 伸一

||(72)発明者 森 三佳

日本国大阪府門真市大字門真1006番地 パナソニック株式会社内

最終頁に続く

(54) 【発明の名称】 固体撮像装置

### (57)【特許請求の範囲】

### 【請求項1】

二次元状に配置された複数の画素を備え、

前記複数の画素のそれぞれは、

金属電極と、

前記金属電極上に形成された、光を電気信号に変換する光電変換層と、

前記光電変換層上に形成された透明電極と、

前記金属電極と電気的に接続され、前記光電変換層からの電荷を蓄積する電荷蓄積領域と、

前記電荷蓄積領域の電荷量に応じた信号電圧を出力する増幅トランジスタと、

前記電荷蓄積領域の電位をリセットするリセットトランジスタとを備え、

前記リセットトランジスタのゲート酸化膜の膜厚が、前記増幅トランジスタのゲート酸 化膜の膜厚より厚く、

前記リセットトランジスタのオフ時に、前記リセットトランジスタのゲート下に、前記 電荷蓄積領域の導電型を担う多数キャリアと異なる電荷を集めるように、前記リセットト ランジスタのゲートに電圧を印加する、

固体撮像装置。

### 【請求項2】

前記増幅トランジスタのチャネル幅は、前記リセットトランジスタのチャネル幅より広い

請求項1に記載の固体撮像装置。

### 【請求項3】

前記リセットトランジスタのゲート長は、前記増幅トランジスタのゲート長より長い 請求項1または2に記載の固体撮像装置。

(2)

### 【請求項4】

前記複数の画素のそれぞれは、

<u>前記増幅トランジスタが前記信号電圧を出力するタイミングを決定する選択トランジス</u>タを備える、

請求項1から3のいずれか一項に記載の固体撮像装置。

### 【請求項5】

前記選択トランジスタのゲート長は、前記増幅トランジスタのゲート長より短い 請求項4に記載の固体撮像装置。

### 【請求項6】

前記複数の画素は、第1の画素を含む、

請求項4または5に記載の固体撮像装置。

#### 【請求項7】

前記第1の画素内の前記選択トランジスタは、前記第1の画素内の前記増幅トランジスタと活性領域の一部を共有しており、

前記第1の画素内の前記リセットトランジスタの活性領域は、前記第1の画素内の前記 増幅トランジスタの活性領域と電気的に分離されている

請求項6に記載の固体撮像装置。

### 【請求項8】

前記複数の画素は、前記第1の画素と受光面において水平方向に隣接する第2の画素を 含む、

請求項6または7に記載の固体撮像装置。

### 【請求項9】

前記第1の画素内の前記リセットトランジスタは、前記第1の画素内の前記選択トランジスタと前記第2の画素内の前記選択トランジスタとの間に配置されている 請求項8に記載の固体撮像装置。

### 【請求項10】

前記第1の画素内の前記リセットトランジスタは、前記第1の画素内の前記増幅トランジスタと前記第2の画素内の前記増幅トランジスタとの間に配置されている 請求項8に記載の固体撮像装置。

### 【請求項11】

前記複数の画素は、<u>前記</u>第1の画素と受光面において垂直方向に隣接する第2の画素とを含み、

前記第1の画素内の前記選択トランジスタと前記第2の画素内の前記選択トランジスタとは、活性領域を共有する

請求項6または7に記載の固体撮像装置。

### 【請求項12】

<u>前記</u>複数の画素は、<u>前記</u>第1の画素と受光面において垂直方向に隣接する第<u>3</u>の画素とを含み、

前記第1の画素内の前記選択トランジスタと前記第<u>3</u>の画素内の前記選択トランジスタとは、活性領域を共有する

請求項8から10のいずれか一項に記載の固体撮像装置。

### 【請求項13】

前記複数の画素は、第1の画素と、当該第1の画素と受光面において垂直方向に隣接する第2の画素とを含み、

前記第1の画素内の前記増幅トランジスタと前記第2の画素内の前記増幅トランジスタとは、活性領域を共有する

10

20

30

40

請求項1から5のいずれか一項に記載の固体撮像装置。

### 【請求項14】

前記複数の画素は、第1の画素と、当該第1の画素と受光面において垂直方向に隣接する第2の画素とを含み、

前記第1の画素内の前記リセットトランジスタと前記第2の画素内の前記リセットトランジスタとは、活性領域を共有する

請求項1から5のいずれか一項に記載の固体撮像装置。

### 【請求項15】

前記リセットトランジスタのゲート酸化膜の膜厚は、4 nm~13 nmの範囲であり、前記増幅トランジスタのゲート酸化膜の膜厚は、3 nm~6 nmの範囲である 請求項1から14のいずれか一項に記載の固体撮像装置。

10

#### 【請求項16】

前記固体撮像装置は、さらに、

前記電荷蓄積領域の上部に、表面注入領域を備え、

前記電荷蓄積領域は第1導電型であり、前記表面注入領域は第2導電型である 請求項1から15のいずれか一項に記載の固体撮像装置。

### 【請求項17】

前記固体撮像装置は、さらに、

前記透明電極に電圧を印加する電源回路を備え、

前記電源回路を構成するトランジスタのゲート酸化膜の膜厚は、前記リセットトランジ スタのゲート酸化膜の膜厚より厚い

請求項1から16のいずれか一項に記載の固体撮像装置。

### 【発明の詳細な説明】

#### 【技術分野】

### [0001]

本発明は、画素がアレイ状に配列された固体撮像装置に関する。

### 【背景技術】

### [0002]

光電変換可能な材料を半導体基板上方に積層し、微細化された画素においても大きな飽 和電荷量を実現できる積層型センサが提案されている。

30

20

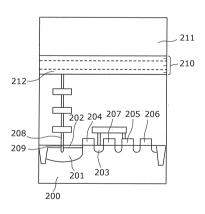

#### [0003]

図5は、特許文献1に記載された積層型イメージセンサの画素断面図である。同図に示されるように、半導体基板200上方に光電変換層210、透明電極211、画素電極212が形成されている。また、半導体基板200内には、出力回路を構成する複数の不純物領域が形成されている。上記不純物領域には、光電変換層210内で発生した電荷を積するn型の電荷蓄積部201と、電荷蓄積部201の上部に、半導体基板200の表面欠陥起因のリークを低減するためのp型の表面注入領域202が形成されている。また、電荷蓄積部201に蓄積された電荷を信号線に出力するため、浮遊拡散部203に電活を電圧に変換するため増幅トランジスタ205のゲートに接続され、浮遊拡散部203には、信号線へ出力する画素を選択するため選択トランジスタ206が形成されている。また、浮遊拡散部203の電位をリセットするため、リセットトランジスタ207が形成されている。また、光電変換層210内で発生した光電荷を電荷蓄積部201へ伝送するため、コンタクト208が設けられており、コンタクト抵抗を下げるため高不純物濃度のn型のコンタクト注入領域209が形成されている。

【先行技術文献】

### 【特許文献】

[0004]

【特許文献 1 】特開 2 0 0 9 - 1 6 4 6 0 4 号公報

### 【発明の概要】

#### 【発明が解決しようとする課題】

### [0005]

半導体基板200表面のコンタクト208近傍では、p型の表面注入領域202とn型のコンタクト注入領域209によりpn接合が形成される。このpn接合のリーク電流は接合部の電界強度に依存し、接合部でのリーク電流を低減するためには、表面注入領域202の不純物濃度を一定以上に高くできない。

#### [0006]

しかしながら、表面注入領域202は、そもそも、半導体基板200の表面欠陥、特に加工時に欠陥が誘発されやすいゲート端近傍での欠陥起因のリーク電流を低減するために設けられおり、この不純物濃度を低くすると、欠陥起因のリーク電流を十分に抑制することが出来ない。

[0007]

本発明は、上記課題に鑑み、リーク電流が抑制された高感度な積層型固体撮像装置を提供することを目的とする。

### 【課題を解決するための手段】

#### [00008]

上記課題を解決するために、本発明に係る固体撮像装置は、二次元状に配置された複数の画素を備え、前記複数の画素のそれぞれは、金属電極と、前記金属電極上に形成された、光を電気信号に変換する光電変換層と、前記光電変換層上に形成された透明電極と、前記金属電極と電気的に接続され、前記光電変換層からの電荷を蓄積する電荷蓄積領域と、前記電荷蓄積領域の電荷量に応じた信号電圧を出力する増幅トランジスタと、前記電荷蓄積領域の電位をリセットするリセットトランジスタとを備え、前記リセットトランジスタのゲート酸化膜の膜厚が、前記増幅トランジスタのゲート酸化膜の膜厚より厚いことを特徴とする。

### [0009]

上記構成によれば、高い電圧をリセットトランジスタのゲート電極に印加することができ、ゲート端近傍に表面注入領域を担う電荷を集めて、表面注入領域の電位を安定させることができ、リーク電流を抑制できる。

### 【発明の効果】

### [0010]

本発明に係る固体撮像装置によれば、電荷蓄積部のリーク電流を低減するとともに、 1 / f ノイズを低減でき、高感度(S / N)の固体撮像装置を実現することができる。

### 【図面の簡単な説明】

### [0011]

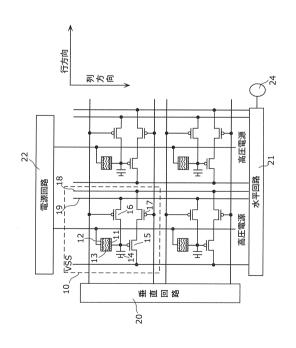

- 【図1】図1は、実施の形態に係る固体撮像装置の一例を示す回路図である。

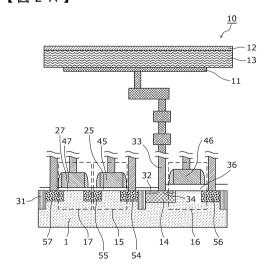

- 【図2A】図2Aは、実施の形態に係る画素の構成の一例を示す断面図である。

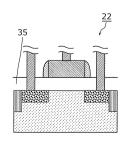

- 【図2B】図2Bは、実施の形態に係る電源回路の構成の一例を示す断面図である。

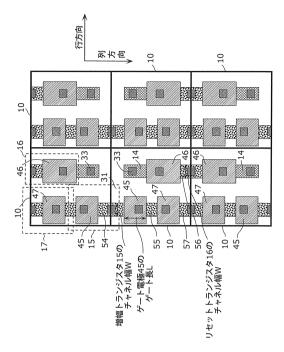

- 【図3】図3は、実施の形態1に係る固体撮像装置の画素平面図である。

- 【図4】図4は、実施の形態2に係る固体撮像装置の画素平面図である。

- 【図5】図5は、特許文献1に記載された積層型センサの画素断面図である。

【発明を実施するための形態】

### [0012]

以下、実施の形態について、図面に基づいて詳細に説明する。なお、本発明は、以下の実施の形態に限定されるものではない。また、本発明の効果を奏する範囲を逸脱しない範囲で、適宜変更は可能である。さらに、他の実施の形態との組み合わせも可能である。

### [0013]

### (実施の形態1)

まず、実施の形態 1 に係る固体撮像装置の画素回路構成の一例について、図 1 を用いて 説明する。

### [0014]

20

10

30

図1は、実施の形態に係る固体撮像装置の一例を示す回路図である。同図に記載された 固体撮像装置は、画素10が、二次元状に配列された積層型イメージセンサの一例である 。画素10内には、金属電極11と、金属電極上に形成された、光を電気信号に変換する 光電変換層13と、光電変換層13上に形成された透明電極12と、光電変換層13から の電荷を蓄積する電荷蓄積領域(フローティングディフュージョン)14と、電荷蓄積領 域14の電荷量に応じた信号電圧を出力する増幅トランジスタ15と、電荷蓄積領域の電 位をリセットするリセットトランジスタ16と、選択トランジスタ17とを備える。

### [0015]

光電変換層13は、入射光を光電変換することで、信号電荷を生成する。光電変換層13によって生成された信号電荷は、電荷蓄積領域14に金属電極11を介して転送される。本実施の形態では、電荷を転送するために、透明電極12に正バイアス10V程度を印加している。

### [0016]

電荷蓄積領域14に転送された電荷は、増幅トランジスタ15によって増幅される。選択トランジスタ17がオン状態になると、増幅トランジスタ15によって増幅された信号が出力信号線18へ出力される。

### [0017]

リセットトランジスタ16を動作させた際に生じる熱(kTC)ノイズを除去するため、出力信号線18からフィードバック配線19を介して逆位相のノイズ成分を電荷蓄積領域14へ戻し、熱(kTC)ノイズを相殺している。

### [0018]

垂直回路20から画素内の各トランジスタを制御する信号を入力し、水平回路21を介して信号端24へ出力している。小型化のため同一チップ内に設けた電源回路22により透明電極12に印加する10V程度の印加電圧を発生させている。

#### [0019]

続いて、実施の形態1に係る固体撮像装置が備える画素10の断面構成の一例について、図2Aを用いて説明する。

#### [0020]

図2Aは、実施の形態に係る画素の構成の一例を示す断面図である。同図に表されたように、本実施の形態に係る固体撮像装置の画素10は、半導体基板に形成されたn型のウエル1と、半導体基板上方に形成され入射した光を光電変換することにより信号電荷を生成する光電変換層13と、光電変換層13を挟み込む金属電極11と透明電極12とを備える。透明電極12は、光電変換層13へ光入射を可能とするためITOまたはZnO等の透明電極が用いられている。

## [0021]

本実施の形態では、半導体基板に形成されたn型のウエル1を用いているが、半導体基板に形成されたp型のウエルであっても良い。その場合、以降で示す不純物の導電型はn型とp型とが入れ替わる。

### [0022]

また、光電変換層13で発生する電荷は、透明電極12に10V程度の正電圧を印加することにより、金属電極11を介してホールを転送し、p型の電荷蓄積領域14に蓄積する。この電荷蓄積領域14は、リセットトランジスタ16の活性領域を兼用しており、リセットトランジスタ16をオンにすると、電荷蓄積領域14の電位がリセットされる。

### [0023]

さらに、この電荷蓄積領域14は、n型あるいはSTI(Shallow Trench Isolation)からなる分離領域31により、画素内の増幅トランジスタ15あるいは選択トランジスタ17と電気的に分離されている。

### [0024]

また、この電荷蓄積領域14の上部に、n型の表面注入領域32を設けて、ウエル1表面に多くある欠陥によって生じるリーク電流の電荷蓄積領域14への漏れ込みを抑制して

10

20

30

40

いる。

### [0025]

また、光電変換層 1 3 からの電荷を電荷蓄積領域 1 4 へ転送するためのコンタクト3 3 と半導体基板との界面に、コンタクト抵抗を低減するコンタクト注入領域 3 4 を設けている。また表面注入領域 3 2 は、リセットトランジスタ 1 6 のゲート端近傍まで拡張されている。

#### [0026]

このリセットトランジスタ16のゲート酸化膜36の膜厚は、増幅トランジスタ15のゲート酸化膜25の膜厚より厚い。この構成により、リセットトランジスタ16に高いゲート電圧を印加することが可能となる。このため、リセットトランジスタ16のオフ時には、ゲート下に表面注入領域32を担う多数キャリアと同じ電子を集めることが可能となり、表面注入領域32の電位を安定させることができ、リーク電流を低減できる。本実施の形態では、例えば、リセットトランジスタ16のオン時の電圧は0V程度、オフ時の電圧は3.8V程度としている。

### [0027]

また、増幅トランジスタ15のゲート酸化膜25を薄く形成することにより、1/fノイズを抑制することが出来る。

### [0028]

また、選択トランジスタ17のゲート酸化膜27の膜厚を、増幅トランジスタ15のゲート酸化膜25の膜厚と同じ厚さにしている。この構成により、選択トランジスタ17をオンにする際のゲート印加電圧を低減できるので、低消費電力化が促進される。なお、上記の同じ厚さとは、略同一の厚さ、すなわち製造上の誤差を含む。

### [0029]

本実施の形態では、増幅トランジスタ15のゲート酸化膜25の膜厚は、例えば、約3nm~6nmの範囲である。またリセットトランジスタ16のゲート酸化膜36の膜厚は、例えば、約4nm~13nmである。また、選択トランジスタ17のゲート酸化膜27の膜厚は、例えば、約3nm~6nmの範囲である。

#### [0030]

図2 B は、実施の形態に係る電源回路の構成の一例を示す断面図である。透明電極 1 2 に電圧を印加する電源回路 2 2 を構成するトランジスタのゲート酸化膜 3 5 の膜厚は、リセットトランジスタ 1 6 のゲート酸化膜 3 6 の膜厚より厚い。この構成により、電源回路 2 2 を構成するトランジスタに高電圧を印加することが可能となり、光電変換層 1 3 で生成した信号電荷を電荷蓄積領域 1 4 へ伝送することが出来る。このゲート酸化膜 3 5 の膜厚は、透明電極 1 2 に 1 0 V程度を印加させるために、約 1 5 ~ 2 5 n m の範囲であることが好ましい。

### [0031]

本実施の形態において、例えば、ウエル電圧を約2.8Vとし、リセットトランジスタ16のゲート電圧を3.8V程度にした際、リーク電流が数10%改善される。

### [0032]

また、電荷蓄積領域14と接続された増幅トランジスタ15のゲート電極45の電位が、リセットトランジスタ16によりリセット電位となる際に、ウエル1と増幅トランジスタ15のゲート電極45との間の耐圧が確保できる程度まで、増幅トランジスタ15のゲート酸化膜25は薄膜化されている。これにより、リーク電流以外のノイズ成分である1/fノイズN1/fは、下記の理論式から明確なように低減される。ここで、Goxは、ゲート酸化膜の膜厚、Wはチャネル幅、およびLはゲート長である。

### [0033]

30

20

10

N1/f

$$\propto \sqrt{\frac{Gox}{W \cdot L}}$$

(式 1)

#### [0034]

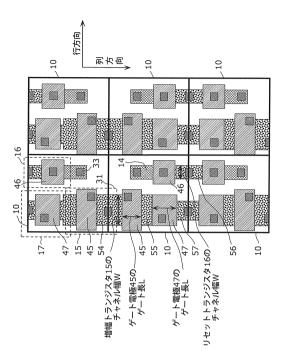

次に、図2Aの断面構造を実現する複数の画素10の第1の平面構成を表す図を、図3 (上層の配線は図示せず)を用いて説明する。

(7)

#### [0035]

図3は、実施の形態1に係る固体撮像装置の画素平面図である。図3に示すように、画素内の電荷蓄積領域14のコンタクト33は、信号電荷が混合されるため隣接する画素10と共有できない。コンタクト33以外のコンタクトは、信号電荷の混合という問題は生じないので、隣接する画素10と共有することが可能であり、受光面において垂直方向に隣接する画素10とコンタクトを共有している。これにより、一画素あたりのコンタクト占有面積率が低下するため、画素サイズの微細化が可能となる。

### [0036]

また、増幅トランジスタ15と受光面において垂直方向に隣接する画素10の増幅トランジスタ15とは活性領域54を共有する。この構成により、上下隣接する画素10でコンタクトを共有するため、増幅トランジスタ15のゲート長を確保でき、ノイズ成分の一つである1/fノイズを低減できる。

### [0037]

また、選択トランジスタ17と受光面において垂直方向に隣接する画素10の選択トランジスタ17とは活性領域57を共有する。この構成により、上下画素でコンタクトを共有するため、選択トランジスタ17のゲート長を確保しながら、活性領域を共有している増幅トランジスタ15のゲート長を確保でき、ノイズ成分の一つである1/fノイズを低減できる。

#### [0038]

また、リセットトランジスタ16と受光面において垂直方向に隣接する画素10のリセットトランジスタ16とは活性領域56を共有する。この構成により、上下画素でコンタクトを共有するため、リセットトランジスタ16のゲート長を確保でき、電荷蓄積領域14を活性領域とするリセットトランジスタ16のオン特性を確保できる。

### [0039]

また、リセットトランジスタ16のゲート長は、増幅トランジスタ15のゲート長より 長い。この構成により、増幅トランジスタ15の駆動能力を確保しながら、電荷蓄積領域 14を活性領域とするリセットトランジスタ16のオン特性バラツキ、つまりゲート長に 依存する閾値電圧、ドレイン電流等のバラツキを低減でき、電荷蓄積領域14の電位を安 定化できる。よって、画素間でのリーク特性が一様になり、鮮明な画像を撮像できる。一 方、増幅トランジスタのゲート長を短くし、 L長に反比例し相互コンダクタンスgmが 高くなるため、駆動能力が高くなり高速に信号を出力信号線18に伝達できる。

### [0040]

また、増幅トランジスタ15と選択トランジスタ17とを同じ列に配置している。選択トランジスタ17のゲート電圧によるオンオフ特性を確保しつつゲート長を短くすれば、 増幅トランジスタ15のゲート長を長くでき、式1から1/fノイズも低減できる。

### [0041]

本実施の形態においては、画素 100 セルサイズが  $0.9\mu$  mである場合、増幅トランジスタ 150 が 150 が

10

20

30

40

るセルサイズに対応するゲート長が導き出せることは言うまでもない。

### [0042]

(実施の形態2)

本実施の形態では、図2Aの断面構造を実現する複数の画素10の第2の平面構成を説明する。

#### [0043]

図4は、実施の形態2に係る固体撮像装置の画素平面図である。同図には、図3と同様に、リセットトランジスタ16が分離領域31により増幅トランジスタ15および選択トランジスタ17と分離して形成されている。

### [0044]

図4に示すように、画素内の選択トランジスタ17は、同一画素内の増幅トランジスタ15と活性領域55の一部を共有しており、画素内のリセットトランジスタ16の活性領域56は、同一画素内の増幅トランジスタ15の活性領域55と電気的に分離されている。この構成により、高速駆動性を求められる増幅トランジスタ15および選択トランジスタ17のチャネル幅を広く確保できる。また、リセットトランジスタ16の活性領域の面積を小さくすることで、表面注入領域32と電荷蓄積領域14とのpn接合面積を小さくすることが可能となり、pn接合リークを抑えることが出来る。

#### [0045]

また、リセットトランジスタ16は、同一画素内の選択トランジスタ17と受光面において水平方向に隣接する画素内の選択トランジスタ17との間に配置されている。または、リセットトランジスタ16は、同一画素内の増幅トランジスタ15と受光面において水平方向に隣接する画素内の増幅トランジスタ15との間に配置されていてもよい(図示せず)。この構成により、チャネル幅が狭小なリセットトランジスタ16と、チャネル幅が広い増幅トランジスタ15および選択トランジスタ17とのチャネル方向を並行に同一画素内に配置でき、ノイズ特性を確保しながら、画素サイズの微細化が容易にできる。

### [0046]

また、増幅トランジスタ15のチャネル幅は、リセットトランジスタ16のチャネル幅よりも広い。式1から、増幅トランジスタ15のチャネル幅を拡大すると、増幅トランジスタ15の1/fノイズを低減できる。他方、リセットトランジスタ16のチャネル幅を縮小することで、リセットトランジスタ16の活性領域を兼ねた電荷蓄積領域14のpn接合面積を小さくでき、1/fノイズとリーク電流を低減でき、信号に対するノイズ成分を低減した高感度な画像が得られる。また、増幅トランジスタ15の動作電流を確保するためトランジスタチャネル幅を拡大でき高速駆動が可能であり、ノイズ成分の一つである1/fノイズも低減できる。

### [0047]

本実施の形態においては、画素のセルサイズが  $0.9\mu$ mである場合、増幅トランジスタ 1.50 チャネル幅は、例えば、約  $0.1\sim0.5\mu$ mの範囲である。リセットトランジスタ 1.60 チャネル幅は、例えば、約  $0.1\sim0.2\mu$ mの範囲である。選択トランジスタ 1.70 チャネル幅は、例えば、約  $0.1\sim0.5\mu$ mの範囲である。画素のセルサイズが異なる場合でも、セルサイズの  $0.9\mu$ mからの変更比率によって、異なるセルサイズに対応するチャネル幅が導き出せることは言うまでもない。

### [0048]

また、選択トランジスタ17のゲート電極47のゲート長は、増幅トランジスタ15ゲート電極45のゲート長より短い。これにより、増幅トランジスタ15のゲート長を確保でき、ノイズ成分の一つである1/fノイズを低減できる。

### [0049]

以上の構成により、リーク電流および1/fノイズが低減された固体撮像装置を製造することができる。また、1μm程度の微細画素サイズを実現でき、高速電荷読み出しも可能となる。

### [0050]

10

20

30

以上、本発明に係る固体撮像装置について、実施の形態1および2に基づいて説明した が、本発明は、実施の形態1および2に限定されるものではない。本発明の趣旨を逸脱し ない限り、当業者が思いつく各種変形を実施の形態1および2に施したものや、異なる実 施の形態における構成要素を組み合わせて構築される形態も、本発明の範囲内に含まれる

### [0051]

また、上記実施の形態に係る固体撮像装置は、典型的には集積回路であるLSIとして 実現される。これらは個別に1チップ化されてもよいし、一部又は全てを含むように1チ ップ化されてもよい。

### [0052]

また、集積回路化はLSIに限るものではなく、専用回路又は汎用プロセッサで実現し てもよい。LSI製造後にプログラムすることが可能なFPGA(Field Prog rammable Gate Array)、又はLSI内部の回路セルの接続や設定を 再構成可能なリコンフィギュラブル・プロセッサを利用してもよい。

### [0053]

また、上記断面図等において、各構成要素の角部および辺を直線的に記載しているが、 製造上の理由により、角部および辺が丸みをおびたものも本発明に含まれる。

### [0054]

また、上記で用いた数字は、全て本発明を具体的に説明するために例示するものであり 、本発明は例示された数字に制限されない。また、表面注入領域32、コンタクト注入領 域34、活性領域54~57等の不純物領域等のn型およびp型等は、本発明を具体的に 説明するために例示するものであり、これらを反転し、同等の結果を得ることも可能であ る。また、上記で示した各構成要素の材料は、全て本発明を具体的に説明するために例示 するものであり、本発明は例示された材料に制限されない。また、構成要素間の接続関係 は、本発明を具体的に説明するために例示するものであり、本発明の機能を実現する接続 関係はこれに限定されない。

### [0055]

また、上記説明では、MOSトランジスタを用いた例を示したが、他のトランジスタを 用いてもよい。

### 【産業上の利用可能性】

#### [0056]

本発明の固体撮像装置は、積層型構造で低ノイズ特性を有する微細画素サイズの固体撮 像装置に適用できる。

### 【符号の説明】

### [0057]

- ウエル 1

- 1 0 画素

- 1 1 金属電極

- 1 2 诱明雷極

- 1 3 光電変換層

- 1 4 電荷蓄積領域

- 1 5 増幅トランジスタ

- 1 6 リセットトランジスタ

- 1 7 選択トランジスタ

- 1 8 出力信号線

- 1 9 フィードバック配線

- 2 0 垂直回路

- 2 1 水平回路

- 2 2 電源回路

- 2 4 信号端

20

10

30

50

- 25、27、35、36 ゲート酸化膜

- 3 1 分離領域

- 32 表面注入領域

- 33 コンタクト

- 34 コンタクト注入領域

- 45 増幅トランジスタのゲート電極

- 46 リセットトランジスタのゲート電極

- 47 選択トランジスタのゲート電極

- 5 4 、 5 5 、 5 6 、 5 7 活性領域

# 【図1】

## 【図2A】

【図2B】

【図3】

【図4】

【図5】

### フロントページの続き

(72)発明者 大槻 浩久

日本国富山県魚津市東山800番地 パナソニック・タワージャズセミコンダクター株式会社内

(72)発明者 大森 愛幸

日本国富山県魚津市東山800番地 パナソニック・タワージャズセミコンダクター株式会社内

(72)発明者 佐藤 好弘

日本国大阪府門真市大字門真1006番地 パナソニック株式会社内

(72)発明者 宮川 良平

日本国富山県魚津市東山800番地 パナソニック・タワージャズセミコンダクター株式会社内

### 審査官 安田 雅彦

(56)参考文献 国際公開第2012/005010(WO,A1)

特開2008-124395(JP,A)

特開2011-216728(JP,A)

特開2006-196884(JP,A)

特開2012-060076(JP,A)

(58)調査した分野(Int.CI., DB名)

H01L 27/14-148

H 0 4 N 5 / 3 3 5 - 3 7 8

H01L 27/088-092

H01L 21/8234-8238