### (19) **日本国特許庁(JP)**

# (12) 特 許 公 報(B2)

(11)特許番号

特許第6863423号 (P6863423)

(45) 発行日 令和3年4月21日(2021.4.21)

(24) 登録日 令和3年4月5日(2021.4.5)

| (51) Int.Cl. |       |           | FΙ   |       |      |

|--------------|-------|-----------|------|-------|------|

| HO1L         | 21/02 | (2006.01) | HO1L | 21/02 | В    |

| HO1L         | 27/12 | (2006.01) | HO1L | 27/12 | В    |

| HO1L         | 21/20 | (2006.01) | HO1L | 21/20 |      |

| СЗОВ         | 29/06 | (2006.01) | C30B | 29/06 | 502Z |

請求項の数 8 (全 12 頁)

最終頁に続く

| (21) 出願番号<br>(22) 出願日          | 令和1年8月6日 (2019.8.6)                                                         | (73) 特許権者 | 6 000190149<br>信越半導体株式会社                                           |

|--------------------------------|-----------------------------------------------------------------------------|-----------|--------------------------------------------------------------------|

| (65) 公開番号<br>(43) 公開日<br>審査請求日 | 特開2021-27186 (P2021-27186A)<br>令和3年2月22日 (2021.2.22)<br>令和3年2月1日 (2021.2.1) | (74) 代理人  | 東京都千代田区大手町二丁目2番1号<br>100102532<br>弁理士 好宮 幹夫                        |

| 早期審査対象出願                       | ,                                                                           | (74) 代理人  | 100194881<br>弁理士 小林 俊弘                                             |

|                                |                                                                             | (72) 発明者  | 萩本 和徳<br>群馬県安中市磯部二丁目13番1号 信越                                       |

|                                |                                                                             | (72) 発明者  | 半導体株式会社 半導体磯部研究所内<br>後藤 正三郎<br>東京都千代田区大手町二丁目2番1号 信<br>越半導体株式会社 本社内 |

|                                |                                                                             | 審査官       | 平野 崇                                                               |

(54) 【発明の名称】電子デバイス用基板およびその製造方法

# (57)【特許請求の範囲】

### 【請求項1】

シリコン単結晶の接合基板上に窒化物半導体膜が形成された電子デバイス用基板であって、

前記接合基板は、少なくとも、シリコン単結晶からなるベースウェーハ上にシリコン単結晶からなるボンドウェーハを接合した基板であって、

前記ベースウェーハは、抵抗率が 0 . 1 cm以下、結晶方位が < 1 0 0 > の C Z シリコンからなり、

前記ボンドウェーハは、結晶方位が < 1 1 1 > <u>、抵抗率が 0 . 1 c m以下の C Z シリ</u>コン基板であることを特徴とする電子デバイス用基板。

#### 【請求項2】

<u>シリコン単結晶の接合基板上に窒化物半導体膜が形成された電子デバイス用基板であっ</u>て、

<u>前記接合基板は、少なくとも、シリコン単結晶からなるベースウェーハ上にシリコン単</u>結晶からなるボンドウェーハを接合した基板であって、

\_\_\_ 前記ベースウェーハは、抵抗率が 0 . 1 c m 以下、結晶方位が < 1 0 0 > の C Z シリコンからなり、

<u>前記ボンドウェーハは、結晶方位が<111></u>、抵抗率が1000 cm以上、窒素濃度が1×10<sup>14</sup> a t o m s / c m  $^3$  以上である C Z シリコン基板であることを特徴とする電子デバイス用基板。

#### 【請求項3】

<u>シリコン単結晶の接合基板上に窒化物半導体膜が形成された電子デバイス用基板であっ</u>て、

<u>前記接合基板は、少なくとも、シリコン単結晶からなるベースウェーハ上にシリコン単</u>結晶からなるボンドウェーハを接合した基板であって、

<u>前記ベースウェーハは、抵抗率が0.1 cm以下、結晶方位が<100>のCZシリ</u>コンからなり、

<u>前記ボンドウェーハは、結晶方位が<1111></u>、抵抗率が1000 cm以上、窒素濃度8 x 10 <sup>14</sup> a t o m s / c m <sup>3</sup> 以上のF Z シリコン基板であることを特徴とす<u>る電</u>子デバイス用基板。

#### 【請求項4】

前記接合基板は、前記ベースウェーハと前記ボンドウェーハとが $SiO_2$ 膜を介して接合されたものであることを特徴とする請求項1から請求項3のいずれか一項に記載の電子デバイス用基板。

### 【請求項5】

シリコン単結晶基板上に窒化物半導体膜を形成する電子デバイス用基板の製造方法であって、

シリコン単結晶からなるベースウェーハ上にシリコン単結晶からなるボンドウェーハを 接合して接合基板とする工程と、

前記接合基板の前記ボンドウェーハ上に窒化物半導体をエピタキシャル成長させる工程とを含み、

前記ベースウェーハとして、抵抗率が 0 . 1 cm以下、結晶方位が < 1 0 0 > の C Z シリコンからなるものを用い、

前記ボンドウェーハとして、結晶方位が<111><u>、抵抗率が0.1 cm以下のCZ</u>シリコン基板を用いることを特徴とする電子デバイス用基板の製造方法。

#### 【請求項6】

<u>シリコン単結晶基板上に窒化物半導体膜を形成する電子デバイス用基板の製造方法であ</u>って、

<u>シリコン単結晶からなるベースウェーハ上にシリコン単結晶からなるボンドウェーハを</u>接合して接合基板とする工程と、

<u>前記接合基板の前記ボンドウェー八上に窒化物半導体をエピタキシャル成長させる工程</u>とを含み、

前記ベースウェーハとして、抵抗率が 0.1 cm以下、結晶方位が < 100 > のCZ シリコンからなるものを用い、

<u>前記ボンドウェーハとして、結晶方位が<111></u>、抵抗率が1000 cm以上、窒素濃度が $1 \times 10^{-1/4}$  a toms / cm<sup>3</sup>以上であるCZシリコン基板を用いることを特徴とする電子デバイス用基板の製造方法。

#### 【請求項7】

<u>シリコン単結晶基板上に窒化物半導体膜を形成する電子デバイス用基板の製造方法であ</u>って、

<u>シリコン単結晶からなるベースウェーハ上にシリコン単結晶からなるボンドウェーハを</u>接合して接合基板とする工程と、

<u>前記接合基板の前記ボンドウェー八上に窒化物半導体をエピタキシャル成長させる工程</u>とを含み、

前記ベースウェーハとして、抵抗率が 0 . 1 cm以下、結晶方位が < 1 0 0 > の C Z シリコンからなるものを用い、

<u>前記ボンドウェーハとして、結晶方位が<1111></u>、抵抗率が1000 cm以上、窒素濃度8×10<sup>14</sup> a t o m s / c m  $^3$  以上のF Z シリコン基板を用いることを特徴とする電子デバイス用基板の製造方法。

### 【請求項8】

40

30

10

20

前記接合基板とする工程において、前記ベースウェーハと前記ボンドウェーハとを S i O  $_2$  膜を介して接合することを特徴とする請求項 $_5$  から請求項 $_7$  のいずれか一項に記載の電子デバイス用基板の製造方法。

#### 【発明の詳細な説明】

#### 【技術分野】

### [0001]

本発明は、電子デバイス用基板およびその製造方法に関する。

#### 【背景技術】

#### [00002]

GaNやAlNをはじめとする窒化物半導体は、2次元電子ガスを用いた高電子移動度トランジスタ(HEMT)や高耐圧電子デバイスの作製に用いることができる。

#### [0003]

これらの窒化物半導体を基板上に成長させた窒化物ウェーハを製作することは難しく、基板としては、サファイア基板やSiC基板が用いられている。しかし、大口径化や基板のコストを抑えるために、シリコン基板上への気相成長によるエピタキシャル成長が用いられている。シリコン基板上への気相成長によるエピタキシャル成長膜の作製は、サファイア基板やSiC基板に比べて大口径の基板が使用できるのでデバイスの生産性が高く、放熱性の点で有利である。ただし、格子定数差や熱膨張係数差による応力により、反りの増大や塑性変形が起こりやすく、成長条件や緩和層による応力低減が行われている。また、高周波用基板には、高抵抗シリコン基板を用いる必要がある。

#### [0004]

反り対策として特許文献 1 では、エピタキシャル層 A 1 N / S i ( 1 0 0 0 0 c m以上 ) / S i ( 1 0 0 0 c m以下 ) として、高抵抗基板を低抵抗基板と接合している。また、特許文献 2 では、エピタキシャル層 A 1 N / S i ( C Z 低抵抗 ) / S i ( F Z 高抵抗 ) として、低抵抗 C Z 基板を高抵抗 F Z 基板と接合している。

### [0005]

電子デバイス作製用の基板(高耐圧用・RF(高周波)用)は、反り量が 50  $\mu$  m 以下であることが望ましいが、従来技術では、未だ反り量が 50  $\mu$  m を超えてしまう課題があった。

### 【先行技術文献】

### 【特許文献】

### [0006]

【特許文献1】国際公開第2011/016219号

【特許文献2】特開2014-19226号公報

### 【発明の概要】

【発明が解決しようとする課題】

### [0007]

本発明は、上記課題を解決するためになされたもので、反りを抑制したシリコン基板上に窒化物半導体が形成された高耐圧用あるいは高周波用の電子デバイス用基板及びその製造方法を提供することを目的とする。

### 【課題を解決するための手段】

### [0008]

上記課題を解決するために、本発明は、シリコン単結晶の接合基板上に窒化物半導体膜が形成された電子デバイス用基板であって、

前記接合基板は、少なくとも、シリコン単結晶からなるベースウェーハ上にシリコン単結晶からなるボンドウェーハを接合した基板であって、

前記ベースウェーハは、抵抗率が 0 . 1 cm以下、結晶方位が < 1 0 0 > の C Z シリコンからなり、

前記ボンドウェーハは、結晶方位が<111>のものであることを特徴とする電子デバー

10

20

30

50

40

10

20

30

40

50

イス用基板を提供する。

### [0009]

このような電子デバイス用基板であれば、抵抗率が 0 . 1 cm以下の、結晶方位が < 1 0 0 > の C Z シリコンからなる、硬いベースウェーハを含むため、電子デバイス用基板の反りが抑制されたものとすることができる。また、そのベースウェーハの上に結晶方位が < 1 1 1 > のボンドウェーハが接合されたものであるため、良好な窒化物半導体膜が形成されたものとなる。更に、結晶方位が < 1 0 0 > と < 1 1 1 > という異なったウェーハを接合することでお互いの劈開方向が異なることとなり、電子デバイス用基板が割れにくくなる。また、ベースウェーハの結晶方位を < 1 0 0 > とすることで、インゴットの成長途中での多結晶化が抑制されたものとすることができる。これらのことから、高耐圧用あるいは高周波用の電子デバイス用基板として最適なものとなる。

[0010]

このうち、前記ボンドウェーハは、抵抗率が 0 . 1 cm以下の C Z シリコン基板であることが好ましい。

#### [0011]

このようなものであれば、更に接合基板の強度を増加させることができる。このような電子デバイス用基板は特に高耐圧デバイス用として適したものとなる。

[0012]

また、前記ボンドウェーハは、抵抗率が 1000 cm以上、窒素濃度が  $1 \times 10^{14}$  atoms / cm  $^3$  以上である C Z シリコン基板であることが好ましい。

[0013]

このようなものであれば、CZシリコン基板のボンドウェーハに窒素がドープされていることで強度が更に増すとともに、高抵抗であるため、特に高周波デバイス用として適したものとなる。

[0014]

また、前記ボンドウェーハは、抵抗率が 1 0 0 0 c m 以上、窒素濃度 8  $\times$  1 0  $^{1}$  4 a t o m s / c m  $^{3}$  以上の F Z シリコン基板であることが好ましい。

[0015]

このようなものであれば、FZシリコン基板のボンドウェーハに窒素がドープされていることで強度が更に増すとともに、高抵抗であるため、特に高周波デバイス用として適したものとなる。

[0016]

また、前記接合基板は、前記ベースウェーハと前記ボンドウェーハとが $SiO_2$ 膜を介して接合されたものであることが好ましい。

[0017]

このようなものであれば、窒化物半導体膜による応力を緩和することができ、より厚い 窒化物半導体膜を形成することができる。

[0018]

また本発明は、シリコン単結晶基板上に窒化物半導体膜を形成する電子デバイス用基板の製造方法であって、

シリコン単結晶からなるベースウェーハ上にシリコン単結晶からなるボンドウェーハを 接合して接合基板とする工程と、

前記接合基板の前記ボンドウェーハ上に窒化物半導体をエピタキシャル成長させる工程とを含み、

前記ベースウェーハとして、抵抗率が 0 . 1 cm以下、結晶方位が < 1 0 0 > の C Z シリコンからなるものを用い、

前記ボンドウェーハとして、結晶方位が<111>のものを用いることを特徴とする電子デバイス用基板の製造方法を提供する。

[0019]

このような電子デバイス用基板の製造方法であれば、抵抗率が 0 . 1 c m 以下、結晶

方位が < 1 0 0 > の C Z シリコンからなる、硬いベースウェーハを使用するので、電子デバイス用基板の反りが抑制され、そのベースウェーハの上に結晶方位が < 1 1 1 > のボンドウェーハが接合されるので、良好な窒化物半導体膜を形成することができる。更に、結晶方位が < 1 0 0 > と < 1 1 1 > という異なったウェーハを接合することでお互いの劈開方向が異なることとなり、製造された電子デバイス用基板が割れにくくなる。また、ベースウェーハの結晶方位を < 1 0 0 > とすることで、インゴットの成長途中での多結晶化が抑制されたものとすることができる。このため、高耐圧用あるいは高周波用の電子デバイス用基板として最適なものを製造することができる。

[0020]

このとき、前記ボンドウェーハとして、抵抗率が 0 . 1 cm以下の C Z シリコン基板を用いることが好ましい。

[0021]

このような製造方法であれば、更に接合基板の強度を増加させることができる。このような方法により製造された電子デバイス用基板は、特に高耐圧デバイス用として適したものとすることができる。

[0022]

また、前記ボンドウェーハとして、抵抗率が 1000 cm以上、窒素濃度が  $1 \times 10$  14 atoms  $1 \times 10$  cm 3 以上である  $1 \times 10$  とが好ましい。

[0023]

このような方法により製造された電子デバイス用基板であれば、CZシリコン基板のボンドウェーハに窒素がドープされていることで強度が更に増すとともに、高抵抗であるため、特に高周波デバイス用として適したものとすることができる。

[0024]

また、前記ボンドウェーハとして、抵抗率が 1000 cm以上、窒素濃度  $8 \times 10^{-1}$  4 atoms / cm 3 以上の F Z シリコン基板を用いることが好ましい。

[0025]

このような方法により製造された電子デバイス用基板であれば、FZシリコン基板のボンドウェーハに窒素がドープされていることで強度が更に増すとともに、高抵抗であるため、特に高周波デバイス用として適したものとすることができる。

[0026]

また、前記接合基板とする工程において、前記ベースウェーハと前記ボンドウェーハとをSiO,膜を介して接合することが好ましい。

**[** 0 0 2 7 **]**

このような方法により製造された電子デバイス用基板であれば、窒化物半導体膜による 応力を緩和することができ、より厚い窒化物半導体膜を形成することができる。

【発明の効果】

[0028]

このような電子デバイス用基板及びその製造方法であれば、抵抗率が 0 . 1 cm以下、結晶方位が < 1 0 0 > C Z シリコンからなる、硬いベースウェーハを含むため、電子デバイス用基板の反りが抑制されたものとすることができる。また、そのベースウェーハの上に結晶方位が < 1 1 2 のボンドウェーハが接合されたものであるため、良好な窒化物半導体膜が形成されたものとなる。更に、結晶方位が < 1 0 0 > と < 1 1 1 > という異なったウェーハを接合することでお互いの劈開方向が異なることとなり、電子デバイス用基板が割れにくくなる。また、ベースウェーハの結晶方位を < 1 0 0 > とすることで、インゴットの成長途中での多結晶化が抑制されたものとなり、安価に製造することができる。このため、高耐圧用あるいは高周波用の電子デバイス用基板として最適なものとなる。

【図面の簡単な説明】

[0029]

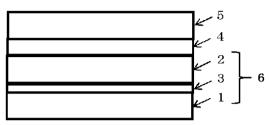

【図1】本発明の電子デバイス用基板を示す概念図である。

【発明を実施するための形態】

50

10

20

30

#### [0030]

以下、本発明について詳細に説明するが、本発明はこれらに限定されるものではない。

#### [0031]

上述したように高耐圧・高周波用電子デバイス用基板では、デバイス特性を向上させるため、エピタキシャル層を厚く積むと、熱膨張係数の違いにより、ウェーハに反りが発生するという問題がある。この課題に対し、本発明者らが鋭意検討を重ねたところ、電子デバイス用基板の反りを抑制するために、結晶方位が < 1 0 0 > で低抵抗率の硬いシリコン基板をベースウェーハとし、その上に結晶方位が < 1 1 1 > のシリコン基板を接合することで窒化物半導体膜を良好に形成させることができることを見出し、本発明を完成させた

10

### [0032]

#### 「電子デバイス用基板 1

本発明は、シリコン単結晶の接合基板上に窒化物半導体膜が形成された電子デバイス用 基板であって、

前記接合基板は、少なくとも、シリコン単結晶からなるベースウェーハ上にシリコン単結晶からなるボンドウェーハを接合した基板であって、

前記ベースウェーハは、抵抗率が 0 . 1 cm以下、結晶方位が < 1 0 0 > の C Z シリコンからなり、

前記ボンドウェーハは、結晶方位が < 1 1 1 > のものであることを特徴とする電子デバイス用基板である。

20

### [0033]

図1に本発明の電子デバイス用基板の概念図を示す。

#### [0034]

図 1 に示すように、本発明の電子デバイス用基板 1 0 はシリコン単結晶からなるベースウェーハ 1 と、シリコン単結晶からなるボンドウェーハ 2 を接合した接合基板 6 と、窒化物からなる窒化物半導体膜(デバイス層) 5 とを含む。このとき、上記の接合基板 6 とデバイス層 5 の間の中間層 4 を含んでもよい。また、図 1 に示すように、ベースウェーハ 1 とボンドウェーハ 2 との間に接着層 3 を有する構造であってもよい。接着層は例えば酸化膜(SiO  $_2$ )とすることができる。

30

### [0035]

### [0036]

また、接合するボンドウェーハ 2 は結晶方位が < 1 1 1 > のウェーハとする。このようにボンドウェーハ 2 の結晶方位が < 1 1 1 > であれば窒化物半導体膜 5 を良好に形成することができ、特に、窒化物系のエピタキシャル層を良好にエピタキシャル成長させることができる。更に結晶方位が < 1 0 0 > と < 1 1 1 > という異なったウェーハを接合することで、お互いの劈開方向が異なり、電子デバイス用基板 1 0 が割れにくくなる。

40

#### [0037]

#### [0038]

### [0039]

また、ボンドウェーハ 2 を抵抗率が 1 0 0 0 c m以上、窒素濃度  $8 \times 1$  0 1 4 a t o m s / c m  $^3$  以上の F Z シリコン基板とすれば、窒素がドープされることで強度が更に増すとともに高抵抗であるため、高周波デバイス用として適したものとなる。

### [0040]

また、ボンドウェーハ 2 の上には中間層 4 が形成されたものとすることができる。中間層 4 は、デバイス層の結晶性改善や応力の制御のために挿入される緩衝層として働く。上記中間層 4 は、窒化物半導体膜 5 と同一の設備で作製できるので、窒化物で作製されたものであることが望ましい。

#### [0041]

#### [0042]

本発明の電子デバイス用基板であれば、抵抗率が 0 . 1 cm以下、結晶方位が < 1 0 0 > の C Z シリコンからなる、硬いベースウェーハを含むため、電子デバイス用基板の反りが抑制されたものとすることができる。また、そのベースウェーハの上に結晶方位が < 1 1 1 > のボンドウェーハが接合されたものであるため、良好な窒化物半導体膜が形成されたものとなる。更に、結晶方位が < 1 0 0 > と < 1 1 1 > という異なったウェーハを接合することでお互いの劈開方向が異なることとなり、電子デバイス用基板が割れにくくなる。また、ベースウェーハの結晶方位を < 1 0 0 > とすることで、インゴットの成長途中での多結晶化が抑制されたものとすることができる。このため、高耐圧用あるいは高周波用の電子デバイス用基板として最適なものとなる。

## [0043]

#### 「電子デバイス用基板の製造方法 ]

また、本発明は、シリコン単結晶基板上に窒化物半導体膜を形成する電子デバイス用基板の製造方法であって、

シリコン単結晶からなるベースウェーハ上にシリコン単結晶からなるボンドウェーハを 接合して接合基板とする工程と、

前記接合基板の前記ボンドウェーハ上に窒化物半導体をエピタキシャル成長させる工程とを含み

前記ベースウェーハとして、抵抗率が 0 . 1 cm以下、結晶方位が < 1 0 0 > の C Z シリコンからなるものを用い、

前記ボンドウェーハとして、結晶方位が < 1 1 1 > のものを用いることを特徴とする電子デバイス用基板の製造方法を提供する。

### [0044]

本発明の製造方法では、シリコン単結晶からなるベースウェーハ上にシリコン単結晶からなるボンドウェーハを接合して接合基板とする。

#### [0045]

このとき、ベースウェーハとして、抵抗率が 0.1 c m以下、結晶方位が < 100 > の C Z シリコンからなるものを用いる。またこのとき、ベースウェーハとして、酸素濃度が  $1\times10^{-18}$  a t o m s / c m  $^3$  (ASTM  $^7$ 79)以下のものを用いることができる

10

20

30

40

0

### [0046]

またこのとき、ボンドウェーハとして、結晶方位が<111>のものを用いる。

#### [0047]

ボンドウェーハとしては、抵抗率が 0.1 cm以下の C Z シリコン基板を用いることができる。このようにボンドウェーハも低抵抗率のものを用いることで更に強度が増加し、反りを更に抑制することができる。また、このようにして製造された電子デバイス用基板は高耐圧用デバイスに好適に用いることができる。またこのとき、ボンドウェーハとして、酸素濃度が  $1\times10^{-18}$  atoms / cm  $^3$  (ASTM  $^7$  79)以下のものを用いることができる。

[0048]

また、ボンドウェーハとして、抵抗率 1000 cm以上、窒素濃度が  $1\times10^{-1}$  4 a toms / cm  $^3$  以上である C Z シリコン基板を用いることもできる。このようにボンドウェーハに窒素がドープされたものを用いることで強度が更に増すとともに高抵抗となるため、高周波デバイス用として適したものとすることができる。またこのとき、ボンドウェーハとして、酸素濃度が  $1\times10^{-1}$  8 a toms / cm  $^3$  (ASTM  $^7$ 79)以下のものを用いることができる。

### [0049]

また、ボンドウェーハとして、抵抗率が 1000 cm以上、窒素濃度  $8\times10^{-14}$  a toms / cm  $^3$  以上の F Z シリコン基板を用いれば、窒素がドープされたものを用いることで強度が更に増すとともに高抵抗となるため、高周波デバイス用として適したものとすることができる。

[0050]

ベースウェーハとボンドウェーハとを接合する方法は特に限定されないが、酸化膜により貼り合わせることが好ましい。また、接合前の酸化膜を薄膜化することで接合後の結合熱処理により、酸化膜の酸素のみを拡散させ、接合界面部で酸化膜の無い構造とすることもできる。このように、シリコン単結晶基板の接着を酸化膜により行うことで、窒化物成長時に加わる応力を緩和することができる。

[0051]

次に、上記のようにして製造した接合基板上に窒化物半導体膜をエピタキシャル成長させる。ここで、窒化物半導体膜の成長前に中間層を形成することができる。窒化物成長時に中間層を形成して適切な緩衝層を入れることで、冷却後には熱膨張係数差と格子定数差による薄膜からの応力を制御することができ、基板を厚くすることで、高温成長中の塑性変形を防ぎ、さらに反りの小さいウェーハを製造することができる。工程を簡単にするため、中間層を窒化物で作製することが望ましい。

[0052]

このような電子デバイス用基板の製造方法であれば、抵抗率が 0 . 1 cm以下、結晶方位が < 1 0 0 > の C Z シリコンからなる、硬いベースウェーハを使用するので、電子デバイス用基板の反りが抑制され、そのベースウェーハの上に結晶方位が < 1 1 1 > のボンドウェーハが接合されるので、良好な窒化物半導体膜を形成することができる。更に、結晶方位が < 1 0 0 > と < 1 1 1 > という異なったウェーハを接合することでお互いの劈開方向が異なることとなり、製造された電子デバイス用基板が割れにくくなる。また、ベースウェーハの結晶方位を < 1 0 0 > とすることで、インゴットの成長途中での多結晶化が抑制されたものとすることができる。このため、高耐圧用あるいは高周波用の電子デバイス用基板として最適なものを製造することができる。

【実施例】

### [0053]

以下、実施例及び比較例を示し、本発明をより具体的に説明するが、本発明は下記の実施例に制限されるものではない。

[0054]

10

20

40

#### (実施例1)

### [0055]

### [0056]

### (実施例2)

抵抗率が 0.1 c m 以下、酸素濃度が  $1 \times 10^{-1}$  8 a t o m s / c m 3 (ASTM 7 9)以下の (100)面 C Z シリコン基板(抵抗率:0.07 c m、酸素濃度: $7 \times 10^{-1}$  7 a t o m s / c m 3)の厚みが  $500 \mu$  m と  $1000 \mu$  m のベースウェーハ(直径  $150 \mu$  m)を準備した。また、貼り合わせ用として、高濃度の窒素ドープした  $1000 \mu$  c m 以上の (111)面 C Z シリコン基板 (8 ×  $10^{-14}$  a t o m s / c m 3、500 c m)、基板の厚みが  $500 \mu$  m のボンドウェーハ(直径  $150 \mu$  m m)を  $200 \mu$  m d  $100 \mu$  d  $100 \mu$  m d  $100 \mu$

### [0057]

次に以下のようにして、図1に示すような電子デバイス用基板を作製した。 2 枚のベースウェーハ1を熱酸化(厚さ1  $\mu$  m)、両面研磨した 2 枚のボンドウェーハ2を熱酸化(厚さ1  $\mu$  m)し、結合工程を経て、結合熱処理を1150 で2時間行った。その後、結合した基板のボンドウェーハを研削及びポリッシュすることで基板におけるボンドウェーハの厚みを200  $\mu$  m とし、酸化膜除去として、10% H F に浸漬し表面酸化膜を除去し、厚さ700  $\mu$  m 、1200  $\mu$  m の接合基板を得た。そして、作製したこれらの接合基板厚さにMOVPE炉で5  $\mu$  m 厚のGaNエピタキシャル成長(中間層2.5  $\mu$  m、デバイス層2.5  $\mu$  m)を行った。その時の反りは、接合基板の厚さが700  $\mu$  mで40  $\mu$  m、厚さが1200  $\mu$  mで20  $\mu$  mであった。

### [0058]

### (実施例3)

抵抗率が 0.1 c m 以下、酸素濃度が  $1 \times 10^{-1}$  8 a t o m s / c m 3 (ASTM 7 9)以下の (100) 面 C Z シリコン基板(抵抗率:0.07 c m、酸素濃度: $7 \times 10^{-1}$  7 a t o m s / c m 3)の厚みが 500  $\mu$  m etor 100  $\mu$  m の etor 100  $\mu$  m etor 100  $\mu$  etor 100  $\mu$  m etor 100  $\mu$  etor 100

### [0059]

ベースウェーハ 1 を熱酸化(厚さ 1  $\mu$  m)、両面研磨したボンドウェーハ 2 を熱酸化(厚さ 1  $\mu$  m)し、結合工程を経て、結合熱処理を 1 1 5 0 で 2 時間行った。その後、結

10

20

30

40

合した基板のボンドウェーハを研削及びポリッシュすることで基板におけるボンドウェーハの厚みを 2 0 0  $\mu$  m とし、酸化膜除去として、 1 0 % H F に浸漬し表面酸化膜を除去し、厚さ 7 0 0  $\mu$  m、 1 2 0 0  $\mu$  mの接合基板を得た。そして、作製したこれらの接合基板にM O V P E 炉で 5  $\mu$  m 厚の G a N エピタキシャル成長(中間層 2 . 5  $\mu$  m、デバイス層 2 . 5  $\mu$  m)を行った。その時の反りは、接合基板の厚さが 7 0 0  $\mu$  mで 4 5  $\mu$  m、厚さが 1 2 0 0  $\mu$  mで 2 0  $\mu$  mで 3 0 0 4 m 4 5 4 m 4 5 4 m 4 5 4 m 4 5 4 m 4 5 4 m 4 5 4 m 4 5 4 m 4 5 4 m 4 5 4 m 4 5 4 m 4 5 4 m 4 5 4 m 4 5 4 m 4 5 4 m 4 5 4 m 4 5 4 m 4 5 4 m 4 5 4 m 4 5 4 m 4 5 4 m 4 5 4 m 4 5 4 m 4 5 4 m 4 5 4 m 4 5 4 m 4 5 4 m 4 5 4 m 4 5 4 m 4 5 4 m 4 5 4 m 4 5 4 m 4 5 4 m 4 5 4 m 4 5 4 m 4 5 4 m 4 5 4 m 4 5 4 m 4 5 4 m 4 5 4 m 4 5 4 m 4 5 4 m 4 5 4 m 4 5 4 m 4 5 4 m 4 5 4 m 4 5 4 m 4 5 4 m 4 5 4 m 4 5 4 m 4 6 4 m 4 6 4 m 4 6 4 m 4 6 4 m 4 6 4 m 4 6 4 m 4 6 4 m 4 6 4 m 4 6 4 m 4 6 4 m 4 0 4 m 4 6 4 m 4 0 4 m 4 0 4 m 4 0 4 m 4 0 4 m 4 0 4 0 4 m 4 0 4 m 4 0 4 0 4 m 4 0 4 0 4 m 4 0 4 0 4 m 4 0 4 0 4 0 4 0 4 0 4 0 4 0 4 0 4 0 4 0 4 0 4 0 4 0 4 0 4 0 4 0 4 0 4 0 4 0 4 0 4 0 4 0 4 0 4 0 4 0 4 0 4 0 4 0 4 0 4 0 4 0 4 0 4 0 4 0 4 0 4 0 4 0 4 0 4 0 4 0 4 0 4 0 4 0 4 0 4 0 4 0 4 0 4 0 4 0 4 0 4 0 4 0 4 0 4 0 4 0 4 0 4 0 4 0 4 0 4 0 4 0 4 0 4 0 4 0 4 0 4 0 4 0 4 0 4 0 4 0 4 0 4 0 4 0 4 0 4 0 4 0 4 0 4 0 4 0 4 0 4 0 4 0 4 0 4 0 4 0 4 0 4 0 4 0 4 0 4 0 4 0 4 0 4 0 4 0 4 0 4 0 4 0 4 0 4 0 4 0 4 0 4 0 4 0 4 0 4 0 4 0 4 0 4 0 4 0 4 0 4 0 4 0 4 0 4 0 4 0 4 0 4 0 4 0 4 0 4 0 4 0 4 0 4 0 4 0 4 0 4 0 4 0 4 0 4 0 4 0 4 0 4 0 4 0 4 0 4 0 4 0 4 0 4 0 4 0 4

#### [0060]

(比較例1)

抵抗率が 2~0 cm、酸素濃度が 5~×~1~0~1~8~a~t~o~m~s~/~c~m~3~o~(~1~1~1~) 面 C Z シリコン基板で、基板の厚みが  $7~0~0~\mu$  m のウェーハ(直径 1~5~0~mmm)を準備した。この基板に、MOVPE 炉で  $5~\mu$  m 厚の G~a~N~x ピタキシャル成長を行ったところ、成長後の反りが  $1~3~0~\mu$  m と大きくなった。

[0061]

(比較例2)

抵抗率が 0.1 c m 以下、酸素濃度が  $1 \times 10^{-1}$  8 a t o m s / c m  $^3$  (ASTM  $^7$  7 9 ) 以下の ( 100 ) 面 C Z シリコン基板(抵抗率: 0.007 c m、酸素濃度:  $7 \times 10^{-1}$  a t o m s / c m  $^3$  ) で、基板の厚みが  $500 \mu$  m と  $1000 \mu$  m のベースウェーハ(直径 150 m m )を準備した。また、貼り合わせ用として、ベースウェーハと同一の抵抗率及び酸素濃度の ( 100 ) 面 C Z シリコン基板、基板の厚みが  $500 \mu$  m のボンドウェーハ(直径 150 m m )を 2 枚準備した。

[0062]

[0063]

上記の結果から、実施例 1 ~ 3 のように、低抵抗率の (100) 面 (2) 回 (2) リコン基板に、結晶方位が < 1 1 1 > のボンドウェーハを貼り合わせて接合基板としたときは、窒化物半導体膜を形成させた場合に、ウェーハの反りが (2) り (2) の (2

[0064]

なお、本発明は、上記実施形態に限定されるものではない。上記実施形態は例示であり、本発明の特許請求の範囲に記載された技術的思想と実質的に同一な構成を有し、同様な作用効果を奏するものは、いかなるものであっても本発明の技術的範囲に包含される。

### 【符号の説明】

[0065]

- 10…電子デバイス用基板、

- 1...ベースウェーハ、 2...ボンドウェーハ、 3...接着層、

- 4…中間層、 5…窒化物半導体膜(デバイス層)、 6…接合基板。

10

20

30

# 【図1】

### フロントページの続き

# (56)参考文献 国際公開第2011/016219(WO,A1)

特開平09-246505(JP,A) 特開平05-090117(JP,A)

特開2011-103380(JP,A)

特開2014-236093(JP,A)

特表2017-507478(JP,A)

# (58)調査した分野(Int.CI., DB名)

H01L 21/02

C30B 29/06

H01L 21/20

H01L 27/12