## (19)**日本国特許庁(JP)**

# (12)特許公報(B2)

(11)特許番号 特許第7478716号 (P7478716)

### (45)発行日 令和6年5月7日(2024.5.7)

(24)登録日 令和6年4月24日(2024.4.24)

| (51)国際特許分類   |                            | FΙ         |          |                    |         |                |

|--------------|----------------------------|------------|----------|--------------------|---------|----------------|

| H01L 2       | 1/76 (2006.01)             | H 0 1 L    | 29/78    | 6 5 2 R            |         |                |

| H01L 29      | 9/78 (2006.01)             | H 0 1 L    | 29/78    | 6 5 2 B            |         |                |

| H01L 29      | 9/739 (2006.01)            | H 0 1 L    | 29/78    | 6 5 2 C            |         |                |

| H01L 2       | 1/336 (2006.01)            | H 0 1 L    | 29/78    | 6 5 2 D            |         |                |

| H01L 29      | 9/41 (2006.01)             | H 0 1 L    | 29/78    | 6 5 2 F            |         |                |

|              |                            |            | 請求項      | 頁の数 11             | (全31頁)  | 最終頁に続く         |

| (21)出願番号     | 特願2021-160106(P20          | (73)特許権者   | 00011602 | 4                  |         |                |

| (22)出願日      | 令和3年9月29日(2021.            |            | ローム株式    | 会社                 |         |                |

| (62)分割の表示    | 特願2019-203351(P2019-203351 |            |          | 京都府京都              | 市右京区西院清 | <b>睛崎町21番地</b> |

|              | )の分割                       |            | (74)代理人  | 11000231           | 0       |                |

| 原出願日         | 平成25年8月12日(2013.8.12)      |            |          | 弁理士法人あい特許事務所       |         |                |

| (65)公開番号     | 特開2022-920(P2022-920A)     |            | (72)発明者  | 日笠 旭紘              |         |                |

| (43)公開日      | 令和4年1月4日(2022.1.4)         |            |          | 京都府京都市右京区西院溝崎町21番地 |         |                |

| 審査請求日        | 令和3年9月30日(2021.            | 9.30)      |          | ローム株式              | 会社内     |                |

| 審判番号         | 不服2023-8625(P2023          | -8625/J1)  | 合議体      |                    |         |                |

| 審判請求日        | 令和5年5月26日(2023.            | 5.26)      | 審判長      | 河本 充雄              |         |                |

| (31)優先権主張番号  | 特願2012-182169(P20          | 12-182169) | 審判官      | 市川 武宜              |         |                |

| (32)優先日      | 平成24年8月21日(2012            | 2.8.21)    | 審判官      | 松永 稔               |         |                |

| (33)優先権主張国・ナ |                            |            |          |                    |         |                |

|              | 日本国(JP)                    |            |          |                    |         |                |

| (31)優先権主張番号  | 特願2012-182170(P20          | ,          |          |                    |         |                |

|              | 重                          | 最終頁に続く     |          |                    |         | 最終頁に続く         |

## (54)【発明の名称】 半導体装置

## (57)【特許請求の範囲】

#### 【請求項1】

半導体層と、

前記半導体層に形成された<u>ゲート</u>トレンチと、

<u>前記ゲート</u>トレンチに絶縁膜を介して埋め込まれた<u>ゲート</u>電極と、

前記<u>ゲート</u>トレンチの<u>一側方</u>において、前記半導体層の表面側から前記<u>ゲート</u>トレンチの深さ方向に順に配置された第1導電型の第1領域、第2導電型の第2領域、および前記第1導電型であり、かつ前記第1領域よりも低い不純物濃度を有する第3領域と、

前記<u>ゲート</u>トレンチ<u>の他側方において、前記ゲートトレンチに隣り合うように形成され</u> たエミッタトレンチと、

<u>前記エミッタトレンチに対して、前記エミッタトレンチと前記ゲートトレンチで挟まれる領域と反対側の</u>領域に形成され、前記第 2 領域よりも深く形成された前記第 2 導電型のフローティング領域と、

前記<u>第1領域および前記第2</u>領域に前記半導体層の表面から掘り下がって形成されたコンタクトトレンチと、

前記コンタクトトレンチの底面に形成され、かつ前記第2領域よりも高い不純物濃度を 有する前記第2導電型のコンタクト領域と、

前記半導体層の表面側に形成され、かつ前記コンタクトトレンチに入り込んでおり、前記コンタクトトレンチの側面で前記第1領域に接続され、前記コンタクトトレンチの底面で前記コンタクト領域に接続された表面電極とを含み、

前記コンタクトトレンチは、その底面が平坦な形状であり、かつ前記コンタクト領域が前記第1領域の底部および前記コンタクトトレンチの底面に接するように、前記コンタクトトレンチの底面が前記コンタクト領域の最表面部よりも深くなるように形成され、

前記第2領域の底部は前記ゲートトレンチよりも浅く形成されている、半導体装置。

### 【請求項2】

表面および裏面を有する半導体層と、

前記半導体層に形成された一対のゲートトレンチと、

<u>前記一対のゲートトレンチで挟まれた領域に、</u>前記半導体層の表面側から裏面側に向かって順に配置された第1導電型の第1領域、第2導電型の第2領域、および前記第1導電型であり、かつ前記第1領域よりも低い不純物濃度を有する第3領域と、

前記半導体層の表面側から裏面側に向かって形成され、前記第2領域よりも深く形成された前記第2導電型のフローティング領域と、

前記半導体層において、前記第1領域、前記第2領域および前記第3領域が配置された領域と、前記フローティング領域との間に形成され、底部が前記<u>第2領域よりも前記裏面</u>側まで延びるエミッタトレンチと、

前記<u>ゲート</u>トレンチに絶縁膜を介して埋め込まれた<u>ゲート</u>電極と、

前記<u>第1領域および前記第2</u>領域に前記半導体層の表面から掘り下がって形成されたコンタクトトレンチと、

前記コンタクトトレンチの底面に形成され、かつ前記第2領域よりも高い不純物濃度を 有する前記第2導電型のコンタクト領域と、

前記半導体層の表面側に形成され、かつ前記コンタクトトレンチに入り込んでおり、前記コンタクトトレンチの側面で前記第1領域に接続され、前記コンタクトトレンチの底面で前記コンタクト領域に接続された表面電極とを含み、

前記コンタクトトレンチは、その底面が平坦な形状であり、かつ前記コンタクト領域が前記第1領域の底部および前記コンタクトトレンチの底面に接するように、前記コンタクトトレンチの底面が前記コンタクト領域の最表面部よりも深くなるように形成<u>されている</u>、半導体装置。

## 【請求項3】

前記フローティング領域は、前記<u>エミッタ</u>トレンチの底部よりも深い位置にまで形成されている、請求項1または2に記載の半導体装置。

## 【請求項4】

前記絶縁膜は、前記<u>ゲート</u>トレンチ外に延び、前記半導体層の前記表面における前記第 1 領域を覆っている、請求項 1 ~ 3 のいずれか一項に記載の半導体装置。

## 【請求項5】

前記絶縁膜の端面が、前記コンタクトトレンチの前記側面に連なっている、請求項 4 に記載の半導体装置。

#### 【請求項6】

前記半導体層上に形成され、前記絶縁膜の前記端面に連なる側面を含む開口が形成された層間膜をさらに含み、

前記表面電極は、前記層間膜の前記開口を介して、前記コンタクトトレンチに入り込んでいる、請求項5に記載の半導体装置。

#### 【請求項7】

前記コンタクト領域は、前記コンタクトトレンチの幅よりも側方に広がるように形成されている、請求項1~6のいずれか一項に記載の半導体装置。

## 【請求項8】

前記第3領域に対して前記半導体層の裏面側に配置された前記第2導電型の第4領域と、前記第3領域と前記第4領域との間に形成され、前記第3領域よりも高い不純物濃度を有する前記第1導電型のバッファ層とを含む、請求項1~7のいずれか一項に記載の半導体装置。

## 【請求項9】

10

20

30

40

前記表面電極は、前記コンタクトトレンチ上の部分に選択的に凹部を有している、請求項1~8のいずれか一項に記載の半導体装置。

#### 【請求項10】

前記<u>ゲート</u>電極の上面には、前記<u>ゲート</u>トレンチ内において、半導体層の前記表面に対して前記<u>ゲート</u>トレンチの深さ方向に凹んだ凹部が形成されている、請求項 1 ~ 9 のいずれか一項に記載の半導体装置。

## 【請求項11】

前記第1導電型がn型であり、前記第2導電型がp型である、請求項1~10のNずれか一項に記載の半導体装置。

【発明の詳細な説明】

【技術分野】

[0001]

本発明は、IGBT (Insulated Gate Bipolar Transistor)を備える半導体装置に関する。

#### 【背景技術】

[0002]

従来、コレクタ・エミッタ間の飽和電圧 $V_{CE}$ (sat)および短絡耐量の高いトレンチ型 IGBTは、p型フローティング層を有している。p型フローティング層は、一般的に、p型ベース層と同一工程形成される。これにより、p型フローティング層は、p型ベース層と同じ深さを有している。

【先行技術文献】

【特許文献】

[0003]

【文献】町田悟、杉山隆英、石子雅康、保田智史、斎藤順、濱田公守、「IGBTのスイッチング損失と素子容量の関連解析」、電気学会電子材料研究会資料(EFM-09,16-26,28-29)、p.55-59

【文献】渡邉聡、森睦宏、新井大夏、石橋亨介、豊田靖、織田哲男、原田卓、齊藤克明、「フローティング p 層をゲートから分離した低損失、低ノイズ、高信頼な1.7 k V トレンチIGBT」、電気学会電子デバイス研究会資料(EDD・11,66-83)、p.67-71

【文献】特許第4785334号公報

【発明の概要】

【発明が解決しようとする課題】

[0004]

しかしながら、従来の構造では、デバイスの耐圧保持のためにp型フローティング層を深く拡散させると耐圧は保持されるが、それに伴いp型ベース層が厚くなってしまってオン電圧が上昇するという不具合がある。一方、オン電圧の低減のためにp型ベース層を薄くしたのでは、逆に、十分な耐圧を保持することが困難になる。

[0005]

そこで、本発明の目的は、耐圧を向上できながら、オン電圧の上昇を抑えることができるIGBTを備える半導体装置を提供することである。

【課題を解決するための手段】

[0006]

上記目的を達成するための本発明の半導体装置は、半導体層と、第1方向に延びるように形成され、前記第1方向と直行する第2方向に並んで前記半導体層に形成された複数のトレンチと、前記複数のトレンチに絶縁膜を介して埋め込まれ、前記第2方向において互いに隣り合う複数のゲート電極および前記第2方向に沿って互いに隣り合う複数のエミッタ電極の繰り返し構造と、前記ゲート電極の側方であって前記互いに隣り合うゲート電極の間の領域において、前記半導体層の表面側から前記トレンチの深さ方向に順に配置された n + 型エミッタ領域、 p 型ベース領域および n ・型ドリフト領域と、前記互いに隣り合

10

20

30

40

うエミッタ電極の間の領域において形成され、前記p型ベース領域よりも深く形成され、 前記エミッタ電極の下方に回り込むオーバーラップ部を含むp型フローティング領域と、 前記n<sup>-</sup>型ドリフト領域に対して前記半導体層の裏面側に配置されたp<sup>+</sup>型コレクタ領域 とを備え、前記p型ベース領域と前記n 型ドリフト領域との界面は、前記トレンチの中 央部もしくは上部に設定されている。

#### 【図面の簡単な説明】

- [0007]

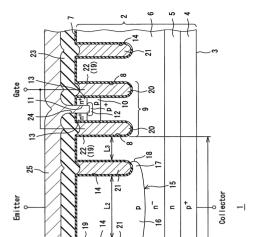

- 【図1】図1は、本発明の第1実施形態に係る半導体装置の模式的な断面図である。

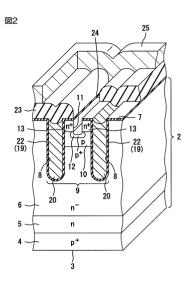

- 【図2】図2は、図1の半導体装置の内部構造を説明するための斜視図である。

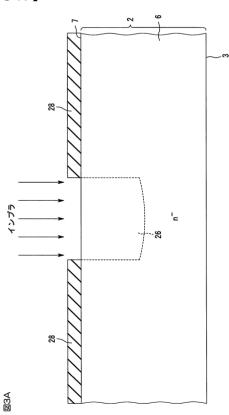

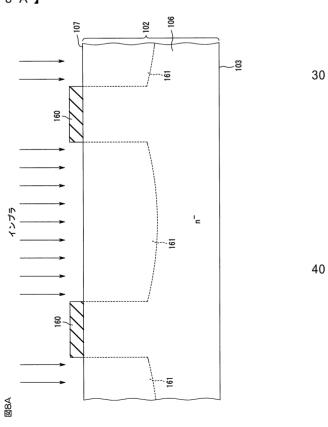

- 【図3A】図3Aは、図1の半導体装置の製造工程を説明するための図である。

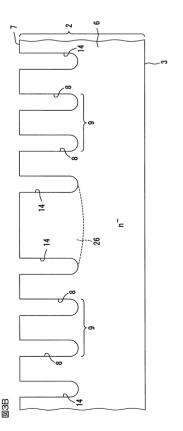

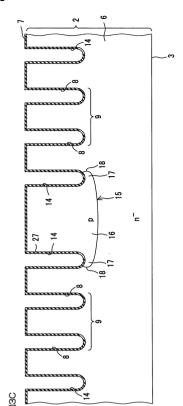

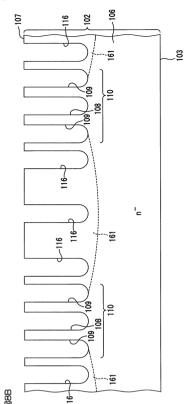

- 【図3B】図3Bは、図3Aの次の工程を示す図である。

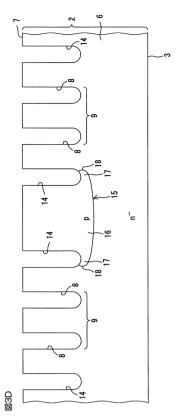

- 【図3C】図3Cは、図3Bの次の工程を示す図である。

- 【図3D】図3Dは、図3Cの次の工程を示す図である。

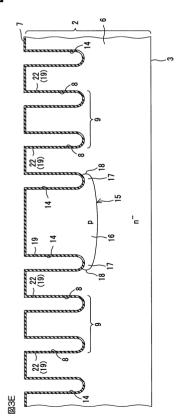

- 【図3E】図3Eは、図3Dの次の工程を示す図である。

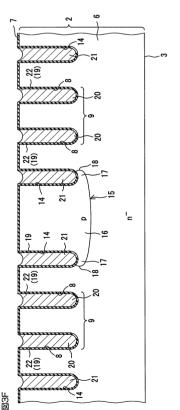

- 【図3F】図3Fは、図3Eの次の工程を示す図である。

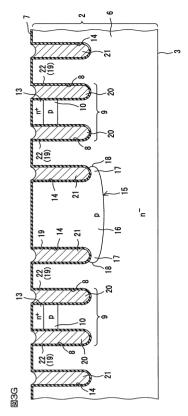

- 【図3G】図3Gは、図3Fの次の工程を示す図である。

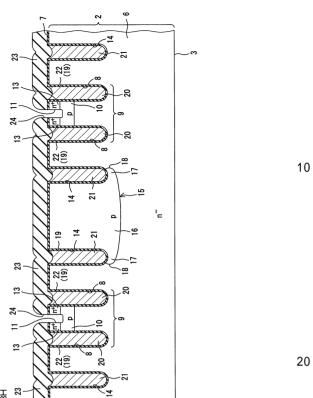

- 【図3H】図3Hは、図3Fの次の工程を示す図である。

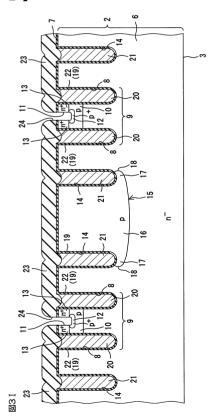

- 【図3Ⅰ】図3Ⅰは、図3Fの次の工程を示す図である。

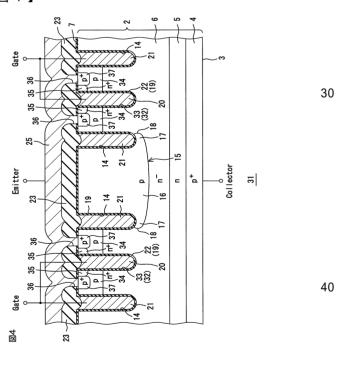

- 【図4】図4は、本発明の第2実施形態に係る半導体装置の模式的な断面図である。

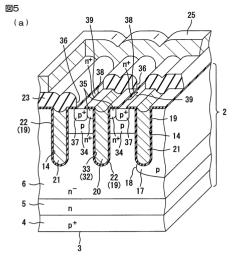

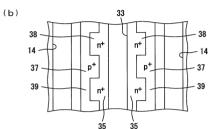

- 【図5】図5は、図4の半導体装置の内部構造を説明するための図であって、図5(a) は斜視図、図5(b)は平面図をそれぞれ示している。

- 【図6】図6は、本発明の第3実施形態に係る半導体装置の模式的な断面図である。

- 【図7】図7は、図6の破線で囲まれた部分の拡大図である。

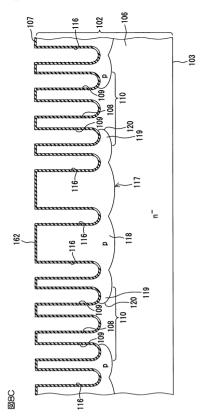

- 【図8A】図8Aは、図7の半導体装置の製造工程を説明するための図である。

- 【図8B】図8Bは、図8Aの次の工程を示す図である。

- 【図8C】図8Cは、図8Bの次の工程を示す図である。

- 【図80】図80は、図80の次の工程を示す図である。

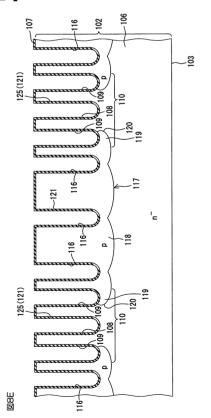

- 【図8E】図8Eは、図8Dの次の工程を示す図である。

- 【図8F】図8Fは、図8Eの次の工程を示す図である。

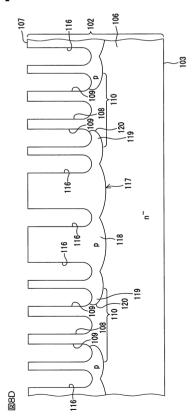

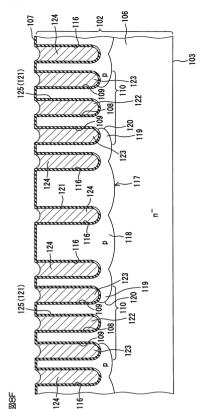

- 【図8G】図8Gは、図8Fの次の工程を示す図である。

- 【図8H】図8Hは、図8Gの次の工程を示す図である。

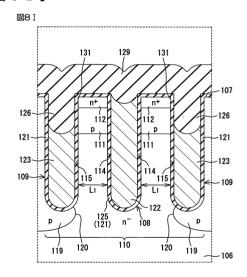

- 【図8Ⅰ】図8Ⅰは、図8Hの次の工程を示す図である。

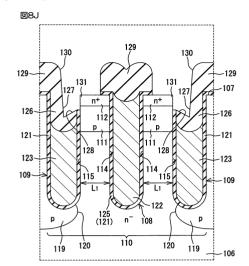

- 【図8」】図8」は、図8Ⅰの次の工程を示す図である。

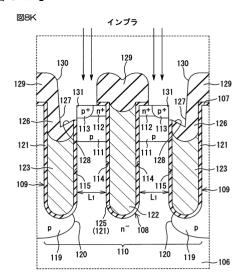

- 【図8K】図8Kは、図8Jの次の工程を示す図である。

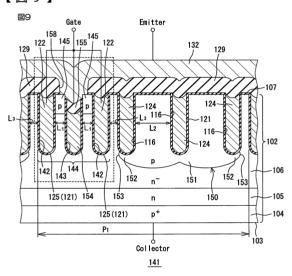

- 【図9】図9は、本発明の第4実施形態に係る半導体装置の模式的な断面図である。

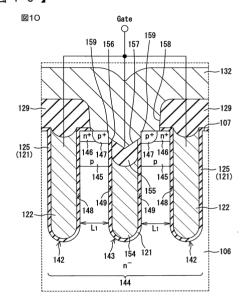

- 【図10】図10は、図9の破線で囲まれた部分の拡大図である。

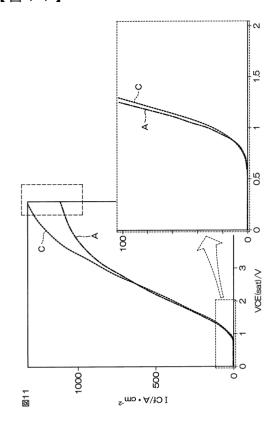

- 【図11】図11は、デバイスのVcE-Icf特性を示すグラフである。

- 【発明を実施するための形態】

- [0008]

以下では、本発明の実施の形態を、添付図面を参照して詳細に説明する。

図1は、本発明の第1実施形態に係る半導体装置1の模式的な断面図である。図2は、 図1の半導体装置の内部構造を説明するための斜視図である。

半導体装置1は、IGBTを備えるデバイスであって、本発明の半導体層の一例として の半導体基板 2 を含む。半導体基板 2 は、たとえば、 5 0 μm ~ 2 0 0 μmの厚さの n -型シリコン基板であってよい。

## [0011]

半導体基板 2 は、その裏面 3 側から順に p <sup>+</sup>型コレクタ領域 4 、 n 型バッファ領域 5 お よび n <sup>-</sup> 型ドリフト領域 6 が積層された構造を有している。 p <sup>+</sup> 型コレクタ領域 4 が半導

10

20

体基板2の裏面3全体に露出し、n 型ドリフト領域6が半導体基板2の表面7の一部に選択的に露出している。

#### [0012]

$p^+$ 型コレクタ領域 4 の p 型ドーパントとしては、たとえば、 B (ホウ素)、 A 1 (アルミニウム)等を使用できる(以下、同じ)。一方、n 型バッファ領域 5 および  $n^-$  型ドリフト領域 6 の n 型ドーパントとしては、たとえば、N (窒素)、P (リン)、A S (ひ素)等を使用できる(以下、同じ)。

#### [0013]

また、 $p^+$ 型コレクタ領域 4 のドーパント濃度は、たとえば、 $1 \times 10^{15}$  c m  $^{-3}$  ~  $2 \times 10^{19}$  c m  $^{-3}$  である。一方、n 型バッファ領域 5 のドーパント濃度は、たとえば、 $1 \times 10^{15}$  c m  $^{-3}$  ~  $5 \times 10^{17}$  c m  $^{-3}$  であり、 $n^-$ 型ドリフト領域 6 のドーパント濃度は、 $1 \times 10^{13}$  c m  $^{-3}$  ~  $5 \times 10^{14}$  c m  $^{-3}$  である。

### [0014]

半導体基板 2 の表面 7 側には、複数のゲートトレンチ 8 が形成されている。この実施形態では、複数のゲートトレンチ 8 は、たとえばストライプ状に形成され、半導体基板 2 の表面 7 に沿う横方向に一対ずつのトレンチ単位 9 として配置されている。互いに隣り合うトレンチ単位 9 のピッチ  $P_1$  は、たとえば、  $4 \mu m \sim 2 0 \mu m$  である。また、一対のゲートトレンチ 8 において、一方のゲートトレンチ 8 と他方のゲートトレンチ 8 とのピッチ  $P_2$  (ゲートトレンチ 8 の中心点同士の距離)は、たとえば、  $P_2$   $P_3$   $P_4$   $P_5$   $P_4$   $P_5$   $P_5$   $P_5$   $P_6$   $P_6$   $P_7$   $P_8$   $P_7$   $P_8$   $P_7$   $P_8$   $P_8$   $P_9$   $P_9$

#### [0015]

一対のゲートトレンチ 8 の間には、 p 型ベース領域 1 0 が形成されている。 p 型ベース領域 1 0 は、一方のゲートトレンチ 8 と他方のゲートトレンチ 8 によって共有されている。また、この実施形態では、 p 型ベース領域 1 0 と n ・型ドリフト領域 6 との界面がゲートトレンチ 8 の中央部もしくは上部に設定されていて、 p 型ベース領域 1 0 は、半導体基板 2 の比較的浅くに拡散形成されている。

## [0016]

p型ベース領域10には、半導体基板2の表面7から掘り下がったコンタクトトレンチ11が形成されている。コンタクトトレンチ11は、ゲートトレンチ8の長手方向に沿って一定の幅で形成されている。コンタクトトレンチ11の底面には、p<sup>+</sup>型ベースコンタクト領域12が形成されている。

#### [0017]

また、コンタクトトレンチ 1 1 と、一方および他方のゲートトレンチ 8 との間において p 型ベース領域 1 0 の表面部には、 n <sup>+</sup> 型エミッタ領域 1 3 が形成されている。 n <sup>+</sup> 型エミッタ領域 1 3 は、コンタクトトレンチ 1 1 の両側に一つずつ設けられ、それぞれがコンタクトトレンチ 1 1 の側面に露出している。

#### [0018]

また、 p 型ベース領域 1 0 のドーパント濃度は、たとえば、 1  $\times$  1 0  $^{16}$  c m  $^{-3}$  ~ 1  $\times$  1 0  $^{18}$  c m  $^{-3}$  である。 p  $^+$  型ベースコンタクト領域 1 2 のドーパント濃度は、たとえば、 5  $\times$  1 0  $^{18}$  c m  $^{-3}$  ~ 1  $\times$  1 0  $^{20}$  c m  $^{-3}$  である。 n  $^+$  型エミッタ領域 1 3 のドーパント濃度は、 1  $\times$  1 0  $^{19}$  c m  $^{-3}$  ~ 5  $\times$  1 0  $^{20}$  c m  $^{-3}$  である。

### [0019]

また、半導体基板 2 の表面 7 側において一対のゲートトレンチ 8 の間には、複数(図 1 では 2 本)のエミッタトレンチ 1 4 が形成されている。この実施形態では、複数のエミッタトレンチ 1 4 は、たとえばストライプ状(ゲートトレンチ 8 に平行)に形成され、半導体基板 2 の表面 7 に沿う横方向に互いに等しい間隔を空けて配置されている。互いに隣り合うエミッタトレンチ 1 4 間隔 L  $_2$  (エミッタトレンチ 1 4 の側面間の距離)は、たとえば、 3  $_\mu$  m以下、好ましくは、 0 . 8  $_\mu$  m  $_\alpha$  3  $_\mu$  m である。また、複数のエミッタトレンチ 1 4 は、ゲートトレンチ 8 と同じ深さで形成されている。これにより、エミッタトレンチ 1 4 をゲートトレンチ 8 と同一工程で形成することができるので、製造工程を簡略化す

10

20

30

40

ることができる。

#### [0020]

複数のエミッタトレンチ14のうち、ゲートトレンチ8に隣り合うトレンチ(ゲートト レンチ8との間にトレンチを介さずに対向するトレンチ)は、ゲートトレンチ8との間に n <sup>-</sup> 型ドリフト領域 6 を介して 2 μ m 以下の間隔 L <sub>3</sub> (エミッタトレンチ 1 4 の側面とゲ ートトレンチ8の側面との距離)を隔てて配置されている。つまり、当該エミッタトレン チ 1 4 とゲートトレンチ 8 との間には、深さ方向全域に渡って n <sup>-</sup>型ドリフト領域 6 が介 在している。

### [0021]

また、複数のエミッタトレンチ14の各間には、p型フローティング領域15が形成さ れている。 p型フローティング領域 1 5 は、電気的にフローティング状態が保たれた半導 体領域であり、ゲートトレンチ8に隣り合うエミッタトレンチ14によって、ゲートトレ ンチ8と分離されている。p型フローティング領域15は、この実施形態では、p型ベー ス領域10よりも深く形成されている。

#### [0022]

p型フローティング領域 1 5 は、エミッタトレンチ 1 4 の底部に対して半導体基板 2 の 裏面3側に膨出する底部16と、ゲートトレンチ8に隣り合うエミッタトレンチ14の下 方に回り込むオーバーラップ部17とを有している。オーバーラップ部17は、当該エミ ッタトレンチ14の幅方向中央に対してゲートトレンチ8の近い側に位置する端部18を 有している。この端部18は、エミッタトレンチ14に対してゲートトレンチ8側にはみ 出ていないことが好ましい。

#### [0023]

また、 p型フローティング領域15のドーパント濃度は、たとえば、5×10<sup>15</sup>cm<sup>-</sup>  $^{3} \sim 1 \times 10^{18} \text{ cm}^{-3} \text{ cm}^{-3}$

### [0024]

ゲートトレンチ8およびエミッタトレンチ14には、絶縁膜19(たとえば、酸化シリ コン(SiO2))を介してゲート電極20および埋め込み電極21がそれぞれ埋め込ま れている。ゲート電極20および埋め込み電極21は、たとえば、ポリシリコン等の導電 材料からなる。絶縁膜19は、ゲートトレンチ8の内面、半導体基板2の表面7およびエ ミッタトレンチ14の内面に沿って一体的に形成されている。絶縁膜19のゲートトレン チ8内の部分は、ゲート絶縁膜22として機能する。また、エミッタトレンチ14の複数 の埋め込み電極21は、後述するエミッタ電極25に電気的に接続されている。

### [0025]

半導体基板2の表面7には、たとえば、ホウ素リンシリケートガラス(BPSG)、酸 化シリコン ( SiO<sub>2</sub> ) 等の絶縁材料からなる層間膜 2 3 が積層されている。層間膜 2 3 には、コンタクトトレンチ 1 1 を介して  $n^+$ 型エミッタ領域 1 3 および  $p^+$ 型ベースコン タクト領域12を選択的に露出させるコンタクトホール24が形成されている。

## [0026]

層間膜23上には、エミッタ電極25が積層されている。エミッタ電極25は、コンタ クトトレンチ11に入り込み、コンタクトトレンチ11の側面においてn<sup>+</sup>型エミッタ領 域13に接続されている。また、コンタクトトレンチ11の底面において、 p <sup>+</sup>型ベース コンタクト領域12を介してp型ベース領域10に接続されている。

#### [0027]

次に、半導体装置1の製造方法について説明する。図3A~図3Iは、図1の半導体装 置1の製造工程を工程順に説明するための図である。

## [0028]

半導体装置1を製造するには、図3Aに示すように、n‐型の半導体基板2(n‐型ド リフト領域6)の表面7にマスク28が形成される。マスク28には、表面7におけるp 型フローティング領域15に形成すべき領域を選択的に露出させる開口が形成されている 。そして、このマスク28を介して、半導体基板2の表面7に対してp型ドーパントがイ 10

20

30

40

オン注入(インプラ)される。これにより、イオン注入領域26が形成される。

#### [0029]

次に、図3Bに示すように、半導体基板2が選択的にエッチングされることによって、 ゲートトレンチ8およびエミッタトレンチ14が同時形成される。

### [0030]

次に、図3Cに示すように、半導体基板2が熱酸化されることによって、ゲートトレン チ8およびエミッタトレンチ14の内面を含む表面全域に犠牲酸化膜27が形成される。 そして、犠牲酸化膜27で覆われた半導体基板2をアニール処理することによって、イオ ン注入領域26中のp型ドーパントが拡散する(ドライブイン)。このアニール処理は、 p型ドーパントがエミッタトレンチ14の下方に回り込む条件で行われる。これにより、 p型フローティング領域15が形成される。この際、半導体基板2が犠牲酸化膜27で覆 われているので、基板表面からのイオン抜けを防止することができるので、p型ドーパン トを効率よく拡散させることができる。

#### [0031]

次に、図3Dに示すように、犠牲酸化膜27が剥離される。

#### [0032]

次に、図3Eに示すように、半導体基板2が熱酸化されることによって、ゲートトレン チ8およびエミッタトレンチ14の内面を含む表面全域に絶縁膜19(ゲート絶縁膜22 )が形成される。

## [0033]

次に、図3Fに示すように、ポリシリコン等の電極材料がゲートトレンチ8およびエミ ッタトレンチ14に埋め込まれる。これにより、ゲート電極20および埋め込み電極21 が同時に形成される。

## [0034]

次に、図3Gに示すように、半導体基板2の表面7に対して選択的にn型およびp型ド ーパントがイオン注入および拡散されることによって、p型ベース領域10およびn + 型 エミッタ領域13が順に形成される。

#### [0035]

次に、図3Hに示すように、半導体基板2の表面7上に、ホウ素リンシリケートガラス (BPSG)、酸化シリコン(SiO2)等の絶縁材料を堆積させることによって、層間 膜23が形成される。次に、層間膜23が選択的にエッチングされてコンタクトホール2 4 が形成された後、当該コンタクトホール24から露出する半導体基板2が選択的にエッ チングされる。これにより、コンタクトトレンチ11が形成される。

## [0036]

次に、図3Iに示すように、コンタクトホール24を介してコンタクトトレンチ11の 底部に対して選択的にp型ドーパントがイオン注入および拡散されることによって、p \* 型ベースコンタクト領域12が形成される。

## [0037]

その後、半導体基板2の表面7側にエミッタ電極24等が形成された後、半導体基板2 の裏面3に対して選択的にn型およびp型ドーパントがイオン注入および拡散されること によって、 n 型バッファ領域 5 および p <sup>+</sup> 型コレクタ領域 4 が順に形成される。

### [0038]

以上のような工程を経ることによって、図1に示す半導体装置1が得られる。なお、図 3A~図3Iでは半導体装置1の製造工程の一部を表したに過ぎず、当該製造工程は、図 3 A ~ 図 3 I で示されなかった工程を含んでいてもよい。

## [0039]

この半導体装置1によれば、埋め込み電極21が埋め込まれたエミッタトレンチ14( 以下、「エミッタ接合トレンチ」という)の底部までp型フローティング領域15(オー バーラップ部17)が形成されているので、スイッチングオフ動作時にエミッタ接合トレ ンチに負荷するコレクタ・エミッタ電圧を緩和することができる。そのため、急峻な電圧 10

20

30

変化(dv/dt)に対してデバイスの破壊を防止することができる。

#### [0040]

また、 p型ベース領域 1 0 よりも深い p型フローティング領域 1 5 によって耐圧を向上できる一方、 p型ベース領域 1 0 は浅くてもよいので、 p型ベース領域 1 0 の深さを適切に設計することによってチャネル長(ゲートトレンチ 8 の深さ方向の長さ)を短くしてオン電圧の上昇を抑制することもできる。

## [0041]

また、ゲート電極 2 0 が埋め込まれたゲートトレンチ 8 (以下、「ゲート接合トレンチ」という)が、エミッタ接合トレンチによって p型フローティング領域 1 5 から分離されている。これにより、 p型フローティング領域 1 5 とゲート接合トレンチとの接合を防止することができる。そのため、ゲート接合トレンチと p型フローティング領域 1 5 との間の浮遊容量をなくすことができる。

#### [0042]

一方、ゲート接合トレンチが深さ方向全域に渡って接合している n 型ドリフト領域 6 は p <sup>†</sup>型コレクタ領域 4 と共に接地されるものである。そのため、スイッチング動作時に、ゲート接合トレンチと n 型ドリフト領域 6 との間の容量変化が安定するので、ノイズが発生し難い。これらの結果、スイッチング動作時のノイズの発生およびスイッチング損失を低減することができる。

## [0043]

また、エミッタ接合トレンチと、ゲート接合トレンチとの間隔 L が 2 μ m 以下であるので、耐圧を良好に保持することもできる。

#### [0044]

さらに、コンタクトトレンチ11の側面を $n^+$ 型エミッタ領域13とのコンタクトのための領域として有効利用することができるので、 $n^+$ 型エミッタ領域13に対するエミッタ電極25の接合面積を十分確保することができる。これにより、 $n^+$ 型エミッタ領域13の平面面積を犠牲にすることができるので、一対のゲートトレンチ8における一方および他方のゲートトレンチ8の間隔L1を微細化して、従来に比べて微細なp型ベース領域10を形成することができる。ゲートトレンチ8の微細化の結果、デバイスの短絡耐量とオン電圧とのトレードオフの関係を改善することができるので、電荷促進効果を向上させることができる。よって、低電流域におけるVCE(sat)を改善することができる。

## [0045]

図4は、本発明の第2実施形態に係る半導体装置31の模式的な断面図である。図5は、図4の半導体装置の内部構造を説明するための図であって、図5(a)は斜視図、図5(b)は平面図をそれぞれ示している。図4および図5において、前述の図1に示された各部と対応する部分には同一の参照符号を付して示す。

## [0046]

前述の第1実施形態では、ゲートトレンチ8は、一対ずつのトレンチ単位9として形成され、一方および他方のゲートトレンチ8の間に共通のp型ベース領域10が形成されていた。これに対し、第2実施形態の半導体装置31は、半導体基板2の表面7に沿う横方向に一つずつのトレンチ単位32として形成された複数のゲートトレンチ33と、各ゲートトレンチ33の両側(エミッタトレンチ14との間の領域)に形成されたp型ベース領域34と、各p型ベース領域34の表面部に形成されたn + 型エミッタ領域35とを含む。n + 型エミッタ領域35は、ゲートトレンチ33の両側面に沿って一つずつ形成され、半導体基板2の表面7に露出している。

#### [0047]

また、 p 型ベース領域 3 4 の表面部には、 n  $^+$ 型エミッタ領域 3 5 の側方(ゲートトレンチ 3 3 の反対側)に p  $^+$ 型ベースコンタクト領域 3 7 が形成されている。 p  $^+$ 型ベースコンタクト領域 3 7 のドーパント濃度は、たとえば、 5 × 1 0  $^{18}$  c m  $^{-3}$   $^-$  1 × 1 0  $^{20}$  c m  $^{-3}$  である。

### [0048]

10

20

30

n \* 型エミッタ領域 3 5 は、図 5 (a)(b)に示すように、ゲートトレンチ 3 3 の側面から半導体基板 2 の表面 7 に沿う横方向に引き出された引き出し部 3 8 を選択的に有している。引き出し部 3 8 は、たとえば、ゲートトレンチ 3 3 の長手方向に沿って一定の間隔を空けて配置されている。この実施形態のようにゲートトレンチ 3 3 に対して一対の n \* 型エミッタ領域 3 5 が設けられる場合、各 n \* 型エミッタ領域 3 5 の引き出し部 3 8 は、図 5 (b)に示すように、一方および他方の端部がゲートトレンチ 3 3 を挟んで互いに対向するように配置されていてもよいし、一方の引き出し部 3 8 の端部が、ゲートトレンチ 3 3 の長手方向に沿って交互に配置されていてもよい(図示せず)。これにより、 p \* 型ベースコンタクト領域 3 7 における引き出し部 3 8 に隣り合う部分は、他の部分よりも選択的に幅が狭い挟部 3 9 となっている。

[0049]

また、層間膜 2 3 には、  $p^+$ 型ベースコンタクト領域 3 7 および  $n^+$ 型エミッタ領域 3 5 を選択的に露出させるコンタクトホール 3 6 が形成されている。  $n^+$ 型エミッタ領域 3 5 は、引き出し部 3 8 がコンタクトホール 3 6 から選択的に露出している。エミッタ電極 2 5 は、コンタクトホール 3 6 を介して、  $p^+$ 型ベースコンタクト領域 3 7 および  $n^+$ 型 エミッタ領域 3 5 に接続されている。

[0050]

この半導体装置31によっても、第1実施形態の半導体装置1と同様の効果を達成することができる。

[0051]

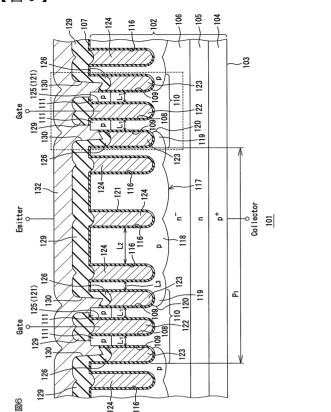

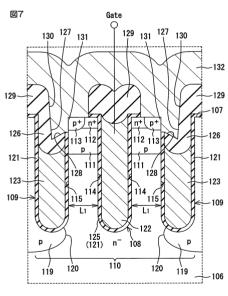

図6は、本発明の第3実施形態に係る半導体装置の模式的な断面図である。図7は、図6の破線で囲まれた部分の拡大図である。

[0052]

半導体装置 1 0 1 は、 I G B T を備えるデバイスであって、本発明の半導体層の一例としての半導体基板 1 0 2 を含む。半導体基板 1 0 2 は、たとえば、 5 0  $\mu$  m ~ 2 0 0  $\mu$  m の厚さの n <sup>-</sup>型シリコン基板であってよい。

[0053]

半導体基板 1 0 2 は、その裏面 1 0 3 側から順に p <sup>+</sup>型コレクタ領域 1 0 4 、 n 型バッファ領域 1 0 5 および n <sup>-</sup>型ドリフト領域 1 0 6 が積層された構造を有している。 p <sup>+</sup>型コレクタ領域 1 0 4 が半導体基板 1 0 2 の裏面 1 0 3 全体に露出し、 n <sup>-</sup>型ドリフト領域 1 0 6 が半導体基板 1 0 2 の表面 1 0 7 の一部に選択的に露出している。

[0054]

$p^+$ 型コレクタ領域104のp型ドーパントとしては、たとえば、B(ホウ素)、A1(アルミニウム)等を使用できる(以下、同じ)。一方、n型ドリフト領域106のn型ドーパントとしては、たとえば、N(窒素)、P(リン)、As(ひ素)等を使用できる(以下、同じ)。

[0055]

また、 $p^+$ 型コレクタ領域 1 0 4 のドーパント濃度は、たとえば、 1 × 1 0  $^{1.5}$  c m  $^{-.3}$  ~ 2 × 1 0  $^{1.9}$  c m  $^{-.3}$  である。一方、n 型バッファ領域 1 0 5 のドーパント濃度は、たとえば、 1 × 1 0  $^{1.5}$  c m  $^{-.3}$  ~ 5 × 1 0  $^{1.7}$  c m  $^{-.3}$  であり、 $n^-$  型ドリフト領域 1 0 6 のドーパント濃度は、 1 × 1 0  $^{1.3}$  c m  $^{-.3}$  ~ 5 × 1 0  $^{1.4}$  c m  $^{-.3}$  である。

[0056]

半導体基板102の表面107側には、複数のゲートトレンチ108および複数のダミートレンチ109が互いに隣り合って形成されている。この実施形態では、一対のダミートレンチ109と、一対のダミートレンチ109の間に挟まれたゲートトレンチ108とを含むトレンチ単位110が、半導体基板102の表面107に沿う横方向に間隔を空けて複数配置されている。これにより、ゲートトレンチ108およびダミートレンチ109は、全体としてストライプ状に形成されている。

[0057]

互いに隣り合うトレンチ単位 1 1 0 のピッチ  $P_1$  は、たとえば、  $2 \mu m \sim 7 \mu m$  である

10

20

30

40

。また、各トレンチ単位 1 1 0 において、ゲートトレンチ 1 0 8 とその両側のダミートレンチ 1 0 9 との間隔  $L_1$  (ゲートトレンチ 1 0 8 の側面とダミートレンチ 1 0 9 の側面との距離)はそれぞれ、 2  $\mu$  m以下であることが好ましい。

#### [0058]

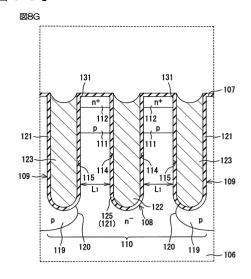

各トレンチ単位110において、ゲートトレンチ108の両側(各ダミートレンチ109との間の領域)には、p型ベース領域111が形成され、さらにp型ベース領域111の表面部にn<sup>+</sup>型エミッタ領域112およびp<sup>+</sup>型ベースコンタクト領域113が形成されている(図7参照)。この実施形態では、p型ベース領域111とn<sup>-</sup>型ドリフト領域106との界面がゲートトレンチ108の中央部もしくは上部に設定されていて、p型ベース領域111は、半導体基板102の比較的浅くに拡散形成されている。

## [0059]

$n^+$ 型エミッタ領域112および $p^+$ 型ベースコンタクト領域113は、ゲートトレンチ108とダミートレンチ109との間の領域において互いに隣接して配置されている。具体的には、 $n^+$ 型エミッタ領域112がゲートトレンチ108の両側面114に沿って一つずつ形成され、 $p^+$ 型ベースコンタクト領域113が各ダミートレンチ109の側面115に沿って一つずつ形成されている。これにより、 $n^+$ 型エミッタ領域112は、半導体基板102の表面107およびゲートトレンチ108の側面114に露出している。一方、 $p^+$ 型ベースコンタクト領域113は、半導体基板102の表面107およびダミートレンチ109の側面115に露出している。

### [0060]

また、 p 型ベース領域 1 1 1 のドーパント濃度は、たとえば、 1  $\times$  1 0  $^{1.6}$  c m  $^{-.3}$  ~ 1  $\times$  1 0  $^{1.8}$  c m  $^{-.3}$  である。 n  $^+$  型エミッタ領域 1 1 2 のドーパント濃度は、 1  $\times$  1 0  $^{1.9}$  c m  $^{-.3}$  ~ 5  $\times$  1 0  $^{2.0}$  c m  $^{-.3}$  である。 p  $^+$  型ベースコンタクト領域 1 1 3 のドーパント濃度は、たとえば、 5  $\times$  1 0  $^{1.8}$  c m  $^{-.3}$  ~ 1  $\times$  1 0  $^{2.0}$  c m  $^{-.3}$  である。

#### [0061]

また、半導体基板 1 0 2 の表面 1 0 7 側において隣り合うトレンチ単位 1 1 0 の間には、複数(図 6 では 3 本)のエミッタトレンチ 1 1 6 が形成されている。この実施形態では、複数のエミッタトレンチ 1 1 6 は、たとえばストライプ状(ゲートトレンチ 1 0 8 およびダミートレンチ 1 0 9 に平行)に形成され、半導体基板 1 0 2 の表面 1 0 7 に沿う横方向に互いに等しい間隔を空けて配置されている。互いに隣り合うエミッタトレンチ 1 1 6 の間隔 L 2 (エミッタトレンチ 1 1 6 の側面間の距離)は、たとえば、 3  $\mu$  m 以下、好ましくは、 0 . 8  $\mu$  m ~ 3  $\mu$  m である。また、複数のエミッタトレンチ 1 1 6 は、ゲートトレンチ 1 0 8 およびダミートレンチ 1 0 9 と同じ深さで形成されている。これにより、エミッタトレンチ 1 1 6 を、ゲートトレンチ 1 0 8 およびダミートレンチ 1 0 9 と同一工程で形成することができるので、製造工程を簡略化することができる。

## [0062]

複数のエミッタトレンチ 1 1 6 のうち、ダミートレンチ 1 0 9 に隣り合うトレンチ (ダミートレンチ 1 0 9 との間にトレンチを介さずに対向するトレンチ) は、ダミートレンチ 1 0 9 との間に 0 . 5  $\mu$  m ~ 2 0  $\mu$  m の間隔 L  $_3$  (エミッタトレンチ 1 1 6 の側面とダミートレンチ 1 0 9 の側面との距離)を隔てて配置されている。

## [0063]

また、半導体基板 1 0 2 には、 p型フローティング領域 1 1 7 が形成されている。 p型フローティング領域 1 1 7 は、エミッタトレンチ 1 1 6 を介して対向する、互いに隣り合うトレンチ単位 1 1 0 のダミートレンチ 1 0 9 で挟まれた領域に広がっている。 p型フローティング領域 1 1 7 は、電気的にフローティング状態が保たれた半導体領域であって、ゲートトレンチ 1 0 8 に隣り合うダミートレンチ 1 0 9 によって、ゲートトレンチ 1 0 8 と分離されている。 p型フローティング領域 1 1 7 は、この実施形態では、 p型ベース領域 1 1 1 よりも深く形成されている。

## [0064]

p型フローティング領域117は、エミッタトレンチ116の底部に対して半導体基板

10

20

30

40

102の裏面103側に膨出する底部118と、ダミートレンチ109の下方に回り込むオーバーラップ部119とを有している。オーバーラップ部119は、当該ダミートレンチ109の幅方向中央に対してゲートトレンチ108の近い側に位置する端部120を有している。この端部120は、エミッタトレンチ116に対してゲートトレンチ108側にはみ出ていないことが好ましい。

### [0065]

また、 p 型 フローティング領域 1 1 7 のドーパント濃度は、たとえば、  $5 \times 10^{15}$  c m  $^{-3}$  ~  $1 \times 10^{18}$  c m  $^{-3}$  である。

#### [0066]

ゲートトレンチ 1 0 8、ダミートレンチ 1 0 9 およびエミッタトレンチ 1 1 6 には、絶縁膜 1 2 1 (たとえば、酸化シリコン ( S i O  $_2$  ) )を介してゲート電極 1 2 2、第 1 埋め込み電極 1 2 3 および第 2 埋め込み電極 1 2 4 がそれぞれ埋め込まれている。ゲート電極 1 2 2、第 1 埋め込み電極 1 2 4 は、たとえば、ポリシリコン等の導電材料からなる。絶縁膜 1 2 1 は、ゲートトレンチ 1 0 8 の内面、ダミートレンチ 1 0 9 の内面、半導体基板 1 0 2 の表面 1 0 7 およびエミッタトレンチ 1 1 6 の内面に沿って一体的に形成されている。絶縁膜 1 2 1 のゲートトレンチ 1 0 8 内の部分は、ゲート絶縁膜 1 2 5 として機能する。また、第 1 埋め込み電極 1 2 3 および第 2 埋め込み電極 1 2 4 は、後述するエミッタ電極 1 3 2 に電気的に接続されている。

#### [0067]

また、この実施形態では、ゲート電極122および第2埋め込み電極124はそれぞれのトレンチ108,116を開口端まで埋め戻しているのに対して、第1埋め込み電極123は、ダミートレンチ109の深さ方向途中まで埋め戻している。これにより、ダミートレンチ109には、第1埋め込み電極123の上方領域に電極のない空間が形成されている。そして、この空間を開口端まで埋め戻すように、埋め込み絶縁膜126がダミートレンチ109に埋め込まれている。

## [0068]

埋め込み絶縁膜126は、たとえば、ホウ素リンシリケートガラス(BPSG)、酸化シリコン(Si〇2)等の絶縁材料からなり、0.5μm以上の厚さを有している。埋め込み絶縁膜126およびその下の絶縁膜121には、ダミートレンチ109の側面115における $p^+$ 型ベースコンタクト領域113を露出させる除去部127が選択的に形成されている。すなわち、埋め込み絶縁膜126は、ダミートレンチ109の側面115に連なるように、半導体基板102の表面107よりも低い位置の上面128を選択的に有しており、この上面128と表面107との間のダミートレンチ109の側面115の領域に $p^+$ 型ベースコンタクト領域113が露出している。

## [0069]

半導体基板102の表面107には、たとえば、ホウ素リンシリケートガラス(BPSG)、酸化シリコン(SiO2)等の絶縁材料からなる層間膜129が積層されている。層間膜129は、埋め込み絶縁膜126と一体的に形成されている。層間膜129には、半導体基板102の表面107およびダミートレンチ109の開口端に跨るコンタクトホール130が形成されている。このコンタクトホール130は、半導体基板102の表面107およびp<sup>+</sup>型ベースコンタクト領域113を露出させ、ダミートレンチ109の側面115(除去部127)でp<sup>+</sup>型ベースコンタクト領域113を露出させ、ダミートレンチ109の側面115(除去部127)でp<sup>+</sup>型ベースコンタクト領域113は、表面107と側面115との交差によって形成されるダミートレンチ109の角部131に露出している。なお、n<sup>+</sup>型エミッタ領域112は、ゲートトレンチ108の側面114から半導体基板102の表面107に沿う横方向に引き出された引き出し部を選択的に有していて、この引き出し部のみがコンタクトホール130から選択的に露出していてもよい。

## [0070]

層間膜129上には、本発明のコンタクト電極の一例としてのエミッタ電極132が積層されている。エミッタ電極132は、コンタクトホール130に入り込み、半導体基板

10

20

30

40

40

102の表面107においてn<sup>+</sup>型エミッタ領域112に接続され、ダミートレンチ10 9の角部131においてp<sup>+</sup>型ベースコンタクト領域113に接続されている。

### [0071]

次に、半導体装置101の製造方法について説明する。図8A~図8Kは、図6および図7の半導体装置101の製造工程を工程順に説明するための図である。なお、図8A~図8Fが図6に対応する断面を示し、図8G~図8Kが図7に対応する断面を示している。

#### [0072]

半導体装置101を製造するには、図8Aに示すように、n 型の半導体基板102(n 型ドリフト領域106)の表面107にマスク160が形成される。マスク160には、表面107におけるp型フローティング領域117に形成すべき領域を選択的に露出させる開口が形成されている。そして、このマスク160を介して、半導体基板102の表面107に対してp型ドーパントがイオン注入(インプラ)される。これにより、イオン注入領域161が形成される。

## [0073]

次に、図8Bに示すように、半導体基板102が選択的にエッチングされることによって、ゲートトレンチ108、ダミートレンチ109およびエミッタトレンチ116が同時 形成される。

### [0074]

次に、図8Cに示すように、半導体基板102が熱酸化されることによって、ゲートトレンチ108、ダミートレンチ109およびエミッタトレンチ116の内面を含む表面全域に犠牲酸化膜162が形成される。そして、犠牲酸化膜162で覆われた半導体基板102をアニール処理することによって、イオン注入領域161中のp型ドーパントが拡散する(ドライブイン)。このアニール処理は、p型ドーパントがダミートレンチ109の下方に回り込む条件で行われる。これにより、p型フローティング領域117が形成される。この際、半導体基板102が犠牲酸化膜162で覆われているので、基板表面からのイオン抜けを防止することができるので、p型ドーパントを効率よく拡散させることができる。

#### [0075]

次に、図8Dに示すように、犠牲酸化膜162が剥離される。

### [0076]

次に、図8 E に示すように、半導体基板102が熱酸化されることによって、ゲートトレンチ108、ダミートレンチ109およびエミッタトレンチ116の内面を含む表面全域に絶縁膜121(ゲート絶縁膜125)が形成される。

## [0077]

次に、図8Fに示すように、ポリシリコン等の電極材料がゲートトレンチ108、ダミートレンチ109およびエミッタトレンチ116に埋め込まれる。これにより、ゲート電極122、第1埋め込み電極123および第2埋め込み電極124が同時に形成される。

## [0078]

次に、図8Gに示すように、半導体基板102の表面107に対して選択的にn型およびp型ドーパントがイオン注入および拡散されることによって、p型ベース領域1111およびn + 型エミッタ領域112が順に形成される。

## [0079]

次に、図8Hに示すように、第1埋め込み電極123を上面からエッチングすることによって、ゲート電極122および第2埋め込み電極124の埋め込み状態を維持したまま、第1埋め込み電極123のみが選択的に掘り下げられる。

## [0080]

次に、図8Iに示すように、半導体基板102の表面107上に、ホウ素リンシリケートガラス(BPSG)、酸化シリコン(SiO2)等の絶縁材料を堆積させることによって、第1埋め込み電極123の上方空間が当該絶縁材料で埋め戻されると共に、表面107が当該絶縁材料で覆われる。これにより、埋め込み絶縁膜126および層間膜129が

10

20

30

同時に形成される。

#### [0081]

次に、図8Jに示すように、層間膜129および埋め込み絶縁膜126を選択的にエッチングすることによって、コンタクトホール130および除去部127が同時に形成される。

## [0082]

次に、図8Kに示すように、コンタクトホール130内に露出した半導体基板102の表面107に対してp型ドーパントが選択的にイオン注入および拡散される。これにより、 $p^+$ 型ベースコンタクト領域113が形成される。

### [0083]

その後、半導体基板102の表面107側にエミッタ電極132等が形成された後、半導体基板102の裏面103に対して選択的にn型およびp型ドーパントがイオン注入および拡散されることによって、n型バッファ領域105およびp<sup>+</sup>型コレクタ領域104が順に形成される。

#### [0084]

以上のような工程を経ることによって、図6および図7に示す半導体装置101が得られる。なお、図8A~図8Kでは半導体装置101の製造工程の一部を表したに過ぎず、 当該製造工程は、図8A~図8Kで示されなかった工程を含んでいてもよい。

#### [0085]

この半導体装置101によれば、ダミートレンチ109の側面115を $p^+$ 型ベースコンタクト領域113として有効利用することができるので、p型ベース領域111に対するエミッタ電極132の接合面積を、半導体基板102の表面107およびダミートレンチ109の側面115の両面で十分確保することができる。これにより、p型ベース領域111の平面面積を犠牲にすることができるので、ゲートトレンチ108とダミートレンチ109との間隔L1を微細化して、従来に比べて微細なp型ベース領域111を形成することができる。しかも、ダミートレンチ109は、ゲートトレンチ108と同一のマスクを使用して形成することができるため、ゲートトレンチ108に対する位置ずれが生じない。そして、エミッタ電極132のアライメントは、ダミートレンチ109の平面面積を含めたエリアに合わせればよいので、簡単にとることができる。

## [0086]

具体的には、まず、半導体基板102を同一のマスクを用いてエッチングすることによ って、ゲートトレンチ108、ダミートレンチ109およびエミッタトレンチ116を同 時に形成する(図8B)。次に、これらのトレンチ108,109,116にポリシリコ ンを埋め込むことによって、ゲート電極122、第1埋め込み電極123および第2埋め 込み電極124を形成する(図8F)。次に、ダミートレンチ109を選択的に露出させ るマスクを半導体基板102上に形成し、このマスクを介して、ダミートレンチ109内 のポリシリコンの上部を選択的にエッチング除去する。これにより、ダミートレンチ10 9 の第 1 埋め込み電極 1 2 3 の上方領域に空間を形成する(図 8 H)。次に、たとえば C VD法によってBPSG等の絶縁材料を半導体基板102上に堆積させることによって層 間膜129を形成する(図8I)。絶縁材料の一部は、ダミートレンチ109内に埋め込 み絶縁膜126として入り込む。次に、コンタクトホール130を形成するためのマスク を、半導体基板102に対してアライメントする。この際、コンタクトホール130の端 部はダミートレンチ109を覆ってもよいので、アライメントは、半導体基板102の表 面107およびダミートレンチ109の平面面積を含めた広いエリアでとることができる 。そして、当該マスクを介して、層間膜129および埋め込み絶縁膜126を連続してエ ッチングする。これにより、コンタクトホール130および除去部127を同時に形成す る(図8J)。この後、層間膜129をマスクとしてp型ドーパントをイオン注入してp <sup>†</sup> 型ベースコンタクト領域113を自己整合的に形成すれば、ダミートレンチ109の角 部 1 3 1 に p <sup>+</sup> 型ベースコンタクト領域 1 1 3 を確実に形成することができる(図 8 K) 。しかも、コンタクトホール130を比較的広く形成できるので、タングステン(W)等 10

20

30

40

の埋め込み性の良いプラグを用いなくても、アルミニウム (A1) 等を用いたエミッタ電極 132の一部をプラグとして利用することができる。

### [0087]

以上のようなトレンチ構造の微細化の結果、デバイスの短絡耐量とオン電圧とのトレードオフの関係を改善することができるので、電荷促進効果を向上させることができる。よって、低電流域におけるVCF(Sat)を改善することができる。

## [0088]

また、この半導体装置101によれば、ゲート電極122が埋め込まれたゲートトレンチ108(以下、「ゲート接合トレンチ」という)が、n +型エミッタ領域112に接続された第1埋め込み電極123が埋め込まれたダミートレンチ109(以下、「エミッタ接合トレンチ」という)によってp型フローティング領域117から分離されている。これにより、p型フローティング領域117とゲート接合トレンチとの接合を防止することができる。そのため、ゲート接合トレンチとp型フローティング領域117との間の浮遊容量をなくすことができる。

#### [0089]

一方、ゲート接合トレンチが深さ方向に渡って接合している n ・型ドリフト領域 1 0 6 は p ・型コレクタ領域 1 0 4 と共に接地されるものである。そのため、スイッチング動作時に、ゲート接合トレンチと n ・型ドリフト領域 1 0 6 との間の容量変化が安定するので、ノイズが発生し難い。これらの結果、スイッチング動作時のノイズの発生およびスイッチング損失を低減することができる。

#### [0090]

また、エミッタ接合トレンチと、ゲート接合トレンチとの間隔 L  $_1$  が 2  $\mu$  m以下であるので、耐圧を良好に保持することもできる。

#### [0091]

さらに、この半導体装置101によれば、エミッタ接合トレンチの底部まで p 型フローティング領域117(オーバーラップ部119)が形成されているので、スイッチングオフ動作時にエミッタ接合トレンチに負荷するコレクタ・エミッタ電圧を緩和することができる。そのため、急峻な電圧変化(dv/dt)に対してデバイスの破壊を防止することができる。

### [0092]

また、p型ベース領域 1 1 1 よりも深いp型フローティング領域 1 1 7 によって耐圧を向上できる一方、p型ベース領域 1 1 1 は浅くてもよいので、p型ベース領域 1 1 1 の深さを適切に設計することによってチャネル長(ゲートトレンチ 1 0 8 の深さ方向の長さ)を短くしてオン電圧の上昇を抑制することもできる。

## [0093]

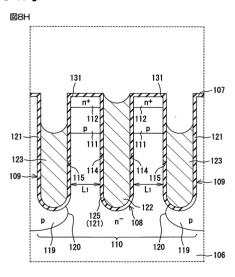

図9は、本発明の第4実施形態に係る半導体装置141の模式的な断面図である。図10は、図9の破線で囲まれた部分の拡大図である。図9および図10において、前述の図6および図7に示された各部と対応する部分には同一の参照符号を付して示す。

## [0094]

前述の第3実施形態では、トレンチ単位110は、一対のダミートレンチ109と、一対のダミートレンチ109の間に挟まれたゲートトレンチ108とを含んでいた。これに対し、第4実施形態の半導体装置141は、一対のゲートトレンチ142と、一対のゲートトレンチ142の間に挟まれたダミートレンチ143とを含むトレンチ単位144を有している。この場合、ゲートトレンチ142とエミッタトレンチ116との間隔L3(ゲートトレンチ142の側面とエミッタトレンチ116の側面との距離)は、2μm以下であることが好ましい。

### [0095]

各トレンチ単位 1 4 4 において、ダミートレンチ 1 4 3 の両側(各ゲートトレンチ 1 4 2 との間の領域)には、p型ベース領域 1 4 5 が形成され、さらにp型ベース領域 1 4 5 の表面部にn<sup>+</sup>型エミッタ領域 1 4 6 およびp<sup>+</sup>型ベースコンタクト領域 1 4 7 が形成さ

10

20

30

40

れている(図10参照)。この実施形態では、p型ベース領域145とn<sup>-</sup>型ドリフト領域106との界面がゲートトレンチ142の中央部もしくは上部に設定されていて、p型ベース領域145は、半導体基板102の比較的浅くに拡散形成されている。

#### [0096]

n + 型エミッタ領域 1 4 6 および p + 型ベースコンタクト領域 1 4 7 は、ゲートトレンチ 1 4 2 とダミートレンチ 1 4 3 との間の領域において互いに隣接して配置されている。 具体的には、 n + 型エミッタ領域 1 4 6 が各ゲートトレンチ 1 4 2 の側面 1 4 8 に沿って一つずつ形成され、 p + 型ベースコンタクト領域 1 4 7 がダミートレンチ 1 4 3 の両側面 1 4 9 に沿って一つずつ形成されている。これにより、 n + 型エミッタ領域 1 4 6 は、半導体基板 1 0 2 の表面 1 0 7 およびゲートトレンチ 1 4 2 の側面 1 4 8 に露出している。一方、 p + 型ベースコンタクト領域 1 4 7 は、半導体基板 1 0 2 の表面 1 0 7 およびダミートレンチ 1 4 3 の側面 1 4 9 に露出している。

## [0097]

また、半導体基板102には、p型フローティング領域150が形成されている。p型フローティング領域150は、複数のエミッタトレンチ116の各間に広がっている。p型フローティング領域150は、電気的にフローティング状態が保たれた半導体領域であって、ゲートトレンチ142に隣り合うエミッタトレンチ116によって、ゲートトレンチ142と分離されている。p型フローティング領域150は、この実施形態では、p型ベース領域145よりも深く形成されている。

## [0098]

p型フローティング領域 1 5 0 は、エミッタトレンチ 1 1 6 の底部に対して半導体基板 1 0 2 の裏面 1 0 3 側に膨出する底部 1 5 1 と、ゲートトレンチ 1 4 2 に隣り合うエミッタトレンチ 1 1 6 の下方に回り込むオーバーラップ部 1 5 2 とを有している。オーバーラップ部 1 5 2 は、当該エミッタトレンチ 1 1 6 の幅方向中央に対してゲートトレンチ 1 4 2 の近い側に位置する端部 1 5 3 を有している。この端部 1 5 3 は、エミッタトレンチ 1 1 6 に対してゲートトレンチ 1 4 2 側にはみ出ていないことが好ましい。

## [0099]

このような p 型フローティング領域 1 5 0 は、たとえば、前述の p 型フローティング領域 1 1 7 と同様に形成することができる。

### [0100]

ダミートレンチ143には、絶縁膜121を介して第1埋め込み電極154が埋め込まれている。第1埋め込み電極154は、たとえば、ポリシリコン等の導電材料からなり、ゲート電極122に電気的に接続されている。また、第1埋め込み電極154は、ダミートレンチ143の深さ方向途中まで埋め戻している。これにより、ダミートレンチ143には、第1埋め込み電極154の上方領域に電極のない空間が形成されている。そして、この空間を開口端まで埋め戻すように、埋め込み絶縁膜155がダミートレンチ143に埋め込まれている。

## [0101]

埋め込み絶縁膜155は、たとえば、ホウ素リンシリケートガラス(BPSG)、酸化シリコン(Si〇2)等の絶縁材料からなり、0.5μm以上の厚さを有している。埋め込み絶縁膜155およびその下の絶縁膜121には、ダミートレンチ143の両側面149における $p^+$ 型ベースコンタクト領域147を露出させる除去部156が選択的に形成されている。すなわち、埋め込み絶縁膜155は、ダミートレンチ143の両側面149に連なるように、半導体基板102の表面107よりも低い位置の上面157を選択的に有しており、この上面157と表面107との間のダミートレンチ143の両側面149の領域に $p^+$ 型ベースコンタクト領域147が露出している。

## [0102]

層間膜129には、ダミートレンチ143を挟んで対向するp型ベース領域145に跨るコンタクトホール158が形成されている。このコンタクトホール158は、半導体基板102の表面107でn<sup>+</sup>型エミッタ領域146およびp<sup>+</sup>型ベースコンタクト領域1

10

20

30

40

47を露出させ、ダミートレンチ143の両側面149(除去部156)で $p^+$ 型ベースコンタクト領域147を露出させる。つまり、 $p^+$ 型ベースコンタクト領域147は、表面107と側面149との交差によって形成されるダミートレンチ143の両角部159に露出している。なお、 $p^+$ 型エミッタ領域146は、ゲートトレンチ142の側面148から半導体基板102の表面107に沿う横方向に引き出された引き出し部を選択的に有していて、この引き出し部のみがコンタクトホール158から選択的に露出していてもよい。

## [0103]

そして、エミッタ電極 1 3 2 は、コンタクトホール 1 5 8 に入り込み、半導体基板 1 0 2 の表面 1 0 7 において n <sup>+</sup>型エミッタ領域 1 4 6 に接続され、ダミートレンチ 1 4 3 の両角部 1 5 9 において p <sup>+</sup>型ベースコンタクト領域 1 4 7 に接続されている。

[0104]

この半導体装置141によっても、第3実施形態の半導体装置101と同様の効果を達成することができる。

[0105]

以上、本発明の実施形態を説明したが、本発明は、他の形態で実施することもできる。

[0106]

たとえば、前述の各実施形態の開示から把握される上記特徴は、異なる実施形態間でも 互いに組み合わせることができる。

[0107]

また、前述の実施形態では、半導体装置1,31,101,141が備えるIGBTの構成のみを図示したが、本発明の半導体装置は、IGBT以外の素子(たとえば、MOSFET、ダイオード等)をIGBTの形成領域とは異なる領域に備えていてもよい。

[0108]

その他、特許請求の範囲に記載された事項の範囲で種々の設計変更を施すことが可能である。

[0109]

なお、この明細書および図面の記載から、特許請求の範囲に記載した発明以外にも、以下のような特徴が抽出され得る。

[0110]

(項1)半導体層と、前記半導体層に形成されたゲートトレンチと、前記ゲートトレンチにゲート絶縁膜を介して埋め込まれたゲート電極と、前記ゲートトレンチの側方に所定の間隔を空けて形成されたダミートレンチと、前記ゲートトレンチと前記ダミートレンチとの間の領域において、前記半導体層の表面側から前記ゲートトレンチの深さ方向に順に配置された n +型エミッタ領域、p型ベース領域および n ・型ドリフト領域と、前記 n ・型ドリフト領域に対して前記半導体層の裏面側に配置された p +型コレクタ領域と、前記ダミートレンチに埋め込まれ、前記半導体層の前記表面に対して前記ダミートレンチの底側に上面を有する埋め込み絶縁膜であって、前記ダミートレンチの側面における前記表面から前記上面までの部分に前記 p型ベース領域の一部をコンタクト領域として選択的に露出させる埋め込み絶縁膜と、前記ダミートレンチの前記埋め込み絶縁膜の上方領域に埋め込まれ、前記ダミートレンチの前記側面において前記コンタクト領域に接続されたコンタクト電極とを含む、半導体装置。

[0111]

この構成によれば、ダミートレンチの側面をコンタクト領域として有効利用することができるので、p型ベース領域に対するコンタクト電極の接合面積を十分確保することができる。これにより、p型ベース領域の平面面積を犠牲にすることができるので、ゲートトレンチとダミートレンチとの間隔を微細化して、従来に比べて微細なp型ベース領域を形成することができる。しかも、ダミートレンチは、ゲートトレンチと同一のマスクを使用して形成することができるため、ゲートトレンチに対する位置ずれが生じない。そして、コンタクト電極のアライメントは、ダミートレンチの平面面積を含めたエリアに合わせれ

10

20

30

40

ばよいので、簡単にとることができる。

#### [0112]

また、トレンチ構造の微細化の結果、デバイスの短絡耐量とオン電圧とのトレードオフの関係を改善することができるので、電荷促進効果を向上させることができる。よって、低電流域におけるVCE(sat)を改善することができる。

## [0113]

(項2)前記半導体装置は、前記ダミートレンチの前記埋め込み絶縁膜の下方領域に絶縁膜を介して埋め込まれた第1埋め込み電極をさらに含む、項1に記載の半導体装置。

#### [0114]

(項3)前記半導体装置は、一対の前記ダミートレンチと、当該一対のダミートレンチの間に挟まれたゲートトレンチを含むトレンチ単位を有する、項2に記載の半導体装置。

#### [0115]

(項4)前記第1埋め込み電極は、前記n<sup>+</sup>型エミッタ領域と電気的に接続されている、項3に記載の半導体装置。

#### [0116]

(項5)前記トレンチ単位は、前記半導体層の前記表面に沿う横方向に複数形成されており、前記半導体装置は、互いに隣り合う前記トレンチ単位の間に形成された複数のエミッタトレンチと、前記エミッタトレンチに絶縁膜を介して埋め込まれ、前記 n +型エミッタ領域と電気的に接続された第2埋め込み電極と、前記トレンチ単位の前記ダミートレンチと、その隣の前記トレンチ単位の前記ダミートレンチとの間に形成されたp型フローティング領域とをさらに含む、項4に記載の半導体装置。

#### [0117]

(項6)前記p型フローティング領域は、前記p型ベース領域よりも深く形成され、前記ダミートレンチの下方に回り込むオーバーラップ部を含む、項5に記載の半導体装置。

## [0118]

この構成によれば、 n <sup>+</sup>型エミッタ領域に接続された第1埋め込み電極が埋め込まれた ダミートレンチ(以下、「エミッタ接合トレンチ」という)の底部まで p型フローティング領域(オーバーラップ部)が形成されているので、スイッチングオフ動作時にエミッタ 接合トレンチに負荷するコレクタ・エミッタ電圧を緩和することができる。そのため、急峻な電圧変化(d v / d t)に対してデバイスの破壊を防止することができる。

## [0119]

また、 p 型ベース領域よりも深い p 型フローティング領域によって耐圧を向上できる一方、 p 型ベース領域は浅くてもよいので、 p 型ベース領域の深さを適切に設計することによってオン電圧の上昇を抑制することもできる。

#### [0120]

(項7)前記オーバーラップ部は、前記ダミートレンチの幅方向中央に対して前記ゲートトレンチの近い側に位置する端部を有している、項6に記載の半導体装置。

#### [0121]

この構成により、エミッタ接合トレンチにかかるコレクタ - エミッタ電圧を、より良好に緩和することができる。

## [0122]

(項8)前記半導体装置は、一対の前記ゲートトレンチと、当該一対の前記ゲートトレンチの間に挟まれたダミートレンチを含むトレンチ単位を有する、項2に記載の半導体装置。

### [0123]

(項9)前記第1埋め込み電極は、前記ゲート電極と電気的に接続されている、項8に記載の半導体装置。

## [0124]

(項10)前記トレンチ単位は、前記半導体層の前記表面に沿う横方向に複数形成されており、前記半導体装置は、互いに隣り合う前記トレンチ単位の間に形成された複数のエ

10

20

\_ \_

30

ミッタトレンチと、前記エミッタトレンチに絶縁膜を介して埋め込まれ、前記 n <sup>+</sup>型エミッタ領域と電気的に接続された第2埋め込み電極と、前記複数のエミッタトレンチの間に形成されたp型フローティング領域とをさらに含む、項9に記載の半導体装置。

#### [0125]

(項11)前記p型フローティング領域は、前記p型ベース領域よりも深く形成され、前記エミッタトレンチの下方に回り込むオーバーラップ部を含む、項10に記載の半導体装置。

### [0126]

この構成によれば、 n <sup>+</sup>型エミッタ領域に接続された第 2 埋め込み電極が埋め込まれたエミッタトレンチ(以下、「エミッタ接合トレンチ」という)の底部まで p 型フローティング領域(オーバーラップ部)が形成されているので、スイッチングオフ動作時にエミッタ接合トレンチに負荷するコレクタ・エミッタ電圧を緩和することができる。そのため、急峻な電圧変化( d v / d t )に対してデバイスの破壊を防止することができる。

## [0127]

また、 p型ベース領域よりも深い p型フローティング領域によって耐圧を向上できる一方、 p型ベース領域は浅くてもよいので、 p型ベース領域の深さを適切に設計することによってオン電圧の上昇を抑制することもできる。

#### [0128]

(項12)前記オーバーラップ部は、前記エミッタトレンチの幅方向中央に対して前記 ゲートトレンチの近い側に位置する端部を有している、項11に記載の半導体装置。

#### [0129]

この構成により、エミッタ接合トレンチにかかるコレクタ - エミッタ電圧を、より良好に緩和することができる。

## [0130]

(項13)前記埋め込み絶縁膜は、0.5 $\mu$ m以上の厚さを有している、項1~12のいずれか一項に記載の半導体装置。

## [0131]

(項14)前記ダミートレンチは、前記ゲートトレンチとの間に  $2 \mu m$ 以下の間隔を隔てて配置されている、項1~13のいずれか一項に記載の半導体装置。

## [0132]

(項15)前記 $n^+$ 型エミッタ領域は、 $1 \times 10^{19}$  c  $m^{-3} \sim 5 \times 10^{20}$  c  $m^{-3}$  の n 型ドーパント濃度を有している、項1~14のいずれか一項に記載の半導体装置。

#### [0133]

(項 1 6 ) 前記 p 型ベース領域は、  $1 \times 10^{16}$  c m  $^{-3}$  ~  $1 \times 10^{18}$  c m  $^{-3}$  の p 型ドーパント濃度を有している、項 1 ~ 1 5 のいずれか一項に記載の半導体装置。

## [0134]

(項17)前記 $n^{-}$ 型ドリフト領域は、 $1 \times 10^{13}$  c m  $^{-3}$  ~  $5 \times 10^{14}$  c m  $^{-3}$  の n 型ドーパント濃度を有している、項1 ~ 16のいずれか一項に記載の半導体装置。

## [0135]

(項18)前記 $p^+$ 型コレクタ領域は、 $1 \times 10^{15}$  cm $^{-3}$ ~ $2 \times 10^{19}$  cm $^{-3}$ の p型ドーパント濃度を有している、項1~17のいずれか一項に記載の半導体装置。

## [0136]

(項19)半導体層と、前記半導体層に形成された複数のゲートトレンチと、前記複数のゲートトレンチにゲート絶縁膜を介して埋め込まれたゲート電極と、各前記ゲートトレンチの側方において、前記半導体層の表面側から前記ゲートトレンチの深さ方向に順に配置された n +型エミッタ領域、 p型ベース領域および n ・型ドリフト領域と、前記 n ・型ドリフト領域に対して前記半導体層の裏面側に配置された p +型コレクタ領域と、互いに隣り合う前記複数のゲートトレンチの間に形成された複数のエミッタトレンチと、 p型ベース領域の表面部において、 n +型エミッタ領域に対して前記ゲートトレンチの反対側に形成された p +型ベースコンタクト領域と、前記複数のエミッタトレンチに絶縁膜を介して

10

20

30

埋め込まれ、前記 n <sup>+</sup>型エミッタ領域と電気的に接続された埋め込み電極と、前記複数のエミッタトレンチの間に形成された p 型フローティング領域と、前記半導体層上に形成された層間膜とを含み、前記 p 型フローティング領域は、前記 p 型ベース領域よりも深く形成され、前記複数のエミッタトレンチのうち前記ゲートトレンチに最も近いエミッタトレンチの下方に回り込み、前記エミッタトレンチの幅方向中央に対して前記ゲートトレンチに近い側に位置する端部を有するオーバーラップ部を含み、前記 p <sup>+</sup>型ベースコンタクト領域と前記エミッタトレンチとの間には、前記 p 型ベース領域が前記半導体層の前記表面に露出しており、前記層間膜は、前記 n <sup>+</sup>型エミッタ領域の全体および前記 p <sup>+</sup>型ベースコンタクト領域の一部を覆うように形成されている、半導体装置。

#### [0137]

この構成によれば、埋め込み電極が埋め込まれたエミッタトレンチ(以下、「エミッタ接合トレンチ」という)の底部までp型フローティング領域(オーバーラップ部)が形成されている。これにより、スイッチングオフ動作時にエミッタ接合トレンチに負荷するコレクタ・エミッタ電圧を緩和することができる。そのため、急峻な電圧変化(d v / d t ) に対してデバイスの破壊を防止することができる。

#### [0138]

また、 p 型ベース領域よりも深い p 型フローティング領域によって耐圧を向上できる一方、 p 型ベース領域は浅くてもよいので、 p 型ベース領域の深さを適切に設計することによってチャネル長を短くしてオン電圧の上昇を抑制することもできる。

#### [0139]

(項20)前記p型フローティング領域は、前記エミッタトレンチの底部に対して前記 半導体層の裏面側に膨出する底部を有していてもよい。

## [0140]

(項21)前記エミッタトレンチは、前記ゲートトレンチと同じ深さで形成されていることが好ましい。

## [0141]

この場合、エミッタトレンチをゲートトレンチと同一工程で形成することができるので 、製造工程を簡略化することができる。

## [0142]

(項22)前記 $n^+$ 型エミッタ領域は、 $1 \times 10^{19}$  cm $^{-3} \sim 5 \times 10^{20}$  cm $^{-3}$  の n 型ドーパント濃度を有していてもよい。

## [0143]

(項23)前記 p 型ベース領域は、 $1 \times 10^{16}$  c m  $^{-3}$  ~  $1 \times 10^{18}$  c m  $^{-3}$  の p 型 ドーパント 濃度を有していてもよい。

## [0144]

(項24)前記 $n^{-2}$ 型ドリフト領域は、 $1 \times 10^{13}$  cm $^{-3} \sim 5 \times 10^{14}$  cm $^{-3}$  の n 型ドーパント濃度を有していてもよい。

#### [0145]

(項25)前記 $p^+$ 型コレクタ領域は、 $1 \times 10^{15}$  c m  $^{-3}$  ~  $2 \times 10^{19}$  c m  $^{-3}$  の p 型ドーパント濃度を有していてもよい。

## [0146]

(項26)前記 n <sup>+</sup>型エミッタ領域は、前記ゲートトレンチの側面から前記半導体層の表面に沿う横方向に引き出された引き出し部を選択的に有していることが好ましい。

#### [0147]

(項27)半導体層と、前記半導体層に形成された複数のゲートトレンチと、前記複数のゲートトレンチにゲート絶縁膜を介して埋め込まれたゲート電極と、各前記ゲートトレンチの側方において、前記半導体層の表面側から前記ゲートトレンチの深さ方向に順に配置された n +型エミッタ領域、p型ベース領域および n -型ドリフト領域と、前記 n -型ドリフト領域に対して前記半導体層の裏面側に配置された p +型コレクタ領域と、互いに隣リ合う前記複数のゲートトレンチの間に形成された複数のエミッタトレンチと、前記複数

10

20

30

30

のエミッタトレンチに絶縁膜を介して埋め込まれ、前記 n <sup>+</sup>型エミッタ領域と電気的に接続された埋め込み電極と、前記複数のエミッタトレンチの間に形成されたp型フロース領域 が領域と、前記ゲートトレンチとの間に前記 n <sup>+</sup>型エミッタ領域、前記p型ベース領域 および前記 n <sup>-</sup>型ドリフト領域が形成されるように、前記ゲートトレンチの側方に所定の間隔を空けて形成されたダミートレンチと、前記ダミートレンチに埋め込み絶縁膜であって、前記ダミートレンチの側面における前記表面から前記上面までの部分に前記する一次領域の一部をコンタクト領域として選択的に露出させる埋め込み絶縁膜と、前記ダミートレンチの前記埋め込み絶縁膜の上方領域に埋め込まれ、前記ダミートレンチの前記に接続されたコンタクト電極とを含み、前記p型ベース領域よりも深く形成され、前記複数のエミッタトレンチの行領域は、前記p型ベース領域よりも深く形成され、前記複数のエミッタトレンチの対領域は、前記p型ベース領域よりも深く形成され、前記複数のエミッタトレンチの行領域は、前記を含む、前記で一トトレンチに近い側に位置する端部を有するオーバーラップ部を含む、半導体装置。

#### [0148]

この構成によれば、ダミートレンチの側面をコンタクト領域として有効利用することができるので、p型ベース領域に対するコンタクト電極の接合面積を十分確保することができる。これにより、p型ベース領域の平面面積を犠牲にすることができるので、ゲートトレンチとダミートレンチとの間隔を微細化して、従来に比べて微細なp型ベース領域を形成することができる。しかも、ダミートレンチは、ゲートトレンチと同一のマスクを使用して形成することができるため、ゲートトレンチに対する位置ずれが生じない。そして、コンタクト電極のアライメントは、ダミートレンチの平面面積を含めたエリアに合わせればよいので、簡単にとることができる。

#### [0149]

また、トレンチ構造の微細化の結果、デバイスの短絡耐量とオン電圧とのトレードオフの関係を改善することができるので、電荷促進効果を向上させることができる。よって、低電流域におけるVCF(sat)を改善することができる。

#### [ 0 1 5 0 ]

(項28)前記半導体装置は、前記ダミートレンチの前記埋め込み絶縁膜の下方領域に 絶縁膜を介して埋め込まれた第1埋め込み電極をさらに含んでいてもよい。

## [0151]

(項29)前記半導体装置は、一対の前記ダミートレンチと、当該一対のダミートレンチの間に挟まれたゲートトレンチを含むトレンチ単位を有していてもよい。

## [ 0 1 5 2 ]

(項30)前記ダミートレンチは、前記第1埋め込み電極が前記n<sup>+</sup>型エミッタ領域と電気的に接続されることによって前記エミッタトレンチを兼ねていることが好ましい。

#### [0153]

(項31)前記半導体装置は、一対の前記ゲートトレンチと、当該一対の前記ゲートトレンチの間に挟まれたダミートレンチを含むトレンチ単位を有していてもよい。

### [0154]

この場合、(項32)前記第1埋め込み電極は、前記ゲート電極と電気的に接続されていることが好ましい。

#### [0155]

(項33)前記埋め込み絶縁膜は、0.5 $\mu$ m以上の厚さを有していることが好ましい。 【実施例】

## [0156]

次に、本発明を実施例に基づいて説明するが、本発明は下記の実施例によって限定されるものではない。

#### [0157]

図6に示す半導体装置101の構造に関して、短絡耐量とオン電圧(VCE)とのトレ

10

20

30

ードオフの関係の改善効果が、ゲートトレンチ 1 0 8 とダミートレンチ 1 0 9 との間隔 L  $_1$  によってどのように変化するかを確認するため、当該間隔 L  $_1$  が互いに異なる 4 種類のデバイスの V  $_C$  E - I  $_C$  f 特性を調べた。結果を図 1 1 に示す。図 1 1 において、デバイス A (トレンチ間隔 L  $_1$  = 2  $_\mu$  m  $_\tau$  一点鎖線)およびデバイス C (トレンチ間隔 L  $_1$  = 3 . 5  $_\mu$  m  $_\tau$  破線)とした。

## [0158]

図11によると、トレンチ間隔L $_1$ が狭いほど、立ち上がりの $_{CE}$ (sat)が低く、定常損失が低いことが確認できた(図11の右下拡大図参照)。また、 $_{ICf}$ の高電流域では、トレンチの微細化( $_{p}$ 型ベース領域111の体積低減)によって飽和電流密度が低くなっており、短絡耐量が向上していることが確認できた。

【符号の説明】

## [0159]

- 1 半導体装置

- 2 半導体基板

- 3 裏面

- 4 p <sup>+</sup>型コレクタ領域

- 5 n型バッファ領域

- 6 n <sup>-</sup> 型ドリフト領域

- 7 表面

- 8 ゲートトレンチ

- 10 p型ベース領域

- 13 n <sup>+</sup>型エミッタ領域

- 14 エミッタトレンチ

- 15 p型フローティング領域

- 16 底部

- 17 オーバーラップ部

- 18 端部

- 19 絶縁膜

- 20 ゲート電極

- 2 1 埋め込み電極

- 2 2 ゲート絶縁膜

- 3 1 半導体装置

- 33 ゲートトレンチ

- 3 4 p型ベース領域

- 35 n <sup>+</sup>型エミッタ領域

- 3 8 引き出し部

- 101 半導体装置

- 102 半導体基板

- 103 裏面

- 1 0 4 p <sup>+</sup>型コレクタ領域

- 106 n<sup>-</sup>型ドリフト領域

- 107 表面

- 108 ゲートトレンチ

- 109 ダミートレンチ

- 1 1 0 トレンチ単位

- 111 p型ベース領域

- 1 1 2 n <sup>+</sup>型エミッタ領域

- 1 1 3 p <sup>+</sup>型ベースコンタクト領域

- 114 側面

- 1 1 5 側面

10

20

30

40

- 116 エミッタトレンチ

- 117 p型フローティング領域

- 118 底部

- 119 オーバーラップ部

- 1 2 0 端部

- 1 2 1 絶縁膜

- 122 ゲート電極

- 123 第1埋め込み電極

- 124 第2埋め込み電極

- 1 2 5 ゲート絶縁膜

- 126 埋め込み絶縁膜

- 1 2 7 除去部

- 128 上面

- 132 エミッタ電極

- 141 半導体装置

- 142 ゲートトレンチ

- 143 ダミートレンチ

- 1 4 4 トレンチ単位

- 1 4 5 p型ベース領域

- 1 4 6 n + 型エミッタ領域

- 1 4 7 p + 型ベースコンタクト領域

- 148 側面

- 149 側面

- 150 p型フローティング領域

- 151 底部

- 152 オーバーラップ部

- 153 端部

- 154 第1埋め込み電極

- 155 埋め込み絶縁膜

- 156 除去部

- 157 上面

- 159 角部

30

10

【図面】

【図1】

【図2】

20

【図3A】

【図3B】

30

40

【図3C】

【図3D】

10

【図3E】

【図3F】

30

【図3G】

【図3H】

【図3I】

【図4】

【図5】

【図6】

【図7】

【図8A】

## 【図8B】

## 【図8C】

20

10

# 【図8D】

# 【図8E】

30

## 【図8F】

## 【図8G】

10

20

30

## 【図8H】

## 【図8I】

## 【図8」】

## 【図8K】

10

## 【図9】

## 【図10】

30

20

# 【図11】

```

フロントページの続き

```

```

(51)国際特許分類

FΙ

H 0 1 L 29/423 (2006.01)

H 0 1 L

29/78

652K

H 0 1 L

29/49 (2006.01)

H 0 1 L

6 5 2 M

29/78

H 0 1 L

29/78

653C

6 5 5 A

H 0 1 L

29/78

6 5 5 B

H 0 1 L

29/78

H 0 1 L

29/78

6 5 8 A

H 0 1 L

29/78

6 5 8 G

H 0 1 L

S

29/44

H 0 1 L

29/58

G

(32)優先日

平成24年8月21日(2012.8.21)

(33)優先権主張国・地域又は機関

日本国(JP)

(56)参考文献

中国特許出願公開第102244095(CN,A)

国際公開第2012/034372(WO,A1)

特開2011-204808(JP,A)

特表2005-524970(JP,A)

特開2009-54903(JP,A)

特開2005-340626(JP,A)

特開2012-151470(JP,A)

特開2011-204803(JP,A)

特開2007-165635(JP,A)

特開2010-171057(JP,A)

米国特許出願公開第2010/0078756(US,A1)

(58)調査した分野

(Int.Cl., DB名)

H01L 21/336

H01L 21/76

H01L 29/41

H01L 29/423

H01L 29/49

H01L 29/78

```

H01L 29/739