# (19) 中华人民共和国国家知识产权局

# (12) 发明专利

(10) 授权公告号 CN 108492844 B (45) 授权公告日 2020. 10. 16

(21)申请号 201810254478.5

(22)申请日 2018.03.26

(65) 同一申请的已公布的文献号 申请公布号 CN 108492844 A

(43) 申请公布日 2018.09.04

(73) 专利权人 上海华虹宏力半导体制造有限公司

地址 201203 上海市浦东新区张江高科技 园区祖冲之路1399号

(72) 发明人 杨光军 高超

(74) 专利代理机构 上海思微知识产权代理事务 所(普通合伙) 31237

代理人 屈蘅

(51) Int.CI.

**G11C** 16/08 (2006.01)

G11C 16/10 (2006.01) G11C 16/24 (2006.01)

### (56) 对比文件

CN 103236269 A, 2013.08.07

CN 1147314 A,1997.04.09

CN 107204203 A,2017.09.26

CN 101208751 A,2008.06.25

CN 101986389 A,2011.03.16

CN 102385920 A,2012.03.21

US 6765825 B1,2004.07.20

CN 1134196 A,1996.10.23

审查员 李妮

权利要求书1页 说明书3页 附图1页

#### (54) 发明名称

一种双分离栅闪存阵列及其编程方法

#### (57) 摘要

本发明公开一种双分离栅闪存阵列及其编程方法,所述双分离栅闪存阵列包括M\*N的存储单元,每个存储单元的控制栅线CGO/CG1与位线BL0/BL1平行而与字线WL垂直,本发明之双分离栅闪存阵列及其编程方法适合于低功耗的场合。

- 1.一种双分离栅闪存阵列,包括M\*N的存储单元,其特征在于:每个存储单元的控制栅线CG0/CG1与位线BL0/BL1平行而与字线WL垂直,每个存储单元包括两个存储位,同一存储单元的两个存储位分别对应一控制栅且每个控制栅分别连接不同的控制栅线。

- 2.如权利要求1所述的一种双分离栅闪存阵列,其特征在于:在列方向,第一控制栅线CG0j和第二控制栅线CG1j分别连接至每一列的存储单元的第一控制栅区和第二控制栅区,j=0,1,2,3,……,N-1,位线BL0连接至第一列的存储单元的源极端,位线BLj连接至第j列的存储单元的漏极端和第j+1列的存储单元的源极端,j=1,2,3,……,N-1,位线BLN连接至第N列的存储单元的漏极端。

- 3.如权利要求2所述的一种双分离栅闪存阵列,其特征在于:于编程时,对选中的存储单元,使其位线电流为0,以适合低功耗的场合。

- 4.如权利要求3所述的一种双分离栅闪存阵列,其特征在于:于编程时,对选中的存储单元,设置其字线电压 $WL=-5V\sim-10V$ ,第一位线BL0和第二位线电压BL1=BL0=0V,第一控制栅线电压 $CG0=0\sim-8V$ ,第二控制栅线电压 $CG1=5V\sim10V$ 。

- 5.如权利要求4所述的一种双分离栅闪存阵列,其特征在于:对于选中存储单元所在行的其他未选中存储单元,该未选中存储单元的字线电压为WL=-5V~-10V,该未选中存储单元列方向上的控制栅线电压CG0和CG1均为0V,因此该未选中存储单元上不会发生隧穿效应从而不会发生编程动作。

- 6.如权利要求4所述的一种双分离栅闪存阵列,其特征在于:对于选中存储单元所在列的其他未选中存储单元,该未选中存储单元的第二控制栅线电压为CG1=5V~10V、第一控制栅线电压为CG0=0~-8V,若不在同一行,则字线电压WL=0V,在该未选中存储单元上不会发生隧穿效应从而不会发生编程动作,对于选中存储单元的未选中存储位,虽然字线电压WL=-5V~-10V,但该未选中存储位对应的第一控制栅线电压CG0=0~-8V,在该未选中存储位上不会发生隧穿效应从而不会发生编程动作。

- 7.如权利要求4所述的一种双分离栅闪存阵列,其特征在于:对于未 选中存储单元所在行和所在列,行方向上,字线电压WL=0V,列方向上,第一和第二控制栅线电压CG0、CG1均为0V,在该未选中存储单元上都不会发生隧穿效应从而不会发生编程动作。

- 8.一种双分离栅闪存阵列的编程方法,其特征在于:所述编程方法用于对如权利要求 1-7任意一项所述的双分离栅闪存阵列进行编程,且于编程时采用多晶硅反转的隧道效应 的方式。

- 9. 如权利要求8所述的一种双分离栅闪存阵列的编程方法,其特征在于:于编程时,对选中的存储单元,使其位线电流为0,以适合低功耗的场合。

- 10. 如权利要求9所述的一种双分离栅闪存阵列的编程方法,其特征在于:于编程时,对选中的存储单元,设置其字线电压WL= $-5V\sim-10V$ ,第一位线BL0和第二位线电压BL1=BL0=0V,第一控制栅线电压CG0= $0\sim-8V$ ,第二控制栅线电压CG1= $5V\sim10V$ 。

# 一种双分离栅闪存阵列及其编程方法

#### 技术领域

[0001] 本发明涉及一种闪存及其编程方法,特别是涉及一种双分离栅闪存阵列及其编程方法。

# 背景技术

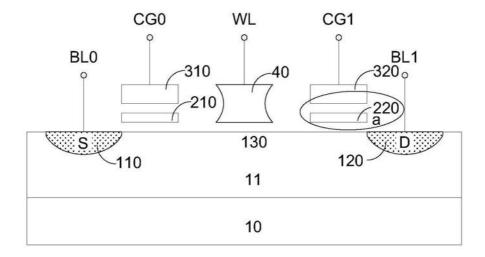

[0002] 图1为一种双分离栅闪存的单元结构示意图。如图1所示,一种双分离栅闪存单元,包括:半导体P型衬底(P\_sub)10,其上设置N阱(N-Well)11,N阱11上具有间隔设置的源极区域(S)110和漏极区域(D)120及沟道区130;沟道区130,位于源极区域(S)110和漏极区域(D)120之间;第一位线BL0和第二位线BL1,分别连接于源极区域110和漏极区域120;第一浮栅210,设置于源极区域110右上方之沟道区130上方;第二浮栅220,设置于漏极区域120左上方之沟道区130上方,第一浮栅210和第二浮栅220分别构成第一存储位单元和第二存储位单元;第一控制栅310和第二控制栅320,分别设置于第一浮栅210和第二浮栅220上方,第一和第二控制栅线分别连接第一控制栅310和第二控制栅320;字线区40,位于第一浮栅210和第二浮栅220之间的沟道区130上方,字线WL连接字线区40。

[0003] 现有技术对图1所示双分离栅闪存编程时一般采用源极注入方式(Source Side injection),假设右侧存储位a(椭圆圈处存储位)被选中,设置字线电压WL=1.4V,第二位线电压BL1=5V,第二控制栅线电压CG1=8V,第一控制栅线电压CG0=5V,第一位线BL0为偏置电压Vdp,这种方式编程速度很快,但编程时位线电流Idp较高,不适合低功耗的场合。

# 发明内容

[0004] 为克服上述现有技术存在的不足,本发明之目的在于提供一种双分离栅闪存阵列及其编程方法,以适合低功耗的场合。

[0005] 为达上述及其它目的,本发明提出一种双分离栅闪存阵列,包括M\*N的存储单元,每个存储单元的控制栅线CGO/CG1与位线BL0/BL1平行而与字线WL垂直。

[0006] 进一步地,在列方向,第一控制栅线CG0j和第二控制栅线CG1j分别连接至每一列的存储单元的第一控制栅区和第二控制栅区, $j=0,1,2,3,\dots,N-1$ ,位线BL0连接至第一列的存储单元的源极端,位线BLj连接至第j列的存储单元的漏极端和第j+1列的存储单元的源极端, $j=1,2,3,\dots,N-1$ ,位线BLN连接至第N列的存储单元的漏极端。

[0007] 进一步地,于编程时,对选中的存储单元,使其位线电流为0,以适合低功耗的场合。

[0008] 进一步地,于编程时,对选中的存储单元,设置其字线电压WL= $-5V\sim-10V$ ,第一位线BL0和第二位线电压BL1=BL0=0V,第一控制栅线电压CG0= $0\sim-8V$ ,第二控制栅线电压CG1= $5V\sim10V$ 。

[0009] 进一步地,对于选中存储单元所在行的其他未选中存储单元,该类存储单元的字线电压为WL=-5V~-10V,其列方向上的控制栅线电压CG0/1=0,因此该类存储单元上不会发生隧穿效应从而不会发生编程动作。

[0010] 进一步地,对于选中存储单元所在列的其他未选中存储单元或存储位,该类存储单元的第二控制栅线电压为CG1=5V~10V、第一控制栅线电压为CG0=0~-8V,若不在同一列,则字线电压WL=0V,在该类存储单元上不会发生隧穿效应从而不会发生编程动作,若不在同一列即选中存储单元的另一存储位,虽然字线电压WL=-5V~-10V,但对应的第一控制栅线电压CG0=0~-8V,在该存储位上不会发生隧穿效应从而不会发生编程动作。

[0011] 进一步地,对于非选中存储单元所在行和所在列,行方向上,字线电压WL=0V,列方向上,第一和第二控制栅线电压CG0/1=0V,在该类存储单元上都不会发生隧穿效应从而不会发生编程动作。

[0012] 进一步地,于编程时采用多晶硅反转的隧道效应的方式。

[0013] 进一步地,于编程时,对选中的存储单元,使其位线电流为0,以适合低功耗的场合。

[0014] 进一步地,于编程时,对选中的存储单元,设置其字线电压WL=-5V $\sim$ -10V,第一位线BL0和第二位线电压BL1=BL0=0V,第一控制栅线电压CG0=0 $\sim$ -8V,第二控制栅线电压CG1=5V $\sim$ 10V。

[0015] 与现有技术相比,本发明一种双分离栅闪存阵列及其编程方法,其可以适用于低功耗场合。

#### 附图说明

[0016] 图1为一种双分离栅闪存的单元结构示意图;

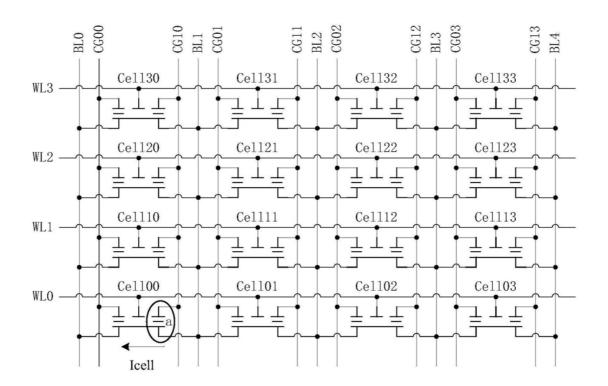

[0017] 图2为本发明一种双分离栅闪存阵列之阵列架构示意图。

# 具体实施方式

[0018] 以下通过特定的具体实例并结合附图说明本发明的实施方式,本领域技术人员可由本说明书所揭示的内容轻易地了解本发明的其它优点与功效。本发明亦可通过其它不同的具体实例加以施行或应用,本说明书中的各项细节亦可基于不同观点与应用,在不背离本发明的精神下进行各种修饰与变更。

[0019] 本发明一种双分离栅闪存阵列的编程方法对图1所示双分离栅闪存编程时采用多晶硅反转(Reverse poly to poly)的隧道效应(Fowler-Nordheim tunneling)的方式,假设右侧存储位a(椭圆圈处存储位)被选中,设置字线电压WL= $-5V\sim-10V$ (较佳地,WL=-8V),第一位线BLO和第二位线电压BLO=BL1=0V,第一控制栅线电压CG0= $0\sim-8V$ (较佳地CG0=-4V),第二控制栅线电压CG1= $5\sim10V$ (较佳地,CG1=8V)。

[0020] 这种方式编程时位线电流为0,适合低功耗的场合。

[0021] 图2为本发明一种双分离栅闪存阵列之阵列架构示意图。如图2所示,本发明一种双分离栅闪存阵列,包括M\*N的存储阵列,在行方向,字线WLi连接至每一行的存储单元的字线区( $i=0,1,2,\dots,M-1$ ),在列方向,第一控制栅线CG0j和第二控制栅线CG1j分别连接至每一列的存储单元的第一控制栅区和第二控制栅区( $j=0,1,2,3,\dots,N-1$ ),位线BL0连接至第一列的存储单元的源极端,位线BLj连接至第j列的存储单元的漏极端和第j+1列的存储单元的源极端( $j=1,2,3,\dots,N-1$ ),位线BLN连接至第N列的存储单元的漏极端,即本发明阵列的控制栅线CG0/CG1与位线BL0/1平行而与字线WL垂直,以实现对单bit的编程操作。

[0022] 对其他未选中的存储单元或存储位(bit),假设选中存储位a,分三类:

[0023] 第一类,选中存储单元所在行的其他未选中存储单元,这类存储单元的字线电压为WL=-8V,但列方向上,其控制栅线电压CG0/1=0,在这类存储单元上不会发生隧穿效应从而不会发生编程动作;

[0024] 第二类,选中存储单元所在列的其他未选中存储单元或存储位,这类存储单元的第二控制栅线电压为,CG1=8V、第一控制栅线电压为CG0=-4V,若不在同一列,则字线电压WL=0V,在这类存储单元上不会发生隧穿效应从而不会发生编程动作,若不在同一列即选中存储单元的另一存储位,虽然字线电压WL=-8V,但对应的第一控制栅线电压CG0=-4V,在该存储位上不会发生隧穿效应从而不会发生编程动作;

[0025] 第三类,非选中存储单元所在行和所在列,行方向上,字线电压WL=0V,列方向上,第一和第二控制栅线电压CG0/1=0V,在这类存储单元上都不会发生隧穿效应从而不会发生编程动作。

[0026] 上述实施例仅例示性说明本发明的原理及其功效,而非用于限制本发明。任何本领域技术人员均可在不违背本发明的精神及范畴下,对上述实施例进行修饰与改变。因此,本发明的权利保护范围,应如权利要求书所列。

图1

图2