# (19) 대한민국특허청(KR) (12) 공개특허공보(A)

(11) 공개번호 10-2012-0086618 (43) 공개일자 2012년08월03일

(51) 국제특허분류(Int. Cl.)

H01L 29/778 (2006.01) H01L 21/335 (2006.01)

(21) 출원번호 **10-2011-0007973**

(22) 출원일자 **2011년01월26일**

심사청구일자 **2011년01월26일**

(71) 출원인

고려대학교 산학협력단

서울 성북구 안암동5가 1

(72) 발명자

이종권

경기도 안양시 만안구 안양천서로 289, 뜨란채 아파트 110-1501 (안양동)

(74) 대리인

특허법인주원

전체 청구항 수 : 총 12 항

## (54) 발명의 명칭 탄소 나노 물질을 이용한 반도체 소자, 및 그 제조 방법

#### (57) 요 약

탄소 나노 물질을 이용한 반도체 소자, 및 그 제조 방법이 개시된다. 탄소 나노 물질을 이용한 반도체 소자는 기판 상에 형성된 미리 설정된 형태를 가지는 패턴층, 패턴층상에 형성된 절연막층, 및 절연막층상에 형성된 미리 설정된 탄소 나노 물질층을 포함한다. 게이트 시그널(Gate signal)을 가하는 게이트 패턴(gate pattern)만을 미리 설정된 형태로 제작함으로써, 탄소 나노 물질이 반도체 성질을 띠게 할 수 있으므로 탄소 나노 물질을 이용하여 우수한 특성의 반도체 소자의 제조가 가능하게 된다.

#### 대 표 도 - 도4

# 이 발명을 지원한 국가연구개발사업

과제고유번호 R32-10082 부처명 한국과학재단

연구사업명 세계적 수준의 연구중심대학 육성사업

연구과제명 플렉서블 나노시스템 기반기술

주관기관고려대학교산학협력단연구기간2010.10.01 ~ 2011.08.31

## 특허청구의 범위

#### 청구항 1

기판 상에 형성된 미리 설정된 형태를 가지는 패턴층;

상기 패턴층상에 형성된 절연막층; 및

상기 절연막충상에 형성된 미리 설정된 탄소 나노 물질충을 포함하는 것을 특징으로 하는 탄소 나노 물질을 이용한 반도체 소자.

### 청구항 2

제 1항에 있어서.

상기 패턴층과 기판 사이에 형성된 절연막층을 더 포함하는 것을 특징으로 하는 탄소 나노 물질을 이용한 반도 체 소자.

### 청구항 3

제 1항에 있어서.

상기 탄소 나노 물질층은 상기 패턴층의 형태에 대해 미리 설정된 방향으로 형성되는 것을 특징으로 하는 탄소 나노 물질을 이용한 반도체 소자.

### 청구항 4

제 1항에 있어서.

상기 탄소 나노 물질은 그래핀인 것을 특징으로 하는 탄소 나노 물질을 이용한 반도체 소자.

#### 청구항 5

제 1항에 있어서.

상기 탄소 나노 물질은 탄소 나노 튜브인 것을 특징으로 하는 탄소 나노 물질을 이용한 반도체 소자.

#### 청구항 6

제 1항에 있어서,

상기 탄소 나노 물질층상의 미리 설정된 영역에 형성된 전극층을 더 포함하는 것을 특징으로 하는 탄소 나노 물질을 이용한 반도체 소자.

# 청구항 7

기판 상에 미리 설정된 형태를 가지는 패턴층을 형성하는 단계;

상기 패턴층상에 절연막층을 형성하는 단계; 및

상기 절연막층상에 미리 설정된 탄소 나노 물질층을 형성하는 단계를 포함하는 것을 특징으로 하는 탄소 나노 물질을 이용한 반도체 소자 제조 방법.

#### 청구항 8

제 7항에 있어서,

상기 패턴층과 기판 사이에 절연막층을 형성하는 단계를 더 포함하는 것을 특징으로 하는 탄소 나노 물질을 이용한 반도체 소자 제조 방법.

### 청구항 9

제 7항에 있어서.

상기 탄소 나노 물질층은 상기 패턴층의 형태에 대해 미리 설정된 방향으로 형성되는 것을 특징으로 하는 탄소 나노 물질을 이용한 반도체 소자 제조 방법.

#### 청구항 10

제 7항에 있어서,

상기 탄소 나노 물질은 그래핀인 것을 특징으로 하는 탄소 나노 물질을 이용한 반도체 소자 제조 방법.

#### 청구항 11

제 7항에 있어서.

상기 탄소 나노 물질은 탄소 나노 튜브인 것을 특징으로 하는 탄소 나노 물질을 이용한 반도체 소자 제조 방법.

#### 청구항 12

제 7항에 있어서.

상기 탄소 나노 물질층상의 미리 설정된 영역에 전극층을 형성하는 단계를 더 포함하는 것을 특징으로 하는 탄소 나노 물질을 이용한 반도체 소자 제조 방법.

# 명 세 서

# 기 술 분 야

[0001] 본 발명은 반도체 소자에 관한 것으로서, 더욱 상세하게는 그래핀이나 탄소 나노 튜브와 같은 탄소 나노 물질 기반의 나노 소자(Nano Device)에 관한 것이다.

### 배경기술

- [0002] 지난 1985년에 발견된 플러린(C60)과 1991년에 발견된 탄소나노튜브와 더불어 2004년~2005년에 이루어진 그래핀 (graphene)의 성공적인 분리로 이제 탄소로만 이루어진 물질을 이용하여 0차원, 1차원 및 2차원 공간에서 전자 및 여러 입자들의 물리적 성질을 연구할 수 있게 되었다.

- [0003] 탄소 나노 튜브는 흑연판(graphite sheet)이 나노 크기의 직경으로 둥글게 말린 형태이며, 그 직경이 나노미터 수준으로 극히 작은 영역의 물질을 말한다. 탄소 나노 튜브는 구조에 따라 한 겹으로 된 단일벽 탄소나노튜브 (SWCNT), 여러겹의 탄소나노튜브가 동심원상을 이루는 다중벽 탄소나노튜브(MWCNT)로 크게 분류한다.

- [0004] 단일벽 탄소 나노 튜브(SWCNT)의 전기적 특성은 흑연판(graphite sheet)이 말린 각도에 따라 암체어(armchair), 지그재그(zigzag), 키랄(chiral) 타입으로 나눌 수 있는데 암체어(armchair) 나노튜브는 금속성을, 지그재그 (zigzag) 나노튜브는 갭이 작은 반도체 이거나 준금속 성질을, 키랄(chiral) 나노튜브는 반도체 특성을 띠게 된다. 도 1은 탄소나노튜브의 여러 형태를 도시한 도면이다.

- [0005] 다이아몬드와 흑연, 플러렌 등이 동소체에 속하며, SWCNT는 단순히 흑연판 한층을 말아 놓은 구조로 직경이 0.5~3nm이며 이중벽 탄소나노튜브는 단일벽 탄소 나노튜브 두 층이 동심축을 이룬 형태로 직경이 1.4~3nm 에 이른다. 다중벽 탄소나노튜브는 벽수가 3~15겹으로 층을 이루며 직경은 5~100nm에 이른다.

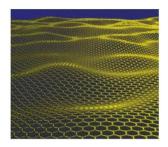

- [0006] 그래핀은 탄소 화합물로써 판상 구조를 가지는 그래파이트(graphite)의 한겹이며 2차원 물질이다. 주로 공유결합을 통해서 이루어진 탄소 동소체들은 4개의 최외각 전자들의 파동함수의 선형결합의 방식에 따라서 결정구조를 포함한 많은 물리적 성질이 결정된다. 도 2는 그래핀의 2차원적 구조를 도시한 도면이다.

- [0007] 그래핀은 탄소 원자 한 층으로 돼 있어 세상에서 가장 얇은 물질이면서도 구조적 화학적으로 안정적이며, 뛰어 난 전기적 성질을 가지고 있다. 현재 반도체에서 사용되는 단결정 실리콘보다 전자를 100배 이상 빠르게 이동시 키고 구리보다도 100배 많은 전류를 흐르게 할 수 있어 기존 기술을 대체할 차세대 트랜지스터 및 전극 소재로 주목받고 있다.

- [0008] 그래핀은 열적, 전기적, 기계적 특성이 좋아 탄소나노튜브만큼 많은 영역에서 그 응용을 기대하고 있다. 특히, 그래핀이 가지고 있는 이차원 구조는 독특한 물리적 성질과 더불어 전기-전자적 응용 측면에서 여타의 탄소 동소체들과는 다른 매우 독특한 장점을 가지고 있다.

- [0009] 이차원 구조로 인하여 인쇄, 식각 등으로 대표되는 탑-다운(top-down) 방식의 일반적인 반도체 공정을 도입해서 전자회로를 구성할 수 있다는 장점이다.

- [0010] 그래핀(Graphene)은 2차원 구조로 π-오비탈의 전자들에 의해 생성되는 에너지 밴드 다이어그램(energy band diagram)을 보면 브릴루인 영역(brillouin zone) 내의 K 위치에서 E=0이 곳에 페르미 준위 (Fermi level)이 있 게 되므로, 기본적으로 금속성(metal-like)의 성격을 가지고 있다.

- [0011] 하지만, 그래핀(Graphene)이 전자 소자로서 활용되기 위해서는 반도체적 성질을 띠어야 하는데 이를 위해서는 그래핀(graphene)의 에너지 밴드 다이어그램(energy band diagram)에서 밴드갭(band gap)을 개방(open)해야 하는 필요가 있다.

- [0012] 따라서 그래핀(graphene)의 에너지 밴드갭(Energy band gap)을 형성하기 위한 여러가지 다양한 방법들 (결함 (defect) 형성등)이 제시되고 있으나, 현재까지는 기존의 실리콘(Si) 기반 트랜지스터(transistor)에 해당하는 스위칭 속도(switching speed)나 온/오프 전류비(On/Off ratio)를 구현하지는 못하고 있는 상황이다.

- [0013] 한편, CNT의 경우도 완벽하게 도체성을 띠거나 반도체성을 띠는 CNT만을 분리하기 힘든 상황이며, 반도체적 성질을 띤 CNT라고 하더라도 어느 정도 도체 성질을 나타내는 성분들이 혼재된 상태로 대부분 존재하게 된다.

- [0014] 따라서 CNT를 전계 효과 트랜지스터(FET)의 반도체층으로 이용할 경우에도 혼재된 도체 성분들 때문에 또는 CNT 로드(rod)들 간에 형성된 네트워크(network) 내의 접촉(contact) 저항 등에 의해서 반도체적 성질을 나타나는데 제약이 생겨 반도체적 성질이 저하되는 부분이 있어 왔다.

#### 발명의 내용

#### 해결하려는 과제

[0015] 본 발명은 상술한 종래의 문제점을 해결하기 위해 안출된 것으로서, 그래핀이나 탄소 나노 튜브를 이용하여 보다 우수한 특성을 가지는 반도체 소자, 및 반도체 소자를 제조하는 방법을 제공하는 것을 목적으로 한다.

## 과제의 해결 수단

- [0016] 상기 목적을 달성하기 위해 본 발명에 따른 탄소 나노 물질을 이용한 반도체 소자는 기판 상에 형성된 미리 설정된 형태를 가지는 패턴층, 패턴층상에 형성된 절연막층, 및 절연막층상에 형성된 미리 설정된 탄소 나노 물질층을 포함한다.

- [0017] 게이트 시그널(Gate signal)을 가하는 게이트 패턴(gate pattern)만을 미리 설정된 형태로 제작함으로써, 탄소 나노 물질이 반도체 성질을 띠게 할 수 있으므로 탄소 나노 물질을 이용하여 우수한 특성의 반도체 소자의 제조가 가능하게 된다.

- [0018] 또한, 반도체 소자는 패턴층과 기판 사이에 형성된 절연막층을 더 포함할 수 있다. 이와 같은 구성으로 보다 다양한 형태의 반도체 소자의 제조가 가능하게 된다.

- [0019] 탄소 나노 물질층에 사용되는 탄소 나노 물질은 그래핀, 또는 탄소 나노 튜브일 수 있다. 이러한 구성에 의해, 그래핀(graphene)의 금속성(metal-like) 성질을 변화시켜 반도체 성질을 띠게 할 수 있고, 탄소 나노 튜브 네트워크(CNT Network) 내의 탄소 나노 튜브 로드(CNT rod)들 간의 접촉 방식에 상관없이 반도체적 성질을 용이하게 갖게 할 수 있다.

- [0020] 탄소 나노 물질층의 그래핀은 패턴층의 형태에 대해 미리 설정된 방향으로 형성될 수 있다. 이 경우 그래핀의 형성 방향에 따라 다른 특성을 가지는 반도체 소자를 제조할 수 있게 된다.

- [0021] 또한, 탄소 나노 물질층상의 미리 설정된 영역에 형성된 전극층을 더 포함할 수 있다. 이러한 구성으로 탄소 나노 물질층에 전력을 공급할 수 있고, 기판을 게이트 전극으로 사용하는 트랜지스터의 구조를 구현할 수 있게 된다.

- [0022] 아울러, 상기 반도체 소자를 제조하는 방법 발명이 개시된다.

#### 발명의 효과

- [0023] 본 발명에 의하면, 기존 그래핀(graphene)의 금속성(metal-like) 성질을 변화시켜 반도체 성질을 띠게 할 수 있고, 탄소 나노 튜브 네트워크(CNT Network) 내의 탄소 나노 튜브 로드(CNT rod)들 간의 접촉 방식에 상관없이 반도체적 성질을 용이하게 갖게 할 수 있다.

- [0024] 또한, 기존에 제안된 방법들 대비 반도체의 밴드 갭 조절이 용이하다.

- [0025] 또한, 게이트 시그널(Gate signal)을 가하는 게이트 패턴(gate pattern)만을 나노 스케일(Nano scale)로 제작함으로써, 후속 소자(device) 제조 공정이 단순해지고 저비용(low cost) 제품 개발이 가능하다.

- [0026] 또한, 본 발명을 통해 제작된 전계효과 트랜지스터는 기존의 그래핀(graphene)이나 탄소 나노 튜브(CNT) 기반의 소자들 대비 우수한 온/오프 전류비(on/off ratio), 및 이동도(mobility) 그리고 스위칭 속도(switching speed)를 보이게 된다.

## 도면의 간단한 설명

[0027] 도 1은 탄소나노튜브의 여러 형태를 도시한 도면.

도 2는 그래핀의 2차원적 구조를 도시한 도면.

도 3은 본 발명에 따른 탄소 나노 물질을 이용한 반도체 소자의 일 실시예의 개략적인 단면도.

도 4는 본 발명에 따른 탄소 나노 물질을 이용한 반도체 소자의 다른 실시예의 개략적인 단면도.

도 5는 기판상에 형성된 패턴에 대한 그래핀층 형성 방향을 도시한 도면.

도 6은 본 발명에 다른 탄소 나노 물질을 이용한 반도체 소자 제조 방법의 일 실시예를 수행하기 위한 개략적인 흐름도.

도 7은 도 6의 방법에 따라 도 3의 소자를 제조하는 공정을 도시한 도면.

도 8은 도 6의 방법에 따라 도 4의 소자를 제조하는 공정을 도시한 도면.

### 발명을 실시하기 위한 구체적인 내용

- [0028] 이하, 첨부된 도면을 참조하여 본 발명의 바람직한 실시예를 설명한다.

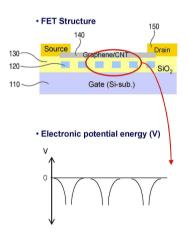

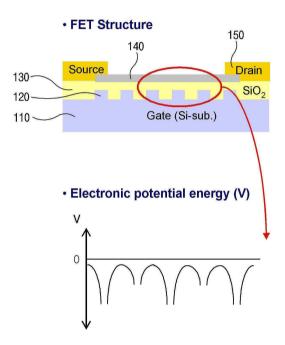

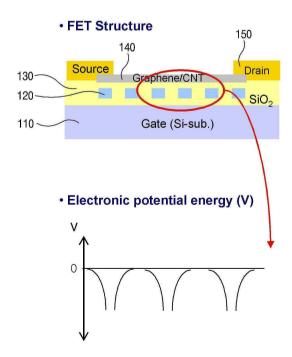

- [0029] 도 3은 본 발명에 따른 탄소 나노 물질을 이용한 반도체 소자의 일 실시예의 개략적인 단면도이다. 도 3에서, 탄소 나노 물질을 이용한 반도체 소자는 기판(110), 패턴충(120), 절연막충(130), 탄소나노물질충(140), 전극충 (150)을 포함한다.

- [0030] 패턴층(120)은 기판(110)상에 형성된 미리 설정된 형태로 형성되고, 절연막층(130)은 패턴층(120)상에 형성되며, 탄소 나노 물질층(140)은 절연막층(130)상에 형성된다.

- [0031] 이때, 반도체 소자는 1차원 또는 2차원 형태의 주기적으로 형성된 게이트 시그널 패턴(gate signal pattern)을 이용하여 그래핀(graphene)의 전자 포텐셜(electronic potential)을 변화시키는 모든 구조를 포함하며, 탄소 나노 튜브 네트워크(CNT network)나 단일 탄소 나노 튜브 로드(CNT rod), 그리고 나노 와이어(Nano wire) 등을 이용하여 전계 효과 트랜지스터(FET)의 활성 채널(active channel)로 이용하는 모든 구조에서 게이트 시그널 (gate signal)을 주기적으로 가하는 형태를 포함한다.

- [0032] 이와 같이, 게이트 시그널(Gate signal)을 가하는 게이트 패턴(gate pattern)만을 미리 설정된 형태로 제작함으로써, 탄소 나노 물질이 반도체 성질을 띠게 할 수 있으므로 탄소 나노 물질을 이용하여 우수한 특성의 반도체소자의 제조가 가능하게 된다.

- [0033] 절연막층(130)은 패턴층(120)과 기판(110) 사이에도 형성될 수 있다. 이와 같은 구성으로 보다 다양한 형태의 반도체 소자의 제조가 가능하게 된다.

- [0034] 도 4는 본 발명에 따른 탄소 나노 물질을 이용한 반도체 소자의 다른 실시예의 개략적인 단면도이다. 도 4에서는 도 3에서와는 달리 절연막층(130)이 패턴층(120)과 기판(110) 사이에도 형성되어 있는 것을 확인할 수 있다.

- [0035] 탄소 나노 물질층(140)에 사용되는 탄소 나노 물질은 그래핀, 또는 탄소 나노 튜브일 수 있다. 탄소 나노 물질

이 그래핀인 경우 그래핀(graphene)의 금속성(metal-like) 성질을 변화시켜 반도체 성질을 띠게 할 수 있고, 탄소 나노 튜브인 경우 탄소 나노 튜브 네트워크(CNT Network) 내의 탄소 나노 튜브 로드(CNT rod)들 간의 접촉 방식에 상관없이 반도체적 성질을 용이하게 갖게 할 수 있다.

- [0036] 이와 같이, 전자빔(e-beam) 등과 같은 장비를 이용하여 나노미터 스케일(scale)의 주기적인 패턴(pattern)을 가진 게이트(gate) 배선들을 형성한 후, 그 위에 게이트(Gate) 절연막을 형성하고 그 위에 그래핀 쉬트(graphene sheet)나 탄소 나노 튜브(Carbon Nano tube) 등을 올리게 되면, 그래핀(graphen) 또는 CNT 내에 전자들이 느끼는 전기적 포텐셜 에너지(potential energy)가 주기적으로 바뀌게 할 수 있다.

- [0037] 이를 위해 도 3에서와 같이 전기적 포텐셜의 변화가 -V, -V', -V', -V', 식으로 변화되도록 주기적 패터닝을 하거나, 도 4에서와 같이 전기적 포텐셜을 -V, 0 V, 0 와 같이 변화되도록 제작 할 수 있다.

- [0038] 따라서, 이들 각각의 경우 서로 다른 에너지 밴드갭을 갖는 반도체 성질을 띠게 할 수 있을 뿐만 아니라, 공간 주기적 게이트 배선의 물리적 구조를 단순히 바꾸어 줌으로써 상대적으로 쉽게 밴드갭 엔지니어링(band gap engineering)을 할 수 있다.

- [0039] 그러므로, 기본적으로 밴드갭(band gap) 에너지가 ~0인 그래핀(graphene)의 특성을 변형시켜 반도체적 성질을 띠게 할 수 있으며, CNT를 이용한 전계 효과 트랜지스터 제작시 CNT 네트워크(network)내의 CNT 로드(rod)들 간의 접촉(contact)에 따른 반도체적 성질을 개선할 수 있으므로 이를 이용한 CNT 전계 효과 트랜지스터의 성능향상도 기대 할 수 있다.

- [0040] 또한, 탄소 나노 물질이 그래핀인 경우 탄소 나노 물질층(140)의 그래핀은 미리 설정된 방향으로 형성된다. 이와 같은 구성으로, 그래핀층의 형성 방향에 따라 다른 특성을 가지는 반도체 소자를 제조할 수 있게 된다.

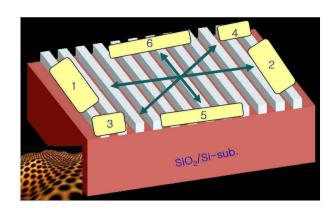

- [0041] 도 5는 기판상에 형성된 패턴에 대한 그래핀층 형성 방향을 도시한 도면이다.

- [0042] 도 5에서처럼 게이트 시그널(gate signal)의 공간 주기적 패턴과 그래핀(graphene) 또는 CNT의 놓인 위치에 따른 변형된 전기 포텐셜에 의해서 서로 다른 밴드갭(band gap)을 갖는 트랜지스터(Transistor)의 제작이 가능하다.

- [0043] 이와 같이, 1차원, 2차원 주기적 어레이(array)에 그래핀(graphene) 또는 CNT의 방향을 0~180도 바꾸어 가면서 올리는 구조를 채택함으로써, 방향에 따른 서로 다른 에너지 밴드갭(energy band gap) 특성을 유도하여 소자 (device) 응용별로 적합한 방향을 선택할 수 있게 된다.

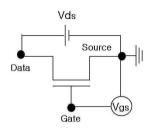

- [0044] 전극층(150)은 탄소 나노 물질층(140)상의 미리 설정된 영역에 형성된다. 이러한 구성으로 탄소 나노 물질층 (140)에 전력을 공급할 수 있고, 기판(110)을 게이트 전극으로 사용하는 트랜지스터의 구조를 구현할 수 있게된다.

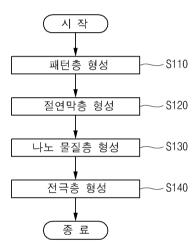

- [0045] 도 6은 본 발명에 다른 탄소 나노 물질을 이용한 반도체 소자 제조 방법의 일 실시예를 수행하기 위한 개략적인 흐름도이고, 도 7은 도 6의 방법에 따라 도 3의 소자를 제조하는 공정을 도시한 도면이다.

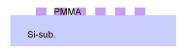

- [0046] 먼저, 실리콘(Silicon) 기판위에 PMMA나 HSQ와 같은 전자빔(e-beam) 용 레지스트(resist)(ER)을 코팅 한 후 전 자빔(e-beam)으로 주기적인 라인 패턴(line pattern)을 형성한다.(S110)

- [0047] 다음으로, 형성된 PMMA 또는 HSQ 패턴(pattern) 사이에 들어나 있는 시실리콘(silicon) 기판의 표면을 드라이 에칭(dry etching)한 후 남아있는 PMMA 또는 HSQ 층(layer)을 스트립(strip) 공정을 하여 벗겨내고, 식각 (etching)된 실리콘(silicon) 기판 위에 SiO2층(layer)을 열산화법 (thermal oxidation)으로 형성한다.(S120)

- [0048] 이어서, 기판의 주기적 패턴(pattern)이 형성되어 있는 영역의 게이트(gate) 절연층 위에 그래핀(graphene) 또는 탄소 나노 튜브(CNT)를 형성한다(S130).

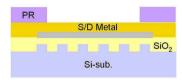

- [0049] 마지막으로, 그 위에 S/D 금속(metal)을 증착(depositon)하고, 포토 레지스트(Photo resist; PR)을 코팅 (coating)한 후 현상(develop) 공정을 통해 PR 패터닝(patterning)을 하며, 금속층(Metal layer)을 식각 (etching)하여 소스/드레인(Source /Drain) 영역을 형성함으로써, 3단자 트랜지스터(transistor) 제작을 완료하게 된다.

- [0050] 이 경우에 주기적 게이트 패턴(gate pattern)에 의해 인가된 전기적 포텐셜이 -V, -V', -V, -V', 순으로 변화하 게 되어 그래핀(graphene)의 밴드갭(band gap)을 개방(open)하거나 탄소 나노 튜브(CNT)의 반도체적 성질을 개선하게 된다.

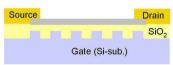

- [0051] 도 8는 도 6의 방법에 따라 도 4의 소자를 제조하는 공정을 도시한 도면이다.

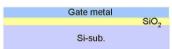

- [0052] 먼저, 실리콘(Silicon) 기판 위에 게이트(gate) 절연막으로 사용되는 SiO<sub>2</sub> 층(layer)을 열산화법 (thermal oxidation)으로 형성한 후, 게이트 메탈층(gate metal layer)을 증착(deposition) 하고, PMMA나 HSQ와 같은 전 자빔(e-beam)용 레지스트(resist)(ER)을 코팅한 후, 전자빔(e-beam)으로 주기적인 라인 패턴(line pattern)을 형성하며, 형성된 PMMA 또는 HSQ 패턴(pattern) 사이에 들어나 있는 게이트 금속(gate metal) 표면을 웨트 에칭 (wet etch) 또는 드라이 에칭(dry etching) 한 후 남아있는 PMMA 또는 HSQ 층(layer)을 스트립(strip) 공정을 하여 벗겨낸다(S110).

- [0053] 다음으로, 그 위에 SiO<sub>2</sub>층(layer)을 열산화법 (thermal oxidation)으로 형성하여, 주기적 게이트(gate) 전극 및 게이트(gate) 절연막 형성을 완료한다(S120).

- [0054] 이어서, 기판의 주기적 패턴(pattern)이 형성되어 있는 영역의 게이트(gate) 절연층위에 그래핀(graphene) 또는 탄소 나노 튜브(CNT)를 형성한다(S130).

- [0055] 마지막으로, 그 위에 S/D 금속(metal)을 증착(deposition)하고, 포토 레지스트(Photo resist; PR)를 코팅 (coating)한 후 현상(develop) 공정을 통해 PR 패터닝(patterning)을 하며, 금속층(Metal layer)을 식각 (etching)하여 소스/드레인(Source /Drain) 영역을 형성함으로써, 3단자 트랜지스터(transistor) 제작을 완료하게 된다(S140).

- [0056] 이 경우에 주기적 게이트 패턴(gate pattern)에 의해 인가된 전기적 포텐셜이 -V, 0, -V, 0, 순으로 변화하게 되어 그래핀(graphene)의 밴드갭(band gap)을 개방(open)하거나 탄소 나노 튜브(CNT)의 반도체적 성질을 개선하게 된다.

- [0057] 본 발명이 비록 일부 바람직한 실시예에 의해 설명되었지만, 본 발명의 범위는 이에 의해 제한되어서는 아니 되고, 특허청구범위에 의해 뒷받침되는 상기 실시예의 변형이나 개량에도 미쳐야 할 것이다.

### 부호의 설명

[0058] 110: 기판

120: 패턴층

130: 절연막층

140: 탄소 나노 물질층

150: 전극층

# 도면

## 도면1

# 도면2

# 도면3

# 도면4

# 도면5

# 도면6

### 도면7

## 1. ER patterning (e-beam)

#### 5. S/D metal deposition

### 2. Si Patterning (Dry etch)

### 6. PR Patterning

#### 3 Gate Insulator deposition

4. Graphene/CNT coating

Graphene/CNT

Si-sub.

SiO<sub>2</sub>

#### 7. S/D metal patterning

# 도면8

## 1. Gate metal deposition

# 5. Graphene/CNT coating

### 2. ER Patterning (e-beam)

# 6. S/D metal deposition

# 3 Gate Metal patterning (Etching)

## 7. PR Patterning

# 4. Gate Insulator deposition

#### 8. S/D metal patterning