(19) **日本国特許庁(JP)**

# (12) 特 許 公 報(B2)

(11) 特許番号

特許第5191555号 (P5191555)

(45) 発行日 平成25年5月8日(2013.5.8)

(24) 登録日 平成25年2月8日(2013.2.8)

(51) Int. Cl. F. I.

**GO 6 F 12/00 (2006.01)** GO 6 F 12/00 5 6 4 D G1 1 C 11/401 (2006.01) G1 1 C 11/34 3 6 2 Z

請求項の数 41 外国語出願 (全 19 頁)

(21) 出願番号 特願2011-50556 (P2011-50556) (22) 出願日 平成23年3月8日 (2011.3.8)

(62) 分割の表示 特願2006-533897 (P2006-533897)

の分割

原出願日 平成16年9月3日 (2004.9.3) (65) 公開番号 特開2011-146063 (P2011-146063A)

(43) 公開日 平成23年7月28日 (2011. 7. 28) 審査請求日 平成23年3月23日 (2011. 3. 23)

(31) 優先権主張番号 10/676,648

(32) 優先日 平成15年9月30日 (2003.9.30)

(33) 優先権主張国 米国(US)

||(73)特許権者 501055961

ラムバス・インコーポレーテッド アメリカ合衆国、 カリフォルニア州 9 4089、サニーヴェール、スイート 7 00、エンタープライズ ウェイ 105

О

(74)代理人 100079108

弁理士 稲葉 良幸

|(74)代理人 100109346

弁理士 大貫 敏史

|(72)発明者 ハンペル,クレイグ,イー.

アメリカ合衆国, カリフォルニア州 95 123, サン ノゼ, ダン アベニュー

5927

最終頁に続く

## (54) 【発明の名称】バイモーダル・データストローブを備えた集積回路

## (57)【特許請求の範囲】

## 【請求項1】

第一のクロック信号に同期して制御およびアドレス信号を送信する第一のインタフェースを含むメモリコントローラであって、

第一の動作モードにおいて、前記メモリコントローラは、書き込み動作中にデータストローブを送信し、読み出し動作中に前記メモリコントローラからの前記データストローブの送信を無効にするように構成され、

第二の動作モードにおいて、前記メモリコントローラは、書き込みおよび読み出し動作の両方の間に第二のクロック信号を送信するように構成され、前記第二のクロック信号は前記第一のクロック信号とは異なる、メモリコントローラ。

【請求項2】

前記第一の動作モードにおいて、前記データストローブは、前記書き込み動作中に第一の書き込みデータをサンプリングするように外部メモリ素子による使用のために前記第一の書き込みデータに同期して送信され、

前記第二の動作モードにおいて、前記第二のクロック信号は、前記書き込み動作中に第二の書き込みデータをサンプリングし、前記読み出し動作中に読み出しデータを送信するように外部メモリ素子による使用のために前記第二の書き込みデータに同期して送信される、請求項1に記載のメモリコントローラ。

## 【請求項3】

前記第一の動作モードにおいて、前記メモリコントローラは、前記書き込み動作の間だ

け前記データストローブを送信するように構成される、請求項 1 に記載のメモリコントローラ。

### 【請求項4】

前記第二の動作モードにおいて、前記メモリコントローラは、前記第二のクロック信号 を連続的に送信するように構成される、請求項1に記載のメモリコントローラ。

## 【請求項5】

前記メモリコントローラが動作する前記第一および第二のモードの 1 つを示す情報を記憶するレジスタを更に含む、請求項 1 に記載のメモリコントローラ。

### 【請求項6】

信号出力を有する第二のインタフェースを更に含み、前記第二のインタフェースは、第一の動作モードでの前記書き込み動作中に前記信号出力を介して前記データストローブを送信し、前記第二の動作モードにおける読み出しおよび書き込み動作の両方の間に前記信号出力を介して前記第二のクロック信号を送信するように構成される、請求項1に記載のメモリコントローラ。

### 【請求項7】

前記第二のインタフェースは、

前記第一の動作モードにおける前記書き込み動作中に前記データストローブを、かつ、前記第二の動作モードにおける前記読み出しおよび書き込み動作の両方の間に前記第二のクロック信号を送信する、出力バッファを含む、請求項6に記載のメモリコントローラ。

### 【請求項8】

前記出力バッファは、前記第一の動作モードにおける前記読み出し動作中に前記信号出力を3状態化させるように構成される、請求項7に記載のメモリコントローラ。

### 【請求項9】

前記出力バッファに接続された論理ゲートであって、前記第一の動作モードにおける前記書き込み動作中に前記データストローブを送信するように前記出力バッファを有効にし、前記第一の動作モードにおける前記読み出し動作中に前記出力バッファを無効にし、かつ、前記第二の動作モードにおける前記読み出しおよび書き込み動作の両方の間に前記第二のクロック信号を送信するように前記出力バッファを有効にする、論理ゲートを更に含む、請求項7に記載のメモリコントローラ。

## 【請求項10】

前記論理ゲートに接続されたレジスタであって、前記メモリコントローラが前記第一の動作モードで動作しているかまたは前記第二の動作モードで動作しているのかを示す指示を前記論理ゲートに提供する、レジスタを更に含む、請求項9に記載のメモリコントローラ。

## 【請求項11】

第三のクロック信号の位相を調整し、かつ、前記位相調整済み第三のクロック信号を前記第二のインタフェースに提供する、クロック較正器を更に含み、

前記第二のインタフェースは、前記位相調整済み第三のクロック信号に基づいて前記データストローブおよび前記第二のクロック信号を送信するように構成される、請求項 6 に記載のメモリコントローラ。

## 【請求項12】

前記クロック較正器に接続され、前記第一および第二の動作モードにおける前記書き込み動作中にデータを送信する出力レジスタを更に含む、請求項11に記載のメモリコントローラ。

### 【請求項13】

前記クロック較正器は、書き込み動作中のデータの送信を計時するように前記出力レジスタに前記位相調整済み第三のクロック信号を提供するように構成される、請求項12に記載のメモリコントローラ。

## 【請求項14】

前記第一の動作モードにおける前記書き込み動作中に送信される前記データストローブ

20

10

30

40

は第一のデータストローブであり、前記メモリコントローラは、

前記第一の動作モードにおける前記読み出し動作中に第二のデータストローブを受信する入力バッファと、

前記第一の動作モードにおける前記読み出し動作中にデータを受信する入力レジスタと

を更に含み、

前記入力レジスタは、前記第一の動作モードにおける前記読み出し動作中に前記データをサンプリングするように前記第二のデータストローブを使用するように構成される、請求項7に記載のメモリコントローラ。

## 【請求項15】

前記入力バッファは、前記第一の動作モードにおける前記読み出し動作中に前記データをサンプリングするように前記入力レジスタに前記第二のデータストローブを提供するように構成される、請求項14に記載のメモリコントローラ。

## 【請求項16】

前記入力レジスタは、前記第二の動作モードにおける前記読み出し動作チ中にデータを 受信するように構成され、

前記メモリコントローラは、第三のクロック信号の位相を調整し、かつ、前記第二の動作モードにおける前記読み出し動作中にデータをサンプリングするように前記位相調整済み第三のクロック信号を前記入力レジスタに提供する、クロック較正器を更に含む、請求項14に記載のメモリコントローラ。

#### 【請求項17】

前記出力バッファおよび前記入力バッファは、前記第一の動作モード中に外部導線に接続され、

前記出力バッファは、前記第一の動作モードにおける前記書き込み動作中に前記外部導線を介して前記第一のデータストローブを送信するように構成され、

前記入力バッファは、前記第一の動作モードにおける前記読み出し動作中に前記外部導線から前記第二のデータストローブを受信するように構成される、請求項14に記載のメモリコントローラ。

## 【請求項18】

メモリコントローラを動作させる方法であって、

外部メモリ素子に接続されたメモリコントローラにおいて、

前記メモリコントローラの動作モードを第一の動作モードまたは第二の動作モードに 設定すること、

第一のクロック信号に同期して制御およびアドレス信号を送信すること、および、

前記第一の動作モードにおいて、書き込み動作中に前記外部メモリ素子にタイミング信号をデータストローブとして送信し、読み出し動作中に前記メモリコントローラからの前記タイミング信号の送信を無効にすること、または、

前記第二の動作モードにおいて、書き込みおよび読み出し動作の両方の間に前記外部 メモリ素子に、前記第一のクロック信号とは異なる第二のクロック信号を送信すること、 を含む、方法。

## 【請求項19】

前記タイミング信号を送信することは、前記タイミング信号をインタフェースを介して 送信することを含み、前記第二のクロック信号を送信することは、前記第二のクロック信 号を前記インタフェースポートを介して送信することを含む、請求項18に記載の方法。

#### 【請求項20】

前記第一の動作モードにおいて、前記タイミング信号は、前記書き込み動作中に第一の書き込みデータをサンプリングするように前記外部メモリ素子による使用のために前記第一の書き込みデータに同期して送信され、

前記第二の動作モードにおいて、前記第二のクロック信号は、前記書き込み動作中に第 二の書き込みデータをサンプリングし、前記読み出し動作中に読み出しデータを送信する 10

20

30

40

ように前記外部メモリ素子による使用のために前記外部メモリ素子に送信され、

前記第二のクロック信号は、前記書き込み動作中に前記第二の書き込みデータに同期して送信される、請求項18に記載の方法。

## 【請求項21】

前記第一の動作モードにおいて、前記タイミング信号は、前記書き込み動作の間だけ前記第一のメモリ素子に送信されること、および、

前記第二の動作モードにおいて、前記第二のクロック信号は、連続的に送信されること

を含む、請求項18に記載の方法。

## 【請求項22】

レジスタにおいて、前記メモリコントローラの前記動作モードを示す情報を記憶することを更に含む、請求項18に記載の方法。

#### 【請求項23】

前記コントローラは、出力を有するインタフェースを含み、

前記第一の動作モードにおいて、前記タイミング信号は、前記書き込み動作中に前記出力を介して前記インタフェースによって送信され、

前記第二の動作モードにおいて、前記第二のクロック信号は、前記読み出しおよび書き 込み動作の両方の間に前記出力を介して前記インタフェースによって送信される、請求項 18に記載の方法。

## 【請求項24】

前記インタフェースは出力バッファを含み、

前記タイミング信号を送信することは、前記出力バッファを用いて前記タイミング信号を出力することを含み、

前記第二のクロック信号を送信することは、前記出力バッファを用いて前記第二のクロック信号を出力することを含む、請求項23に記載の方法。

### 【請求項25】

前記第一の動作モードが選択される場合、前記読み出し動作中に前記出力バッファの出力を3状態化することを更に含む、請求項24に記載の方法。

## 【請求項26】

第三のクロック信号の位相を調整することを更に含み、

前記第一の動作モードにおいて、前記タイミング信号の送信は、前記位相調整済み第三のクロック信号に基づき、

前記第二の動作モードにおいて、前記第二のクロック信号の送信は、前記位相調整済み第三のクロック信号に基づく、請求項23に記載の方法。

## 【請求項27】

前記インタフェースは出力バッファを含み、

前記方法は、

前記第一の動作モードにある場合に前記タイミング信号として、また、前記第二の動作 モードにある場合に前記第二のクロック信号として、前記位相調整済み第三のクロック信 号を前記出力バッファに提供することを更に含む、請求項 2 6 に記載の方法。

## 【請求項28】

前記位相調整済み第三のクロック信号を用いて前記書き込み動作中に出力レジスタから データを送信することを更に含む、請求項26に記載の方法。

## 【請求項29】

前記出力レジスタからの前記データの伝送を計時するために前記出力レジスタに前記位相調整済み第三のクロック信号を提供することを更に含む、請求項28に記載の方法。

#### 【請求項30】

前記第一の動作モードにおける前記書き込み動作中に前記出力バッファから送信される 前記タイミング信号は第一のデータストローブであり、

前記方法は、

10

20

30

前記第一の動作モードにおいて、

前記読み出し動作中に、入力バッファにおいて第二のデータストローブを受信すること、および、

前記読み出し動作中に、入力レジスタにおいて、前記第二のデータストローブを用いてデータをサンプリングすること、

を更に含む、請求項23に記載の方法。

#### 【請求項31】

前記第二の動作モードにおいて、

第三のクロック信号の位相を調整すること、および、

前記読み出し動作中に、入力レジスタにおいて、前記位相調整済み第三のクロック信号を用いてデータをサンプリングすること、

を更に含む、請求項18に記載の方法。

## 【請求項32】

アドレス情報と、書き込みコマンドまたは読み出しコマンドの1つである転送コマンドとをメモリ素子に送信するインタフェースであって、前記アドレス情報および前記転送コマンドは第一のクロック信号に同期して送信される、インタフェースと、

前記転送コマンドが書き込みコマンドである場合、データバス上の書込みデータを前記 メモリ素子に送信する第一の回路と、

前記転送コマンドが読み出しコマンドである場合、前記データバス上の読み出しデータ を前記メモリ素子から受信する第二の回路と、

第一のモードにあり、かつ、前記転送コマンドが書き込みコマンドである場合、データストローブ線上の第一のデータストローブを前記メモリ素子に送信し、第二のモードにある場合、連続的に継続する第二のクロック信号を前記メモリ素子に送信するように構成された第三の回路であって、前記メモリ素子は前記第一のデータストローブを用いて前記書き込みデータをサンプリングし、前記転送コマンドが書き込みコマンドである場合、前記メモリ素子は前記第二のクロックを用いて前記書き込みデータをサンプリングし、前記転送信号が読み出しコマンドである場合、前記メモリ素子は前記第二のクロックを用いて前記読み出しデータを送信する、第三の回路と、

前記第一のモードにあり、かつ、前記転送コマンドが読み出しコマンドである場合、前記メモリ素子から前記データストローブ線上の第二のデータストローブを受信するように構成された第四の回路であって、前記第二のデータストローブを用いて前記読み出しデータをサンプリングする、第四の回路と、

を含む、メモリコントローラ。

## 【請求項33】

前記第三の回路は、前記第二のモードにある場合、前記データストローブ線上の前記第 二のクロック信号を送信するように構成される、請求項32に記載のメモリコントローラ

### 【請求項34】

アドレス情報と、書き込みコマンドまたは読み出しコマンドの1つである転送コマンドとをメモリ素子に送信するインタフェースであって、前記アドレス情報および前記転送コマンドは第一のクロック信号に同期して送信される、インタフェースと、

前記転送コマンドが書き込みコマンドである場合、データバス上の書込みデータを送信する第一の回路と、

前記転送コマンドが読み出しコマンドである場合、前記データバス上の読み出しデータを受信する第二の回路と、

第一のモードにあり、かつ、前記転送コマンドが書き込みコマンドである場合、データストローブ線上の第一のデータストローブを、また、第二のモードにある場合、連続的に継続する第二のクロック信号を、送信するように構成された第三の回路と、

前記第一のモードにあり、かつ、前記転送コマンドが読み出しコマンドである場合、前記データストローブ線上の第二のデータストローブを受信するように構成された第四の回

20

10

30

40

路であって、前記第二のデータストローブを用いて前記読み出しデータをサンプリングする、第四の回路と、

を含むメモリコントローラ。

## 【請求項35】

前記第三の回路は、前記第二のモードの場合、前記データストローブ線上の第二のクロック信号を送信するように構成される、請求項34に記載のメモリコントローラ。

#### 【請求項36】

メモリコントローラであって、

タイミング信号を送信し、かつ、第一の動作モードおよび第二の動作モードの1つで動作するように構成可能な第一のインタフェース回路であって、前記第一の動作モードにおいて、前記コントローラが書き込み動作を行っている場合、第一のタイミング信号を書き込みストローブとして送信し、また、前記コントローラが読み出し動作を行っている場合、前記第一のタイミング信号を送信することが無効にされ、また、前記第二の動作モードにおいて、読み出しおよび書き込み動作の両方の間に第二のタイミング信号を自由継続クロックとして送信するように構成される、第一のインタフェース回路と、

書き込み動作中に前記第一のタイミング信号および前記第二のタイミング信号のうちの1つと共にデータ信号を送信する第二のインタフェース回路と、

を含むメモリコントローラ。

### 【請求項37】

前記コントローラが前記第一または前記第二の動作モードで動作するかどうかを示すモード設定を記憶するレジスタを更に含み、前記第一のインタフェースは前記モード設定に基づくように構成される、請求項36に記載のメモリコントローラ。

### 【請求項38】

前記第一および第二のタイミング信号は、クロック信号から導出され、前記コントローラは、前記クロック信号に同期してコマンド / アドレス信号を送信する、請求項36に記載のメモリコントローラ。

## 【請求項39】

前記第一のインタフェース回路は、前記第一のタイミング信号および前記第二のタイミング信号を送信する信号出力を有する、請求項36に記載のメモリコントローラ。

## 【請求項40】

前記第一のインタフェース回路は、前記第一および第二のタイミング信号を送信する出力バッファを含む、請求項36に記載のメモリコントローラ。

# 【請求項41】

前記出力バッファは出力を有し、前記出力バッファは、前記第一のインタフェース回路が前記第一の動作モードにある場合、読み出し動作中に前記出力を 3 状態化させる、請求項 4 0 に記載のメモリコントローラ。

【発明の詳細な説明】

### 【技術分野】

## [0001]

発明の簡単な説明

本発明は、一般に集積回路技術に関する。より具体的には、本発明はバイモーダル・データストローブを備えた集積回路素子に関する。

## 【背景技術】

## [0002]

#### 背景

ソース同期データストローブは、データを送信している素子の送信経路、および当該データを受信している素子の受信経路における遅延を補償する機能を果たす。これらの遅延の程度は、半導体素子の動作条件および製造公差にわたる速度および経路速度の変化の関数である。

## [0003]

10

20

30

- -

通常、素子間のデータストローブ相互接続線は、データストローブを生成する責任が一方の素子からもう一方へ移った場合、 3 状態または休止状態に置かれる。これらの休止期間の結果として、データストローブには、所定の一定周波数が無く、短期間オン / オフされるクロックに類似している。単一の素子によりデータストローブの複数の周期が生成される期間中、データストローブ信号に定常波現象という問題が生じる。第一のエッジ、および恐らくはデータストローブの最初の数個のエッジは通常、データに関して同相に到着する。しかし、データストローブの後続するエッジは、前のデータストローブエッジの反射に起因してシフトする場合があるため、データに関して同相でなくなる。換言すれば、データストローブは、むしろ自由継続クロックの如く振舞う。

【発明の開示】

【発明が解決しようとする課題】

[0004]

メモリバス速度が増すにつれて、メモリシステムにおいてソース同期データストローブを用いる利点が減少している。次第に、より高速で動作するシステムに対応すべくデータストローブを改良する必要があることは明らかである。製造コストおよびスケールメリットの観点から、データストローブに関する問題に対処する新規なシステム設計がソース同期データストローブを用いる製品と互換性を持つならば有益であろう。

【課題を解決するための手段】

[0005]

要約

メモリシステム用のコントローラがデータストローブ・バス、データバスおよびクロック・バスに接続されている。コントローラは、出力バッファが有効にされた際にデータストローブ・バス上の第一のデータストローブ信号をアサートすべく構成された出力バッファを含んでいる。コントローラはまた、コントローラの動作モードを記憶するレジスタを含んでいる。出力バッファが有効にされるのは、コントローラの動作モードが第一のコントローラ動作モードに設定されている場合、データバス経由で第一のデータ信号がコントローラから転送されている期間だけである。しかし、出力バッファは、コントローラの動作モードが第二のコントローラ動作モードに設定されている場合、連続的に有効にされる。更に、コントローラはクロック・バス経由でクロック信号を受信し、クロック信号によりデータバス経由で第二のデータ信号の受信を計時すべく構成されている。

[0006]

別の態様においては、メモリ素子はデータストローブ・バス、データバス、およびクロック・バスに接続されている。メモリ素子は、データストローブ・バス上で連続的かつ遠隔的にアサートされたデータストローブ信号をデータストローブ・バス経由で受信すべく構成されている。メモリ素子はまた、データバス経由でデータストローブ信号と共に第一のデータ信号を受信して、データストローブ信号により第一のデータ信号の受信を計時すべく構成されている。メモリ素子は更に、クロック・バス経由でクロック信号を受信すべく構成されている。第一の動作モードにおいて、メモリ素子はデータバス経由でクロック信号と共に第二のデータ信号を送信し、クロック信号により第二のデータ信号の送信を計時すべく構成されている。第二の動作モードにおいて、メモリ素子はデータストローブ信号により第二のデータ信号の送信を計時すべく構成されている。

[0007]

本発明の態様は、添付の図面と共に、以下の記述および添付の請求項から容易に理解されよう。

【発明を実施するための最良の形態】

[0008]

実施形態の説明

本発明の多くの実施形態について以下に述べる。簡潔のため、現実の実装の全ての特徴を記述する訳ではない。そのような実施形態の開発において、システム関連および事業関連の制約の準拠等、実装毎に異なる開発者固有の目標に到達すべく、多くの実装に固有の

10

20

30

40

20

30

40

50

決定を行なう必要がある点を理解されたい。更に、そのような開発の努力は複雑かつ時間を要するであろうが、それにもかかわらず本開示の利点を享受する当業者にとっては日常的であることを理解されたい。

## [0009]

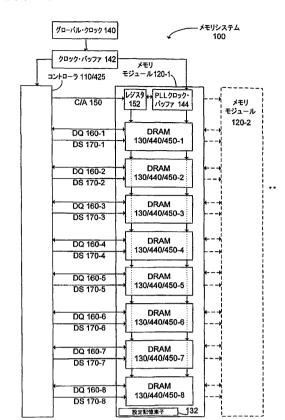

図 1 に、マスター・システム・クロックまたはグローバル・クロック 1 4 0 、クロック ・バッファ 1 4 2 、コントローラ 1 1 0 / 4 2 5 、 1 個以上のメモリモジュール 1 2 0 ( 1 2 0 - 1、 1 2 0 - 2 )、 1 個以上の制御およびアドレス (「 C / A 」) 導線 1 5 0、 8個のデータ(「DQ」) 導線160(160-1~160-8)、8個のデータストロ ーブ(「DS」) 導線170(170-1~170-8) を含むメモリシステム100を 示す。いくつかの実施形態におけるメモリモジュール120-1は、8個のDRAM13 0 / 4 4 0 / 4 5 0 ( 1 3 0 - 1 ~ 1 3 0 - 8 ) および設定記憶素子 1 3 2 を含む D I M M(デュアルインライン・メモリモジュール)である。図1に示すメモリモジュール12 0 - 1 は 1 列の D R A M 群を備えていて、一方、システム 1 0 0 内の 1 個以上のメモリモ ジュールは2列以上のDRAM群(ランクとも呼ぶ)を備えたマルチランク・メモリモジ ュールであってよい。そのようなメモリモジュールにおいて、メモリモジュールを使用す る各々のメモリが動作する間、 1 列またはランクの D R A M がアクセスされる。各メモリ モジュール120はオプションとしてレジスタ152、および位相固定ループ(「PLL 」)クロック・バッファ144を含んでいる。これらオプションの補助回路は、例えば大 規模なファンアウト(すなわち多数のDRAM)対応型システムにおいて有用である。特 に、これらオプションの回路は、DRAM130同士でクロック、制御、およびアドレス 信号を分配しやすくする。

#### [0010]

いくつかの実施形態において、メモリモジュール設定記憶素子132(モード・レジスタまたは設定レジスタと呼ぶこともある)は、PROM(プログラム可能読出専用メモリ)等のシリアル・プレゼンス検出(SPD)素子として実装されている。設定記憶素子132は通常、電源投入時またはシステム・リセット時にコントローラが読んで、メモリモジュール120の能力および/または設定を決定する。いくつかの実施形態において、メモリモジュール改定記憶素子132内のビットは、メモリモジュール内のメモリ素子が他のモード値だけでなく、データストローブの駆動を無効にすべく設定可能か否かを表わすデータストローブ・モード値(本明細書では方向モード値とも呼ぶ)を記憶する。メモリモジュール設定記憶素子132から読み込まれた情報をコントローラ110が用いて、コントローラ110およびDRAM130内のモード・ビットを設定する。いくつかの実施形態において、データ導線、データストローブ、およびDRAMの個数が増減してもよい。別途注記しない限り、コントローラ110に関して本明細書に記述する内容はまた、コントローラ425にも適用できる。

## [0011]

C / A 導線 1 5 0 はメモリシステム 1 0 0 で必要とする個数の並列信号経路を備えた制御およびアドレス・バスとして機能する。同様に、各々の D Q 導線 1 6 0 はメモリシステム 1 0 0 で必要とする個数の並列信号経路(または信号経路 1 個のみ)を備えたデータバスとして機能する。メモリシステム 1 0 0 が 2 個以上のメモリモジュールを備えている場合、 C / A 導線 1 5 0、 D Q 導線 1 6 0、および D S 導線 1 7 0 はコントローラ 1 1 0 を各々のメモリモジュールに接続する。

# [0012]

いくつかの実施形態において、DS導線170は、ソース同期双方向タイミング基準として機能するデータストロープを送信する。コントローラ110/425とメモリモジュール120を相互接続する導線150、160、170の組は、集合的にメモリバス、またはより一般的に、相互接続部と呼ばれることもある。DS導線170は、コントローラ110を個別にメモリモジュール120内の各DRAM130に接続する。コントローラ110が所与のDQ導線160経由でDRAM130へデータを送信した場合、当該デー

20

30

40

50

タの送信および受信はコントローラ 1 1 0 が対応する D S 導線 1 7 0 経由で送信したデータストローブにより計時される。同様に、いくつかの実施形態において、 D R A M 1 3 0 が所与の D Q 導線 1 6 0 経由でコントローラ 1 1 0 ヘデータを送信した場合、当該データの送信および受信は D R A M 1 3 0 が対応する D S 導線 1 7 0 経由で送信したデータストローブにより計時される。

## [0013]

他の実施形態において、メモリシステム100内のDS導線170は、一方向的に動作すべく設定されている。より具体的には、DS導線170が送信するデータストローブは一方向性である。すなわちコントローラ110だけが生成および送信する。従ってDRAM130は、データストローブの受信を行なっても、データストローブの生成および送信は行なわない。これらの実施形態において、DRAM130が所与のDQ導線160経由でコントローラ110へデータを送信した場合、データの送信および受信はクロック・バッファ142から受信したクロック信号により計時される。

## [0014]

以下に詳述するように、メモリシステム100は、双方向または一方向のDS導線170と協働して動作すべく設定可能なコントローラ110およびDRAM130を含んでいる。本明細書に述べる実施形態は、一方向的に動作するコントローラ110および/またはDRAM130に限定されない。メモリシステム市場の過去、現在、未来にわたるニーズを満たすべく、単一の部品(例:コントローラ110、DRAM130/440/450、またはメモリモジュール120)が設定可能であってよい。換言すれば、これらの素子は後方互換性を維持しながら、向上した性能を提供することができる。

#### [0015]

図示していないが、コントローラ 1 1 0 (メモリコントローラと呼ばれる場合もある) は好適には、外部構成要素(すなわち図 1 に示していない構成要素)との間でデータを送受信する。また、コントローラ 1 1 0 はメモリモジュール 1 2 0 との間で同データを送受信し、メモリモジュール 1 2 0 が D Q 導線 1 6 0 経由で当該データを記憶する。より具体的には、D Q 導線 1 6 0 の各々がコントローラ 1 1 0 をメモリモジュール 1 2 0 内の D R A M 1 3 0 に接続している。図 1 に示すように、D Q 導線 1 6 0 は双方向性である。より具体的には、コントローラ 1 1 0 は D Q 導線 1 6 0 経由で D R A M 1 3 0 との間でデータを送受信する。

### [0016]

コントローラ 1 1 0 は制御およびアドレス信号により、 C / A 導線 1 5 0 経由で、メモリモジュール 1 2 0 の、従って D R A M 1 3 0 の動作を制御する。これらの信号によりコントローラ 1 1 0 は、コントローラ 1 1 0 が接続されている恐らく 2 個以上のメモリモジュール 1 2 0 のうちの 1 個を選択できるようになる。メモリモジュール 1 2 0 は、制御およびアドレス・バス 1 5 0 経由で、クロック・バス上のアサートされたクロック信号と共に、制御およびアドレス信号を受信すべく設定されており、クロック信号が制御およびアドレス信号の受信を計時する。 D R A M 1 3 0 への制御およびアドレス信号の送信は同期していて、 D O 導線 1 6 0 経由でデータ信号の同期送信と並列に動作する。

### [0017]

グローバル・クロック140は、クロック・バッファ142へ送信されるクロック(システム・クロックまたは基準クロックと呼ぶ場合がある)を生成し、クロック・バッファ142はコントローラ110およびメモリモジュール120へクロックを送る。クロック・バッファは通常、クロックの位相を揃えるべくPLLに基づいている。本明細書に引用している米国特許第5,485,490号に示す構成等、システムまたは基準クロックを配信する他のバス構造を用いてもよい。メモリモジュール120内で、PLLクロック・バッファ144は、クロック・バッファ142からクロックを受信する。PLLクロック・バッファ144は、モジュールクロック(メモリモジュール内で内部的に使用)の位相を、受信された基準クロックに揃えて、モジュールクロックをレジスタ152およびDRAM130へ送信する。メモリモジュール120へのデータおよび制御信号の送信は、こ

20

30

40

50

のようにグローバル・クロック140により生成されたクロックに同期している。

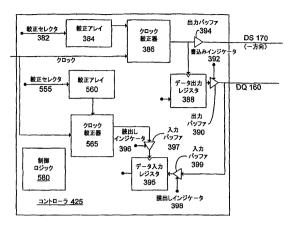

## [0018]

方向モード制御機能を備えたコントローラ

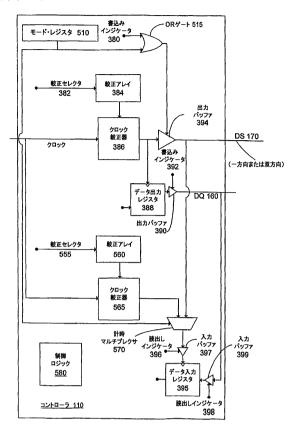

図2に、メモリシステム 1 0 0 のコントローラ 1 1 0 をより詳細に示す。図2が、典型的なコントローラの構成要素の小さいサブセットを概念的に表現したものである点に注意されたい。コントローラ 1 1 0 は、書込みインジケータ 3 8 0、データ出力レジスタ 3 8 8、出力バッファ 3 9 0、別の書込みインジケータ 3 9 2、出力バッファ 3 9 4、データ入力レジスタ 3 9 5、読出しインジケータ 3 9 6、入力バッファ 3 9 7、別の読出しインジケータ 3 9 8、および入力バッファ 3 9 9を含んでいる。いくつかの実装方式において、2個の読出しインジケータ 3 9 6、3 9 8は同一の読出し制御信号であり、2個の書込みインジケータ 3 8 0、3 9 2は同一の書込み制御信号である。

### [0019]

いくつかの実施形態において、コントローラは更に、較正セレクタ382、較正アレイ384、クロック較正器386を含んでいる一方、他の実施形態では、これらの要素は含まれていない。これらの要素を含まない実施形態において、クロック・バッファ142からのクロックは出力バッファ394に接続されている。

### [0020]

コントローラ 1 1 0 はまた、モード・レジスタ 5 1 0、 O R ゲート 5 1 5、較正セレクタ 5 5 5、較正アレイ 5 6 0、クロック較正器 5 6 5、および計時マルチプレクサ 5 7 0を含んでいる。追加的な制御ロジック 5 8 0 が図 2 に示す制御信号を生成し、更に本明細書の記述に関係しないコントローラ 1 1 0 の制御機能を実行する。モード・レジスタ 5 1 0 は、方向モードを記憶する。一般に、当該モードは、D S 導線 1 7 0 が一方向か双方向かを判定する。モード・レジスタ 5 1 0 は好適には、1個以上の外部構成要素(図示しない)によりコントローラ 1 1 0 が動作する間、またはコントローラ 1 1 0 を製造する間に設定されてよい。モード・レジスタ 5 1 0 により記憶された方向モードは、O R ゲート 5 1 5 へ、次いで計時マルチプレクサ 5 7 0 へ送信される。

## [0021]

上段に示したように、ORゲート515はモード・レジスタ510から入力を受信する。ORゲート515はまた、書込みインジケータ380から入力も受信する。ORゲート515の出力は従って、方向モードが「高」、または書込みインジケータ380が「高」のいずれかであれば「高」である。好適には、コントローラ110がデータをDRAMに書き込んだ場合、書込みインジケータ380は「高」であり、コントローラ110がデータの書き込みや読み込みを行なっているか、あるいは停止中であるに無関係に)で動作すべく設定されている場合、方向モードは「高」である。ORゲート515の出力は出力バッファ394に接続されていて、出力バッファ394を有効または無効にする。従って、コントローラ110がDRAMにデータを書き込んだ場合、またはコントローラ110が一方向モードで動作すべく設定されている場合に出力バッファ394は有効にされる。出力バッファ394が有効でない場合、その出力は出力バッファ394が有効でない場合、その出力は出力バッファ394が有効でない場合、その出力は3状態化され(すなわち高インピーダンス状態に設定される)、他のどの素子もDS導線上の信号をアサートしていなければDS導線170は浮動状態のままであり、より一般的には別の素子(例:メモリモジュール内のメモリ素子)によりDS導線170を駆動してもよい。

## [0022]

上に示したように、コントローラ110は、DRAM130へデータを送信する際に出力バッファ394の出力を有効にすべく書込みインジケータ380を設定する。また、コントローラ110は、コントローラ110が接続されている各メモリモジュール120用の較正データを記憶する。本出願で説明するメモリシステムにおいて、1個のメモリモジュール120だけを示す。しかし、メモリシステムは2つ以上のメモリモジュール120を含んでいてよい。メモリモジュール120へのコントローラ110の各種な接続は異なっていてよい。例えば、そのような接続の長さおよびインピーダンスは変わる場合がある

20

30

40

50

。その結果、タイミング信号(例:クロックまたはデータストローブ)を較正または調整 してもよい。

## [0023]

上に注記したように、いくつかの実施形態において、コントローラは、較正セレクタ382、較正アレイ384、およびメモリ素子にデータを書き込む際に用いるタイミング信号を調整するクロック較正器386を含んでいる。較正アレイ384は、この目的で較正データを記憶する。較正セレクタ382は、コントローラ110がどのメモリモジュール120に書き込むかに基づいて特定の較正を選択するコントローラ110により生成される信号を搬送する。較正セレクタ382は、例えば、較正アレイ384に記憶されている特定の較正値を選択するためのアドレスを送信することができる。

## [0024]

選択された較正値は、較正アレイ384によりクロック較正器386へ送信され、当該クロック較正器はまた、クロック・バッファ142からクロックを受信する。クロック較正器386は選択された較正値を用いることにより、受信したクロックの位相を調整する。いくつかの実施形態において、各々の記憶された較正値は、クロック信号の状態遷移をオフセットすべく遅延素子を指定する。いくつかの実施形態において、記憶された較正値は各々クロック位相を指定する。調整されたクロックは、コントローラ110が生成するデータストローブの基礎になる。当該データストローブはクロック較正器386により、データ出力レジスタ388および出力バッファ394へ送信する。データストローブは、出力バッファ394はデータストローブをDS導線170へ送信する。データストローブは、データ出力レジスタ388から出力バッファ390へのデータの出力を計時し、当該出力バッファはDQ導線160に接続されていて、書込みインジケータ392により有効にされる。

#### [0025]

ある動作モードにおいて、コントローラ110のデータ入力レジスタ395は、入力バッファ397からデータストローブを、および入力バッファ399からデータを受信する。入力バッファ397は、読出しインジケータ396により有効にされ、入力バッファ399は読出しインジケータ398により有効にされる。入力バッファ397は、DS導線170から入力(すなわちデータ・ストローブ)を受信し、入力バッファ399はDQ導線160から入力(すなわちデータ)を受信する。制御ロジック580コントローラ110は、DRAM130からデータを受信する際に、入力バッファ397、399を有効にすべく読出しインジケータ396、398を設定する。受信されたデータストローブは従って、データの受信を計時する。

## [0026]

コントローラ 1 1 0 が、 D S 導線を双方向的に用いるべく設定されている場合、 D R A M が データを送信する間、 データストローブはソース同期されていて、 D R A M により駆動される。このモードにおいて、コントローラ 1 1 0 は従来型 D R A M (例: D R A M 1 3 0) メモリモジュールと互換性を有する。しかし、コントローラが D S 導線 1 7 0 を一方向的に用いるべく設定されている場合、 データストローブはソース同期されておらず、 D R A M により駆動されない。このモードにおいて、 データストローブは、 コントローラ 1 1 0 により送信されたデータをサンプリングすべく自由継続クロックとして D R A M により用いることができる。

## [0027]

上述のように、メモリモジュール120は複数のDRAM130を含んでいる。従って、コントローラ110はメモリモジュール120内で各DRAM130用のデータ出力レジスタ388(しかし簡潔のため図示しないが)を含んでいてよい。クロック較正器386の出力は、各々のデータ出力レジスタ388に接続されている。また、各データ出力レジスタ388用に出力バッファ390が含まれていて、これは次いで各々のDQ導線160に接続している。書込みインジケータ392は、好適にはこれらのデータ出力レジスタ388の各々に接続していることにより、各データ出力レジスタ388の出力が同一デー

20

30

40

50

タストローブにより計時されて、同一書込みインジケータ392により有効にされる。また、メモリモジュール120内の各DRAM130用に出力バッファ394が含まれている。クロック較正器386の出力は各々のデータ出力バッファ394に接続しており、これは次いで各々のDS導線170に接続している。この構成により、コントローラはメモリモジュール120の各DRAM130に別々のデータを同時に送信することが可能になる。

## [0028]

所与の較正値は、従って、データストローブにより同時に計時される各々のデータ出力レジスタ388に適用される。出力バッファ390、394の所与の組に接続されたDS170およびDQ導線160の各々の組はまた、2つ以上のメモリモジュール120に接続されていてよい。従って、較正値は通常、メモリモジュール120内の各DRAM130ではなく、各メモリモジュール120について導かれる。特定のメモリモジュール120が選択された場合、選択されたメモリモジュール120がデータを受信すべく設定するために、各メモリモジュール120へ送信された制御およびアドレス信号にこの選択を反映させる。

#### [0029]

同様に、コントローラ110は、(簡潔のため図示しないが)メモリモジュール120内の各DRAM130(すなわちDS170およびDQ導線160の各組)用にデータ入力レジスタ395、入力バッファ397、および入力バッファ399を含んでいてよい。この構成により、コントローラは、メモリモジュール120の各DRAM130から別々のデータを同時に受信可能になる。データをコントローラに送信するために特定のメモリモジュール120が選択された場合、データおよびデータストローブをDQ160とDS導線170の各々に配置するのはこのメモリモジュール120だけである。

#### [0030]

較正セレクタ555は、コントローラ110がどのメモリモジュールから読み出しているかに応じて(すなわち、どのメモリモジュールがDQ導線160経由でコントローラ110へデータを送信しているかに応じて)、コントローラ110の制御ロジック580により生成された信号を搬送する。較正セレクタ555は、較正アレイ560に記憶された特定の較正値を選択すべくアドレスを送信することができる。

## [0031]

選択された較正値は、較正アレイ560によりクロック較正器565へ送信され、当該クロック較正器はまた、クロック・バッファ142からクロックも受信する。クロック較正器565は選択された較正値を用いて、受信したクロックの位相を調整する。調整済みクロックは、クロック較正器565により計時マルチプレクサ570へ送信される。較正セレクタ555、較正アレイ560、およびクロック較正器565は、方向モードが一方向である場合にだけ使用され、データの送信元であるメモリ素子に従って調整または較正された位相調整済み受信クロックを生成すべく使用される点に留意されたい。いくつかの実施形態において、省電力のため、方向モードが双方向の場合はクロック較正器565の動作が無効になる。

### [0032]

計時マルチプレクサ 5 7 0 は、クロック較正器 5 6 5 により送信された位相調整済みクロック、あるいは D S 導線 1 7 0 経由で送信されたデータストローブを送信すべく構成されている。計時マルチプレクサ 5 7 0 の出力は、ある状況では当該信号は受信されたデータストローブから導かれる場合もあるが、クロック信号または基準信号と呼ばれる。計時マルチプレクサ 5 7 0 による信号出力の選択はモード・レジスタ 5 1 0 により制御され、上述のように当該モード・レジスタは計時マルチプレクサ 5 7 0 へ方向モードを出力する。計時マルチプレクサ 5 7 0 の出力は入力バッファ 3 9 7 へ送信され、上述のように当該入力バッファは読出しインジケータ 3 9 6 により有効にされてデータ入力レジスタ 3 9 5 に接続されている。データ入力レジスタ 3 9 5 により受信されたデータは、従って、クロック較正器 5 6 5 が生成した調整済みクロックか、または D S 導線 1 7 0 経由で送信され

るデータストローブにより計時される。コントローラ110が双方向モードで動作すべく構成されている場合、計時マルチプレクサ570はDS導線170経由で送信されたデータストローブを入力バッファ397へ送信する。また、コントローラ110が一方向モードで動作すべく構成されている場合、計時マルチプレクサ570はクロック較正器565が生成した調整済みクロックを入力バッファ397に送信する。

### [0033]

従って、コントローラ110が、DS導線を双方向的に用いるべく構成されている場合、コントローラ110がデータストローブを用いて、DRAMにより送信されたデータをサンプリングすることができる。しかし、一方向的に動作すべく構成されている場合、コントローラ110による読込みデータの取得は、較正済み内部タイミング基準(例:調整済みクロック)により、計測または計時される。

10

#### [0034]

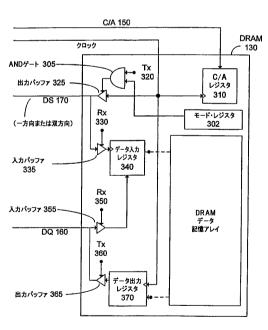

方向モード制御機能を備えたDRAM

図 3 に、メモリシステム 1 0 0 の D R A M 1 3 0 を示す。図 3 に示すように、 D R A M 1 3 0 は、モード・レジスタ 3 0 2 、 C / A レジスタ 3 1 0 、送信( T  $\times$  ) インジケータ 3 2 0 、出力バッファ 3 2 5 、受信( R  $\times$  ) インジケータ 3 3 0 、入力バッファ 3 3 5 、データ入力レジスタ 3 4 0 、受信インジケータ 3 5 0 、入力バッファ 3 5 5 、送信( T  $\times$  ) インジケータ 3 6 0 、出力バッファ 3 6 5 、データ出力レジスタ 3 7 0 、および A N D ゲート 3 0 4 を含んでいる。いくつかの実施形態において、 2 個の受信インジケータ 3 3 0 、3 5 0 は同一の受信制御信号であって、 2 個の送信インジケータ 3 2 0 、 3 6 0 は同一送信制御信号である。更に、送受信インジケータは互いに補完的であってよい。

20

#### [0035]

図3がDRAM・チップの構成要素の小さいサブセットの概念的な表現である点に注意されたい。例えば、この図に示すデータ入力およびデータ出力レジスタ340、370は、DRAMの感度増幅器アレイ等、DRAMの記憶アレイへのインタフェースにおける回路であって、当該回路が(例えばラッチその他のクロック制御された回路とは対照的に)厳密に「レジスタ」の定義を満たしていても、いなくてもよい。更に、図3ではデータ入力およびデータ出力レジスタ340、370を別々に示しているが、同一回路の一部または全体として実装されていてもよい。

[0036]

30

C / A レジスタ 3 1 0 は、(通常は図 1 の P L L クロック・バッファ 1 4 4 からの) クロックと、 C / A 導線 1 5 0 経由でコントローラ 1 1 0 から制御およびアドレス信号を受信する。クロックは、これらの制御およびアドレス信号の受信を計時または計測する。

[0037]

入力および出力バッファ335、325の第一の組は、DS導線170に接続されていて、各々データストローブの受信と送信を行なう。図に示すように、出力バッファ325が送信するデータストローブは、DRAM130がクロックから生成したものである。

[0038]

DRAMモード・レジスタ302は、DRAM130(または図4のDRAM440)と連動して使われた場合に方向モードを記憶する。方向モードは、DS導線170が一方向または双方向のいずれであるかを判定する。モード・レジスタ302は好適には、コントローラ110により、DRAM130が動作している間、またはDRAM130またはメモリモジュール120を製造する間に設定されてよい。いくつかの実施形態において、コントローラ110およびDRAM130は、コントローラが制御およびアドレス線150経由で、DRAMに対し特定のモード値をモード・レジスタ302に記憶すべく指示するコマンドを送信可能なように構成されている。モード・レジスタ302により記憶された方向モードは、ANDゲート304へ送信される。

[0039]

上段に示す A N D ゲート 3 0 4 は、 D R A M モード・レジスタ 3 0 2 から入力を受信する。 A N D ゲート 3 0 4 はまた、送信( T x )インジケータ 3 2 0 から入力を受信する。

50

20

30

40

50

方向モードが「高」であって、送信(Tx)インジケータ320が「高」である場合、A NDゲート304の出力は「高」である。好適には、DRAM130がコントローラヘデ ータストローブを送信し、DRAM130が双方向モードで動作すべく構成されている場 合、送信(Tx)インジケータ320および方向モードは「高」である。ANDゲート3 0 4 の出力は、出力バッファ 3 2 5 を有効または無効にすべく出力バッファ 3 2 5 に接続 されている。従って、DRAM130がデータを送信し、さらに、DRAM130が双方 向モードで動作すべく構成されている場合、出力バッファ325は有効にされて、データ 用のデータストローブがデータ出力レジスタ370から送信されるにつれて、受信された クロック信号をDS導線170へ送る。逆に、DRAM130が一方向モードで動作すべ く構成されている場合、出力バッファ325が無効になるようANDゲート304の出力 は低くなっている。出力バッファ325が有効でない場合、その出力が3状態(すなわち 高インピーダンス状態に設定)にされ、他のどの素子もDS導線上の信号をアサートして いなければDS導線170は浮動状態のままであり、より一般的には、別の素子(例:メ モリコントローラ 1 1 0、または D R A M 1 3 0 が存在するメモリモジュール 1 2 0 と同 ーメモリバス上の別のメモリモジュール内の別のメモリ素子)により D S 導線 1 7 0 を駆 動してもよい。

### [0040]

入力バッファ335が受信するデータストローブは、コントローラ110が生成および送信したものである。さらに、入力バッファ335は、受信(R×)インジケータ330により有効にされる(またはDS導線170からデータ入力レジスタ340ヘデータストローブを送信すべく設定される)。従って、DRAMがコントローラ110からデータを受信した場合、受信(R×)インジケータ330は入力バッファ335を有効にすべく設定される。データ入力レジスタ340によるデータの受信は従って、DS導線170経由で受信されたデータストローブにより計時される。

#### [0041]

入力および出力バッファ355、365の第二の組は、各々データを送受信すべくデータ信号(DQ)導線160に接続されている。図3に示すように、出力バッファ365が送信するデータはデータ出力レジスタ370から送信されたものであり、当該データアンスタはDRAM130内の記憶素子からデータを受信する。さらに、出力バッファ365は、送信(Tx)インジケータ360により有効にされる(またはDQ導線160へデータを送信すべく設定されている)。従って、DRAMがコントローラ110へデータを送信する場合、送信(Tx)インジケータ360は出力バッファ365が有効にされるように設定されている。入力バッファ355が受信するデータは、コントローラ110が送信したものである。また、入力バッファ355が受信するデータ入力レジスタは、受信したものである。また、入力バッファ355は、DQ導線160からデータ入力レジスタ340へデータを送信すべく有効にされていて、当該データ入力レジスタは、で、ファスタ350により、DRAM130内の記憶素子へデータを送信する。従って、DRAMがコントローラ110からデータを受信した場合、受信(Rx)インジケータ350は、入力バッファ355が有効にされるよう設定されている。データ出力レジスタ370によるデータの送信は従って、(DS導線170経由で受信されたデータストロープではなく)クロックにより計時される。

## [0042]

上述のように、DRAM130が双方向的にDS導線を用いるべく構成されている場合、DRAM130がデータを送信する間、データストローブはソース同期されていて、DRAM130により駆動される。ストローブ出力バッファ325とデータ出力バッファ365に付随する送信遅延は好適には同一であるか、またはほぼ同一に近い。その結果、これらの信号がコントローラに到達した際に、送信されたデータとデータストローブの位相関係は記憶される。このモードでは、DRAM130は従来型コントローラ(例:図1のコントローラ110)と互換性を有する。しかし、DRAM130が一方向的にDS導線を用いるべく構成されている場合、データストローブはソース同期されておらず、DRAMにより駆動されない。このモードでは、DRAM130は本明細書に述べるコントロー

20

30

40

50

ラ (例: DRAM130からデータを受信すべく較正されたタイミングを有するコントローラ)と互換性を有する。

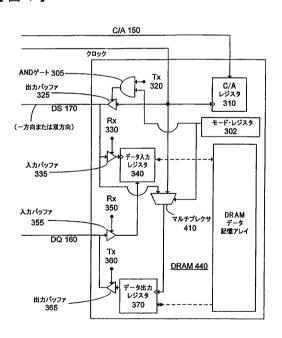

## [0043]

図4に、メモリシステム100のDRAM440の別の実施形態を示す。図3に示すDRAM130と関連して上で述べた構成要素に加え、図4に示すDRAM440はマルチプレクサ410を含んでいる。

#### [0044]

マルチプレクサ410は(通常はPLLクロック・バッファ144からの)クロックと、DS導線170により送信されたデータストローブを受信する。マルチプレクサの出力は、データ出力レジスタ370へ送信される。従って、マルチプレクサ410による選択に応じて、データ出力・バッファによるデータの出力は、クロックまたはDS導線170により送信されたデータストローブにより計測または計時される。この選択はモード・レジスタ302により行なわれ、方向モードを選択入力としてマルチプレクサ410へ送信する。

### [0045]

上で示したように、DRAM440が一方向的にDS導線170を用いるべく構成されている場合、DRAM440が出力したデータはコントローラ(例:コントローラ110)が生成したデータストローブにより計時される。これが可能なのは、コントローラにより常にデータストローブが送信されるためである。また、データストローブは通常、クロックより位相シフトが小さい点が問題であり、その結果、メモリバス経由のデータ送信速度が従来型システムよりも増大してもよい。このモードでは、DRAM440はDRAM440へデータストローブを連続的に送信すべく構成されたコントローラ(本明細書に述べるコントローラ等)と互換性を有する。しかし、DRAM440が一方向的にDS導線170を用いるべく構成されている場合、DRAM440がデータを送信する間、データストローブは利用できない。その代わり、DRAM440が出力したデータは、クロックにより計時される。このモードでは、DRAM440は従来型コントローラ(例:コントローラ110)と互換性を有する。

#### [0046]

追加的な実施形態

図5Aに、メモリシステム100で使用するコントローラ425の別の実施形態を示す。図2に示したコントローラ110とは異なり、図5Aに示すコントローラ425は双方向モードでは動作しない。従って、コントローラ425は、モード・レジスタ510、書込みインジケータ380、ORゲート515、または計時マルチプレクサ570を含んでいない。これらの構成要素が不要なのは、クロック較正器386の出力がDS導線170に連続的に印加されるからである。あるいは、コントローラは、方向モード値以外の各種モード値を記憶するモード・レジスタを含んでいてよい。

## [0047]

コントローラ425の本実施形態は、オプションとして、データ出力レジスタ388および出力バッファ390に付随する送信遅延に一致またはほぼ一致する信号遅延を提供すべく、データストローブ出力バッファ394を含んでいてよい。さらに、データ入力レジスタへの入力は、クロック較正器565の出力により常に計時されている。コントローラ425は、本明細書に述べるDRAM(例:DRAM130、DRAM440、およびDRAM450)と互換性を有するが、従来型DRAMとは互換性を有しない。

## [0048]

図5 Bに、メモリシステム 1 0 0 で使用する D R A M 4 5 0 の別の実施形態を示す。図3、4の D R A M 1 3 0、4 4 0 とは異なり、 D R A M 4 5 0 は A N D ゲート 3 0 4 または出力バッファ 3 2 5 を含んでいない。これは、 D R A M 4 5 0 が D S 導線 1 7 0 経由出でデータストローブを送信しないからである。さらに、データ出力レジスタ 3 7 0 の出力がクロックにより計時または計測されないため、 D R A M 4 5 0 はマルチプレクサ 4 1 0 を含んでいない。その代わり、データ出力レジスタ 3 7 0 はデータ入力レジスタ 3 4 0 と

同様に、DS導線170経由で送信されるデータストローブにより常に計時されている。 好適には、C/A導線150経由で送信された制御およびアドレス信号だけがクロックに より計時される。DRAM450は、本明細書に述べるコントローラ(例:コントローラ 110およびコントローラ425)と互換性を有するが、従来型コントローラとは互換性 を有しない。

### [0049]

特定の実施形態に関する上の記述は、例示および説明目的で提示されている。各実施形態は、本発明の原理および実際的な応用を最適に説明し、それにより他の当業者が本発明を最適に利用できるようにすべく選択および記述したものである。従ってこれらが全てではなく、開示した方式を以って本発明を限定するものでもない。本開示の利点を享受し得る当業者は、本明細書に述べた本発明の概念から逸脱することなく、各種の変更を想起することが可能であろう。

[0050]

例えば、上に述べた各種のデータストローブおよびクロック(すなわちクロック信号)は単一終端信号として提示されている。しかし、別の実施形態では、これらのデータストローブおよびクロックは差分信号である。差分信号を利用することにより、クロック速度およびデータ速度を向上させることが可能である。従って、単に上記の説明だけではなく、特許請求の範囲によって、本発明の排他的権利の規定を意図する。

【図面の簡単な説明】

[0051]

図面の簡単な説明

【図1】メモリシステムを示す図である。

【図2】図1に示すメモリシステムのコントローラを示す図である。

【図3】図1に示すメモリシステムに含まれるDRAMを示す図である。

【図4】図1に示すメモリシステムに含まれる別のDRAMを示す図である。

【図5A】図1に示すメモリシステムに含まれる別のコントローラを示す図である。

【図5日】図1に示すメモリシステムに含まれる別のDRAMを示す図である。

10

## 【図1】

【図2】

図 1

【図3】

【図4】

図 2

図 3

図 4

# 【図5A】

# 【図5B】

(一方向) Rx 330 プロック DS 170 Rx 350 スカバッファ 355 Rx 350 Rx 370 PRAM 450

図 5A

## フロントページの続き

## 審査官 野田 佳邦

(56)参考文献 特開平11-025029(JP,A)

特開2005-044494(JP,A)

特開2002-007200(JP,A)

特開2003-007069(JP,A)

特開2000-163965(JP,A)

特開2003-050739(JP,A)

米国特許第6188638(US,B1)

# (58)調査した分野(Int.CI., DB名)

G 0 6 F 1 2 / 0 0 - 1 2 / 0 6

G06F 13/16-13/18

G11C 11/401

G11C 11/409