# (19) **日本国特許庁(JP)**

# (12) 公 開 特 許 公 報(A)

(11)特許出願公開番号

特開2007-13640 (P2007-13640A)

(43) 公開日 平成19年1月18日(2007.1.18)

| (51) Int.C1. |       |            | FΙ   |      |      | テーマコード (参考) |

|--------------|-------|------------|------|------|------|-------------|

| HO4N         | 1/40  | (2006.01)  | HO4N | 1/40 | 103B | 5BO57       |

| G06T         | 5/00  | (2006.01)  | GO6T | 5/00 | 200A | 5CO77       |

| HO4N         | 1/405 | (2006, 01) | HO4N | 1/40 | В    |             |

#### 審査譜求 未譜求 譜求項の数 5 〇1. (全 29 頁)

|                       |                                                        | 音宜請水     | 不請水                                           | 雨水坝     | の数5  | OL   | ( <b>王</b> ) | 29 貝) |

|-----------------------|--------------------------------------------------------|----------|-----------------------------------------------|---------|------|------|--------------|-------|

| (21) 出願番号<br>(22) 出願日 | 特願2005-192341 (P2005-192341)<br>平成17年6月30日 (2005.6.30) | (71) 出願人 | 0000052                                       |         | :式会社 |      |              |       |

| (22) H MX H           | 1 /2011 1 0/100 [ (2000.0.00)                          |          | ブラザー工業株式会社<br>愛知県名古屋市瑞穂区苗代町15番1号<br>100079669 |         |      | 1号   |              |       |

|                       |                                                        | (74) 代理人 |                                               |         |      |      |              |       |

|                       |                                                        |          | 弁理士                                           | 神戸      | 典和   |      |              |       |

|                       |                                                        | (74) 代理人 | 理人 100111394                                  |         |      |      |              |       |

|                       |                                                        |          | 弁理士                                           | 佐藤      | 光俊   |      |              |       |

|                       |                                                        | (72) 発明者 | 杉本                                            | 典子      |      |      |              |       |

|                       |                                                        |          | 名古屋市瑞穂区苗代町15番1号 ブラザ<br>一工業株式会社内               |         |      | ブラザ  |              |       |

|                       |                                                        |          |                                               |         |      |      |              |       |

|                       |                                                        | Fターム (参  | 考) 5B05                                       | 57 AA11 | CA08 | CA12 | CA16         | CB07  |

|                       |                                                        |          |                                               | CB12    | CB16 | CC01 | CE13         | DA16  |

|                       |                                                        |          |                                               | DA17    | DB02 | DB09 | DC22         | DC36  |

|                       |                                                        |          | 5C07                                          | 77 LL19 | NN11 | PP46 | PP48         | PP68  |

|                       |                                                        |          |                                               | PQ12    | PQ18 | RR05 | TT02         |       |

|                       |                                                        |          |                                               |         |      |      |              |       |

#### (54) 【発明の名称】画像処理装置

### (57)【要約】

【課題】 誤差拡散法による画像処理における平均誤差 の算出を迅速に実行する。

【解決手段】 画像処理装置が備える平均誤差算出部 2 2 を、近傍画素の並びに対応させて配置された乗算部 2 6 a ~ 2 6 g ,加算記憶部 3 2 a ~ 3 2 gによって構成する。それら乗算部は、近傍画素の並びにおける最前の画素の誤差値 Y<sub>0</sub> , Y<sub>1</sub>と、各近傍画素に設定された重み付け係数 K a ~ K g とを乗算し、それら加算記憶部は、自身の後方側に配置されたものの記憶値と自身に対応する乗算部による乗算値とを加算して記憶する処理を行う。それら加算記憶部の処理は、前方に位置するもの 3 2 e , 3 2 f に向かって順次実行され、最前方に位置するもの記憶値を最終加算器 3 6 によって加算して平均誤差とする。このような構成とすることで、近傍画素の平均誤差の算出処理における処理クロック数を、可及的に減少させることが可能となる。

### 【選択図】 図5

### 【特許請求の範囲】

# 【請求項1】

あるマトリクスとして規定された複数の画素からなる原始画像の画像データを、誤差拡散法に従う処理によって、変換画像の画像データに変換するために用いられる画像処理装置であって、

当該画像処理装置が、

前記原始画像の画像データを構成するところのその画像の複数の画素の各々の画素値を、原始画素値と、前記変換画像の画像データを構成するところのその画像の複数の画素の各々の画素値を、変換画素値と、誤差拡散法に従う1つの画素についての処理を単位処理と、それぞれ、定義した場合において、

前記マトリクスにおける画素のラインの1つである対象ライン上に存在する1つの画素である対象画素についての単位処理を実行し、その対象画素の原始画素値に基づいて、その対象画素の変換画素値および変換誤差値を取得する単位処理実行部を備え、

前記対象画素がライン方向の前方に向かって順次遷移させられつつ、前記単位処理実行部による単位処理が前記対象ラインについて繰り返されるところの1ライン処理が実行され、かつ、その対象ラインが、順次遷移させられつつ、その1ライン処理が繰り返されることによって、前記原始画像の画像データを前記変換画像の画像データに変換するように構成され、

前記単位処理実行部が、

それぞれが前記マトリクスにおいて前記対象画素の近傍に設定されてその対象画素の変換画素値を取得するために自身の変換誤差値が利用される複数の画素を、複数の誤差利用画素と定義した場合において、

前回の1ライン処理での前記対象ライン上において互いに連続するものとして設定された複数の画素であって前記複数の誤差利用画素の少なくとも一部である複数の前ライン上誤差利用画素の各々の変換誤差値に基づいて、前記複数の誤差利用画素の平均誤差値を算出する平均誤差算出部を有し、

その平均誤差算出部によって算出された前記平均誤差値に基づいて前記対象画素の原始 画素値を補正し、その補正によって得られた画素値に基づいて、その対象画素の変換画素 値を取得するように構成され、

前記平均誤差算出部が、

前記複数の前ライン上誤差利用画素のうちのライン方向において最前に位置するものを前ライン上最前誤差利用画素と定義した場合において、

ライン方向に仮想的に配置され、前記複数の前ライン上誤差利用画素の各々に対応して設定された重み付け係数の各々と前記前ライン上最前誤差利用画素の変換誤差値との乗算処理を実行するところの前記複数の前ライン上誤差利用画素の数に相当する数の複数の前ライン用乗算部と、

それら複数の前ライン用乗算部の各々に対応して設けられ、それぞれが、自身の直近の後方側に配置されたものが存在する場合にはそのものの記憶値と前記複数の前ライン用乗算部のうちの自身に対応するものによる乗算処理の結果値とを加算して記憶し、自身の後方側に配置されたものが存在しない場合には前記複数の前ライン用乗算部のうちの自身に対応するものによる乗算処理の結果値を記憶するところの前記複数の前ライン上誤差利用画素の数に相当する数の複数の前ライン用加算記憶部とを有し、

それら複数の前ライン用加算記憶部の各々による処理が前方に配置されたものによる処理から順次実行されるように構成されるとともに、それら複数の前ライン用加算記憶部のうちの最前のものの記憶値に基づいて、前記平均誤差値を算出するように構成された画像処理装置。

#### 【請求項2】

前記平均誤差算出部が、

さらに、前記対象ライン上において前記対象画素とライン方向の後方側において連続するものとして設定された1以上の画素であって前記複数の誤差利用画素の一部である1以

10

20

30

40

上の当該ライン上誤差利用画素の各々の変換誤差値に基づいて、前記平均誤差値を算出するものとされるとともに、

ライン方向に仮想的に配置され、前記1以上の当該ライン上誤差利用画素の各々に対応して設定された重み付け係数の各々と前記対象画素の直近の後方側に位置する画素の変換誤差値との乗算処理を実行するところの前記1以上の当該ライン上誤差利用画素の数に相当する数の1以上の当該ライン用乗算部と、

それら1以上の当該ライン用乗算部の各々に対応して設けられ、それぞれが、自身の直近の後方側に配置されたものが存在する場合にはそのものの記憶値と前記1以上の当該ライン用乗算部のうちの自身に対応するものによる乗算処理の結果値とを加算して記憶し、自身の後方側に配置されたものが存在しない場合には前記1以上の当該ライン乗算部のうちの自身に対応するものによる乗算処理の結果値を記憶するところの前記1以上の当該ライン上誤差利用画素の数に相当する数の1以上の当該ライン用加算記憶部とを有し、

それら1以上の当該ライン用加算記憶部の各々による処理が前方に配置されたものによる処理から順次実行されるように構成されるとともに、さらにそれら1以上の当該ライン用加算記憶部のうちの最前のものの記憶値に基づいて、前記平均誤差値を算出するように構成された請求項1に記載の画像処理装置。

#### 【請求項3】

前記平均誤差算出部が、前記複数の前ライン用加算記憶部のうちの最前のものの記憶値と、前記1以上の当該ライン用加算記憶部のうちの最前のものの記憶値との和を、前記平均誤差値として算出するように構成された請求項2に記載の画像処理装置。

#### 【請求項4】

当該画像処理装置が、前記単位処理実行部による単位処理の実行ごとに、前記前ライン上最前誤差利用画素となる1つの画素の変換誤差値が入力されるものとされた請求項1ないし請求項3のいずれかに記載の画像処理装置。

### 【請求項5】

当該画像処理装置が、前記単位処理実行部による単位処理の実行ごとに、前記対象画素の変換誤差値が出力されるものとされた請求項4に記載の画像処理装置。

# 【発明の詳細な説明】

# 【技術分野】

[0001]

本発明は、誤差拡散法に従う画像処理によって画像データを変換するための画像処理装置に関する。

# 【背景技術】

# [0002]

誤差拡散法は、例えば、スキャナ等によって読み取られたある画像の画像データを、その画像をプリンタ等によって再現するための画像データに変換する際に用いられる手法であり、階調として表された画素値からなる原始画像データから、多値化(2値化を含む概念である)された画素値からなる変換画像データへの変換に対して適用され、良好なハーフトーン画像が再現可能な手法として、既に、広く用いられている。この誤差拡散法に従う画像処理は、例えば、下記特許文献に記載されている。

【 特 許 文 献 1 】 特 開 平 6 - 2 8 4 2 9 1 号 公 報

### 【発明の開示】

【発明が解決しようとする課題】

#### [0003]

画像読取装置,画像形成装置等の作動の高速化,高精度化に伴い、画像データの変換処理は、常に、より高速に実行でき,より負担の小さいものであることが求められ、また、電子機器の低コスト化に伴い、その変換処理を実行する装置も、より低コストであることが望まれる。そのことは、上記誤差拡散法に従った画像処理を実行する装置についてもあてはまり、その画像処理装置について種々の改良を施すことは、その装置の実用性を向上

20

30

40

30

40

50

させることに繋がるのである。そのような実情に鑑み、本発明は、実用性の高い画像処理 装置を提供することを課題とする。

#### 【課題を解決するための手段】

#### [0004]

上記課題を解決するために、本発明の画像処理装置は、誤差拡散法による画像処理、詳しくは、画像データの変換処理を実行する装置であって、対象画素値の変換に際に利用されるとことろのその画素の近傍に設定された複数の近傍画素の平均誤差値の算が、対象画素が存在する画素ラインの前のラインにある複数の前ライン近傍画素の並に対応して仮想的に配置された複数の乗算部と複数の加算記憶部とを有するよう方向で設定された重み付け係数とを乗りまるものとされ、それら加算記憶部は、それぞれ、自身の後方に配置されたものの記憶であるものとされ、それら加算記憶部が前方に位置するものから順に処理を実行するように表して、それら複数の加算記憶部の最前方に位置するもの記憶値に基づいて上記複数の近傍画素の平均誤差値を算出するように構成されたことを特徴とする。

#### 【発明の効果】

### [0005]

従来の画像処理装置では、対象画素についての処理ごとに、前ライン近傍画素の各々の誤差値と重み付け係数とを掛け合わせ、それら乗算値を合計することによって平均誤差値を算出していたのに対して、上記本発明の画像処理装置では、上記構成としたことにより、乗算値を累積的に加算するようにされている。したがって、平均誤差値の算出処理に必要なクロック数を減少させることが可能であり、また、回路構成の単純化が図れることなる。その結果、本画像処理装置は、実用性の高い画像処理装置となる。なお、本発明画像処理装置の具体的な構成および作用効果については、以下の〔発明の態様〕の項において詳しく説明する。

### 【発明の態様】

#### [0006]

以下に、本願において特許請求が可能と認識されている発明(以下、「請求可能発明」という場合がある)の態様をいくつか例示し、それらについて説明する。各態様は請求項と同様に、項に区分し、各項に番号を付し、必要に応じて他の項の番号を引用する形式で記載する。これは、あくまでも請求可能発明の理解を容易にするためであり、それらの発明を構成する構成要素の組み合わせを、以下の各項に記載されたものに限定する趣旨ではない。つまり、請求可能発明は、各項に付随する記載,実施例の記載等を参酌して解釈されるべきであり、その解釈に従う限りにおいて、各項の態様にさらに他の構成要素を付加した態様も、また、各項の態様から何某かの構成要素を削除した態様も、請求可能発明の一態様となり得るのである。

### [0007]

なお、下記(1)項および(2)項は、請求可能発明の態様ではなく、請求可能発明の前提となる構成要素を掲げた態様であり、それらの項のいずれかを引用する(11)項ないし(16)項の態様、および、(21)項ないし(40)項の態様が、並びに、(51)項の態様が、請求可能発明の種々の態様である。ちなみに、以下の各項において、(2)項を引用する(11)項が請求項1に相当し、(12)項と(13)項とを合わせたものが請求項2に、(14)項が請求項3に、(15)項が請求項4に、(16)項が請求項5に、それぞれ、相当する。

# [0008]

(1)あるマトリクスとして規定された複数の画素からなる原始画像の画像データを、 誤差拡散法に従う処理によって、変換画像の画像データに変換するために用いられる画像 処理装置であって、

前記原始画像の画像データを構成するところのその画像の複数の画素の各々の画素値を

30

40

50

、原始画素値と、前記変換画像の画像データを構成するところのその画像の複数の画素の各々の画素値を、変換画素値と、誤差拡散法に従う1つの画素についての処理を単位処理 と、それぞれ、定義した場合において、

前記マトリクスにおける画素のラインの1つである対象ライン上に存在する1つの画素である対象画素についての単位処理を実行し、その対象画素の原始画素値に基づいて、その対象画素の変換画素値および変換誤差値を取得する単位処理実行部を備え、

前記対象画素がライン方向の前方に向かって順次遷移させられつつ、前記単位処理実行部による単位処理が前記対象ラインについて繰り返されるところの1ライン処理が実行され、かつ、その対象ラインが、順次遷移させられつつ、その1ライン処理が繰り返されることによって、前記原始画像の画像データを前記変換画像の画像データに変換する画像処理装置。

### [0009]

#### [0010]

本項の態様おいて、上記「原始画素値」は、例えば、スキャナ,デジタルカメラ等によ って読み取られた画素ごとの光学的特性値に基づいて定まる値であって、濃度等のその画 素の特性を階調として表す値であればよく、例えば、0~255といった具合に離散的な 値であってもよく、連続的な値であってもよい。また、それらの画素値を平滑化,エッジ 強調化等のフィルタ処理を実行した後の画素値であってもよい。一方、上記「変換画素値 」は、原始画素値が上記単位処理によって変換された値であり、例えば、2値に多値化さ れた値であってもよく、3値以上に多値化された値であってもよい。なお、上記「ライン 方向」とは、上記原始画像,変換画像が互いに交差する2方向にマトリクス状に画素が配 列されたと考えた場合におけるその2方向のうちの一方、つまり、マトリクスを、行,列 で規定した場合において、行と列との一方を構成する画素の並ぶ方向である。本項の態様 では、平たく言えば、ライン方向に走査し、1つの画素のラインについてのそのライン方 向の走査を完了させつつ、ライン方向に交差する方向に走査されて、画像処理が行われる 。したがって、上記ライン方向を、主走査方向と呼ぶことも可能であり、ライン方向に交 差する方向(以下、「コラム方向」という場合がある)を副走査方向と呼ぶことも可能で ある。ちなみに、ライン方向,コラム方向における「前方」は、それぞれ、単位処理,上 記1ライン処理が進行する向きを意味し、「後方」は、それらの処理が進行する向きとは 反対の向きを意味するものとする。

# [0011]

本項の態様の画像処理は、作成された後の原始画像データを変換画像データに変換する場合に実行されるものであってもよい。つまり、例えば、ファイル化された原始画像データを、バッチ処理的に、変換画像データに変換するために実行するものであってもよい。また、作成されつつある原始画像データを、順次、変換画像データに変換する場合に実行されるものであってもよい。つまり、例えば、スキャナ等で読み取りつつ原始画像データが作成される過程において、その原始画像データのうちの一部の画素ラインについての画

像データが作成されるごとに、逐次その画像データを変換するといった処理(以下、「逐次的処理」という場合がある)、すなわち、ラインスキャナ等での読み取りと並行して実行されるようなものであってもよい。なお、その逐次的処理の場合、例えば、スキャナの受光素子が並ぶ方向に対応する方向を主走査方向とし、スキャナヘッドの移動方向に対応する方向を、上記副走査方向とすることが可能である。

#### [0012]

本項の態様の画像処理装置は、ハード的にいえば、専用の電子回路,電気回路として構成されるものであってもよく、また、コンピュータを主体として構成されるものであってもよい。コンピュータを主体とするものである場合、専用の画像処理プログラムがそのコンピュータによって実行されることで上記画像処理が実現するような構成のものとすることが可能である。

#### [0013]

(2) それぞれが前記マトリクスにおいて前記対象画素の近傍に設定されてその対象画素の変換画素値を取得するために自身の変換誤差値が利用される複数の画素を、複数の誤差利用画素と定義した場合において、

前記単位処理実行部が、

前回の1ライン処理での前記対象ライン上において互いに連続するものとして設定された複数の画素であって前記複数の誤差利用画素の少なくとも一部である複数の前ライン上誤差利用画素の各々の変換誤差値に基づいて、前記複数の誤差利用画素の平均誤差値を算出する平均誤差算出部を有し、

その平均誤差算出部によって算出された前記平均誤差値に基づいて前記対象画素の原始画素値を補正し、その補正によって得られた画素値に基づいて、その対象画素の変換画素値を取得するように構成された(1)項に記載の画像処理装置。

#### [0014]

誤差拡散法に従う画像処理では、対象画素の変換画素値を決定する場合に、その対象画素の近傍の画素、つまり、周辺の画素であって、既に単位処理が実行された画素の変換誤差値を平均化した平均誤差値が利用される。本項の態様の画像処理装置は、その可変換誤差値を算出する機能部を備えた態様である。上記「誤差利用画素」は、上記「前ラインに限定された画素のライン(以下、「前回の1ライン処理が実行された回表のライン(以下、「前回の1ライン処理がまって構成されるものに限定されない」という場合がある)上の複数の画素のみにはがまれるものに限定されない下で構成されるものに限定がある)とのもで構成されるものに限定されたの重素をも含んで構成されるものであってもよいで構成されるものであってもよい。また、前ラインより前に1カイン処理が表された1以上の画素の多々の画素値に対してである。は、誤差利用画素の各々の画素値に対けを施した平均値を意味でもとがである。ちなみに、各画素値についての重み付けをあることによって、単純平均誤差値とすることも可能である。

# [ 0 0 1 5 ]

(11)前記複数の前ライン上誤差利用画素のうちのライン方向において最前に位置するものを前ライン上最前誤差利用画素と定義した場合において、

前記平均誤差算出部が、

ライン方向に仮想的に配置され、前記複数の前ライン上誤差利用画素の各々に対応して設定された重み付け係数の各々と前記前ライン上最前誤差利用画素の変換誤差値との乗算処理を実行するところの前記複数の前ライン上誤差利用画素の数に相当する数の複数の前ライン用乗算部と、

それら複数の前ライン用乗算部の各々に対応して設けられ、それぞれが、自身の直近の後方側に配置されたものが存在する場合にはそのものの記憶値と前記複数の前ライン用乗算部のうちの自身に対応するものによる乗算処理の結果値とを加算して記憶し、自身の後方側に配置されたものが存在しない場合には前記複数の前ライン用乗算部のうちの自身に

20

30

40

30

40

50

対応するものによる乗算処理の結果値を記憶するところの前記複数の前ライン上誤差利用 画素の数に相当する数の複数の前ライン用加算記憶部とを有し、

それら複数の前ライン用加算記憶部の各々による処理が前方に配置されたものによる処理から順次実行されるように構成されるとともに、それら複数の前ライン用加算記憶部のうちの最前のものの記憶値に基づいて、前記平均誤差値を算出するように構成された(2)項に記載の画像処理装置。

### [0016]

本項に記載の態様は、平均誤差値の算出処理の改善を目的とする態様である。従来の画 像処理装置では、対象画素についての単位処理ごとに、上記前ライン上誤差利用画素の各 々 の 変 換 誤 差 値 と 、 そ れ ら の 画 素 の 各 々 に つ い て 設 定 さ れ た 重 み 付 け 係 数 と を 掛 け 合 わ せ 、その掛け合わせた各々の値を合計することによって、平均誤差値の少なくとも一部を算 出している。したがって、当該画像処理装置が、電子回路,電気回路を主体として構成さ れるようなものの場合、単位処理ごとに、変換誤差値と重み付け係数とを掛け合わせたも のを、一旦記憶して、その記憶したものを、順次、加算する必要があるため、それら乗算 の結果を記憶するの複数のレジスタに加え、加算用としてのレジスタをも必要とされ、そ の分回路構成が煩雑となり、また、平均誤差値の算出処理のためのクロック数が、少なく とも前 ライン 上 誤 差 利 用 画 素 の 数 に 相 当 す る ク ロ ッ ク 数 必 要 と な る た め 、 処 理 時 間 が 長 く かかることになる。それに対し、本項に記載の態様では、前ライン誤差利用画素のうちの 1 つのものの変換誤差値と、前ライン誤差利用画素の数設定された重み付け係数の各々と を掛け合わせたものを、単位処理の進行に伴って累積的に加算するようなレジスタ構成す ることができるため、レジスタの数を少なくして回路構成を単純化することが可能となり 、また、平均画素値の算出処理に要するクロック数を、極端に言えば、1クロックとする ことも可能となる。

### [0017]

なお、本項にいう「ライン方向に仮想的に配置され」とは、上記前ライン用乗算部が実際にその方向に配置されていることを意味するのではなく、それら前ライン用乗算部が、前ライン上誤差利用画素の並びに対応していることを意味し、上記乗算部と上記前ライン上誤差利用画素の各々について設定された重み付け係数との対応関係,どの乗算部による乗算処理の結果値をどの前ライン用加算記憶部の記憶値と加算してどの前ライン用加算記憶部に記憶するかといった対応関係を規定するために、便法的に導入した概念である。ちなみに、本項の対応では、前ライン用乗算部の各々による乗算処理の結果値は、単位処理の進行に伴い、前ライン用加算記憶部によって、仮想的に配置された方向における後方側から前方側に向かって、換言すれば、対象画素が遷移する方向と同じ方向に向かって、加算されることになる。

# [0018]

(12)前記平均誤差算出部が、

さらに、前記対象ライン上において前記対象画素とライン方向の後方側において連続するものとして設定された1以上の画素であって前記複数の誤差利用画素の一部である1以上の当該ライン上誤差利用画素の各々の変換誤差値に基づいて、前記平均誤差値を算出するものとされた(11)項に記載の画像処理装置。

# [ 0 0 1 9 ]

(13)前記平均誤差算出部が、

ライン方向に仮想的に配置され、前記1以上の当該ライン上誤差利用画素の各々に対応して設定された重み付け係数の各々と前記対象画素の直近の後方側に位置する画素の変換誤差値との乗算処理を実行するところの前記1以上の当該ライン上誤差利用画素の数に相当する数の1以上の当該ライン用乗算部と、

それら1以上の当該ライン用乗算部の各々に対応して設けられ、それぞれが、自身の直近の後方側に配置されたものが存在する場合にはそのものの記憶値と前記1以上の当該ライン用乗算部のうちの自身に対応するものによる乗算処理の結果値とを加算して記憶し、自身の後方側に配置されたものが存在しない場合には前記1以上の当該ライン乗算部のう

20

30

40

50

ちの自身に対応するものによる乗算処理の結果値を記憶するところの前記 1 以上の当該ライン上誤差利用画素の数に相当する数の 1 以上の当該ライン用加算記憶部とを有し、

それら1以上の当該ライン用加算記憶部の各々による処理が前方に配置されたものによる処理から順次実行されるように構成されるとともに、さらにそれら1以上の当該ライン用加算記憶部のうちの最前のものの記憶値に基づいて、前記平均誤差値を算出するように構成された(12)項に記載の画像処理装置。

[0020]

上記2つの項に記載の態様は、現在1ライン処理が実行されている画素のラインである当該ライン上においても誤差利用画素が設定されている態様である。そして、それら2つの項における後者は、当該ライン上誤差利用画素に対しても、上述した前ライン上誤差利用画素における算出処理と同様の処理を実行する態様とされており、上述の算出処理が実行される場合と同様のメリットを、当該ライン上誤差利用画素についての処理に対して有することとなる。

[0021]

(14)前記平均誤差算出部が、前記複数の前ライン用加算記憶部のうちの最前のものの記憶値と、前記1以上の当該ライン用加算記憶部のうちの最前のものの記憶値との和を、前記平均誤差値として算出するように構成された(13)項に記載の画像処理装置。

[0022]

本項に記載の態様は、誤差利用画素が、前ライン上誤差利用画素,当該ライン上誤差利用画素のみから構成された場合に有効な態様である。

[ 0 0 2 3 ]

(15)当該画像処理装置が、前記単位処理実行部による単位処理の実行ごとに、前記前ライン上最前誤差利用画素となる1つの画素の変換誤差値が入力されるものとされた(11)項ないし(14)項のいずれかに記載の画像処理装置。

[0024]

先に説明した従来の画像処理装置では、対象画素についての単位処理ごとに、上記前ライン上誤差利用画素の各々の変換誤差値と重み付け係数とが掛け合わされる。したがって、例えば、既に単位処理が完了した前ラインにおける画素の変換誤差値が、当該画像処理装置の外部から入力されるような場合には、複数の画素についての変換誤差値を入力する必要があるため、その入力処理が煩雑であり、また、そのことが、画像処理の速度の向上を阻害する要因となっている。それに対し、前ライン上誤差利用画素のうち最前の画素の変換画素値のみが重み付け係数と掛け合わされる上述の態様では、単位処理ごとに、その最前の画素の変換画素値のみを入力すればよいことになる。本項に記載の態様は、そのことに鑑みた態様であり、本項の態様によれば、変換誤差値の入力処理を単純化することが可能であり、そのことによって当該画像処理の高速化が可能となる。

[0025]

(16)当該画像処理装置が、前記単位処理実行部による単位処理の実行ごとに、前記対象画素の変換誤差値が出力されるものとされた(15)項に記載の画像処理装置。

[0026]

単位処理が完了した画素の変換誤差値は、次の1ライン処理における前ライン上誤差利用画素となる。本項に記載の態様は、そのことに鑑みて、単位処理ごとに対象画像の変換誤差値を出力する態様である。変換画素値が当該画像処理装置の外部に設けられた記憶手段に記憶されるような場合、本項の態様では、単位処理ごとに、1の画素の変換誤差値が入力されるとともに、1つの画素の変換誤差値が出力されることになり、変換誤差値の入出力処理が簡素化されたものとなる。

[0027]

(21)当該画像処理装置が、

前記原始画像の画像データを、前記マトリクスであるその原始画像のマトリクスのラインの間に画素を補いつつ、そのマトリクスが画素のラインによって補間された別のマトリクスとして規定された複数の画素からなる前記変換画像の画像データに変換するために用

30

40

50

いられるものであり、

前記原始画像の画素のマトリクスにおける画素のラインであって前記変換画像の画素のマトリクスにおいても存置される画素のラインの各々を、原始ラインと、その原始ラインに対応して前記原始画像の画素のマトリクスを補間するための画素のラインを、補間ラインと、それぞれ、定義した場合において、

原始ラインの1つを前記対象ラインとし、その対象ライン上に存在する1つの画素である第1対象画素を前記対象画素として、その第1対象画素についての単位処理を実行し、その第1対象画素の原始画素値に基づいて、その第1対象画素の変換画素値および変換誤差値を取得するところの前記単位処理実行部としての第1単位処理実行部と、

その第1単位処理実行部によって今回以前に実行された1の単位処理において前記第1対象画素とされた今回以前第1対象画素の原始画素値を、前記対象ラインに対応する補間ライン上において前記第1対象画素と対応付けられた第2対象画素の画素値として、その画素値に基づき、前記第1単位処理実行部によって取得された前記第1対象画素の変換誤差値を利用しつつ、前記第2対象画素についての単位処理を実行し、その第2対象画素の変換画素値を取得する第2単位処理実行部とを備え、

前記第 1 対象画素および前記第 2 対象画素がライン方向の前方に向かって順次遷移させられつつ、前記第 1 単位処理実行部による単位処理と前記第 2 単位処理実行部による単位処理とがそれぞれ前記対象ラインと前記補間ラインとについて繰り返されるところの 1 ライン処理が実行されるように構成された (1)項に記載の画像処理装置。

### [0028]

従来、前述の副走査方向において画素のラインが補間された変換画像を作成する場合、まず、原始画像のライン間に画素のラインを補間した別の原始画像(以下、「補間原始画像のライン間に画素のラインを補間した別の原始画像を作成で、「補間原始画像に対して誤差拡散法に従う画像を実行することで、その変換画像が作成される。このような従来の処理では、例えばを記憶しておくために大きなのりと並行う場合、補間原始画像を記憶しておくために大きのようなでも、ラインスキャナ等による画像に対してで表現りと並行でも、の前述の逐次的処理を行う場合でも、1の画素のフィルタ処理でとに複数の画素についての画素値にアクセスしなければならない等の事情から、フィルタ処理を行っていての画素値にアクセスしなければならない等の事情から、フィルタ処理を行ってが困難である。本項に記載の態様は、そのような実情に当該画像処理を高速に行うことが困難である。本項に記載の態様は、そのような鑑み、副走査方向にライン補間された変換画像を簡便に作成可能とすることを、1つの目的とするものである。

# [ 0 0 2 9 ]

本項の態様の画像処理装置は、平たく言えば、上述の単位処理を実行する単位処理実行部を2つ有するものとし、2つの単位処理実行部の一方である第1単位処理実行部が、原始画像における対象ライン上の1つの画素についての単位処理を実行し、2つの単位処理実行部の他方である第2単位処理実行部が、第1単位処理実行部による処理における原始画素値を補間ライン上の1つの画素の原始画素値とみなして、その1つの画素についての単位処理を実行するように構成されている。したがって、2つの単位処理実行部の一連の単位処理によって、対象ライン上の1つの画素,補間ライン上の1つの画素についての変換画像値が得られることとなり、本項の態様の画像処理装置によれば、簡便に、ライン補間を行いつつ誤差拡散法に従う画像処理を行うことが可能となる。

# [0030]

本項の態様における「今回以前第1対象画素」は、第1単位処理実行部において今回の単位処理の対象とされたものであってもよく、また、前回以前の単位処理の対象とされたものであってもよい。前者の場合は、第1単位処理実行部と第2単位処理実行部との一連の処理によって、同じコラムの2つの画素、つまり、ライン方向における画素の並びにおける同じ順位にある2つの画素の原始画素値が、変換画素値に変換されることになる。それに対して、後者の場合には、補間ライン上の対象画素は、対象ライン上の対象画素に対

して、ライン方向の後方側に位置する画素となる。つまり、補間ライン上の画素の原始画素値は、対象ライン上の画素の画素値に対して遅れて変換されるのである。

#### [0031]

なお、本項は、1つの補間ラインによる画素のラインの補間を行う表現とされているが、2以上の補間ラインによる補間を行う態様を排除するものではない。つまり、例えば、主走査方向であるライン方向の画素数(ライン数に相当する)が300ピクセルであり、ころの(以下、「600×300」という場合がある)原始画像データを、600×600の変換画像データに変換する場合だけでなく、600×600、600×900・・といった変換画像データに変換する場合にも適用することが可能である。具体的えば、上記対象ライン上において、今回以前に第1対象画素とされた原始画素を、ち、上記補間ライン上において、今回以前に第2対象画素とされた画素を第3対象方、上記補間ライン上において、今回以前に第2対象画素とされた画素を第3対をといった。といった変換画素値に基づいて、その画素の変換画素値を取得する第3単位処理実行のといるに備えるような態様とすることが可能である。その態様によれば、上記補間ラインとは別のさらなる補間ラインを補いつつ、誤差拡散法に従う画像処理が実行可能である。

#### [0032]

(22)当該画像処理装置が、前記第1単位処理実行部による単位処理の実行ごとに、前記第1対象画素となる1つの画素の原始画素値が入力され、その単位処理の実行および前記第2単位処理実行部による単位処理の実行ごとに、前記第1対象画素および前記第2対象画素の各々の変換画素値が出力されるものとされた(21)項に記載の画像処理装置。

#### [0033]

本項に記載の態様によれば、当該画像処理装置に対する画素値の入出力処理が単純化される。つまり、先に説明したように、逐次的処理を実行する場合においても、予め画素を補うことなく、当該画像処理装置に1の画素ごとの原始画素値を入力すればよく、画素値の入力処理が特に簡便なものとなる。また、例えば、上記フィルタ処理が実行されるような場合であっても、そのフィルタ処理の段階で画素を補うことを要しないことから、そのフィルタ処理の負担を軽減でき、画像処理全体の速度の向上を図ることが可能となる。

### [0034]

(23)前記今回以前第1対象画素が、前記第1単位処理実行部によって前回以前に実行された1の単位処理において前記第1対象画素とされたものであり、

当該画像処理装置が、前記今回以前第 1 対象画素の原始画素値を、その画素値を前記第 2 対象画素の画素値とした前記第 2 単位処理実行部による単位処理が実行されるまでの間記憶する原始画素値一時記憶部を備えた(21)項または(22)項に記載の画像処理装置。

### [0035]

本項に記載の態様は、補間ライン上における単位処理の対象となる画素が、対象ライン上における単位処理の対象となる画素より、ライン方向において後方側に位置するような場合に有効な態様となる。そのような場合においても、本項の態様の画像処理装置によれば、上記原始画素一時記憶部は相当に小さなメモリ,あるいは,小さなレジスタとすればよく、当該画像処理装置の構成の単純化が図れることになる。なお、本項の態様は、単位処理ごとに1つの原始画素値のみが入力されるような態様において、特に有効である。

# [0036]

(24)それぞれが前記変換画像の画素のマトリクスにおいて前記第2対象画素の近傍に設定されてその第2対象画素の変換画素値を取得するために自身の変換誤差値が利用される複数の画素を、複数の第2誤差利用画素と定義した場合において、

前記第2単位処理実行部が、

前記対象ライン上において設定された複数の画素であって前記複数の第2誤差利用画素の少なくとも一部である複数の第2前ライン上誤差利用画素の各々の変換誤差値に基づいて、前記複数の第2誤差利用画素の平均誤差値である第2平均誤差値を算出する第2平均誤差算出部を有し、

その第2平均誤差算出部によって算出された前記第2平均誤差値に基づいて前記第2対

20

30

40

象画素の画素値を補正し、その補正によって得られた画素値に基づいて、その第 2 対象画素の変換画素値を取得するように構成され、

前記第2平均誤差算出部が、前記第1対象画素の変換誤差値を、前記複数の第2前ライン上誤差利用画素のうちの1つの画素の変換誤差値として利用して、前記第2平均誤差値を算出するように構成された(21)項ないし(23)項のいずれかに記載の画像処理装置。

#### [0037]

本項に記載の態様は、上記第2対象画素についての単位処理について、平均誤差値の算出処理に関する限定を加えた態様である。詳しく言えば、その対象画素に対する誤差利用画素のうちの前ライン上誤差利用画素を上記対象ライン上の画素とし、かつ、今回の第1対象画素についての単位処理によって得られた変換誤差値を、直接的に、詳しく言えば、その変換誤差値を画像処理装置外部から入力されることなく利用する態様である。本項の態様によれば、例えば、第1対象画素の変換誤差値を、連続的に行われる第2対象画素についての単位処理において利用するような態様とすることも可能であり、当該画像処理装置の処理の流れ、詳しくは、第1単位処理実行部から第2単位処理実行部への画素値の受け渡しを単純化することが可能である。

#### [0038]

(25)前記第2単位処理実行部が、前記第2対象画素についての単位処理によって、 さらに、その第2対象画素の変換誤差値を取得するものとされ、

前記第2平均誤差算出部が、さらに、前記補間ライン上において前記第2対象画素とライン方向の後方側において連続するものとして設定された1以上の画素であって前記複数の第2誤差利用画素の一部である1以上の第2当該ライン上誤差利用画素の各々の変換誤差値に基づいて、前記第2平均誤差値を算出するものとされた(24)項に記載の画像処理装置。

### [0039]

本項に記載の態様は、第2対象画素対する誤差利用画素が、当該ラインとしての上記補間ライン上の画素をも含む態様である。

#### [ 0 0 4 0 ]

(26)前記複数の第2前ライン上誤差利用画素が、互いに連続する複数の画素として 設定され、

前記第2単位処理実行部が、前記第1対象画素の変換誤差値を前記複数の第2前ライン上誤差利用画素のうちのライン方向において最前に位置する第2前ライン上最前誤差利用画素の変換誤差値として利用可能な画素を、前記第2対象画素として、その画素についての単位処理を実行するようにされた(24)項または(25)項に記載の画像処理装置。

### [0041]

本項に記載の態様は、第 1 対象画素と第 2 対象画素とのライン方向の位置関係が限定された態様であり、詳しく言えば、例えば、今回の単位処理における第 1 対象画素の変換誤差値が、今回以後の単位処理における第 2 対象画素についての前ライン誤差利用画素のうちの最も前方のものの変換誤差値として利用されるように、 2 つの対象画素の位置関係が限定された態様である。後に説明する態様であるが、前述の平均誤差値の算出処理を第 2 対象画素についての単位処理に適用する場合に、特に有効となる。

# [ 0 0 4 2 ]

(27)前記第2平均誤差算出部が、

ライン方向に仮想的に配置され、前記複数の第2前ライン上誤差利用画素の各々に対応して設定された重み付け係数の各々と前記第2前ライン上最前誤差利用画素の変換誤差値との乗算処理を実行するところの前記複数の第2前ライン上誤差利用画素の数に相当する数の複数の第2前ライン用乗算部と、

それら複数の第2前ライン用乗算部の各々に対応して設けられ、それぞれが、自身の直近の後方側に配置されたものが存在する場合にはそのものの記憶値と前記複数の第2前ライン用乗算部のうちの自身に対応するものによる乗算処理の結果値とを加算して記憶し、自身の後方側に配置されたものが存在しない場合には前記複数の第2前ライン用乗算部の

10

20

30

40

うちの自身に対応するものによる乗算処理の結果値を記憶するところの前記複数の第 2 前 ライン上誤差利用画素の数に相当する数の複数の第 2 前ライン用加算記憶部とを有し、

それら複数の第2前ライン用加算記憶部の各々による処理が前方に配置されたものによる処理から順次実行されるように構成されるとともに、それら複数の第2前ライン用加算記憶部のうちの最前のものの記憶値に基づいて、記第2平均誤差値を算出するように構成された(26)項に記載の画像処理装置。

#### [ 0 0 4 3 ]

(28)前記第2単位処理実行部が、前記第2対象画素についての単位処理によって、 さらに、その第2対象画素の変換誤差値を取得するものとされ、

前記第2平均誤差算出部が、

さらに、前記補間ライン上において前記第2対象画素とライン方向の後方側において連続するものとして設定された1以上の画素であって前記複数の第2誤差利用画素の一部である1以上の第2当該ライン上誤差利用画素の各々の変換誤差値に基づいて、前記第2平均誤差値を算出するものとされ、

ライン方向に仮想的に配置され、前記1以上の第2当該ライン上誤差利用画素の各々に対応して設定された重み付け係数の各々と前記第2対象画素の直近の後方側に位置する画素の変換誤差値との乗算処理を実行するところの前記1以上の第2当該ライン上誤差利用画素の数に相当する数の1以上の第2当該ライン用乗算部と、

それら1以上の第2当該ライン用乗算部の各々に対応して設けられ、それぞれが、自身の直近の後方側に配置されたものが存在する場合にはそのものの記憶値と前記1以上の第2当該ライン用乗算部のうちの自身に対応するものによる乗算処理の結果値とを加算して記憶し、自身の後方側に配置されたものが存在しない場合には前記1以上の第2当該ライン用乗算部のうちの自身に対応するものによる乗算処理の結果値を記憶するところの前記1以上の第2当該ライン上誤差利用画素の数に相当する数の1以上の第2当該ライン用加算記憶部とを有し、

それら1以上の第2当該ライン用加算記憶部の各々による処理が前方に配置されたものによる処理から順次実行されるように構成されるとともに、さらにそれら1以上の第2当該ライン用加算記憶部のうちの最前のものの記憶値に基づいて、前記第2平均誤差値を算出するように構成された(27)項に記載の画像処理装置。

#### [0044]

(29)前記第2平均誤差算出部が、前記複数の第2前ライン用加算記憶部のうちの最前のものの記憶値と、前記1以上の第2当該ライン用加算記憶部のうちの最前のものの記憶値との和を、前記第2平均誤差値として算出するように構成された(28)項に記載の画像処理装置。

# [0045]

上記3つの頃に記載の態様は、前述の特徴的な平均誤差値の算出処理を第2対象画素についての単位処理に適用する各種の態様である。上記3つの頃に記載の平均誤差値の算出処理に関する構成は、先に説明した処理に関する構成と同様であるため、ここでの説明は省略する。なお、先に説明した当該処理によるメリットは、上記3つの項の態様においても、享受されることとなる。

# [0046]

(30)それぞれが前記変換画像の画素のマトリクスにおいて前記第1対象画素の近傍に設定されてその第1対象画素の変換画素値を取得するために自身の変換誤差値が利用される複数の画素を、複数の第1誤差利用画素と定義した場合において、

前記第1単位処理実行部が、

前回の1ライン処理での前記補間ライン上において設定された複数の画素であって前記複数の第1誤差利用画素の少なくとも一部である複数の第1前ライン上誤差利用画素の各々の変換誤差値に基づいて、それら前記複数の第1誤差利用画素の平均誤差値である第1平均誤差値を算出する第1平均誤差算出部を有し、

その第1平均誤差算出部によって算出された前記第1平均誤差値に基づいて前記第1対

10

20

30

象画素の原始画素値を補正し、その補正によって得られた画素値に基づいて、その第 1 対象画素の変換画素値を取得するように構成された(21)項ないし(29)項のいずれかに記載の画像処理装置。

#### [0047]

(31)前記第1平均誤差算出部が、

さらに、前記対象ライン上において前記第1対象画素とライン方向の後方側において連続するように設定された1以上の画素であって前記複数の第1誤差利用画素の一部である1以上の第1当該ライン上誤差利用画素の各々の変換誤差値に基づいて、前記第1平均誤差値を算出するものとされた(30)項に記載の画像処理装置。

#### [0048]

(32)前記第1平均誤差算出部が、

前回の1ライン処理での1の単位処理において前記第2対象画素とされた1つの画素であって前記第1対象画素と対応付けられた対応前回ライン処理画素の変換誤差値を、前記複数の第1前ライン上誤差利用画素のうちの1つの画素の変換誤差値として利用して、前記第1平均誤差値を算出するものとされた(30)項または(31)項に記載の画像処理装置。

#### [0049]

上記3つの項に記載の態様は、先に説明したとことろの第2対象画素についての平均誤差の算出処理と同様の処理を、上記第1対象画素についての単位処理についても適用した態様である。それら3つの項に記載されている平均誤差の算出処理の説明は、先の説明と重複する部分が多いため、ここでの説明は省略する。

#### [0050]

(33)前記第2単位処理実行部が、前記第2対象画素についての単位処理によって、 さらに、その第2対象画素の変換誤差値を取得するものとされ、

当該画像処理装置が、前記第2単位処理実行部による単位処理の実行ごとに、前記第2対象画素の変換誤差値が出力され、前記第1単位処理実行部による単位処理の実行ごとに、前記対応前回ライン処理画素となる1つの画素の変換誤差値が入力されるものとされた(32)項に記載の画像処理装置。

#### [0051]

本項に記載の態様は、変換誤差値の当該画像処理装置に対する入出力に対する限定を加えた態様である。本項の態様では、第1単位処理実行部から第2単位処理実行部への変換誤差値が当該装置内部において受け渡されるように構成することができるため、その場合には、それら2つの単位処理実行部による一連の単位処理において、それぞれ、1つの変換誤差値のみが当該画像処理装置に対して入出力されるに過ぎず、その入出力処理が簡素化,単純化されたものとなる。

### [0052]

(34)前記複数の第1前ライン上誤差利用画素が、互いに連続する複数の画素として 設定され、

前記第1単位処理実行部が、前記対応前回ライン処理画素の変換誤差値を前記複数の第1前ライン上誤差利用画素のうちのライン方向において最前に位置する第1前ライン上最前誤差利用画素の変換誤差値として利用して、前記第1対象画素についての単位処理を実行するものとされた(32)項または(33)項に記載の画像処理装置。

#### [0053]

本項に記載の態様は、第1対象画素とそれについての単位処理において利用される誤差 利用画素とのライン方向における位置関係に関する限定を加えた態様である。

#### [0054]

(35)前記第1平均誤差算出部が、

ライン方向に仮想的に配置され、前記複数の第1前ライン上誤差利用画素の各々に対応して設定された重み付け係数の各々と前記第1前ライン上最前誤差利用画素の変換誤差値との乗算処理を実行するところの前記複数の第1前ライン上誤差利用画素の数に相当する数の複数の第1前ライン用乗算部と、

10

20

30

40

20

30

40

50

それら複数の第1前ライン用乗算部の各々に対応して設けられ、それぞれが、自身の直近の後方側に配置されたものが存在する場合にはそのものの記憶値と前記複数の第1前ライン用乗算部のうちの自身に対応するものによる乗算処理の結果値とを加算して記憶し、自身の後方側に配置されたものが存在しない場合には前記複数の第1前ライン用乗算部のうちの自身に対応するものによる乗算処理の結果値を記憶するところの前記複数の第1前ライン上誤差利用画素の数に相当する数の複数の第1前ライン用加算記憶部とを有し、

それら複数の第 1 前ライン用加算記憶部の各々による処理が前方に配置されたものによる処理から順次実行されるように構成されるとともに、それら複数の第 1 前ライン用加算記憶部のうちの最前のものの記憶値に基づいて、前記第 1 平均誤差値を算出するように構成された(34)項に記載の画像処理装置。

[0055]

(36)前記第1平均誤差算出部が、

さらに、前記対象ライン上において前記第1対象画素とライン方向の後方側において連続するように設定された1以上の画素であって前記複数の第1誤差利用画素の一部である1以上の第1当該ライン上誤差利用画素の各々の変換誤差値に基づいて、前記第1平均誤差値を算出するものとされ、

ライン方向に仮想的に配置され、前記1以上の第1当該ライン上誤差利用画素の各々に対応して設定された重み付け係数の各々と前記第1対象画素の直近の後方側に位置する画素の変換誤差値との乗算処理を実行するところの前記1以上の第1当該ライン上誤差利用画素の数に相当する数の1以上の第1当該ライン用乗算部と、

それら1以上の第1当該ライン用乗算部の各々に対応して設けられ、それぞれが、自身の直近の後方側に配置されたものが存在する場合にはそのものの記憶値と前記1以上の第1当該ライン用乗算部のうちの自身に対応するものによる乗算処理の結果値とを加算して記憶し、自身の後方側に配置されたものが存在しない場合には前記1以上の第1当該ライン用乗算部のうちの自身に対応するものによる乗算処理の結果値を記憶するところの前記1以上の第1当該ライン上誤差利用画素の数に相当する数の1以上の第1当該ライン用加算記憶部とを有し、

それら1以上の第1当該ライン用加算記憶部の各々による処理が前方に配置されたものによる処理から順次実行されるように構成されるとともに、さらにそれら1以上の第1当該ライン用加算記憶部のうちの最前のものの記憶値に基づいて、前記第1平均誤差値を算出するように構成された(35)項に記載の画像処理装置。

[0056]

(37)前記第1平均誤差算出部が、前記複数の第1前ライン用加算記憶部のうちの最前のものの記憶値と、前記1以上の第1当該ライン用加算記憶部のうちの最前のものの記憶値との和を、前記第1平均誤差値として算出するように構成された(36)項に記載の画像処理装置。

[0057]

上記3つの項に記載の態様は、前述の特徴的な平均誤差値の算出処理を、第2対象画素についての単位処理と同様、第1対象画素についての単位処理にも適用する各種の態様である。上記3つの項に記載の平均誤差値の算出処理に関する構成は、先に説明した処理に関する構成と同様であるため、ここでの説明は省略する。なお、先に説明した当該処理によるメリットは、第1対象画素についての単位処理に適用された場合のメリットに加え、上記3つの項の態様において重畳的に享受されることとなる。

[0058]

(38)それぞれが前記変換画像の画素のマトリクスにおいて前記第1対象画素の近傍に設定されてその第1対象画素の変換画素値を取得するために自身の変換誤差値が利用される複数の画素を、複数の第1誤差利用画素と定義し、それぞれが前記変換画像の画素のマトリクスにおいて前記第2対象画素の近傍に設定されてその第2対象画素の変換画素値を取得するために自身の変換誤差値が利用される複数の画素を、複数の第2誤差利用画素と定義した場合において、

前記第1単位処理実行部が、前記複数の第1誤差利用画素の平均誤差値である第1平均 誤差値を算出する第1平均誤差算出部を有し、

前記第2単位処理実行部が、前記複数の第2誤差利用画素の平均誤差値である第2平均誤差値を算出する第2平均誤差算出部を有する(21)項ないし(37)項のいずれかに記載の画像処理装置

### [0059]

本項に記載の態様は、先に掲げた第1平均誤差算出部,第2平均誤差算出部を、それぞれ、第1単位処理実行部と第2単位処理実行部とにおいて備えた態様である。

#### [0060]

(39)当該画像処理装置が、

前記第1平均誤差算出部によって算出された前記第1平均誤差値に基づいて前記第1対象画素の原始画素値を補正し、その補正によって得られた画素値に基づいて、その第1対象画素の変換画素値を決定し、かつ、第2平均誤差算出部によって算出された前記第2平均誤差値に基づいて前記第2対象画素の画素値を補正し、その補正によって得られた画素値に基づいて、その第2対象画素の変換画素値を決定する単一の変換画素値決定部を備えた(38)項に記載の画像処理装置。

### [0061]

(40) 当該画像処理装置が、

前記第1平均誤差算出部によって算出された前記第1平均誤差値に基づく前記第1対象画素の原始画素値の補正によって得られた画素値と、その画素値に基づいて取得されたその第1対象画素の変換画素値とに基づいて、その第1対象画素の変換誤差値を算出し、かつ、前記第2平均誤差算出部によって算出された前記第2平均誤差値に基づく前記第2対象画素の画素値の補正によって得られた画素値と、その画素値に基づいて取得されたその第2対象画素の変換画素値とに基づいて、その第2対象画素の変換誤差値を算出する単一の変換誤差値算出部を備えた(37)項または(38)項に記載の画像処理装置。

#### [0062]

上記2つの頃に記載の態様は、第1平均誤差算出部,第2平均誤差算出部を、それぞれ、第1単位処理実行部と第2単位処理実行部とにおいて備えた場合において、それら2つの単位処理実行部が有すべき変換画素値決定部,変換画素値算出部を共用化させた態様である。上記2つの頃の態様は、当該画像処理装置が、電子回路,電気回路を主体として構成される場合において特に有効である。つまり、2つの単位処理部を備えた画像処理装置であっても、上記変換画素値決定部,変換画素値算出部に相当する回路部分を1つとすることができるため、回路構成を簡素化することができるのである。なお、変換画素値決定部,変換画素値算出部の処理については、従来から採用されている種々の処理を採用することができ、その処理は既に公知なものであるため、それらの処理についての説明は省略する。

# [0063]

(51)あるマトリクスとして規定された複数の画素からなる原始画像の画像データを、そのマトリクスのラインの間に画素を補いつつ、誤差拡散法に従う処理によって、そのマトリクスが画素のラインによって補間された別のマトリクスとして規定された複数の画素からなる変換画像の画像データに変換する画像処理方法であって、

前記原始画像の画像データを構成するところのその画像の複数の画素の各々の画素値を、原始画素値と、前記変換画像の画像データを構成するところのその画像の複数の画素の各々の画素値を、変換画素値と、前記原始画像の画素のマトリクスにおける画素のラインであって前記変換画像の画素のマトリクスにおいても存置される画素のラインの各々を、原始ラインと、その原始ラインに対応して前記原始画像の画素のマトリクスを補間するための画素のラインを、補間ラインと、誤差拡散法に従う1つの画素についての処理を単位処理と、それぞれ、定義した場合において、

原始ラインの1つである対象ライン上に存在する1つの画素である第1対象画素についての単位処理を実行することで、その第1対象画素の原始画素値に基づいて、その第1対

10

20

30

40

象画素の変換画素値および変換誤差値を取得し、

その第1単位処理実行部によって今回以前に実行された1の単位処理において前記第1対象画素とされた今回以前第1対象画素の原始画素値を、前記対象ラインに対応する補間ライン上において前記第1対象画素と対応付けられた第2対象画素の画素値として、その画素値に基づき、前記第1単位処理実行部によって取得された前記第1対象画素の変換誤差値を利用しつつ、前記第2対象画素についての単位処理を実行することで、その第2対象画素の変換画素値を取得し、

前記第1対象画素および前記第2対象画素をライン方向の前方に向かって順次遷移させつつ、前記第1対象画素についての単位処理と前記第2対象画素についての単位処理とをそれぞれ前記対象ラインと前記補間ラインとについて繰り返し、かつ、その繰り返しを、対象ラインを順次遷移させつつ繰り返すことによって、前記原始画像の画像データを前記変換画像の画像データに変換する画像処理方法。

[0064]

本項に記載の態様は、カテゴリを画像処理方法とした場合の請求可能発明の態様である。本項の態様の説明は、画像処理装置のカテゴリに属する上記態様と重複するため、ここでの説明は省略する。なお、明細書が冗長となることに配慮して具体的な構成の例示は省略するが、請求可能発明の画像処理方法は、画像処理装置に関する上記各態様における技術的特徴を本項の態様に適用した各種構成の態様のものとすることができる。

【実施例】

[0065]

以下、請求可能発明の一実施例およびそれの変形例を、電子回路によって構成された画像処理装置を例にとって、図を参照しつつ詳しく説明する。なお、請求可能発明は、下記実施例の他、前記〔発明の態様〕の項に記載された態様を始めとして、当業者の知識に基づいて種々の変更、改良を施した種々の態様で実施することができる。

[0066]

画像処理の概要

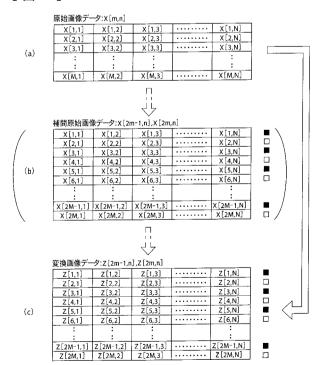

本実施例の画像処理装置によって変換の対象となる原始画像は、図1(a)に示すように、コラム方向の画素数(ライン数)がM,ライン方向の画素数(コラム数)がNのマトリクスとして規定されている。ライン,コラム,画素は、一般化して、mライン,nコラムと呼ぶこととし、画素は、mライン,nコラムに対応して[m,n]と表し、画素値、つまり、原始画素値は、X、あるいは、画素の位置に対応付けてX[m,n]として表すこととする。原始画素値Xは、0~255の1刻みの離散的な階調値とされている。原始画像の画像データは、原始画素値X[m,n]の集合として構成される。

[0067]

一方、変換された後の変換画像は、図1(c)に示すように、コラム方向の画素数が2M,ライン方向の画素数がNのマトリクスとして規定されている。つまり、変換画像のマトリクスは、ライン数が、原始画像の2倍であり、変換画像は、原始画素に存在するラインである原始ラインの間を1の補間ラインによって補間されたものとされる。変換画像のラインを、一般化して、2m・1ライン、2mラインと呼ぶこととすれば、2m・1ラインは、上記原始ラインであり、2mラインは、2m・1に対応して補われた補間ラインは、上記原始ラインに の印を、補間ラインに の印を付している。コラム呼び、画素は、原始ライン上のものを[2m・1,n]は、原始画像と同様に、nコラム呼び、画素は、原始ライン上のものを[2m・1,n]は、こあるいは、画素に対応付けて、原始ライン上の画素のものをZ[2m・1,n]、補間ライン上の画素のものをZ[2m,n]と呼ぶこととする。変換画素値Zは、0,1の1位化値である。変換画像の画像データは、変換画素値Z[2m・1,n],Z[2m,n]の集合として構成される。

[0068]

誤差拡散法に従う処理(以下、「誤差拡散処理」という場合がある)による上記原始画像データから上記変換画像データへの変換は、従来、原始画像データを、一旦、図1(b

10

20

30

40

)に示すような補間原始画像の画像データを作成し、その画像データに対して誤差拡散処理を実行するようにして行われている。補間原始画像データは、単に、原始ラインの間に補間ラインを補った画像の画像データである。詳しく言えば、2mライン上の原始画素値Xの各々が2m-1ライン上の同じコラムの画素値となるように作成したものである。したがって、[2m-1,n]と[2m,n]とが同じ値となる原始画素値の集合として構成される。

#### [0069]

本実施例の画像処理装置による画像処理(以下、「本実施例の画像処理」という場合がある)では、上記補間原始画像データを作成せず、上記原始画像データから、直に、上記変換画像データに変換される。つまり、画素のラインによる画像の補間と、誤差拡散法に従う原始画素値の変換画像値への変換処理とが、渾然一体として実行されるのである。以下に、本実施例の画像処理を、図2に示すテーブルを参照しつつ、説明する。

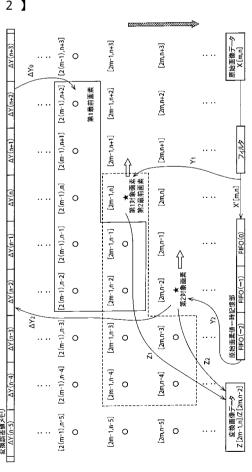

#### [0070]

図 2 における画素の並びは、変換画像のマトリクスを示している。中段に示されている 2 m - 1 ラインは、原始画像のmラインに相当する原始ラインであり、下段に示されている 2 m ラインは、 2 m - 1 ラインに対応して、原始画像のmラインとm + 1 ラインとの間に補われるラインである。上段のラインは、原始画像のm - 1 ラインに対応して補間されて既に変換画素値 Z が取得されたラインである。なお、図における は、その画素において既に変換画素値 Z が取得されていることを示している。

### [0071]

本実施例の画像処理では、原始ラインの1つのラインを対象ラインとして、その対象ライン上の1つの画素についての単位処理(第1単位処理)、詳しく言えば、その画素る原始画素値に変換することを主体とする処理と、その対象ライン方で実行言されるの当なが実行されることによって、原始画像の1つの画素についての単位処理(第2単位処理)とが、1セットで実行言れるの第1単位処理と、補間ライン上において画素値の変換の対象となる第2対象画素に対する第2単位処理とが実行されることによって、原始画像の1つの画素の原始画のの方が出力されるので表して、第1対象画素および第2対象画素は、図において、 印を付して表している。そして、第1対象画素および第2対象画素がそれぞれライン方向(画素のラインにるの方の当位のである1ラインについてのすべての単位処理である1ライン処理が実行され、その1ラインに対理が、対象ラインが遷移させられつつ(図に示すら対変換画像データに変換されるのである。

### [0072]

以下に、図における2m-1ラインを対象ラインと、2mラインを補間ラインとし、画素[2m-1,n]を第1対象画素と、画素[2m,n-2]を第2対象画素とした場合の第1単位処理,第2単位処理について説明する。

#### [0073]

画素 [2 m - 1 , n]を第1対象画素とした第1単位処理では、本画像処理装置に入力された原始画素における画素値 X [ m , n ](実際は、フィルタ処理後の原始画素値 X ' [ m , n ] であり、それは、原始画素値 X と同様、0 ~ 2 5 5 の階調値とされている)が、第1対象画素の画素値(第1対象画素値) Y 1 とされ、その第1対象画素値 Y 1 に対する変換画像値(第1変換画素値) Z 1 が取得される。その取得に際しては、第1対象画素の近傍において既に変換画素値 Z への変換が行われた画素、つまり、第1対象画素に対応する誤差利用画素の変換誤差値 Y の平均値である平均誤差値(第1平均誤差値) Y A V E 1 が利用される。詳しく言えば、第1対象画素値 Y 1 と第1平均誤差値 Y A V E 1 とを加算することで、第1対象画素値 Y 1 が補正された補正後対象画素値(第1補正後対象画素値) Y 1 が求められ、その第1補正後対象画素値 Y 1 と 2 値化閾値 S とが比較され、補

10

20

30

30

40

50

正後対象画素値  $Y_1$  'が 2 値化閾値 S より大きい場合には第 1 変換画素値  $Z_1$ が 1 に、補正後対象画素値  $Y_1$  'が 2 値化閾値 S 以下である場合には第 1 変換画素値  $Z_1$ が 0 に、それぞれ決定される。このようにして決定された第 1 変換画素値  $Z_1$ は、変換画像における変換画素値  $Z_1$   $Z_1$   $Z_2$   $Z_3$   $Z_4$   $Z_4$   $Z_5$   $Z_5$

#### [0074]

第 1 平均誤差値 Y A V F . 1 の算出のために、第 1 対象画素に対して、図に実線で囲った 範囲において、誤差利用画素(第1誤差利用画素)が設定される。詳しく言えば、対象ラ インである2m・1ラインを当該ライン(第1当該ライン)とし、前回の1ライン処理に おける補間ラインである2(m・1)ラインを前ライン(第1前ライン)とした場合にお い て 、 第 1 前 ラ イ ン 上 に 、 第 1 対 象 画 素 の コ ラ ム と 同 じ n コ ラ ム を 中 心 に 連 続 的 に 位 置 す る 5 つの画素 [ 2 ( m - 1 ) , n - 2 ] ~ [ 2 ( m - 1 ) , n + 2 ] が、前ライン上誤差 利用画素(第1前ライン上誤差利用画素)として、また、第1当該ライン上に、第1対象 画素のライン方向における後方側に位置してそれと連続する 2 つの画素 [ 2 m - 1 , n -2],[2m-1,n-1]が、当該ライン上誤差利用画素(第1当該ライン上誤差利用 画素)として、それぞれ設定されることになる。ちなみに、誤差利用画素の各々に対して は、図3に示すように、対象画素との相対位置に応じた重み付け係数Kが設定されている 。詳しく言えば、例えば、前ライン誤差利用画素に対しては、ライン方向の後方のものか ら前方のものにかけて、それぞれ、Ka=1/16,Kb=1/16,Kc=4/16, K d = 1 / 1 6 , K e = 1 / 1 6 という値の係数が、当該ライン誤差利用画素に対しては 、ライン方向の後方のものから前方のものにかけて、Kf=4/16,Kg=4/16と いう値の係数が設定されており(Ka゠1/16,Kb=2/16,Kc=4/16,K d = 2 / 1 6 , K e = 1 / 1 6 , K f = 2 / 1 6 , K g = 4 / 1 6 という値等を採用する ことも可能である)、そして、それらの重み付け係数 K と第 1 誤差利用画素の各々の変換 誤差値 Yとが掛け合わされてそれら掛け合わされたものが合計された値として、第1平 均誤差値 Yдүғ. 」が算出される。このようにして算出された第1平均誤差値 Yдүғ. 」 が、先に説明した第1変換画素値Zィの決定において利用されるのである。なお、本実施 例の画像処理では、後に詳しく説明するが、第 1 平均誤差値 Y<sub>AVE.1</sub>の算出にあたって 、 第 1 前 ラ イ ン 誤 差 利 用 画 素 の う ち 、 ラ イ ン 方 向 に お け る 最 も 前 方 の 画 素 で あ る 前 ラ イ ン 上最前誤差利用画素(第1前ライン上最前誤差利用画素:図では「第1最前画素」と表さ れている)は、前回の1ライン処理での1の単位処理において第2対象画素とされた1つ の画素であり、第1対象画素と対応付けられた画素(対応前回ライン処理画素)とされて おり、その画素の変換誤差値 Y、つまり、本第1単位処理では画素 [2 ( m - 1 ) , n +2]の変換誤差値 Y[2(m-1),n+2]のみが、外部から本画像処理装置に入 力され(以下、この変換誤差値を「入力変換誤差値 Y。」という場合がある)、他の誤 差利用画素の変換誤差値 Yは、今回の単位処理では、外部から入力されない。

### [0075]

また、第1単位処理では、上記第1補正後対象画素値  $Y_1$  ' と第1変換画素値  $Z_1$  とに基づいて、第1対象画素についての変換誤差値(第1変換誤差値)  $Y_1$ も取得される。詳しく言えば、変換画素値  $Z_1$ が1である場合には、第1補正後対象画素値  $Y_1$  ' から上限画素値  $Y_{MAX}$  (例えば、255、あるいはそれ以下の何らかの値)を減じた値が、変換画素値  $Z_1$ が0である場合には、第1補正後対象画素値  $Y_1$  ' から下限画素値  $Y_{MIN}$  (例えば、0)を減じた値が、それぞれ、第1変換誤差値  $Y_1$  とされる。

### [0076]

補間ライン上の画素 [2 m, n - 2]を第2対象画素とした第2単位処理では、後に説明する理由から、前々回の単位処理において入力された原始画素値 X [m, n]、つまり、前々回の第1単位処理での第1対象画素の原始画素値が、第2対象画素の画素値(第2対象画素値) $Y_2$ とされ、その第2対象画素値  $Y_2$ に対する変換画像値(第2変換画素値) $Z_2$ が取得される。その取得に際しては、第1対象画素の場合と同様、第2対象画素に対応する誤差利用画素の平均誤差値(第2平均誤差値)  $Y_{AVE}$ .  $Z_2$  が利用され、第2対象画素値  $Z_2$  と第2平均誤差値  $Z_2$  をが加算されることで第2対象画素値  $Z_2$  が補正さ

れた補正後対象画素値(第 2 補正後対象画素値)  $Y_2$ 'が求められ、その第 2 補正後対象画素値  $Y_2$ 'と 2 値化閾値 S とが比較されて、第 2 変換画素値  $Z_1$ が決定される。このようにして決定された第 2 変換画素値  $Z_2$ は、変換画像における変換画素値  $Z_2$   $Z_3$   $Z_4$   $Z_5$   $Z_$

### [0077]

第2平均誤差値 Y<sub>AVE・1</sub>の算出のための誤差利用画素(第2誤差利用画素)は、図に破線で囲った範囲において、第2対象画素に対して、第1誤差利用画素の第1対象画素に対する位置関係と等しい位置関係となるように設定される。具体的には、補間ラインである2mラインを当該ライン(第2当該ライン)とし、対象ラインである2m・1ラインを前ライン(第2前ライン)とした場合において、第2前ライン上に、画素[2m・1,n・4]~[2m・1,n]が、前ライン上誤差利用画素(第2前ライン上誤差利用画素(第2前ライン上に、第2対象画素のライン方向における後方側に位置として、また、第2当該ライン上に、第2対象画素のライン方向における後方側に位置とでそれと連続する2つの画素[2m,n・4],[2m,n・3]が、当該ライン上誤差利用画素(第2当該ライン上誤差利用画素)として、それぞれ設定されることになる。また、それらの誤差利用画素の各々に対する重み付け係数Kは、第1単位処理における場合と同様、図3に示すように設定されており、第1単位処理の場合と同様の処理によって、第2平均誤差値 Y<sub>AVE・2</sub>が算出される。

#### [0078]

本第2単位処理では、第2前ライン誤差利用画素のうち、ライン方向における最も前方 の画素である前ライン上最前誤差利用画素(第2前ライン上最前誤差利用画素:図では、 「第2最前画素」と表されている)は、画素[2m-1,n]であり、それは、すなわち 、 今 回 の 第 1 単 位 処 理 に お け る 第 1 対 象 画 素 と さ れ て い る 。 し た が っ て 、 こ の 第 2 前 ラ イ ン上最前誤差利用画素の変換誤差値 Yには、第1単位処理によって取得された第1変換 誤差値 Y╷が、そのまま、詳しく言えば、当該画像処理装置から出力されることなく利 用される。本実施例の画像処理では、このような利用が可能なように、第1対象画素と第 2 対象画素とのライン方向における相対位置関係が設定され、第2単位処理は、第1単位 処理に対して、コラム数において2つ遅れた画素の単位処理を行うようにされているので ある。したがって、第1対象画素値とされた上記原始画素値X'[m,n]は、当該画像 処理装置内において、その画素値が次に第2対象画素値とされるまで、一時的にではある が記憶される。また、第2単位処理においても、第1単位処理の場合と同様の処理によっ て、第2対象画素についての変換誤差値(第2変換誤差値) Yゥが取得される。この取 得された第2変換誤差値 Y₂は、画像処理装置から出力され、当該装置外に設けられた メモリに記憶され、当該1ライン処理の次の1ライン処理において、先に説明した対応前 回ライン処理画素の画素値として利用される。

# [0079]

以上、画像処理の概要について説明したが、上記説明において使用された種々の値等については、第1単位処理,第2単位処理に対応して、「第1」,「第2」という区別をつけ、また、符号に添え字1,2を付している。以下の説明においては、「第1」,「第2」を表記しない総称を使用する場合もあることとし、また、その場合には、符号の添え字を付さない場合もあることとする。

# [ 0 0 8 0 ]

#### 画像処理装置の構成

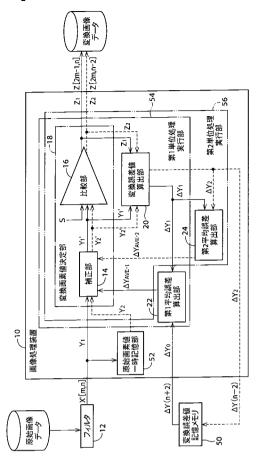

本実施例の画像処理装置10は、ラインスキャナとインクジェットプリンタとが複合した複合機内に組み込まれており、図4にブロック図で示すような構成とされている。原始画像データは、ラインスキャナで読み取られつつある原始画像データが、当該画像処理装置外に設けられたフィルタ12によって平滑化等のフィルタ処理が施されつつ、1つの原始画素値(詳しくは、フィルタ処理後原始画素値) X ' [m,n]ごとに、順次、画像処理装置10に入力される。この原始画素値 X ' [m,n]は、対象画素値 Y として扱われる。

# [0081]

20

30

画像処理装置10は、補正部14と比較部16とを含んで構成されて対象画素値Yに対する変換画素値Zを決定する変換画素値決定部18を有している。補正部14は、加算器を主体に構成されており、この補正部14によって、対象画素値Yと平均誤差値 Yavㅌ 対象画素値とが加算されることで、対象画素値Yが平均誤差値 Yavㅌ によって補正された補正後対象画素置Y,を得るようにされている。比較部16は、比較器を主体に構成されており、補正後対象画素置Y,と2値化閾値Sとを比較することによって対象画素についての2値化された変換画素値Zを得るようにされている。また、画像処理装置10は、補正後対象画素値Y,と変換画素値Zとに基づいて、対象画素の変換誤差値 Yを算出する変換誤差値 Yを算出する変換誤差値 Yを算出する変換誤差値 Yを算出する2つの平均誤差算出部を有している。詳しく言えば、それらの1つは、第1単位処理において、外部からの入力変換誤差値 Y。に基づいて第1平均誤差値 Y。とす。第1単位処理において、外部からの入力変換誤差値 Y。に基づいて第1平均誤差値 Y。以下第1平均誤差値 Y。以下第1平均誤差値 Y。以下:1を算出する第1平均誤差算出部22であり、もう1つは、第2単位処理において第2平均誤差値 Y。以下:2を算出する第2平均誤差値 Y。以下:1を算出する第1平均誤差算出部22であり、もの1つは、第2単位処理において第2平均誤差値 Y。以下:2を算出する第2平均誤差算出部24である。

#### [0082]

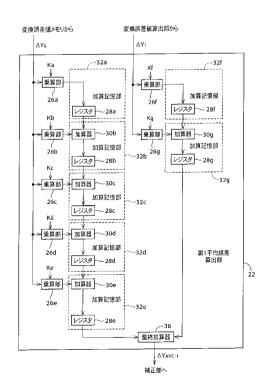

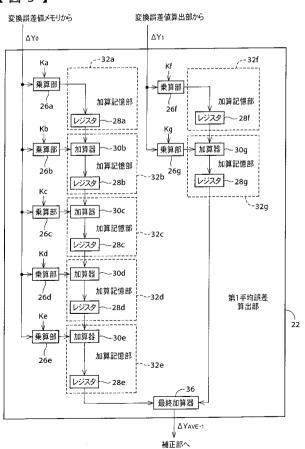

上記2つの平均誤差算出部をさらに詳しく説明すれば、第1平均誤差算出部22は、図5にブロック図で示すように、それぞれが乗算器を主体とした7つの乗算部26a~26gと、それぞれがレジスタ28a~28gと加算器30b~30e,30gとを主体とした7つの加算記憶部32a~32g(加算記憶部32a,32fにはレジスタは設けられていない)と、最終加算器36とを含んで構成されている。

### [0083]

乗算部26a~26eと加算記憶部32a~32eとは、それぞれが1対1に対応しており、また、それらは、第1平均誤差値 Y<sub>AVE・1</sub>の算出処理における5つの第1前ライン誤差利用画素の各々に、詳しく言えば、それらの添え字a~eの順に、ライン方向の前方に向かって第1前ライン誤差利用画素の各々に対応している。このことにより、乗算部26a~26eと加算記憶部32a~32eとは、ライン方向に仮想的に配置されたものとなっている。つまり、図における上方が、ライン方向の後方に,下方が、ライン方向における前方に対応するものとなっている。

# [0084]

# [ 0 0 8 5 ]

# [0086]

50

20

30

30

40

50

上記のような構成から、乗算部26f,26g、加算記憶部32f,32gは、それぞれ、当該ライン用乗算部(第1当該ライン用乗算部),当該ライン用加算記憶部(第1当該ライン用加算記憶部(第1当該ライン用加算記憶部)として機能する。詳しく言えば、乗算部26f,26gは、それぞれ、変換誤差値算出部20によって算出された今回の第1対象画素の変換誤差値である第1変換誤差値 Y₁を、第1当該ライン上の次回の第1単位処理における第1対象画素の直ぐ後方側の画素の変換誤差値 Yとして、それと重み付け係数Kf,Kgの各々との乗算処理を行うようにされている。また、加算記憶部32gは、自身に対応する乗算部26gの乗算処理の結果値と、自身の直近の後方側(図における上方側)の加算記憶部32gのレジスタ28fに記憶されている記憶値とを自身の加算器30gによって加算し、その加算値を、自身のレジスタ28gに記憶するようにされており、加算記憶部32fは、自身に対応する乗算部26fの乗算処理の結果値を、自身のレジスタ28fに記憶するようにされている。

#### [0087]

そして、第1平均誤差算出部22は、加算記憶部32eのレジスタ28eの値と、加算記憶部32gのレジスタ28gの値とが、最終加算器36によって加算されるように構成されており、また、加算記憶部32e,加算記憶部32f,32gは、それぞれ、前方に配置されたものによる処理から順次実行されるようにされている。つまり、図における下方に位置するものから上方に位置するものに向かって順次処理が行われる。に詳しく説明すれば、この第1平均誤差算出部22の処理は、まず、乗算部26e,加算記憶部32eによる処理と、それに続く最終加算器36によず、乗算部26e,加算記憶部32eによる処理と、それに続く最終加算器36による処理が実行されて、今回の第1対象画素に対する第1誤差利用画素の第1平均誤差値 YAVE.1が算出された その後に、乗算部26a~26d、加算記憶部32a~32dによる処理および乗算部26f,26g、加算記憶部32f,32gによる処理が、前の処理は、次の回の第1単位処理における第1平均誤差値 YAVE.1が算出された 後の処理は、次の回の第1単位処理における第1平均誤差値 YAVE.1の算出のための準備処理として実行されることになる。

### [0088]

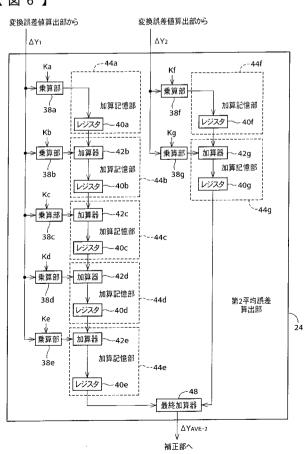

第2平均誤差算出部24は、図6にブロック図で示すように、それぞれが乗算器を主体とした7つの乗算部38a~38gと、それぞれがレジスタ40a~40gと加算器42b~42e,42gとを主体とした7つの加算記憶部44a~44g(加算記憶部44a,44fにはレジスタは設けられていない)と、最終加算器48とを含んで構成されている。

#### [0089]

上記構成は、第1平均誤差算出部22と同様であるため、説明を簡単に行なえば、乗算 部 3 8 a ~ 3 8 e ,加算記憶部 4 4 a ~ 4 4 e は、それぞれ、第 2 平均誤差値 Y <sub>A V F</sub> . っ の算出処理における5つの第2前ライン誤差利用画素の各々に対応し、前ライン用乗算部 ( 第 2 前 ラ イ ン 用 乗 算 部 ) , 前 ラ イ ン 用 加 算 記 憶 部 ( 第 2 前 ラ イ ン 用 加 算 記 憶 部 ) と し て 機 能 す る 。 ま た 、 乗 算 部 3 8 f , 3 8 g , 加 算 記 憶 部 4 4 f , 4 4 g は 、 それ ぞ れ 、 2 つ の第2当該ライン誤差利用画素の各々に対応し、当該ライン用乗算部(第2当該ライン用 乗算部),当該ライン用加算記憶部(第2当該ライン用加算記憶部)として機能する。な お、第2平均誤差値算出部24では、乗算部38a~38eは、それぞれ、変換誤差値算 出部20によって算出された今回の第1単位処理における第1対象画素の変換誤差値であ る第 1 変換誤差値 Y₁を、第 2 前ライン上最前誤差利用画素の変換誤差値として、それ と重み付け係数Ka~Keの各々との乗算処理を行うようにされている。また、乗算部3 8 f , 3 8 g は、それぞれ、変換誤差値算出部 2 0 によって算出された今回の第 2 対象画 素 の 変 換 誤 差 値 で あ る 第 2 変 換 誤 差 値 Y ₂ を 、 第 2 当 該 ラ イ ン 上 の 次 回 の 第 2 単 位 処 理 における第 2 対象画素の直ぐ後方側の画素の変換誤差値 Yとして、それと重み付け係数 K f , K g の各々との乗算処理を行うようにされている。そして、第 1 変換誤差算出部 2 4 と同様の順に処理がなされて、今回の第 2 対象画素に対する第 2 誤差利用画素の第 2 平 均誤差値 ΥΑΥΕ. 2が算出され、次の回の第2単位処理における第2平均誤差値 ΥΑΥΕ

. っの算出のための準備処理が行われる。

### [0090]

ここで、当該画像処理装置10の外部に設けられている変換誤差値記憶メモリ50は、図2に示すように、概ね1ライン上の画素数に相当する記憶領域を備えたラインメモリとされており(実際は、第1対象画素と第2対象画素とのライン方向の位置関係に依拠して、ライン方向における前方,後方のそれぞれに2画素分ずつ余分に記憶領域が設けられている)、図に示すように、それぞれの領域に、コラムに対応した変換誤差値・・・, Y(n・1), Y(n), Y(n+1),・・・が記憶されている。第2単位処理の実行ごとに、第2変換誤差値 Y₂が、第2対象画素のコラムに対応する記憶領域に記憶され、また、第1単位処理ごとに、第1対象画素に対応付けられた対応前回ライン処理画素、すなわち、第1前ライン上最前誤差利用画素のコラムに対応する記憶領域から読み出た。この変換誤差値記憶メモリ50は、画像処理装置10内に設けられるものであってもよく、そのように構成すれば、当該画像処理装置10と外部との画素値の入出力処理をより簡素化することが可能である。

#### [0091]

また、画像処理装置10は、原始画素値一時記憶部52を備えている。この一時記憶部52は、図2に示すように、3つの記憶領域FIFO(0)~FIFO(-2)を有する先入れ先出しレジスタを主体に構成されており、その記憶領域の記憶値は、記憶領域FIFO(0)~FIFO(-2)を順次移動させられるようになっている。このような構成により、今回の単位処理において原始画素値一時記憶部52に入力された原始画素値X  $^{\prime}$  [ m , n ] は、次々回の単位処理において、第2対象画素値 $Y_2$ として利用される。

#### [0092]

以上のような構成から、画像処理装置10は、変換画素値決定部18,変換誤差値決定部20,第1平均誤差算出部22を含んで構成される第1単位処理実行部54を備え、変換画素値決定部18,変換誤差値決定部20,第2平均誤差算出部24を含んで構成される第2単位処理実行部56を備えるものとなっている。つまり、上記変換画素値決定部18,変換誤差値決定部20は、第1単位処理実行部54,第2単位処理実行部56が共用する機能部とされ、第1単位処理における一部の処理と第2単位処理における一部の処理とを、交互に行うようにされているのである。

#### [0093]

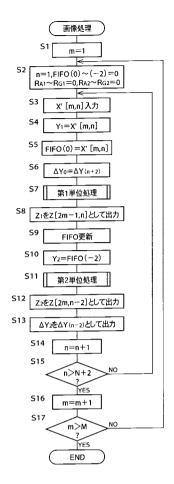

画像処理のフロー

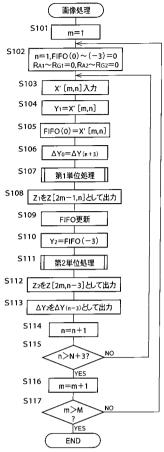

図7に、画像処理装置10による上述の画像処理のフローチャートを示す。以下に、そのフローチャートを基に、本画像処理の流れを、時間の進行に沿って説明する。なお、画像処理装置10は電子回路を主体として構成されたものであることから、2以上の処理が並行して実行され、実際には、本画像処理装置10画像処理のプロセスは、厳密な意味において、このフローチャートに従うものとはならない。ここで説明する処理の流れは、あくまでも、本画像処理の理解を容易にするための目安である。

### [0094]

本画像処理では、まず、ステップ1(以下、「S1」と略す。他のステップも同様である。)において、ラインカウンタとして機能するmの値が1にリセットされる。続く、S2において、コラムカウンタとして機能するnの値が1にリセットされるとともに、原始画素値一時記憶部52の記憶領域FIFO(0)~FIFO(-2)の各々の値、第1平均誤差算出部22が有するレジスタ28a~28gのレジスタ値RД1~RG1、第2平均誤差算出部24が有するレジスタ40a~40gのレジスタ値RД2~RG2が、それぞれ0にリセットされる。なお、変換誤差値記憶メモリ50は、本画像処理が開始される時点で、記憶領域がすべて0にリセットされている。

#### [0095]

次に、S3において、原始画像のフィルタ処理後の原始画素値 X′[m,n]が、画像処理装置 10に入力される。続いて、その原始画素値 X′[m,n]が、S4において、第1対象画素値 Y<sub>1</sub>として認定され、S5において、原始画素値一時記憶部 52の記憶領

20

30

40

域 F I F O ( 0 ) に記憶される。次に、 S 6 において、変換誤差値記憶メモリ 5 0 の n + 2 コラムに対応する記憶領域の記憶値 Y ( n + 2 ) が、入力変換誤差値 Y  $_0$ として、入力される。

#### [0096]

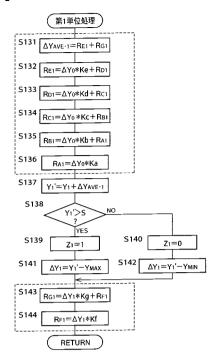

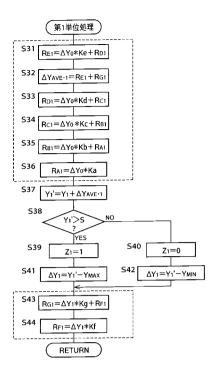

次に、S7において、図8にフローチャートを示す第1単位処理が実行される。第1単 位処理では、まず、S31において、乗算部26eによって、入力変換誤差値 Y<sub>0</sub>と重 み付け係数 K e とが掛け合わされ、その掛け合わされたものとレジスタ 2 8 d の記憶値と が、加算記憶部32eの加算器30eによって加算され、その加算されたものが、レジス タ 2 8 e のレジスタ値 R ғ ₁ とされる。続くS32において、レジスタ28 e のレジスタ値 R ӻ ₁ と、レジスタ 2 8 g のレジスタ値 R ց ₁ とが、最終加算器 3 6 によって加算されて、第 1 平均誤差値 Y<sub>AVF</sub>. 1 が算出される。次いで、S33~S35おいて、前方側から(図 におけるより下方に位置するものから)順に、乗算部26d~26bによって、入力変換 誤差値 Y。と重み付け係数Kd~Kbの各々とが掛け合わされ、その掛け合わされたも のとレジスタ28c~28aの記憶値の各々が、加算記憶部32d~32bの加算器30 d ~ 3 0 b によって加算され、その加算されたものの各々が、レジスタ 2 8 d ~ 2 8 b の レジスタ値Rը1~Rც1とされる。そして、S36において、乗算部26aによって、入力 変換誤差値 Y ₀と重み付け係数Kaとが掛け合わされ、その掛け合わされたものが、レ ジスタ 2 8 a の レ ジ ス タ 値 R 🛕 1 と さ れ る 。 そ れ ら S 3 1 ~ S 3 6 の 処 理 は 、 第 1 変 換 誤 差 算出部22によって行われる(フローチャートにおいて、破線で囲んだステップが第1変 換誤差算出部22によって行われるステップである)。

#### [0097]

### [0098]

次に、S43において、乗算部 26gによって、算出された第1変換誤差値  $Y_1$ と重み付け係数 Kgとが掛け合わされ、その掛け合わされたものとレジスタ 28 f の記憶値とが、加算記憶部 44gの加算器 42gによって加算され、その加算されたものが、レジスタ 28gのレジスタ値  $R_{G1}$ とされる。そして、S44において、乗算部 26 f によって、第1変換誤差値  $Y_1$ と重み付け係数 K f とが掛け合わされ、その掛け合わされたものがレジスタ 28 f のレジスタ値  $R_{F1}$ とされる。それら S43、S44の処理は、第1変換誤差算出部 22によって行われ、それらの処理が終了して、第1単位処理が終了する。

#### [0099]

S7の第1単位処理の後、S8において、決定された第1変換画素値 $Z_1$ が、変換画像における原始ライン上の画素 [2m-1,n]の変換画素値 $Z_2m-1,n]$ として出力される。次に、S9において、原始画素値一時記憶部S2の更新処理がなされる。具体的には、記憶領域FIFO(-2)の値が、FIFO(-1)の値とされ、続いて、FIFO(-1)の値がFIFO(0)の値とされる。そして、S10において、記憶領域FIFO(-2)の値が、第2対象画素値 $Y_2$ とされる。このS10の処理の後、S11において、図9にフローチャートを示す第2単位処理が実行される。

# [0100]

50

40

20

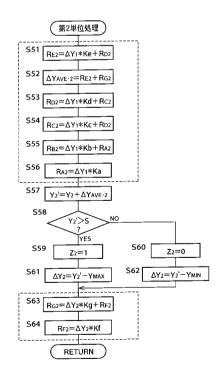

第2単位処理におけるS51~S64の各々は、第1単位処理におけるS31~S44の各々と略同様であるため、それらの説明は簡単なものに留める。相違点は、第1単位処理において第1平均誤差算出部22において行われた処理(破線で囲んだ処理)が、第2平均誤差算出部24によって行われること、また、その処理において、入力変換誤差値  $Y_0$ に代えて、第1単位処理において算出された第1変換誤差値  $Y_1$ が、乗算部38a~38gによって、それぞれ重み付け係数Ka~Kgと掛け合わされること等である。この第2単位処理における第2平均誤差算出部24の処理によって第2平均誤差値  $Y_{AVE.2}$ が算出され、第2単位処理においては、その第2平均誤差値  $Y_{AVE.2}$ に基づいて、第2変換画素値Z $_2$ が決定され、第2変換誤差値  $Y_2$ が算出されることになる。

#### [0101]

第2単位処理の後、S12において、決定された第2変換画素値 $Z_2$ が、変換画像における補間ライン上の画素 [2 m, n-2]の変換画素値Z[2 m, n-2]として出力され、S13において、算出された第2変換誤差値  $Y_2$ が、変換誤差値記憶メモリS0の第2対象画素のコラムに対応する記憶領域に、その記憶領域において記憶されるべき記憶値Y(n-2)として出力される。

#### [0102]

次に、S14において、nの値がカウントアップされ、続くS15において、nの値が、原始画像のコラム総数Nに2を加えた値より大きいか否かが判断される。その値以下の場合には、S3以降の処理が繰り返される。その値より大きい場合は、1ライン処理が完了したものとして、S16において、mの値がカウントアップされ、次の対象ラインについての1ライン処理に移行する。そして、S17において、mの値が原始画像のコラム総数Nをより大きいか否かが判断され、N以下である場合には、S2以降の処理が繰り返され、Nより大きい場合は、すべての1ライン処理が完了したものとして、画像処理が終了する。

### [0103]

なお、以上の処理においては、 n が 0 以下の場合の第 2 単位処理、 n が N より大きい場合における第 1 単位処理も存在する。それらの処理は、原始画像のマトリクスをはみ出す第 2 対象画素,第 1 対象画素についての処理となるため、ダミー的に行われる。

# [0104]

また、上記画像処理は、電子回路によって構成される画像処理について説明したが、当該画像処理を、コンピュータを主体とする画像処理装置で行う場合には、上記フローチャートに従うプログラムを作成し、そのプログラムをコンピュータが実行させればよい。その場合は、画像処理装置10において実体を有して存在した各機能部は、その機能部が行っていた処理を実行する仮想的、あるいは、概念的な機能部となる。

# [0105]

### 变形例

以下に、第1平均誤差算出部22,第2平均誤差算出部24における処理の順序を入れ替えた変形例について説明する。なお、変形例の画像処理装置についても、画像処理装置10と呼ぶこととし、それが備える各機能部についても、同じ符号を用いることとする。

### [0106]

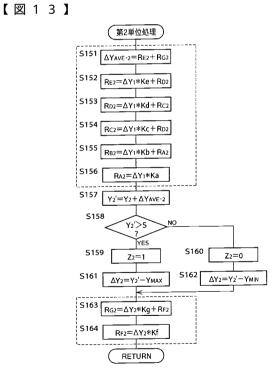

変形例の画像処理装置10における第1平均誤差算出部22,第2平均誤差算出部24では、図12,図13にフローチャートを示すような順に、平均誤差値の算出処理が行われる。具体的には、図8におけるS31とS32とを、また、図9におけるS51とS52とを入れ替えただけである。図5,図6を参照しつつ説明すれば、まず、最終加算器36,48による加算処理が実行された後、乗算部38,40、加算記憶部32,44による処理が、ライン方向における前方側のもの(図における下方に位置するもの)から順次行われる。このような順序で処理が実行される場合、算出される第1平均誤差値 YAVE 1、第2平均誤差値 YAVE 2は、今回の単位処理における第1対象画素,第2対象画素に対する第1誤差利用画素,第2誤差利用画素のものであるが、第1平均誤差算出部22に入力される入力変換誤差値 Yo,第2平均誤差算出部24に入力される第1変換誤

10

20

30

30

40

50

差値 Y1は、次回の単位処理における第 1 対象画素,第 2 対象画素に対応する第 1 前ライン上最前誤差利用画素,第 2 前ライン上最前誤差利用画素の変換誤差値 Yとなる。つまり、乗算部 3 8 , 4 0 、加算記憶部 3 2 , 4 4 の各々による処理は、いずれも、次回の単位処理において第 1 平均誤差値 YAVE . 1 , 第 2 平均誤差値 YAVE . 2 を算出するための準備処理となる。

[0107]

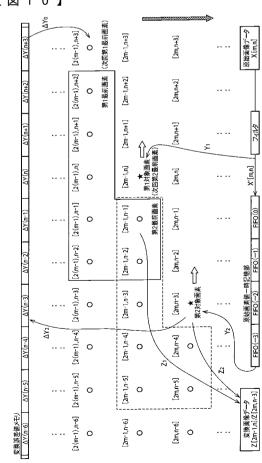

上記のことから、本画像処理においては、第1対象画素を[2m‐1,n]とする場合、図10に示すように、変換誤差値記憶メモリ50から入力される入力変換誤差値 Y。は、次回の第1単位処理における第1対象画素についての第1前ライン上最前誤差利用画素(図では、「次回第1最前画素」と表されている)に対応する記憶領域に記憶されている記憶値 Y(n+3)となる。また、今回の第1単位処理において算出される変換誤差値 Y<sub>1</sub>が、次回の第2単位処理における第2対象画素についての第2前ライン上最前誤差利用画素(図では、「次回第2最前画素」と表されている)となるように、第2対象画素が、第1対象画素に対して、ライン方向において3つ後方の画素とされる。

[0108]

上記第1対象画素と第2対象画素との位置関係により、第2単位処理によって算出された第2変換誤差値  $Y_2$ は、変換誤差値記憶メモリ50の第2対象画素のコラムに相当するコラムの記憶領域に記憶されるべき記憶値 Y(n-3)とされ、また、原始画像値一時記憶部52の記憶領域は、FIFO(0)~FIFO(3)と、1つ拡張されている。そして、本変形例の画像処理では、1つの原始画素値 $X^*$ [m,n]についての単位処理によって、2つの変換画素値Z[2m-1,n],Z[2m,n-3]が得られることになる。なお、本画像処理のメインフローは、先に説明した画像処理との相違によって、図11に示すものとなる。このフローは、先のフローと略同様であるため、ここでの説明は省略する。また、画像処理装置10の全体構成も図4に示すものと同様であるため、その説明も省略する。

【図面の簡単な説明】

[0109]

【図1】実施例の画像処理装置の対象となる原始画像の画像データおよび画像処理装置による画像処理が実行されて得られる変換画像の画像データを示す概念的なテーブルである

【図2】実施例の画像処理装置によって実行される画像処理を説明するために用いる概念的なテーブルである。

【図3】実施例の画像処理装置による画像処理において設定されている重み付け係数を示す概念的なテーブルである。

【図4】実施例の画像処理装置の構成を示すブロック図である。

- 【図5】実施例の画像処理装置が有する第1平均誤差値算出部を示すブロック図である。

- 【図6】実施例の画像処理装置が有する第2平均誤差値算出部を示すブロック図である。

- 【図 7 】実施例の画像処理装置によって実行される画像処理の流れを示すフローチャートである。

【図8】実施例の画像処理装置によって実行される第1単位処理の流れを示すフローチャートである。

【 図 9 】 実 施 例 の 画 像 処 理 装 置 に よ っ て 実 行 さ れ る 第 2 単 位 処 理 の 流 れ を 示 す フ ロ ー チ ャ ー ト で あ る 。

【図10】変形例の画相処理装置によって実行される画像処理を説明するために用いる概念的なテーブルである。

【図11】変形例の画像処理装置によって実行される画像処理の流れを示すフローチャートである。

【図12】変形例の画像処理装置によって実行される第1単位処理の流れを示すフローチャートである。

【図13】変形例の画像処理装置によって実行される第2単位処理の流れを示すフローチ

# ャートである。

# 【符号の説明】

# [0110]

1 0 : 画像処理装置 1 2 : フィルタ 1 4 : 補正部 1 6 : 比較部 1 8 : 変換画素値決定部 2 0 : 変換誤差値算出部 2 2 8 a ~ 2 8 g : レジスタ 3 0 b ~ 3 0 e , 3 0 g : 加算器 3 2 a ~ 3 2 g : 加算記憶部 2 4 2 e , 4 2 g : 加算器 4 4 a ~ 4 4 g : 加算記憶部 5 4 5 2 : 最終加算器 5 6 : 第 2 単

位処理実行部

# 【図1】

【図2】

# 【図3】

| 重み  | 付け係数                                     |                                             |                              |                            |                                  |

|-----|------------------------------------------|---------------------------------------------|------------------------------|----------------------------|----------------------------------|

| [2  | m-1),n-2]<br>m-1,n-4]                    | [2(m-1),n-1]<br>[2m-1,n-3]                  | [2(m-1),n]<br>[2m-1,n-2]     | [2(m-1),n+1]<br>[2m-1,n-1] | 最前画素<br>[2(m-1),n+2]<br>[2m-1,n] |

| K   | (a=1/16<br>(1/16)                        | Kb=1/16<br>(2/16)                           | Kc=4/16<br>(4/16)            | Kd=1/16<br>(2/16)          | Ke=1/16<br>(1/16)                |

| ] [ | m-1,n-2]<br>2m,n-4]<br>(f=4/16<br>(2/16) | [2m-1,n-1]<br>[2m,n-3]<br>Kg=4/16<br>(4/16) | 対象画素<br>[2m-1,n]<br>[2m,n-2] |                            |                                  |

# 【図4】

【図5】

【図6】

# 【図7】

# 【図8】

【図9】

【図10】

# 【図11】

# 【図12】