(19) **日本国特許庁(JP)**

## (12)特 許 公 報(B2)

(11)特許番号

特許第4770885号 (P4770885)

(45) 発行日 平成23年9月14日(2011.9.14)

(24) 登録日 平成23年7月1日(2011.7.1)

(51) Int.Cl. F I

HO 1 L 29/78 (2006.01) HO 1 L 29/78 3 O 1 S

HO 1 L 21/28 (2006.01) HO 1 L 29/78 3 O 1 N

HO 1 L 21/28 3 O 1 S

請求項の数 4 (全 30 頁)

(21) 出願番号 特願2008-169793 (P2008-169793) (22) 出願日 平成20年6月30日 (2008.6.30) (65) 公開番号 特開2010-10508 (P2010-10508A) 平成22年1月14日 (2010.1.14) 審査請求日 平成21年6月17日 (2009.6.17) ||(73)特許権者 000002185

ソニー株式会社

東京都港区港南1丁目7番1号

||(74)代理人 100080160

弁理士 松尾 憲一郎

|(72)発明者 山川 真弥

東京都港区港南1丁目7番1号 ソニー株

式会社内

審査官 松嶋 秀忠

最終頁に続く

### (54) 【発明の名称】半導体装置

## (57)【特許請求の範囲】

### 【請求項1】

前置審查

半導体基板の表面を掘り下げた凹部内にゲート絶縁膜を介して設けられたゲート電極と

前記ゲート電極の両脇における前記半導体基板の<u>掘り下げられた</u>表面側に設けられたソース / ドレイン拡散層と、

前記ソース / ドレイン拡散層の表面を覆う状態で前記半導体基板の表面よりも深く設けられた応力印加層と、を備え、

前記応力印加層は、前記ソース / ドレイン拡散層の表面側に形成させたシリサイド膜 <u>と</u> <u>この上部に形成された絶縁性材料からなるストレスライナー膜との積層構造からなり</u>、 前記半導体基板の表面に対する前記チャネル部の深さ位置は、前記応力印加層の深さ位置よりも浅く、

前記凹部の底部が、前記ストレスライナー膜の膜厚の範囲に配置されている半導体装置

【請求項2】

前記応力印加層を構成する前記ストレスライナー膜は、

前記ソース / ドレイン拡散層上から前記ゲート電極の側壁に掛けて連続的に覆う<u>請求項</u> 1 に記載の半導体装置。

## 【請求項3】

前記半導体基板および当該半導体基板上の絶縁膜に、当該半導体基板を底面としてこれ

を掘り下げた溝パターンが設けられ、

少なくとも前記半導体基板の露出面を覆う前記ゲート絶縁膜を介して前記溝パターンを 埋め込む状態で前記ゲート電極が形成されている

請求項1または請求項2に記載の半導体装置。

#### 【請求項4】

前記ゲート絶縁膜は、前記溝パターンの内壁上部を露出する状態で設けられている請求項3記載の半導体装置。

#### 【発明の詳細な説明】

#### 【技術分野】

### [0001]

本発明は、半導体装置およびその製造方法に関し、特には電界効果型トランジスタ構造の半導体装置において、半導体基板におけるチャネル部に応力を印加することによってキャリア移動度を向上させる技術を適用した半導体装置およびその製造方法を提供することを目的とする。

#### 【背景技術】

#### [0002]

電界効果型トランジスタを用いた集積回路の微細化は、高速化・低消費電力化・低価格化・小型化など様々な利点があることから絶え間なく進歩し、今日では100nmを切るゲート長を有するトランジスタの形成が可能となっている。さらにITRS(Internatio nal Technology Roadmap for Semiconductors)のロードマップ上では、32nmノードと呼ばれているトランジスタにおいて20nm以下のゲート長が予想されている。

#### [0003]

また、ゲート長の縮小のみでなくデバイス構造そのものの縮小化(スケーリング)も進められている。しかしながら、ゲート長がサブミクロン領域から 1 0 0 n m を切る領域では、ゲートリーク電流の抑制の観点から、従来からゲート絶縁膜として用いられている酸化シリコン(Si〇₂)系絶縁膜の物理膜厚が限界になってきている。

#### [0004]

そこで、ゲート絶縁膜の実効膜厚を下げる方法として、酸化ハフニウム系の高誘電率(High-K)絶縁膜をゲート絶縁膜として用いることでゲート絶縁膜の誘電率を上げる方法、さらには金属材料を用いることでゲート電極の空乏化を抑制する方法などが検討されている。

## [0005]

このうちゲート電極の空乏化を抑制する方法では、ゲート電極用の金属材料としてタングステン(W)、チタン(Ti)、ハフニウム(Hf)、ルテニウム(Ru)、イリジウム(Ir)などを用いることが検討されている。しかしながら、これらの金属材料は、高温の熱処理が加わるとゲート絶縁膜などと反応し、ゲート絶縁膜の劣化やトランジスタのしきい値電圧の変化を引き起こす問題が発生する。このため、ゲート電極を形成した後に、ソース・ドレイ領域などの不純物拡散層を形成する従来プロセスでは、不純物の活性化熱処理において上記の問題が引き起こされてしまう。

#### [0006]

このような金属材料からなるゲート電極の問題を解決するために、ソース・ドレイン領域を形成した後に、ゲート電極を形成するダマシンゲートプロセスが提案されている(下記特許文献 1,2 参照)。ダマシンゲートプロセスにおいては、ダミーゲートを形成した状態で、先ずソース・ドレイン領域を形成する。その後、ダミーゲートを覆う層間絶縁膜を形成し、これを研磨してダミーゲートを露出させてエッチング除去し、除去した部分に新たなゲート絶縁膜およびゲート電極を形成する方法である。この方法によれば、ソース・ドレイン領域の形成における不純物の活性化熱処理の影響が、ゲート電極に及ぶことを防止できる。

#### [0007]

一方、シリコン基板におけるチャネル部に応力を印加することにより、チャネル部のキ

10

20

30

40

ャリア移動度を増加させる手法が積極的に利用されている。

#### [00008]

このような技術の一つに、サイドウォールを設けたゲート電極脇のシリコン基板にトレンチを形成し、このトレンチ内にソース / ドレインとして、シリコン ( S i ) と格子定数の異なる半導体層をエピタキシャル成長によって形成する構成が提案されている。このような構成によれば、ソース / ドレインを構成する半導体層からチャネル部に応力が印加される ( 例えば、下記特許文献 3 参照 ) 。

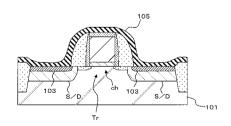

### [0009]

またこの他の技術として、図20に示すように、基板101の表面側に設けたMOSトランジスタTrのソース/ドレイン(S/D)表面にシリサイド層103を設け、さらにこのトレンジスタTrを覆う状態で基板101上に応力印加層としてストレスライナー膜105を設ける構成が提案されている。この際、MOSトランジスタTrがnチャンネル型であれば、引張応力を持つストレスライナー膜105が設けられ、MOSトランジスタTrがpチャンネル型であれば、圧縮応力を持つストレスライナー膜105が設けられる。このような構成によれば、シリサイド層103およびストレスライナー膜105からトランジスタTrのチャネル部chに応力が印加される(下記特許文献4~7参照)。

#### [0010]

【特許文献1】特開2000-315789号公報

【特許文献2】特開2005-26707号公報

【特許文献3】特開2006-186240号公報

【特許文献4】特開2002-198368号公報

【特許文献 5 】特開 2 0 0 5 - 5 7 3 0 1 号公報

【特許文献 6 】特開 2 0 0 6 - 1 6 5 3 3 5 号公報

【特許文献7】特開2006-269768号公報

【発明の開示】

【発明が解決しようとする課題】

#### [0011]

上述したようなチャネル部に応力を印加する技術においては、トレンチ内にソース/ドレインとして設けた半導体層や、シリサイド層および応力印加膜からチャネル部に印加される応力は、チャネル部の上方に設けられたゲート電極からの反作用により弱められてしまう。このため、半導体層や、シリサイド層および応力印加膜からの応力が、チャネル部に対して効果的に印加できておらず、キャリア移動度の向上が妨げられていた。

#### [0012]

そこで本発明は、チャネル部に対して効果的に応力を印加することが可能で、これによりキャリア移動度の向上を図ることが可能で高機能化が達成された半導体装置、およびその製造方法を提供することを目的とする。

【課題を解決するための手段】

#### [0013]

上記目的を達成するための本発明の半導体装置は、半導体基板上にゲート絶縁膜を介してゲート電極が設けられ、ゲート電極の両脇における半導体基板の掘り下げられた表面側にソース / ドレイン拡散層が設けられたものである。このうち、ゲート電極は、半導体基板の表面を掘り下げた凹部内にゲート絶縁膜を介して設けられている。そして、ソース / ドレイン拡散層の表面を覆う状態で、半導体基板の表面よりも深く設けられた応力印加層を備えており、応力印加層は、ソース / ドレイン拡散層の表面側に形成させたシリサイド膜と、この上部に形成された絶縁性材料からなるストレスライナー膜との積層構造からなり、半導体基板の表面に対するチャネル部の深さ位置は、応力印加層の深さ位置よりも浅く、凹部の底部が、ストレスライナー膜の膜厚の範囲に配置されていることを特徴としている。

#### [0014]

このような構成の半導体装置では、半導体基板の表面を掘り下げた部分を埋め込んでな

10

20

30

40

るゲート絶縁膜およびゲート電極を設けたことにより、半導体基板の表面よりも深い位置がチャネル部となる。これにより、ゲート電極の両脇における半導体基板の表面より深い位置に設けられた応力印加層の深さ方向にわたって当該応力印加層間の半導体基板部分に印加される応力が、チャネル部に対して集約的に印加されるようになる。したがって、半導体基板の表面とほぼ同一高さにチャネル部が形成される従来構成と比較して、応力印加層からの応力をより効果的にチャネル部に対して印加することができる。

#### 【発明の効果】

#### [0019]

以上説明したように本発明によれば、ゲート電極の両脇の応力印加層から、より効果的にチャネル部に応力を印加することができるため、効果的にキャリア移動度の向上を図ることが可能になる。この結果、半導体装置の高機能化を図ることが可能になる。

【発明を実施するための最良の形態】

#### [0020]

以下、本発明の各実施の形態を図面に基づいて詳細に説明する。尚、各実施の形態においては、先ず半導体装置の構成を説明し、次に半導体装置の製造方法を説明する。

#### [0021]

第1実施形態の半導体装置の構成

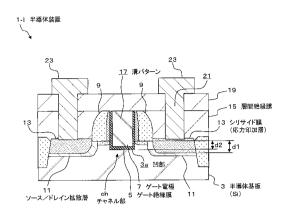

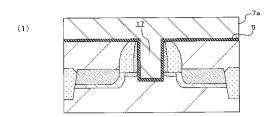

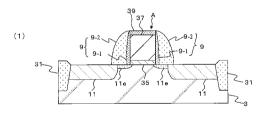

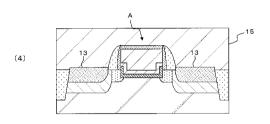

図1は、本発明を適用した第1実施形態の半導体装置1-1の要部断面図である。この図に示す半導体装置1-1は、電界効果型トランジスタ構成の半導体装置であり、次のように構成されている。

#### [0022]

すなわち、単結晶シリコンからなる半導体基板3には、表面を掘り下げてリセスした凹部3aが設けられている。そして、半導体基板3上には、この凹部3aを埋め込む状態でゲート絶縁膜5を介してゲート電極7が設けられている。ゲート電極7の両脇には、絶縁性のサイドウォール9が設けられている。また、サイドウォール9が設けられたゲート電極7の両脇における半導体基板3の表面側にはソース/ドレイン拡散層11が設けられている。このソース/ドレイン拡散層11の表面は、シリサイド膜13で覆われている。

#### [0023]

そして特に本第1実施形態においては、このシリサイド膜13が、ゲート電極7下部における半導体基板3のチャネル部chに対して応力を加えるための応力印加層としても設けられているところが特徴的である。このようなシリサイド膜(応力印加層)13は、次の製造方法で詳細に説明するように、ソース/ドレイン拡散層9が形成されている半導体基板3の露出面においてシリサイド化されたものであり、ソース/ドレイン拡散層9の深さの範囲において、半導体基板3の表面から十分な深さd1を有して設けられている。

#### [0024]

ここで、半導体基板3の表面に対する、シリサイド膜(応力印加層)13の深さd1と、ゲート絶縁膜5およびゲート電極7が埋め込まれた凹部3aの深さ、すなわちチャネル部chの深さd2とは、[d2]<[d1]であることとする。尚、この範囲においてのチャネル部chの深さd2の最適な深さについては、チャネル部chに印加される応力が最も高くなるように、実験的に求められることとする。

## [0025]

また、シリサイド膜13は、例えばコバルト(Co)、ニッケル(Ni),プラチナ(Pt)などのシリサイドからなる。このようなシリサイド膜13であれば、単結晶シリコンからなる半導体基板3に対して引っ張り応力を印加する応力印加層となる。したがって、このようなシリサイド膜13を備えた半導体装置1-1は、nチャンネル型の電界効果型トランジスタに好ましく適用される。尚、シリサイド膜13が圧縮応力を持つものであれば、このようなシリサイド膜13を備えた半導体装置1-1は、pチャンネル型の電界効果型トランジスタに好ましく適用される。

#### [0026]

またゲート絶縁膜5およびゲート電極7は、例えばダマシンゲート構造であって、絶縁

10

20

30

40

性のサイドウォール 9 を備えている。この構造においては、例えば半導体基板 3 とシリサイド膜(応力印加層) 1 3 とを覆う層間絶縁膜 1 5 に、サイドウォール 9 によって側壁が規定された溝パターン 1 7 が設けられている。この溝パターン 1 7 の底面は、さらに半導体基板 3 部分を掘り下げた凹部 3 a の底部に設定されている。そして、この溝パターン 1 7 の底面を含む内壁を覆う状態でゲート絶縁膜 5 が設けられ、このゲート絶縁膜 5 を介して溝パターン 1 7 内を埋め込む状態でゲート電極 7 が設けられている。

#### [0027]

尚、このような半導体装置 1-1は、さらに必要に応じて上層絶縁膜 19で覆われていても良い。この場合、この上層絶縁膜 19と層間絶縁膜 15とに、例えばシリサイド膜(応力印加層) 13に達する接続孔 21を設け、この接続孔 21の底部においてシリサイド膜(応力印加層) 13を介してソース / ドレイン拡散層 11に接続された配線 23を設けることができる。

#### [0028]

ゲート絶縁膜 5 を構成する誘電率絶縁膜としては、アルミニウム(A 1)、イットリウム(Y)、ジルコニウム(Z r)、ランタン(L a)、ハフニウム(H f)、タンタル(T a)のうちから選択される少なくとも 1 種を含んだ酸化物、酸化珪化物、窒化酸化物、または酸化窒化珪化物からなる膜が用いられる。具体的には、H f O  $_2$  , Z r O  $_3$  , Y  $_2$  O  $_3$  , T a  $_2$  O  $_5$  , A 1  $_2$  O  $_3$  , H f S i O  $_3$  , Z r S i O  $_3$  , Z r T i O  $_3$  , H f S i O  $_3$  , Z r S i O  $_3$  , Z r T i O  $_3$  , H f S i O  $_3$  , T a  $_3$  O  $_4$  , さらにはこれらの窒化物(H f S i O N など)が例示される。これらの材料の比誘電率は、組成や結晶性などによって多少の変動はあるが、例えば H f O  $_2$  の比誘電率は 2 5  $_3$  O 、 Z r O  $_2$  の比誘電率は 2 0  $_4$  C 5 である。尚、ゲート絶縁膜 5 はシリコン酸化膜と高誘電率(H i g h - K)絶縁膜との積層構造であっても良い。

#### [0029]

またゲート電極7を構成する主たる金属層は、Ti,Ru,Hf,Ir,Co,W,Mo,La,Ni,Cu,Al等の金属、またはこれら金属のSi化合物やN化合物、さらにはこれらを組み合わせて用いる。積層構造である場合には、ゲート電極の仕事関数を調整するための仕事関数制御層として、またはしきい値電圧を調整するための層として、ゲート電極の抵抗を下げるために複数の金属膜を積層しても良い。このような金属膜は、ゲート絶縁膜に接して設けることとする。

### [0030]

ここで一般的には、 n 型の電界効果型トランジスタであれば、ゲート電極 7 の仕事関数 は 4 . 6 e V 以下、望ましくは 4 . 3 e V 以下とされる。一方 p 型の電界効果トランジス タであれば、ゲート電極 7 の仕事関数は 4 . 6 e V 以上、望ましくは 4 . 9 e V とされる。そして、 n 型と p 型とで、ゲート電極 7 の仕事関数の差が 0 . 3 e V 以上あることが望ましいとされている。

### [0031]

そこで、ゲート電極 7 を積層構造にしてその下層部分を仕事関数制御層とする場合、この仕事関数制御層を構成する材料としては、 T i, V, N i, Z r, N b, M o, R u, H f, T a, W, P t 等から成る群から構成された金属、またはこれらの金属を含む合金のなかから、適宜の仕事関数を示す材料が選択して用いられる。またこの他にも、これらの金属の化合物、例えば金属窒化物や、金属と半導体材料との化合物である金属シリサイドが用いられる。

### [0032]

具体的には、n型の電界効果型トランジスタのゲート電極 7 であれば、Hf, Ta等から成る群から構成された金属、当該金属を含む合金、または当該の化合物が好ましく、HfSixがより好ましい。HfSiの仕事関数は、組成や結晶性によって異なるが、概ね4.1~4.3 e V程度である。

#### [0033]

また、p型の電界効果トランジスタのゲート電極 7 であれば、Ti, Mo, Ru等から成る群から構成された金属、当該金属を含む合金、または当該金属の化合物が好ましく、T

10

20

30

40

iNやRuがより好ましい。TiNの仕事関数は、組成や結晶性によって異なるが、概ね4.5~5.0eV程度である。

#### [0034]

このため、半導体基板3上に、p型の電界効果トランジスタとn型電界効果トランジスタとの両方が設けられている場合であれば、これらのうちの少なくとも一方のゲート電極は、ゲート電極の仕事関数を調整するための仕事関数制御層を含む積層構造を有する構成となっていても良い。尚、p型の電界効果トランジスタとn型電界効果トランジスタとの両方ともが、ゲート電極の仕事関数を調整するための仕事関数制御層を含む積層構造を有する構成である場合、それぞれのゲート電極は、それぞれに適する異なる仕事関数を有するように構成されることとする。

[0035]

以上のような構成の半導体装置 1-1では、半導体基板 3 においてゲート絶縁膜 5 との界面側に設けられるチャネル部 c h が、シリサイド膜(応力印加層) 1 3 間において半導体基板 3 の表面よりも深い部分に設定された状態となる。

#### [0036]

これにより、シリサイド膜(応力印加層)13の深さ方向にわたって当該シリサイド膜(応力印加層)13間の半導体基板3部分に印加される応力が、シリサイド膜(応力印加層)13の深さ方向の中間部に位置するチャネル部chに対して集約的に印加されるようになる。したがって、半導体基板3の表面とほぼ同一高さにチャネル部が形成される従来構成と比較して、シリサイド膜(応力印加層)13からの応力をより効果的にチャネル部chに対して印加させることができる。

[0037]

この結果、シリサイド膜(応力印加層)13を構成する材料濃度によらずにキャリア移動度の向上を図ることが可能になるため、半導体装置1-1のさらなる高機能化を図ることが可能になる。

[0038]

第1実施形態の半導体装置の製造方法

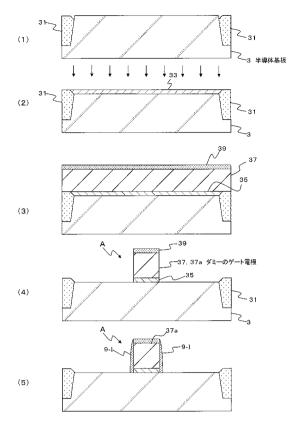

図2~図5は、図1を用いて説明した第1実施形態の半導体装置1-1の製造方法を示す断面工程図である。以下これらの図に基づいて第1実施形態の製造方法を説明する。尚、図1を用いて説明したと同様の構成要素には同一の符号を付して説明を行うこととする。

[0039]

先ず、図 2 ( 1 )に示すように、単結晶シリコンからなる半導体基板 3 の表面側に、溝内を酸化シリコン膜で埋め込んでなる S T I (Shallow Trench Isoration)構造の素子分離 3 1を形成する。

[0040]

次いで図2(2)に示すように、表面酸化などにより、酸化シリコンからなるチャネリング防止用の保護膜33を5~10nm程度の膜厚で成膜する。その後、しきい値調整用にリン(P)、ヒ素(As)、ホウ素(B)、インジウム(In)などの不純物のイオン注入を行う。この際、nチャンネル型の電界効果トランジスタの形成領域(以下nMOS領域と記す)と、pチャンネル型の電界効果トランジスタの形成領域(以下pMOS領域と記す)とに対して、それぞれに選択された不純物のイオン注入を行う。イオン注入後には、保護膜33を除去する。

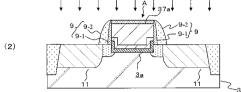

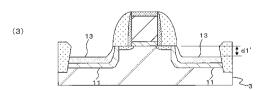

[0041]

次に図2(3)に示すように、例えば熱酸化法によって、酸化シリコンからなるダミーのゲート絶縁膜35を1~3nm程度の膜厚で成膜する。その後、CVD法により、ポリシリコンまたはアモルファスシリコンからなるダミーのゲート電極膜37を100~150nm程度の膜厚で成膜する。さらにこの上部にCVD法によって窒化シリコンからなるハードマスク層39を30~100nm程度の膜厚で成膜する。

[0042]

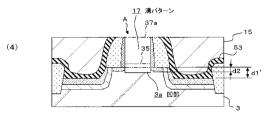

次に、図2(4)に示すように、ハードマスク層39、ダミーのゲート電極膜37、お

10

20

30

40

よびダミーのゲート絶縁膜35を、ゲート電極の形状にパターンエッチングしてダミーゲート構造Aを形成する。

#### [0043]

このようなパターンエッチングは次のように行う。先ず、ハードマスク層39上に光リソグラフィー技術や電子ビームリソグラフィー技術を用いてゲート電極用のレジストパターンを形成する。次に、このレジストパターンをマスクにしてハードマスク層39をエッチングし、ハードマスク層39をパターニングする。その後、パターニングされたハードマスク層39上からのエッチングより、ダミーのゲート電極膜37をパターニングしてダミーのゲート電極37aとし、さらにダミーのゲート絶縁膜35をパターニングする。このパターニングは、ハードマスク層39をほとんどエッチングしないような選択比でのドライエッチングによって行うこととする。また、ダミーのゲート電極膜37のパターニングにおいては、ダミーのゲート絶縁膜35をストッパにしたエッチングを行うことにより、ダミーゲート構造Aの両脇の半導体基板3の表面にエッチングダメージが入ることを防止することが好ましい。

#### [0044]

以上の後には、図2(5)に示すように、ダミーゲート構造Aの側壁に、絶縁性の第1サイドウォール9-1を形成する。この場合、例えばCVD法によって成膜した膜厚1~10nm程度の窒化シリコン膜を、ドライエッチング法を用いた異方性エッチングによりエッチバックすることにより、ダミーゲート構造Aの側壁のみに窒化シリコン膜を残して第1サイドウォール9-1を形成する。尚、第1サイドウォール9-1は、堆積成膜した酸化シリコン膜をエッチバックしてなるものであっても良く、さらにダミーのゲート電極37aの側壁を酸化させて形成しても良い。

#### [0045]

尚、この第1サイドウォール9-1は、以降に行うソース・ドレイン領域のエクステンション形成においてエクステンションの位置調整のために設けられるものであり、必要に応じて設ければ良い。したがって、この工程は必要に応じて行えば良い。

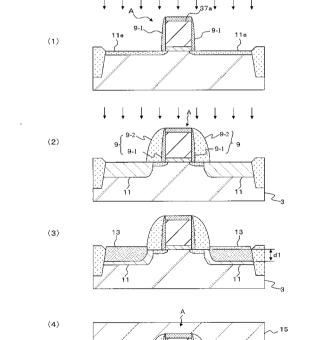

#### [0046]

次いで図 3 ( 1 )に示すように、イオン注入によって、ソース・ドレイン領域のエクステンション 1 1 e を形成するための不純物を、半導体基板 3 の表面層に導入する。この際、 p M O S 領域には B や I n などのp型不純物を、 n M O S 領域には A s や P などの n 型不純物を導入する。また、注入エネルギー 0 . 5 ~ 2 k e V 程度、ドーズ量 5 × 1 0  $^{14}$  ~ 2 × 1 0  $^{15}$ 個 / c  $m^2$  程度でのイオン注入を行うこととする。

#### [0047]

次いで、図3(2)に示すように、第1サイドウォール9-1の外側に、絶縁性の第2サイドウォール9-2を形成する。ここでは、CVD法による窒化シリコン膜の成膜と、その後の窒化シリコン膜のエッチバックによって第2サイドウォール9-2を形成する。尚、第1サイドウォール9-1と、この外側の第2サイドウォール9-2とを、合わせてサイドウォール9と称する。

### [0048]

以上の後には、ソース・ドレイン拡散層11形成のため、P、As、Bなどの不純物イオン注入を行う。このイオン注入の後には、注入した不純物を活性化させるために900~1100 の熱処理を60秒以下の範囲で行う。尚、この際、pMOS領域にはBやInなどのp型不純物を、nMOS領域にはAsやPなどのn型不純物を導入する。

## [0049]

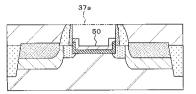

その後、図3(3)に示すように、サリサイドプロセス技術によってソース・ドレイン拡散層11の表面に、コバルト(Co)、ニッケル(Ni)、プラチナ(Pt)などの金属のシリサイド膜13を応力印加層として形成する。またこのシリサイド膜13により、ソース・ドレイン拡散層11のコンタクト抵抗を低減させる。この際、ソース・ドレイン拡散層11の表面、すなわち単結晶シリコンからなる半導体基板3の表面においては、シリサイド化の進行にともなって深さ方向にもシリサイド膜(応力印加層)13が成長する。

10

20

30

40

このため、ここでは、ソース / ドレイン拡散層 1 1 の深さの範囲内において、半導体基板 3 の表面に対して十分な深さ d 1 となるように、シリサイド膜(応力印加層) 1 3 を成長させることが重要である。

#### [0050]

次に、図3(4)に示すように、ダミーゲート構造Aおよびシリサイド膜(応力印加層)13を埋め込む状態で、例えば酸化シリコンからなる層間絶縁膜15を成膜する。

#### [0051]

次いで、図4(1)に示すように、ダミーゲート構造Aにおけるダミーのゲート電極3 7aが露出するまで層間絶縁膜15の表面をCMP法によって研磨する。

#### [0052]

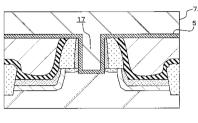

次に、図4(2)に示すように、ポリシリコンまたはアモルファスシリコンからなるダミーのゲート電極37aをドライエッチングにより除去した後に、酸化シリコンからなるダミーのゲート絶縁膜35をウェットエッチングにより除去する。これにより、半導体基板3とシリサイド膜(応力印加層)13とを覆う層間絶縁膜15に、ダミーゲート構造Aを除去してなる溝パターン17を形成し、溝パターン17の底面に半導体基板3を露出させる。この溝パターン17は、サイドウォール9(9-1,9-2)によって側壁が規定されたものになる。

#### [0053]

次に、図4(3)に示すように、溝パターン17の底部における半導体基板3の露出面を掘り下げ、半導体基板3に凹部3aを形成するリセスエッチングを行い、シリサイド膜(応力印加層)13との間に離間させた位置において溝パターン17を掘り下げる。

#### [0054]

この際、半導体基板3の表面に対して、シリサイド膜(応力印加層)13の深さd1とした場合、凹部3aの深さd2(すなわちチャネル深さd2)が、[d2]<[d1]となるようにする。尚、この範囲においての凹部3aのチャネル深さd2の最適値については、ここで形成するMOSトランジスタ(電界効果トランジスタ)のチャネル部に印加される応力が最も高くなるように、実験的に求められることとする。

#### [0055]

このようなリセスエッチングには、プラズマ雰囲気中で酸化を行うプラズマ酸化によって単結晶シリコンからなる半導体基板3の表面に1~2nm程度の膜厚の酸化シリコン膜を形成した後、フッ酸のウェットエッチングにより酸化シリコン膜を除去する手法を適用する。プラズマ酸化とウェットエッチングとは、チャネル深さd2に合わせて必要回数繰り返し行うこととする。これにより、リセスエッチングによって露出する半導体基板3の露出面にダメージが加わることを防止する。またこの際のプラズマ酸化は、不純物の熱による再拡散を防ぐために500以下で行うことが望ましい。

## [0056]

尚、半導体基板3の表面酸化には、上記のプラズマ酸化以外に、オゾンを用いた酸化や、ガスを用いた酸化を行っても良い。またシリコン表面をドライエッチング法によって直接エッチングする方法もある。

#### [0057]

次に、図4(4)に示すように、半導体基板3の表面を掘り下げた溝パターン17の内壁を覆う状態で、ゲート絶縁膜5を成膜する。ここでは、CVD法やALD法などにより、上述した高誘電率材料からなるゲート絶縁膜5を成膜することが好ましい。

## [0058]

次に、図5(1)に示すように、溝パターン17の内部を埋め込む状態で、ゲート絶縁膜5を介してゲート電極材料膜7aを成膜する。ここでは、ゲート電極材料膜7aとして、メタルゲート用の金属層をCVD法、PVD法、またはALD法によって成膜する。このゲート電極材料膜7aは、単層または積層構造であって良く、装置の構成において述べた各材料を用いて成膜されることとする。

### [0059]

50

10

20

30

次に、図 5 ( 2 )に示すように、層間絶縁膜 1 5 が露出するまで、ゲート電極材料膜 7 a とゲート絶縁膜 5 を C M P によって研磨する。これにより、溝パターン 1 7 内に、ゲート絶縁膜 5 を介してゲート電極材料膜 7 a を残してなるゲート電極 7 を形成する。

#### [0060]

以上の後には必要に応じて、図5(3)に示すように、層間絶縁膜15およびゲート電極7を覆う状態で、酸化シリコンからなる上層絶縁膜19を成膜する。次いで、上層絶縁膜19および層間絶縁膜15に、シリサイド膜(応力印加層)13に達する接続孔21を形成する。そして、これらの接続孔21を埋め込むプラグおよびこれに接続する配線23を形成する。

### [0061]

以上により図1を用いて説明したように、半導体基板3の表面を掘り下げた凹部3a内にゲート絶縁膜5を介して設けられたゲート電極7が設けられ、ゲート電極7両脇のソース/ドレイン拡散層11の表面を覆う状態で半導体基板3の表面よりも深くシリサイド膜(応力印加層)13を設けた構成の半導体装置1-1が得られる。

#### [0062]

そして以上説明した製造方法によれば、図4(2)を用いて説明したように、シリサイド膜(応力印加層)13が形成された状態でダミーゲート構造Aを除去することにより、シリサイド膜(応力印加層)13からダミーゲート構造A下の半導体基板3部分に印加される応力が、ダミーのゲート電極37aからの反作用により弱められることが防止される。このため、チャネル部chに対して、シリサイド膜(応力印加層)13からの応力が効果的に印加された状態となる。

#### [0063]

そして特に、次の図4(3)で用いて説明したように、ダミーゲート構造Aを除去した 溝パターン17の底部の半導体基板3をさらに掘り下げることにより、半導体基板3の表 面よりも深い位置がチャネル部chとなる。これにより、このチャネル部chには、シリ サイド膜(応力印加層)13の深さ方向にわたって当該シリサイド膜(応力印加層)13 間の半導体基板3部分に印加される応力が、集約的に印加されるようになる。したがって 、シリサイド膜(応力印加層)13からの応力を効果的にかつ集約させた状態でチャネル 部chに印加させることが可能な構成の半導体装置1-1を作製することが可能になる。

### [0064]

第2実施形態の半導体装置の構成

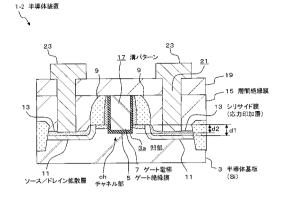

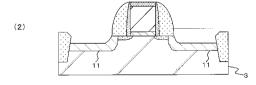

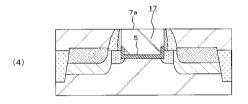

図6は、本発明を適用した第2実施形態の半導体装置1-2の要部断面図である。この図に示す半導体装置1-2は、電界効果型トランジスタ構成の半導体装置である。この図に示す半導体装置1-2が、図1を用いて説明した第1実施形態と異なるところは、ソース/ドレイン拡散層11およびシリサイド膜(応力印加層)13が設けられている半導体基板3の表面部分が、リセスエッチングによって掘り込まれているところにある。これ以外の構成は、第1実施形態と同様である。

#### [0065]

すなわち、第1実施形態と同様に、単結晶シリコンからなる半導体基板3には、表面を掘り下げてリセスした凹部3aが設けられている。そして、半導体基板3上には、この凹部3aを埋め込む状態でゲート絶縁膜5を介してゲート電極7が設けられている。ゲート電極7の両脇には、絶縁性のサイドウォール9が設けられている。また、本第2実施形態においては、サイドウォール9が設けられたゲート電極7の両脇における半導体基板3の表面がリセスエッチングによって掘り下げられており、掘り下げられた表面側にソース/ドレイン拡散層11が設けられている。このソース/ドレイン拡散層11の表面は、シリサイド膜13で覆われている。

#### [0066]

そして特に本第2実施形態においても、このシリサイド膜13が、ゲート電極7下部における半導体基板3のチャネル部chに対して応力を加えるための応力印加層としても設けられているところが特徴的である。このようなシリサイド膜(応力印加層)13は、次

10

20

30

40

の製造方法で詳細に説明するように、ソース / ドレイン拡散層 9 が形成されている半導体基板 3 の露出面においてシリサイド化されたものであり、ソース / ドレイン拡散層 9 の深さの範囲において、半導体基板 3 の表面から十分な深さ d 1 を有して設けられている。

#### [0067]

ここで、半導体基板3の表面に対する、シリサイド膜(応力印加層)13の深さd1と、ゲート絶縁膜5およびゲート電極7が埋め込まれた凹部3aの深さ、すなわちチャネル部chの深さd2とは、[d2]<[d1]であることも第1実施形態と同様である。さらに、チャネル部chの深さd2の最適な深さについては、チャネル部chに印加される応力が最も高くなるように、実験的に求められることも第1実施形態と同様である。

#### [0068]

尚、本第2実施形態では、シリサイド膜(応力印加層)13の膜厚の範囲、すなわちシリサイド膜(応力印加層)13の表面と深さd1の位置(裏面)との間に、凹部3aの底部が配置されることが好ましい。

## [0069]

また、この場合であっても、第1実施形態と同様に、シリサイド膜13は、例えばコバルト(Co)、ニッケル(Ni)、プラチナ(Pt)などのシリサイドからなるものであれば、半導体基板3に対して引っ張り応力を印加する応力印加層となり、nチャンネル型の電界効果型トランジスタに好ましく適用される。一方、シリサイド膜13が圧縮応力を持つものであれば、このようなシリサイド膜13を備えた半導体装置1-2は、pチャンネル型の電界効果型トランジスタに好ましく適用される。

#### [0070]

またゲート絶縁膜5およびゲート電極7は、第1実施形態と同様に、例えばダマシンゲート構造であって、絶縁性のサイドウォール9を備えている。この構造においては、例えば半導体基板3とシリサイド膜(応力印加層)13とを覆う層間絶縁膜15に、サイドウォール9によって側壁が規定された溝パターン17が設けられている。この溝パターン17の底面は、さらに半導体基板3部分を掘り下げた凹部3aの底部に設定されている。そして、この溝パターン17の内壁を覆う状態でゲート絶縁膜5が設けられ、このゲート絶縁膜5を介して溝パターン17内を埋め込む状態でゲート電極7が設けられている。

### [0071]

尚、このような半導体装置 1-2は、さらに必要に応じて上層絶縁膜 19で覆われていても良い。この場合、この上層絶縁膜 19と層間絶縁膜 15とに、例えばシリサイド膜(応力印加層) 13に達する接続孔 21を設け、この接続孔 21の底部においてシリサイド膜(応力印加層) 13を介してソース / ドレイン拡散層 11に接続された配線 23を設けることができる。

## [0072]

またゲート絶縁膜 5 は、物理的な膜厚を維持しつつ実効膜厚を下げるために、高誘電率 ( H i g h - K ) 絶縁膜で構成されていることが好ましいことも第 1 実施形態と同様であり、誘電率絶縁膜としては用いられる材料も同様である。

#### [ 0 0 7 3 ]

またゲート電極 7 の構造および構成材料も、第 1 実施形態で示したと同様の構成および 40 構成材料が適用される。

#### [0074]

以上のような構成の半導体装置 1-2であっても、半導体基板 3 においてゲート絶縁膜 5 との界面側に設けられるチャネル部 c h が、シリサイド膜(応力印加層) 1 3 間において半導体基板 3 の表面よりも深い部分に設定された状態となる。

## [0075]

これにより、シリサイド膜(応力印加層)13の深さ方向にわたって当該シリサイド膜(応力印加層)13間の半導体基板3部分に印加される応力が、シリサイド膜(応力印加層)13の深さ方向の中間部に位置するチャネル部chに対して集約的に印加されるようになる。したがって、半導体基板3の表面とほぼ同一高さにチャネル部が形成される従来

10

20

30

20

30

40

50

構成と比較して、シリサイド膜(応力印加層)13からの応力をより効果的にチャネル部 chに対して印加させることができる。

#### [0076]

この結果、シリサイド膜(応力印加層)13を構成する材料濃度によらずにキャリア移動度の向上を図ることが可能になるため、半導体装置1-2のさらなる高機能化を図ることが可能になる。

#### [0077]

第2実施形態の半導体装置の製造方法

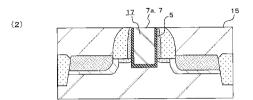

図7は、図6を用いて説明した第2実施形態の半導体装置1-2の製造方法の特徴部を示す断面工程図である。以下、この図および第1実施形態の製造方法で用いた断面工程図に基づいて第2実施形態の製造方法を説明する。

#### [0078]

先ず、第1実施形態において図2(1)~図3(2)を用いて説明した工程を同様に行なう。

#### [0079]

これにより、図7(1)に示すように、単結晶シリコンからなる半導体基板3の表面側に、素子分離31を形成し、さらにハードマスク層39、ダミーのゲート電極膜37、およびダミーのゲート絶縁膜35を、ゲート電極の形状にパターンエッチングしてダミーゲート構造Aを形成する。また、ダミーゲート構造Aの側壁に、絶縁性の第1サイドウォール9-1と、この外側の第2サイドウォール9-2とを合わせたサイドウォール9を形成する。さらに、サイドウォール9の外側に、エクステンション11eを有するソース・ドレイン拡散層11を形成する。

#### [0800]

次に、図7(2)に示すように、半導体基板3の露出表面、すなわちソース / ドレイン 拡散層11の露出表面をリセスエッチングすることによって掘り下げる。

#### [0081]

その後、図7(3)に示すように、サリサイドプロセス技術によってソース・ドレイン拡散層11の表面に、コバルト(Co),ニッケル(Ni),プラチナ(Pt)などの金属のシリサイド膜13を応力印加層として形成する。またこのシリサイド膜13により、ソース・ドレイン拡散層11のコンタクト抵抗を低減させる。この際、ソース・ドレイン拡散層11の表面、すなわち単結晶シリコンからなる半導体基板3の表面においては、シリサイド化の進行にともなって深さ方向にもシリサイド膜(応力印加層)13が成長する。このため、ここでは、ソース/ドレイン拡散層11の深さの範囲内において、半導体基板3の表面に対して十分な深さd1となるように、シリサイド膜(応力印加層)13を成長させることが重要である。

### [0082]

以上の後には、第1実施形態において図3(4)~図5(3)を用いて説明した工程を 同様に行なう。

### [0083]

すなわち、層間絶縁膜15を成膜し、ダミーゲート構造Aにおけるダミーのゲート電極37aが露出するまで層間絶縁膜15の表面をCMP法によって研磨し、その後、ダミーゲート構造Aを除去してなる溝パターン17を形成して溝パターン17の底面に半導体基板3を露出させる。この溝パターン17は、サイドウォール9(9-1,9-2)によって側壁が規定されたものになる。

#### [0084]

次に、溝パターン 1 7 の底部における半導体基板 3 の露出面を掘り下げ、半導体基板 3 に凹部 3 a を形成するリセスエッチングを行い、シリサイド膜(応力印加層) 1 3 との間に離間させた位置において溝パターン 1 7 を掘り下げる。この際、半導体基板 3 の表面に対して、シリサイド膜(応力印加層) 1 3 の深さ d 1 とした場合、凹部 3 a の深さ d 2 (すなわちチャネル深さ d 2)が、[d 2] < [d 1]となるようにする。ただし、本第 2

実施形態では、シリサイド膜(応力印加層)13の膜厚の範囲、すなわちシリサイド膜(応力印加層)13の表面と深さd1の位置(裏面)との間に、凹部3aの底部が位置するようにリセスエッチングを行なうことが好ましい。

#### [0085]

さらに、半導体基板3の表面を掘り下げた溝パターン17の内壁を覆う状態で、ゲート 絶縁膜5を成膜し、次いでゲート電極材料膜7aを成膜し、これらをCMPによって研磨 することにより、溝パターン17内にゲート絶縁膜5を介してゲート電極材料膜7aを残 してなるゲート電極7を形成する。その後、必要に応じて、上層絶縁膜19、接続孔21 、および配線23を形成する。

### [0086]

以上により図6を用いて説明したように、半導体基板3の表面を掘り下げた凹部3a内にゲート絶縁膜5を介して設けられたゲート電極7が設けられ、ゲート電極7両脇のソース/ドレイン拡散層11の表面を覆う状態で半導体基板3の表面よりも深くシリサイド膜(応力印加層)13を設けた構成の半導体装置1-2が得られる。

#### [0087]

そして以上説明した製造方法であっても、第1実施形態の製造方法と同様に、シリサイド膜(応力印加層)13が形成された状態でダミーゲート構造Aの除去が行われる。このため、シリサイド膜(応力印加層)13からダミーゲート構造A下の半導体基板3部分に印加される応力が、ダミーのゲート電極37aからの反作用により弱められることが防止される。このため、チャネル部chに対して、シリサイド膜(応力印加層)13からの応力が効果的に印加された状態となる。

#### [0088]

また第1実施形態と同様に、ダミーゲート構造Aを除去した溝パターン17の底部の半導体基板3をさらに掘り下げることにより、半導体基板3の表面よりも深い位置がチャネル部chとなる。これにより、このチャネル部chには、シリサイド膜(応力印加層)13の深さ方向にわたって当該シリサイド膜(応力印加層)13間の半導体基板3部分に印加される応力が、集約的に印加されるようになる。したがって、シリサイド膜(応力印加層)13からの応力を効果的にかつ集約させた状態でチャネル部chに印加させることが可能な構成の半導体装置1-2を作製することが可能になる。

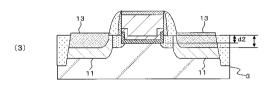

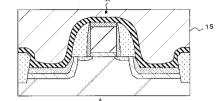

### [0089]

第3実施形態の半導体装置の構成

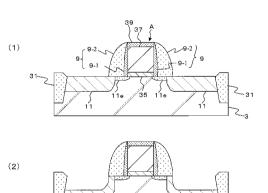

図8は、本発明を適用した第3実施形態の半導体装置1-3の要部断面図である。この図に示す半導体装置1-3は、電界効果型トランジスタ構成の半導体装置である。この図に示す半導体装置1-3が、図1を用いて説明した第1実施形態と異なるところは、ゲート絶縁膜5が、溝パターン17の内壁全面を覆っておらず、内壁の上部を露出する状態で設けられているところにある。これ以外の構成は、第1実施形態と同様である。

## [0090]

すなわち、第1実施形態と同様に、単結晶シリコンからなる半導体基板3には、表面を掘り下げてリセスした凹部3aが設けられている。そして、半導体基板3上には、この凹部3aを埋め込む状態でゲート絶縁膜5を介してゲート電極7が設けられている。ゲート電極7の両脇には、絶縁性のサイドウォール9が設けられている。また、サイドウォール9が設けられたゲート電極7の両脇における半導体基板3の表面側にはソース/ドレイン拡散層11が設けられている。このソース/ドレイン拡散層11の表面は、シリサイド膜13で覆われている。

#### [0091]

そして特に本第3実施形態においても、このシリサイド膜13が、ゲート電極7下部における半導体基板3のチャネル部chに対して応力を加えるための応力印加層としても設けられているところが特徴的である。このようなシリサイド膜(応力印加層)13は、次の製造方法で詳細に説明するように、ソース/ドレイン拡散層9が形成されている半導体基板3の露出面においてシリサイド化されたものであり、ソース/ドレイン拡散層9の深

10

20

30

40

20

30

50

さの範囲において、半導体基板3の表面から十分な深さd1を有して設けられている。

### [0092]

ここで、半導体基板3の表面に対する、シリサイド膜(応力印加層)13の深さd1と、ゲート絶縁膜5およびゲート電極7が埋め込まれた凹部3aの深さ、すなわちチャネル部chの深さd2とは、[d2]<[d1]であることも第1実施形態と同様である。さらに、チャネル部chの深さd2の最適な深さについては、チャネル部chに印加される応力が最も高くなるように、実験的に求められることも第1実施形態と同様である。

### [0093]

さらに、シリサイド膜(応力印加層)13の膜厚の範囲、すなわち膜(応力印加層)13の表面と深さd1の位置(裏面)との間に、チャネル部chが配置されることが好ましいことも第1実施形態と同様である。

#### [0094]

また、この場合であっても、第1実施形態と同様に、シリサイド膜13は、例えばコバルト(Co)、ニッケル(Ni)、プラチナ(Pt)などのシリサイドからなるものであれば、半導体基板3に対して引っ張り応力を印加する応力印加層となり、nチャンネル型の電界効果型トランジスタに好ましく適用される。一方、シリサイド膜13が圧縮応力を持つものであれば、このようなシリサイド膜13を備えた半導体装置1-3は、pチャンネル型の電界効果型トランジスタに好ましく適用される。

#### [0095]

またゲート絶縁膜5およびゲート電極7は、第1実施形態と同様に、例えばダマシンゲート構造であって、絶縁性のサイドウォール9を備えている。この構造においては、例えば半導体基板3とシリサイド膜(応力印加層)13とを覆う層間絶縁膜15に、サイドウォール9によって側壁が規定された溝パターン17が設けられている。この溝パターン17の底面は、さらに半導体基板3部分を掘り下げた凹部3aの底部に設定されている。そして、特に本第3実施形態においては、この溝パターン17の下部である凹部3aの内壁を覆うが、溝パターン17の内壁の上部を露出する状態でゲート絶縁膜5が設けられ、このゲート絶縁膜5を介して溝パターン17内を埋め込む状態でゲート電極7が設けられている。

### [0096]

尚、このような半導体装置 1-3は、さらに必要に応じて上層絶縁膜 1 9 で覆われていても良い。この場合、この上層絶縁膜 1 9 と層間絶縁膜 1 5 とに、例えばシリサイド膜(応力印加層) 1 3 に達する接続孔 2 1 を設け、この接続孔 2 1 の底部においてシリサイド膜(応力印加層) 1 3 を介してソース / ドレイン拡散層 1 1 に接続された配線 2 3 を設けることができる。

## [0097]

またゲート絶縁膜 5 は、物理的な膜厚を維持しつつ実効膜厚を下げるために、高誘電率 ( H i g h - K ) 絶縁膜で構成されていることが好ましいことも第 1 実施形態と同様であり、誘電率絶縁膜としては用いられる材料も同様である。

#### [0098]

またゲート電極 7 の構造および構成材料も、第 1 実施形態で示したと同様の構成および 40 構成材料が適用される。

#### [0099]

以上のような構成の半導体装置 1-3であっても、半導体基板 3 においてゲート絶縁膜 5 との界面側に設けられるチャネル部 c h が、シリサイド膜(応力印加層) 1 3 間において半導体基板 3 の表面よりも深い部分に設定された状態となる。

## [0100]

これにより、シリサイド膜(応力印加層)13の深さ方向にわたって当該シリサイド膜(応力印加層)13間の半導体基板3部分に印加される応力が、シリサイド膜(応力印加層)13の深さ方向の中間部に位置するチャネル部chに対して集約的に印加されるようになる。したがって、半導体基板3の表面とほぼ同一高さにチャネル部が形成される従来

(14)

構成と比較して、シリサイド膜(応力印加層) 1 3 からの応力をより効果的にチャネル部 c h に対して印加させることができる。

#### [0101]

この結果、シリサイド膜(応力印加層)13を構成する材料濃度によらずにキャリア移動度の向上を図ることが可能になるため、半導体装置1-3のさらなる高機能化を図ることが可能になる。

#### [0102]

また本第3実施形態では、ゲート絶縁膜5は、溝パターン17の下部を構成する凹部3 aの内壁のみに設けられていて、溝パターン17の内壁上部を露出する状態で設けられた 構成となる。このため、高誘電率材料からなるゲート絶縁膜5が、ゲート電極7と配線2 3との間に存在せず、ゲート電極7・配線23間の寄生容量による素子性能の低下を防止 できると言った効果を得ることが可能である。

#### [0103]

第3実施形態の半導体装置の製造方法

図9~図11は、図8を用いて説明した第3実施形態の半導体装置1-3の製造方法を示す断面工程図である。以下これらの図に基づいて第3実施形態の製造方法を説明する。

#### [0104]

先ず、図9(1)に示すように、半導体基板の表面側に素子分離を形成し、さらに、ここでの図示を省略した保護膜を形成し、これを介してしきい値調整用の不純物のイオン注入を行い、イオン注入後に保護膜を除去するまでを第1実施形態と同様に行う。

#### [0105]

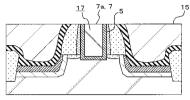

次に、図9(2)に示すように、半導体基板3における素子分離31で分離された間に、以降に形成するゲート電極の形成部に一致させた溝形状の凹部3aを形成する。この凹部3aは、光リソグラフィー技術や電子ビームリソグラフィー技術を適用して形成したレジストパターンをマスクにした半導体基板3のリセスエッチングによって形成する。尚、ここでは、この凹部3aの表面層がチャネル部となるため、凹部3aの深さが第実施形態で説明したチャネル深さd2となる。このチャネル深さd2は、先の第1実施形態と同様であり、後で形成するシリサイド膜(応力印加層)の深さd1に対して、[d2]<[d1]となるようにする。

### [0106]

次に、図9(3)に示すように、半導体基板3の表面を掘り下げた凹部3aの内壁を覆う状態で、CVD法やALD法などにより上述した高誘電率材料からなるゲート絶縁膜5 を成膜する。尚、ここでは予め高誘電率材料からなるゲート絶縁膜5を成膜しているが、 ゲート絶縁膜5に代えてダミーの酸化膜を形成しても良い。

#### [0107]

その後、図9(4)に示すように、ゲート絶縁膜5上に、ポリシリコンまたはアモルファスシリコンからなるダミーのゲート電極膜37、さらには窒化シリコンからなるハードマスク層39を順次成膜する。

### [0108]

次に、図9(5)に示すように、ここでの図示を省略したレジストパターンをマスクにしてハードマスク層39をエッチングし、ハードマスク層39をパターニングする。その後、パターニングされたハードマスク層39上からのエッチングより、ダミーのゲート電極膜37をパターニングしてダミーのゲート電極37aとする。ダミーのゲート電極膜37のパターニングにおいては、高誘電率材料からなるゲート絶縁膜5をストッパにしたエッチングを行うことにより、ダミーゲート構造Aの両脇の半導体基板3の表面にエッチングダメージが入ることを防止する。このようなエッチングには、エッチングガスとしては例えばHBr /  $O_2$ などを用いたドライエッチングを行う。

#### [0109]

また、以上のドライエッチングに続けてゲート絶縁膜5のエッチングを行い、ダミーゲート構造A下のみにゲート絶縁膜5を残す。

10

20

30

50

#### [0110]

尚、図示した例においては、ダミーゲート構造Aが凹部3aに対して一致した状態を示している。しかしながら、ダミーゲート構造Aは、凹部3aに重ねて設けられていれば良く、これらのパターンがずれていても良い。

#### [0111]

すなわち、図10(1)に示すように、ダミーゲート構造Aの側壁に、絶縁性の第1サイドウォール9-1を形成する。その後、イオン注入によって、ソース/ドレイン拡散層のエクステンション11eを形成するための不純物を、半導体基板3の表面層に導入する。この際、イオン注入の打ち分けによりpMOS領域とnMOS領域とで異なる不純物を導入することは、第1実施形態と同様である。尚、この工程は必要に応じて行えば良い。

#### [0112]

次いで、図10(2)に示すように、第1サイドウォール9-1の外側に、絶縁性の第2サイドウォール9-2を形成する。尚、第1サイドウォール9-1と、この外側の第2サイドウォール9-2とを、合わせてサイドウォール9と称する。

#### [0113]

その後、ソース・ドレイン拡散層 1 1 を形成するための不純物の注入を行い、さらに不 純物を活性化させるための熱処理を行う。尚、ダミーゲート構造 A と凹部 3 a とのパター ンがずれていて、凹部 3 a の底面がダミーゲート構造 A から露出している場合、凹部 3 a の露出部分が第 2 サイドウォール 9 -2で完全に覆われるようにすることが好ましい。

### [0114]

その後、図10(3)に示すように、サリサイドプロセス技術によってサイドウォール 9 の外側のソース・ドレイン拡散層11の表面に、コバルト(Co), ニッケル(Ni), プラチナ(Pt)などの金属のシリサイド膜13を応力印加層として形成する。またこのシリサイド膜13により、ソース・ドレイン拡散層11のコンタクト抵抗を低減させる。この際、ソース・ドレイン拡散層11の表面、すなわち単結晶シリコンからなる半導体基板3の表面においては、シリサイド化の進行にともなって深さ方向にもシリサイド膜(応力印加層)13が成長する。このため、ここでは、ソース / ドレイン拡散層11の深さの範囲内において、半導体基板3の表面に対して十分な深さd1となり、かつ凹部3aの深さd2に対して[d2] < [d1]となるように、シリサイド膜(応力印加層)13を成長させることが重要である。

#### [0115]

その後、図10(4)に示すように、ダミーゲート構造 A およびシリサイド膜(応力印加層)13を埋め込む状態で、例えば酸化シリコンからなる層間絶縁膜15を成膜する。

### [0116]

次いで、図11(1)に示すように、ダミーゲート構造Aにおけるダミーのゲート電極37aが露出するまで層間絶縁膜15の表面をCMP法によって研磨する。

## [0117]

次に、図11(2)に示すように、ゲート絶縁膜5を残して、ポリシリコンまたはアモルファスシリコンからなるダミーのゲート電極37aをドライエッチングにより除去する。これにより、半導体基板3とシリサイド膜(応力印加層)13とを覆う層間絶縁膜15に、ダミーゲート構造Aを除去してなる溝パターン17を形成する。溝パターン17の底面はゲート絶縁膜5で覆われた状態となるが、この溝パターン17は、凹部3aに重ねて形成される。またこの溝パターン17は、サイドウォール9(9-1,9-2)によって側壁が規定されたものになる。尚、本実施例では予め高誘電率膜からなるゲート絶縁膜3を形成してあるが、ダミーのゲート絶縁膜を形成している場合は、ここでダミーのゲート絶縁膜も除去する。

#### [0118]

次に、図11(3)に示すように、溝パターン17の内部を埋め込む状態でゲート電極 7を形成する。この際、先ず溝パターン17の内部を埋め込む状態で、ゲート絶縁膜5を 介してゲート電極材料膜を成膜する。ここでは、ゲート電極材料膜として、メタルゲート 10

20

30

40

20

30

40

50

用の金属層をCVD法、PVD法、またはALD法によって成膜する。このゲート電極材料膜7は、単層または積層構造であって良く、第1実施形態において述べた各材料を用いて成膜されることとする。その後、層間絶縁膜15が露出するまで、ゲート電極材料膜をCMPによって研磨する。これにより、溝パターン17内に、ゲート絶縁膜5を介してゲート電極材料膜を残してなるゲート電極7を形成する。尚、ダミーゲート絶縁膜を除去していた場合は、ゲート電極材料膜の成膜前に、ゲート絶縁膜を成膜しておくものとする。

以上の後には必要に応じて、図11(4)に示すように、層間絶縁膜15およびゲート電極7を覆う状態で、酸化シリコンからなる上層絶縁膜19を成膜する。次いで、上層絶縁膜19および層間絶縁膜15に、シリサイド膜(応力印加層)13に達する接続孔21を形成する。そして、これらの接続孔21を埋め込むプラグおよびこれに接続する配線23を形成する。

[0120]

以上により図8を用いて説明したように、半導体基板3の表面を掘り下げた凹部3a内にゲート絶縁膜5を介して設けられたゲート電極7が設けられ、ゲート電極7両脇のソース/ドレイン拡散層11の表面を覆う状態で半導体基板3の表面よりも深くシリサイド膜(応力印加層)13を設けた構成の半導体装置1-3が得られる。

[0121]

そして以上説明した製造方法であっても、図11(2)を用いて説明したように、シリサイド膜(応力印加層)13が形成された状態でダミーのゲート電極37aの除去が行われる。このため、シリサイド膜(応力印加層)13からダミーゲート構造A下の半導体基板3部分に印加される応力が、ダミーのゲート電極37aからの反作用により弱められることが防止される。このため、チャネル部chに対して、シリサイド膜(応力印加層)13からの応力が効果的に印加された状態となる。

[0122]

また、半導体基板 3 をさらに掘り下げた凹部 3 a を溝パターン 1 7 の底部としたことにより、半導体基板 3 の表面よりも深い位置がチャネル部 c h となる。これにより、このチャネル部 c h には、シリサイド膜(応力印加層) 1 3 の深さ方向にわたって当該シリサイド膜(応力印加層) 1 3 間の半導体基板 3 部分に印加される応力が、集約的に印加されるようになる。したがって、第1実施形態と同様に、シリサイド膜(応力印加層) 1 3 からの応力を効果的にかつ集約させた状態でチャネル部 c h に印加させることが可能な構成の半導体装置 1-3を作製することが可能になる。

[0123]

第3実施形態の半導体装置の製造方法(変形例)

図12~図14は、図8を用いて説明した第3実施形態の半導体装置1-3の製造方法の変形例を示す断面工程図である。以下これらの図に基づいて第3実施形態の製造方法の変形例を説明する。

[0124]

先ず、図12(1)、(2)は、第3実施形態の手順と同様に行なう。

[0125]

すなわち、図12(1)に示すように、半導体基板の表面側に素子分離を形成し、さらに、ここでの図示を省略した保護膜を形成し、これを介してしきい値調整用の不純物のイオン注入を行い、イオン注入後に保護膜を除去するまでを第1実施形態と同様に行う。

[0126]

次に、図12(2)に示すように、半導体基板3における素子分離31で分離された間に、以降に形成するゲート電極の形成部に一致させた溝形状の凹部3aを形成する。この凹部3aは、光リソグラフィー技術や電子ビームリソグラフィー技術を適用して形成したレジストパターンをマスクにした半導体基板3のリセスエッチングによって形成する。尚、ここでは、この凹部3aの表面層がチャネル部となるため、凹部3aの深さが第実施形態で説明したチャネル深さd2となる。このチャネル深さd2は、先の第1実施形態と同

様に例と同様であり、後で形成するシリサイド膜(応力印加層)の深さd1に対して、[d2]<[d1]となるようにする。

### [0127]

次に、図12(3)に示すように、半導体基板3の表面を掘り下げた凹部3aの内壁を覆う状態で、CVD法やALD法などにより上述した高誘電率材料からなるゲート絶縁膜5を成膜する。そしてこの変形例では、さらにゲート絶縁膜5上に、キャップ膜50をCVD法、PVD法、またはALD法などにより成膜する。このキャップ膜50は、以降の工程においてゲート絶縁膜5を保護するためのものである。このようなキャップ膜50として、例えば窒化チタン(TiN)膜を1~10nm程度の膜厚で形成する。

### [0128]

その後、図12(4)に示すように、キャップ膜50上に、ポリシリコンまたはアモルファスシリコンからなるダミーのゲート電極膜37、さらには窒化シリコンからなるハードマスク層39を順次成膜する。

## [0129]

次に、図12(5)に示すように、ここでの図示を省略したレジストパターンをマスクにしてハードマスク層39をエッチングし、ハードマスク層39をパターニングする。その後、パターニングされたハードマスク層39上からのエッチングより、ダミーのゲート電極膜37をパターニングしてダミーのゲート電極37aとする。またこのダミーのゲート電極37のエッチングに続けて、キャップ膜50、さらにはゲート絶縁膜5のエッチングを行う。これにより、ダミーゲート構造A下のみにゲート絶縁膜5を残す。

#### [0130]

その後、図13(1)~図14(1)までは、第3実施形態において図10(1)~図11(1)を用いて説明したと同様に行なう。

#### [0131]

すなわち図13(1)に示すように、ダミーゲート構造Aの側壁に、絶縁性の第1サイドウォール9-1を形成する。その後、イオン注入によって、ソース/ドレイン拡散層のエクステンション11eを形成するための不純物を、半導体基板3の表面層に導入する。この際、イオン注入の打ち分けによりpMOS領域とnMOS領域とで異なる不純物を導入することは、第1実施形態と同様である。尚、この工程は必要に応じて行えば良い。

## [0132]

次いで、図13(2)に示すように、第1サイドウォール9-1の外側に、絶縁性の第2サイドウォール9-2を形成する。尚、第1サイドウォール9-1と、この外側の第2サイドウォール9-2とを、合わせてサイドウォール9と称する。

### [0133]

その後、ソース・ドレイン拡散層 1 1 を形成するための不純物の注入を行い、さらに不純物を活性化させるための熱処理を行う。尚、ダミーゲート構造 A と凹部 3 a とのパターンがずれていて、凹部 3 a の底面がダミーゲート構造 A から露出している場合、凹部 3 a の露出部分が第 2 サイドウォール 9 -2で完全に覆われるようにすることが好ましい。

### [0134]

その後、図13(3)に示すように、サリサイドプロセス技術によってソース・ドレイン拡散層11の表面に、コバルト(Co),ニッケル(Ni),プラチナ(Pt)などの金属のシリサイド膜13を応力印加層として形成する。またこのシリサイド膜13により、ソース・ドレイン拡散層11のコンタクト抵抗を低減させる。この際、ソース・ドレイン拡散層11の表面、すなわち単結晶シリコンからなる半導体基板3の表面においては、シリサイド化の進行にともなって深さ方向にもシリサイド膜(応力印加層)13が成長する。このため、ここでは、ソース/ドレイン拡散層11の深さの範囲内において、半導体基板3の表面に対して十分な深さd1となり、かつ凹部3aの深さd2に対して[d2]<[d1]となるように、シリサイド膜(応力印加層)13を成長させることが重要である

0

50

40

[0135]

\_ \_

20

10

その後、図13(4)に示すように、ダミーゲート構造Aおよびシリサイド膜(応力印加層)13を埋め込む状態で、例えば酸化シリコンからなる層間絶縁膜15を成膜する。

#### [0136]

次いで、図14(1)に示すように、ダミーゲート構造Aにおけるダミーのゲート電極37aが露出するまで層間絶縁膜15の表面をCMP法によって研磨する。

#### [0137]

その後、図14(2)に示すように、キャップ膜50をエッチングストッパーとして、ポリシリコンまたはアモルファスシリコンからなるダミーのゲート電極37aをドライエッチングにより除去する。これにより、高誘電率材料からなるゲート絶縁膜5にダメージが入ることを抑制する。

#### [0138]

次に、図14(3)に示すように、下地に対するエッチングダメージの小さいウェットエッチングやドライエッチングによって、キャップ膜50を選択的に除去する。これにより、半導体基板3とシリサイド膜(応力印加層)13とを覆う層間絶縁膜15に、溝パターン17を形成する。溝パターン17の底面はゲート絶縁膜5で覆われた状態となるが、この溝パターン17は、凹部3aに重ねて形成される。またこの溝パターン17は、サイドウォール9(9-1,9-2)によって側壁が規定されたものになる。

## [0139]

その後、図14(4)、(5)に示す工程は、第3実施形態において図11(3)、( 4)を用いて説明したと同様に行なう。

#### [0140]

すなわち、先ず図14(4)に示すように、溝パターン17の内部を埋め込む状態でゲート電極7を形成する。この際、先ず溝パターン17の内部を埋め込む状態で、ゲート絶縁膜5を介してゲート電極材料膜を成膜する。ここでは、ゲート電極材料膜として、メタルゲート用の金属層をCVD法、PVD法、またはALD法によって成膜する。このゲート電極材料膜7は、単層または積層構造であって良く、第1実施形態において述べた各材料を用いて成膜されることとする。その後、層間絶縁膜15が露出するまで、ゲート電極材料膜をCMPによって研磨する。これにより、溝パターン17内に、ゲート絶縁膜5を介してゲート電極材料膜を残してなるゲート電極7を形成する。

## [0141]

以上の後には必要に応じて、図8にも示したように、層間絶縁膜15およびゲート電極7を覆う状態で、酸化シリコンからなる上層絶縁膜19を成膜する。次いで、上層絶縁膜19および層間絶縁膜15に、シリサイド膜(応力印加層)13に達する接続孔21を形成する。そして、これらの接続孔21を埋め込むプラグおよびこれに接続する配線23を形成する。

## [0142]

以上により図8を用いて説明したように、半導体基板3の表面を掘り下げた凹部3a内にゲート絶縁膜5を介して設けられたゲート電極7が設けられ、ゲート電極7両脇のソース/ドレイン拡散層11の表面を覆う状態で半導体基板3の表面よりも深くシリサイド膜(応力印加層)13を設けた構成の半導体装置1-3が得られる。

## [0143]

そして以上説明した製造方法であっても、図14(2)を用いて説明したように、シリサイド膜(応力印加層)13が形成された状態でダミーのゲート電極37aの除去が行われる。このため、シリサイド膜(応力印加層)13からダミーのゲート電極37a下の半導体基板3部分に印加される応力が、ダミーのゲート電極37aからの反作用により弱められることが防止される。このため、チャネル部chに対して、シリサイド膜(応力印加層)13からの応力が効果的に印加された状態となる。

#### [0144]

また、半導体基板 3 をさらに掘り下げた凹部 3 a を溝パターン 1 7 の底部としたことにより、半導体基板 3 の表面よりも深い位置がチャネル部 c h となる。これにより、このチ

10

20

30

40

20

30

40

50

ャネル部 c h には、シリサイド膜(応力印加層) 1 3 の深さ方向にわたって当該シリサイド膜(応力印加層) 1 3 間の半導体基板 3 部分に印加される応力が、集約的に印加されるようになる。したがって、第1実施形態と同様に、シリサイド膜(応力印加層) 1 3 からの応力を効果的にかつ集約させた状態でチャネル部 c h に印加させることが可能な構成の半導体装置 1-3を作製することが可能になる。

#### [0145]

また本第3実施形態の変形例の作製手順では、ゲート絶縁膜5上にキャップ膜50を設け、ダミーのゲート電極37aを除去する際のエッチングストッパーとしたことにより、予めゲート絶縁膜5を形成しておく手順であっても、ダミーのゲート電極37aを除去する際のエッチングダメージがゲート絶縁膜5に加わることが防止でき、ゲート絶縁膜5の膜質を維持できる。

#### [0146]

尚、本第3実施形態の変形例の作製手順では、キャップ膜50を除去する構成としたが、キャップ膜50はゲート電極の一部としてそのまま残すようにしても良い。この場合、キャップ膜50は、装置の構造で述べた仕事関数制御層として残しても良く、材料を適宜選択して用いれば良い。

#### [0147]

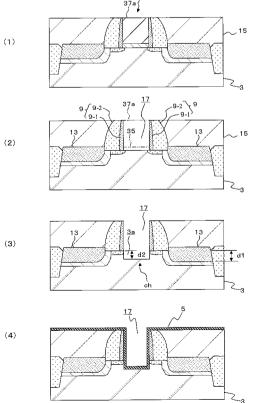

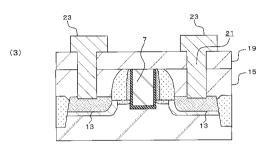

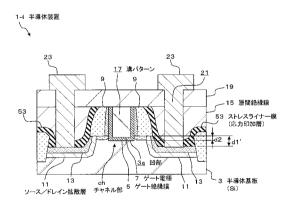

第4実施形態の半導体装置の構成

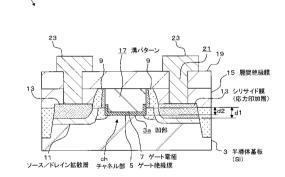

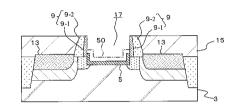

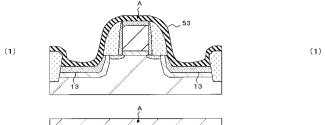

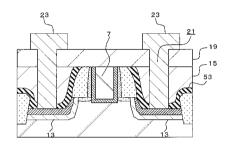

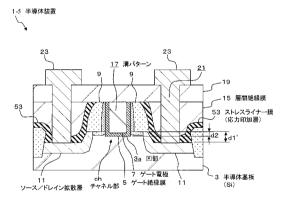

図15は、本発明を適用した第4実施形態の半導体装置1-4の要部断面図である。この図に示す半導体装置1-4は、電界効果型トランジスタ構成の半導体装置である。この図に示す半導体装置1-4が、図1を用いて説明した第1実施形態と異なるところは、第1にソース/ドレイン拡散層11およびシリサイド膜13が設けられている半導体基板3の表面部分が、リセスエッチングによって掘り込まれているところにある。また第2に、応力印加層として、ストレスライナー膜(応力印加層)53が設けられているところにある。これ以外の構成は、第1実施形態と同様である。

#### [0148]

すなわち、第1実施形態と同様に、単結晶シリコンからなる半導体基板3には、表面を掘り下げてリセスした凹部3aが設けられている。そして、半導体基板3上には、この凹部3aを埋め込む状態でゲート絶縁膜5を介してゲート電極7が設けられている。ゲート電極7の両脇には、絶縁性のサイドウォール9が設けられている。また、本第4実施形態においては、サイドウォール9が設けられたゲート電極7の両脇における半導体基板3の表面がリセスエッチングによって掘り下げられており、掘り下げられた表面側にソース/ドレイン拡散層11が設けられている。このソース/ドレイン拡散層11の表面は、シリサイド膜13で覆われている。さらに本第4実施形態においては、このシリサイド層13上からサイドウォール9の側壁にかけてが、連続してストレスライナー膜53で覆われている。

## [0149]

ここでストレスライナー膜53は、ゲート電極7下部における半導体基板3のチャネル部chに対して応力を加えるための応力印加層として設けられている。このようなストレスライナー膜53は、例えば窒化シリコンからなり、nMOS領域には半導体基板3に対して引張応力を与える材質が適用され、pMOS領域には半導体基板3に対して圧縮応力を与える材質が適用される。また、このストレスライナー膜(応力印加層)53は、半導体基板3の表面から十分な深さd1、を有して設けられている。

## [0150]

ここで、半導体基板3の表面に対する、ストレスライナー膜(応力印加層)53の深さd1 ′と、ゲート絶縁膜5およびゲート電極7が埋め込まれた凹部3aの深さ、すなわちチャネル部chの深さd2とは、[d2]<[d1 ′]であることとする。さらに、チャネル部chの深さd2の最適な深さについては、チャネル部chに印加される応力が最も高くなるように、実験的に求められることは第1実施形態と同様である。

## [0151]

尚、本第4実施形態では、ストレスライナー膜(応力印加層)53の膜厚の範囲、すなわちストレスライナー膜(応力印加層)53の表面と深さd1'の位置(裏面)との間に、凹部3aの底部が配置されることが好ましい。

#### [0152]

また本第4実施形態においても、シリサイド膜13が、ゲート電極7下部における半導体基板3のチャネル部chに対して応力を加えるための応力印加層として設けられていても良い。これにより、シリサイド膜13とストレスライナー膜53との積層構造として応力印加層が構成されることになる。

#### [0153]

この場合であっても、第1実施形態と同様に、シリサイド膜13は、例えばコバルト(Co)、ニッケル(Ni)、プラチナ(Pt)などのシリサイドからなるものであれば、半導体基板3に対して引っ張り応力を印加する応力印加層となり、nチャンネル型の電界効果型トランジスタに好ましく適用される。一方、シリサイド膜13が圧縮応力を持つものであれば、このようなシリサイド膜13を備えた半導体装置1-2は、pチャンネル型の電界効果型トランジスタに好ましく適用される。

#### [0154]

またゲート絶縁膜5およびゲート電極7は、第1実施形態と同様に、例えばダマシンゲート構造であって、絶縁性のサイドウォール9を備えている。この構造においては、例えば半導体基板3とシリサイド膜(応力印加層)13とを覆う層間絶縁膜15に、サイドウォール9によって側壁が規定された溝パターン17が設けられている。この溝パターン17の底面は、さらに半導体基板3部分を掘り下げた凹部3aの底部に設定されている。そして、この溝パターン17の内壁を覆う状態でゲート絶縁膜5が設けられ、このゲート絶縁膜5を介して溝パターン17内を埋め込む状態でゲート電極7が設けられている。

#### [ 0 1 5 5 ]

尚、このような半導体装置 1-4は、さらに必要に応じて上層絶縁膜 1 9 で覆われていても良い。この場合、この上層絶縁膜 1 9 と層間絶縁膜 1 5 とに、例えばシリサイド膜(応力印加層) 1 3 に達する接続孔 2 1 を設け、この接続孔 2 1 の底部においてシリサイド膜(応力印加層) 1 3 を介してソース / ドレイン拡散層 1 1 に接続された配線 2 3 を設けることができる。

## [0156]

またゲート絶縁膜 5 は、物理的な膜厚を維持しつつ実効膜厚を下げるために、高誘電率(High-K)絶縁膜で構成されていることが好ましいことも第 1 実施形態と同様であり、誘電率絶縁膜としては用いられる材料も同様である。

### [0157]

またゲート電極 7 の構造および構成材料も、第 1 実施形態で示したと同様の構成および 構成材料が適用される。

## [0158]

以上のような構成の半導体装置 1-4であっても、半導体基板 3 においてゲート絶縁膜 5 との界面側に設けられるチャネル部 c h が、シリサイド膜 1 3 とストレスライナー膜 5 3 との積層構造からなる応力印加層において半導体基板 3 の表面よりも深い部分に設定された状態となる。

#### [0159]

これにより、ストレスライナー膜53とシリサイド膜13とからなる応力印加層の深さ方向にわたって半導体基板3部分に印加される応力が、応力印加層の深さ方向の中間部に位置するチャネル部chに対して集約的に印加されるようになる。したがって、半導体基板3の表面とほぼ同一高さにチャネル部が形成される従来構成と比較して、応力印加層からの応力をより効果的にチャネル部chに対して印加させることができる。

#### [0160]

この結果、応力印加層を構成する材料濃度によらずにキャリア移動度の向上を図ることが可能になるため、半導体装置 1-4のさらなる高機能化を図ることが可能になる。

10

20

30

40

20

30

40

50

#### [0161]

第4実施形態の半導体装置の製造方法

図16~18は、図15を用いて説明した第4実施形態の半導体装置1-4の製造方法の特徴部を示す断面工程図である。以下、この図および第1実施形態の製造方法で用いた断面工程図に基づいて第4実施形態の製造方法を説明する。

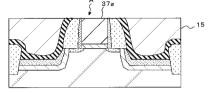

#### [0162]

先ず、第1実施形態において図2(1)~図3(2)を用いて説明した工程を同様に行なう。

#### [0163]

これにより、図16(1)に示すように、単結晶シリコンからなる半導体基板3の表面側に、素子分離31を形成し、さらにハードマスク層39、ダミーのゲート電極膜37、およびダミーのゲート絶縁膜35を、ゲート電極の形状にパターンエッチングしてダミーゲート構造Aを形成する。また、ダミーゲート構造Aの側壁に、絶縁性の第1サイドウォール9-1と、この外側の第2サイドウォール9-2とを合わせたサイドウォール9を形成する。さらに、サイドウォール9の外側に、エクステンション11eを有するソース・ドレイン拡散層11を形成する。

#### [0164]

次に、図16(2)に示すように、半導体基板3の露出表面、すなわちソース/ドレイン拡散層11の露出表面をリセスエッチングすることによって掘り下げる。この際、掘り下げたリセス表面が、以降に形成するストレスライナー膜の深さを決めるため、ここではソース/ドレイン拡散層11の深さの範囲内において、十分な深さで半導体基板3を掘り下げることが重要である。

## [0165]

その後、図16(3)に示すように、サリサイドプロセス技術によってソース・ドレイン拡散層11の表面に、コバルト(Co), ニッケル(Ni), プラチナ(Pt)などの金属のシリサイド膜13を応力印加層として形成する。またこのシリサイド膜13により、ソース・ドレイン拡散層11のコンタクト抵抗を低減させる。この際、ソース・ドレイン拡散層11のコンタクト抵抗を低減させる。この際、ソース・ドレイン拡散層11の表面、すなわち単結晶シリコンからなる半導体基板3の表面においては、シリサイド化の進行にともなってリセス表面の上方にもシリサイド膜13が成長する。このため、ここで成長したシリサイド膜13の表面が、次に形成するストレスライナー膜の深さd1,となる。

## [0166]

次に、図17(1)に示すように、ダミーゲート構造 A およびシリサイド膜(応力印加層)13を埋め込む状態で、ストレスライナー膜 5 3を成膜する。この際、 n M O S 領域には引張応力を有するストレスライナー膜 5 3を、 p M O S 領域には圧縮応力を有するストレスライナー膜 5 3を形成する。このようなストレスライナー膜 5 3形成は、例えば以下のように行う。

#### [0167]

すなわち、 n M O S 領域に形成する引張応力を有するストレスライナー膜 5 3 は、プラズマ C V D 法によって、成膜した窒化シリコン膜を用いる。このような窒化シリコン膜の成膜は、成膜雰囲気内に  $N_2$  ガス( $500 \sim 2000 \text{sccm}$ )、 N H  $_3$  ガス( $500 \sim 1500 \text{sccm}$ )、 S i H  $_4$  ガス( $50 \sim 300 \text{sccm}$ )をそれぞれの流量で供給し、基板温度 2 0 0  $\sim$  4 0 0 、成膜雰囲気内圧力 5  $\sim$  1 5 T o r r 、R F パワー 5 0  $\sim$  5 0 0 W の条件で化学反応させる。さらに成膜後、H e ガス( $10 \sim 20 \text{slm}$ )を供給し、温度 4 0 0  $\sim$  6 0 0 、圧力 5  $\sim$  1 5 T o r r 、U V ランプパワーが 1  $\sim$  1 0 k W の条件で U V 照射処理を行う。これにより、膜厚が 4 0 n m 程度で、 1 . 2 G P a 程度の引張応力を有する窒化シリコン膜がストレスライナー膜 5 3 として成膜される。尚、ストレスライナー膜 5 3 の膜厚、および引張応力は、上述した値に限定されるものではない。

#### [0168]

一方、pMOS領域に形成する圧縮応力を有するストレスライナー膜53についても、

プラズマ C V D 法によって、成膜した窒化シリコン膜が用いられる。このような窒化シリコン膜の成膜は、成膜雰囲気内に  $H_2$ ガス( $1000 \sim 5000 \text{sccm}$ )、 $N_2$ ガス( $500 \sim 2500 \text{sccm}$ )、A r ガス( $1000 \sim 5000 \text{sccm}$ )、N  $H_3$ ガス( $50 \sim 200 \text{sccm}$ )、F リメチルシランガス( $10 \sim 50 \text{sccm}$ )をそれぞれの流量で供給し、基板温度 4 0 0  $\sim$  6 0 0 、成膜雰囲気内圧力  $1 \sim 5$  T o r r 、R F パワー 5 0  $\sim$  5 0 0 W の条件で化学反応させて行われる。これにより、膜厚が 4 0 n m 程度で、 1 . 2 G P a 程度の圧縮応力を有する窒化シリコン膜がストレスライナー膜 5 3 として成膜される。尚、ストレスライナー膜 5 3 の膜厚、および圧縮応力は、上述した値に限定されるものではない。

#### [0169]

次に、図17(2)に示すように、ダミーゲート構造 A を埋め込む状態で、例えば酸化シリコンからなる層間絶縁膜15を成膜する。

#### [0170]

次いで、図17(3)に示すように、ダミーゲート構造 A におけるダミーのゲート電極 37aが露出するまで層間絶縁膜15の表面を C M P 法によって研磨する。

#### [0171]

次に、図17(4)に示すように、ポリシリコンまたはアモルファスシリコンからなるダミーのゲート電極37aをドライエッチングにより除去し、さらに酸化シリコンからなるダミーのゲート絶縁膜35をウェットエッチングにより除去する。これにより、半導体基板3を覆う層間絶縁膜15に、ダミーゲート構造Aを除去してなる溝パターン17を形成し、さらに、溝パターン17の底部における半導体基板3の露出面を掘り下げるリセスエッチングを行う。

#### [0172]

この際、半導体基板3の表面に対して、ストレスライナー膜(応力印加層)53の深さd1 'とした場合、凹部3aの深さd2(すなわちチャネル深さd2)が、[d2]<[d1']となるようにする。尚、この範囲においての凹部3aのチャネル深さd2の最適値については、ここで形成するMOSトランジスタ(電界効果トランジスタ)のチャネル部に印加される応力が最も高くなるように、実験的に求められることとする。

#### [0173]

またここでは、ストレスライナー膜(応力印加層)53の膜厚の範囲、すなわちストレスライナー膜(応力印加層)53の表面と深さd1'の位置(裏面)との間に、凹部3aの底部が位置するようにリセスエッチングを行なうことが好ましい。

## [0174]

次に、図18(1)に示すように、溝パターン17の内部を埋め込む状態で、ゲート絶縁膜5を介してゲート電極材料膜7aを成膜する。ここでは、CVD法やALD法などにより、上述した高誘電率材料からなるゲート絶縁膜5を成膜することが好ましい。その後、溝パターン17の内部を埋め込む状態で、ゲート絶縁膜5を介してゲート電極材料膜7aを成膜する。ここでは、ゲート電極材料膜7aとして、メタルゲート用の金属層をCVD法、PVD法、またはALD法によって成膜する。このゲート電極材料膜7aは、単層または積層構造であって良く、第1実施形態の装置の構成において述べた各材料を用いて成膜されることとする。

## [0175]

次に、図18(2)に示すように、層間絶縁膜15が露出するまで、ゲート電極材料膜 7aとゲート絶縁膜5をCMPによって研磨する。これにより、溝パターン17内に、ゲート絶縁膜5を介してゲート電極材料膜7aを残してなるゲート電極7を形成する。

#### [0176]

以上の後には必要に応じて、図18(3)に示すように、層間絶縁膜15およびゲート電極7を覆う状態で、酸化シリコンからなる上層絶縁膜19を成膜する。次いで、上層絶縁膜19、層間絶縁膜15、およびストレスライナー膜53に、シリサイド膜13に達する接続孔21を形成する。そして、これらの接続孔21を埋め込むプラグおよびこれに接続する配線23を形成する。

10

20

30

20

30

40

50

### [0177]

以上により図15を用いて説明したように、半導体基板3の表面を掘り下げた凹部3a内にゲート絶縁膜5を介して設けられたゲート電極7が設けられ、ゲート電極7両脇のソース/ドレイン拡散層11上のシリサイド膜13表面を覆う状態で、半導体基板3の表面よりも深くストレスライナー膜(応力印加層)53を設けた構成の半導体装置1-4が得られる。

#### [ 0 1 7 8 ]

そして以上説明した製造方法によれば、図17(4)を用いて説明したように、ストレスライナー膜(応力印加層)53が形成された状態でダミーゲート構造Aを除去することにより、ストレスライナー膜(応力印加層)53からダミーゲート構造A下の半導体基板3部分に印加される応力が、ダミーのゲート電極37aからの反作用により弱められることが防止される。このため、チャネル部chに対して、ストレスライナー膜(応力印加層)53からの応力が効果的に印加された状態となる。

### [0179]

そして、ダミーゲート構造 A を除去した溝パターン 1 7 の底部の半導体基板 3 をさらに掘り下げることにより、半導体基板 3 の表面よりも深い位置がチャネル部 c h となる。これにより、このチャネル部 c h には、ストレスライナー膜(応力印加層) 5 3 の深さ方向にわたって当該ストレスライナー膜(応力印加層) 5 3 間の半導体基板 3 部分に印加される応力が、集約的に印加されるようになる。したがって、ストレスライナー膜(応力印加層) 5 3 からの応力を効果的にかつ集約させた状態でチャネル部 c h に印加させることが可能な構成の半導体装置 1 -4を作製することが可能になる。

#### [0180]

尚、上述した第4実施形態の製造方法では、溝パターン17を形成してその底部の半導体基板3をリセスエッチングによって掘り下げて、半導体基板3に凹部3aを形成する手順を説明した。しかしながら、本第4実施形態のようにストレスライナー膜53を応力印加層とした半導体装置の製造にも、第3実施形態を適用し、予め半導体基板3をリセスエッチングして凹部3aを形成してゲート絶縁膜5を形成した後に、溝パターン17を形成する手順を適用しても良い。尚この場合、第3実施形態において図10(2)を用いて説明したようにソース/ドレイン拡散層11を形成した後、ソース/ドレイン拡散層11の表面を掘り下げ、この上部に絶縁性のストレスライナー膜からなる前記応力印加層を形成する手順とする。

## [0181]

このような手順を適用することにより、溝パターン17の側壁上部にゲート絶縁膜が形成されない構成の半導体装置の作製が可能となる。これにより、第3実施形態で説明したように、高誘電率材料からなるゲート絶縁膜5がゲート電極7と配線23との間に存在せず、ゲート電極7・配線23間の寄生容量による素子性能の低下を防止できると言った効果を得ることが可能である。

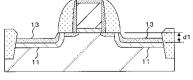

#### [0182]

第5実施形態の半導体装置の構成

図19は、本発明を適用した第5実施形態の半導体装置1-5の要部断面図である。この図に示す半導体装置1-5が、図15に示した第4実施形態の半導体装置と異なるところは、ソース/ドレイン拡散層11の表面にシリサイド膜(13)を設けておらず、ソース/ドレイン拡散層11の上面に直接ストレスライナー膜53を設けているところにある。これ以外の構成は、第4実施形態と同様である。

#### [0183]

ここでストレスライナー膜53は、第4実施形態と同様であり、ゲート電極7下部における半導体基板3のチャネル部chに対して応力を加えるための応力印加層として設けられている。このようなストレスライナー膜53は、例えば窒化シリコンからなり、nMOS領域には半導体基板3に対して引張応力を与える材質が適用され、pMOS領域には半導体基板3に対して圧縮応力を与える材質が適用される。また、このストレスライナー膜

(応力印加層) 53は、半導体基板3の表面から十分な深さは1'を有して設けられてい る。

#### [0184]

また半導体基板3の表面に対する、ストレスライナー膜(応力印加層)53の深さd1 'と、ゲート絶縁膜5およびゲート電極7が埋め込まれた凹部3aの深さ、すなわちチャ ネル部chの深さd2とは、「d2]<「d1']であることは、第4実施形態と同様で ある。さらに、ストレスライナー膜(応力印加層)53の膜厚の範囲、すなわちストレス ライナー膜(応力印加層)53の表面と深さd1'の位置(裏面)との間に、凹部3aの 底部が配置されることが好ましいことも、第4実施形態と同様である。

#### [0185]

尚、以上のような第5実施形態の半導体装置1-5の製造手順は、第4実施形態で説明し た製造手順においてシリサイド膜(13)の形成工程を省けば良い。

このような構成の半導体装置1-5であっても、第4実施形態と同様の効果を得ることが できる。またさらに、nMOS領域とpMOS領域とに、例えば一般的に用いられている コバルト(Co)、ニッケル(Ni),プラチナ(Pt)などのシリサイド膜を設けた場 合、これらのシリサイド膜13は、半導体基板3に対して引張応力を印加する。このため 、pチャンネル型の電界効果型トランジスタに対しては、ストレスライナー膜から効果的 に圧縮応力を印加することが困難である。したがって、シリサイド膜を除去した本第5実 施形態の構成っであれば、pMOS領域にも、ストレスライナー膜53から効果的に圧縮 応力を印加することが可能になる。

【図面の簡単な説明】

## [0187]

- 【図1】第1実施形態の半導体装置を示す断面図である。

- 【図2】第1実施形態の製造方法の第1例を示す断面工程図(その1)である。

- 【図3】第1実施形態の製造方法を第1例示す断面工程図(その2)である。

- 【図4】第1実施形態の製造方法を第1例示す断面工程図(その3)である。

- 【図5】第1実施形態の製造方法を第1例示す断面工程図(その4)である。

- 【図6】第2実施形態の半導体装置を示す断面図である。

- 【図7】第2実施形態の製造方法の特徴部を示す断面工程図である。

- 【図8】第3実施形態の半導体装置を示す断面図である。

- 【図9】第3実施形態の製造方法を示す断面工程図(その1)である。

- 【図10】第3実施形態の製造方法を示す断面工程図(その2)である。

- 【図11】第3実施形態の製造方法を示す断面工程図(その3)である。

- 【図12】第3実施形態の製造方法の変形例を示す断面工程図(その1)である。

- 【図13】第3実施形態の製造方法の変形例を示す断面工程図(その2)である。

- 【図14】第3実施形態の製造方法の変形例を示す断面工程図(その3)である。

- 【図15】第4実施形態の半導体装置を示す断面図である。

- 【図16】第4実施形態の製造方法の第1例を示す断面工程図(その1)である。

- 【図17】第4実施形態の製造方法を第1例示す断面工程図(その2)である。

- 【図18】第4実施形態の製造方法を第1例示す断面工程図(その3)である。

- 【図19】第5実施形態の半導体装置を示す断面図である。

- 【図20】従来の半導体装置の一例を示す断面図である。

## 【符号の説明】

#### [0188]

1-1, 1-2, 1-3, 1-4, 1-5...半導体装置、3...半導体基板、3a...凹部、5...ゲー ト絶縁膜、 7 ... ゲート電極、 9 ... サイドウォール 1 1 ... ソース / ドレイン拡散層、 1 3 ... シリサイド膜(応力印加層)、15...層間絶縁膜、17...溝パターン、37a...ダミーの ゲート電極、50…キャップ膜(仕事関数制御層)、53…ストレスライナー膜、ch… チャネル部

10

20

30

40

## 【図1】

【図3】

【図4】

## 【図5】

【図6】

# 【図7】

【図8】

半導体装置

## 【図9】

## 【図10】

## 【図11】

## 【図13】

## 【図14】

(2)

(3)

## 【図15】

【図16】

## 【図17】

(2)

(3)

## 【図18】

(2)

(3)

## 【図19】

## 【図20】

## フロントページの続き

## (56)参考文献 特開2005-353675(JP,A)

特開2005-057301(JP,A)

特開2007-081330(JP,A)

国際公開第2008/072573(WO,A1)

特開2004-140059(JP,A)

特開平03-227571(JP,A)

特開2007-103654(JP,A)

特開2009-152394(JP,A)

特開2007-294680(JP,A)

国際公開第2006/081012(WO,A1)

特開2008-193060(JP,A)

J.Wang et al., Novel Channel-Stress Enhancement Technology with eSiGe S/D and Recessed Channel on Damascene Gate Process, 2007 Symposium on VLSI Technology Digest of Technical Papers, 2 0 0 7  $\pm$ , pp.46-47

## (58)調査した分野(Int.CI., DB名)

H01L 29/78

H01L 21/336

H01L 21/28