### (19) **日本国特許庁(JP)**

# (12) 特 許 公 報(B2)

(11)特許番号

特許第5594294号 (P5594294)

(45) 発行日 平成26年9月24日(2014.9.24)

(24) 登録日 平成26年8月15日(2014.8.15)

| (51) Int.Cl. |         |           | F I  |       |      |  |

|--------------|---------|-----------|------|-------|------|--|

| HO1L         | 21/82   | (2006.01) | HO1L | 21/82 | В    |  |

| HO1L         | 21/822  | (2006.01) | HO1L | 27/04 | A    |  |

| H01L .       | 27/04   | (2006.01) | HO1L | 27/08 | 102D |  |

| HO1L .       | 27/088  | (2006.01) |      |       |      |  |

| HO1L .       | 21/8234 | (2006.01) |      |       |      |  |

請求項の数 8 (全 16 頁)

(21) 出願番号 特願2011-547278 (P2011-547278) (86) (22) 出願日 平成22年12月14日 (2010.12.14)

(86) 国際出願番号 PCT/JP2010/007255 (87) 国際公開番号 W02011/077664

(87) 国際公開日 平成23年6月30日 (2011.6.30) 審査請求日 平成25年9月19日 (2013.9.19) (31) 優先権主張番号 特願2009-294231 (P2009-294231)

(32) 優先日 平成21年12月25日 (2009.12.25)

(33) 優先権主張国 日本国(JP)

||(73)特許権者 000005821

パナソニック株式会社

大阪府門真市大字門真1006番地

||(74)代理人 100104732

弁理士 徳田 佳昭

(74)代理人 100120156

弁理士 藤井 兼太郎

||(72)発明者 田丸 雅規

大阪府門真市大字門真1006番地 パナ

ソニック株式会社内

(72) 発明者 中西 和幸

大阪府門真市大字門真1006番地 パナ

ソニック株式会社内

最終頁に続く

# (54) 【発明の名称】半導体装置

### (57)【特許請求の範囲】

# 【請求項1】

第1方向に延びる複数のゲートが前記第1方向に直交する第2方向に並べて配置されているセル列が、複数個、前記第1方向に並べて配置されており、

前記複数のセル列は、それぞれ、

前記ゲートの下に形成されており、前記第2方向にそれぞれ延びている第1導電型ウエル領域および第2導電型ウエル領域を備え、

前記複数のセル列のうちの1つである第1のセル列は、

前記第1導電型ウエル領域において、前記第1導電型ウエル領域と同一導電型の不純物が注入されてなる第1のウエル電位給電領域と、

前記第1のウエル電位給電領域の前記第2方向における両側にそれぞれ配置された、第1および第2の隣接ゲートと、

前記第1の隣接ゲートに、前記第1のウエル電位給電領域の反対側に隣接して配置された第3の隣接ゲートと、

前記第2の隣接ゲートに、前記第1のウエル電位給電領域の反対側に隣接して配置された第4の隣接ゲートとを備え、

前記第1~第4の隣接ゲートは、前記第2方向において同一ピッチで配置されており、かつ、

前記複数のセル列のうちの、前記第1のセル列に前記第1方向において隣接する第1の隣接セル列は、前記第1~第4の隣接ゲートに前記第1方向においてそれぞれ対向してい

る4本のゲートを、有し、

前記第1の隣接ゲートと前記第3の隣接ゲートとの間に、前記第1導電型ウエル領域と同一導電型の不純物が注入されてなる第2のウエル電位給電領域が形成されていることを特徴とする半導体装置。

## 【請求項2】

請求項1記載の半導体装置において、

前記第1および第2の隣接ゲートのうち少なくともいずれか一方は、前記第1の隣接セル列における、当該隣接ゲートと対向しているゲートと、一体になるように接続されている

ことを特徴とする半導体装置。

10

20

# 【請求項3】

請求項1または2記載の半導体装置において、

前記第1および第2の隣接ゲートは、ダミーゲートである

ことを特徴とする半導体装置。

## 【請求項4】

請求項1記載の半導体装置において、

前記第1および第2のウエル電位給電領域は、一体に形成されている

ことを特徴とする半導体装置。

#### 【請求項5】

請求項1または4記載の半導体装置において、

前記第1、第2および第3の隣接ゲートは、ダミーゲートである

ことを特徴とする半導体装置。

### 【請求項6】

請求項1記載の半導体装置において、

前記第1のセル列における前記第1導電型ウエル領域と、前記第1の隣接セル列における前記第1導電型ウエル領域とは、前記第1方向において隣接しており、

前記第1の隣接セル列は、

前記第1導電型ウエル領域において、前記第1導電型ウエル領域と同一導電型の不純物が注入されてなる第3のウエル電位給電領域を備えている

ことを特徴とする半導体装置。

30

### 【請求項7】

請求項1記載の半導体装置において、

前記第1~第4の隣接ゲートは、前記第1導電型ウエル領域と前記第2導電型ウエル領域との境界を跨いで延びている

ことを特徴とする半導体装置。

## 【請求項8】

請求項1記載の半導体装置において、

前記第1~第4の隣接ゲートは、前記第1導電型ウエル領域と前記

第2導電型ウエル領域との境界において分割されている

ことを特徴とする半導体装置。

40

#### 【発明の詳細な説明】

## 【技術分野】

# [0001]

本発明は、ウエル領域に給電するためのウエル電位給電領域が設けられた半導体装置に関するものである。

#### 【背景技術】

## [0002]

従来の半導体装置では、ウエル電位を制御することを目的として、あるいは、ラッチアップを防止することを目的として、活性トランジスタの近傍に、ウエル領域に給電するためのウエル電位給電領域が設けられている。なお、「活性トランジスタ」とは、トランジ

スタの動作特性を利用して、回路の所望の機能に寄与するトランジスタのことをいう。

#### [00003]

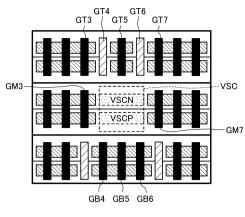

図12はウエル電位給電領域が設けられた半導体装置の従来のレイアウトの一例を示す図である。図12の構成では、図面横方向において標準セルが複数配置された標準セル列が、図面縦方向に並べて配置されている。そして中央の標準セル列に、ウエル電位給電セルVSCが挿入されている。VSCNはN型の不純物が注入されており、N型ウエルにウエル電位を給電するウエル電位給電領域(TAP領域)であり、VSCPはP型の不純物が注入されており、P型ウエルにウエル電位を給電するウエル電位給電領域である。

【先行技術文献】

【特許文献】

[0004]

【特許文献 1 】特開 2 0 0 8 - 2 3 5 3 5 0 号公報

【特許文献 2 】特開 2 0 0 7 - 1 2 8 5 5 号公報

【特許文献3】特開2001-148464号公報

【特許文献4】特開2009-32961号公報

【発明の概要】

【発明が解決しようとする課題】

[0005]

最近の半導体装置では、微細化の進展により、ゲートを露光する際に、回折光による光近接効果の影響が大きくなっている。このため、周辺のゲートパターンの状況に応じて、 光近接効果の影響が大きく異なってしまい、ゲート長のばらつきが生じるという問題が起 こっている。

[0006]

この問題に対処するためには、対象ゲートの周辺のゲートパターンの形状規則性を保つことが必要である。そして、対象ゲートの左右方向に並ぶゲートパターンだけでなく、その上下方向に並ぶゲートパターンの形状規則性に関しても、これを維持する必要がある。

[0007]

しかしながら、従来では、ウエル電位給電セルを配置した場合には、対象ゲートの左右方向および上下方向に並ぶゲートパターンの形状規則性を維持することができなくなる。例えば図12のレイアウトでは、ウエル電位給電セルVSCの挿入により、上の標準セル列におけるゲート電極GT5およびダミーゲートGT4,GT6に関しては、その下側にゲートが隣接配置されておらず、また下の標準セル列におけるゲート電極GB4,GB5,GB6に関しては、その上側にゲートが隣接配置されていない。また、ゲート電極GM3,GM7に関しては、それぞれ右側および左側にゲートが隣接配置されていない。このように、ウエル電位給電セルVSCを挿入したことによって、その周辺のゲートパターンの形状規則性が維持されなくなってしまう。

[0008]

よって、従来の半導体装置では、ゲートパターンの形状規則性を維持するために、活性トランジスタを有する標準セルを、ウエル電位給電セルVSCの近傍を避けて配置する必要があった。ところがこの場合には、半導体装置のレイアウト面積の増大を招くことになり、好ましくない。

[0009]

前記の問題に鑑み、本発明は、ウエル電位給電領域を有する半導体装置を、光近接効果によるゲート長のばらつきを確実に抑制し、かつ、レイアウト面積を増大させることなく、実現することを目的とする。

【課題を解決するための手段】

[0010]

本発明の一態様では、第1方向に延びる複数のゲートが前記第1方向に直交する第2方向に並べて配置されているセル列が、複数個、前記第1方向に並べて配置されている半導体装置において、

10

20

30

40

前記複数のセル列は、それぞれ、

前記ゲートの下に形成されており、前記第2方向にそれぞれ延びている第1導電型ウエル領域および第2導電型ウエル領域を備え、

前記複数のセル列のうちの1つである第1のセル列は、

前記第1導電型ウエル領域において、前記第1導電型ウエル領域と同一導電型の不純物が注入されてなる第1のウエル電位給電領域と、

前記第1のウエル電位給電領域の前記第2方向における両側にそれぞれ配置された、第1および第2の隣接ゲートと、

前記第1の隣接ゲートに、前記第1のウエル電位給電領域の反対側に隣接して配置された第3の隣接ゲートと、

前記第2の隣接ゲートに、前記第1のウエル電位給電領域の反対側に隣接して配置された第4の隣接ゲートとを備え、

前記第1~第4の隣接ゲートは、前記第2方向において同一ピッチで配置されており、かつ、

前記複数のセル列のうちの、前記第1のセル列に前記第1方向において隣接する第1の 隣接セル列は、前記第1~第4の隣接ゲートに前記第1方向においてそれぞれ対向してい る4本のゲートを、有している。

## [0011]

この態様によると、第1のセル列の第1導電型ウエル領域において、第1のウエル電位 給電領域が設けられている。そして、第1のウエル電位給電領域の第2方向における両側 に配置された第1および第2の隣接ゲート、およびそのさらに両側に配置された第3およ び第4の隣接ゲートは、第2方向において同一ピッチで配置されている。さらに、第1の セル列に第1方向において隣接する第1の隣接セル列は、第1~第4の隣接ゲートに第1 方向においてそれぞれ対向している4本のゲートを、有している。すなわち、第1のウエ ル電位給電領域の周辺のゲートパターンに関して、形状規則性が維持されている。したが って、ゲートパターンに応じて異なる光近接効果の影響を回避することができるので、ゲ ート長のばらつきを確実に抑制しつつ、ウエル電位給電領域の設置によるレイアウト面積 の増大を抑制することができる。

## [0012]

本発明の他の態様では、第1方向に延びる複数のゲートが前記第1方向に直交する第2 方向に並べて配置されているセル列が、複数個、前記第1方向に並べて配置されている半 導体装置において、

前記複数のセル列は、それぞれ、

前記ゲートの下に形成されており、前記第2方向にそれぞれ延びている第1導電型ウエル領域および第2導電型ウエル領域を備え、

前記複数のセル列のうちの1つである第1のセル列は、

前記第1導電型ウエル領域において、前記第1導電型ウエル領域と同一導電型の不純物が注入されてなる第1のウエル電位給電領域と、

前記第1のウエル電位給電領域の上に配置された第1のゲートとを備えている。

# [0013]

この態様によると、第1のセル列の第1導電型ウエル領域において、第1のウエル電位給電領域が設けられている。そして、この第1のウエル電位給電領域の上に、第1のゲートが配置されている。この構造によって、この第1のゲートを含む複数のゲートに関して、第2方向において同一ピッチで配置することが可能になり、また、第1方向において他のゲートを対向させることが可能になる。すなわち、第1のウエル電位給電領域の周辺のゲートパターンに関して、形状規則性を維持することができる。したがって、ゲートパターンに応じて異なる光近接効果の影響を回避することができるので、ゲート長のばらつきを確実に抑制しつつ、ウエル電位給電領域の設置によるレイアウト面積の増大を抑制することができる。

## 【発明の効果】

10

20

30

#### [0014]

本発明によると、ウエル電位給電領域を配置した場合でも、その周辺のゲートパターンの形状規則性を維持することができるので、ゲート長のばらつきを確実に抑制しつつ、ウエル電位給電領域の設置によるレイアウト面積の増大を抑制することができる。

【図面の簡単な説明】

[0015]

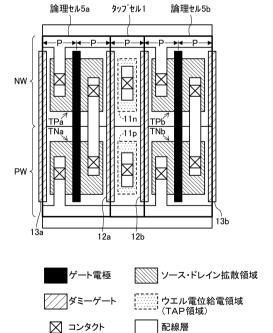

- 【図1】第1の実施形態に係るタップセルのレイアウト構造の例である。

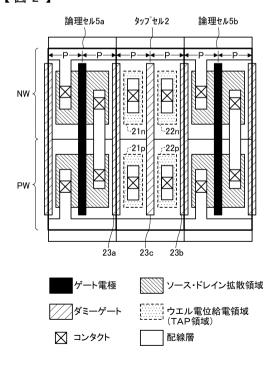

- 【図2】第1の実施形態に係るタップセルのレイアウト構造の他の例である。

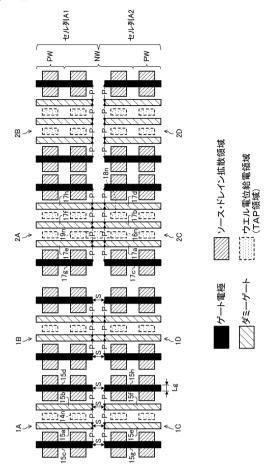

- 【図3】図1および図2のタップセルを用いた半導体装置のレイアウト構成の一例である

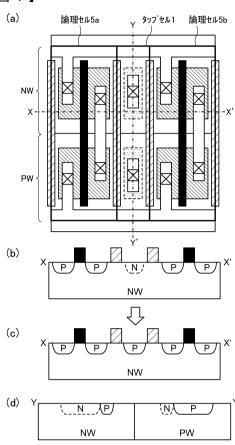

【図4】図1のタップセルの断面構造を示す図である。

- 【図5】図2のタップセルの断面構造を示す図である。

- 【図6】第2の実施形態に係るタップセルのレイアウト構造の例である。

- 【図7】図6に示すトランジスタ型のウエル電位給電領域を用いた半導体装置のレイアウト構成の一例である。

- 【図8】半導体装置のレイアウト構成の他の例である。

- 【図9】半導体装置のレイアウト構成の他の例である。

- 【図10】半導体装置のレイアウト構成の他の例である。

- 【図11】半導体装置のレイアウト構成の他の例である。

- 【図12】従来の半導体装置のレイアウトの一例である。

【発明を実施するための形態】

[0016]

以下、本発明の実施形態を図面に基づいて詳細に説明する。なお、本願明細書において、「ダミーゲート」とは、トランジスタを構成しないゲートのことをいう。また、活性トランジスタのゲートとして機能するゲートのことを、「ゲート電極」という。さらに、単に「ゲート」という場合は、「ダミーゲート」と「ゲート電極」の両方を含み得るものとする。

[0017]

(第1の実施形態)

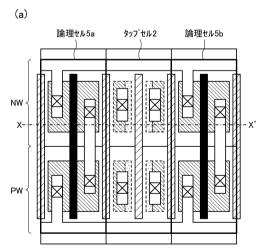

図1は第1の実施形態に係るタップセルのレイアウト構造の例を示す図である。ここで、「タップセル」とは、ウエルへの電位給電領域を有するセルのことをいう。図1のレイアウト構造では、インバータを構成する論理セル5a,5bの間にタップセル1が隣接配置されている。

[0018]

図1において、タップセル1は、N型ウエル領域NWに形成されたN型不純物拡散領域11nと、P型ウエル領域PWに形成されたP型不純物拡散領域11pとを有している。N型ウエル領域NWには、N型不純物拡散領域11nからコンタクトおよび配線を介して所望のウエル電位が給電される。P型ウエル領域PWには、P型不純物拡散領域11pからコンタクトおよび配線を介して所望のウエル電位が給電される。すなわち、N型不純物拡散領域11nとP型不純物拡散領域11pは、ウエル電位給電領域(TAP領域)を構成する。

[0019]

論理セル 5a , 5b は、それぞれ、N 型ウエル領域 N W に形成された P M O S トランジスタ T P a , T P b と P 型ウエル領域 P W に形成された N M O S トランジスタ T N a , T N b とを備えている。

[0020]

そして、タップセル 1 と論理セル 5 a , 5 b との間には、それぞれ、ダミーゲート 1 2 a , 1 2 b が配置されている。また、論理セル 5 a , 5 b のタップセル 1 とは反対側の境界にも、ダミーゲート 1 3 a , 1 3 b がそれぞれ配置されている。

[0021]

10

20

30

このようにダミーゲートを配置したことによって、図1に示すように、縦方向に延びる複数のゲート(ダミーゲートを含む)が、横方向においてほぼ一定ピッチPでレイアウトされる。すなわち、図1のようなタップセル1のレイアウト構造を採用することによって、論理セル5 a , 5 b の間にタップセル1を配置した場合でも、ゲートパターンの形状規則性を保つことができる。

#### [0022]

図2は第1の実施形態に係るタップセルのレイアウト構造の他の例を示す図である。図2のレイアウト構造では、インバータを構成する論理セル5a,5bの間にタップセル2が隣接配置されている。論理セル5a,5bのレイアウト構造は、図1と同様である。

# [0023]

図2において、タップセル2は、N型ウエル領域NWに形成された2個のN型不純物拡散領域21 n,22 nと、P型ウエル領域PWに形成された2個のP型不純物拡散領域21 p,22 pとを有している。N型ウエル領域NWには、N型不純物拡散領域21 n,2 nからコンタクトおよび配線を介して所望のウエル電位が給電される。P型ウエル領域PWには、P型不純物拡散領域21 p,22 pからコンタクトおよび配線を介して所望のウエル電位が給電される。すなわち、2個のN型不純物拡散領域21 n,22 nと2個のP型不純物拡散領域21 p,22 pは、ウエル電位給電領域(TAP領域)を構成する。

# [0024]

そして、タップセル 2 と論理セル 5 a , 5 b との間には、それぞれ、ダミーゲート 2 3 a , 2 3 b が配置されている。さらに、N型不純物拡散領域 2 1 n , 2 2 n の間から P 型不純物拡散領域 2 1 p , 2 2 p の間にわたって、ダミーゲート 2 3 c が配置されている。

#### [0025]

このようにダミーゲートを配置したことによって、図2に示すように、縦方向に延びる複数のゲート(ダミーゲートを含む)が、横方向においてほぼ一定のピッチPでレイアウトされる。すなわち、図2のようなタップセル2のレイアウト構造を採用することによって、論理セル5 a , 5 b の間にタップセル2を配置した場合でも、ゲートパターンの形状規則性を保つことができる。

#### [0026]

図3は図1および図2に示すタップセルを用いた半導体装置のレイアウト構成の一例である。図3のレイアウトでは、縦方向(第1方向)に延びる複数のゲートが横方向(第2方向)に並べて配置されているセル列 A 1 , A 2 が、縦方向に並べて配置されている。セル列 A 1 , A 2 では、それぞれ、横方向に延びている P 型ウエル領域 P W および N 型ウエル領域 N W がゲートの下に形成されている。なお、セル列 A 2 では、 P 型ウエル領域 P W と N 型ウエル領域 N W が フリップされており、セル列 A 1 , A 2 の N 型ウエル領域 N W は 隣接している。

## [0027]

図3のレイアウト構成では、図1に示したタップセル1と同一構成からなるタップセル1A,1B,1C,1Dと、図2に示したタップセル2と同一構成からなるタップセル2A,2B,2C,2Dとが配置されている。

#### [0028]

ここで、セル列A1に配置されたタップセル1AにおけるN型不純物拡散領域14nに着目する。N型不純物拡散領域14nは、セル列A1のN型ウエル領域NWにウエル電位を給電するウエル電位給電領域として機能する。そして、第1のウエル電位給電領域としてのN型不純物拡散領域14nの横方向における両側に、第1および第2の隣接ゲートとしてのダミーゲート15aの、N型不純物拡散領域14nの反対側には、第3の隣接ゲートとしてのゲート電極15cが隣接して配置されており、ダミーゲート15bの、N型不純物拡散領域14nの反対側には、第4の隣接ゲートとしてのゲート電極15dが隣接して配置されている。

### [0029]

そして、ゲート電極15c、ダミーゲート15a,15b、ゲート電極15dは、横方

10

20

30

40

向において同一ピッチ P で配置されている。さらに、第1の隣接セル列としてのセル列 A 2 は、セル列 A 1 のゲート電極 1 5 c、ダミーゲート 1 5 a , 1 5 b、ゲート電極 1 5 d に縦方向においてそれぞれ対向(間隔 S )している、4 本のゲート 1 5 e , 1 5 f , 1 5 g , 1 5 hを有している。すなわち、着目した N 型不純物拡散領域 1 4 n に関して、横方向に 2 本ずつ隣接する計 4 本のゲートのパターンが、形状規則性を有している。

#### [0030]

また、セル列A2に配置されたタップセル2CにおけるN型不純物拡散領域16nに着目する。N型不純物拡散領域16nは、セル列A2のN型ウエル領域NWにウエル電位を給電するウエル電位給電領域として機能する。そして、第1のウエル電位給電領域としてのN型不純物拡散領域16nの横方向における両側に、第1および第2の隣接ゲートとしてのダミーゲート17a,17bがそれぞれ配置されている。ダミーゲート17aの、N型不純物拡散領域16nの反対側には、第3の隣接ゲートとしてのゲート電極17cが隣接して配置されており、ダミーゲート17bの、N型不純物拡散領域16nの反対側には、第4の隣接ゲートとしてのダミーゲート17dが隣接して配置されている。さらに、ダミーゲート17bとダミーゲート17dとの間には、第2のウエル電位給電領域としてのN型不純物拡散領域18nが形成されている。

### [0031]

そして、ゲート電極 1 7 c、ダミーゲート 1 7 a , 1 7 b , 1 7 d は、横方向において同一ピッチ P で配置されている。さらに、第 1 の隣接セル列としてのセル列 A 1 は、セル列 A 2 のゲート電極 1 7 c、ダミーゲート 1 7 a , 1 7 b , 1 7 d に縦方向においてそれぞれ対向している、4 本のゲート 1 7 e , 1 7 f , 1 7 g , 1 7 h を有している。すなわち、着目した N 型不純物拡散領域 1 6 n に関して、横方向に 2 本ずつ隣接する計 4 本のゲートのパターンが、形状規則性を有している。

#### [0032]

このようなレイアウトによって、ウエル電位給電領域を配置した場合でもその周辺のゲートパターンの形状規則性を維持することができるため、ゲートパターンに応じて異なる光近接効果の影響を回避することができる。したがって、ゲート長のばらつきを確実に抑制しつつ、ウエル電位給電領域の設置によるレイアウト面積の増大を抑制することができる。

## [0033]

なお、ここでは、N型ウエル領域にウエル電位を給電するN型不純物拡散領域に着目して説明を行ったが、P型ウエル領域にウエル電位を給電するP型不純物拡散領域に関しても、同様の構成を実現することができ、同様の作用効果が得られる。

#### [0034]

ここで、「ゲートが同一ピッチPで配置されている」とは、ピッチが完全に同一であることを意味するものでは必ずしもなく、ほぼ同一のピッチで配置されていればよく、ある程度までの変動を許容するものとする。例えば、ピッチPの半分(= P/2)程度までの変動は許容するものとする。

## [0035]

また、ウエル電位給電領域に隣接する4本のゲートと、これらに対向する4本のゲートとは、ほぼ同じ間隔をもって配置されているのが好ましい。なお、タップセル2Cにおけるダミーゲート17a,17b,17dのように、対向しているゲートと、一体となるように接続されていてもかまわない。

# [0036]

また、ウエル電位給電領域は、隣接するセル列における同一導電型のウエル電位給電領域と、一体に形成されていてもかまわない。例えば、タップセル2CにおけるN型不純物拡散領域16nは、一点鎖線で示したように、セル列A1のタップセル2Aにおける第3のウエル電位給電領域としてのN型不純物拡散領域19nと、一体に形成されていてもよい。このように形成することによって、ウエル電位給電領域を形成するための不純物注入がより容易になる。

10

20

30

40

#### [0037]

なお、図1~図3の構成において、ゲートが同一ピッチPで配置されていることに加えて、各ゲートの横方向の幅が同一であることが、好ましい。

#### [0038]

また、図1~図3では、ウエル電位給電領域の縦方向のサイズは、隣接するトランジスタのゲート幅(拡散領域の幅)と同じであるように図示しているが、これに限られるものではなく、トランジスタのゲート幅とは異なるようにしてもよい。

### [0039]

また、図1~図3では、各ゲートは、N型ウエル領域NWとP型ウエル領域PWとの境界を跨いで延びているが、この境界で分割して配置してもよい。さらには、N型ウエル領域NW内、またはP型ウエル領域PW内においても、近接効果による影響を考慮した上で、ゲートを分割して配置してもかまわない。

### [0040]

また、ウエル電位給電領域は、ゲート同士の間に挟まれて配置されていればよく、縦方向および横方向においてそのサイズは特には制限されない。

#### [0041]

図4(a)は図1と同一の平面図、図4(b),(c)は図4(a)の線X-X<sup>\*</sup>における断面構造を示す図、図4(d)は図4(a)の線Y-Y<sup>\*</sup>における断面構造を示す図である。図1のようなタップセルの構造を採用した場合、ウエル電位給電領域11n,11pの横方向の幅が微小であるため、不純物の注入が必ずしもうまくいかない可能性がある。すなわち図4(b)に示すように、理想的には、ダミーゲートに挟まれたウエル電位給電領域にはウエル領域と同一導電型(図ではN型)の不純物が注入されるのが好ましい。ところが実際の製造プロセスでは、図4(c),(d)に示すように、隣接する拡散領域に注入される別の導電型(図ではP型)の不純物がウエル電位給電領域に注入されてしまい、このため、ダミーゲートの間にウエル電位給電領域がうまく形成されない可能性がある。

## [0042]

図5(a)は図2と同一の平面図、図5(b)は図5(a)の線X・X'における断面構造を示す図である。図2のようなタップセルの構造を採用した場合には、図5(b)に示すように、たとえ、隣接する拡散領域に注入される別の導電型(図ではP型)の不純物がウエル電位給電領域に注入されてしまった場合であっても、ダミーゲートの間には、ウエル領域と同一導電型(図ではN型)のウエル電位給電領域が形成される。

#### [0043]

## (第2の実施形態)

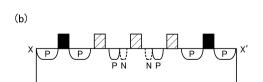

図 6 は第 2 の実施形態に係るタップセルのレイアウト構造の例を示す図である。図 6 のレイアウト構造では、インバータを構成する論理セル 5 a , 5 b の間にタップセル 3 が隣接配置されている。論理セル 5 a , 5 b のレイアウト構造は、図 1 と同様である。

### [0044]

図6において、タップセル3は、N型ウエル領域NWに形成されたN型不純物拡散領域31 nと、P型ウエル領域PWに形成されたP型不純物拡散領域31 pとを有している。N型ウエル領域NWには、N型不純物拡散領域31 nからコンタクトおよび配線を介して所望のウエル電位が給電される。P型ウエル領域PWには、P型不純物拡散領域31 pからコンタクトおよび配線を介して所望のウエル電位が給電される。すなわち、N型不純物拡散領域31 nとP型不純物拡散領域31 pは、ウエル電位給電領域(TAP領域)を構成する。

# [0045]

そして、タップセル3と論理セル5 a , 5 b との間には、それぞれ、ダミーゲート3 2 a , 3 2 b が配置されている。さらに、N型不純物拡散領域3 1 n およびP型不純物拡散領域3 1 p の上に、ダミーゲート3 2 c が配置されている。すなわち、N型不純物拡散領域3 1 n およびP型不純物拡散領域3 1 p は、いわゆるトランジスタ型のウエル電位給電

10

20

30

40

領域になっている。

### [0046]

このようにダミーゲートを配置したことによって、図6に示すように、縦方向に延びる複数のゲート(ダミーゲートを含む)が、横方向においてほぼ一定のピッチPでレイアウトされる。すなわち、図6のようなタップセル3のレイアウト構造を採用することによって、論理セル5a,5bの間にタップセル3を配置した場合でも、ゲートパターンの形状規則性を保つことができる。

## [0047]

図7は図6に示すトランジスタ型のウエル電位給電領域を用いた半導体装置のレイアウト構成の一例である。図7のレイアウトでは、縦方向(第1方向)に延びる複数のゲートが横方向(第2方向)に並べて配置されているセル列B1,B2,B3が、縦方向に並べて配置されている。セル列B1,B2,B3では、それぞれ、横方向に延びているP型ウエル領域PWおよびN型ウエル領域NWがゲートの下に形成されている。なお、セル列B2では、P型ウエル領域PWとN型ウエル領域NWがフリップされており、セル列B1,B2のN型ウエル領域NWは隣接しており、セル列B2,B3のP型ウエル領域PWは隣接している。

### [0048]

図7のレイアウト構成では、トランジスタ型の第1のウエル電位給電領域として、P型不純物拡散領域33p,34pと、N型不純物拡散領域33nとが設けられている。P型不純物拡散領域33pはセル列B1のP型ウエル領域PWに給電を行い、N型不純物拡散領域34pはセル列B1のN型ウエル領域NWに給電を行い、P型不純物拡散領域34pはセル列B2のP型ウエル領域PWに給電を行う。そして、P型不純物拡散領域33pの上には第1のゲートとしてのダミーゲート34aが、N型不純物拡散領域33pの上には第1のゲートとしてのダミーゲート34bが、そしてP型不純物拡散領域34pの上には第1のゲートとしてのダミーゲート34cが、それぞれ配置されている。

### [0049]

このようなレイアウトによって、ウエル電位給電領域を配置した場合でもその周辺のゲートパターンの形状規則性を維持することができるため、ゲートパターンに応じて異なる光近接効果の影響を回避することができる。したがって、ゲート長のばらつきを確実に抑制しながら、ウエル電位の制御やラッチアップ防止のためのウエル電位給電領域の設置による面積増大を抑制できる。

# [0050]

なお、トランジスタ型のウエル電位給電領域上に配置するゲートは、活性トランジスタのゲートとして機能するゲート電極であってもかまわない。図7のレイアウトでは、セル列B3のP型ウエル領域PWに給電を行う第1のウエル電位給電領域としてのP型不純物拡散領域35pの上に、その下の活性トランジスタTN1から延びる第1のゲートとしてのゲート電極36が配置されている。

### [0051]

<レイアウト構成の他の例>

#### (その1)

図8は半導体装置のレイアウト構成の他の例である。図8のレイアウトでは、図7と同様に、縦方向に延びる複数のゲートが横方向に並べて配置されているセル列 C 1 , C 2 , C 3 が、縦方向に並べて配置されている。セル列 C 1 , C 2 , C 3 では、それぞれ、横方向に延びているP型ウエル領域PWおよびN型ウエル領域NWがゲートの下に形成されている。なお、セル列 C 2 では、P型ウエル領域PWとN型ウエル領域NWがフリップされており、セル列 C 1 , C 2 のN型ウエル領域NWは隣接しており、セル列 C 2 , C 3 のP型ウエル領域PWは隣接している。

#### [0052]

図8のレイアウト構成の特徴の1つは、P型不純物拡散領域41pとN型不純物拡散領域41nである。P型不純物拡散領域41pはセル列C1のP型ウエル領域PWに給電を

10

20

30

40

行い、N型不純物拡散領域41mはセル列C1のN型ウエル領域NWに給電を行う。そして、P型不純物拡散領域41pとN型不純物拡散領域41mはともに、両側のダミーゲート42a,42bの下に重なるように配置されている。このような配置を許容することによって、不純物拡散領域の横方向の幅を拡大することができるので、製造プロセスにおいて不純物注入がより容易になるという効果が得られる。

#### [0053]

また、セル列 C 3 の P 型ウエル領域 P W に給電を行う P 型不純物拡散領域 4 3 p は、片側のダミーゲート 4 4 a の下に重なるように配置されている。同様に、セル列 C 3 の N 型ウエル領域 N W に給電を行う N 型不純物拡散領域 4 3 n は、片側のダミーゲート 4 4 b の下に重なるように配置されている。このような配置によっても、不純物拡散領域の横方向の幅を拡大することができる。

10

### [0054]

(その2)

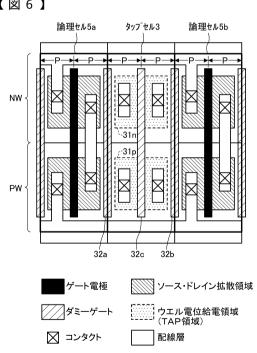

図9は半導体装置のレイアウト構成の他の例である。図9のレイアウトでは、図7と同様に、縦方向に延びる複数のゲートが横方向に並べて配置されているセル列D1,D2,D3が、縦方向に並べて配置されている。セル列D1,D2,D3では、それぞれ、横方向に延びているP型ウエル領域PWおよびN型ウエル領域NWがゲートの下に形成されている。なお、セル列D2では、P型ウエル領域PWとN型ウエル領域NWがフリップされており、セル列D1,D2のN型ウエル領域NWは隣接しており、セル列D2,D3のP型ウエル領域PWは隣接している。

20

### [0055]

図9のレイアウト構成の特徴の1つは、トランジスタ型のウエル電位給電領域において、ダミーゲートを挟む拡散領域の一方が、ウエル領域とは異なる導電型の不純物が注入されている点にある。例えば、セル列 D 1 の N 型ウエル領域 N W に、N 型不純物拡散領域 4 5 n と P 型不純物拡散領域 4 5 p とがダミーゲート 4 6 を挟んで配置されている。また、セル列 D 2 の P 型ウエル領域 P W に、P 型不純物拡散領域 4 7 p と N 型不純物拡散領域 4 7 n とがダミーゲート 4 8 を挟んで配置されている。

[0056]

30

例えば、P型不純物拡散領域 4 5 p を配置することによって、その右側に配置される P M O S トランジスタのソースまたはドレインとなる P 型不純物拡散領域に対して、動作上問題とならないように確実に不純物を注入することが可能になる。 すなわち、トランジスタ型のウエル電位給電領域において、ダミーゲートを挟む拡散領域の一方を、ウエル領域とは異なる導電型の不純物拡散領域にすることによって、これに隣接するトランジスタの拡散領域を確実に形成することができる。

[0057]

(その3)

これまでの説明では、主として、ウエル電位給電領域の両側に配置された隣接ゲートはダミーゲートである例を示した。ただし、本実施形態では、ウエル電位給電領域の両側に配置された隣接ゲートは、活性トランジスタのゲート電極として機能するゲートであってもかまわない。

40

[0058]

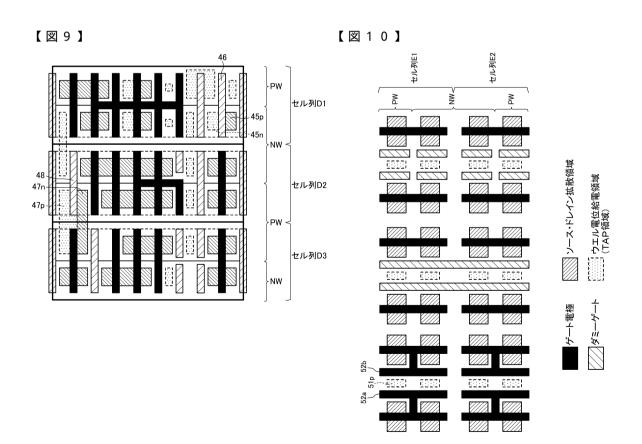

図10および図11は半導体装置のレイアウト構成の他の例である。図10のレイアウトでは、縦方向に延びる複数のゲートが横方向に並べて配置されているセル列 E1, E2が、縦方向に並べて配置されている。セル列 E1, E2では、それぞれ、横方向に延びている P型ウエル領域 PW および N型ウエル領域 NWがゲートの下に形成されている。なお、セル列 E2では、P型ウエル領域 PW とN型ウエル領域 NWがフリップされており、セル列 E1, E2のN型ウエル領域 NWは隣接している。図11のレイアウトも同様に、セル列 F1, F2が配置されている。

# [0059]

例えば、図10において、第1のウエル電位給電領域となるP型不純物拡散領域51p

(11)

には、活性トランジスタのゲートとして機能する第1および第2の隣接ゲートとしてのゲ ート電極52a,52bが隣接している。また、図11において、第1のウエル電位給電 領域となるN型不純物拡散領域53nには、活性トランジスタのゲートとして機能する第 1の隣接ゲートとしてのゲート電極54aと、第2の隣接ゲートとしてのダミーゲート5 4 b が隣接している。

#### [0060]

なお、上述した半導体装置のレイアウトにおいて、セル列同士の間に、横方向に延びる 、ウエル領域と同一導電型の不純物拡散領域を設けてもよい。例えば、図7のレイアウト において、セル列B1,B2間に、横方向に延びるN型不純物拡散領域を設け、セル列B 2 , B 3 間に、横方向に延びる P 型不純物拡散領域を設けてもかまわない。例えば、セル 列間に設けた不純物拡散領域をウエル領域への給電に用いることによって、ウエル領域の 電位をより安定させることが可能になる。

#### [0061]

あるいは、上述した半導体装置のレイアウトにおいて、セル列同士の間に、横方向に延 びる、ウエル領域と異なる導電型の不純物拡散領域を設けてもよい。例えば、図7のレイ アウトにおいて、セル列B1,B2間に、横方向に延びるP型不純物拡散領域を設け、セ ル列B2,B3間に、横方向に延びるN型不純物拡散領域を設けてもかまわない。例えば 、セル列間に設けた不純物拡散領域を電源電位または基板電位の供給に用いることによっ て、トランジスタのソース電位をより安定させることが可能になる。

### 【産業上の利用可能性】

[0062]

本発明では、ウエル電位給電領域を有する半導体装置を、光近接効果によるゲート長の ばらつきを確実に抑制し、かつ、レイアウト面積を増大させることなく、実現できるので 、例えば、半導体チップの歩留まり向上や小型化等に有効である。

# 【符号の説明】

# [0063]

1,2,3 タップセル

1 A , 1 B , 1 C , 1 D , 2 A , 2 B , 2 C , 2 D タップセル

11 n , 11 p , 21 n , 21 p , 22 n , 22 p ウエル電位給電領域

12a,12b,23a,23b,23c ダミーゲート

14 n ウエル電位給電領域(第1のウエル電位給電領域)

15 a , 15 b ダミーゲート (第1 および第2 の隣接ゲート)

15 c . 15 d ゲート電極(第3および第4の隣接ゲート)

15e,15f,15g,15h 4本のゲート

16n ウエル電位給電領域(第1のウエル電位給電領域)

17a,17b ダミーゲート(第1および第2の隣接ゲート)

1 7 c ゲート電極(第3の隣接ゲート)

17d ダミーゲート(第4の隣接ゲート)

17e,17f,17g,17h 4本のゲート

ウエル電位給電領域(第2のウエル電位給電領域)

19 n ウエル電位給電領域(第3のウエル電位給電領域)

3 1 n , 3 1 p ウエル電位給電領域(第 1 のウエル電位給電領域)

32a,32b ダミーゲート

3 2 c ダミーゲート (第1のゲート)

3 3 p , 3 3 n , 3 4 p , 3 5 p ウエル電位給電領域(第 1 のウエル電位給電領域)

3 4 a , 3 4 b , 3 4 c ダミーゲート (第 1 のゲート)

3 6 ゲート電極(第1のゲート)

5 1 p ウエル電位給電領域(第1のウエル電位給電領域)

5 2 a , 5 2 b ゲート電極 (第 1 および第 2 の隣接ゲート)

53n ウエル電位給電領域(第1のウエル電位給電領域)

20

10

30

40

5 4 a ゲート電極(第1の隣接ゲート) 5 4 b ダミーゲート(第2の隣接ゲート)

NW N型ウエル領域

PW P型ウエル領域

TN1 活性トランジスタ

# 【図1】

# 【図2】

# 【図3】

# 【図4】

# 【図5】

# 【図6】

43n 44a 44b

`-43p

【図11】

【図12】

ゲート電極 ソース・ドレイン拡散領域 ソース・ドレイン拡散領域 / グミーゲート (TAP領域)

# フロントページの続き

# (72)発明者 西村 英敏

大阪府門真市大字門真1006番地 パナソニック株式会社内

# 審査官 宇多川 勉

# (56)参考文献 特開2007-012855(JP,A)

特開2006-005103(JP,A)

特開平05-082640(JP,A)

特開昭61-099348(JP,A)

特開2009-267094(JP,A)

特開2003-309178(JP,A)

特開2008-235350(JP,A)

特開2007-129094(JP,A)

# (58)調査した分野(Int.CI., DB名)

H01L 21/82

H01L 21/822

H01L 21/8234

H01L 27/04

H01L 27/088