(19) **日本国特許庁(JP)**

# (12) 特 許 公 報(B2)

(11)特許番号

特許第6181203号 (P6181203)

(45) 発行日 平成29年8月16日(2017.8.16)

(24) 登録日 平成29年7月28日 (2017.7.28)

(51) Int.Cl. F I **GO2F** 1/1368 (2006.01) GO2F

GO2F 1/1368 (2006.01) GO2F 1/1368 HO1L 21/28 (2006.01) HO1L 21/28 3O1B HO1L 29/786 (2006.01) HO1L 29/78 618B HO1L 29/78 612B

請求項の数 15 (全 24 頁)

(21) 出願番号 特願2015-552346 (P2015-552346)

(86) (22) 出願日 平成26年8月28日 (2014. 8. 28)

(86) 国際出願番号 PCT/JP2014/072615 (87) 国際公開番号 W02015/087586

(87) 国際公開日 平成27年6月18日 (2015. 6. 18) 審査請求日 平成28年6月6日 (2016. 6. 6)

(31) 優先権主張番号 特願2013-254917 (P2013-254917) (32) 優先日 平成25年12月10日 (2013.12.10)

(33) 優先権主張国 日本国(JP)

(73) 特許権者 000005049 シャープ株式会社

大阪府堺市堺区匠町1番地

人败州将市场区压明工程地

(74)代理人 100101683

弁理士 奥田 誠司

(74)代理人 100155000

弁理士 喜多 修市

|(74)代理人 100139930

弁理士 山下 亮司

(74) 代理人 100125922

弁理士 三宅 章子

(74)代理人 100135703

弁理士 岡部 英隆

|(74)代理人 100184985

弁理士 田中 悠

最終頁に続く

(54) 【発明の名称】半導体装置およびその製造方法

# (57)【特許請求の範囲】

# 【請求項1】

基板と、前記基板上に、行方向および列方向を有するマトリクス状に配列された複数の画素領域と、それぞれが前記行方向に略平行に延設された複数のゲートラインと、それぞれが前記列方向に略平行に延設された複数のソースラインとを備えた半導体装置であって

前記複数の画素領域のそれぞれは、

前記基板に支持された薄膜トランジスタであって、ゲート電極、前記ゲート電極を覆うゲート絶縁層、前記ゲート絶縁層上に形成された酸化物半導体層、および、前記酸化物半導体層に電気的に接続されたソース電極およびドレイン電極を有する、薄膜トランジスタと、

前記酸化物半導体層と同一の酸化物膜から形成された金属酸化物層と、

前記薄膜トランジスタおよび前記金属酸化物層を覆う層間絶縁層と、

前記層間絶縁層上に設けられ、かつ、前記ドレイン電極に電気的に接続された画素電極*と*

を有しており、

前記金属酸化物層は導電体領域を含み、

前記画素電極は、前記層間絶縁層を介して前記導電体領域の少なくとも一部と重なっており、

前記複数の画素領域は、第1画素領域、および、前記第1画素領域と前記列方向に隣接

### する第2画素領域を有し、

<u>前記第1画素領域および前記第2画素領域における前記金属酸化物層の前記導電体領域</u>は、互いに電気的に接続されている、半導体装置。

## 【請求項2】

前記第1画素領域における前記金属酸化物層と、前記第2画素領域における前記金属酸化物層とは一体的に形成されている、請求項1に記載の半導体装置。

### 【請求項3】

前記複数のソースラインと同じ導電膜から形成され、かつ、前記第1および第2画素領域を横切るように前記列方向に延設された接続配線をさらに備え、

前記第1画素領域および前記第2画素領域における前記金属酸化物層の前記導電体領域は、前記接続配線を介して互いに電気的に接続されている、請求項<u>1</u>に記載の半導体装置

10

### 【請求項4】

前記複数のソースラインと同一の導電膜から形成され、かつ、互いに分離された第1および第2の接続部をさらに備え、

前記第2画素領域における前記金属酸化物層の前記導電体領域は、前記第1の接続部によって、前記第1画素領域における前記金属酸化物層の前記導電体領域と電気的に接続され、かつ、前記第2の接続部によって、前記第2画素領域と前記列方向に隣接する他の画素領域における前記金属酸化物層の前記導電体領域と電気的に接続されている、請求項<u>1</u>に記載の半導体装置。

20

## 【請求項5】

前記複数の画素領域のそれぞれは、前記層間絶縁層に形成されたコンタクトホール内で 前記ドレイン電極と前記画素電極とが直接接するコンタクト部をさらに有し、

前記基板の法線方向から見たとき、前記コンタクト部は、前記薄膜トランジスタと前記列方向に隣接して配置されている、請求項1から4のいずれかに記載の半導体装置。

### 【請求項6】

前記複数のゲートラインは、前記第1画素領域における前記ゲート電極と電気的に接続された第1のゲートラインを含み、

前記基板の法線方向から見たとき、前記第1のゲートラインは、第1部分と、前記第1部分よりも幅の小さい第2部分とを含んでおり、

30

前記基板の法線方向から見たとき、前記第1画素領域における前記酸化物半導体層の少なくとも一部は、前記第1部分と重なるように配置されており、前記接続配線または前記第1の接続部は前記第2部分を跨いで延設されている、請求項<u>3</u>または<u>4</u>に記載の半導体装置。

## 【請求項7】

前記金属酸化物層は、半導体領域をさらに含み、

前記半導体領域は前記金属酸化物層の周縁部に位置している請求項1から<u>6</u>のいずれかに記載の半導体装置。

# 【請求項8】

前記層間絶縁層は、第1絶縁膜と、前記第1絶縁膜上に設けられた第2絶縁膜とを含み

40

前記第1絶縁膜は、前記金属酸化物層上に開口を有しており、

前記導電体領域は、前記金属酸化物層のうち前記開口によって露出された部分を含み、前記半導体領域は、前記金属酸化物層のうち前記第 1 絶縁膜で覆われた部分を含む、請求項 7 に記載の半導体装置。

# 【請求項9】

前記層間絶縁層のうち前記金属酸化物層の前記導電体領域と前記画素電極との間に位置する部分は、前記第2絶縁膜を含み、かつ、前記第1絶縁膜を含まない請求項<u>8</u>に記載の半導体装置。

# 【請求項10】

前記酸化物半導体層および前記金属酸化物層は、In、GaおよびZnのうち少なくとも1種の金属元素を含む請求項1から9のいずれかに記載の半導体装置。

# 【請求項11】

前記酸化物半導体層および前記金属酸化物層は、結晶質部分を含む、請求項<u>10</u>に記載の半導体装置。

# 【請求項12】

基板と、行方向および列方向を有するマトリクス状に配列された複数の画素領域と、前記複数の画素領域のそれぞれに配置された薄膜トランジスタと、それぞれが前記行方向に略平行に延設された複数のゲートラインと、それぞれが前記列方向に略平行に延設された、複数のソースラインとを備えた半導体装置の製造方法であって、

前記複数の画素領域は、前記列方向に隣接する第1および第2画素領域を含み、

前記第1および第2画素領域のそれぞれにおいて、

- (a)前記基板上に、ゲート電極および前記ゲート電極を覆うゲート絶縁層を形成する 工程と、

- (b)前記ゲート絶縁層上に、酸化物半導体膜を形成し、これをパターニングすることにより、酸化物半導体層および金属酸化物層をそれぞれ形成する工程であって、前記酸化物半導体層は、少なくとも一部が前記ゲート絶縁層を介して前記ゲート電極と重なるように配置される、工程と、

- ( c )前記酸化物半導体層と接するソース電極およびドレイン電極を形成する、工程と

(d)前記ソース電極および前記ドレイン電極と前記金属酸化物層とを覆うように第1 絶縁膜を形成し、前記第1絶縁膜に、前記ドレイン電極の一部を露出する第1開口と、前 記金属酸化物層の一部を露出する第2開口とを形成する工程と、

- (e)前記金属酸化物層のうち前記第2開口によって露出された部分を導体化して導電体領域を形成するとともに、前記金属酸化物層のうち導体化されなかった部分は半導体領域として残る工程と、

- (f)前記第1絶縁膜上および前記第1および第2開口内に第2絶縁膜を形成し、前記第2絶縁膜のうち前記第1開口内に位置する部分を除去することにより、前記第1および第2絶縁膜を貫通し、且つ、前記ドレイン電極を露出するコンタクトホールを形成する工程と、

- (g)前記第2絶縁膜上および前記コンタクトホール内に画素電極を形成する工程であって、前記画素電極は、前記コンタクトホール内で前記ドレイン電極と接し、且つ、前記金属酸化物層の前記導電体領域の少なくとも一部と前記第2絶縁膜を介して重なるように配置される、工程と

を包含する半導体装置の製造方法。

### 【請求項13】

前記工程(b)において、前記第1および第2画素領域における前記金属酸化物層を一体的に形成する、請求項12に記載の半導体装置の製造方法。

### 【請求項14】

前記第1および第2画素領域における前記金属酸化物層を互いに電気的に接続する接続配線を形成する工程をさらに含み、前記接続配線は、前記ソースおよびドレイン電極と同じ導電膜から形成される、請求項12に記載の半導体装置の製造方法。

# 【請求項15】

互いに分離された第1および第2の接続部を形成する工程をさらに含み、前記第1の接続部は、前記第1および第2画素領域における前記金属酸化物層を接続するように配置され、前記第2の接続部は、前記第2画素領域および前記第2画素領域に前記列方向に隣接する他の画素領域における前記金属酸化物層を接続するように配置される、請求項12に記載の半導体装置の製造方法。

# 【発明の詳細な説明】

# 【技術分野】

10

20

30

30

#### [00001]

本発明は、酸化物半導体を用いた半導体装置およびその製造方法に関する。

### 【背景技術】

## [0002]

液晶表示装置等に用いられるアクティブマトリクス基板は、画素毎に薄膜トランジスタ(Thin Film Transistor;以下、「TFT」)などのスイッチング素子を備えている。このようなスイッチング素子としては、従来から、アモルファスシリコン膜を活性層とするTFT(以下、「アモルファスシリコンTFT」)や多結晶シリコン膜を活性層とするTFT(以下、「多結晶シリコンTFT」)が広く用いられている。

# [0003]

近年、TFTの活性層の材料として、アモルファスシリコンや多結晶シリコンに代わって、酸化物半導体を用いることが提案されている。このようなTFTを「酸化物半導体TFT」と称する。酸化物半導体は、アモルファスシリコンよりも高い移動度を有している。このため、酸化物半導体TFTは、アモルファスシリコンTFTよりも高速で動作することが可能である。また、酸化物半導体膜は、多結晶シリコン膜よりも簡便なプロセスで形成されるため、大面積が必要とされる装置にも適用できる。酸化物半導体TFTを備えるアクティブマトリクス基板(以下、「TFT基板」)は、例えば特許文献1に開示されている。

### [0004]

また、例えば特許文献 2 には、酸化物半導体膜の一部を低抵抗化することにより、TFTの活性層となる半導体層と、画素電極などの導電体層とを一体的に形成することが開示されている。特許文献 2 には、上記の低抵抗化処理により、酸化物半導体TFTを備えるTFT基板をより低いコストで製造できる旨が記載されている。

#### [0005]

特許文献1および2などに開示された従来のTFT基板を液晶表示装置に用いる場合、TFT基板には、必要に応じて、補助容量が設けられる。補助容量は、補助容量電極(または補助容量配線)と、画素電極と、それらの間に位置する誘電体層とから構成され得る。補助容量電極は、例えば、ゲート配線と同じ導電膜から形成される。

# 【先行技術文献】

# 【特許文献】

[0006]

【特許文献1】特開2003-86808号公報

【特許文献 2 】特開 2 0 0 8 - 4 0 3 4 3 号公報

# 【発明の概要】

【発明が解決しようとする課題】

# [0007]

TFT基板に補助容量を設ける場合、上述したように、ゲート配線と同じ導電膜(通常は金属膜)から補助容量電極を形成すると、製造プロセスを複雑にすることなく、各画素内に補助容量を形成することが可能である。しかしながら、補助容量電極の分だけ開口率および光透過率が低下するという問題がある。

# [ 0 0 0 8 ]

また、本発明者が検討したところ、例えば特許文献 2 に開示されたTFT基板では、画素全体に占める画素電極の面積の割合が小さいので、開口率がさらに低下するおそれがあることも分かった。詳細は後述する。

### [0009]

本発明は上記事情に鑑みてなされたものであり、本発明の一実施形態は、簡便なプロセスで製造することができ、且つ、従来よりも高い開口率および透過率を実現することが可能な半導体装置およびその製造方法を提供することを目的とする。

## 【課題を解決するための手段】

# [0010]

10

20

30

40

本発明による一実施形態の半導体装置は、基板と、前記基板上に、行方向および列方向を有するマトリクス状に配列された複数の画素領域とを備えた半導体装置であって、ゲート電数の画素領域のそれぞれは、前記基板に支持された薄膜トランジスタであって、ゲート電極、前記ゲート電極を覆うゲート絶縁層、前記ゲート絶縁層上に形成された酸化物半導体層、および、前記酸化物半導体層に電気的に接続されたソース電極およびドレイン電極を有する、薄膜トランジスタと、前記酸化物半導体層と同一の酸化物膜から形成された金属酸化物層と、前記薄膜トランジスタおよび前記金属酸化物層を覆う層間絶縁層と、前記層間絶縁層上に設けられ、かつ、前記ドレイン電極に電気的に接続された画素電極とを有しており、前記金属酸化物層は導電体領域を含み、前記画素電極は、前記層間絶縁層を介して前記導電体領域の少なくとも一部と重なっている。

[0011]

ある実施形態において、それぞれが前記行方向に略平行に延設された複数のゲートラインと、それぞれが前記列方向に略平行に延設された複数のソースラインとをさらに備え、前記複数の画素領域は、第1画素領域、および、前記第1画素領域と前記列方向に隣接する第2画素領域を有し、前記第1画素領域および前記第2画素領域における前記金属酸化物層の前記導電体領域は、互いに電気的に接続されている。

[0012]

ある実施形態において、前記第1画素領域における前記金属酸化物層と、前記第2画素 領域における前記金属酸化物層とは一体的に形成されている。

[0013]

ある実施形態において、前記複数のソースラインと同じ導電膜から形成され、かつ、前記第1および第2画素領域を横切るように前記列方向に延設された接続配線をさらに備え、前記第1画素領域および前記第2画素領域における前記金属酸化物層の前記導電体領域は、前記接続配線を介して互いに電気的に接続されている。

[0014]

ある実施形態において、前記複数のソースラインと同一の導電膜から形成され、かつ、 互いに分離された第1および第2の接続部をさらに備え、前記第2画素領域における前記 金属酸化物層の前記導電体領域は、前記第1の接続部によって、前記第1画素領域におけ る前記金属酸化物層の前記導電体領域と電気的に接続され、かつ、前記第2の接続部によって、前記第2画素領域と前記列方向に隣接する他の画素領域における前記金属酸化物層 の前記導電体領域と電気的に接続されている。

[0015]

ある実施形態において、前記複数の画素領域のそれぞれは、前記層間絶縁層に形成されたコンタクトホール内で前記ドレイン電極と前記画素電極とが直接接するコンタクト部をさらに有し、前記基板の法線方向から見たとき、前記コンタクト部は、前記薄膜トランジスタと前記列方向に隣接して配置されている。

[0016]

ある実施形態において、前記複数のゲートラインは、前記第1画素領域における前記ゲート電極と電気的に接続された第1のゲートラインを含み、前記基板の法線方向から見たとき、前記第1のゲートラインは、第1部分と、前記第1部分よりも幅の小さい第2部分とを含んでおり、前記基板の法線方向から見たとき、前記第1画素領域における前記酸化物半導体層の少なくとも一部は、前記第1部分と重なるように配置されており、前記接続配線または前記第1の接続部は前記第2部分を跨いで延設されている。

[0017]

ある実施形態において、前記金属酸化物層は、半導体領域をさらに含み、前記半導体領域は前記金属酸化物層の周縁部に位置している。

[0018]

ある実施形態において、前記層間絶縁層は、第1絶縁膜と、前記第1絶縁膜上に設けられた第2絶縁膜とを含み、前記第1絶縁膜は、前記金属酸化物層上に開口を有しており、前記導電体領域は、前記金属酸化物層のうち前記開口によって露出された部分を含み、前

10

20

30

40

記半導体領域は、前記金属酸化物層のうち前記第1絶縁膜で覆われた部分を含む。

#### [0019]

ある実施形態において、前記層間絶縁層のうち前記金属酸化物層の前記導電体領域と前記画素電極との間に位置する部分は、前記第2絶縁膜を含み、かつ、前記第1絶縁膜を含まない。

#### [0020]

ある実施形態において、前記酸化物半導体層および前記金属酸化物層は、In、GaおよびZnのうち少なくとも1種の金属元素を含む。

## [0021]

ある実施形態において、前記酸化物半導体層および前記金属酸化物層は、結晶質部分を含む。

### [0022]

本発明による一実施形態の半導体装置の製造方法は、基板と、行方向および列方向を有 するマトリクス状に配列された複数の画素領域と、前記複数の画素領域のそれぞれに配置 された薄膜トランジスタと、それぞれが前記行方向に略平行に延設された複数のゲートラ インと、それぞれが前記列方向に略平行に延設された、複数のソースラインとを備えた半 導体装置の製造方法であって、前記複数の画素領域は、前記列方向に隣接する第1および 第2画素領域を含み、前記第1および第2画素領域のそれぞれにおいて、(a)前記基板 上に、ゲート電極および前記ゲート電極を覆うゲート絶縁層を形成する工程と、(b)前 記ゲート絶縁層上に、酸化物半導体膜を形成し、これをパターニングすることにより、酸 化物半導体層および金属酸化物層をそれぞれ形成する工程であって、前記酸化物半導体層 は、少なくとも一部が前記ゲート絶縁層を介して前記ゲート電極と重なるように配置され る、工程と、(c)前記酸化物半導体層と接するソース電極およびドレイン電極を形成す る、工程と、(d)前記ソース電極および前記ドレイン電極と前記金属酸化物層とを覆う ように第1絶縁膜を形成し、前記第1絶縁膜に、前記ドレイン電極の一部を露出する第1 開口と、前記金属酸化物層の一部を露出する第2開口とを形成する工程と、(e)前記金 属酸化物層のうち前記第2開口によって露出された部分を導体化して導電体領域を形成す るとともに、前記金属酸化物層のうち導体化されなかった部分は半導体領域として残るエ 程と、(f)前記第1絶縁膜上および前記第1および第2開口内に第2絶縁膜を形成し、 前記第2絶縁膜のうち前記第1開口内に位置する部分を除去することにより、前記第1お よび第2絶縁膜を貫通し、且つ、前記ドレイン電極を露出するコンタクトホールを形成す る工程と、(g)前記第2絶縁膜上および前記コンタクトホール内に画素電極を形成する 工程であって、前記画素電極は、前記コンタクトホール内で前記ドレイン電極と接し、且 つ、前記金属酸化物層の前記導電体領域の少なくとも一部と前記第2絶縁膜を介して重な るように配置される、工程とを包含する。

### [0023]

ある実施形態において、前記工程(b)において、前記第1および第2画素領域における前記金属酸化物層を一体的に形成する。

# [0024]

ある実施形態において、前記第1および第2画素領域における前記金属酸化物層を互いに電気的に接続する接続配線を形成する工程をさらに含み、前記接続配線は、前記ソースおよびドレイン電極と同じ導電膜から形成される。

### [0025]

ある実施形態において、互いに分離された第1および第2の接続部を形成する工程をさらに含み、前記第1の接続部は、前記第1および第2画素領域における前記金属酸化物層を接続するように配置され、前記第2の接続部は、前記第2画素領域および前記第2画素領域に前記列方向に隣接する他の画素領域における前記金属酸化物層を接続するように配置される。

## 【発明の効果】

# [0026]

50

40

10

20

本発明の実施形態によると、簡便なプロセスで製造することができ、且つ、高い開口率および透過率を実現することが可能な酸化物半導体TFTを備える半導体装置を提供できる。

【図面の簡単な説明】

[0027]

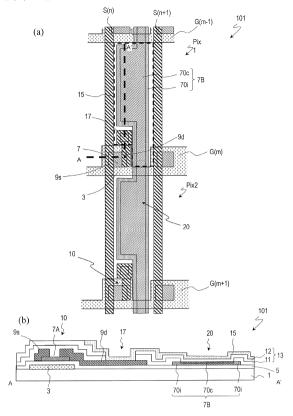

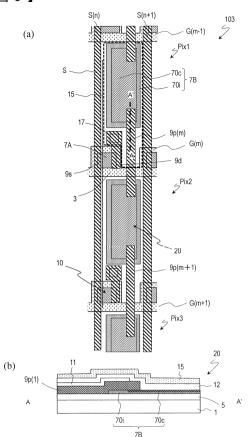

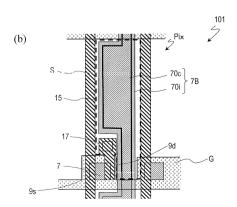

【図1】(a)および(b)は、それぞれ、本発明による第1の実施形態の半導体装置101の平面図および断面図である。

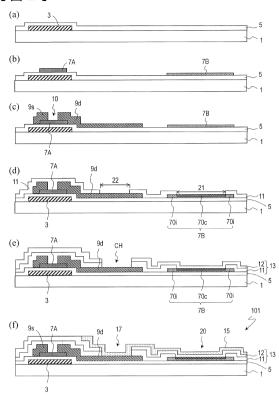

【図2】(a)から(f)は、それぞれ、第1の実施形態の半導体装置101の製造方法を説明するための工程断面図である。

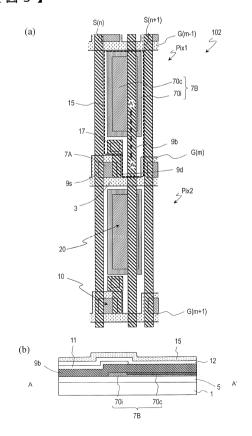

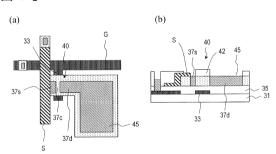

【図3】(a)および(b)は、それぞれ、本発明による第2の実施形態の半導体装置102の平面図および断面図である。

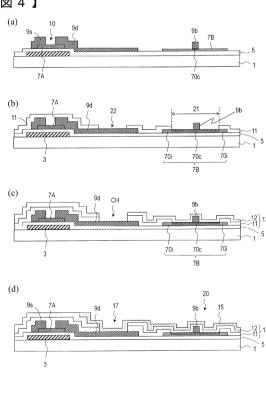

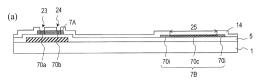

【図4】(a)から(d)は、それぞれ、第2の実施形態の半導体装置102の製造方法を説明するための工程断面図である。

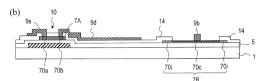

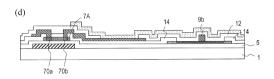

【図5】(a)から(d)は、それぞれ、第2の実施形態の半導体装置102の製造方法の他の例を説明するための工程断面図である。

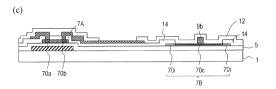

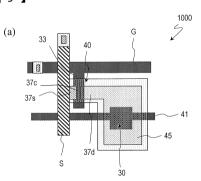

【図6】(a)および(b)は、それぞれ、本発明による第3の実施形態の半導体装置103の平面図および断面図である。

【図7】本発明による実施形態の半導体装置を用いた表示装置を例示する断面図である。

【図8】(a)および(b)は、それぞれ、特許文献2に開示されたTFT基板の平面図および断面図である。

【図9】(a)は、従来のTFT基板に補助容量配線を設けた参考例のTFT基板における一画素を示す平面図であり、(b)は、第1の実施形態のTFT基板101の一画素を示す平面図である。

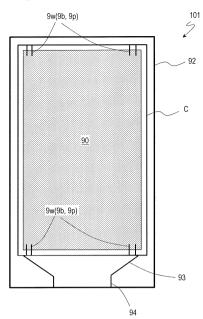

【図10】TFT基板101の一例を示す模式的な平面図である。

【発明を実施するための形態】

[0028]

(第1の実施形態)

以下、図面を参照しながら本発明の第1の実施形態を説明する。

[0029]

図1(a)は、本実施形態の半導体装置(TFT基板)101の平面図である。図1(b)は、図1(a)中のA-A'線に沿った断面図であり、半導体装置101におけるTFT10および補助容量20を示す。なお、本明細書において、「半導体装置」とは、TFTおよび容量素子を備えた装置であればよく、TFT基板およびTFT基板を有する表示装置などを広く含む。

[0030]

TFT基板101は、例えば、VA(Vertical Alignment)モードで表示を行う液晶表示装置に用いられる。液晶表示装置は、行方向および列方向を有するマトリクス状に配置された複数の画素を有している。TFT基板101は、表示装置の複数の画素に対応する複数の領域(以下、「画素領域」)Pixを有している。図1(a)は、複数の画素領域Pixのうち、列方向に隣接された2つの画素領域Pix1、Pix2を示している。

[0031]

TFT基板101は、基板1と、列方向に略平行に延設された複数のソースライン(ソースバスラインともいう。)Sと、行方向に略平行に延設された複数のゲートライン(ゲートバスラインともいう。)Gとを有している。行方向および列方向は、互いに直交していてもよい。行方向および列方向は、それぞれ、液晶表示装置の表示面における水平方向および垂直方向であってもよい。基板1の法線方向から見たとき、ソースラインSおよびゲートラインGによって包囲された領域が、それぞれ、「画素領域Pix」となる。各画素領域Pixには、TFT10、金属酸化物層7Bおよび画素電極15が形成されている

10

20

30

10

20

30

40

50

#### [0032]

図 1 ( a )には、複数のソースラインSのうち隣接する2つのソースラインS( n )、S( n + 1 )と、隣接する3つのゲートラインG( m - 1 )、G( m )、G( m + 1 )とが示されている( n およびmは自然数)。ソースラインS( n )、S( n + 1 )およびゲートラインG( m - 1 )、G( m )によって包囲された領域を「第1画素領域 P i  $\times$  1 」、ソースラインS( n )、S( n + 1 )によって包囲された領域を「第2画素領域 P i  $\times$  2 」と称する。

# [0033]

第1画素領域 Pix1における TFT10のゲート電極3は、ゲートライン G(m)に電気的に接続され、ソース電極9sは、ソースライン S(n)に電気的に接続されている。同様に、第2画素領域 Pix2における TFT10のゲート電極3は、ゲートライン G(m+1)に電気的に接続され、ソース電極9sは、ソースライン S(n)電気的に接続されている。

# [0034]

各画素領域PixのTFT10は、基板1に支持されている。TFT10は、ゲート電極3、ゲート電極3を覆うゲート絶縁層5、ゲート絶縁層5上に形成された酸化物半導体層7A、および、ソース電極9sおよびドレイン電極9dを有するボトムゲート構造のTFTである。酸化物半導体層7Aは、少なくともチャネル領域がゲート絶縁層5を介してずート電極3と重なるように配置されている。本実施形態では、ゲートラインGのうち酸化物半導体層7Aとゲート絶縁層5を介して重なる部分がゲート電極3となる。ソースおよびドレイン電極9s、9dは、それぞれ、酸化物半導体層7Aと直接接していてもよい。本実施形態では、ソースラインSのうち酸化物半導体層7Aと直接接していてもよい。本実施形態では、ソースラインSのうち酸化物半導体層7Aと接する部分がソース電極9sである。ソース電極9sは、ソースラインSに電気的に接続され、ドレイン電極9dは画素電極15に電気的に接続されている。また、TFT10は、層間絶縁層13で覆われている。

### [0035]

金属酸化物層7Bは、酸化物半導体層7Aと同一の酸化物膜から形成されている。金属酸化物層7Bは、導電体領域70cを含んでいる。導電体領域70cは、TFT10の酸化物半導体層7Aよりも抵抗の低い領域であり、例えば、酸化物半導体膜に低抵抗化処理を行うことによって形成される。ここでは、導電体領域70cは、酸化物半導体層7Aの表面近傍に形成されている。なお、導電体領域70cは、酸化物半導体層7Aの厚さ方向に亘って形成されていてもよい。図示するように、金属酸化物層7Bは、導電体領域70cの他に、半導体領域70iを含んでもよい。半導体領域70iは、基板1の法線方向から見たとき、金属酸化物層7Bの周縁部に位置していてもよい。

### [0036]

画素電極15は、透明な導電材料(例えばITO)から形成されている。画素電極15は層間絶縁層13上に設けられ、層間絶縁層13に形成されたコンタクトホール内でTFT10のドレイン電極9dに電気的に接続されている。この接続部分を「コンタクト部」17と称する。

# [0037]

画素電極15は、また、層間絶縁層13を介して、金属酸化物層7Bの導電体領域70 c の少なくとも一部と重なるように配置されている。これにより、導電体領域70cを下 層電極(補助容量配線または補助容量電極ともいう。)、画素電極15を上層電極とし、 層間絶縁層13のうちこれらの電極の間に位置する部分を誘電体層とする補助容量20が 形成される。補助容量20の上層電極(画素電極15)および下層電極(導電体領域70 c )は、それぞれ透明な導電材料から形成されている。補助容量20は、例えば液晶表示 装置において、液晶容量と電気的に並列に接続される。

### [0038]

このように、本実施形態によると、酸化物半導体層7Aと同じ酸化物膜を利用して補助

容量 2 0 の下層電極を形成するので、プロセスを複雑にすることなく、画素領域 P i x 内に補助容量 2 0 を形成できる。補助容量 2 0 は透明材料から構成されている。このため、開口率を低下させることなく、所望の面積(基板 1 の法線方向から見たときの面積)を有する補助容量 2 0 を設けることができ、十分な補助容量値を確保できる。

# [0039]

列方向に隣接する2つの画素領域 Pix1、Pix2における金属酸化物層 7 Bの導電体領域 7 0 c は、互いに電気的に接続されていてもよい。図示していないが、列方向に配列された全ての画素領域 Pixにおける導電体領域 7 0 c が互いに電気的に接続されていてもよい。これにより、複数の画素領域 Pixの導電体領域 7 0 c (補助容量電極として機能する)に、共通の補助容量電圧(Cs電圧)を供給し得る。

### [0040]

本実施形態では、隣接する第1および第2画素領域Pi×1、Pi×2における金属酸化物層7Bは、一体的に形成されており、それぞれの導電体領域70cは連続している。言い換えると、基板1の法線方向から見たとき、画素領域Pi×1、Pi×2の金属酸化物層7Bは、第1画素領域Pi×1から、ゲートラインG(ここではゲートラインG(m))を跨いで第2画素領域Pi×2に延設された金属酸化物配線を構成している。

#### [0041]

各列に配列された3以上の画素領域Pix、好ましくは各列に配列された全ての画素領域Pixにおける金属酸化物層7Bは一体的に形成されていてもよい。例えば、列方向に配列された複数の画素領域Pixの金属酸化物層7Bが一体となり、複数のゲートラインGを跨いで列方向に延設された金属酸化物配線を構成していてもよい。

### [0042]

本実施形態では、各画素領域Pixにおいて、ソースラインSとゲートラインGとが交差する部分の近傍にTFT10が配置されている。また、画素電極15と、TFT10のドレイン電極9dとを電気的に接続するためのコンタクト部17は、TFT10と列方向に隣接して配置されている。図示する例では、基板1の法線方向から見たとき、第1画素電極Pix1におけるTFT10は、ソースラインS(n)とゲートラインG(m)との交点付近に位置しており、コンタクト部17は、ソースラインS(n)、ゲートラインG(m)および金属酸化物層7Bに包囲された領域に配置されている。このような構成により、開口率を低下させずに、列方向に隣接する2つの画素領域Pixにおける金属酸化物層7Bを互いに接続することが可能になる。

# [0043]

TFT10を覆う層間絶縁層13は、補助容量20の誘電体層としても機能する。本実施形態における層間絶縁層13は、第1絶縁膜11と、第1絶縁膜11上に設けられた第2絶縁膜12とを含んでいる。第1絶縁膜11は、金属酸化物層7B上に開口を有している。金属酸化物層7Bの導電体領域70cは、金属酸化物層7Bのうち第1絶縁膜11の開口によって露出された部分を含む。一方、半導体領域70iは、金属酸化物層7Bのうち第1絶縁膜11で覆われた部分を含む。第1絶縁膜11の開口には、導電体領域70cと接するように第2絶縁膜12が形成されている。層間絶縁層13のうち補助容量20の下層電極(導電体領域70c)と上層電極(画素電極15)との間に位置する部分は、第2絶縁膜12を含み、かつ、第1絶縁膜11を含まない。つまり、層間絶縁層13のうちの主として第2絶縁膜12が、補助容量20の誘電体層として機能する。

### [0044]

上記のような構成は、第1絶縁膜11をマスクとして、金属酸化物層7Bの低抵抗化処理(後述するプラズマ処理など)を行うことによって得られる。ただし、低抵抗化処理の条件によっては、基板1の法線方向から見たとき、導電体領域70cは第1絶縁膜11の開口よりも一回り大きくなり、第1絶縁膜11の端部と重なる場合がある。

### [0045]

なお、層間絶縁層13は、上記のような2層構造に限定されず、3層以上の積層構造を 有していてもよい。あるいは、層間絶縁層13は単一の絶縁膜であってもよい。その場合 10

20

30

40

10

20

30

40

50

、絶縁膜を堆積した後、ハーフトーン露光を利用して絶縁膜上にレジスト層を形成し、絶縁膜のエッチングを行ってもよい。これにより、絶縁膜にドレイン電極9dを露出するコンタクトホールを形成するとともに、絶縁膜のうち金属酸化物層7B上に位置する部分(補助容量20の誘電体層となる部分)の表面を露出する。この後、レジスト層をマスクとして低抵抗化処理を行い、絶縁膜(絶縁膜の露出部分)越しに、その下方にある金属酸化物層7Bの低抵抗化を行ってもよい。

### [0046]

基板1の法線方向から見たとき、ゲートラインGは、第1部分と、第1部分よりも幅の小さい第2部分とを含んでいてもよい。TFT10の酸化物半導体層7Aのチャネル領域は、ゲートラインGの第1部分と重なるように配置されている。図示するように、酸化物半導体層7A全体が、ゲートラインGの第1部分と重なっていてもよい。これにより、ゲートラインGが酸化物半導体層7Aの遮光膜としても機能するので、酸化物半導体層7Aに光が入射することによるTFT特性の変動を抑制できる。また、ゲートラインGのうちTFT10と重ならない部分の幅を小さく抑えることにより、ゲートラインGに起因する開口率の低下を抑制できる。列方向に隣接する2つの画素領域Pix1、Pix2の金属酸化物層7Bは、それらの画素領域Pixの間に位置するゲートラインG(m)の第2部分を跨ぐように一体的に形成されていてもよい。

# [0047]

ゲート電極 3 は、ゲートライン G と電気的に接続されていればよく、ゲートライン G と同じ導電膜から形成されていてもよい。ゲート電極 3 はゲートライン G と一体的に形成されていてもよい。例えば、ゲート電極 3 は、ゲートライン G の一部であってもよい。すなわち、ゲートライン G のうち T F T 1 0 の酸化物半導体層 7 A のチャネル領域と重なる部分が、ゲート電極 3 として機能してもよい。また、基板 1 の法線方向から見たとき、ゲートライン G は所定の方向に延びる部分と、その部分から上記所定の方向とは異なる方向に延びる延出部分とを有し、延出部分がゲート電極 3 として機能してもよい。

### [0048]

ソース電極9sおよびドレイン電極9dは、ソースラインSと同じ導電膜から形成されていてもよい。ソース電極9sはソースラインSと電気的に接続されていればよく、ソースラインSと一体的に形成されていてもよい。例えば、ソース電極9sは、ソースラインGの一部であってもよい。すなわち、ソースラインGのうちTFT10の酸化物半導体層7Aと接する部分が、ソース電極9sとして機能してもよい。また、基板1の法線方向から見たとき、ソースラインSは所定の方向に延びる部分と、その部分から上記所定の方向とは異なる方向に延びる延出部分とを有し、延出部分がソース電極9sとして機能してもよい。

# [0049]

本実施形態では、基板1の法線方向から見たとき、ソースラインSは、酸化物半導体層7Aを横切って延びている。ソースラインSのうち酸化物半導体層7Aの上面と接する部分がソース電極9sとして機能する。一方、ドレイン電極9dは、酸化物半導体層7Aと接し、かつ、酸化物半導体層7Aからコンタクト部17に延びている。この例では、ドレイン電極9dは、ソースラインSと略平行に延び、コンタクト部17において画素電極15と接している。

# [0050]

酸化物半導体層7Aおよび金属酸化物層7Bは、例えば、In、GaおよびZnのうち少なくとも1種の金属元素を含んでもよい。本実施形態では、酸化物半導体層7Aおよび金属酸化物層7Bは、例えば、In-Ga-Zn-O系の酸化物を含む。ここで、In-Ga-Zn-O系の酸化物は、In(インジウム)、Ga(ガリウム)、Zn(亜鉛)の三元系酸化物であって、In、GaおよびZnの割合(組成比)は特に限定されず、例えばIn:Ga:Zn=2:2:1、In:Ga:Zn=1:1:1、In:Ga:Zn=1:1:2等を含む。このような酸化物半導体層7Aおよび金属酸化物層7Bは、In-Ga-Zn-O系の半導体を含む酸化物半導体膜から形成され得る。In-Ga-Zn-

○系の半導体は、アモルファスでもよいし、結晶質でもよい。結晶質 In-Ga-Zn-O系の半導体としては、c軸が層面に概ね垂直に配向した結晶質 In-Ga-Zn-O系の半導体が好ましい。なお、結晶質 In-Ga-Zn-O系の半導体の結晶構造は、例えば、特開 2 0 1 2 - 1 3 4 4 7 5 号公報に開示されている。参考のために、特開 2 0 1 2 - 1 3 4 4 7 5 号公報の開示内容の全てを本明細書に援用する。 In-Ga-Zn-O系半導体層を有する TFTは、高い移動度(a-SiTFTに比べ 2 0 倍超)および低いリーク電流(a-SiTFTに比べ 1 0 0 分の 1 未満)を有しているので、駆動 TFT および画素 TFT として好適に用いられる。

## [0051]

酸化物半導体層 7 A および金属酸化物層 7 B は、 I n - G a - Z n - O 系の酸化物の代わりに、他の酸化物を含んでいてもよい。例えば Z n - O 系(Z n O)、Z n - Z n - Z n - Z n - Z n - Z n - Z n - Z n - Z n - Z n - Z n - Z n - Z n - Z n - Z n - Z n - Z n - Z n - Z n - Z n - Z n - Z n - Z n - Z n - Z n - Z n - Z n - Z n - Z n - Z n - Z n - Z n - Z n - Z n - Z n - Z n - Z n - Z n - Z n - Z n - Z n - Z n - Z n - Z n - Z n - Z n - Z n - Z n - Z n - Z n - Z n - Z n - Z n - Z n - Z n - Z n - Z n - Z n - Z n - Z n - Z n - Z n - Z n - Z n - Z n - Z n - Z n - Z n - Z n - Z n - Z n - Z n - Z n - Z n - Z n - Z n - Z n - Z n - Z n - Z n - Z n - Z n - Z n - Z n - Z n - Z n - Z n - Z n - Z n - Z n - Z n - Z n - Z n - Z n - Z n - Z n - Z n - Z n - Z n - Z n - Z n - Z n - Z n - Z n - Z n - Z n - Z n - Z n - Z n - Z n - Z n - Z n - Z n - Z n - Z n - Z n - Z n - Z n - Z n - Z n - Z n - Z n - Z n - Z n - Z n - Z n - Z n - Z n - Z n - Z n - Z n - Z n - Z n - Z n - Z n - Z n - Z n - Z n - Z n - Z n - Z n - Z n - Z n - Z n - Z n - Z n - Z n - Z n - Z n - Z n - Z n - Z n - Z n - Z n - Z n - Z n - Z n - Z n - Z n - Z n - Z n - Z n - Z n - Z n - Z n - Z n - Z n - Z n - Z n - Z n - Z n - Z n - Z n - Z n - Z n - Z n - Z n - Z n - Z n - Z n - Z n - Z n - Z n - Z n - Z n - Z n - Z n - Z n - Z n - Z n - Z n - Z n - Z n - Z n - Z n - Z n - Z n - Z n - Z n - Z n - Z n - Z n - Z n - Z n - Z n - Z n - Z n - Z n - Z n - Z n - Z n - Z n - Z n - Z n - Z n - Z n - Z n - Z n - Z n - Z n - Z n - Z n - Z n - Z n - Z n - Z n - Z n - Z n - Z n - Z n - Z n - Z n - Z n - Z n - Z n - Z n - Z n - Z n - Z n - Z n - Z n -

### [0052]

ここで、従来のTFT基板および参考例のTFT基板と比較しながら、本実施形態による効果をより詳しく説明する。

### [0053]

まず、従来のTFT基板として、特許文献2に開示されたTFT基板を説明する。

### [0054]

図8(a)および(b)は、それぞれ、特許文献2に開示されたTFT基板の平面図および断面図である。TFT基板は複数の画素を有するが、ここでは1つの画素のみを示している。

#### [0055]

図示するように、TFT基板は、ソースラインSと、ゲートラインGとを有している。 ソースラインSおよびゲートラインGによって規定される各画素には、TFT40と、画 素電極45とが形成されている。TFT40は、ゲート電極33と、ゲート絶縁層35と 、ゲート絶縁層35上に形成されたチャネル部37c、ソース部37sおよびドレイン部 37dを有している。TFT40のチャネル部37c、ソース部37sおよびドレイン部 37dと画素電極45とは、同じ酸化物半導体膜から一体的に形成されている。具体的に は、酸化物半導体膜の一部を低抵抗化し、画素電極45、ソース部37s、ドレイン部3 7dとして用いている。酸化物半導体膜の低抵抗化処理は、保護絶縁膜42をマスクとし て行われる。

# [0056]

特許文献2に開示されたTFT基板では、酸化物半導体膜の低抵抗化を行う際のマスクの位置合わせを考慮すると、ソースラインSおよびゲートラインGにより規定される画素領域の面積に対し、画素電極の面積が大幅に小さくなるおそれがある。従って、高い開口率を実現することは困難である。

# [0057]

次に、図8に示すTFT基板に補助容量30を設けた構成を説明する。

# [0058]

図9(a)は、特許文献2に開示された従来のTFT基板(図8)に補助容量30を形成した参考例のTFT基板1000を示す平面図である。図8と同様の構成要素には、同じ参照符号を付している。図9(b)は、本実施形態のTFT基板101の平面図であり、図1(a)に示す平面図のうち1つの画素領域Pixのみを示している。

# [0059]

図9(a)に示すように、参考例のTFT基板1000には、下層電極(補助容量配線)41が設けられている。下層電極41と画素電極45とが絶縁膜を介して重なる部分が補助容量30となる。

# [0060]

50

10

20

30

10

20

30

40

50

下層電極 4 1 は、例えば、ゲートライン G と同じ導電膜(金属膜)を用いて形成される。この場合、補助容量 3 0 の形成によって開口率が低下する。特に、補助容量 3 0 の面積を大きくすると、その分だけ開口率が低下するので、高い開口率を確保することは困難である。

# [0061]

あるいは、下層電極 4 1 は、ゲートライン G とは別の導電膜を利用して形成される場合もある。例えば、画素電極 4 5 の下方に、透明な導電膜からなる下層電極(透明電極) 4 1 を形成することも考えられる。これにより、補助容量 3 0 による開口率の低下を抑制できる。しかしながら、下層電極(透明電極) 4 1 を形成するために、透明導電膜を形成し、パターニングするプロセスを追加する必要がある。

#### [0062]

なお、透明電極膜を用いて下層電極 4 1 を形成する場合には、下層電極 4 1 に補助容量電圧を供給するために、TFT基板のうち、複数の画素領域が配置された表示領域の周辺に位置する周辺領域にCSコンタクト部を設ける必要がある。CSコンタクト部では、例えば、周辺領域まで延設された下層電極 4 1 と、外部から補助容量電圧が供給される金属配線(コモン信号用配線)とを接続する。金属配線は、例えばゲートラインG(またはソースラインS)と同じ金属膜から形成される金属配線であってもよい。

### [0063]

このように、従来のTFT基板に補助容量配線を設ける場合、ゲートラインGと同じ導電膜を用いて補助容量電極を形成すると、開口率が低下するというデメリットがある。一方、別途形成した透明導電膜を用いて補助容量電極を形成すると、マスクプロセスが増加し、製造プロセスが複雑になるというデメリットがある。なお、図8および図9では、特許文献2に開示されたTFT基板を参照して説明したが、VAモードの液晶表示装置に使用される従来の他のTFT基板に補助容量を設ける場合でも同様のデメリットがある。

### [0064]

これに対し、本実施形態では、酸化物半導体層7Aと同じ酸化物膜を利用するので、プロセスを複雑にすることなく、補助容量20の下層電極(導電体領域70c)を形成できる。また、下層電極は透明であるため、開口率を低下させることなく、所望の面積の補助容量20の形成が可能である。従来よりも面積の大きい下層電極(補助容量電極)を形成することができるので、十分な補助容量値を確保できる。例えば図9(b)に示す平面図において、画素領域Pixにおける導電体領域70cを太線で示している。この図からわかるように、ソースラインSおよびゲートラインGによって規定される画素領域Pixのうち、電極9s、9d、ラインS、Gおよびコンタクト部17と重ならない領域の略全体に、補助容量20の下層電極となる導電体領域70cを配置し、補助容量20を形成することが可能である。

# [0065]

さらに、本実施形態によると、導電体領域(補助容量電極)70cとコモン信号用配線 との電気的な接続を容易に確保できる。以下、図10を参照して説明する。

### [0066]

図10は、TFT基板101の模式的な平面図である。TFT基板101は、複数の画素領域を含む表示領域90と、表示領域以外の領域(周辺領域)92とを有している。周辺領域92には、表示領域90を包囲するようにコモン信号用配線Cが形成されている。コモン信号用配線Cは、各画素の補助容量電極(図示せず)に接続されている。また、コモン信号用配線Cには、端子部94を介して、外部からコモン信号が供給される。本実施形態では、各列の画素電極における導電体領域(補助容量電極)70cが一体的に形成され、配線9wによってコモン信号用配線Cに接続されていてもよい。配線9wとコモン信号用配線Cとは、ソースラインSと同じ導電膜を用いて一体的に形成されていてもよい。これにより、各画素の導電体領域(補助容量電極)70cを、周辺領域92にあるコモン信号用配線Cに電気的に接続できる。端子部94は、ゲートラインGと同じ導電膜から形成されていてもよい。端子部94とコモン信号用配線Cとを接続する配線93は、コモン

信号用配線 C と一体的に形成され、ゲート絶縁層に形成されたコンタクトホール内で、端子部 9 4 (または端子部 9 4 と一体的に形成された配線)に接続されていてもよい。なお、後述する実施形態では、配線 9 wの代わりに、接続配線 9 bまたは接続部 9 pをコモン信号用配線 C と一体的に形成することにより、本実施形態と同様に、コモン信号用配線 C と補助容量電極との電気的接続を確保できる。

### [0067]

このように、本実施形態によると、従来のTFT基板において補助容量を形成することによるデメリットをなくすことができる。すなわち、開口率の低下を抑制しつつ、簡便なプロセスで、所望の面積を有する補助容量 2 0 を形成できる。

### [0068]

次に、図2を参照しながら、本実施形態における半導体装置(TFT基板)101の製造方法の一例を説明する。図2(a)~(f)は、TFT基板101におけるTFT10および補助容量20の製造方法を説明するための工程断面図である。これらの断面図は、図1(a)中のA-A<sup>²</sup>線に沿った断面に対応する。

### [0069]

まず、図 2 (a)に示すように、基板 1 上に、ゲート用金属膜を形成した後、これを公知のフォトリソ工程によりパターニングする。これにより、ゲート電極 3 およびゲートライン(図示せず)を含むゲート配線層を形成する。次いで、ゲート配線層を覆うように、ゲート絶縁層 5 を形成する。

# [0070]

基板1として、透明で絶縁性を有する基板を用いることができる。ここでは、ガラス基 板を用いる。

### [0071]

ゲート用電極膜の材料は、特に限定されず、アルミニウム(A1)、タングステン(W)、モリブデン(Mo)、タンタル(Ta)、クロム(Cr)、チタン(Ti)、銅(Cu)等の金属又はその合金を含む膜を適宜用いることができる。また、これら複数の膜を積層した積層膜を用いてもよい。ここでは、ゲート用電極膜として、W膜(厚さ:300nm)を上層、TaN膜(厚さ:30nm)を下層とする積層膜(W/TaN)を用いる

# [0072]

ゲート絶縁層 5 として、例えば、酸化シリコン( $SiO_2$ )層や窒化シリコン( $SiN_x$ )層を用いてもよい。ここでは、ゲート絶縁層 5 として、酸化シリコン( $SiO_2$ )層(厚さ:50nm)を上層、窒化シリコン( $SiN_x$ )層(厚さ:325nm))を下層とする積層膜を用いる。

## [0073]

次いで、図2(b)に示すように、ゲート絶縁層5の上に、例えばスパッタリング法により酸化物半導体膜を形成し、これをパターニングすることにより酸化物半導体層7Aおよび金属酸化物層7Bを得る。酸化物半導体層7Aは、ゲート絶縁層5を介してゲート電極3(ゲートラインG)と重なるように配置される。ここでは、酸化物半導体膜として、例えばIn-Ga-Zn-O系半導体膜(厚さ:50nm)を用いる。酸化物半導体膜の厚さは例えば30nm以上60nm以下であってもよい。

### [0074]

この後、酸化物半導体層 7 A および金属酸化物層 7 B を覆うように、例えばスパッタリング法によりソース用電極膜を形成する。次いで、図 2 ( c )に示すように、公知のフォトリソ工程でソース用電極膜をパターニングすることにより、ソース電極 9 s、ドレイン電極 9 d、およびソースライン(図示せず)を含むソース配線層を形成する。ソース電極 9 s およびドレイン電極 9 d は、酸化物半導体層 7 A と接するように配置される。このようにして、TFT10が形成される。

## [0075]

ソース用電極膜の材料は特に限定せず、アルミニウム(A1)、タングステン(W)、

10

20

30

40

モリブデン(Mo)、タンタル(Ta)、銅(Cu)、クロム(Cr)、チタン(Ti)等の金属又はその合金、若しくはその金属窒化物を含む膜を適宜用いることができる。ここでは、ソース用電極膜として、基板1側から、Ti膜(厚さ:30nm)、A1膜(20nm)およびTi膜(100nm)をこの順で有する積層膜(Ti/Al/Ti)を用いる。

# [0076]

続いて、図 2 ( d )に示すように、ソース配線層および金属酸化物層 7 B を覆うように、第 1 絶縁膜 1 1 を形成する。第 1 絶縁膜 1 1 として、例えば S i O 2 層を用いることができる。第 1 絶縁膜 1 1 の厚さは特に限定しないが、例えば 2 0 0 n m以上であれば、低抵抗化工程でより確実にマスクとして機能し得る。一方、TFT基板の省スペース化のためには 5 0 0 n m以下であることが好ましい。ここでは、第 1 絶縁膜 1 1 として、例えば S i O 2 層(厚さ: 3 0 0 n m)を用いる。

### [0077]

この後、第1絶縁膜11に、金属酸化物層7Bの一部を露出する開口21と、ドレイン電極9dの一部を露出する開口22を設ける。続いて、基板1を、還元性プラズマまたはドーピング元素を含むプラズマに晒す(低抵抗化処理)。ここでは、還元性プラズマであるアルゴンプラズマに晒す。これにより、金属酸化物層7Bのうち開口21によって露出された部分の表面近傍で抵抗が低下し、導電体領域70cとなる。金属酸化物層7Bのうち第1絶縁膜11によってマスクされ、低抵抗化されなかった領域は半導体領域70iとして残る。導電体領域70cの電気抵抗は、半導体領域70iの電気抵抗よりも低く、例えば1×10・2 cm以下であってもよい。導電体領域70cの厚さは、低抵抗化処理の条件によって変わり得る。低抵抗化処理(プラズマ処理)の具体的な方法や、それによって酸化物半導体の電気抵抗を低減するメカニズムは、例えば特許文献2に記載されている。参考のために、特許文献2の開示内容の全てを本明細書に援用する。

#### [0078]

次いで、図2(e)に示すように、第1絶縁膜11上および開口21、22内に、第2絶縁膜12を形成し、次いで、公知のフォトリソ工程により、第2絶縁膜12のうち開口22内に位置する部分を除去する。これにより、第1および第2絶縁膜11、12を貫通し、ドレイン電極9dを露出するコンタクトホールCHが形成される。

# [0079]

第2 絶縁膜12は、例えば窒化珪素(SiNx)膜、酸化珪素(SiOx)膜、酸化窒化珪素(SiOxNy;x>y)膜、窒化酸化珪素(SiNxOy;x>y)膜等を適宜用いることができる。本実施形態では、第2 絶縁膜12は、補助容量を構成する容量絶縁膜としても利用されるため、所定の容量  $C_{CS}$ が得られるように、第2 絶縁膜12の材料や厚さを適宜選択することが好ましい。例えば、誘電率と絶縁性の観点からSiNxが好適に用いられ得る。第2 絶縁膜12の厚さは、例えば70 nm以上180 nm以下である。70 nm以上であれば、より確実に絶縁性を確保できる。一方、180 nm以下であれば、より確実に所望の容量  $C_{CS}$ が得られる。ここでは、第2 絶縁膜12として、SiN膜(厚さ:100 nm)を用いる。

### [0800]

続いて、図2(f)に示すように、第2絶縁膜12上およびコンタクトホールCH内に透明導電膜を形成し、これを公知のフォトリソ工程でパターニングすることにより、画素電極15を形成する。画素電極15は、第2絶縁膜12を介して金属酸化物層7Bの導電体領域70cと重なるように配置される。これにより、導電体領域70cを下層電極、第2絶縁膜12を誘電体層、および画素電極15を上層電極とする補助容量20が形成される。

### [0081]

透明導電膜として、例えばITO(インジウム・錫酸化物)膜、IZO膜やZnO膜(酸化亜鉛膜)などを用いることができる。ここでは、透明導電膜として、ITO膜(厚さ:100nm)を用いる。

10

20

30

40

#### [0082]

このようにして、画素領域 Pix内にTFT10および補助容量20を有するTFT基板101が得られる。

### [0083]

(第2の実施形態)

以下、本発明による半導体装置の第2の実施形態を説明する。本実施形態では、列方向に隣接する2つの画素領域における導電体領域70cを、接続配線を用いて互いに電気的に接続させる点で、第1の実施形態のTFT基板101と異なっている。

## [0084]

図3(a)は、本実施形態の半導体装置(TFT基板)102の平面図である。ここでは、TFT基板102に2次元に配列された複数の画素領域Pixのうち、列方向に隣接された2つの画素領域Pix1、Pix2を示している。

#### [0085]

図3(b)は、図3(a)中のA-A'線に沿った断面図であり、TFT基板102における補助容量20の一部を示す。図3(a)および(b)において、図1(a)および(b)と同様の構成要素には同じ参照符号を付し、説明を省略する。さらに、本実施形態におけるTFT10の断面構造は、図1(b)に示す断面構造と同様であるため、ここでは図示を省略する。

### [0086]

TFT基板102では、各画素領域Pix1、Pix2における金属酸化物層7Bは、 互いに分離して形成されている。

#### [0087]

また、TFT基板102は、ソース電極9sやソースラインSと同じ導電膜から形成された接続配線9bを備えている。接続配線9bは、第1および第2画素領域Pix1、Pix2を横切るように列方向に延設され、各画素領域Pix1、Pix2における金属酸化物層7Bの導電体領域70cを互いに電気的に接続している。基板1の法線方向から見たとき、接続配線9bは、複数のゲートラインGを跨いで形成されていてもよい。

### [0088]

第1および第2画素領域Pi×1、Pi×2における金属酸化物層7Bの導電体領域70cを接続する接続配線9bは、図示するように、ゲートラインG(m)を跨いで延設される。なお、基板1の法線方向から見たとき、各列における複数の画素領域Pi×を横切るように接続配線9bを延設し、その列にある全ての画素領域Pi×の導電体領域70cを電気的に接続してもよい。

# [0089]

図示するように、ゲートライン G ( m ) は、TFT10の酸化物半導体層7Aの少なくとも一部と重なる第1部分と、第1部分よりも幅の小さい第2部分とを含んでいてもよい。接続配線9bは、ゲートライン G ( m ) の第2部分を跨いで形成されていてもよい。

### [0090]

本実施形態でも、第1の実施形態と同様に、金属酸化物層7Bの導電体領域70cを補助容量20の下層電極として機能させる。また、接続配線9bを、ソースラインSと同じ導電膜を利用して形成する。このため、製造プロセスを複雑にすることなく、補助容量20および接続配線9bを形成できる。補助容量20は透明材料から形成されるので、補助容量20に起因する開口率の低下を抑制できる。また、開口率を低下させることなく補助容量20の面積を拡大できるので、所望の補助容量値を確保できる。

### [0091]

さらに、本実施形態によると、次のような効果も得られる。

### [0092]

前述した第1の実施形態では、金属酸化物層7Bは、ゲートラインGを跨いで列方向に延設されている。しかしながら、このような構造を画素ピッチが小さい高精細パネルに適用すると、TFT10と金属酸化物層7Bとを十分に離して配置することが困難になる。

10

20

30

40

10

20

30

40

50

特に画素領域 P i x において T F T 1 0 の y - スライン S ( n + 1 ) 側に位置する領域で、 T F T 1 0 と金属酸化物層 7 B との間隔が狭くなる。間隔を大きくするために、金属酸化物層 7 B の幅を小さくすると、画素領域 P i x 1 、P i x 2 における金属酸化物層 7 B の導電体領域 7 0 c 同士を低抵抗で接続することが困難になる。

# [0093]

### [0094]

なお、本実施形態では、接続配線9bを設ける分だけ、第1の実施形態よりも開口率が低下する。しかしながら、接続配線9bの面積は、補助容量20の面積よりも十分小さいので、ゲートラインGと同じ導電膜を用いて補助容量配線を形成する場合(補助容量20の面積に応じて開口率が低下する)と比べて、TFT基板の開口率を高めることができる

### [0095]

次に、図面を参照しながら、TFT基板102の製造方法の一例を説明する。

#### 【0096】

図4(a)~(d)は、TFT基板102の製造方法を説明するための工程断面図である。

# [0097]

まず、図 2 ( a )および( b )を参照しながら前述したように、基板 1 上にゲート電極 3 、ゲート絶縁層 5 、酸化物半導体層 7 A および金属酸化物層 7 B を形成する。

### [0098]

次いで、図4(a)に示すように、ソース用電極膜を形成し、パターニングすることにより、ソース電極9s、ドレイン電極9dおよびソースライン(不図示)に加え、接続配線9bも形成する。接続配線9bは、各画素領域Pixにおける金属酸化物層7Bの一部上に形成される。具体的には、金属酸化物層7Bのうち導電体領域となる領域の一部上に形成される。このとき、金属酸化物層7Bのうち接続配線9bと接する部分は、接続配線9b(金属)と接することによって低抵抗化され、導電体領域70cとなる。この低抵抗化を行うためには、接続配線9bの材料(ソース用電極膜の材料)として、金属酸化物層7BがIn・Ga・Zn・O系酸化物層であれば、例えば、Inよりも標準電極電位の低いTi、Mo、Alなどの金属を用いることができる。

### [0099]

この後、図4(b)に示すように、開口21および22を有する第1絶縁膜11を形成する。次いで、低抵抗化処理(プラズマ処理)を行い、金属酸化物層7Bのうち第1絶縁膜11の開口21によって露出された部分を低抵抗化する。第1絶縁膜11の材料や厚さ、低抵抗化処理の方法は、図2(d)を参照しながら前述した材料、厚さおよび低抵抗化処理の方法と同じであってもよい。

# [0100]

これにより、金属酸化物層7Bのうち開口21によって露出され、かつ、接続配線9bと接していない部分が低抵抗化される。この結果、金属酸化物層7Bのうち開口21によって露出された領域に導電体領域70cが形成される。導電体領域70cは、本工程で低抵抗化された部分と接続配線9bと接する部分とを含む。

### [0101]

この後、図4(c)および図4(d)に示すように、第2絶縁膜12および画素電極1

5 を形成することにより、TFT基板102を得る。第2絶縁膜12および画素電極15を形成する工程は、図2(e)および図2(f)を参照しながら前述した工程と同様である。

### [0102]

なお、TFT基板102の製造方法は、図4に示す方法に限定されない。例えば、TFT10として、チャネル領域上にエッチストップ膜を有する、いわゆるエッチストップ構造のTFTを形成し、エッチストップ膜を利用して、金属酸化物層7Bの低抵抗化を行うことも可能である。

## [0103]

まず、図 2 ( a )および( b )を参照しながら前述したように、基板 1 上にゲート電極 3 、ゲート絶縁層 5 、酸化物半導体層 7 A および金属酸化物層 7 B を形成する。

### [0104]

次いで、図5(a)に示すように、酸化物半導体層7Aおよび金属酸化物層7Bを覆うエッチストップ膜14を形成する。この後、エッチストップ膜14に、酸化物半導体層7Aのうちチャネル領域の両側に位置する領域を露出する開口23、24と、金属酸化物層7Bの一部を露出する開口25とを形成する。

#### [0105]

続いて、前述の実施形態と同様の方法で低抵抗化処理を行う。これにより、酸化物半導体層7Aのうちエッチストップ膜14の開口23、24によって露出された部分と、金属酸化物層7Bのうちエッチストップ膜14の開口25によって露出された部分とが低抵抗化されて、導電体領域70a、70b、70cとなる。酸化物半導体層7Aおよび金属酸化物層7Bのうち低抵抗化されなかった領域は半導体領域70iとして残る。

### [0106]

この後、図5(b)に示すように、エッチストップ膜14上および開口23、24、25内にソース用電極膜を形成し、パターニングすることにより、ソース電極9s、ドレイン電極9d、ソースライン(図示せず)および接続配線9bを形成する。ソース電極9sは開口23内で導電体領域70aと接し、ドレイン電極9dは開口24内で導電体領域70bと接するように形成される。また、接続配線9bは、開口25内において、導電体領域70cの一部と接するように形成される。ソース用電極膜の材料や厚さは、図2(c)を参照しながら前述した材料および厚さと同じであってもよい。

# [0107]

この後、図5(c)および図5(d)に示すように、第2絶縁膜12および画素電極15を形成することにより、TFT基板102′を得る。第2絶縁膜12および画素電極15を形成する工程は、図2(e)および図2(f)を参照しながら前述した工程と同様である。このようにして、本実施形態の他のTFT基板102′を得る。

# [0108]

# (第3の実施形態)

以下、本発明による半導体装置の第3の実施形態を説明する。本実施形態では、列方向に隣接する2つの画素領域における導電体領域70cを、接続部を用いて、互いに電気的に接続させる点で、第1の実施形態のTFT基板101と異なっている。

# [0109]

図6(a)は、本実施形態の半導体装置(TFT基板)103の平面図である。ここでは、TFT基板103に2次元に配列された複数の画素領域Pixのうち、列方向に配列された3つの画素領域(第1画素領域Pix1、第2画素領域Pix2および第3画素領域Pix3)を示している。

# [0110]

図6(b)は、図6(a)中のA・A<sup>'</sup>線に沿った断面図であり、TFT基板103における補助容量20の一部を示す。図6(a)および(b)において、図1(a)および(b)と同様の構成要素には同じ参照符号を付し、説明を省略する。さらに、本実施形態におけるTFT10の断面構造は、図1(b)に示す断面構造と同様であるため、ここで

20

10

30

40

は図示を省略する。

## [0111]

TFT基板103では、第2の実施形態と同様に、各画素領域Pi×1、Pi×2、Pi×3における金属酸化物層7Bは、互いに分離して形成されている。

# [0112]

また、TFT基板103は、ソース電極9sやソースラインSと同じ導電膜から形成された複数の接続部9pを備えている。複数の接続部9pは、互いに分離されている。各接続部9pは、列方向に隣接する2つの画素領域における金属酸化物層7Bの導電体領域70cを互いに電気的に接続するように配置されている。

### [0113]

上記の構成を、図6(a)に示す画素領域  $Pi \times 1 \sim Pi \times 3$  を用いて、より具体的に説明する。第2画素領域  $Pi \times 2$  における金属酸化物層 7 B の導電体領域 7 0 c は、第1の接続部 9 p (m) (mは自然数)によって、第1画素領域  $Pi \times 1$  における金属酸化物層 7 B の導電体領域 7 0 c に接続され、かつ、第2の接続部 9 p (m+1) によって、第3画素領域  $Pi \times 3$  における金属酸化物層 7 B の導電体領域 7 0 c と電気的に接続されている。第1の接続部 9 p (m) と第2の接続部 9 p (m+1) とは、互いに分離して形成されている。また、各接続部 9 p (m) および第2の接続部 9 p (m+1) は、それぞれ、ゲートライン G (m) および G (m+1) を跨ぐように延設されている。

# [0114]

図示するように、基板1の法線方向から見たとき、ゲートラインG(m)、G(m+1)は、それぞれ、TFT10の酸化物半導体層7Aの少なくとも一部と重なる第1部分と、第1部分よりも幅の小さい第2部分とを含んでいてもよい。第1の接続部9p(m)および第2の接続部9p(m+1)は、それぞれ、ゲートラインG(m)およびG(m+1)の第2部分を跨いで形成されていてもよい。

### [0115]

複数の接続部9pは、第2の実施形態における接続配線9bを、各導電体領域70cの中央部上で分断された構造を有していてもよい。また、各接続部9pは、接続しようとする2つの導電体領域70cの端部近傍のみと接していてもよい。

# [0116]

本実施形態でも、前述の実施形態と同様に、金属酸化物層7Bの導電体領域70cを補助容量20の下層電極として機能させる。また、接続部9pを、ソースラインSと同じ導電膜を利用して形成する。このため、製造プロセスを複雑にすることなく、補助容量20および接続部9pを形成できる。補助容量20は透明材料から形成されるので、補助容量20に起因する開口率の低下を抑制できる。さらに、開口率を低下させることなく補助容量20の面積を拡大できるので、所望の補助容量値を確保できる。

# [0117]

また、第2の実施形態と同様に、第1および第2画素領域Pi×1、Pi×2における金属酸化物層7Bは、互いに分離したパターンを有する。このため、金属酸化物層7Bと、コンタクト部17およびTFT10とを十分に離して配置することが可能である。また、第1および第2画素領域Pi×1、Pi×2における金属酸化物層7Bの導電体領域70cは、ソース用電極膜からなる、より低抵抗な接続部9pを用いて接続される。従って、第1の実施形態よりも、補助容量電極の抵抗を低減でき、負荷を小さくできる。

# [0118]

なお、本実施形態では、複数の接続部9pを設ける分だけ、第1の実施形態よりも開口率は低下する。しかしながら、各画素領域Pixにおいて、接続部9pに必要な面積は、補助容量20の面積よりも十分小さいことから、ゲートラインGと同じ導電膜から補助容量配線を形成する場合(補助容量20の面積に応じて開口率が低下する)よりも高い開口率を実現できる。さらに、本実施形態によると、画素領域Pixを横切るように接続配線9bを設ける第2の実施形態よりも、補助容量20の形成に起因する開口率の低下を抑制

10

20

30

40

できる。

## [0119]

図示していないが、基板1の法線方向から見たとき、各列における全ての画素領域Pixの導電体領域70cを、接続部9pで電気的に接続してもよい。これにより、配線構造を複雑にすることなく、複数の画素領域Pixの導電体領域70c(補助容量電極として機能する)に、共通の補助容量電圧(Cs電圧)を供給し得る。

#### [ 0 1 2 0 ]

本実施形態のTFT基板103は、図4を参照しながら前述したTFT基板102と同様の方法で製造され得る。ただし、ソース用電極膜のパターニング工程(図4(a))において、接続配線9bの代わりに、互いに分断された複数の接続部9pを形成する。また、図5を参照しながら前述した方法と同様の方法で、エッチストップ構造を有するTFTを備えたTFT基板を製造することも可能である。なお、これらの製造工程を説明する断面構造は、接続配線9bの代わりに接続部9pが形成される点を除くと、前述の実施形態における図4および図5に示す断面構造と同じであるため、ここでは図示していない。

### [0121]

上述したTFT基板101~103は、例えば液晶表示装置のアクティブマトリクス基板として用いることができる。

#### [0122]

図7は、上記実施形態のTFT基板101~103を用いた液晶表示装置200の構成の一例を示す模式的な断面図である。

[0123]

液晶表示装置200は、TFT基板100と、対向基板(例えばガラス基板)151と、液晶層153とを有している。TFT基板100は、上述したTFT基板101~103のいずれであってもよい。対向基板151の液晶層153側には、対向電極152が形成されている。液晶表示装置200では、TFT基板100の画素電極15と対向電極152との間に存在する液晶層153に電圧が印加される。画素電極15および対向電極152のそれぞれの液晶層153側には必要に応じて配向膜(例えば垂直配向膜)が形成される。

# [0124]

液晶表示装置200は、例えば次のようにして製造され得る。

[ 0 1 2 5 ]

まず、ガラス基板上に、遮光膜(例えば厚さ: 2 0 0 n mの T i 膜)を形成し、フォトリソ工程により所望の形状にパターニングする。これにより、ブラックマトリクスを形成する。次いで、ブラックマトリクスが形成されたガラス基板上に、絶縁膜(例えば厚さ: 2 0 0 n mの S i O  $_2$  膜)を形成する。この後、絶縁膜上に、対向電極 1 5 2 を形成する。対向電極 1 5 2 は、透明導電膜(例えば厚さ: 1 0 0 n mの I T O)をスパッタ法で形成し、これをパターニングすることによって形成される。このようにして対向基板 1 5 1 を得る。

[0126]

次に、上記の実施形態で説明した方法で形成されたTFT基板100(TFT基板10 1~103)上にフォトスペーサーを配置した後、TFT基板100と対向基板151と を貼り合わせる。続いて、これらの基板100、151の間に液晶を注入することにより 、液晶層153を形成する。次いで、液晶層153が形成された基板100、151を分 断し、液晶表示装置200を得る。

### [0127]

液晶表示装置200は、例えば垂直配向モード(VAモード)液晶表示装置である。もちろん、本発明の実施形態による液晶表示装置はこれに限られず、例えば、TFT基板上に、画素電極と対向電極とを有する、例えば、In-Plane Switching(IPS)モードやFringe Field Switching(FFS)モードのような横電界モードの液晶表示装置にも適用できる。IPSモードやFFSモードの液晶表

10

20

30

40

示装置のTFTの構造は良く知られているので、説明を省略する。

## [0128]

なお、FFSモードの液晶表示装置などには、2層の透明電極層が設けられるため、そ れらを利用した補助容量の形成が可能である。これに対し、VAモードの液晶表示装置に は、通常、単一の透明電極層(画素電極)しか設けられていない。このため、上記実施形 態をVAモードの液晶表示装置に適用すると、別途透明電極層を追加することなく、透明 な補助容量を形成できるので、特に顕著な効果が得られる。

### [0129]

上記では液晶表示装置を例に説明したが、上記実施形態のTFT基板101~103は 、有機エレクトロルミネセンス(EL)表示装置、無機エレクトロルミネセンス表示装置 MEMS表示装置等の他の表示装置にも用いられ得る。

10

30

【産業上の利用可能性】

# [0130]

本発明の実施形態は、アクティブマトリクス基板等の回路基板、液晶表示装置、有機工 レクトロルミネセンス(EL)表示装置および無機エレクトロルミネセンス表示装置等の 表示装置、イメージセンサー装置等の撮像装置、画像入力装置や指紋読み取り装置等の電 子装置などの薄膜トランジスタを備えた装置に広く適用できる。

### 【符号の説明】

[0131]

20 1 基板 3 ゲート電極 ゲート絶縁層 5 7 A 酸化物半導体層(活性層) 7 B 金属酸化物層

ソース電極 9 s

9 d ドレイン電極

1 1 第1絶縁膜

1 2 第2絶縁膜

1 3 層間絶縁層

1 5 画素電極

1 7 コンタクト部

2 1 第1絶縁膜の開口

金属酸化物層の半導体領域 7 0 i

7 0 c 金属酸化物層の導電体領域

1 0 酸化物半導体TFT

2 0 補助容量

S ソースライン

ゲートライン

101、102、103、102 ' 半導体装置(TFT基板)

# 【図1】

# 【図2】

【図3】

【図4】

# 【図5】

# 【図6】

【図7】

# 【図8】

# 【図9】

【図10】

# フロントページの続き

(74)代理人 100202197

弁理士 村瀬 成康

(74)代理人 100202142

弁理士 北 倫子

(72)発明者 内田 誠一

大阪府大阪市阿倍野区長池町22番22号 シャープ株式会社内

# 審査官 佐藤 洋允

(56)参考文献 特開2011-91110(JP,A)

国際公開第2013/172185(WO,A1)

国際公開第2012/020525(WO,A1)

国際公開第2011/148537(WO,A1)

(58)調査した分野(Int.CI., DB名)

G02F1/136-1/1368

H01L21/28

H01L29/786