# (19)**日本国特許庁(JP)**

# (12) 公開特許公報(A)

(11)公開番号 **特開2022-147141** (**P2022-147141A**)

(43)公開日 令和4年10月6日(2022.10.6)

| (51)国際特許分類 |                   | FI      |          |       | テーマコード(参考) |

|------------|-------------------|---------|----------|-------|------------|

| H 0 1 L    | 27/11582(2017.01) | H 0 1 L | 27/11582 |       | 5 F 0 3 3  |

| H 0 1 L    | 21/336 (2006.01)  | H 0 1 L | 29/78    | 3 7 1 | 5 F 0 8 3  |

| H 0 1 L    | 21/768 (2006.01)  | H 0 1 L | 21/90    | В     | 5 F 1 0 1  |

|            |                   | H 0 1 L | 21/90    | М     |            |

|                     | H 0 1 L 21/90                                     |                       | M                                   |                                                                                             |                                             |  |

|---------------------|---------------------------------------------------|-----------------------|-------------------------------------|---------------------------------------------------------------------------------------------|---------------------------------------------|--|

|                     | 審済                                                | 查請求 未請求               | 請求項の数                               | 5 O L                                                                                       | (全23頁)                                      |  |

| (21)出願番号<br>(22)出願日 | 特願2021-48271(P2021-48271)<br>令和3年3月23日(2021.3.23) | (71)出願人(74)代理人(72)発明者 | 東京都港区芝浦<br>110002147弁<br>務所<br>濱 裕之 | プクシア株式会社<br>都港区芝浦三丁目1番21号<br>002147弁理士法人酒井国際特許事<br>に<br>総之<br>都港区芝浦三丁目1番21号 キオ              |                                             |  |

|                     |                                                   | Fターム (参考              | ₹) 5F033                            | HH04 HH18<br>HH21 HH32<br>JJ08 JJ18 JJ1<br>JJ21 JJ32 JJ3<br>MM12 MM13<br>N33<br>QQ09 QQ10 Q | HH33 JJ04<br>19 JJ20<br>33 MM11<br>3 MM15 N |  |

# (54)【発明の名称】 半導体記憶装置

# (57)【要約】

【課題】積層体の一部の領域に絶縁層を残しつつ、他の 領域の絶縁層をより確実に導電層に置き換えること。

【解決手段】実施形態の半導体記憶装置1は、複数の第1の導電層WLが第1の絶縁層OLを介して積層される第1の積層体LMa,LMbと、複数の第2の絶縁層NLが第1の絶縁層OLを介して積層され、第1の積層体LMa,LMbに周囲を囲まれた第2の積層体LMar,LMbrの両の方向に延び、積層方向および第1の方向と交差する第1の方向に延び、積層方向および第1の方向と交差する第2の方向における第2の積層体LMar,LMbrの間に配置される1対の第1の板状部BRと、を備え、1対の第1の板状部BRの第1の積層体LMa,LMbに対向する第1の側壁は、第1の積層体LMa,LMbの第1の絶縁層OLの端面と接する金属元素含有層62を有する。

【選択図】図2

10

#### 【特許請求の範囲】

#### 【請求項1】

複数の第1の導電層が第1の絶縁層を介して積層される第1の積層体と、

複数の第2の絶縁層が前記第1の絶縁層を介して積層され、前記第1の積層体の各層の 積層方向から見て、前記第1の積層体に周囲を囲まれた第2の積層体と、

前記積層方向および前記積層方向と交差する第1の方向に延び、前記積層方向および前記第1の方向と交差する第2の方向における前記第2の積層体の両側で、前記第1及び第2の積層体の間に配置される1対の第1の板状部と、

前記第1の方向に延び、前記1対の第1の板状部から離れた位置で、前記1対の第1の板状部を前記第2の方向の両側から挟み、前記第1の積層体内を前記積層方向に延びる1対の第2の板状部と、を備え、

前記1対の第1の板状部の前記第1の積層体に対向する第1の側壁は、前記第1の積層体の前記第1の絶縁層の端面と接する金属元素含有層を有する、半導体記憶装置。

#### 【請求項2】

前記第1の側壁は、

前記第1の積層体の前記複数の第1の導電層および前記第1の絶縁層の高さ位置全体に亘って配置される第3の絶縁層を有し、

前記第1の絶縁層の高さ位置において、前記第3の絶縁層と前記第1の絶縁層の端面の間には前記金属元素含有層が介在する、

請求項1に記載の半導体記憶装置。

#### 【請求項3】

前記第3の絶縁層は、

前記複数の第1の導電層のそれぞれの高さ位置において、前記複数の第1の導電層の端 面と接する、

請求項2に記載の半導体記憶装置。

# 【請求項4】

前記複数の第1の導電層の前記端面は、前記第1の絶縁層の前記端面よりも前記1対の板状部から後退した位置にあり、

前記第3の絶縁層は、

前記複数の第1の導電層のそれぞれの高さ位置において、前記複数の第1の導電層側へと突出する、

請求項3に記載の半導体記憶装置。

# 【請求項5】

複数の第1の導電層が第1の絶縁層を介して積層される第1の積層体と、

複数の第2の絶縁層が前記第1の絶縁層を介して積層され、前記第1の積層体の各層の 積層方向から見て、前記第1の積層体に周囲を囲まれた第2の積層体と、

前記積層方向および前記積層方向と交差する第1の方向に延び、前記積層方向および前記第1の方向と交差する第2の方向における前記第2の積層体の両側で、前記第1及び第 2の積層体の間に配置される1対の第1の板状部と、

前記第1の方向に延び、前記1対の第1の板状部から離れた位置で、前記1対の第1の 板状部を前記第2の方向の両側から挟み、前記第1の積層体内を前記積層方向に延びる1 対の第2の板状部と、を備え、

前記1対の第1の板状部の前記第2の積層体に対向する第2の側壁は、前記第2の積層体の前記複数の第2の絶縁層および前記第1の絶縁層の高さ位置全体に亘って配置され、前記複数の第2の絶縁層および前記第1の絶縁層のそれぞれの端面と接する金属元素含有層を有する、

半導体記憶装置。

【発明の詳細な説明】

【技術分野】

10

20

30

[0001]

本発明の実施形態は、半導体記憶装置に関する。

【背景技術】

[00002]

3 次 元 不 揮 発 性 メ モ リ 等 の 半 導 体 記 憶 装 置 の 製 造 工 程 で は 、 例 え ば 複 数 の 絶 縁 層 を 導 電 層に置き換えて、導電層の積層体を形成する。例えば積層体の上下構造を接続するコンタ クトを通すため、積層体の一部が、導電層に置き換えられることなく絶縁層のまま維持さ れることがある。

【先行技術文献】

【特許文献】

[00003]

【 特 許 文 献 1 】 米 国 特 許 出 願 公 開 第 2 0 1 9 / 0 0 6 7 3 1 4 号 明 細 書

【特許文献2】米国特許出願公開第2017/0179154号明細書

【発明の概要】

【発明が解決しようとする課題】

[00004]

1 つの実施形態は、積層体の一部の領域に絶縁層を残しつつ、他の領域の絶縁層をより 確実に導電層に置き換えることができる半導体記憶装置を提供することを目的とする。

【課題を解決するための手段】

[00005]

実施形態の半導体記憶装置は、複数の第1の導電層が第1の絶縁層を介して積層される 第1の積層体と、複数の第2の絶縁層が前記第1の絶縁層を介して積層され、前記第1の 積層体の各層の積層方向から見て、前記第1の積層体に周囲を囲まれた第2の積層体と、 前記積層方向および前記積層方向と交差する第1の方向に延び、前記積層方向および前記 第1の方向と交差する第2の方向における前記第2の積層体の両側で、前記第1及び第2 の積層体の間に配置される1対の第1の板状部と、前記第1の方向に延び、前記1対の第 1の板状部から離れた位置で、前記1対の第1の板状部を前記第2の方向の両側から挟み 、 前 記 第 1 の 積 層 体 内 を 前 記 積 層 方 向 に 延 び る 1 対 の 第 2 の 板 状 部 と 、 を 備 え 、 前 記 1 対 の第1の板状部の前記第1の積層体に対向する第1の側壁は、前記第1の積層体の前記第 1の絶縁層の端面と接する金属元素含有層を有する。

【図面の簡単な説明】

[0006]

【図1】図1は、実施形態1にかかる半導体記憶装置の概略の構成例を示す図である。

【図2】図2は、実施形態1にかかる半導体記憶装置の詳細な構成例を示すY方向に沿う 断面図である。

【図3】図3は、実施形態1にかかる半導体記憶装置の製造方法の手順の一例を示すY方 向に沿う断面図である。

【 図 4 】 図 4 は 、 実 施 形 態 1 に か か る 半 導 体 記 憶 装 置 の 製 造 方 法 の 手 順 の 一 例 を 示 す Y 方 向に沿う断面図である。

【 図 5 】 図 5 は、 実 施 形 態 1 に か か る 半 導 体 記 憶 装 置 の 製 造 方 法 の 手 順 の 一 例 を 示 す Y 方 向に沿う断面図である。

【 図 6 】 図 6 は、 実 施 形 態 1 に か か る 半 導 体 記 憶 装 置 の 製 造 方 法 の 手 順 の 一 例 を 示 す Y 方 向に沿う断面図である。

【 図 7 】 図 7 は 、 実 施 形 態 1 に か か る 半 導 体 記 憶 装 置 の 製 造 方 法 の 手 順 の 一 例 を 示 す Y 方 向に沿う断面図である。

【 図 8 】 図 8 は、 実 施 形 態 1 に か か る 半 導 体 記 憶 装 置 の 製 造 方 法 の 手 順 の 一 例 を 示 す Y 方 向に沿う断面図である。

【 図 9 】 図 9 は、 実 施 形 態 2 に か か る 半 導 体 記 憶 装 置 の 製 造 方 法 の 手 順 の 一 例 を 示 す Y 方 向に沿う断面図である。

【 図 1 0 】 図 1 0 は 、 実 施 形 態 2 に か か る 半 導 体 記 憶 装 置 の 製 造 方 法 の 手 順 の 一 例 を 示 す

10

20

30

40

20

30

Y方向に沿う断面図である。

# 【発明を実施するための形態】

#### [0007]

以下に、本発明につき図面を参照しつつ詳細に説明する。なお、下記の実施形態により、本発明が限定されるものではない。また、下記実施形態における構成要素には、当業者が容易に想定できるものあるいは実質的に同一のものが含まれる。

# [0008]

# [実施形態1]

以下、図面を参照して実施形態1について詳細に説明する。

#### [0009]

(半導体記憶装置の構成例)

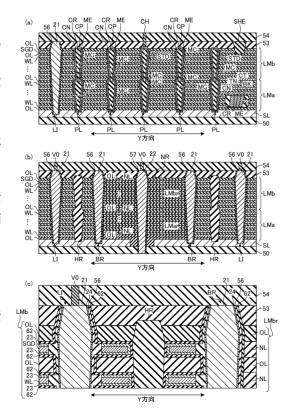

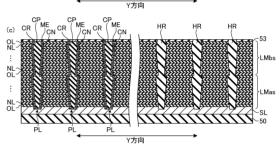

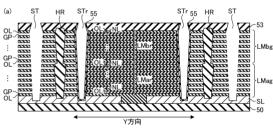

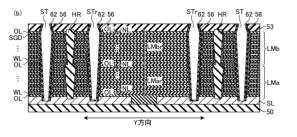

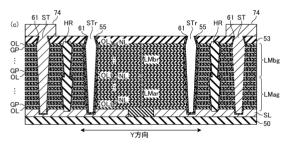

図1は、実施形態1にかかる半導体記憶装置1の概略の構成例を示す図である。図1(a)は、半導体記憶装置1の概略構成を示すX方向に沿う断面図であり、図1(b)は、半導体記憶装置1の貫通コンタクト領域TPを含む領域の横断面図である。ただし、図1(a)においては図面の見やすさを考慮してハッチングを省略する。また、図1(a)においては一部の上層配線が省略されている。

#### [0010]

なお、本明細書において、 X 方向および Y 方向は共に、後述するワード線 W L の面の向きに沿う方向であり、 X 方向と Y 方向とは互いに直交する。また、後述するワード線 W L の電気的な引き出し方向を第 1 の方向と呼ぶことがあり、この第 1 の方向は X 方向に沿う方向である。また、第 1 の方向と交差する方向を第 2 の方向と呼ぶことがあり、この第 2 の方向は Y 方向に沿う方向である。ただし、半導体記憶装置 1 は製造誤差を含みうるため、第 1 の方向と第 2 の方向とは必ずしも直交しない。

# [0011]

図1に示すように、半導体記憶装置1は、基板SB上に、周辺回路CUA、メモリ領域MR、貫通コンタクト領域TP、及び階段領域SRを備える。

#### [ 0 0 1 2 ]

基板SBは、例えばシリコン基板等の半導体基板である。基板SB上にはトランジスタTR及び配線等を含む周辺回路CUAが配置されている。周辺回路CUAは、後述するメモリセルの動作に寄与する。

# [0013]

周辺回路CUAは絶縁層50で覆われている。絶縁層50上にはソース線SLが配置されている。ソース線SL上には複数の導電層が積層されており、その中の少なくとも一部はワード線WLとして機能する。

# [0014]

複数の第1の導電層としてのワード線WLは、それぞれX方向に沿って延び、Y方向に並ぶ複数のコンタクトLIによってY方向に分割されている。すなわち、複数のコンタクトLIのそれぞれは、ワード線WLの面に沿うX方向に沿って延び、ワード線WLを積層方向に貫通する。

#### [0015]

1 対の第 2 の板状部としての 2 つの隣接するコンタクトLIの間には、複数のメモリ領域 M R 、絶縁領域 N R を含む貫通コンタクト領域 T P 、及びワード線 W L の両端部に形成される階段領域 S R が配置されている。

# [0016]

また、2つのコンタクトLI間には、ソース線SL上に積層される上述の複数の導電層のうち、少なくとも最上層の導電層を含む1つまたは複数の導電層を分離する分離層SHEが配置されている。分離層SHEは、メモリ領域MR、及び貫通コンタクト領域TPの絶縁領域NRを除く領域をX方向に沿って延びる。分離層SHEが両端部の階段領域SRにまで延びていてもよい。

## [0017]

50

第1の導電層としての選択ゲート線SGDは、最上層の導電層を含む1つまたは複数の 導電層を分離層SHEが貫通することによって形成される。つまり、分離層SHEは、積 層される1つまたは複数の導電層を、分離層SHEのY方向両側に配置される選択ゲート 線SGDのパターンに区画する。なお、図1(b)は、半導体記憶装置1の選択ゲート線 SGDの高さ位置における横断面を示している。

[0018]

メモリ領域MRには、ワード線WLを積層方向に貫通する複数のピラーPLが配置されている。ピラーPLとワード線WLとの交差部には複数のメモリセルが形成される。これにより、半導体記憶装置1は、例えばメモリ領域MRにメモリセルが3次元に配置された3次元不揮発性メモリとして構成される。ピラーPLの上端部には、ピラーPLとビット線等の上層配線とを接続するプラグが配置されている。

[0019]

階段領域SRは、複数のワード線WLが階段状に引き出された構成を有する。階段状に引き出された複数のワード線WLの個々のテラス部には、ワード線WLと上層配線等とを接続するコンタクトCCが配置されている。なお、本明細書においては、階段領域SRの各段のテラス面が向いた方向を上方向と規定する。

[0020]

貫通コンタクト領域TPは、例えば隣接する2つのコンタクトLI間で、メモリ領域MRによりX方向に挟まれた領域に配置される。貫通コンタクト領域TPには、絶縁領域NR、1対の第1の板状部としての板状部BR、複数のコンタクトC4、及び複数の柱状部HRが配置されている。

[0021]

絶縁領域NRは、ワード線WLの積層方向から見て、積層された複数のワード線WLに周囲を取り囲まれている。絶縁領域NR内には、ワード線WLは配置されず、複数種類の絶縁層が積層されている。

[0022]

板状部BRは、絶縁領域NRのY方向の両側に、X方向に沿って延びるように配置される。すなわち、板状部BRのそれぞれは、絶縁領域NR両側で、X方向に沿う方向およびワード線WLの積層方向に延びる。ただし、図1の例に依らず、絶縁領域NRを他の領域から充分に分離できるのであれば、板状部BRが他の形状および配置を有していてもよい

[0023]

1 対の第 1 の板状部としての 2 つの板状部 B R の間には、下方の基板 S B 上に配置された周辺回路 C U A と各種の上層配線等とを接続するコンタクト C 4 が配置されている。

[0024]

図1の例では、X方向に並ぶ複数のコンタクトC4が絶縁領域NR内に配置されている。ただし、コンタクトC4は、絶縁領域NR内に1つのみ配置されてもよい。またあるいは、コンタクトC4は、X方向に替えて、あるいは加えて、Y方向にも複数配置されてもよい。

[0025]

このようなコンタクトC4によって、ピラーPL及びワード線WL等の構成は、上層配線を介して周辺回路CUAに接続される。

[0026]

複数の柱状部HRは、コンタクトC4の周辺を除く貫通コンタクト領域TPに分散して配置される。個々の柱状部HRは、ワード線WLを積層方向に貫通しており、後述する半導体記憶装置1の製造工程において、半導体記憶装置1の積層構造を支える支柱として機能する。

[0027]

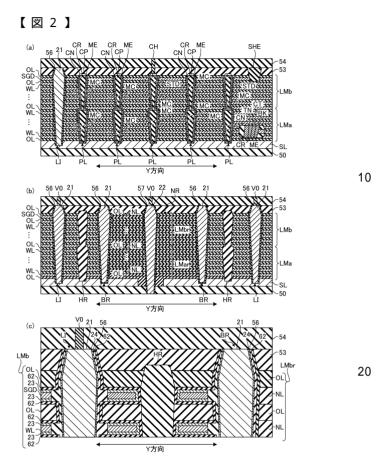

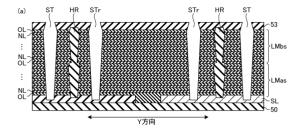

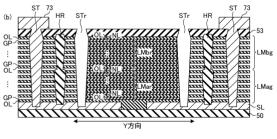

図2は、実施形態1にかかる半導体記憶装置1の詳細な構成例を示すY方向に沿う断面図である。図2(a)は、メモリ領域MRにおける1つのコンタクトLIを含む一部断面

10

20

30

20

30

40

50

図であり、図2(b)は貫通コンタクト領域TPにおける1対のコンタクトLI間を示す一部断面図である。図2(c)は、貫通コンタクト領域TPにおける1つのコンタクトLIと1つの板状部BRとの間を示す拡大断面図である。なお、図2において、周辺回路CUA及び一部の上層配線は省略されている。

[0028]

図 2 ( a )( b )に示すように、ソース線 S L 上には積層体 L M a が配置され、積層体 L M a 上には積層体 L M b が配置されている。

[0029]

第1の積層体としての積層体LMa,LMbはともに、複数の第1の導電層としてのワード線WLが第1の絶縁層としての絶縁層OLを介して積層された構成を有する。積層体LMa,LMbにおけるワード線WLの積層数は任意である。

[0030]

また、積層体 L M b は、最上層のワード線 W L の上層に、第 1 の絶縁層としての絶縁層 O L を介して第 1 の導電層としての 1 つまたは複数の選択ゲート線 S G D を備える。換言すれば、上述のように、積層体 L M b の最上層の導電層を含む 1 つまたは複数の導電層を分離層 S H E が貫通することにより、選択ゲート線 S G D が構成される。分離層 S H E は、例えば S i O 2 層等の絶縁層であり、これにより、選択ゲート線 S G D を Y 方向に分離する。

[0031]

なお、積層体 L M a が、最下層のワード線 W L の下層に、第 1 の導電層としての 1 つまたは複数の選択ゲート線を備えていてもよい。

[0032]

ワード線WL及び選択ゲート線SGDは、例えばタングステン層またはモリブデン層等である。ワード線WLと選択ゲート線SGDとが異なる導電材で構成されていてもよい。この場合、選択ゲート線SGDを例えばポリシリコン層等とすることも可能である。絶縁層OLは例えばSiOっ層等である。

[0033]

積層体 L M b 上には絶縁層 5 3 が配置され、絶縁層 5 3 上には絶縁層 5 4 が配置される。これらの絶縁層 5 3 , 5 4 は例えば S i O <sub>2</sub> 層等である。

[0034]

図2(a)に示すように、メモリ領域MRにおいて、積層体LMa,LMbには複数のピラーPLが配置されている。個々のピラーPLは、積層体LMa,LMbを貫通し、ソース線SLに到達している。これらのピラーPLの上端部は絶縁層53内に配置されている。また、個々のピラーPLは、積層体LMa,LMbの各層に沿う方向の断面形状として、例えば円形、楕円形、または小判型(オーバル型)等の形状を有する。

[0035]

このとき、個々のピラーPLは、積層体LMa内における上端部、つまり、積層体LMa,LMbの界面の高さに位置する端部よりも、下端部、つまり、ソース線SLと接する端部の径が小さく、これら上端部と下端部との間に最大径を有するボーイング形状となっていてもよい。また、個々のピラーPLは、上端部、つまり、絶縁層53内に位置する端部よりも、積層体LMb内における下端部、つまり、積層体LMa,LMbの界面の高さに位置する端部の径が小さく、これら上端部と下端部との間に最大径を有するボーイング形状となっていてもよい。

[0036]

個々のピラーPLは、ピラーPLの外周側にメモリ層MEを有し、メモリ層MEの内側にチャネル層CNを有し、チャネル層CNの内側にコア層CRが充填されている。チャネル層CNは、ピラーPL下端でソース線SLと接している。メモリ層MEは、ピラーPLの外周側から順に、ブロック絶縁層BK、電荷蓄積層CT、及びトンネル絶縁層TNが積層された積層構造を有する。また、個々のピラーPLは、ピラーPLの上端部側に、例えばチャネル層CNの外形と略等しい径を有するキャップ層CPを有する。

## [0037]

ブロック絶縁層BK、トンネル絶縁層TN、及びコア層CRは例えばSiO₂層等である。電荷蓄積層CTは例えばSiN層等である。チャネル層CN及びキャップ層CPは例えばアモルファスシリコン層およびポリシリコン層の少なくともいずれかを含む。

# [0038]

キャップ層 C P の上面には、絶縁層 5 3 , 5 4 を貫通し、図示しないビット線等に接続されるプラグ C H が配置されている。ここで、図 2 (a)は、メモリ領域 M R の 1 つの断面を示しており、一部のピラー P L 上にしかプラグ C H が描かれていない。しかし、 X 方向に異なる断面では他のピラー P L にもプラグ C H が接続されている。このように、実質的に半導体記憶装置 1 の動作に寄与する全てのピラー P L にはプラグ C H が接続されている。

#### [0039]

上記のような構成により、ピラーPLの複数のワード線WLとの交差部には、複数のメモリセルMCが高さ方向に並んで形成される。また、ピラーPLの選択ゲート線SGDとの交差部には選択ゲートSTDが形成される。最下層のワード線WLの下方に選択ゲート線が配置される場合には、この選択ゲート線とピラーPLとの交差部にも選択ゲートが形成される。

## [0040]

選択ゲート線SGDから選択ゲートSTDに所定電圧を印加することで、選択ゲートSTDをオンまたはオフして、その選択ゲートSTDが属するピラーPLに形成されるメモリセルMCを選択状態または非選択状態にすることができる。選択状態となったメモリセルMCに、ワード線WLから所定電圧を印加すること等により、メモリセルMCにデータを書き込み、また、メモリセルMCに書き込んだデータを読み出すことができる。

## [ 0 0 4 1 ]

図2(a)(b)に示すように、コンタクトLIは、絶縁層53及び積層体LMa,LMbを貫通し、ソース線SLに到達する。このとき、コンタクトLIは、上面のY方向の幅より底面のY方向の幅が小さく、上面と底面との間に最大幅を有するボーイング形状となっていてもよい。また、コンタクトLIは、メモリ領域MR及び貫通コンタクト領域TPをX方向に沿って延び、積層体LMa,LMbのX方向両端部の階段領域SR(図1(a)参照)まで達している。これにより、コンタクトLIは、Y方向に積層体LMa,LMbを分割する。

#### [0042]

コンタクトLIは、側壁に配置される絶縁層 5 6 と、絶縁層 5 6 の内側に充填される導電層 2 1 とを有する。コンタクトLIの導電層 2 1 上には、絶縁層 5 3 , 5 4 を貫通し、図示しない上層配線等に接続されるプラグ V 0 が配置されている。これにより、コンタクトLIは例えばソース線コンタクトとして機能する。

# [0043]

図2(b)に示すように、貫通コンタクト領域TPには、積層体LMa,LMbの各層の積層方向から見て、積層体LMa,LMbに囲まれた絶縁領域NRが配置されている。 絶縁領域NRは、ソース線SL上に配置される積層体LMarと、積層体LMar上に配置される積層体LMbrとを備える。

# [0044]

第2の積層体としての積層体LMar,LMbrはともに、複数の第2の絶縁層としての絶縁層NLが第1の絶縁層としての絶縁層OLを介して積層された構成を有する。積層体LMar,LMbrにおける絶縁層NLは、例えば積層体LMa,LMbrはおけるワード線WL及び選択ゲート線SGDの合計の積層数と等しい積層数を有し、また、ワード線WL及び選択ゲート線SGDと等しい高さ位置に配置される。

# [0045]

絶縁層NLは例えばSiN層等である。絶縁層OLは、積層体LMa,LMbの絶縁層OLと等しい材料から構成されており、例えばSiO2層等である。

10

20

30

#### [0046]

絶縁領域NR内には、例えば1つまたは複数のコンタクトC4が配置されている。コンタクトC4は、絶縁層53及び積層体LMar,LMbrを貫通し、周辺回路CUAを覆う絶縁層50に到達している。なお、コンタクトC4の配置位置におけるソース線SLは除去されていてもよく、コンタクトC4は例えばソース線SLが除去された部分を抜けて絶縁層50へと延びる。このとき、コンタクトC4は、上端部よりも下端部の径が小さく、上端部と下端部との間に最大径を有するボーイング形状となっていてもよい。

# [0047]

コンタクト C 4 は、コンタクト C 4 の外周に配置される絶縁層 5 7 と、絶縁層 5 7 の内側に充填される導電層 2 2 とを有する。絶縁層 5 7 は例えば S i O 2 層等であり、導電層 2 2 は例えばタングステン層等である。絶縁層 5 0 内で、コンタクト C 4 の導電層 2 2 は図示しないビア及び配線等を介して周辺回路 C U A (図 1 (a)参照)に接続される。コンタクト C 4 の導電層 2 2 の上端部には、絶縁層 5 4 を貫通し、図示しない上層配線等に接続されるプラグ V 0 が配置されている。

## [0048]

このように、コンタクト C 4 は、絶縁領域 N R 内に配置され、コンタクト C 4 の周囲にワード線 W L 等は配置されない。これにより、コンタクト C 4 とワード線 W L とが電気的にショートしてしまうこと等を抑制することができる。したがって、上述のように、図 2 ( b ) の例ではコンタクト C 4 が絶縁層 5 7 のライナを有することとしたが、コンタクト C 4 が他の構成から電気的に充分に絶縁されるのであれば絶縁層 5 7 はなくともよい。

#### [0049]

また、後述する半導体記憶装置1の製造工程において、ワード線WL等を有さない積層体LMar,LMbrが配置された絶縁領域NRを積層体LMa,LMb内に確保するため、以下に述べる板状部BRが用いられる。

#### [0050]

絶縁領域NRのY方向の両側には、積層体LMa,LMbと積層体LMar,LMbrとの間に板状部BRが配置されている。つまり、板状部BRのY方向の一方側の側面は積層体LMa,LMbと対向し、他方側の側面は積層体LMar,LMbrと対向している。このとき、板状部BRは、上面のY方向の幅より底面のY方向の幅が小さく、上面と底面との間に最大幅を有するボーイング形状となっていてもよい。

# [0051]

板状部 B R は、例えばコンタクトLIに類似する構成を有する。すなわち、板状部 B R は、側壁に配置される絶縁層 5 6 と、絶縁層 5 6 の内側に充填される導電層 2 1 とを有する。ただし、絶縁層 5 6 は板状部 B R の底面にも配置されており、導電層 2 1 はソース線 S L とは接していない。

# [0052]

第3の絶縁層としての絶縁層56は、上述のようにコンタクトLI及び板状部BRの側壁に配置される同一の層であり、例えばSiO2層等である。導電層21は、上述のようにコンタクトLI及び板状部BRの内部に充填される同一の層であり、例えばタングステン層およびポリシリコン層の少なくともいずれかを含んでいてよい。

# [0053]

このように、貫通コンタクト領域TPにおいては、1対の第1の板状部としての板状部BRが、積層体LMar,LMbrの両側で、積層体LMa,LMbと積層体LMar,LMbrとの間に配置される。1対の第2の板状部としてのコンタクトLIは、1対の板状部BRから離れた位置で、1対の板状部BRをY方向の両側から挟む。

# [0054]

貫通コンタクト領域TPのコンタクトC4周辺を除く領域には、複数の柱状部HRが配置されている。複数の柱状部HRのうち少なくとも一部の柱状部HRは、積層体LMa,LMbを貫通し、ソース線SLに到達している。複数の柱状部HRのうち他の一部の柱状部HRは、積層体LMar,LMbrを貫通し、ソース線SLに到達していてもよい。こ

20

10

30

40

20

30

れらの柱状部HRの上端部は絶縁層53内に配置されている。個々の柱状部HRは、積層体LMa,LMb及び積層体LMar,LMbrの各層に沿う方向の断面形状として、例えば円形、楕円形、または小判型(オーバル型)等の形状を有する。

#### [0055]

このとき、個々の柱状部HRは、積層体LMaまたは積層体LMar内における上端部よりも、積層体LMaまたは積層体LMar内における下端部、つまり、ソース線SLと接する端部の径が小さく、これら上端部と下端部との間に最大径を有するボーイング形状となっていてもよい。同様に、個々の柱状部HRは、積層体LMbまたは積層体LMbr内における上端部、つまり、絶縁層53内に位置する端部よりも、積層体LMbまたは積層体LMbr内における下端部の径が小さく、これら上端部と下端部との間に最大径を有するボーイング形状となっていてもよい。

[0056]

柱状部 H R は、例えば S i O  $_2$  層等の絶縁層、またはピラー P L と同一の構成層であり、半導体記憶装置 1 の機能には寄与しない。後述するように、犠牲層と絶縁層とが積層された積層体から積層体 L M a , L M b を形成する際、柱状部 H R は、これらの構成を支持する役割を持つ。

[0057]

ここで、板状部BR及びコンタクトLIのより詳細な構成について説明する。

[0058]

図2(c)に示すように、板状部BRのY方向両側の側壁のうち、積層体LMa,LM bに対向する側壁と、積層体LMar,LMbrに対向する側壁とでは、構成が異なっている。

[0059]

積層体 L M a r , L M b r に対向する第 2 の側壁としての板状部 B R の側壁は、板状部 B R の外側に近い側、つまり、積層体 L M a r , L M b r 側から順に、ブロック層 6 2 、 絶縁層 5 6 、 及びバリアメタル層 2 4 を有している。これらのブロック層 6 2 、 絶縁層 5 6 、 及びバリアメタル層 2 4 は、 絶縁層 5 3 及び積層体 L M a r , L M b r の絶縁層 O L , N L の高さ位置全体に亘って配置されている。

[0060]

金属元素含有層としてのブロック層 6 2 は、例えば A l  $_2$  O  $_3$  層、 H f O  $_2$  層、または Z r O  $_2$  層等の金属酸化物層等である。ブロック層 6 2 は、絶縁層 5 3 の板状部 B R に対向する端面、及び積層体 L M a , L M b の絶縁層 O L , N L の板状部 B R に対向する端面と接している。

[0061]

バリアメタル層 2 4 は、例えばTiN層等であり、タングステン層またはモリブデン層等の導電層 2 1 と接して配置され、導電層 2 1 を構成する金属原子が、隣接する他の層に拡散することを抑制する。したがって、バリアメタル層 2 4 は、例えばTi層、TiN層、Ta層、及びTaN層の少なくともいずれかの層によって構成されていてよい。また、板状部BRの内部に充填される導電層 2 1 が、例えばポリシリコン層等である場合、板状部BRの側壁にバリアメタル層 2 4 が配置されていなくともよい。

[0062]

すなわち、積層体 L M a r , L M b r 側では、板状部 B R の側壁に配置される上述の絶縁層 5 6 と、積層体 L M a r , L M b r の絶縁層 O L , N L の端面との間に、ブロック層 6 2 が介在している。また、積層体 L M a r , L M b r 側では、板状部 B R 側壁の絶縁層 5 6 と、導電層 2 1 との間に、例えばバリアメタル層 2 4 が介在している。

[0063]

積層体 L M a , L M b に対向する第 1 の側壁としての板状部 B R の側壁は、絶縁層 5 3 の板状部 B R に対向する端面、及び積層体 L M a , L M b の絶縁層 O L の板状部 B R に対向する端面を覆うブロック層 6 2 を有している。

[0064]

50

このブロック層62は、絶縁層OLの端面から更に板状部BRからは離れる方向に延び、絶縁層OLの積層方向の両面、つまり、ワード線WLまたは選択ゲート線SGDに対向する面を覆っている。絶縁層OLの面上のブロック層62と、ワード線WL及び選択ゲート線SGDとの間には、バリアメタル層23が介在している。すなわち、ワード線WLと絶縁層OLとの間、及び選択ゲート線SGDと絶縁層OLとの間には、絶縁層OL側から順に、ブロック層62とバリアメタル層23とが介在されている。

[0065]

第2の導電層としてのバリアメタル層23は、例えばTiN層等であり、上述のように、所定の導電層を構成する金属原子が、隣接する他の層に拡散することを抑制する。したがって、バリアメタル層23は、例えばTi層、TiN層、Ta層、及びTaN層の少なくともいずれかの層によって構成されていてよい。

[0066]

また、板状部BRの積層体LMa,LMbに対向する側壁は、絶縁層53、並びに積層体LMa,LMbの絶縁層OL、ワード線WL、及び選択ゲート線SGDの高さ位置全体に亘って配置される絶縁層56を有している。絶縁層56と、絶縁層53の板状部BRに対向する端面、及び積層体LMa,LMbの絶縁層OLの板状部BRに対向する端面との間には、ブロック層62が介在している。絶縁層56と、積層体LMa,LMbのワード線WL及び選択ゲート線SGDの板状部BRに対向する端面とは直接、接している。

[0067]

ここで、積層体 L M a , L M b のワード線 W L 及び選択ゲート線 S G D の板状部 B R に対向する端面は、ブロック層 6 2 で覆われた絶縁層 O L の端面よりも板状部 B R から後退した位置にあってもよい。これにより、ワード線 W L 及び選択ゲート線 S G D の高さ位置において、板状部 B R の絶縁層 5 6 が、ワード線 W L 及び選択ゲート線 S G D の方へと突出していてもよい。

[0068]

また、板状部 B R の積層体 L M a , L M b に対向する側壁は、絶縁層 5 3 、並びに積層体 L M a , L M b の絶縁層 O L 、ワード線 W L 、及び選択ゲート線 S G D の高さ位置全体に亘って配置されるバリアメタル層 2 4 を有している。バリアメタル層 2 4 は、ブロック層 6 2 及び絶縁層 5 6 の更に内側に配置される。

[0069]

すなわち、板状部BRの側壁に配置される上述の絶縁層56は、積層体LMa,LMb側では、ブロック層62を介することなく直接、積層体LMa,LMbのワード線WL及び選択ゲート線SGDの端面と接している。また、積層体LMa,LMb側でも、板状部BR側壁の絶縁層56と、導電層21との間には、例えばバリアメタル層24が介在している。ただし、上述のように、板状部BRの内部に充填される導電層21が、例えばポリシリコン層等である場合、板状部BRの側壁にバリアメタル層24が配置されていなくともよい。

[0070]

一方、コンタクトLIのY方向両側の側壁はいずれも同様の構成を有する。

[0071]

コンタクトLIの側壁は、絶縁層 5 3 のコンタクトLIに対向する端面、及び積層体 L M a , L M b の絶縁層 O L のコンタクトLIに対向する端面を覆うブロック層 6 2 を有している。ブロック層 6 2 は、絶縁層 O L の端面から更にコンタクトLIからは離れる方向に延び、絶縁層 O L の積層方向の両面、つまり、ワード線W L または選択ゲート線 S G D に対向する面を覆っている。更に、ブロック層 6 2 とワード線W L 及び選択ゲート線 S G D との間には、バリアメタル層 2 3 が介在している。

[ 0 0 7 2 ]

また、コンタクトLIの側壁は、絶縁層 5 3、並びに積層体LMa,LMbの絶縁層OL、ワード線WL、及び選択ゲート線SGDの高さ位置全体に亘って配置される絶縁層 5 6 を有している。絶縁層 5 6 と、絶縁層 5 3 のコンタクトLIに対向する端面、及び積層

10

20

30

40

体 L M a , L M b の絶縁層 O L のコンタクト L I に対向する端面との間には、ブロック層 6 2 が介在している。絶縁層 5 6 と、積層体 L M a , L M b のワード線 W L 及び選択ゲート線 S G D のコンタクト L I に対向する端面とは直接、接している。

#### [ 0 0 7 3 ]

ここで、積層体 L M a , L M b のワード線 W L 及び選択ゲート線 S G D のコンタクト L I に対向する端面は、ブロック層 6 2 で覆われた絶縁層 O L の端面よりもコンタクト L I から後退した位置にあってもよい。これにより、ワード線 W L 及び選択ゲート線 S G D の高さ位置において、コンタクト L I の絶縁層 5 6 が、ワード線 W L 及び選択ゲート線 S G D の方へと突出していてもよい。

#### [0074]

また、コンタクトLIの側壁は、絶縁層 5 3、並びに積層体LMa,LMbの絶縁層OL、ワード線WL、及び選択ゲート線SGDの高さ位置全体に亘って配置されるバリアメタル層 2 4 を有している。バリアメタル層 2 4 は、ブロック層 6 2 及び絶縁層 5 6 の更に内側に配置される。

#### [0075]

すなわち、コンタクトLIの側壁に配置される上述の絶縁層 5 6 と、導電層 2 1 との間には、例えばバリアメタル層 2 4 が介在している。ただし、上述の板状部 B R の場合と同様、コンタクトLIの内部に充填される導電層 2 1 が、例えばポリシリコン層等である場合、コンタクトLIの側壁にバリアメタル層 2 4 が配置されていなくともよい。また、コンタクトLI側壁の絶縁層 5 6 と、積層体LMa,LMbの絶縁層OLの端面との間には、ブロック層 6 2 が介在しており、また、コンタクトLI側壁の絶縁層 5 6 と、積層体LMa,LMbのワード線WL及び選択ゲート線SGDの端面とは、ブロック層 6 2 を介することなく直接、接している。

#### [0076]

なお、コンタクトLIが有するブロック層62、絶縁層56、バリアメタル層24、及び導電層21は、後述するように、それぞれが、板状部BRが有するブロック層62、絶縁層56、バリアメタル層24、及び導電層21と並行して形成される同一の層である。

#### [0077]

また、後述するように、ワード線WLと接して配置されるバリアメタル層 2 3 は、コンタクトLI及び板状部BRの内部に配置されるバリアメタル層 2 4 とは別途、形成される。したがって、バリアメタル層 2 3 , 2 4 は、互いに同一の材料から構成されていてもよく、異なる材料から構成されていてもよい。

## [0078]

更に、柱状部HRの周辺の構成について説明する。

# [0079]

柱状部HRの側面は、絶縁層53の柱状部HRに対向する端面、及び積層体LMa,LMbの絶縁層OLの柱状部HRに対向する端面と直接、接している。柱状部HRの側面と、積層体LMa,LMbのワード線WL及び選択ゲート線SGDの柱状部HRに対向する端面との間には、ブロック層62及びバリアメタル層23が介在している。ブロック層62及びバリアメタル層23が介在している。ブロック層62及びバリアメタル層23は、柱状部HR側からこの順に配置される。

# [0800]

より詳細には、上述した絶縁層OLの積層方向の両面を覆うブロック層62は、柱状部HRと対向するワード線WL及び選択ゲート線SGDの端面をも覆っている。絶縁層OLの積層方向の両面において、ブロック層62とワード線WL及び選択ゲート線SGDとの間に介在されるバリアメタル層23は、更に柱状部HRと対向するワード線WL及び選択ゲート線SGDとの間に介在される。

# [ 0 0 8 1 ]

なお、図示はしないが、ピラーPLの周辺においても柱状部HRと同様の構成が認められる。

10

20

30

#### [0082]

すなわち、絶縁層OLの積層方向の両面を覆うブロック層62は、ピラーPLと対向するワード線WL及び選択ゲート線SGDの端面をも覆っている。絶縁層OLの積層方向の両面において、ブロック層62とワード線WL及び選択ゲート線SGDとの間に介在されるバリアメタル層23は、更にピラーPLと対向するワード線WL及び選択ゲート線SGDとの間に介在される。

# [0083]

これにより、ピラーPLの側面は、絶縁層53のピラーPLに対向する端面、及び積層体LMa,LMbの絶縁層OLのピラーPLに対向する端面と直接、接する。また、ピラーPLの側面と、積層体LMa,LMbのワード線WL及び選択ゲート線SGDのピラーPLに対向する端面との間には、ブロック層62及びバリアメタル層23が介在する。

#### [0084]

このように、柱状部HR及びピラーPLの周辺において、積層体LMa,LMbの各層の積層方向から見て、ブロック層62、バリアメタル層23、及びワード線WLは、柱状部HR及びピラーPL側からこの順に、例えば同心円状に柱状部HR及びピラーPLをそれぞれ取り囲む。

## [0085]

(半導体記憶装置の製造方法)

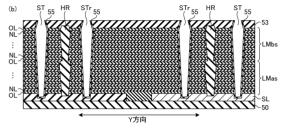

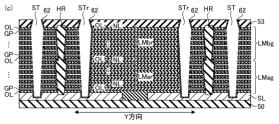

次に、図3~図8を用いて、実施形態1の半導体記憶装置1の製造方法について説明する。図3~図8は、実施形態1にかかる半導体記憶装置1の製造方法の手順の一例を示す Y方向に沿う断面図である。なお、図3~図8において、周辺回路CUAは省略されている。

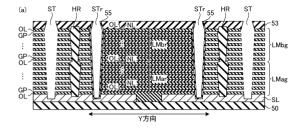

# [0086]

図3~図5は、実施形態1の半導体記憶装置1のピラーPL及び柱状部HRの形成方法の一例を示す。図3~図5において、紙面左側はピラーPLが形成される様子を示し、紙面右側は柱状部HRが形成される様子を示す。なお、図3に示す処理の前に、周辺回路CUA、周辺回路CUAを覆う絶縁層50、及び絶縁層50上のソース線SLは形成済みであるものとする。

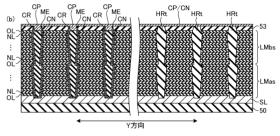

# [0087]

図3(a)に示すように、複数の第2の絶縁層としての絶縁層NLが第1の絶縁層としての絶縁層OLを介して積層された積層体LMasをソース線SL上に形成する。絶縁層NLは、後の処理でタングステン層またはモリブデン層等の導電層と置き換えられてワード線WLとなる犠牲層である。絶縁層NLの一部は、導電層と置き換えられることなく積層体LMarの一部として残る。

# [0088]

また、積層体 L M a s を貫通してソース線 S L に到達する複数のメモリホール M H a 及び複数のホール H L a を形成する。

# [0089]

図3(b)に示すように、個々のメモリホールMHa内にアモルファスシリコン層等の 犠牲層を充填して複数のピラーPLaを形成する。また、個々のホールHLa内にアモル ファスシリコン層等の犠牲層を充填して複数の柱状部HRaを形成する。

## [0090]

また、複数の第2の絶縁層としての絶縁層NLが第1の絶縁層としての絶縁層OLを介して積層された積層体LMbsを積層体LMas上に形成する。絶縁層NLは、後の処理でタングステン層またはモリブデン層等の導電層と置き換えられてワード線WLまたは選択ゲート線SGDとなる犠牲層である。絶縁層NLの一部は、導電層と置き換えられることなく積層体LMbrの一部として残る。

## [0091]

また、積層体LMbsの上面を覆う絶縁層53を形成し、絶縁層53及び積層体LMb

10

20

30

40

20

30

40

50

sを貫通して積層体LMasに到達する複数のメモリホールMHb及び複数のホールHLbを形成する。このとき、複数のメモリホールMHbのそれぞれは、対応するピラーPLaと接続される。また、複数のホールHLbのそれぞれは、対応する柱状部HRaと接続される。

[0092]

図3(c)に示すように、複数のメモリホールMHbを介して下層のメモリホールMHa内の犠牲層を除去し、絶縁層53及び積層体LMas,LMbsを貫通してソース線SLに到達する複数のメモリホールMHを形成する。また、複数のホールHLbを介して下層のホールHLa内の犠牲層を除去し、絶縁層53及び積層体LMas,LMbsを貫通してソース線SLに到達する複数のホールHLを形成する。

[0093]

図4(a)に示すように、複数のメモリホールMHをレジスト層71で覆った状態で、複数のホールHL内にSiO₂層等の絶縁層を充填する。これにより、絶縁層53及び積層体LMas,LMbsを貫通してソース線SLに到達する複数の柱状部HRtが形成される。

[0094]

図4(b)に示すように、複数のメモリホールMHを覆うレジスト層71を除去した後、個々のメモリホールMHの側壁および底面、並びに絶縁層53の上面にメモリ層MEを形成する。つまり、メモリホールMHの外周側から順に、ブロック絶縁層BK、電荷蓄積層CT、及びトンネル絶縁層TNを形成する。また、メモリホールMHの底面に形成されたメモリ層MEを除去しても良い。この場合、絶縁層53上面のメモリ層MEも除去される。

[0095]

また、メモリホールMHのメモリ層MEの内側にチャネル層CNを形成する。メモリホールMH底面のメモリ層MEを除去した場合には、チャネル層CNはメモリホールMHの底面にも形成される。更には、チャネル層CNは、メモリホールMHが形成された絶縁層53の上面、柱状部HRtが形成された絶縁層53の上面、及び柱状部HRtの上面にも形成される。

[0096]

図4(c)に示すように、複数のメモリホールMHのチャネル層CNの内側をコア層CRで充填する。コア層CRは、メモリホールMHが形成された絶縁層53の上面、柱状部HRtが形成された絶縁層53の上面、及び柱状部HRtの上面にも、チャネル層CNを介して形成される。

[0097]

図5(a)に示すように、メモリホールMHが形成された絶縁層53の上面、柱状部HRtが形成された絶縁層53の上面、及び柱状部HRtの上面のコア層CRをエッチバックによって除去する。これにより、メモリホールMH内に充填されたコア層CRの上端部が除去される。一方、柱状部HRtにおいては、チャネル層CNがエッチストッパ層となって柱状部HRtの上端部は除去されない。

[0098]

図5(b)に示すように、コア層CRが除去されたメモリホールMHの上端部にキャップ層CPを充填する。このとき、メモリホールMHが形成された絶縁層53の上面、柱状部HRtが形成された絶縁層53の上面、及び柱状部HRtの上面にもキャップ層CPが形成されてもよい。

[0099]

図5(c)に示すように、メモリホールMHが形成された絶縁層53の上面、柱状部HRtが形成された絶縁層53の上面、及び柱状部HRtの上面のキャップ層CP及びチャネル層CNを、また、メモリ層MEが残っている場合には更にメモリ層MEをエッチバックによって除去する。更に、キャップ層CP及びチャネル層CNが除去されてメモリホールMHが露出した絶縁層53の上面に対

してもエッチバックを継続する。

[0100]

これにより、薄くなった絶縁層 5 3 の上面から露出するキャップ層 C P を上端部に有する複数のピラー P L が形成される。また、薄くなった絶縁層 5 3 の上面から上端部が露出した複数の柱状部 H R が形成される。

[0101]

この後、キャップ層 C P の上面および柱状部 H R の上面を覆うように絶縁層 5 3 を積み増しする。

[0102]

なお、図3~図5までの処理におけるいずれかのタイミングで、積層体LMas,LM bsのX方向両端部に階段領域SRを形成する。

[0103]

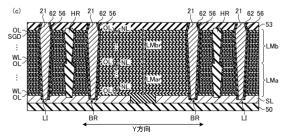

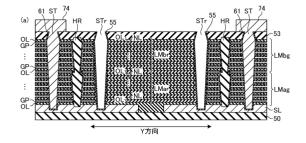

図6~図8は、実施形態1の半導体記憶装置1のコンタクトLI及び板状部BRの形成方法の一例を示す。図6~図8に示す断面図は、上述の図2(b)の断面図に示す領域に相当する。

[0104]

図6(a)に示すように、絶縁層53及び積層体LMas,LMbsを貫通してソース線SLに到達するスリットST,STrを形成する。スリットSTはコンタクトLIが配置される位置に形成され、スリットSTrは板状部BRが配置される位置に形成される。

[0105]

図6(b)に示すように、スリットST,STrの側壁および底面に絶縁層55を形成する。柱状部HRを構成する絶縁層と同様、絶縁層55は例えばSiO2層等である。ただし、絶縁層55は、メモリホールMH内に形成したブロック絶縁層BKと同様に緻密な層であることが好ましい。このように緻密な絶縁層55は、例えば絶縁層55の形成条件を調整することによって得ることができる。

[0106]

図 6 ( c )に示すように、スリットSTrをレジスト層72で覆った状態で、スリットSTの側壁および底面の絶縁層55を除去する。

[0107]

図7(a)に示すように、スリットSTrを覆うレジスト層72を除去した後、スリットSTから熱リン酸溶液等を流入させ、積層体LMas,LMbsの絶縁層NLを除去する。これにより、スリットSTrで挟まれた領域を除く積層体LMas,LMbsが、絶縁層NLが除去された複数のギャップGPが絶縁層OLを介して配置される積層体LMag,LMbgとなる。

[0108]

複数のギャップGPを含む積層体LMag,LMbgは脆弱な構造物であり、歪み及び倒壊等が生じる恐れがある。貫通コンタクト領域TPにおいては、絶縁層53からソース線SLにまで到達する柱状部HRが、脆弱な積層体LMag,LMbgを支持する。また、図示しないメモリ領域MRにおいては、絶縁層53からソース線SLにまで到達するピラーPLが、脆弱な積層体LMag,LMbgを支持する。これによって、積層体LMag,LMbgが歪んだり倒壊したりすることが抑制される。

[0109]

一方、スリットSTrは側壁に緻密な絶縁層55を有している。このため、スリットSTrから積層体LMas,LMbsのY方向内側へと向かう熱リン酸溶液の流入が、スリットSTrによって堰き止められる。また、スリットSTから流入する熱リン酸溶液が、X方向側から回り込んで、1対のスリットSTrで挟まれた領域内に流入する前に、熱リン酸溶液による処理を終了する。

[0110]

これにより、1対のスリットSTrで挟まれた領域内では、積層体LMas,LMbsの絶縁層NLが除去されることなく維持され、1対のスリットSTrで挟まれた領域内に

20

10

30

40

積層体LMar,LMbrが形成される。

# [0111]

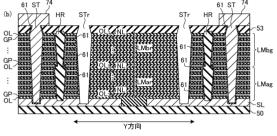

図7(b)に示すように、スリットSTをレジスト層73で覆った状態で、スリットS Trの側壁および底面の絶縁層55を除去する。

#### [0112]

このとき、絶縁層NLが除去された積層体LMag,LMbgの絶縁層OLの上下面は 露出した状態となっている。このため、絶縁層55と共に、絶縁層0Lまでもが層厚方向 に浸食されて所望の層厚未満となってしまわないよう留意する。

#### [0113]

絶 縁 層 55を除去する際 に 絶 縁 層 OLま で も が 浸 食 さ れ る こ と を 見 越 し て 、 予 め 絶 縁 層 OLを所望の層厚より厚く形成しておき、絶縁層 5 5 の除去後に所望の層厚の絶縁層OL が得られるようにしておいてもよい。

## [0114]

なお、絶縁層55を除去する際、スリットSTrに対向する絶縁層OLの端面もスリッ トSTrから後退する可能性がある。しかし、絶縁層OLの端面の後退は、半導体記憶装 置1の機能に殆ど影響しないと考えられる。

#### [0115]

スリットSTrの側壁から絶縁層55を除去することにより、スリットSTrと、積層 体LMag,LMbgのギャップGPとが連通する。

#### [0116]

図 7 ( c )に示すように、スリットSTを覆うレジスト層 7 3 を除去した後、スリット ST,STrからAl203層等のブロック層62の材料ガスを流入させて、 積層体LM ag,LMbgの絶縁層OLの上下面にブロック層62を形成する。

## [0117]

こ の と き 、 ス リ ッ ト S T r の 積 層 体 L M a r , L M b r 側 の 側 壁 に も 、 絶 縁 層 5 3 、 及 び積層体LMar,LMbrの絶縁層NL,OLの高さ位置全体に亘ってブロック層62 が形成される。また、スリットSTrの積層体LMag,LMbg側の側壁、つまり、絶 緣 層 5 3 の 端 面 、 及 び 積 層 体 L M a g , L M b g の 絶 縁 層 O L の 端 面 に ブ ロ ッ ク 層 6 2 が 形成される。同様に、スリットSTのY方向両側の側壁、つまり、絶縁層53の端面、及 び積層体LMag,LMbgの絶縁層OLの端面にブロック層62が形成される。また、 スリットST,STrの底面を含むソース線SLと接する部分にもブロック層62が形成 される。更に、柱状部HRの側面のうち、積層体LMag,LMbgのギャップGPの高 さ位置の側面にブロック層62が形成される。

# [0118]

また、スリットST,STrからTiN層等のバリアメタル層23の材料ガスを流入さ せて、 積層体 LMag,LMbgの絶縁層OLの上下面にブロック層 62を介してバリア メタル層 2 3 (図 2 ( c ) 参照) を形成する。

# [0119]

このとき、スリットST,STrのY方向両側の側壁および底面に形成されたブロック 層62上に、更にバリアメタル層23が形成される。また、柱状部HRの側面のうち、積 層体LMag,LMbgのギャップGPの高さ位置の側面に、ブロック層62を介してバ リアメタル層23が形成される。

## [ 0 1 2 0 ]

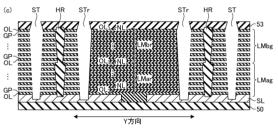

図 8 ( a )に示すように、スリットST,STrからタングステン層またはモリブデン 層等の導電層 2 5 の材料ガスを流入させて、積層体LMag,LMbgのギャップGPに 導電層25を充填する。これにより、複数のワード線WLが絶縁層OLを介して積層され た積層体 L M a , L M b が形成される。

# [0121]

なお、図中、積層体LMbの最上層のギャップGPの高さ位置には導電層25が形成さ れることとしている。この導電層25は、後に形成される分離層SHEによってY方向に 10

20

30

40

20

30

40

50

分離された選択ゲート線SGDに区画される。ただし、分離層SHEの形成タイミングは種々に選択することができ、例えば図8(a)に示す工程以前に、既に分離層SHEが形成済みであってもよい。

[ 0 1 2 2 ]

このとき、スリットST,STr側壁にも導電層25が形成される。また、この段階において上述の図2(c)で説明した柱状部HRの周辺構成が形成される。

[ 0 1 2 3 ]

なお、図7(a)~図8(a)に示す絶縁層NLからワード線WLへの置き換え処理を リプレース処理などとも呼ぶ。

[0124]

図 8 ( b ) に示すように、スリットST,STr内の導電層 2 5 及びバリアメタル層 2 3 (不図示)を除去する。このとき、スリットST,STrの側壁と接する積層体LMa,LMbのワード線WL及び最上層の導電層 2 5 の端面が後退してもよい。

[0125]

また、スリットST,STr底面のブロック層62を除去した後、スリットST,STrの側壁および底面に絶縁層56を形成する。スリットST,STr内の導電層25及びバリアメタル層23を除去する際に、積層体LMa,LMbのワード線WL及び最上層の導電層25の端面が後退していた場合には、スリットST,STr側壁の絶縁層56は、ワード線WL及び最上層の導電層25側へと突出し、これらの端面と接する。

[0126]

更に、スリットSTの底面から絶縁層56を除去する。なお、上記タイミングに替えて、スリットST底面からのブロック層62除去をこのときに一括して行ってもよい。また、スリットSTrの底面に絶縁層56及びブロック層62を残してもよい。

[0127]

また、スリットST,STrの側壁および底面に、例えばバリアメタル層 2 4 (図 2 (c )参照)を形成する。上述のように、この後、スリットST,STr内にポリシリコン層等の導電層 2 1 を充填する場合には、このバリアメタル層 2 4 は形成されなくともよい

[ 0 1 2 8 ]

図 8 ( c ) に示すように、スリットST,STr内にタングステン層またはポリシリコン層等の導電層 2 1 を充填する。これにより、上述の図 2 ( c ) で説明した構成を有するコンタクトLI及び板状部BRが形成される。

[0129]

この後、積層体 L M b の最上層の導電層 2 5 を含む 1 つまたは複数の導電層 2 5 を貫通する溝を設け、溝内に絶縁層を充填して分離層 S H E を形成する。これにより、分離層 S H E が貫通した導電層 2 5 が選択ゲート線 S G D に区画される。ただし、分離層 S H E の形成タイミングが、この時点に限られないことは上述したとおりである。

[0130]

また、絶縁層53及び積層体LMar,LMbrを貫通してソース線SL下方の絶縁層50に到達する貫通孔を形成し、貫通孔の側壁に必要に応じて絶縁層57を形成し、絶縁層57の内側を導電層22で充填する。これにより、コンタクトC4が形成される。また、階段領域SRに、個々のワード線WL及び選択ゲート線SGDと接続される複数のコンタクトCC(図1(a)参照)を形成する。

[0131]

また、積層体 L M b 上の絶縁層 5 3 を覆う絶縁層 5 4 を形成する。絶縁層 5 3 , 5 4 を 貫通してピラー P L 上端部のキャップ層 C P に到達する貫通孔を設け、貫通孔内に導電層 を充填してピラー P L のキャップ層 C P と接続されるプラグ C H を形成する。また、絶縁 層 5 4 を貫通して、コンタクト L I , C 4 , C C の上面に到達する貫通孔を設け、貫通孔 内に導電層を充填してコンタクト L I , C 4 , C C と接続されるプラグ V 0 を形成する。 更に、プラグ C H , V 0 の上層配線等を形成する。 [ 0 1 3 2 ]

以上により、実施形態1の半導体記憶装置1が製造される。

[ 0 1 3 3 ]

なお、半導体記憶装置 1 においては、上述の例に依らず、例えばピラー P L 下端部付近の側面で、チャネル層 C N とソース線 S L とが接続する構成を採ることも可能である。

[0134]

3次元不揮発性メモリ等の半導体記憶装置の製造工程において、SiN層等の犠牲層とSiO2層等の絶縁層との積層体の一部領域に犠牲層を残しつつ、他の領域の犠牲層を導電層に置き換えるリプレース処理が行われることがある。これにより、導電層を含む積層体中に導電層を有さない絶縁領域を形成することができる。

[ 0 1 3 5 ]

この場合、例えば犠牲層が残される一部領域のY方向両側に近接させて、リプレース処理の障壁となる絶縁層を側壁に有するスリットを形成する。また、これらのスリットから Y方向に離れた位置に、絶縁層を側壁に有さないスリットを形成する。リプレース処理では、専ら絶縁層を有さないスリットを介して犠牲層を除去し、それにより生じたギャップに導電材を充填して導電層を形成する。

[0136]

絶縁層を側壁に有するスリットは、その後の処理によって、リプレース処理された積層体側に形成されたブロック層と、スリットの内部に形成されたブロック層との間に、リプレース処理の障壁として用いた絶縁層が介在された構成を有することとなる。

[0137]

しかしながら、上記のようなリプレース処理には課題が生じ得る。導電層の材料ガスは、絶縁層を有さないスリット近傍から、所定時間をかけて絶縁層を有するスリット近傍へと流入していく。したがって、リプレース処理の一定期間において、積層体のギャップへの導電材の充填密度が、絶縁層を有さないスリット近傍で高く、絶縁層を有するスリット近傍で低い状態が生じる。これにより、導電材が低密度の領域から高密度の領域への引っ張り応力が発生し、積層体を支持する柱状部および積層体そのものが、高密度領域へ向かって傾いてしまう場合がある。

[ 0 1 3 8 ]

そこで、犠牲層の除去前に、例えば絶縁層を有するスリット内を絶縁層等で充填し、このスリットの Y 方向両側の積層体の接続を強固にして、柱状部および積層体等の傾きを抑制することも考えられる。しかしながら、この場合、スリット内に充填した絶縁層等にクラックが発生してしまう恐れがある。

[0139]

実施形態1の半導体記憶装置1の製造方法によれば、絶縁層NL層の除去後、導電層25の充填前に、スリットSTr側壁の絶縁層55を除去する。これにより、スリットST、STrの両方から積層体LMag,LMbgのギャップGP内に導電層25を充填することができる。よって、スリットST近傍とスリットSTr近傍とにおける導電層25の充填密度の差を低減することができ、柱状部HR及び積層体LMag,LMbg等の傾きを抑制することができる。

[0140]

実施形態1の半導体記憶装置1の製造方法によれば、レジスト層73でスリットSTを覆った状態で、スリットSTr側壁の絶縁層55を除去する。これにより、絶縁層55等を有さないスリットST側から、積層体LMag,LMbgの絶縁層OLが層厚方向に浸食されてしまうのを抑制することができる。

[0141]

実施形態1の半導体記憶装置1の製造方法によれば、例えば積層体LMas,LMbsの形成時、予め絶縁層OLの層厚を所望の層厚よりも厚く形成しておいてもよい。これにより、スリットSTr側壁の絶縁層55を除去する際に、絶縁層OLが層厚方向に浸食されてしまっても、絶縁層55の除去後の絶縁層OLを所望の層厚に維持することができる

10

20

30

40

[0142]

なお、上述の実施形態1では、スリットSTをリプレース処理に使用した後、スリットST内に導電層21を充填して、ソース線コンタクトとして機能するコンタクトLIを形成することとした。しかし、スリットST内を例えば絶縁層56等で充填して、半導体記憶装置1の動作に寄与しない構成を形成してもよい。この場合、スリットSTr内にも絶縁層56等を充填して、スリットSTと類似の構成とすることが製造工程上、簡便である。しかしながら、半導体記憶装置1において、スリットST,STrに異なる材料を充填して、これらが互いに異なる構成を有することとなってもよい。

[0143]

また、上述の実施形態1では、スリットSTrの側壁にSiO2層等の絶縁層55を形成して、リプレース処理の障壁として用いることとした。しかし、リプレース処理の障壁として、例えばアルミニウム、タングステン等の金属層、A1203層等の金属酸化物層、TiN層等の導電層等を用いてもよい。このように、絶縁層OLの構成材とは異なる構成材を含む層を用いることで、この層をスリットSTrの側壁から除去する際に、絶縁層OLとの選択比を取ることができ、絶縁層OLの層厚を維持することが容易となる。

[0144]

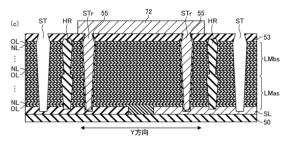

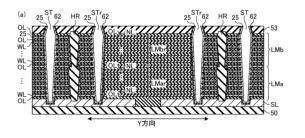

「実施形態2]

以下、図面を参照して実施形態 2 について詳細に説明する。実施形態 2 の半導体記憶装置は、その製造方法が上述の実施形態 1 とは異なる。ただし、実施形態 2 においても、実施形態 1 と実質的に同一の半導体記憶装置 1 が製造される。

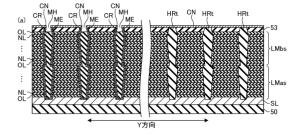

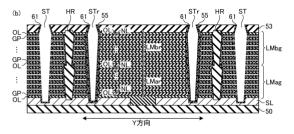

[0145]

図9及び図10を用いて、実施形態2の半導体記憶装置1の製造方法について説明する。図9及び図10は、実施形態2にかかる半導体記憶装置1の製造方法の手順の一例を示すY方向に沿う断面図である。なお、図9及び図10において、周辺回路CUAは省略されている。

[0146]

実施形態2の半導体記憶装置1においても、ピラーPL及び柱状部HRは例えば上述の実施形態1のピラーPL及び柱状部HRと同様に形成される。また、実施形態2の半導体記憶装置1において、コンタクトLI及び板状部BRを形成する際には、上述の実施形態1の図6(a)~図7(a)までの処理が同様に行われる。

[0147]

図 9 ( a ) は、コンタクトLI及び板状部 B R の形成工程において、上述の実施形態 1 の図 7 ( a ) の処理が行われた後の様子を示す。

[ 0 1 4 8 ]

図 9 ( b )に示すように、スリット S T から A l <sub>2</sub> O <sub>3</sub> 層等の材料ガスを流入させて、 積層体 L M a g , L M b g の絶縁層 O L の上下面に保護層 6 1 を形成する。

[0149]

このとき、スリットSTrの側壁および底面に配置される絶縁層55のスリットSTr内部に向いた面の全体に亘って保護層61が形成される。また、絶縁層55の積層体LMag,LMbg側を向いた面のうち、ギャップGPの高さ位置にある部分に保護層61が形成される。同様に、スリットSTのY方向両側の側壁、つまり、絶縁層53の端面、及び積層体LMag,LMbgの絶縁層OLの端面に保護層61が形成される。更に、スリットSTの底面を含むソース線SLと接する部分にも保護層61が形成される。また、柱状部HRの側面のうち、積層体LMag,LMbgのギャップGPの高さ位置の側面に保護層61が形成される。

[0150]

図9(c)に示すように、スリットSTをレジスト層74で覆う。

[0151]

図10(a)に示すように、スリットSTをレジスト層74で覆った状態で、スリット

10

20

30

40

STr内の保護層61を除去して、スリットSTr内に絶縁層55を露出させる。

#### [0152]

図10(b)に示すように、スリットSTをレジスト層74で覆った状態で、スリットSTr内の絶縁層55を除去する。このとき、積層体LMag,LMbgの絶縁層OLの上下面は保護層61に覆われている。このため、絶縁層OLが層厚方向に浸食されてしまうことが抑制される。

# [0153]

スリットSTr内の絶縁層55を除去することで、スリットSTr内に、積層体LMag,LMbgのギャップGPの高さ位置に形成された保護層61が露出する。

[0154]

図10(c)に示すように、スリットSTを覆うレジスト層74を除去し、スリットST,STrの両方を介して、積層体LMag,LMbgの全体の保護膜61を除去する。これにより、スリットSTr内に露出し、スリットSTrとギャップGPとを隔でる保護層61が除去されて、スリットSTrと積層体LMag,LMbgのギャップGPとを連通させることができる。

[ 0 1 5 5 ]

この後、上述の実施形態1の図7(c)以降の処理を行う。

【 0 1 5 6 】

以上により、実施形態2の半導体記憶装置1が製造される。

[0157]

実施形態2の半導体記憶装置1の製造方法によれば、実施形態1の半導体記憶装置1の製造方法と同様の効果を奏する。

[ 0 1 5 8 ]

実施形態2の半導体記憶装置1の製造方法によれば、絶縁層OLの上下面に形成された保護層61によって絶縁層OLを保護しつつ、スリットSTr側壁の絶縁層55を除去する。これにより、絶縁層55の除去に伴って絶縁層OLが層厚方向に浸食されてしまうのを抑制することができる。

[ 0 1 5 9 ]

実施形態 2 の半導体記憶装置 1 の製造方法によれば、保護層 6 1 として、例えばブロック層 6 2 と同種の層を用いる。これにより、保護層 6 1 を形成するために新たな処理技術を構築する必要が無く、簡便に保護層 6 1 を形成することができる。

[0160]

[0161]

本発明のいくつかの実施形態を説明したが、これらの実施形態は、例として提示したものであり、発明の範囲を限定することは意図していない。これら新規な実施形態は、その他の様々な形態で実施されることが可能であり、発明の要旨を逸脱しない範囲で、種々の省略、置き換え、変更を行うことができる。これら実施形態やその変形は、発明の範囲や要旨に含まれるとともに、特許請求の範囲に記載された発明とその均等の範囲に含まれる

【符号の説明】

[0162]

1 … 半導体記憶装置、 2 1 … 導電層、 2 3 , 2 4 … バリアメタル層、 5 5 , 5 6 … 絶縁層、 6 1 … 保護層、 6 2 … ブロック層、 B R … 板状部、 C 4 … コンタクト、 H R … 柱状部、 L I … コンタクト、 L M a , L M a g , L M a r , L M b , L M b g , L M b r … 積層体、 M C … メモリセル、 M R … メモリ領域、 N L , O L … 絶縁層、 N R … 絶縁領域、 P L … ピラー、 S G D … 選択ゲート線、 S T , S T r … スリット、 T P … 貫通コンタクト領域、 W L … ワード線。

10

20

30

40

# 【図5】

# 【図6】

# 【図7】

# 【図8】

10

20

30

# 【図9】

# 【図10】

30

10

20

# フロントページの続き

F ターム (参考) RR04 RR06 TT02 VV06 VV16

5F083 EP18 EP23 EP33 EP34 EP76 GA10 GA25 JA02 JA19 JA39

JA40 KA01 LA21 MA06 MA16 MA19 ZA01

5F101 BA45 BB05 BD16 BD22 BD30 BD34 BH21