(19) **日本国特許庁(JP)**

# (12) 特 許 公 報(B2)

(11) 特許番号

特許第4388926号 (P4388926)

(45) 発行日 平成21年12月24日(2009.12.24)

(24) 登録日 平成21年10月9日(2009.10.9)

(51) Int. CL. F. L.

HO1L 25/065 (2006.01) HO1L 25/07 (2006.01)

HO1 L 25/07 (2006.01) HO1 L 25/18 (2006.01) HO1L 25/08 Z

請求項の数 1 (全 15 頁)

(21) 出願番号 特願2005-336256 (P2005-336256) (22) 出願日 平成17年11月21日 (2005.11.21)

(62) 分割の表示 特願2004-164489 (P2004-164489)

の分割

原出願日 平成16年6月2日 (2004.6.2) (65) 公開番号 特開2006-80564 (P2006-80564A)

(43) 公開日平成18年3月23日 (2006. 3. 23)審査請求日平成19年6月1日 (2007. 6. 1)

||(73)特許権者 503291439

株式会社GENUSION

兵庫県尼崎市道意町7丁目1番3号 尼崎 リサーチ・インキュベーションセンター

(74)代理人 110000408

特許業務法人高橋・林アンドパートナーズ

|(74)代理人 100123940

弁理士 村上 辰一

|(72) 発明者 中島 盛義

兵庫県尼崎市道意町7丁目1番3号 尼崎 リサーチインキュベーションセンター 株

式会社GENUSION内

最終頁に続く

## (54) 【発明の名称】半導体装置のパッケージ構造

## (57)【特許請求の範囲】

## 【請求項1】

パッケージ基板(10)と、

前記パッケージ基板(10)の表面に搭載され、ボンディングパッド部を有する第1の半 導体チップ(34)と、

前記第1の半導体チップ(34)のボンディングパッド部と前記パッケージ基板(10)とを電気的に接続する第1のワイヤと、

前記第1の半導体チップ(34)の前記ボンディングパッド部がかくれないように前記第1の半導体チップ(34)の表面に配置されたスペーサー(90)と、

前記スペーサー(90)上に搭載され、前記スペーサー(90)よりも大きな半導体チップマウント封止サブ基板(100)とから構成され、

前記半導体チップマウント封止サブ基板(100)は、

- a) 第2の半導体チップ(30)と

- b) 上面及び下面を有し、前記下面には、前記第2の半導体チップ(30)が搭載されるとともに、第2の半導体チップ(30)と電気的に接続され<u>第1の一辺に沿って前記第1の一辺からは距離をおきつつ前記第1の一辺に接しないように列状に配列され</u>た複数の第1の電極(130)が形成され、前記上面には、前記第2の半導体チップ(30)の電極ピッチよりも大きいピッチでアレイ状に配列された複数の第2の電極(110)と、<u>第</u>2の一辺に沿って前記複数の第2の電極(110)よりも小さいピッチで<u>前記第2の一辺</u>からは距離をおきつつ前記第2の一辺に接しないように列状に配列された複数の第3の電

極(120)とが形成されたインターポーザー(70)と、

c) 前記インターポーザー(70)の下面と前記第2の半導体チップ(30)とを<u>前記</u> インターポーザーの前記第1の一辺に沿った側面を有するように封止する第1の樹脂とから構成され、

前記半導体チップマウント封止サブ基板(100)は、前記インターポーザー(70)の下面が前記スペーサー(90)に対向するとともに前記第1の樹脂が前記スペーサー(9 0)に接するように配置され、

前記第3の電極(120)と前記パッケージ基板(10)とは第2のワイヤにより電気的に接続され、

前記パッケージ基板(10)の表面と、前記第1の半導体チップ(34)と、前記第1のワイヤと、前記スペーサー(90)と、前記半導体チップマウント封止サブ基板(100)と、前記第2のワイヤとを封止する、第1の樹脂とは別に行って樹脂封止される第2の樹脂を含む

ことを特徴とする半導体パッケージ。

【発明の詳細な説明】

【技術分野】

[0001]

この発明は、半導体装置のパッケージ構造に関するものである。

【背景技術】

[0002]

移動体通信システムの端末装置(携帯電話機)などのように半導体装置を用いた電子機器において、その小型軽量化を図る上で半導体装置の高集積化を如何に高めるかは常に重要である。これまで半導体回路の微細化が順調に進んでいたときには可能な限りの回路を1チップ化して、実装面積の縮小化、高速化、消費電力の低減化というメリットを生かしてきた。ところが、半導体回路の微細化に伴う製造コストの急騰と設計開発期間の長期化という問題が顕在化してきた。

[0003]

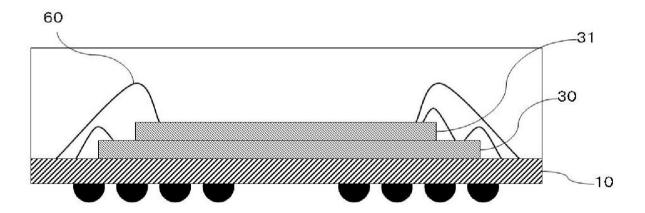

そこで、複数の半導体チップを3次元実装するSIP(System in Package)技術が注目されている。例えば図13に示すように、パッケージ基板10の上に半導体ベアチップ30をマウントし、この半導体ベアチップ30の上にさらに別の半導体ベアチップ31をマウントし、これらの半導体ベアチップ30、31とパッケージ基板10との間をワイヤ60でワイヤボンディングしている(非特許文献1参照)。

【非特許文献1】日経エレクトロニクス2002,2-11 no.815 p108 「第1部 チップがダメならパッケージがある」

【発明の開示】

【発明が解決しようとする課題】

[0004]

上記のように複数の半導体チップを1つのパッケージに納めたSIPの良品率は、各半導体チップの良品率の相乗値となり、たとえば、良品率が8割の半導体チップを3個納めたSIPの場合、その良品率はほぼ5割(=0.8×0.8×0.8)に低下してしまうという問題点があった。特に、DRAMなどの低価格のチップの良品率のほうが、高価なCPUなどのロジック半導体チップの良品率よりも低いため、低価格の半導体チップの不良のために高価な半導体チップが無駄になってしまうという問題点があった。したがって、SIPに実装する半導体チップは、予め検査をすませて良品であることが確認された半導体チップ(検査済み良品チップ、KGD:Known-Good-Die)であることが強く望まれる。

[0005]

次に、KGDを取得する方法を説明する。まず、半導体ウェハの状態で個々の半導体チップに所定のプローブ検査を行う。半導体ウェハをダイシング(切断)して半導体チップの個片に分離する。プローブ検査の結果に基づいて半導体チップを選別し、これにより、

20

10

30

40

良品の半導体チップのみをバーンイン検査(以下、BTとする)等のスクリーニング検査を行う。この際、良品の半導体チップのみをBT用のチップトレイまたはキャリアソケットに収容し、KGD専用治具および専用装置を用いてチップ状態でのBTを行い、さらに、選別した後、BT用のチップトレイもしくは、キャリアソケットから半導体チップを取り出し、良品の半導体チップを出荷用のトレイに移し換えて梱包及び出荷を行っている。半導体チップ個片(ベアチップ)は、非常に薄く形成されているため、割れやすく、選別試験に使用されるソケットやプローブ、テスターの操作には非常に繊細な操作が要求されていた。

## [0006]

この問題を解決するために、たとえば特開 2 0 0 2 - 4 0 0 9 5 に開示されているような方法がある。

#### [0007]

特開2002-40095に開示されている半導体装置は、半導体チップを樹脂封止してなる第一の樹脂封止パッケージの表面に形成された電極が前記半導体チップの電極に接続されると共に実装対象に接続される実装用領域と試験用機器を接続する試験用領域とが設けられてなることを特徴とする。特開2002-40095に開示されている半導体装置をSIPに適用した場合の例を図14に示し、これを参照して以下に説明する。

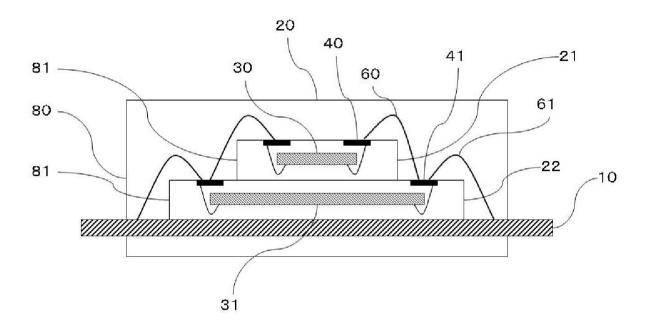

#### [00008]

図14に示すように、半導体パッケージ20は、パッケージ基板10に実装される際に、パッケージ基板10上の電極と接続されるリードフレームに半導体パッケージ21及び半導体パッケージ22が搭載されると共に、封止樹脂80によって樹脂封止される。このとき、半導体パッケージ21及び半導体パッケージ22は、それぞれ半導体ベアチップ30及び半導体ベアチップ31を内蔵し、かつ封止樹脂81によってそれぞれ樹脂封止されている。但し、特開2002-40095に開示されている半導体光ッケージ21を載置している半導体パッケージ21の電極40は、半導体パッケージ21を載置している半導体パッケージ22の電極41にワイヤ60によって接続されている。また、半導体パッケージ22の電極41にワイヤ60によって接続されている。このように、特開2002-40095に開示されている樹脂封止パッケージ(半導体パッケージ21および半導体パッケージ22)は従来のベアチップに比べて、樹脂封止されているがゆえに、その取り扱いが簡単になり、選別試験に使用されるソケットやプローブ、テスターの操作に要求される繊細度は減る、という効果がある。

## [0009]

さらに、特開2002-40095では、電極を試験用領域と実装用領域とに分けることにより、実装時に選別試験で傷がついた前記電極を使用することがなくなる構成をとっている。この試験用電極と実装用電極に対しては、以下のような要求がある。

## [0010]

まず、試験用電極に対しては、その電極ピッチを例えば、BGAタイプのパッケージでは、0.8mm程度にする。このレベルの電極ピッチが実現できれば、選別試験に使用されるソケットやプローブ、テスターの操作に要求される繊細度はCSPを測定するレベルでよくなる。一方、実装用電極に対しては、その電極ピッチを通常のベアチップの電極ピッチと同等にすることで、その有用性を発揮する。このピッチは例えば、130um程度である。このレベルの電極ピッチが実現できれば、アセンブリ装置等は特に変更する必要なく使用できる。

## [0011]

上記のような、実装用の狭いピッチでも配線できるようにするために、ガラス基材を用いたインターポーザーを使った方法が特開2003-249606に開示されている。しかし、試験用電極配置と実装用電極配置とにそれぞれ自由度をもたせるには、単に狭いピッチで配線できるだけでは限界があり、任意の試験用電極配置と実装用電極配置とが実現できないという問題があった。

## [0012]

10

20

30

10

20

30

40

50

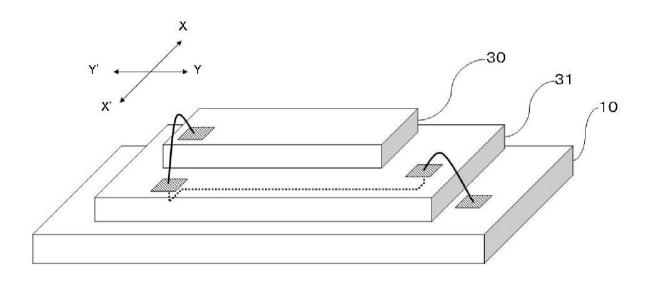

一方、半導体チップのパッド電極を任意の電気接続部に対して接続できる配線方法を提供したものに特開 2 0 0 1 - 1 9 6 5 2 9 がある。特開 2 0 0 1 - 1 9 6 5 2 9 に開示される配線手法を図 1 5 に示す。図 1 5 では、半導体ベアチップ 3 0 の矢印 Y - Y '方向に伸びる縁部近傍に配置されたパッド電極とパッケージ基板 1 0 において矢印 X - X '方向に伸びる縁部近傍に配置されたパッド電極とを半導体ベアチップ 3 1 の内部配線を介して接続している。

#### [0013]

以上のごとくSIPを実現するのであるが、複数チップを3次元に積層するチップ・オン・チップを実現するには、積層するチップに隙間を設ける必要がある。この隙間は、半導体素子の放熱を行う働きや、実装の際の半導体素子の保護の働きをする。また、この隙間は、積層するチップのサイズが同じ、あるいは、ほぼ同じの場合、それらのチップを直接積層すると、下側のチップのボンディングパッド部分がかくれてワイヤボンディングができなくなることを防ぐ働きもする。この積層するチップ間に隙間を設ける手段をスペーサーと呼ぶ。

## 【課題を解決するための手段】

#### [0014]

この発明は、複数の半導体<u>ベア</u>チップを搭載す<u>る基</u>材と、該基材に搭載した半導体<u>ベア</u>チップとを備えた半導体装置のパッケージ構造において、

マウントすべき半導体<u>ベア</u>チップの<u>電極</u>端子を接続する内部電極と、<u>半導体ベアチップマウント後の試験時に試験装置の端子が接続される試験用電極と、半導体ベアチップをマウントしたのち前記基材に実装される時</u>に他の部品に接続される実装用電極と<u>を設けた</u>半導体チップマウントサブ基板と、

前記半導体チップマウントサブ基板を、前記基材に搭載した半導体ベアチップの上部に 配置するスペーサと、を備え、

前記半導体チップマウントサブ基板と<u>前記基材に搭載された半導体ベアチップ</u>を前記基材とともに樹脂封止したことを特徴としている。

## 【発明の効果】

#### [0020]

この発明によれば、半導体チップマウントサブ基板は、内部電極と、実装用電極と、試験用電極をそれぞれ設けて成り、前記半導体チップマウントサブ基板をテストするときには、試験用電極を用いることで、従来のソケット方式でテストができ、テスト費用の削減が図れるとともに、前記半導体チップマウントサブ基板を実装するときには、実装用電極を用いることで、従来の実装装置が使用でき、実装費用の削減が図れる。さらに、前記内部電極と、前記実装用電極と、前記試験用電極との相互接続を多層配線で実現することで、内部電極の配置と、試験用電極の配置と、実装用電極の配置とがそれぞれ任意に設定でき、様々なパッド配置の半導体チップに対して、テスト方式に適した試験用電極の配置と、実装条件に適した実装用電極の配置とがそれぞれ選択できる。

## 【発明を実施するための最良の形態】

## [0026]

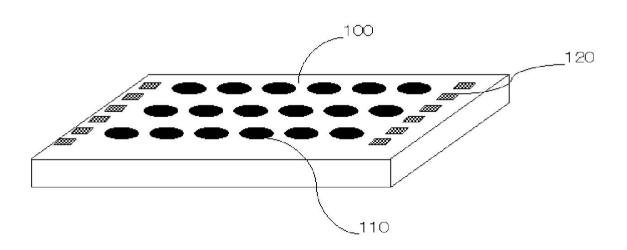

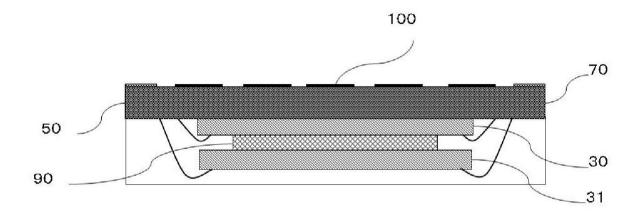

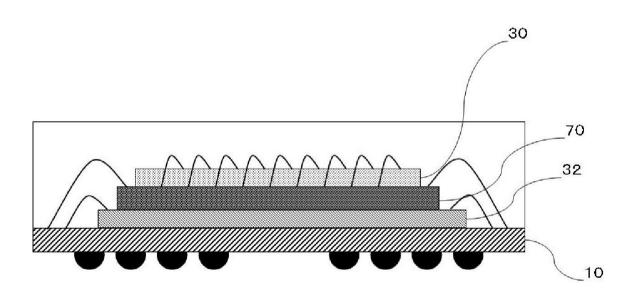

図1は本発明に係る半導体チップマウント封止サブ基板100の構造を示したものである。図2は、図1の断面図である。インターポーザー70に対して半導体ベアチップ30をマウントし、その下に、スペーサー90を積層し、さらにその下に半導体ベアチップ31を積層している。この半導体チップマウントサブ基板50を樹脂封止したものが半導体チップマウント封止サブ基板100である。

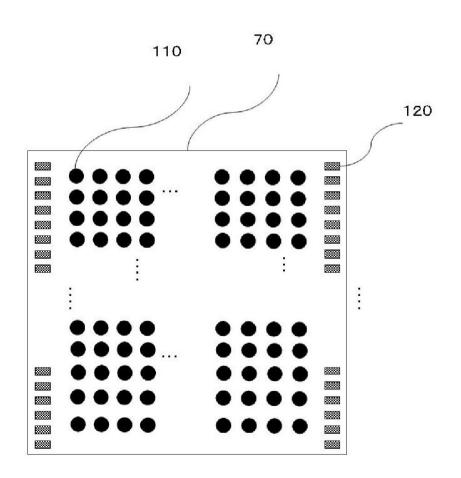

#### [0027]

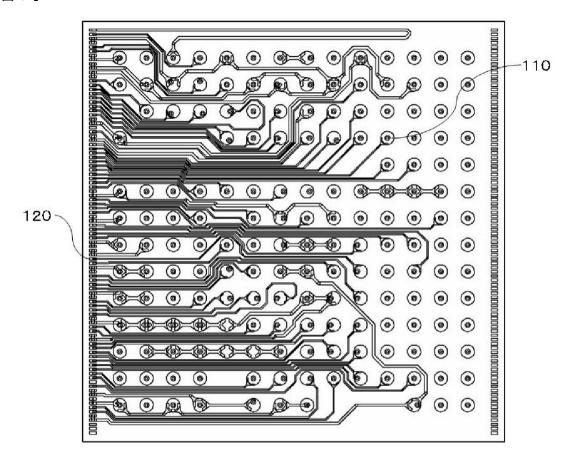

図3は図2に示したインターポーザー70の上面図であり、試験用電極110と実装用電極120とをその表面に配備している。試験用電極110は、例えば、14×14のアレイ状に配備し、0.8mmピッチである。これはCSPチップの電極ピッチと同じレベルである。したがって、これらの試験用電極に対する測定は、従来のソケット方式でのテストが可能になる。実装用電極120は、例えば、片側に96個ずつ配備され、130μ

10

20

30

40

50

mピッチである。これは、ベアチップの電極ピッチと同じレベルである。したがって、これらの実装用電極 1 2 0 からリードフレームへのワイヤリングは従来装置を用いて実施できる。

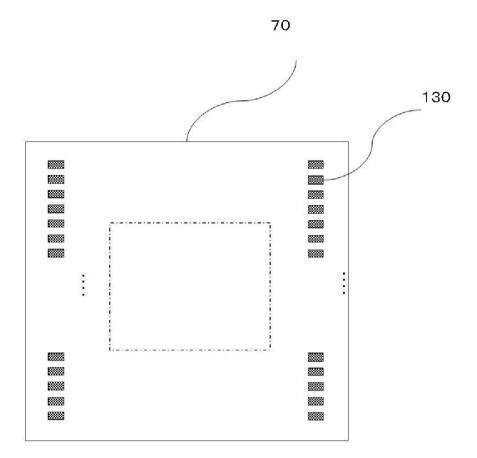

#### [0028]

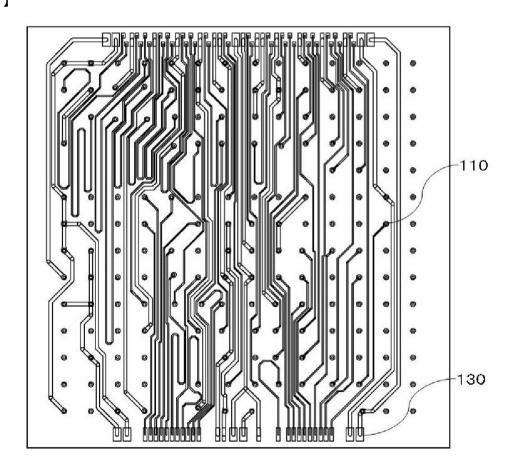

図4は図2に示したインターポーザー70の下面図である。このインターポーザー70上に配備する半導体ベアチップ30から内部電極130ヘワイヤリングを行う。内部電極130は、例えば、片側に36個ずつ配備され、160μmピッチである。

## [0029]

内部電極 1 3 0 と試験用電極 1 1 0 と実装用電極 1 2 0 との相互接続はインターポーザー 7 0 の内部配線で実現する。内部電極 1 3 0 と試験用電極 1 1 0 とを相互接続する第 1 層目の接続パターンを図 5 に示す。試験用電極 1 1 0 と実装用電極 1 2 0 とを相互接続する第 2 層目の接続パターンを図 6 に示す。 2 層を用いることで内部電極群、試験用電極群、実装用電極群を基板の面積を増加することなしに、相互の接続を実現している。このように、インターポーザー内の配線を多層にすることで、任意の試験用電極配置と実装用電極配置とが実現できる。

#### [0030]

インターポーザー内の配線を多層にすることで、任意の電極の接続が実現できることを、特開2001-196529の着想に応用したものが、図7である。図7の半導体ベアチップ30が図15の半導体ベアチップ30に相当し、図7のインターポーザー70が図15の半導体ベアチップ31の役割を受け持っている。すなわち、インターポーザー70の内部配線が半導体ベアチップ30からワイヤで接続可能な範囲を超えてパッケージ基板10への電気的接続を可能にしている。

## [0031]

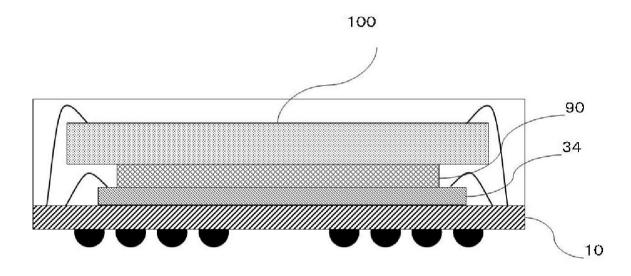

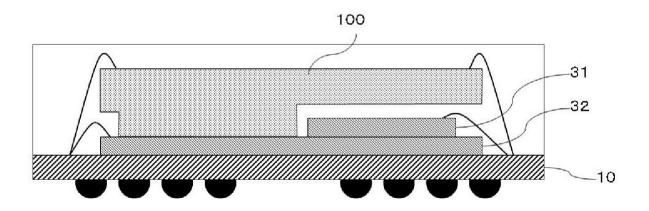

半導体チップマウント封止サブ基板100と半導体ベアチップ34とをSIP化した場合の例を図8に示す。この場合、半導体チップマウント封止サブ基板100が半導体ベアチップ34とほぼ同じ大きさなので、下チップのボンディングパッド部がかくれないよう、スペーサー90を半導体チップマウント封止サブ基板100と半導体ベアチップ34との間に挿入している。

## [0032]

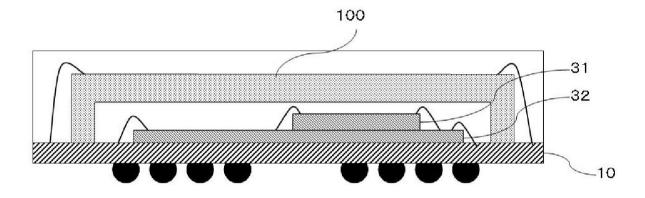

図8ではスペーサー90を用いていたが、半導体チップマウント封止サブ基板100にスペーサーの役割を果たす突起を備えることもできる。半導体チップマウント封止サブ基板100に突起を具備したものを図9に示す。この突起はモールド金型を所望の形状にすることで実現できる。この突起を半導体ベアチップ32上に接着し、半導体ベアチップ32からのワイヤリングスペースと半導体ベアチップ31からのワイヤリングスペースとを確保している。

## [0033]

図10に、図9と同様に半導体チップマウント封止サブ基板100に突起を備えた、別の実施例を示す。図9では、半導体チップマウント封止サブ基板に設けた突起を半導体ベアチップ32上に接着しているが、図10では、半導体チップマウント封止サブ基板100に設けた突起をパッケージ基板10上に接着している。この半導体チップマウント封止サブ基板100とパッケージ基板10との間に形成される空間に半導体ベアチップ31と32とを配備し、ワイヤリングを可能にしている。

## [0034]

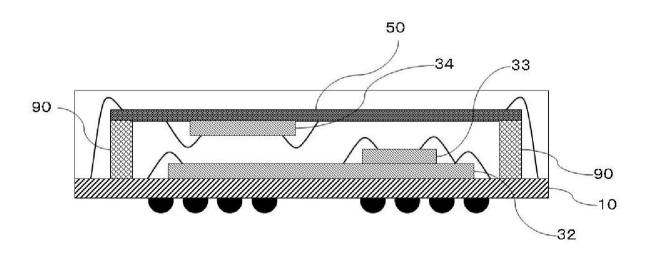

図11は、半導体チップマウントサブ基板50をパッケージ基板10上にスペーサー90を介して積層したものである。半導体チップマウントサブ基板50には、あらかじめ半導体ベアチップ34をマウントしている。この半導体チップマウントサブ基板50以外に、半導体ベアチップ32と半導体ベアチップ33とを積層配置した後、一括して樹脂封止を行っている。

## [0035]

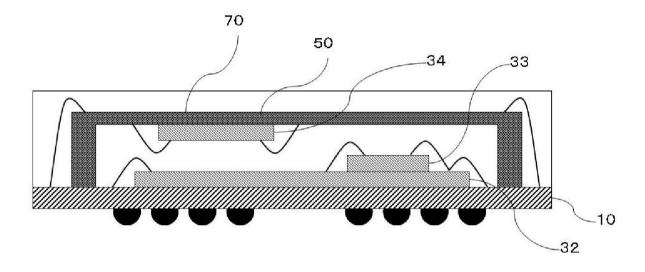

図11の半導体チップマウントサブ基板50は、スペーサー90を介して積層している

が、インターポーザー70に突起を具備し、これにスペーサーの役割をさせてもよい。インターポーザー70に突起を設けた構造を図12に示す。この場合でも封止は一括で行うことが可能である。

【図面の簡単な説明】

[0036]

- 【図1】本発明に係る半導体チップマウント封止サブ基板の外観図。

- 【図2】図1の半導体チップマウンド封止サブ基板の断面図。

- 【図3】図2に示したインターポーザー70の上面図。

- 【図4】図2に示したインターポーザー70の下面図。

- 【図5】内部電極130と試験用電極110とを相互接続するインターポーザー70内の 第1層目の接続パターン。

- 【図6】試験用電極110と実装用電極120とを相互接続するインターポーザー70内の第2層目の接続パターン。

- 【図7】本発明に係る、インターポーザー70の内部配線により、半導体ベアチップ30からワイヤで接続可能な範囲を超えてパッケージ基板10への電気的接続を可能にしている例。

- 【図8】本発明に係る、半導体チップマウント封止サブ基板100と半導体ベアチップ34とをSIP化した場合の例。

- 【図9】本発明に係る、突起を具備した半導体チップマウント封止サブ基板100と半導体ベアチップ31、32とをSIP化した場合の例。

- 【図10】本発明に係る、突起を具備した半導体チップマウント封止サブ基板100と半導体ベアチップ31、32とをSIP化した場合の例。

- 【図11】本発明に係る、半導体チップマウントサブ基板50をパッケージ基板10上にスペーサー90を介して積層し、半導体ベアチップ32、33とともに一括して樹脂封止した場合の例。

- 【図12】本発明に係る、突起を具備したインターポーザー70を持つ半導体チップマウントサブ基板50をパッケージ基板10上に積層し、半導体ベアチップ32、33とともに一括して樹脂封止した場合の例。

- 【図13】従来のSIPの例。

- 【図14】従来のSIPの例。

- 【図15】従来のSIPの例。

【符号の説明】

[0037]

- 10 パッケージ基板

- 20 半導体パッケージ

- 2 1 半導体パッケージ

- 22 半導体パッケージ

- 30 半導体ベアチップ

- 3 1 半導体ベアチップ 3 2 半導体ベアチップ

- 33 半導体ベアチップ

- 3 4 半導体ベアチップ

- 40 電極

- 4 1 電極

- 50 半導体チップマウントサブ基板

- 60 ワイヤ

- 61 ワイヤ

- 70 インターポーザー

- 80 封止樹脂

- 8 1 封止樹脂

20

10

30

40

- 90 スペーサー

- 100 半導体チップマウント封止サブ基板

- 1 1 0 試験用電極

- 120 実装用電極

- 1 3 0 内部電極

# 【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

## フロントページの続き

(72)発明者 小林 和男

兵庫県尼崎市道意町 7 丁目 1 番 3 号 尼崎リサーチインキュベーションセンター 株式会社 G E N U S I O N 内

(72)発明者 味香 夏夫

兵庫県尼崎市道意町7丁目1番3号 尼崎リサーチインキュベーションセンター 株式会社GENUSION内

審査官 今井 拓也

(56)参考文献 特表2007-516616(JP,A)

国際公開第2004/034433(WO,A1)

特開2002-141459(JP,A)

特開2005-209882(JP,A)

特開2002-040095(JP,A)

(58)調査した分野(Int.CI., DB名)

H01L 25/065

H01L 25/07

H01L 25/18