## RÉPUBLIQUE FRANÇAISE

## INSTITUT NATIONAL DE LA PROPRIÉTÉ INDUSTRIELLE

(A n'utiliser que pour les commandes de reproduction).

2 510 781

**PARIS**

A1

## DEMANDE DE BREVET D'INVENTION

<sub>20</sub> N° 82 12658

- Générateur de tension de référence.

- (51) Classification internationale (Int. Cl. 3). G 05 F 3/16; H 01 L 27/06.

- (33) (32) (31) Priorité revendiquée : JP, 31 juillet 1981, nº 119072/1981.

- (71) Déposant : Société dite : HITACHI LTD. JP.

- (72) Invention de : Jiroh Sakaguchi.

- 73 Titulaire : Idem 71

- Mandataire : Cabinet René G. Dupuy et Jean M. L. Loyer, 14, rue La Fayette, 75009 Paris.

La présente invention concerne un générateur de tension de référence, qui est constitué de transistor à effet de champ MISFET (l'abréviation MISFET désignant des transistors à effet de champ du type à grille isolée).

Deux transistors à effet de champ MISFET, dont les électrodes de grille sont constituéespar des matériaux possédant des fonctions de travail différentes l'une de l'autre, présentent des tension de seuil différentes l'une de l'autre. La différence entre les tensions de seuil des deux transistors MISFET est égale à la différence des fonctions de travail des électrodes de grille dans les transistors MISFET respectifs. La différence des tensions de seuil peut être utilisée en tant que tension de référence. Etant donné que la tension de référence ainsi obtenue possède une valeur déterminée par la différence des fonctions de travail des deux électrodes de grille, cette tension est moins susceptible de présenter des effets nuisibles attribués à des dispersions des caractéristiques des éléments du circuit.

C'est pourquoi, lorsqu'il est réalisé sous la forme d'un circuit intégré, un générateur de tension de référence utilisant la différence des fonctions de travail produit une tension de référence possédant une valeur relativement précise en dépit de dispersions comparativement importantes caractéristiques des différents éléments contenus dans le circuit intégré.

Cependant les recherches de l'inventeur ont révélé que la tension de référence présente une dépendance vis-à-vis de la température et une dépendance vis-à-vis de 30 la tension d'alimentation, qui ne sont pas négligeables.

C'est pourquoi un but de la présente invention est de fournir un générateur de tension de référence délivrant une tension de référence possédant un niveau stable indépendamment de fluctuations de la température.

Un autre but de la présente invention est de fournir un générateur de tension de référence qui délivre une

35

tension de référence d'un niveau stable indépendamment de fluctuations de la tension d'alimentation.

Un autre but de l'invention est de fournir un générateur de tension de référence, qui contient un nombre 5 réduit d'éléments de circuit.

Un autre but de la présente invention est de fournir un générateur de tension de référence qui convient pour être fabriqué sous la forme d'un circuit intégré CMOS (abréviation issue de l'expression anglaise "Complementary 10 Metal Oxyd Semiconductor" désignant un métal-oxyde-ensemble semiconducteur-complémentaire).

D'autres caractéristiques et avantages de la présente invention ressortiront de la description qui va suivre prise en référence aux dessins annexés, sur lesquels:

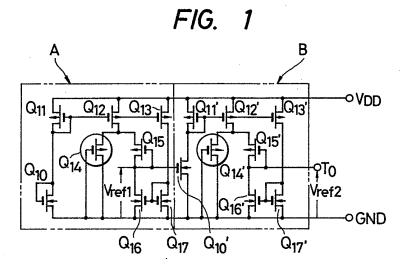

La figure 1 représente le schéma d'un générateur de tension de référence composé conformément à la présente invention;

15

30

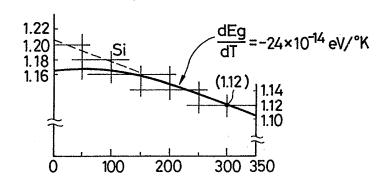

la figure 2 est un diagramme montrant l'intervalle de bande ou bande interdite  $E_g$  du silicium et la varia-20 tion de cet intervalle de bande en fonction de la température;

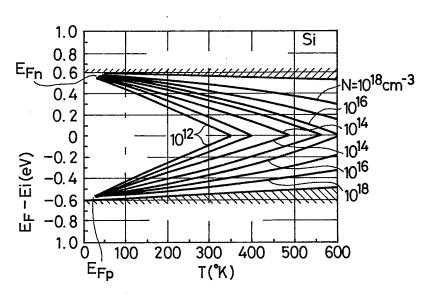

la figure 3 est un diagramme montrant les caractéristiques, en fonction de la température, des niveaux de Fermi d'un silicium de type n et d'un silicium de type p, 25 dont les densités d'impuretés sont prises en tant que paramètres;

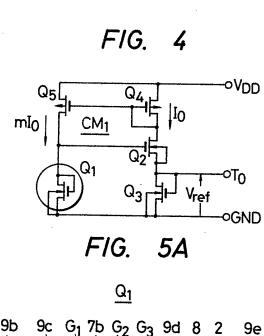

la figure 4 est le schéma du circuit d'un générateur de tension de référence qui représente une forme de réalisation de la présente invention;

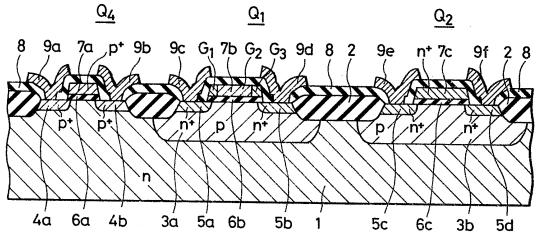

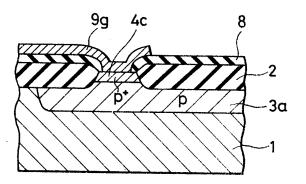

les figures 5A et 5B sont des vues en coupe d'une partie d'un circuit intégré CMOS;

les figures 5, 7 et 8 sont des schémas montrant chacun une autre forme de réalisation de la présente invention;

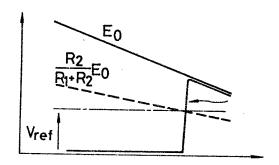

la figure 9 est un graphique montrant les courbes caractéristiques des circuits des figures 1 et 4; les figures 10A, 10B et 10C sont des diagrammes montrant chacun un circuit fournissant un courant en rapport géométrique;

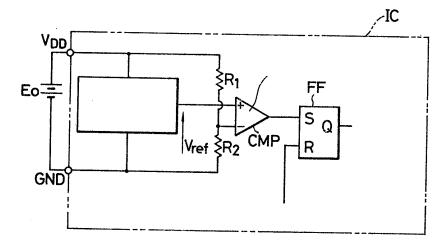

la figure 11 montre le schéma du circuit d'un vé-5 rificateur de batterie;

la figure 12 un diagramme d'une forme d'onde de fonctionnement du circuit de la figure 11; et

la figure 13 est le diagramme du circuit illustrant une autre forme de réalisation du générateur de 10 tension de référence.

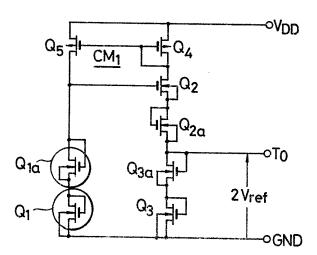

Antérieurement à la présente demande, l'inventeur avait proposé un générateur de tension de référence possédant l'agéncement illustré sur la figure 1.

Ce générateur de tension de référence est cons15 titué par un circuit B qui délivre une tension de référence V<sub>ref2</sub>, et un circuit A qui délivre une tension de

polarisation V<sub>ref1</sub> devant être envoyée au circuit B.

Dans le circuit B, deux transistors MISFET du type à canal p Q<sub>14</sub>, et Q<sub>15</sub>, ont leurs électrodes de gril20 le constituées par des couches de silicium polycristallin possédant des types de conductivité réciproquement opposés.

C'est-à-dire que l'électrode de grille du transistor MISFET Q<sub>14</sub>, est formée par une couche de silicium polycristallin de type n, tandis que l'électrode de grille du transistor

25 MISFET Q<sub>15</sub>, est constituée par une couche de silicium polycristallin de type p.

En raison des connexions du circuit telles que représentées sur la figure, la tension de référence V<sub>ref2</sub> devant être délivrée par le circuit B est réglée à une

30 valeur prodhe de la différence (V<sub>th1</sub> - V<sub>th2</sub>) entre la tension de seuil V<sub>th1</sub> du transistor MISFET Q<sub>14</sub>, et la tension de seuil V<sub>th2</sub> du transistor MISFET Q<sub>15</sub>. Etant donné que la différence des tensions de seuil (V<sub>th1</sub> - V<sub>th2</sub>) est égale à la différence entre le niveau de Fermi de la couche

35 de silicium polycristallin de type n et le niveau de Fermi de la couche de silicium polycristallin de type p, la

tension de référence V<sub>ref2</sub> prend une valeur proche de la différence des niveaux de Fermi entre la couche de silicium polycristallin de type n et la couche de silicium polycristallin de type p. Dans le cas où une impureté déterminant le type de conductivité dans la couche de silicium polycristallin du type n et dans la couche de silicium polycristallin du type p est présente avec une densité élevée égale par exemple à 10<sup>18</sup> atomes/cm³ ou plus, la différence des niveaux de Fermi prend une valeur proche de l'intervalle de bande ou bande interdite du silicium. La tension de référence V<sub>ref2</sub> prend par conséquent une valeur proche de l'intervalle de bande du silicium.

Dans le générateur de tension de référence présenté, la tension de sortie V<sub>ref2</sub> est stabilitée indépendamment de fluctuations de la température et de fluctuations de la tension d'alimentation, comme cela va être expliqué ci-après.

L'intervalle de bande du silicium dépend de la température. La physique des semiconducteurs est expliquée d'une manière très détaillée dans bon nombre d'articles de littérature. Parmi les ouvrages de la littérature on peut mentionner la publication "Physics of Semiconductor Devices" (physique des dispositifs à semiconducteurs) de S.M. SZE, publiéepar John Wiley & Sons en 1969, et notamment le chapitre 2 "Physics and Properties of Semiconductors" (physique et propriétés des semiconducteurs) pp 11 à 65.

La page 24 de ce document fournit la relation existant entre l'intervalle de bande E<sub>g</sub> et la température pour plusieurs semiconducteurs, et la figure 2 annexée à la présente demande reproduit la relation relative au silicium. De façon analogue le niveau de Fermi du silicium de type n et le niveau de Fermi du silicium de type p dépendent de la température. La figure 3 illustre les relations existant entre le niveau de Fermi et la température pour des matériaux formés de silicium de type n et de silicium de type p, et ce pour différentes densités d'impu-

retés.

Comme on le comprendra en se référant aux figures 2 et 3, la différence des tensions de seuil (v<sub>th1</sub> - v<sub>th2</sub>) entre les transistors MISFET Q<sub>14</sub>, et Q<sub>15</sub>; représentés sur la figure 1 implique une dépendance vis-à-vis de la température et sa valeur diminue lorsque la température augmente.

Par conséquent, dans le générateur de tension de la figure 1, le courant de fonctionnement du transistor

MISFET Q<sub>14</sub>, et celui du transistor MISFET Q<sub>15</sub>, sont en déséquilibre approprié de manière qu'une tension substantielle de compensation de la température puisse être produite par les transistors MISFET Q<sub>14</sub>, et Q<sub>15</sub>. Le rapport entre le courant de fonctionnement du transistor MISFET Q<sub>14</sub>, et celui du transistor MISFET Q<sub>15</sub>, est réglé à une valeur appropriée grâce à un réglage correct des dimensions des transistors MISFET Q<sub>11</sub>, - Q<sub>13</sub>, constituant un circuit fournissant un courant en rapport géométrique, et grâce à un réglage correct des dimensions des transistors MISFET Q<sub>16</sub>, et Q<sub>17</sub>, constituant un autre circuit fournissant un courant en rapport géométrique.

Le générateur de tension de référence de la fiquire 1 est également équipé d'un circuit similaire au circuit B, à savoir le circuit A constitué des transistors

25 MISFET Q<sub>10</sub> - Q<sub>17</sub>, afin de réduire les dépendances, vis-à-vis de la tension d'alimentation, des courants d'entrée des circuits délivrant des courants en rapport géométrique et constitués des transistors MISFET Q<sub>11</sub>, Q<sub>12</sub>, etc. Dans le circuit A, les courants de fonctionnement des transis-tors MISFET Q<sub>14</sub> et Q<sub>15</sub> sont rendus égaux. Etant donné que les courants de fonctionnement du transistor MISFET Q<sub>14</sub> du type à canal p comportant une électrode constituée par une couche de silicium polycristallin de type n, et du transistor MISFET Q<sub>15</sub> du type à canal p comportant une électrode de silicium polycristallin de type p sont rendus égaux, la tension de

sortie V<sub>ref1</sub> du circuit A prend par conséquent une valeur constante, non perturbée par des fluctuations des courants de polarisation, même lorsque ces derniers, qui sont délivrés par les transistors MISFET  $Q_{12}$  et  $Q_{13}$  dans le 5 circuit A, ont varié par suite d'une fluctuation de la tension d'alimentation  $\mathbf{V}_{\mathrm{DD}}.$  C'est-à-dire que la tension de sortie V<sub>ref1</sub> prend une valeur égale à la différence entre les niveaux de Fermi du silicium de type n et du silicium de type p. Etant donné qu'un transistor MISFET Q10, du 10 type à canal n situé dans le circuit B est alimenté par la tension de polarisation constante V<sub>ref1</sub> appliquée entre sa grille et sa source, il délivre un courant de drain constant qui n'est pas perturbé par la fluctuation de la tension d'alimentation  $V_{\mathrm{DD}}$ . On a supposé que les courants 15 de polarisation devant être délivrés par les drains des transistors MISFET Q<sub>12</sub>, et Q<sub>13</sub>, en réponse au courant de drain mentionné précédemment ne devraient pas avoir de dépendance vis-à-vis de la tension d'alimentation. Par conséquent on a supposé que la tension de référence V<sub>ref2</sub> devant être délivrée par le circuit B ne présenterait aucune dépendance vis-à-vis de la tension d'alimentation.

Cependant le générateur de tension de référence représenté requiert un nombre important d'éléments constitutifs du circuit étant donné qu'il est constitué de deux circuits possédant des agencements réciproquement semblables, à savoir le circuit A servant à stabiliser les courantsde polarisation indépendamment de fluctuations de la tension d'alimentation et le circuit B servant à déterminer la tension de sortie V<sub>ref2</sub> et réalisant une compensation en température de cette tension. En outre l'inventeur s'est aperçu que, en dépit de compensation de température, la caractéristique de variation de la tension de sortie du générateur de tension de référence en fonction de la température est légèrement incurvée vers le haut, comme cela est repéré par une courbe caractéristique L<sub>1</sub> sur la figure 9, à titre d'

exemple. En d'autres termes il était difficile de réaliser sur la tension de sortie  $V_{\rm ref2}$ , et ce dans une gamme étendue de températures, une compensation satisfaisante de l'action de la température.

Conformément à la présente invention, il est prévu un générateur de tension de référence possédant un nombre relativement réduit d'éléments de circuit et dont la compensation en température est réalisée de façon satisfaisante dans une gamme étendue de températures.

5

35

10 Conformément à la présente invention, le premier d'un couple de transistors MISFET dotés de tensions de seuil différentes de l'autre est connecté en diode. Le second du couple des transistors MISFET constitue un circuit en source suiveuse, qui reçoit la tension de drain 15 du premier transistor MISFET. La source du second transistor MISFET délivre par conséquent une tension possédant un niveau correspondant à la différence des tensions de seuil entre le premier transistor MISFET et le second transistor MISFET. Il est prévu un circuit approprié de 20 polarisation destiné à appliquer des courants de polarisation au premier et au second transistors MISFET. Le circuit de polarisation inclut un transistor MISFET qui reçoit, aux bornes de sa grille et de sa source, la tension délivrée par la source du second transistor MISFET. 25 Les courants de polarisation devant être envoyés au premier et au second transistors MISFET sont déterminés par le transistor MISFET situé dans le circuit de polarisation. Etant donné que le transistor MISFET situé dans le circuit de polarisation possède une caractéristique appropriée de 30 variation de sa tension de seuil en fonction de la température, la différence des tensions de seuil entre le premier et le second transistors MISFET ou la tension devant être délivrée par la source du second transistor MISFET est compensée en température.

La figure 4 montre le schéma d'un générateur de tension de référence constituant une première forme de réalisation de la présente invention. Dans cette forme de réalisation, bien qu'il ne faille y voir aucune limitation particulière, des transistors MISFET à canal p et des transistors MISFET à canal n constituent des circuits complémentaires et sont formés sur une seule puce ou microplaquette de silicium moyennant l'utilisation de la technologie connue descircuitsintégrés CMOS, utilisant la technique d'auto-alignement du silicium polycristallin.

Une couche de silicium polycristallin, qui sert

d'électrode de grille d'un transistor MISFET Q<sub>1</sub> à canal,

n, possède pour sa majeure partie une conductivité de

type p<sup>+</sup>. Une couche de silicium polycristallin qui sert

à constituer les électrodes de grille des transistors

MISFET Q<sub>2</sub> et Q<sub>3</sub> à canal n, est formée avec le type de

conductivité n<sup>+</sup> tout comme l'électrode de grille d'un

transistor MISFET à canal n ordinaire, qui est fabriqué

selon la technique connue d'auto-alignement du silicium

polycristallin. Les électrodes de grille des transistors

MISFET Q<sub>4</sub> et Q<sub>5</sub> de type p sont constituées par une couche

de silicium polycristallin du type de conductivité p<sup>+</sup>.

Le transistor MISFET, tel que le transistor

MISFET Q<sub>1</sub>, dont l'électrode de grille est réalisée avec

un matériau du type de conductivité opposé au type de

conductivité du canal de ce transistor, est entouré

25 d'un cercle. Etant donné que les autres transistors

MISFET usuels ne sont pas entourés de cercles, ils se

trouvent par conséquent bien distingués par rapport au

transistor MISFET indiqué précédemment, tel que le

transistor MISFET Q<sub>1</sub>. On a adopté la même disposition

30 sur les schémas d'autres formes de réalisations, que

l'on décrira ultérieurement.

Les figures 5A et 5B représentent des vues en coupe des transistors MISFET.

La surface principale d'un substrat 1 en mono-35 cristal de silicium de type n est parallèle au plan d' orientation cristalline (100) et l'on forme sur cette surface une pellicule d'oxyde de champ épaisse 2 ayant une épaisseur égale par exemple à environ 1 µm, au moyen de la technique connue d'oxydation locale. Les parties du substrat 1, qui ne sont pas recouvertes par la pellicule d'oxyde de champ 2, sont utilisées en tant que régions actives servant à former les éléments du circuit.

Le transistor MISFET Q<sub>4</sub> à canal p est constitué par la région de source 4a et la région de drain 4b possédant le type de conductivité b<sup>+</sup>, qui sont formées dans la surface du substrat 1, et par une couche de silicium polycristallin 7a de type b<sup>+</sup> qui est formée sur la surface du substrat 1 au-dessus d'une pellicule d'isolant de grille 6a. La couche de silicium polycristallin de type p<sup>+</sup> 7a constitue l'électrode de grille du transistor MISFET Q<sub>4</sub>.

Dans la surface du substrat 1 se trouvent formées des régions de puits de type p 3a et 3b servant à former les transistors MISFET  $Q_1$  et  $Q_2$  à canal n.

Le transistor MISFET Q1 est constitué par une région de source 5a et une région de drain 5b réalisées en un matériau du type n et qui sont formées dans la surface de la région de puits de type p 3a, et par une couche de silicium polycristallin 7b qui est formée sur la surface de la région de type p 3a au-dessus d'une pellicule d'isolant de grille 6b. La partie centrale  ${\tt G_2}$  de la source de silicium polycristallin 7b est du type pt. Sans que l'invention y soit particulièrement limitée, les deux zones ou parties d'extrémité G, et G, de la couche de silicium polycristallin 7b sont du typenn . Le transistor MISFET Q2 est constitué par une région de source 5c et une région de drain 5d, qui sont toutes deux du type n et qui sont formées dans la surface de la région de puits de type p 3b, et par une couche de silicium polycristallin de type n 7c, qui est formée à la surface la région de puits de type p 3b, au-dessus d'une pellicule d'isolant de grille 6c.

La surface de la région de puits de type p 3a est munie d'une région de contact de type p 4c comme cela est représenté sur la figure 5B.

Une pellicule isolante 8 constituée par exemple 5 par du verre aux phosphosilicates est formée sur la pellicule d'oxyde de champ 2 et sur la surface des parties du substrat 1 munie des transistors MISFET. A la surface de la pellicule isolant 8 se trouvent formées des couches de câblage 9a à 9g constituées par exemple par de l'aluminium déposé par évaporation. Les couches de câblage 9a 10 à 9g sont maintenues en contact ohmique avec les différentes régions des transistors MISFET. Afin d'accroître les tensions de rupture grille-drain des différents transistors MISFET et également afin d'empêcher que des impuretés indésirables ne s'introduisent dans les couches de 15 silicium polycristallin 7a à 7c, on réalise sur les surfaces de ces couches de silicium polycristallin 7a à 7c, des pellicules d'oxyde minces au moyen d'une action thermique, avant de réaliser la formation de la pellicule isolante 8. Cependant, sur l'illustration de la figure 5A, 20 de telles pellicules d'oxyde minces sont omises de manière à éviter une complication des dessins.

Le circuit intégré tel que représenté sur les figures 5A et 5B peut être fabriqué en utilisant la technologie de la fabrication des circuits intégrés CMOS, et ce sans adjonction d'une phase opératoire particulière de fabrication.

25

30

35

A titre d'exemple, après que les régions de puits de type p 3a et 3b, la pellicule d'oxyde de champ 2 et les pellicules d'isolant de grille 6a à 6c aient été formées, on réalise une couche de silicium polycristallin sur l'ensemble de la surface du substrat 1, en utilisant le processus connu de dépôt chimique en phase vapeur. Moyennant une attaque chimique sélective de cette couche de silicium polycristallin, on forme les couches de silicium polycristallin 7a à 7c.

Ultérieurement, on forme sur la surface du substrat 1, en utilisant le processus de dépôt chimique en phase vapeur, une première pellicule d'oxyde de silicium destinée à être utilisée en tant que masque introduisant une impure-5 té. On met en oeuvre l'attaque chimique sélective de manière à éliminer les parties de la première pellicule d'oxyde de silicium qui recouvrent les parties dans lesquelles doivent être formés les transistors MISFET à canal p, la partie  $G_2$  de la couche de silicium polycristallin  $7_{\rm h}$  est la 10 partie dans laquelle doit être formée la région de contact 4c. Ultérieurement on introduit une impureté de type p, tel que du bore, au moyen du processus de diffusiond'impuretés à l'intérieur des couches de silicium polycristallin et à l'intérieur des parties de la surface du substrat, qui ne sont pas recouvertes par la première couche d'oxyde de silicium. On forme ainsi les régions semiconductrices de type b 4a à 4c. En outre, l'ensemble de la couche de silicium polycristallin 7a et la partie centrale G2 de la couche de silicium polycristallin 7b sont réalisées avec le type de conductivité p<sup>†</sup>.

Ensuite, on enlève la première pellicule d'oxyde de silicium, à la suite de quoi on forme sur le substrat 1 une second pellicule d'oxyde de silicium destinée à être utilisée en tant que masque introduisant une impureté.

On élimine la seconde pellicule d'oxyde de silicium, au niveau de ses parties qui recouvrent les parties destinées à former les régions de source et de drain du transistor MISFET Q<sub>1</sub>, les parties d'extrémité G<sub>1</sub> et G<sub>3</sub> de la couche de silicium polycristallin 7b et la partie dans laquelle doit être formé le transistor MISFET Q<sub>2</sub>.

Ensuite, on introduit une impureté de type n, telle que du phosphore, dans les couches de silicium polycristallin et dans les parties superficielles des régions de puits de type b 3a et 3b, qui sont mises à nu.

35 Il en résulte que se trouvent ainsi formées les régions semiconductrices de type n 5a et 5b. En outre, les par-

ties d'extrémité G<sub>1</sub> et G<sub>3</sub> de la couche de silicium polycristallin 7b et de l'ensemble de la couche de silicium polycristallin 7c sont réalisées avec le type n<sup>+</sup>. L'impureté de type n est introduite dans les parties d'extrémité G<sub>1</sub> et G<sub>3</sub> de la couche de silicium polycristallin 7b, de sorte que les positions des parties d'extrémité des régions de source et de drain de type n<sup>+</sup> 5a et 5b du transistor MISFET Q<sub>1</sub> peuvent être déterminées par la couche de silicium polycristallin 7b, c'est-à-dire que, en d'autres termes, les régions 5a et 5b peuvent être formées en utilisant la technique d'auto-alignement. Les largeurs des parties d'extrémité G<sub>1</sub> et G<sub>3</sub> sont déterminées par la précision d'alignement du masque.

Le transistor MISFET Q<sub>1</sub> à canal n possède une

valeur de seuil V<sub>th1</sub> possédant une valeur relativement

importante étant donné que la partie G<sub>2</sub> de son électrode de grille est constituée par la couche de silicium

polycristallin de type p<sup>†</sup>. Le transistor MISFET Q<sub>2</sub> à

canal n possède une tension de seuil relativement fai

ble V<sub>th2</sub> étant donné que son électrode de grille est

constituée par la couche de silicium polycristallin de

type n<sup>†</sup>.

Les régions de puits de type p 3a et 3b, dans lesquelles les canaux des transistors MISFET respectifs

25 Q<sub>1</sub> et Q<sub>2</sub> sont formés, sont réalisées simultanément en utilisant la technologie de fabrication des circuits intégrés, de sorte qu'elles contiennent l'impureté déterminant le type de conductivité, et ce en des densités réciproquement égales. Etant donné que les pellicules

30 d'isolant de grille 6b et 6c sont formées de façon simultanée, elles sont constituées par le même matériau et en des épaisseurs identiques. Etant donné que les régions de canal des transistors MISFET Q<sub>1</sub> et Q<sub>2</sub> possèdent des caractéristiques identiques et que les pellicules d'isolant de grille 6b et 6c sont constituées par le même matériau et possèdent la même épaisseur, la différence entre

les tensions de seuil V<sub>th1</sub> et V<sub>th2</sub> devient égale à la différence entre le niveau de Fermi du silicium polycristallin de type p<sup>+</sup> et le niveau de Fermi du silicium polycristallin de type n<sup>+</sup>. Le silicium polycristallin de type n<sup>+</sup>, qui contient l'impureté déterminant le type de conductivité en une densité élevée égale par exemple à 10<sup>18</sup> atomes/cm³,possède un niveau de Fermi proche de la base de la bande de conduction dudit matériau. De facon analogue, le silicium polycristallin de type b<sup>+</sup> possède un niveau de Fermi proche de la valeur supérieure de la bande de valance dudit matériau. Par conséquent la différence des tensions de seuil (V<sub>th1</sub> - V<sub>th2</sub>) prend une valeur qui est proche de l'intervalle de bande ou bande interdite du silicium.

15 Sur la figure 4, le transistor MISFET  $Q_1$  est monté en diode, c'est-à-dire que le drain et la grille du transistor MISFET Q, sont raccordés l'un à l'autre. Le drain du transistor MISFET Q est raccordé à la grille du transistor MISFET  $\mathbf{Q}_2$  , qui doit être apparié au transistor MISFET  $Q_1$ . Le transistor MISFET  $Q_2$  constitue un circuit en source suiveuse, avec le transistor MISFET Q3. Un courant de polarisation devant s'écouler entre le drain et la source du transistor MISFET  $Q_2$ est déterminé par le transistor MISFET Q3. Le drain et la grille de ce transistor MISFET  $Q_3$  sont raccordés de telle manière que le courant de polarisation mentionné précédemment peut être déterminé par une tension de sortie V qui est délivrée par la source du transistor MISFET Q2. C'est-à-dire que le transistor MISFET Q3 est monté en diode. Afin d'envoyer un courant de polarisation au transistor MISFET Q1, il est prévu un circuit  $CM_1$  de production de courant en rapport géométrique, constitué par les transistors MISFET  $\mathbf{Q}_4$  et  $\mathbf{Q}_5$ à canal p. Le circuit CM<sub>1</sub> délivrant un courant en rap-35 port géométrique constitue une source de courant constant. Compte-tenu des raccordements du circuit tels

qu'indiqués sur la figure, le courant de polarisation d' entrée de la source de courant constant du type à courant à rapport géométrique est délivré par le drain du transistor MISFET Q<sub>2</sub>. Par conséquent un courant de polarisation 5 destiné à s'écouler à travers le transistor MISFET Q<sub>1</sub> se trouve dans un rapport précis avec le courant de polarisation traversant le transistor MISFET Q<sub>2</sub>.

Sur la figure 4, les grilles respectives de substrat (c'est-à-dire le substrat en silicium de type n 1 tel que représenté sur la figure 5A) des transistors MISFET Q4 et Q5 à canal p sont raccordés à une source d'alimentation en énergie VDD, ainsi que leurs sources respectives. Sur la figure cependant, les conducteurs de câblage situés entre les grilles de substrat des transistors MISFET Q4 et Q5 et la borne d'alimentation en énergie sont omis afin de conserver la clareté du dessin. De façon similaire les conducteurs de câblage reliant les transistors MISFET à canal p aux grilles de substrat sont omis des schémas des autres formes de réalisation que 1' on décrira ultérieurement.

Les grilles de substrat respectives des transistors MISFET Q<sub>1</sub> et Q<sub>3</sub> canal n, ainsi que leurs sources respectives, sont raccordées à une borne de potentiel de référence GND qui est maintenue à un potentiel tel que le potentiel de masse du circuit.

Dans cette forme de réalisation, il est souhaitable que la différence des tensions de seuil (V<sub>th1</sub> - V<sub>th2</sub>) entre les transistors MISFET Q<sub>1</sub> et Q<sub>2</sub> ne soient pas perturbée par un quelconque autre facteur que la différence entre les niveaux de Fermi du silicium polycristallin de type p<sup>+</sup> et du silicium polycristallin de type n<sup>+</sup>. Si la grille de substrat du transistor MISFET Q<sub>2</sub> est raccordée à la borne de potentiel de référence GND, une tension égale à la tension de sortie V<sub>ref</sub> sera appliquée entre la source et la grille de substrat du transistor MISFET Q<sub>2</sub>. Par conséquent la tension de seuil

V<sub>th2</sub> augmentera sous l'effet de la polarisation du substrat. La valeur de l'accroissement de la tension de seuil, qui est provoqué par l'effet de polarisation du substrat, est affectée par le niveau de Fermi d'un semiconducteur. Au contraire la tension de seuil V<sub>th1</sub> n'est pas affectée par l'effet de polarisation du substrat, étant donné que la source et la grille de substrat du transistor MISFET Q<sub>1</sub> sont au même potentiel. Par conséquent la différence des valeurs de seuil (V<sub>th1</sub> - V<sub>th2</sub>) prend une valeur inférieure à la différence des niveaux de Fermi.

Dans cette forme de réalisation, bien que l'invention n'y soit pas spécialement limitée, la grille de substrat dutransistor MISFET  $Q_2$  est raccordée à sa source de façon similaire au transistor MISFET  $Q_1$  apparié de manière à empêcher la diminution indésirable de la différence des tensions de seuil  $(V_{\rm th1}-V_{\rm th2})$ .

Ci-après on va décrire les caractéristiques électriques du circuit représenté.

En supposant que  $\underline{m}$  désigne un : facteur de multiplication de courant dans la circuit CM, délivrant un courant en rapport géométrique et constitué par les transistors MISFET  $Q_4$  et  $Q_5$  est que  $I_0$  désigne le courant de polarisation du transistor MISFET  $Q_2$ , le courant de polarisation, qui envoyé au drain du transistor MISFET Q1, 25 prend la valeur (m x  $I_0$ ). En supposant que  $\beta_0$  ( $W_1/L_1$ ),  $\beta_{o}$  (W<sub>2</sub>/L<sub>2</sub>) et  $\beta_{o}$  (W<sub>3</sub>/L<sub>3</sub>) (expressions dans lesquelles  $\beta_{\Omega}$  désigne une constante, W la largeur d'un canal et L la largeur d'un canal), désignent les transconductances des transistors MISFET respectifs  $Q_1$ ,  $Q_2$  et  $Q_3$ , 30 en supposant que  $V_{th1}$  et  $V_{th2}$  désignent les tensions de seuil des transistors MISFET respectifs  $Q_1$  et  $Q_2$  comme décrit précédemment et en supposant que V<sub>th3</sub> désigne la tension de seuil du transistor MISFET  $Q_3$ , la tension de sortie V ref prend une valeur satisfaisant à la relation  $v_{\text{ref}} = (v_{\text{th1}} - v_{\text{th2}}) + \sqrt{\frac{2 I_0}{\beta_C (\frac{1}{L_1})}} \sqrt{\frac{W_1}{W_2}} - \sqrt{\frac{W_1}{\frac{1}{W_2}}} \cdots (1)$ 35 suivante:

Ici le courant de polarisation  $I_0$  prend une valeur qui est déterminée par le transistor  $Q_3$  et qui satisfait à la relation (2):

$$I_o = \frac{1}{2} \beta_o (\frac{W_3}{L_3}) (V_{ref} - V_{th3})^2$$

....(2)

A partir des relations (1) et (2), on obtient par conséquent la tension de sortie  $V_{\text{ref}}$ , conformément à la relation (3):

5

10

15

20

$$v_{ref} = \{ (v_{th1} - v_{th2}) \} A v_{th3} \} / (1 - A) .....(3)$$

dans laquelle le terme A est une constante qui est fournie par la relation (4):

nie par la relation (4):

$$A = \sqrt{\frac{W_3}{(\frac{L}{3})} / (\frac{L}{L_1})} \left\{ \sqrt{m} - \sqrt{\frac{W_1}{L_1} / \frac{W_2}{L_2}} \right\} \qquad \dots (4)$$

Comme cela ressort des relations (3) et (4), la tension de sortie  $V_{\rm ref}$  prend une valeur déterminée uniquement par les dimensions et les tensions de seuil des transistors MISFET respectifs et ne dépend pas de la tension d'alimentation  $V_{\rm DD}$ .

Comme cela est visible d'après la relation (4), la valeur de la constante A est rendue nulle lorsque l' on donne des valeurs appropriées au facteur de multiplication de courant m et au rapport des dimensions de transistors MISFET Q<sub>1</sub> et Q<sub>2</sub>. A titre d'exemple, lorsque le facteur de multiplication de courant m est égal à 1 (un) et que les tailles des transistors MISFET Q<sub>1</sub> et Q<sub>2</sub> sont identiques, la constante A devient nulle. Alors la tension de sortie V<sub>ref</sub> devient égale à la différence des tensions de seuil (V<sub>th1</sub> - V<sub>th2</sub>), c'est-à-dire à la différence des niveaux de Fermi entre le silicium polycristallin de type p<sup>+</sup> et le silicium polycristallin de type n<sup>+</sup>, comme cela est visible d'après la relation (3).

Cependant il faut prendre soin de tenir compte du fait que l'intervalle de bande du silicium dépend de la température, comme cela est représenté sur la figure 2, et du fait que les niveaux de Fermi du silicium de type p et du silicium de type n dépendent de la température, comme cela est représenté sur la figure 3.

Dans le cas où les électrodes de grille des transistors MISFET  $Q_1$  et  $Q_2$  sont constituées par du silicium polycristallin comme cela est décrit ci-dessus, la différence des tensions de seuil ( $v_{th1} - v_{th2}$ ) présente une courbe caractéristique de température conformément à de telles dépendances des niveaux de Fermi des matériaux en silicium polycristallin, vis-à-vis de la tem-10 pérature. A titre d'exemple, dans le cas où l'on fait diffuser du bore et du phosphore à des densités importantes et sensiblement égales aux densités de saturation, dans les couches de silicium polycristallin destinées à former les électrodes de grille des transistors 15 MISFET Q<sub>1</sub> et Q<sub>2</sub> en vue d'obtenir une différence des tensions de seuil ( $v_{th1} - v_{th2}$ ) d'environ 1,2 volt , le coefficient de température mesuré de la différence des tensions de seuil ( $v_{th1} - v_{th2}$ ) était égale à environ - 0,3  $\sim$  - 0,5 mV/°C.

Dans cette forme de réalisation, on note la dépendance, vis-à-vis de la température, de la différence des tensions de seuil (V<sub>th1</sub> - V<sub>th2</sub>) et de la tension de seuil V<sub>th3</sub>.

Lorsque l'on prend la dérivée partielle du membre de droite de la relation (3) par rapport à la température T, on obtient la relation (5) suivante indiquant la dépendance de la tension de sortie V<sub>ref</sub> par rapport à la température:

$$\frac{\delta V_{ref}}{\delta T} = \begin{cases} \frac{\delta (V_{th1} - V_{th2})}{\delta T} - A \frac{\delta V_{th3}}{\delta T} \end{cases} / (1 - A) \dots (5)$$

Afin d'annuler la dépendance de la tension de sortie V<sub>ref</sub> vis-à-vis de la température, il est possible de régler la constante A en tenant compte de la dépendance, vis-à-vis de la température, de la différence des tensions de seuil (V<sub>th1</sub> - V<sub>th2</sub>) et de la tension de seuil V<sub>th3</sub> de manière à annuler les termes situés au numérateur

du membre de droite de la relation (4). Comme cela ressort de cette relation (4), la constante A est déterminée par les rapports des dimensions des transistors MISFET respectifs et par le facteur de multiplication de courant. Comme on le comprendra d'après les figures 2 et 3, la courbe caractéristique de variation de la différence des tensions de seuil (V<sub>th1</sub> - V<sub>th2</sub>) en fonction de la température est légèrement convexe. Bien que cela ne soit pas représentée, la courbe caractéristique de variation de la tension de seuil V<sub>th3</sub> du transistor MISFET Q<sub>3</sub> en fonction de la température est légèrement convexe tout comme celle de la différence des tensions de seuil (V<sub>th1</sub> - V<sub>th2</sub>).

Dans le cas précédent du circuit de la figure

15 1, la tension de compensation en température, qui est formée essentiellement par les transistors MISFET Q<sub>14</sub>: et Q<sub>15</sub>:, dont les courants de fonctionnement ne sont pas équilibrés, peut corriger la différence des tensions de seuil uniquement sur une gamme relativement étroite de températures. Il en résulte que la tension de sortie V<sub>ref2</sub> du circuit de la figure 1 présente une variation incurvée tout comme la courbe L<sub>1</sub> de la figure 9, auquelle on s'est référé précédemment.

Au contraire, dans le cas du circuit de la forme

25 de réalisation de la figure 4, la tension de seuil V<sub>th3</sub>

possède une dépendance vis-à-vis de la température, similaire à celle de la différence des tensions de seuil (V<sub>th1</sub>

- V<sub>th2</sub>), de sorte que la dépendance de cette différence

des tensions de seuil (V<sub>th1</sub> - V<sub>th2</sub>) vis-à-vis de la température peut être compensée de façon satisfaisante sur

une plage étendue de températures.

La courbe  $L_2$  représentée sur la figure 9 désigne le résultat mesuré de la tension de sortie  $V_{\rm ref}$  lorsque les dimensions des transistors MISFET  $Q_1$  et  $Q_3$  sont rendues réciproquement identiques et lorsque l'on rend égal à 1,5 le facteur de multiplication de courant

m du circuit CM<sub>1</sub> délivrant un courant en rapport géométrique et constitué par les transistors MISFET  $Q_4$  et  $Q_5$ , c'est-à-dire lorsque l'on rend la constante A égale à 0,22.

5 Comme cela ressort de la figure, le coefficient de température de la tension de sortie  $V_{ref}$  est constant indépendamment des températures. Le coefficient de température peut être rendu sensiblement nul grâce à un réglage approprié de la constante A.

10

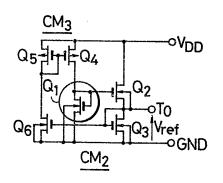

La figure 6 montre le circuit d'une autre forme de réalisation. Dans ce circuit un circuit  ${

m CM}_2$  délivrant un courant en rapport géométrique est constitué des transistors  $Q_3$  et  $Q_6$ , tandis qu'un autre circuit  $CM_3$  délivrant un courant à rapport géométrique est constitué des 15 transistor MISFET  $Q_5$  et  $Q_4$ . Le courant de drain du transistor MISFET  $Q_4$  est enveyé à un transistor MISFET  $Q_4$  à canal n possédant une électrode en silicium polycristal: lin de type p\*.

Frant donné que les transistors MISFET  $Q_q$  et 20 Q6 sont réglés à des dimensions appropriées, le rapport des courants entre les transistors MISFET  $Q_q$  et Q6 est réglé de façon correcte. Par conséquent le rapport des courants entre les translators MISFEF Q, et Q, est réglé de façon correcte.

25 Etant donné que le rapport des courants de polarisation destiné à traversar les transistors MISFET  $\mathbf{Q_1}$  et  $\mathbf{Q_2}$  et que les tailles des translistors MISFET  $\mathbf{Q_4}$  , Q2 et Q3 sont correctement réglés, il est possible d' obtenir, comme dans le circuit de la figure 4, une 30 tension de sortie V ref souhaitable, qui est stable visà-vis de variations de la température et de fluctuations

de l'alimentation en énergie.

Dans le circuit de la figure 6, le rapport des courants de polarisation devant traverser les transistors 35 MISFET Q1 et Q2 peut être également correctement réglé au moyen d'un réglage approprié du rapport des dimensions entre les transistors MISFET  $Q_5$  et  $Q_7$  constituant le circuit  ${\rm CM}_3$  délivrant un courant en rapport géométrique, au lieu de modifier le rapport des dimensions entre les transistors MISFET  $Q_3$  et  $Q_6$ .

5

25

Conformément au circuit de la figure 6, le drain du transistor MISFET  $\mathbf{Q}_2$  est maintenu à une tension élevée, étant donné qu'il est raccordé à une borne d'alimentation en énergie  $\mathbf{V}_{\mathrm{DD}}$ . Par conséquent le circuit de la figure 6 fonctionne de façon satisfaisante même avec une tension d'alimentation possédant une valeur inférieure à la tension limite inférieure de fonctionnement du circuit de la figure 4.

La figure 7 montre le circuit d'une autre forme de réalisation. Dans ce circuit de la figure 7, le courant de drain d'un transistor MISFET  $Q_3$  est envoyé à un circuit  $CM_4$  délivrant un courant en rapport géométrique et qui est constitué par les transistors MISFET  $Q_7,Q_6$  et  $Q_4$ .

Un courant de sortie du circuit  ${\rm CM_4}$  délivrant 20 un courant en rapport géométrique est envoyé à un transistor MISFET branché en diode  ${\rm Q_1}$ , tandis que le reste du courant de sortie est envoyé à un circuit  ${\rm CM_5}$  délivrant un courant en rapport géométrique et qui est constitué par les transistors MISFET  ${\rm Q_8}$  et  ${\rm Q_5}$ .

Un courant de polarisation est envoyé à force à travers un transistor MISFET  $\mathbf{Q}_2$  par le circuit  $\mathbf{CM}_5$  délivrant un courant en rapport géométrique.

Les transistors MISFET  $Q_1$ ,  $Q_2$  et  $Q_3$  sont constitués par destransistors MISFET possédant des structures semblages à celles des transistors MISFET  $Q_1$ ,  $Q_2$  et  $Q_3$  des figures 4 et 6.

Etant donné que les transistors MISFET  $Q_1$ ,  $Q_2$  et  $Q_3$  sont raccordés comme cela est représenté sur la figure 7, on peut tirer une tension constante  $V_{\rm ref}$  sur la grille du transistor MISFET  $Q_3$ .

Les courants de polarisation devant traverser

les transistors MISFET  $Q_1$  et  $Q_2$  sont réglés selon un rapport approprié par modification du facteur de multiplication de courant d'au moins l'un des circuits  ${\rm CM}_4$  et  ${\rm CM}_5$  délivrant des courants en rapport géométrique.

Le circuit de la forme de réalisation de la figure 7 a pour avantage que sa tension de sortie V peut être difficilement perturbée par une fluctuation d'une tension d'alimentation, comme cela est décrit ci-après.

5

La tension source-drain du transistor MISFET

10 Q<sub>4</sub> est modifiée par suite de la fluctuation de la tension d'alimentation. Lorsque la tension source-drain est modifiée de cette manière, l'intensité du courant dedrain du transistor MISFET Q<sub>4</sub> varie sous l'effet de l'action connue de modulation de la longueur du canal. Par conséquent l'intensité du courant de polarisation du transistor MISFET Q<sub>1</sub> est modifiée.

Cependant, dans cette forme de réalisation, de façon appropriée le courant de drain du transistor MISFET  $\mathbf{Q}_{\mathbf{6}}$  est modifié en même temps que le courant de drain du 20 transistor MISFET  $Q_4$ , sous l'action de l'effet de modulation de la longueur du canal. Par conséquent le rapport entre le courant dedrain du transistor MISFET  $Q_4$  et le courant de drain du transistor MISFET Q6 est réglé à une valeur essentiellement constante correspondant au rapport 25 des dimensions entre les transistors MISFET  $Q_4$  et  $Q_6$ , indépendamment de la fluctuation de la tension d'alimentation. Le transistor MISFET  $Q_5$  constituant un circuit  $CM_5$ délivrant un courant en rapport géométrique possède sa tension drain-source maintenue constante par le transis-30 tor MISFET Q2. Par conséquent le facteur de multiplication de courant du circuit  ${\rm CM}_5$  délivrant un courant en rapport géométrique est maintenu à une valeur constante indépendamment de la fluctuation de la tension d'alimentation.

Par conséquent le rapport entre les courants de polarisation devant traverser les transistors MISFET Q<sub>1</sub>

et Q<sub>2</sub> est maintenu à une valeur essentiellement constante indépendamment de la fluctuation de la tension d'alimentation. Etant donné que de cette manière le rapport des courants de polarisation des deux transistors MISFET Q<sub>1</sub> et Q<sub>2</sub> est maintenu à la bonne valeur, la variation, qui est imposée à la tension de sortie V<sub>ref</sub> dans le cas de la fluctuation de la tension d'alimentation, devient suffisamment faible.

La figure 8 montre le circuit d'une autre forme

de réalisation de la présente invention. Conformément au

circuit de cette forme de réalisation représentée sur la

figure 8, la dépendance d'une tension de sortie V<sub>ref</sub> visà-vis de la tension d'alimentation est améliorée d'une

manière plus satisfaisante. Dans un transistor MISFET

qui fonctionne dans sa plage de saturation, même lorsqu'

une tension de polarisation constante est appliquée en tre sa grille et sa source, le courant source-drain de

ce transistor est modifié sous l'effet connu de modula tion de longueur de canal, comme décrit ci-dessus, par

suite d'une modification de la tension source-drain de

ce transistor.

Dans le cas du circuit tel que représenté sur la figure 4, la grille et le drain d'un transistor MIS-FET Q<sub>5</sub> constituant le circuit CM<sub>1</sub> délivrant un courant en rapport géométrique sont raccordés en commun et par conséquent la tension source-drain de ce transistor est maintenue à une valeur essentiellement égale à sa tension de seuil. Par conséquent la tension source-drain du transistor MISFET Q<sub>5</sub> est maintenue à une valeur essentiellement constante indépendamment de la fluctuation de la tension d'alimentation V<sub>DD</sub>. Au contraire la tension source-drain du transistor Q<sub>1</sub> branché en diode est amenée à une valeur essentiellement constante, de sorte que la tension source-drain de l'autre transistor MISFET Q<sub>4</sub> constituant le circuit CM<sub>1</sub> délivrant un courant en rapport géométrique varie conformé-

ment à la fluctuation de la tension d'alimentation V<sub>DD</sub>. Le courant de drain du transistor MISFET Q<sub>4</sub> est par conséquent modifié d'une manière relativement importante conformément à la fluctuation de la tension d'alimentation V<sub>DD</sub>. Etant donné que le courant de drain du transistor MISFET Q<sub>4</sub> est modifié, le facteur m de multiplication de courant du circuit CM<sub>1</sub> délivrant un courant en rapport géométrique est modifié conformément à la fluctuation de la tension d'alimentation V<sub>DD</sub>. Pour cette raison la tension V<sub>ref</sub>, qui est délivrée par le circuit représenté sur la figure 4, vient à posséder une certaine dépendance vis-à-vis de la tension d'alimentation.

Dans le circuit représenté sur la figure 8, un circuit CM<sub>1</sub> délivrant un courant en rapport géométrique est constitué par des transistors MISFET Q<sub>5</sub> et Q<sub>4</sub> à canal p. En outre un amplificateur différentiel D-AMP est constitué par les transistors MISFET Q<sub>7</sub> et Q<sub>8</sub> à canal p servant à réaliser une amplification, et par les transistors MISFET Q<sub>9</sub> et Q<sub>10</sub> à canal n branchés de manière à former un circuit délivrant un courant en rapport géométrique. Un transistor MISFET Q<sub>6</sub> à canal p est interposé entre le drain du transistor MISFET Q<sub>4</sub> de sortie dans le circuit CM<sub>1</sub> délivrant un courant en rapport géométrique et entre la grille et le drain d'untransistor MISFET Q<sub>4</sub> branché en diode. La grille du transistor Q<sub>5</sub> est alimentéepar le signal de sortie de l'amplificateur différentiel D-AMP.

Compte-tenu des connexions représentées les tensions de drain des transisters MISFET Q<sub>4</sub> et Q<sub>5</sub> sont envoyées à l'amplificateur différentiel D-AMP. La sortie de l'amplificateur différentiel D-AMP est envoyée par contre-réaction à la grille du transistor MISFET Q<sub>6</sub>. Comme conséquence du fonctionnement en contre-réaction, la tension de drain du transistor MISFET Q<sub>4</sub> passe à une valeur égale à celle du transistor MISFET Q<sub>5</sub>.

35 Etant donné que les tensions source-drain des transistors MISFET  $Q_4$  et  $Q_5$  sont rendues égales l'une à

l'autre, les variations relatives des courants source-drain des transistors MISFET Q<sub>4</sub> et Q<sub>5</sub>, basées sur les effets respectifs de modulation de longueur de canal de ces transistors, deviennent réciproquement égales.Par conséquent le facteur de multiplication de courant m du circuit CM<sub>1</sub> délivrant un courant en rapport géométrique est maintenu constant indépendamment de la fluctuation de la tension d'alimentation V<sub>DD</sub>.

Etant donné que le facteur de multiplication m

10 est maintenu constant, une tension V<sub>ref</sub>, qui est délivrée par le circuit représenté sur la figure 8, ne présente essentiellement aucune dépendance vis-à-vis de la tension d'alimentation.

Chacune des figures 10A à 10C montrent l'

15 agencement d'un circuit CM<sub>1</sub> délivrant un courant en rapport géométrique, dont le facteur d'amplification de courant <u>m</u> varie légèrement par suite de l'effet de modulation

de la longueur de canal.

Chaucun des circuits des figures 10A à 10C peut 20 être remplacé par le circuit CM<sub>1</sub> délivrant un courant en rapport géométrique et représenté sur la figure 4, ou bien par le circuit CM, délivrant un courant en rapport géométrique ou l'amplificateur différentiel D-AMP et le transistor MISFET Q6 représentés sur la figure 8. Le cir-25 cuit représenté sur la figure 10A est constitué par le nombre le plus faible de transistors MISFET. Lorsque, dans le circuit de la figure 10B ou de la figure 10C, au moins les transistors MISFET  $Q_{23}$  et  $Q_{24}$  sont dotés de tensions de seuil identiques, les tensions source-30 drain des transistors MISFET  $Q_4$  et  $Q_5$  peuvent être rendues essentiellement égales l'une à l'autre. Afin de rendre égales les tensions de drain des transistors MIS-FET  $Q_4$  et  $Q_5$  indépendamment du facteur de multiplication de courant m, le rapport entre les dimensions des transistors MISFET  $Q_{23}$  et  $Q_{24}$  peut être rendu égal au rapport entre les dimensions des transistors MISFET  $Q_A$  et  $Q_5$ . La présente invention peut être largement utilisée en tant que générateur de tension de référence.

Par exemple ce dispositif convient pour former la tension de référence d'un contrôleur de pile, tel que représenté sur la figure 11, qui délivre une alarme lors de la diminution de la tension d'une pile et qui est utilisé dans un calculateur électronique de bureau, etc.. La raison en est qu'il comporte un nombre réduit d'éléments utilisés et qu'il peut être aisément mis sous la forme d'un circuit intégré MIS tenant sur une microplaquette.

Ce circuit fonctionne comme indiqué ci-après, En premier lieu il est prévu un générateur non représenté de signaux de remise à l'état initial et un signal de re-15 mise à l'état initial est produit par ce générateur au moment de la fermeture d'une alimentation en énergie. Un circuit à bascule bistable FF est, de façon correspondante, ramené à l'état initial par le signal de remise à l'état initial envoyé à sa borne de remise à l'état initial lors 20 de la fermeture de l'alimentation en énergie. Une tension divisée  $(R_2 E_0)/(R_1 + R_2)$ , qui délivrée par un diviseur de tension constitué par les résistances R<sub>1</sub> et R<sub>2</sub>, est remplacée par une tension de pile E<sub>0</sub>. Cette tension divisée et la tension de référence délivrée par le générateur 25 de tension de référence sont comparées par un comparateur CMP.

Dans le cas où la tension de pile E<sub>0</sub> est supérieure à une valeur prédéterminée, la sortie du comparateur CMP est placée à un niveau bas, qui est essentiellement égal au potentiel de masse.

Dans le cas où la tension E<sub>O</sub> est devenue inférieure à la valeur prédéterminée, la sortie du comparateur CMP est placée, en réponse, à un niveau haut, qui est essentiellement égal au niveau de la tension de pile E<sub>O</sub>.

La bascule bistable FF est par conséquent placée

dans son état positionné. Un dispositif d'affichage non représenté est commandé par le signal de sortie de positionnement de la bascule bistable FF, c'est-à-dire que l'affichage ou l'indication ou analogue de l'alarme d'une pile déchargée est réalisé. Les formes d'onde de fonctionnement sont représentées sur la figure 12.

Cette invention n'est pas limitée aux exemples de réalisation précédents. Au lieu de la réalisation, dans laquelle en vue de rendre inégales les tensions de seuil des transistors MISFET respectifs, on donne aux types de conductivité des couches de silicium polycristallin servant d'électrodes de grille, des valeurs différentes comme décrit précédemment, il est possible d' adopter une constitution dans laquelle on donne des valeurs différentes à différents facteurs aptes à influencer les tensions de seuil. Par exemple dans le cas de l'utilisation de différences entre les fonctions de travail des électrodes de grille, on peut réaliser l'électrode de grille de l'un de deux transistors MISFET avec 20 du silicium polycristallin et l'électrode de grille de l'autre transistor MISFET en aluminium, en molybdène ou analogue. On peut également modifier la densité d'une impureté déterminant le type de conductivité dans une partie devant être utiliséeen tant que région de canal 25 d'un transistor MISFET, en utilisant la technique d'implantation ionique ou analogue. Si cela est nécessaire on peut utiliser des transistors MISFET à canal p au lieu de transistors MISFET à canal n pour constituer les transistors MISFET tels que Q3 représentés sur les figures 4, 6 et 8 et qui sont branchés en diode afin de déterminer les niveaux des courants de polarisation. Dans le cas où une tension de référence relativement élevée est nécessaire, il est possible de combiner par exemple le circuit représenté sur la figure 4 avec un amplifica-35 teur linéaire possédant un gain approprié. On peut utiliser tout aussi bien un circuit possédant un agencement tel que représenté sur la figure 13.

## REVENDICATIONS

- 1. Générateur de tension de référence, caractérisé en ce qu'il comporte une borne de sortie, un circuit de polarisation (CM $_1$ -Q $_1$  à Q $_5$ ), comprenant un premier transis-5 tor MISFET  $(Q_3)$ , auquelest appliquée, entre sa grille et sa source, une tension  $\mathbf{V}_{\text{ref}}$  présente entre la borne de sortie et un point de référence (GND) et qui délivre un courant drain-source possédant un niveau correspondant à la tension appliquée entre la grille et la source, ledit circuit 10 de polarisation produisant un premier et un second courants de polarisation possédant des niveaux proportionnels au courant drain-source du premier transistor MISFET (Q2), un second transistor MISFET (Q1), dont la voie drain-source est branchée entre un premier noeud et ledit point de réfé-15 rence (GND) et dont la grille est accouplée au drain, la voie drain-source étant alimentée par le premier courant de polarisation, et un troisième transistor MISFET (Q2) qui possède une grille accouplée au premier noeud, une source accouplée à ladite borne de sortie, et un drain et 20 dont la tension de seuil est établie à une valeur inférieure à celle du second transistor MISFET (Q1) et dont la voie drain-source est alimentée par le second courant de polarisation, une tension correspondant à une différence entre la tension de seuil du premier transistor MISFET et 25 celle du troisième transistor MISFET étant appliquée par le troisième transistor MISFET à la borne de sortie.

- Générateur de tension de référence selon la revendication 1, caractérisé en ce qu'une différence de potentiel, qui est appliquée entre la grille de substrat

et la source du troisième transistor MISFET (Q<sub>1</sub>), est rendue égale à une différence de potentiel qui est appliquée entre la grille de substrat et la source du second transistor MISFET (Q<sub>1</sub>).

- 3. Générateur de tension de référence selon la 35 revendication 1, caractérisé en ce que le second transistor MISFET (Q<sub>1</sub>) et le troisième transistor (Q<sub>2</sub>) ont des

longueurs et des largeurs de canal réciproquement égales entre elles et que le premier courant de polarisation possède une valeur supérieure au courant de polarisation.

- 4. Générateur de tension de référence selon la 5 revendication 1, caractérisé en ce que la voie drain-source du premier transistor MISFET (Q3) est branchée entre la borne de sortie et le point de référence (GND), tandis que la grille de ce transistor est accouplée à son drain.

- 5. Générateur de tension de référence selon la revendication 4, caractérisé en ce que le circuit de polarisation comporte un circuit  $(CM_1, Q_4, Q_5)$  délivrant un courant en rapport géométrique et qui est alimenté par un courant de drain dudit troisième transistor à effet de champ  $(Q_1)$  de manière à fournir le premier courant de polarisation.

- 6. Générateur de tension de référence selon la revendication 5, caractérisé en ce que le circuit (CM<sub>1</sub>) produisant un courant en rapport géométrique est constitué par un quatrième transistor MISFET (Q<sub>4</sub>) dont la gril20 le et le drain sont accouplés et qui possède un type de conductivité opposé au celui du troisième transistor MISFET (Q<sub>1</sub>), et un cinquième transistor (Q<sub>5</sub>) dont la grille est accouplée à la grille du quatrième transistor MISFET (Q<sub>4</sub>), dont la source est accouplée à la source de ce transistor et qui possède le même type de conductivité que celui de ce quatrième transistor (Q<sub>4</sub>).

- 7. Générateur de tension de référence selon la revendication 6, caractérisé en ce qu'il comporte en outre un circuit additionnel  $(Q_6,D-AMP,Q_7-Q_{10})$ , qui rend la tension source-drain du cinquième transistor MISFET  $(Q_5)$ , essentiellement égale à celle du quatrième transistors MISFET  $(Q_4)$ .

- 8. Générateur de tension de référence selon la revendication 7, caractérisé en ce que le circuit addi35 tionnel est constitué par un sixième transistor MISFET (Q6), dont la voie source-drain est branchée entre le

drain du cinquième transistor MISFET  $(Q_5)$  et le drain du second transistor MISFET  $(Q_1)$  et qui possède le même type de conductivité que celui du cinquième transistor MISFET  $(Q_5)$ , et un amplificateur différentiel  $(D-AMP,Q_7 \ a \ Q_{10})$  qui possède une borne d'entrée non inverseuse alimentée par une tension de drain du quatrième transistor MISFET  $(Q_4)$ , une borne d'entrée inverseuse qui est alimentée par une tension de drain du cinquième transistor MISFET  $(Q_5)$  et une borne de sortie qui délivre une tension devant être  $(Q_6)$ .

- 9. Générateur de tension de référence selon la revendication 4, caractérisé en ce que le circuit de polarisation comporte un quatrième transistor MISFET, dont la grille et la source sont raccordées en commun à la grille et à la source du premier transistor MISFET, et un circuit (CM4) produisant un courant en rapport géométrique et qui est alimenté par un courant de drain du quatrième transistor MISFET, de manière à produire ainsi le premier courant de polarisation.

- 10. Générateur de tension de référence selon la revendication 1, caractérisé en ce que le circuit de polarisation comporte un circuit (CM<sub>4</sub>,CM<sub>5</sub>) délivrant un courant en rapport géométrique et qui est alimenté par le courant de drain du premier transistor MISFET (Q<sub>3</sub>) de manière à produire ainsi les premier et second courants de polarisation.

- 11. Générateur de tension de référence selon la revendication 10, caractérisé en ce que le circuit (CM4, Q7,Q6,Q4,CM5) produisant un courant en rapport géométrique est constitué par un quatrième transistor MISFET possédant une grille et un drain raccordés en commun au drain du premier transistor MISFET et qui possède un type de conductivité opposé à celui du premier transistor MISFET, et un cinquième et un sixième transistors MISFET dont les grilles et les sources sont raccordées respectivement à la grille et à la source du quatrième transistor MISFET et qui possèdent

le même type de conductivité que celui du quatrième transistor MISFET, ce qui a pour effet que le premier courant de polarisation est délivré par le drain du sixième transistor MISFET et que le second courant de polarisation est délivré par le drain du cinquième transistor MISFET.

- 12. Générateur de tension de référence selon la revendication 11, caractérisé en ce que le circuit (CM<sub>4</sub>; CM<sub>5</sub>,Q<sub>8</sub>;Q<sub>5</sub>) produisant un courant en rapport géométrique comporte en outre un septième transistor MISFET, dont la grille et le drain sont raccordés en commun au drain du cinquième transistor MISFET et qui possède le même type de conductivité que celui du premier transistor MISFET, et un huitième transistor MISFET dont une grille et une source sont raccordées respectivement en commun à la grille et à une source du septième transistor MISFET, et qui possède le même type de conductivité que celui du premier transistor MISFET, grâce à quoi le second courant de polarisation est produit sur le drain dudit huitième transistor MISFET.

- 13. Générateur de tension de référence selon la revendication 1, caractérisé en ce que les premier, second et troisième transistors MISFET (Q<sub>3</sub>,Q<sub>1</sub>,Q<sub>2</sub>) sont formés sur un substrat semiconducteur (1) qui constitue un circuit intégré CMOS.

- 25 14. Générateur de tension de référence selon la revendication 12, caractérisé en ce que la grille du second transistor MISFET (Q<sub>1</sub>) et la grille du troisième transistor MISFET (Q<sub>1</sub>) sont constituées en des matériaux possédant des fonctions de travail différentes l'une de 30 l'autre.

- 15. Générateur de tension de référence selon la revendication 14, caractérisé en ce que la grille du second transistor MISFET  $(Q_1)$  et la grille du troisième transistor MISFET  $(Q_2)$  sont réalisées en silicium.

- 35 16. Générateur de tension de référence selon la revendication 15, caractérisé en ce que le second et troi-

sième transistors MISFET  $(Q_1,Q_2)$  sont du type à canal n. 17. Générateur de tension de référence selon la revendication 16, caractérisé en ce que la grille du second transistor MISFET  $(Q_1)$  est du type p, tandis que la grille du troisième transistor MISFET  $(Q_1)$  est du type n. 18. Générateur de tension de référence selon la revendication 17, caractérisé en ce que le second et le troisième transistors MISFET  $(Q_1,Q_2)$  sont formés sur des régions de puits de type p, qui sont formées sur une surface dudit substrat semiconducteur (1), en étant électri-

quement indépendantes l'une de l'autre.

FIG. 2

FIG. 3

FIG. 5B

FIG. 6

FIG. FIG. ∽VDD D-AMP FIG. 1.43 1.42 1.41 <u>↓</u> -20 20 40 60 80 100 10B FIG. 10C FIG. 10A FIG. ∠VDD ∠VDD

FIG. 11

FIG. 12

FIG. 13