# (19) 대한민국특허청(KR) (12) 공개특허공보(A)

(43) 공개일자 2011년04월28일

(51) Int. Cl.

**H01L 23/12** (2006.01)

(21) 출원번호10-2009-0100892(22) 출원일자2009년10월22일

심사청구일자 **없음**

(71) 출원인

(11) 공개번호

삼성전자주식회사

경기도 수원시 영통구 매탄동 416

(72) 발명자

송인상

서울특별시 은평구 응암3동 120-9 월드빌아파트 103동 701호

10-2011-0044077

김혜진

경기도 수원시 영통구 영통2동 벽적골8단지아파트 822동 405호

(74) 대리인 **박상수**

전체 청구항 수 : 총 10 항

### (54) 반도체 패키지 구조물

### (57) 요 약

반도체 패키지 구조물을 제공할 수 있다. 이를 위해서, 제 1 및 2 패키지들을 차례로 적층시킬 수 있다. 상기 제 1 패키지는 하부측에 제 1 인쇄 회로 기판 및 상부측에 제 1 패드를 가질 수 있다. 상기 제 2 패키지는 하부측에 제 2 패드를 가질 수 있다. 상기 제 2 인쇄 회로 기판은 상부측에 제 3 패드를 가질 수 있다. 상기 제 2 인쇄 회로 기판은 상부측에 제 3 패드를 가질 수 있다. 상기 제 2 인쇄 회로 기판 상에 제 3 패키지가 배치될 수 있다. 상기 제 3 패키지는 하부측에 차례로 적충된 제 4 패드 및 제 3 인쇄 회로 기판을 가질 수 있다. 상기 제 1 패드 및 제 2 패드, 상기 제 3 패드 및 제 4 패드 사이에 솔더 볼들이 배치될 수 있다.

### 대 표 도 - 도2

45 45 -10 P1 -15 -20 -25 -30 70 -83 -50 55 -35 80-145 140-140-150 160 P2 . -174 -98 110 115 90 100 105 135 135 120 125 C2

242

### 특허청구의 범위

#### 청구항 1

제 1 인쇄 회로 기판 상에 제 1 반도체 칩들, 그리고 상기 제 1 반도체 칩들 상에 위치하면서 동일 레벨에 제 1 재 배선들 및 적어도 하나의 제 1 패드를 가지는 제 1 패키지; 및

상기 제 1 패키지 상에 적어도 하나의 제 1 솔더 볼, 상기 적어도 하나의 제 1 솔더 볼 상에 위치하면서 동일 레벨에 제 2 재 배선들 및 적어도 하나의 제 2 패드, 그리고 상기 제 2 재 배선들 및 상기 적어도 하나의 제 2 패드 상에 제 2 반도체 칩들을 가지는 제 2 패키지를 포함하되,

상기 제 1 반도체 칩들은 상기 제 1 인쇄 회로 기판과 전기적으로 접속하고, 상기 적어도 하나의 제 1 솔더 볼, 상기 제 2 재 배선들 및 상기 적어도 하나의 제 2 패드는 상기 제 2 반도체 칩들과 전기적으로 접속하고, 그리 고 상기 적어도 하나의 제 1 패드는 상기 적어도 하나의 제 1 솔더 볼과 마주보는 반도체 패키지 구조물.

### 청구항 2

제 1 항에 있어서.

상기 제 2 패키지 상에 제 2 인쇄 회로 기판;

상기 제 2 인쇄 회로 기판 상에 제 3 반도체 칩들, 그리고 상기 제 3 반도체 칩들 상에 위치하면서 동일 레벨에 제 3 재 배선들 및 적어도 하나의 제 3 패드를 가지는 제 3 패키지; 및

상기 제 3 패키지 상에 적어도 하나의 제 2 솔더 볼, 상기 적어도 하나의 제 2 솔더 볼 상에 위치하면서 동일 레벨에 제 4 재 배선들 및 적어도 하나의 제 4 패드, 그리고 상기 제 4 재 배선들 및 상기 적어도 하나의 제 4 패드 상에 제 4 반도체 칩들을 가지는 제 4 패키지를 포함하되,

상기 제 3 반도체 칩들은 상기 제 2 인쇄 회로 기판과 전기적으로 접속하고, 상기 적어도 하나의 제 2 솔더 볼, 상기 제 4 재 배선들 및 상기 적어도 하나의 제 4 패드는 상기 제 4 반도체 칩들과 전기적으로 접속하고, 그리 고 상기 적어도 하나의 제 3 패드는 상기 제 2 솔더 볼과 마주보는 반도체 패키지 구조물.

## 청구항 3

제 2 항에 있어서,

상기 제 1 반도체 칩들은 상기 제 1 인쇄 회로 기판 상에 차례로 적층되고, 상기 제 1 반도체 칩들은 양 측면들 중 적어도 하나를 실질적으로 동일 선 상에 위치시키는 형상 및 양 측면들 중 적어도 하나를 통해서 서로를 노 출시키는 형상 중 하나를 가지고,

상기 제 2 반도체 칩들은 상기 제 1 반도체 칩 상에 차례로 적충되고, 그리고 상기 제 2 반도체 칩들은 양 측면들 중 적어도 하나를 실질적으로 동일 선 상에 위치시키는 형상 및 양 측면들 중 적어도 하나를 통해서 서로를 노출시키는 형상 중 하나를 가지는 반도체 패키지 구조물.

#### 청구항 4

제 3 항에 있어서,

상기 제 3 반도체 칩들은 상기 제 2 인쇄 회로 기판 상에 차례로 적충되고, 상기 제 3 반도체 칩들은 양 측면들 중 적어도 하나를 실질적으로 동일 선 상에 위치시키는 형상 및 양 측면들 중 적어도 하나를 통해서 서로를 노출시키는 형상 중 하나를 가지고,

상기 제 4 반도체 칩들은 상기 제 3 반도체 칩 상에 차례로 적충되고, 그리고 상기 제 4 반도체 칩들은 양 측면들 중 적어도 하나를 실질적으로 동일 선 상에 위치시키는 형상 및 양 측면들 중 적어도 하나를 통해서 서로를 노출시키는 형상 중 하나를 가지는 반도체 패키지 구조물.

### 청구항 5

제 4 항에 있어서,

상기 제 1 재 배선들 및 상기 적어도 하나의 제 1 패드는 상기 제 2 재 배선들 및 상기 적어도 하나의 제 2 패

드와 서로 마주보고, 상기 적어도 하나의 제 1 솔더 볼은 상기 적어도 하나의 제 1 패드 및 상기 적어도 하나의 제 2 패드와 접촉하고,

상기 제 3 재 배선들 및 상기 적어도 하나의 제 3 패드는 상기 제 4 재 배선들 및 상기 적어도 하나의 제 4 패드와 서로 마주보고, 그리고 상기 적어도 하나의 제 2 솔더 볼은 상기 적어도 하나의 제 3 패드 및 상기 적어도 하나의 제 4 패드와 접촉하는 반도체 패키지 구조물.

#### 청구항 6

제 5 항에 있어서,

상기 적어도 하나의 제 1 패드는 상기 제 1 반도체 칩들과 전기적으로 접속하고, 상기 적어도 하나의 제 3 패드는 상기 제 3 반도체 칩들과 전기적으로 접속하고,

상기 제 1 재 배선들 중 일부는 상기 적어도 하나의 제 1 패드와 접촉하고, 상기 제 2 재 배선들 중 일부는 상 기 적어도 하나의 제 2 패드와 접촉하고, 상기 제 3 재 배선들 중 일부는 상기 적어도 하나의 제 3 패드와 접촉 하고, 그리고 상기 제 4 재 배선들 중 일부는 상기 적어도 하나의 제 4 패드와 접촉하는 반도체 패키지 구조물.

### 청구항 7

제 6 항에 있어서,

상기 제 1 반도체 칩들은 적어도 하나의 제 1 관통 실리콘 비아(Through Silicon Via; TSV)를 가지고, 상기 적어도 하나의 제 1 관통 실리콘 비아는 상기 제 1 반도체 칩들을 관통해서 상기 제 1 반도체 칩들을 전기적으로서로 접속시키고, 상기 제 1 재 배선들 중 나머지는 상기 적어도 하나의 제 1 관통 실리콘 비아와 접촉하고,

상기 제 2 반도체 칩들은 적어도 하나의 제 2 관통 실리콘 비아를 가지고, 상기 적어도 하나의 제 2 관통 실리콘 비아는 상기 제 2 반도체 칩들을 관통해서 상기 제 2 반도체 칩들을 전기적으로 서로 접속시키고, 그리고 상기 제 2 재 배선들 중 나머지는 상기 적어도 하나의 제 2 관통 실리콘 비아와 접촉하는 반도체 패키지 구조물.

#### 청구항 8

제 7 항에 있어서,

상기 제 3 반도체 칩들은 적어도 하나의 제 3 관통 실리콘 비아를 가지고, 상기 적어도 하나의 제 3 관통 실리콘 비아는 상기 제 3 반도체 칩들을 관통해서 상기 제 3 반도체 칩들을 전기적으로 서로 접속시키고, 상기 제 3 재 배선들 중 나머지는 상기 적어도 하나의 제 3 관통 실리콘 비아와 접촉하고,

상기 제 4 반도체 칩들은 적어도 하나의 제 4 관통 실리콘 비아를 가지고, 상기 적어도 하나의 제 4 관통 실리콘 비아는 상기 제 4 반도체 칩들을 관통해서 상기 제 2 반도체 칩들을 전기적으로 서로 접속시키고, 그리고 상기 제 4 재 배선들 중 나머지는 상기 적어도 하나의 제 4 관통 실리콘 비아와 접촉하는 반도체 패키지 구조물.

#### 청구항 9

제 1 항에 있어서,

상기 제 2 패키지 상에 차례로 적층된 제 2 인쇄 회로 기판 및 제 3 패키지를 더 포함하되,

상기 제 2 패키지는 상기 제 2 인쇄 회로 기판를 통해서 상기 제 3 패키지와 전기적으로 접속하는 반도체 패키지 구조물.

#### 청구항 10

제 8 항에 있어서,

상기 제 4 패키지 상에 차례로 적층된 제 3 인쇄 회로 기판 및 제 5 패키지를 더 포함하되,

상기 제 4 패키지는 상기 제 3 인쇄 회로 기판을 통해서 상기 제 5 패키지와 전기적으로 접속하는 반도체 패키지 구조물.

### 명 세 서

### 발명의 상세한 설명

### 기술분야

[0001] 실시예들은 반도체 패키지 구조물에 관한 것이다.

## 배경기술

- [0002] 최근에, 반도체 패키지 구조물은 고집적화를 구현하기 위해서 하부 패키지 및 상부 패키지를 차례로 적충해서 제조되고 있다. 상기 하부 패키지는 하부 인쇄 회로 기판 상에 하부 칩 적층 구조물(lower chip stack structure)을 갖는다. 상기 상부 패키지는 상부 인쇄 회로 기판 상에 상부 칩 적층 구조물을 갖는다. 상기 하부 및 상부 칩 적층 구조물들의 각각은 차례로 적충된 반도체 칩들을 갖는다. 이를 통해서, 상기 반도체 패키지 구조물은 하부 인쇄 회로 기판, 하부 칩 적층 구조물, 상부 인쇄 회로 기판 및 상부 칩 적층 구조물을 순서적으로 갖는다.

- [0003] 이 경우에, 상기 반도체 패키지 구조물은 하부 칩 적층 구조물 및 상부 칩 적층 구조물 사이에 상부 인쇄 회로 기판을 가지기 때문에 고집적화를 구현하는데 공정적인 한계를 줄 수 있다. 왜냐하면, 상기 상부 인쇄 회로 기판은 하부 칩 적층 구조물 및 상부 칩 적층 구조물 사이에서 반도체 패키지 구조물의 두께를 줄이는데 어려움을 준다. 더불어서, 상기 반도체 패키지 구조물은 하부 인쇄 회로 기판 및 상부 인쇄 회로 기판 사이에 하부 칩 적층 구조물을 가지기 때문에 고집적화를 구현하는데 공정적인 한계를 줄 수 있다.

- [0004] 왜냐하면, 상기 하부 칩 적충 구조물은 반도체 칩들의 적충 수를 증가시킴에 따라서 하부 인쇄 회로 기판 및 상부 인쇄 회로 기판 사이에서 공간적인 한계를 가지면서 공정 불량률을 증가시키기 때문이다. 따라서, 상기 반도체 패키지 구조물은 고집적화에 대한 공정 여유도를 가지지 못하기 때문에 다기능화의 추세에 저촉될 수 있다.

### 발명의 내용

#### 해결 하고자하는 과제

- [0005] 발명의 실시예들이 해결하고자 하는 기술적 과제는 전체적인 두께를 줄여서 고집적화를 구현하는 반도체 패키지 구조물을 제공하는데 있다.

- [0006] 발명의 실시예들이 해결하고자 하는 다른 기술적 과제는 공정 불량률을 줄이고 공정 여유도를 증가시켜서 다기 능화를 구현하는 반도체 패키지 구조물을 제공하는데 있다.

### 과제 해결수단

- [0007] 상기 기술적 과제들을 구현하기 위해서, 발명의 실시예들은 고집적화를 구현하기 위해서 인접한 하부 및 중부 칩 적층 구조물들 사이에 인쇄 회로 기판을 가지지 않는 반도체 패키지 구조물을 제공한다.

- [0008] 더불어서, 발명의 실시예들은 다기능화를 구현하기 위해서 하부 및 중부 칩 적층 구조물들 사이에 인쇄 회로 기판을 가지지 않고 그리고 중부 및 상부 칩 적층 구조물들을 사이에 두 개의 인쇄 회로 기판들을 가지는 반도체패키지 구조물을 제공하는데 있다.

- [0009] 실시예들에 따르는 반도체 패키지 구조물은 차례로 적충된 제 1 패키지 및 제 2 패키지를 포함할 수 있다. 상기 제 1 패키지는 제 1 인쇄 회로 기판, 적어도 하나의 제 1 반도체 칩 및 적어도 하나의 제 1 패드를 가질 수 있다. 상기 적어도 하나의 제 1 반도체 칩은 제 1 인쇄 회로 기판 상에 배치될 수 있다. 상기 적어도 하나의 제 2 패드는 상기 적어도 하나의 제 1 반도체 칩 상에 배치될 수 있다. 상기 제 2 패키지는 적어도 하나의 제 2 패드 및 적어도 하나의 제 2 반도체 칩을 가질 수 있다. 상기 적어도 하나의 제 2 패드는 상기 제 1 패키지 상에 배치될 수 있다. 상기 적어도 하나의 제 2 반도체 칩은 상기 제 1 인쇄 회로 기판과 전기적으로 접속할 수 있다. 상기 적어도 하나의 제 2 패드는 상기 적어도 하나의 제 1 패드와 마주볼 수 있다.

- [0010] 선택된 실시예들에 따라서, 상기 반도체 패키지 구조물은 제 2 인쇄 회로 기판, 제 3 패키지 및 제 4 패키지를 더 포함할 수 있다. 상기 제 2 인쇄 회로 기판은 상기 제 2 패키지 상에 배치될 수 있다. 상기 제 3 패키지는

적어도 하나의 제 3 반도체 칩 및 적어도 하나의 제 3 패드를 가질 수 있다. 상기 적어도 하나의 제 3 반도체 칩은 상기 제 2 인쇄 회로 기판 상에 배치될 수 있다. 상기 적어도 하나의 제 3 패드는 상기 적어도 하나의 제 3 반도체 칩 상에 배치될 수 있다. 상기 제 4 패키지는 적어도 하나의 제 4 패드 및 적어도 하나의 제 4 반도체 칩을 가질 수 있다. 상기 적어도 하나의 제 4 패드는 상기 제 3 패키지 상에 배치될 수 있다. 상기 적어도 하나의 의 제 4 반도체 칩은 상기 적어도 하나의 제 4 패드 상에 배치될 수 있다. 상기 제 2 인쇄 회로 기판은 상기 제 2 패키지와 전기적으로 접속할 수 있다. 상기 적어도 하나의 제 4 패드는 상기 적어도 하나의 제 4 반도체 칩과 전기적으로 접속한다. 상기 적어도 하나의 제 4 패드는 상기 적어도 하나의 제 3 패드와 마주볼 수 있다.

- [0011] 선택된 실시예들에 따라서, 상기 반도체 패키지 구조물은 상기 제 2 패키지에 적어도 하나의 제 1 솔더 볼, 및 상기 제 4 패키지에 적어도 하나의 제 2 솔더 볼을 더 포함할 수 있다. 상기 적어도 하나의 제 1 패드 및 상기 적어도 하나의 제 2 패드는 상기 적어도 하나의 솔더 볼과 접촉할 수 있다. 그리고, 상기 적어도 하나의 제 3 패드 및 상기 적어도 하나의 제 4 패드는 상기 적어도 하나의 제 2 솔더 볼과 접촉할 수 있다.

- [0012] 나머지 실시예들에 따라서, 상기 적어도 하나의 제 1 패드는 상기 적어도 하나의 제 1 반도체 칩과 전기적으로 접속할 수 있다. 상기 적어도 하나의 제 3 패드는 상기 적어도 하나의 제 3 반도체 칩과 전기적으로 접속할 수 있다.

- [0013] 나머지 실시예들에 따라서, 상기 반도체 패키지 구조물은 상기 제 2 패키지 상에 차례로 적충된 제 2 인쇄 회로 기판 및 제 3 패키지를 더 포함할 수 있다. 상기 제 2 패키지는 상기 제 2 인쇄 회로 기판을 통해서 상기 제 3 패키지와 전기적으로 접속할 수 있다.

- [0014] 실시예들에 따르는 반도체 패키지 구조물은 차례로 적충된 제 1 패키지 및 제 2 패키지를 포함할 수 있다. 상기 제 1 패키지는 제 1 인쇄 회로 기판, 제 1 반도체 칩들 및 제 1 재 배선들 및 적어도 하나의 제 1 패드를 가질수 있다. 상기 제 1 반도체 칩들은 제 1 인쇄 회로 기판 상에 배치될 수 있다. 상기 제 1 재 배선들 및 적어도하나의 제 1 패드은 상기 제 1 반도체 칩들 상에 위치하면서 동일 레벨에 배치될 수 있다. 상기 제 2 패키지는 적어도 하나의 제 1 솔더 볼, 제 2 재 배선들, 적어도 하나의 제 2 패드 및 제 2 반도체 칩들을 가질 수 있다. 상기 적어도 하나의 제 1 솔더 볼은 상기 제 1 패키지 상에 배치될 수 있다. 상기 제 2 재 배선들 및 적어도 하나의 제 2 패드는 상기 적어도 하나의 제 1 솔더 볼 상에 위치하면서 동일 레벨에 배치될 수 있다. 상기 제 2 반도체 칩들은 상기 제 2 재 배선들 및 상기 적어도 하나의 제 2 패드 상에 배치될 수 있다. 상기 제 1 반도체 칩들은 상기 제 1 인쇄 회로 기판과 전기적으로 접속할 수 있다. 상기 적어도 하나의 제 1 솔더 볼, 상기 제 2 재 배선들, 및 상기 적어도 하나의 제 2 밴도체 칩들과 전기적으로 접속할 수 있다. 상기 적어도 하나의 제 1 패드는 상기 적어도 하나의 제 1 솔더 볼과 마주볼 수 있다.

- [0015] 선택된 실시예들에 따라서, 상기 반도체 패키지 구조물은 제 2 인쇄 회로 기판, 제 3 패키지 및 제 4 패키지를 더 포함할 수 있다. 상기 제 2 인쇄 회로 기판은 상기 제 2 패키지 상에 배치될 수 있다. 상기 제 3 패키지는 제 3 반도체 칩들, 제 3 재 배선들 및 적어도 하나의 제 3 패드를 가질 수 있다. 상기 제 3 반도체 칩들은 상기 제 2 인쇄 회로 기판 상에 배치될 수 있다. 상기 제 3 재 배선들 및 적어도 하나의 제 3 패드는 상기 제 3 반도체 칩들 상에 위치하면서 동일 레벨에 배치될 수 있다. 상기 제 4 패키지는 적어도 하나의 제 2 솔더 볼, 제 4 재 배선들, 적어도 하나의 제 4 패드 및 제 4 반도체 칩들을 가질 수 있다. 상기 적어도 하나의 제 2 솔더 볼은 상기 제 3 패키지 상에 배치될 수 있다. 상기 제 4 재 배선들 및 적어도 하나의 제 4 패드는 상기 적어도 하나의 제 1 패트는 상기 적어도 하나의 제 2 솔더 볼 상에 위치하면서 동일 레벨에 배치될 수 있다. 상기 제 4 반도체 칩들은 상기 제 2 인쇄 회로 기관과 전기적으로 접속할 수 있다. 상기 적어도 하나의 제 2 솔더 볼, 상기 제 4 재 배선들, 및 상기 적어도 하나의 제 4 패드는 상기 제 4 반도체 칩들과 전기적으로 접속할 수 있다. 상기 제 5 반도체 집들은 상기 제 3 패드는 상기 제 2 솔더 볼과 마주볼 수 있다.

- [0016] 선택된 실시예들에 따라서, 상기 제 1 반도체 칩들은 상기 제 1 인쇄 회로 기판 상에 차례로 적충될 수 있다. 상기 제 1 반도체 칩들은 양 측면들 중 적어도 하나를 실질적으로 동일 선 상에 위치시키는 형상 및 양 측면들 중 적어도 하나를 통해서 서로를 노출시키는 형상 중 하나를 가질 수 있다. 상기 제 2 반도체 칩들은 상기 제 1 반도체 칩 상에 차례로 적충될 수 있다. 그리고, 상기 제 2 반도체 칩들은 양 측면들 중 적어도 하나를 실질적으로 동일 선 상에 위치시키는 형상 및 양 측면들 중 적어도 하나를 통해서 서로를 노출시키는 형상 중 하나를 가질 수 있다.

- [0017] 선택된 실시예들에 따라서, 상기 제 3 반도체 칩들은 상기 제 2 인쇄 회로 기판 상에 차례로 적충될 수 있다. 상기 제 3 반도체 칩들은 양 측면들 중 적어도 하나를 실질적으로 동일 선 상에 위치시키는 형상 및 양 측면들

중 적어도 하나를 통해서 서로를 노출시키는 형상 중 하나를 가질 수 있다. 상기 제 4 반도체 칩들은 상기 제 3 반도체 칩 상에 차례로 적충될 수 있다. 그리고, 상기 제 4 반도체 칩들은 양 측면들 중 적어도 하나를 실질적으로 동일 선 상에 위치시키는 형상 및 양 측면들 중 적어도 하나를 통해서 서로를 노출시키는 형상 중 하나를 가질 수 있다.

- [0018] 선택된 실시예들에 따라서, 상기 제 1 재 배선들 및 상기 적어도 하나의 제 1 패드는 상기 제 2 재 배선들 및 상기 적어도 하나의 제 2 패드와 서로 마주볼 수 있다. 상기 적어도 하나의 제 1 솔더 볼은 상기 적어도 하나의 제 1 패드 및 상기 적어도 하나의 제 2 패드와 접촉할 수 있다. 상기 제 3 재 배선들 및 상기 적어도 하나의 제 3 패드는 상기 제 4 재 배선들 및 상기 적어도 하나의 제 4 패드와 서로 마주볼 수 있다. 그리고, 상기 적어도 하나의 제 2 솔더 볼은 상기 적어도 하나의 제 3 패드 및 상기 적어도 하나의 제 4 패드와 접촉할 수 있다.

- [0019] 선택된 실시예들에 따라서, 상기 적어도 하나의 제 1 패드는 상기 제 1 반도체 칩들과 전기적으로 접속할 수 있다. 상기 적어도 하나의 제 3 패드는 상기 제 3 반도체 칩들과 전기적으로 접속할 수 있다. 상기 제 1 재 배선들 중 일부는 상기 적어도 하나의 제 1 패드와 접촉할 수 있다. 상기 제 2 재 배선들 중 일부는 상기 적어도 하나의 제 2 패드와 접촉할 수 있다. 상기 제 3 재 배선들 중 일부는 상기 적어도 하나의 제 3 패드와 접촉할 수 있다. 그리고, 상기 제 4 재 배선들 중 일부는 상기 적어도 하나의 제 4 패드와 접촉할 수 있다.

- [0020] 선택된 실시예들에 따라서, 상기 제 1 반도체 칩들은 적어도 하나의 제 1 관통 실리콘 비아(Through Silicon Via; TSV)를 가질 수 있다. 상기 적어도 하나의 제 1 관통 실리콘 비아는 상기 제 1 반도체 칩들을 관통해서 상기 제 1 반도체 칩들을 전기적으로 서로 접속시킬 수 있다. 상기 제 1 재 배선들 중 나머지는 상기 적어도 하나의 제 1 관통 실리콘 비아와 접촉할 수 있다. 상기 제 2 반도체 칩들은 적어도 하나의 제 2 관통 실리콘 비아를 가질 수 있다. 상기 적어도 하나의 제 2 관통 실리콘 비아는 상기 제 2 반도체 칩들을 관통해서 상기 제 2 반도체 칩들을 전기적으로 서로 접속시킬 수 있다. 그리고, 상기 제 2 재 배선들 중 나머지는 상기 적어도 하나의 제 2 관통 실리콘 비아와 접촉할 수 있다.

- [0021] 선택된 실시예들에 따라서, 상기 제 3 반도체 칩들은 적어도 하나의 제 3 관통 실리콘 비아를 가질 수 있다. 상 기 적어도 하나의 제 3 관통 실리콘 비아는 상기 제 3 반도체 칩들을 관통해서 상기 제 3 반도체 칩들을 전기적으로 서로 접속시킬 수 있다. 상기 제 3 재 배선들 중 나머지는 상기 적어도 하나의 제 3 관통 실리콘 비아와 접촉할 수 있다. 상기 제 4 반도체 칩들은 적어도 하나의 제 4 관통 실리콘 비아를 가질 수 있다. 상기 적어도 하나의 제 4 관통 실리콘 비아는 상기 제 4 반도체 칩들을 관통해서 상기 제 2 반도체 칩들을 전기적으로 서로 접속시킬 수 있다. 그리고, 상기 제 4 재 배선들 중 나머지는 상기 적어도 하나의 제 4 관통 실리콘 비아와 접촉할 수 있다.

- [0022] 나머지 실시예들에 따라서, 상기 반도체 패키지 구조물은 상기 제 2 패키지 상에 차례로 적흥된 제 2 인쇄 회로 기판 및 제 3 패키지를 더 포함할 수 있다. 상기 제 2 패키지는 상기 제 2 인쇄 회로 기판를 통해서 상기 제 3 패키지와 전기적으로 접속할 수 있다.

- [0023] 나머지 실시예들에 따라서, 상기 반도체 패키지 구조물은 상기 제 4 패키지 상에 차례로 적충된 제 3 인쇄 회로 기판 및 제 5 패키지를 더 포함할 수 있다. 상기 제 4 패키지는 상기 제 3 인쇄 회로 기판을 통해서 상기 제 5 패키지와 전기적으로 접속할 수 있다.

- [0024] 실시예들에 따르는 반도체 패키지 구조물은 차례로 적충된 제 1 패키지, 제 2 패키지, 제 2 인쇄 회로 기판 및 제 3 패키지를 포함할 수 있다. 상기 제 1 패키지는 제 1 인쇄 회로 기판, 제 1 반도체 칩들 및 적어도 하나의 제 1 패드를 가질 수 있다. 상기 제 1 반도체 칩들은 상기 제 1 인쇄 회로 기판 상에 배치될 수 있다. 상기 적어도 하나의 제 1 패드는 상기 제 1 반도체 칩들은 상이 배치될 수 있다. 상기 제 2 패키지는 적어도 하나의 제 2 패드 및 제 2 반도체 칩들은 사기 적어도 하나의 제 2 패드는 상기 제 1 패키지 상에 배치될 수 있다. 상기 제 2 반도체 칩들은 상기 적어도 하나의 제 2 패드 상에 배치될 수 있다. 상기 제 2 인쇄 회로 기판 및 제 3 패키지는 상기 제 2 패키지 상에 차례로 배치될 수 있다. 상기 제 1 및 2 패키지들은 상기 적어도 하나의 제 2 패드는 상기 제 2 반도체 칩들과 전기적으로 접속할 수 있다. 상기 적어도 하나의 제 2 패드는 상기 제 2 반도체 칩들과 전기적으로 접속할 수 있다. 상기 적어도 하나의 제 2 패드는 상기 제 2 반도체 칩들과 전기적으로 접속할 수 있다. 상기 적어도 하나의 제 2 패드는 상기 제 2 반도체 칩들과 전기적으로 접속할 수 있다. 상기 제 2 인쇄 회로 기판을 통해서 상기 제 3 패키지와 전기적으로 접속할 수 있다.

- [0025] 선택된 실시예들에 따라서, 상기 제 1 반도체 칩들은 상기 제 1 인쇄 회로 기판 상에 차례로 적충될 수 있다. 상기 제 1 반도체 칩들은 양 측면들 중 적어도 하나를 실질적으로 동일 선 상에 위치시키는 형상 및 양 측면들

중 적어도 하나를 통해서 서로를 노출시키는 형상 중 하나를 가질 수 있다. 상기 제 2 반도체 칩들은 상기 제 1 반도체 칩들 상에 차례로 적충될 수 있다. 그리고, 상기 제 2 반도체 칩들은 양 측면들 중 적어도 하나를 실질 적으로 동일 선 상에 위치시키는 형상 및 양 측면들 중 적어도 하나를 통해서 서로를 노출시키는 형상 중 하나를 가질 수 있다.

- [0026] 선택된 실시예들에 따라서, 상기 반도체 패키지 구조물은 상기 제 2 패키지에 적어도 하나의 제 1 솔더 볼을 더 포함할 수 있다. 그리고, 상기 적어도 하나의 제 1 솔더 볼은 상기 적어도 하나의 제 1 패드 및 상기 적어도 하나의 제 2 패드와 접촉할 수 있다.

- [0027] 나머지 실시예들에 따라서, 상기 제 1 인쇄 회로 기판은 상기 제 1 반도체 칩들과 전기적으로 접속하는 컨트롤러를 가질 수 있다. 상기 제 1 반도체 칩들은 외부를 통해서 서로를 전기적으로 접속시키는 와이어들(Wires)을 가질 수 있다. 상기 와이어들은 상기 제 1 인쇄 회로 기판과 접속할 수 있다. 상기 제 2 반도체 칩들은 적어도 하나의 관통 실리콘 비아를 가질 수 있다. 상기 적어도 하나의 관통 실리콘 비아는 상기 제 2 반도체 칩들을 관통해서 상기 제 2 반도체 칩들과 전기적으로 접속할 수 있다. 그리고, 상기 적어도 하나의 관통 실리콘 비아는 상기 제 2 인쇄 회로 기판과 접촉할 수 있다.

- [0028] 나머지 실시예들에 따라서, 상기 적어도 하나의 제 1 패드는 상기 제 1 반도체 칩들과 전기적으로 접속할 수 있다. 상기 제 2 인쇄 회로 기판은 적어도 하나의 제 3 패드를 가질 수 있다. 상기 제 3 패키지는 전기적으로 서로 접속하는 제 3 인쇄 회로 기판 및 적어도 하나의 제 3 반도체 칩을 가질 수 있다. 상기 제 3 인쇄 회로 기판은 차례로 적충된 적어도 하나의 제 2 솔더 볼 및 적어도 하나의 제 4 패드를 가질 수 있다. 그리고, 상기 적어도 하나의 제 2 솔더 볼은 상기 적어도 하나의 제 3 패드 및 상기 적어도 하나의 제 4 패드와 접촉할 수 있다.

### 直 과

- [0029] 상술한 바와 같이, 실시예들 따르는 반도체 패키지 구조물은 인접한 하부 및 중부 칩 적층 구조물들 사이에 인쇄 회로 기판을 가지지 않는다. 상기 하부 및 중부 칩 적층 구조물들의 각각은 차례로 적충된 반도체 칩들을 가질 수 있다. 이를 통해서, 상기 반도체 패키지 구조물은 종래 기술 대비 전체적인 두께를 줄이면서 반도체 칩들의 적층 수에 저촉받지 않고 고집적화를 구현할 수 있다.

- [0030] 더불어서, 실시예들 따르는 반도체 패키지 구조물은 하부 및 중부 칩 적층 구조물들 사이에 인쇄 회로 기판을 가지지 않고 그리고 중부 및 상부 칩 적층 구조물들을 사이에 두 개의 인쇄 회로 기판들을 가질 수 있다. 상기 하부 내지 상부 칩 적층 구조물들의 각각은 차례로 적층된 반도체 칩들을 가질 수 있다. 상기 상부 칩 적층 구조물은 하부 및 중부 칩 적층 구조물들과 다른 회로적인 기능을 할 수 있다. 이를 통해서, 상기 반도체 패키지 구조물은 종래 기술 대비 공정 여유도를 가지면서 다기능화를 구현할 수 있다.

### 발명의 실시를 위한 구체적인 내용

- [0031] 발명의 기술적 사상에 따르는 실시예들은 이후로 첨부 도면들을 참조해서 보다 상세하게 설명하기로 한다. 그러나, 발명은 여러가지 다른 형태들로 구체화되어질 수 있고, 그리고 여기에서 설명되는 실시예들로 한정되는 것으로 해석되지 않는다. 오히려, 상기 실시예들은 발명을 더욱 철저하고 그리고 완전하게 되도록 해주며, 당업자에게 본 발명의 영역을 충분히 전달할 수 있도록 해준다. 비록 '제 1 내지 3 패키지들', '하부 내지 상부 반도체 칩들', '제 1 내지 3 인쇄 회로 기판들', '하부 내지 상부 비아 홀들', '하부 내지 상부 관통 실리콘비아들', 및 '패드들' .. 등을 지청하는 용어들이 여러 구성 요소들을 기술하기 위하여 여기에서 사용되어질 수 있다면, 상기 구성 요소들은 이러한 용어들로 한정되지 않는 것으로 이해되어질 것이다. 단지, 이러한 용어들은 어떤 구성 요소로부터 다른 구성 요소를 구별하기 위해서 사용되어질 뿐이다. 여기에서, 사용되어진 바와 같이, "적어도 하나, 아래, 선택된, 일부, 나머지, 주변 및 상에" 등과 같이 특별히 상대적인 용어들은 선택된 구성요소, 다른 구성요소와 어떤 형상과의 상대적인 관계, 또는 도면들에 도시된 형상을 간단하게 설명하는데 설명의 간소화를 위해서 사용되어질 수 있다. 그리고, 여기에서 전문용어의 사용은 특별한 실시예들을 단지 설명하기 위함이지 발명을 한정하려는 것은 아니다.

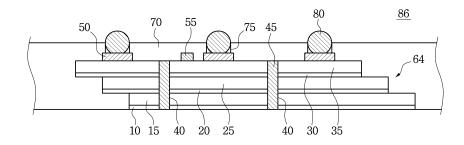

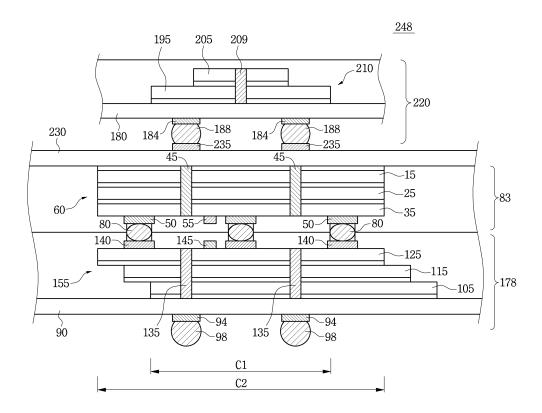

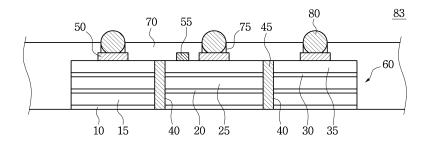

- [0032] 이제, 실시예들에 따르는 반도체 패키지 구조물은 도 1 및 2 를 참조해서 보다 상세하게 설명하기로 한다.

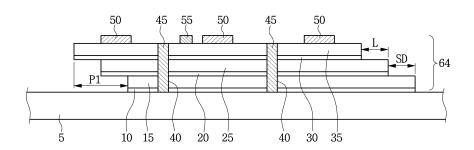

- [0033] 도 1 은 실시예들에 따르는 반도체 패키지 구조물들을 보여주는 평면도이다.

- [0034] 도 1 을 참조하면, 실시예들에 따르는 반도체 패키지 구조물들(242, 244, 246, 248)의 각각은 하부 반도체 칩

(105)을 가질 수 있다. 상기 반도체 패키지 구조물들(242, 244, 246, 248)의 각각은 하부 중심 영역(C2), 제 1 주변 영역(P1) 및 제 2 주변 영역(P2)을 가질 수 있다. 상기 하부 반도체 칩(105)은 적어도 하나일 수 있다. 상기 하부 반도체 칩(105)은 하부 중심 영역(C2)에 배치될 수 있다. 상기 하부 반도체 칩(105)은 하부 중심 영역(C2) 및 제 1 주변 영역(P1), 또는 하부 중심 영역(C2) 및 제 2 주변 영역(P2)에 배치될 수도 있다. 상기 하부 반도체 칩(105)은 하부 중심 영역(C2)에 하부 패드(140)들 및 하부 재 배선(145)들을 가질 수 있다.

- [0035] 상기 하부 패드(140)들 및 하부 재 배선(145)들은 하부 반도체 칩(105)의 선택된 면 상에 배치될 수 있다. 상기 하부 패드(140)들은 하부 반도체 칩(105)과 전기적으로 접속할 수 있다. 상기 하부 재 배선(145)들은 하부 패드(140)들과 전기적으로 접속할 수 있다. 상기 하부 반도체 칩(105)이 하부 패드(140)들 및 하부 재 배선(145)들을 가지는 경우에, 상기 하부 반도체 칩(105)은 하부 관통 실리콘 비아(135)들을 가질 수 있다. 상기 하부 관통 실리콘 비아(135)들은 하부 반도체 칩(105)을 관통할 수 있다.

- [0036] 상기 하부 관통 실리콘 비아(135)들은 하부 재 배선(145)들을 통해서 하부 패드(140)들과 전기적으로 접속할 수 있다. 상기 하부 반도체 칩(105) 아래에 하부 인쇄 회로 기판(90)이 배치될 수 있다. 상기 하부 인쇄 회로 기판(90)은 하부 관통 실리콘 바아(135)들과 전기적으로 접속할 수 있다. 상기 하부 반도체 칩(105)은 하부 중심 영역(C2)에 하부 패드(140)들, 하부 재 배선(145)들 및 제 1 접속 패드(CP1)들을 가질 수도 있다. 상기 제 1 접속 패드(CP1)들은 하부 재 배선(145)을 통해서 하부 패드(145)들과 전기적으로 접속할 수 있다. 상기 하부 반도체 칩(105)이 제 1 접속 패드(CP1)들을 가지는 경우에, 상기 하부 인쇄 회로 기판(90)은 제 1 주변 영역(P1) 또는 제 2 주변 영역(P2)에 제 1 컨트롤러(M1) 또는 제 2 컨트롤러(M2)를 가질 수 있다.

- [0037] 상기 제 1 컨트롤러(M1) 또는 제 2 컨트롤러(M2)는 하부 인쇄 회로 기판(90)과 전기적으로 접속할 수 있다. 상기 제 1 컨트롤러(M1) 또는 제 2 컨트롤러(M2)는 와이어(Wire; W)를 통해서 제 1 접속 패드(CP1)들 중 일부와 전기적으로 접속할 수 있다. 상기 제 1 접속 패드(CP1)들 중 나머지는 다른 와이어들(도면에 미 도시)을 통해서 하부 인쇄 회로 기판(90)과 전기적으로 접속될 수 있다. 상기 하부 반도체 칩(105) 상에 중부 반도체 칩(15)이 배치될 수 있다. 상기 중부 반도체 칩(15)은 하부 반도체 칩(105)과 동일한 형상을 가지거나 다른 형상을 가질수 있다.

- [0038] 상기 중부 반도체 칩(15)은 하부 반도체 칩(105)의 선택된 면과 마주보는 면 상에 중부 패드(50) 및 중부 재 배선(55)들을 가질 수 있다. 상기 중부 패드(50)는 중부 반도체 칩(15)과 전기적으로 접속할 수 있다. 상기 중부 재 배선(55)들은 중부 패드(50)들과 전기적으로 접속할 수 있다. 상기 중부 반도체 칩(15)이 중부 패드(50) 및 중부 재 배선(55)들을 가지는 경우에, 상기 중부 반도체 칩(15)은 중부 관통 실리콘 비아(45)들을 가질 수 있다. 상기 중부 관통 실리콘 비아(45)들은 중부 반도체 칩(15)을 관통할 수 있다.

- [0039] 상기 중부 관통 실리콘 비아(45)들은 중부 재 배선(55)들을 통해서 중부 패드(50)들과 전기적으로 접속할 수 있다. 상기 중부 패드(50)들은 솔더 볼(80)들을 통해서 하부 패드(140)들과 전기적으로 접속한다. 상기 중부 반도체 칩(15) 상에 중부 인쇄 회로 기판(230)이 배치될 수 있다. 상기 중부 인쇄 회로 기판(230)은 중부 관통 실리콘 비아(45)들과 전기적으로 접속할 수 있다. 상기 중부 인쇄 회로 기판(230)은 하부 인쇄 회로 기판(90)과 동일한 형상을 가지거나 다른 형상을 가질 수 있다.

- [0040] 상기 중부 반도체 칩(15)은 하부 중심 영역(C2)에 중부 패드(50)들, 중부 재 배선(55)들 및 제 2 접속 패드(CP2)들을 가질 수도 있다. 상기 제 2 접속 패드(CP2)들은 중부 재 배선(55)들을 통해서 중부 패드(55)들과 전기적으로 접속할 수 있다. 상기 중부 반도체 칩(15)이 제 2 접속 패드(CP2)들을 가지는 경우에, 상기 중부 인쇄회로 기판(230)은 제 1 주변 영역(P1) 또는 제 2 주변 영역(P2)에 제 1 컨트롤러(M1) 또는 제 2 컨트롤러(M2)를 가질 수 있다. 상기 제 1 컨트롤러(M1) 또는 제 2 컨트롤러(M2)는 중부 인쇄 회로 기판(230)과 전기적으로 접속할 수 있다. 상기 제 1 컨트롤러(M1) 또는 제 2 컨트롤러(M2)는 와이어(W)를 통해서 제 2 접속 패드(CP2)들 중일부와 전기적으로 접속할 수 있다.

- [0041] 상기 제 2 접속 패드(CP2)들 중 나머지는 다른 와이어들(도면에 미 도시)을 통해서 중부 인쇄 회로 기판(230)과 전기적으로 접속될 수 있다. 상기 중부 인쇄 회로 기판(230) 상에 상부 인쇄 회로 기판(180)이 배치될 수 있다. 상기 상부 인쇄 회로 기판(180)은 중부 인쇄 회로 기판(230)과 전기적으로 접속할 수 있다. 상기 상부 인쇄 회로 기판(180)은 중부 인쇄 회로 기판(230)과 동일한 형상을 가지거나 다른 형상을 가질 수 있다.

- [0042] 상기 상부 인쇄 회로 기판(180)은 중부 인쇄 회로 기판(230)과 동일한 구성 요소들을 가지거나 다른 구성 요소들을 가질 수 있다. 상기 상부 인쇄 회로 기판(180)은 하부 중심 영역(C2) 또는 상부 중심 영역(C1)에 상부 반도체 칩(195)을 가질 수 있다. 상기 상부 반도체 칩(195)은 적어도 하나일 수 있다. 상기 상부 반도체 칩(195)

은 하부 반도체 칩(105) 및 중부 반도체 칩(15)과 동일한 형상 또는 다른 형상을 가질 수 있다.

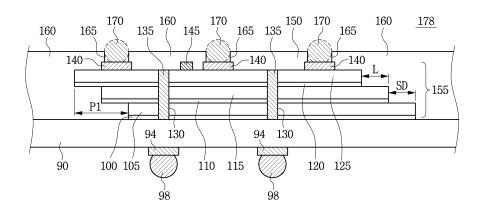

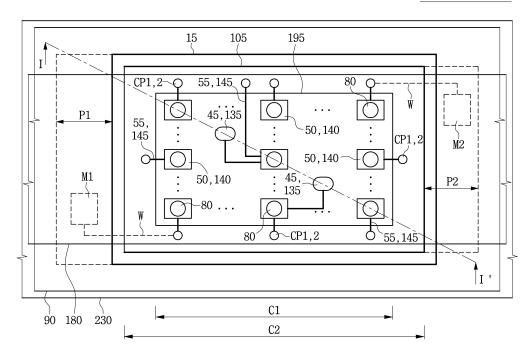

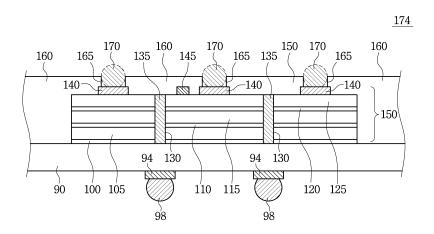

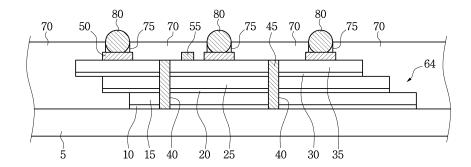

- [0043] 도 2 는 도 1 의 절단선 I-I'를 따라 취해서 반도체 패키지 구조물을 보여주는 단면도이다.

- [0044] 도 2 를 참조하면, 실시예들에 따르는 반도체 패키지 구조물(242)은 하부 패키지(174)를 포함할 수 있다. 상기하부 패키지(174)는 하부 인쇄 회로 기판(90), 하부 칩 적층 구조물(150) 및 보호막(160)을 가질 수 있다. 상기하부 인쇄 회로 기판(90)은 하부 회로부(도면에 미 도시), 외부 접속 패드(94)들 및 외부 접속 솔더 볼(98)들을 가질 수 있다. 상기 하부 회로부는 반도체 개별 소자들 및 도전 라인들을 가질 수 있다. 상기 도전 라인들은 반도체 개별 소자들과 전기적으로 접속할 수 있다.

- [0045] 상기 외부 접속 패드(94)들은 하부 인쇄 회로 기판(90) 아래에 위치해서 하부 회로부와 전기적으로 접속할 수 있다. 상기 외부 접속 솔더 볼(98)들은 외부 접속 패드(94)들을 통해서 하부 회로부와 전기적으로 접속할 수 있다. 상기 하부 칩 적층 구조물(150)은 하부 인쇄 회로 기판(90) 상에 배치될 수 있다. 상기 하부 칩 적층 구조물(150)은 제 1 내지 3 하부 접착제들(100, 110, 120), 제 1 내지 3 하부 반도체 칩들(105, 115, 125), 하부 관통 실리콘 비아(135)들, 하부 패드(140)들 및 하부 재 배선(145)들을 가질 수 있다.

- [0046] 상기 제 1 내지 3 하부 접착제들(100, 110, 120)은 제 1 내지 3 하부 반도체 칩들(105, 115, 125) 아래에 배치될 수 있다. 상기 제 1 내지 3 하부 반도체 칩들(105, 115, 125)은 반도체 패키지 구조물(242) 내 하부 중심 영역(C2)에 배치될 수 있다. 상기 제 1 내지 3 하부 반도체 칩들(105, 115, 125)은 동일한 반도체 소자이거나 서로 다른 반도체 소자들일 수 있다. 상기 제 1 내지 3 하부 반도체 칩들(105, 115, 125)은 양 측면들의 각각을 실질적으로 동일 선 상에 위치시키는 형상을 가질 수 있다.

- [0047] 상기 제 1 내지 3 하부 반도체 칩들(105, 115, 125)은 하부 중심 영역(C2)으로부터 제 2 주변 영역(P2)으로 연장할 수 있다. 이 경우에, 상기 제 1 내지 3 하부 반도체 칩들(105, 115, 125)은 양 측면들을 통해서 서로를 노출시키는 형상을 가질 수 있다. 상기 하부 관통 실리콘 비아(135)들은 제 1 내지 3 하부 접착제들(100, 110, 120) 및 제 1 내지 3 하부 반도체 칩들(105, 115, 125)을 관통해서 하부 인쇄 회로 기판(90)과 전기적으로 접속할 수 있다. 상기 하부 관통 실리콘 비아(135)들은 도 2 의 형상을 가지거나 도 2 와 다른 형상을 가질 수 있다.

- [0048] 상기 하부 관통 실리콘 비아(135)들은 도 1 의 와이어들(Wires)로 대체될 수도 있다. 상기 와이어들은 제 1 내지 3 하부 반도체 칩들(105, 115, 125)의 외부를 통해서 제 1 내지 3 하부 반도체 칩들(105, 115, 125)을 전기적으로 서로 접속시킬 수 있다. 상기 하부 관통 실리콘 비아(135)들이 와이어들(Wires)로 대체되는 경우에, 상기 하부 인쇄 회로 기판(90)은 도 1 의 제 1 컨트롤러(M1) 또는 제 2 컨트롤러(M2)를 가질 수 있다. 상기 하부 인쇄 회로 기판(90)은 도 1 의 와이어들, 도 1 의 제 1 접속 패드(CP1)들 및 도 1 의 제 1 컨트롤러(M1)를 통해서 제 1 내지 3 하부 반도체 칩들(105, 115, 125)과 전기적으로 서로 접속할 수 있다.

- [0049] 상기 하부 인쇄 회로 기판(90)은 도 1 의 와이어들, 도 1 의 제 1 접속 패드(CP1)들 및 도 1 의 제 2 컨트롤러 (M2)를 통해서 제 1 내지 3 하부 반도체 칩들(105, 115, 125)과 전기적으로 서로 접속할 수 있다. 상기 하부 패드(140)들 및 하부 재 배선(145)들은 제 3 하부 반도체 칩(125) 상에 위치해서 동일 레벨에 배치될 수 있다. 상기 하부 패드(140)들 및 하부 재 배선(145)들은 도 1 의 형상을 가지거나 도 1 과 다른 형상을 가질 수 있다. 상기 하부 패드(140)들은 제 3 하부 반도체 칩(125)과 전기적으로 접속할 수 있다. 상기 하부 패드(140)들은 하부 재 배선(145)들을 통해서 하부 관통 실리콘 비아(135)들과 전기적으로 접속할 수 있다. 상기 하부 보호막 (160)은 하부 칩 적층 구조물(150)을 덮도록 하부 인쇄 회로 기판(90) 상에 배치될 수 있다.

- [0050] 상기 하부 보호막(160)은 하부 패드(140)들을 노출시킬 수 있다. 상기 보호막(160) 상에 중부 패키지(83)가 배치될 수 있다. 상기 중부 패키지(83)는 중부 칩 적층 구조물(60) 및 중부 보호막(70)을 가질 수 있다. 상기 중부 칩 적층 구조물(60)은 제 1 내지 3 중부 접착제들(10, 20, 30), 제 1 내지 3 중부 반도체 칩들(15, 25, 35), 중부 관통 실리콘 비아(45)들, 및 중부 패드(50)들을 가질 수 있다. 상기 제 1 내지 3 중부 접착제들(10, 20, 30)은 제 1 내지 3 중부 반도체 칩들(15, 25, 35) 상에 배치될 수 있다.

- [0051] 상기 제 1 내지 3 중부 반도체 칩들(15, 25, 35)은 반도체 패키지 구조물(242) 내 하부 중심 영역(C2)에 배치될 수 있다. 상기 제 1 내지 3 중부 반도체 칩들(15, 25, 35)은 제 1 내지 3 하부 반도체 칩들(105, 115, 125)과 동일하거나 다를 수 있다. 상기 제 1 내지 3 중부 반도체 칩들(15, 25, 35)은 양 측면들의 각각을 실질적으로 동일 선 상에 위치시키는 형상을 가질 수 있다. 상기 제 1 내지 3 중부 반도체 칩들(15, 25, 35)은 하부 중심 영역(C2)으로부터 제 1 주변 영역(P1)으로 연장할 수 있다.

- [0052] 이 경우에, 상기 제 1 내지 3 중부 반도체 칩들(15, 25, 35)은 양 측면들을 통해서 서로를 노출시키는 형상을

가질 수 있다. 상기 제 1 내지 3 중부 반도체 칩들(15, 25, 35)은 하부 중심 영역(C2)으로부터 제 2 주변 영역 (P2)으로 연장할 수도 있다. 상기 제 1 내지 3 하부 반도체 칩들(105, 115, 125)은 하부 중심 영역(C2)으로부터 제 1 주변 영역(P1)으로 연장할 수도 있다. 상기 중부 관통 실리콘 비아(45)들은 제 1 내지 3 중부 접착제들 (10, 20, 30), 및 제 1 내지 3 중부 반도체 칩들(15, 25, 35)을 관통할 수 있다.

- [0053] 상기 중부 관통 실리콘 비아(45)들은 도 2 의 형상을 가지거나 도 2 와 다른 형상을 가질 수 있다. 상기 중부 관통 실리콘 비아(45)들은 도 1 의 와이어들로 대체될 수도 있다. 상기 와이어들은 제 1 내지 3 중부 반도체 칩들(15, 25, 35)의 외부를 통해서 제 1 내지 3 중부 반도체 칩들(15, 25, 35)을 전기적으로 서로 접속시킬 수 있다. 상기 중부 패드(50)들 및 중부 재 배선(55)들은 제 3 중부 반도체 칩(35) 상에 위치해서 동일 레벨에 배치될 수 있다. 상기 중부 패드(50)들은 제 3 중부 반도체 칩(35)과 전기적으로 접속할 수 있다.

- [0054] 상기 중부 패드(50)들은 중부 재 배선(55)들을 통해서 중부 관통 실리콘 비아(45)들과 전기적으로 접속할 수 있다. 상기 중부 패드(50)들 및 중부 재 배선(55)들은 도 1 의 형상을 가지거나 도 1 과 다른 형상을 가질 수 있다. 상기 중부 패드(50)들은 하부 패드(140)들과 서로 마주볼 수 있다. 상기 중부 재 배선(55)들은 하부 재 배선(145)들과 서로 마주보거나 부분적으로 중첩할 수 있다. 상기 중부 보호막(70)은 중부 칩 적층 구조물(60)을 감쌀 수 있다. 상기 중부 보호막(70)은 제 1 중부 접착제(10)를 노출시킬 수 있다.

- [0055] 상기 중부 보호막(70)은 중부 솔더 볼(80)들을 가질 수 있다. 상기 중부 솔더 볼(80)들은 중부 보호막(70)을 통해서 중부 패드(50)들과 접촉할 수 있다. 상기 중부 솔더 볼(80)들은 중부 보호막(70)의 상면으로부터 돌출해서하부 패드(140)들과 접촉할 수 있다. 이 경우에, 상기 하부 및 중부 패키지들(174, 83)은 하부 및 중부 보호막들(160, 70) 사이에 인쇄 회로 기판을 가지지 않는다. 상기 하부 및 중부 패키지들(174, 83)은 반도체 패키지구조물(242)의 전체적인 두께를 줄여서 반도체 패키지 구조물(242)의 고집적화를 구현할 수 있다.

- [0056] 상기 하부 및 중부 패키지들(174, 83)은 제 1 내지 3 하부 반도체 칩들(15, 25, 35), 및 제 1 내지 3 중부 반도 체 칩들(105, 115, 225)을 직접적으로 접촉시키지 않기 때문에 고정 여유도를 가지면서 공정 불량률을 감소시킬수 있다.

- [0057] 상기 중부 보호막(70) 및 제 1 중부 접착제(10) 상에 도 8 의 중부 인쇄 회로 기판(230)을 배치할 수도 있다. 상기 중부 인쇄 회로 기판(230)은 중부 회로부(도면에 미 도시), 및 내부 접속 패드(235)들을 가질 수 있다. 상기 중부 회로부는 하부 인쇄 회로 기판(90)의 하부 회로부와 동일하거나 다를 수 있다. 상기 내부 접속 패드(235)들은 중부 인쇄 회로 기판(230) 상에 위치해서 중부 회로부와 전기적으로 접속할 수 있다. 상기 중부 인쇄 회로 기판(230)은 하부 및 중부 패키지들(174, 83)과 함께 하나의 단위로 해서 적어도 한 번 반복적으로 적충될 수도 있다. 이 경우에, 상기 하부 패키지(174)의 외부 접속 솔더 볼(98)들은 중부 인쇄 회로 기판(230)의 내부 접속 패드(235)들과 접촉할 수 있다.

- [0058] 상기 중부 관통 실리콘 비아(45)들이 도 1 의 와이어들로 대체되는 경우에, 상기 중부 인쇄 회로 기판(230)은 도 1 의 제 1 컨트롤러(M1) 또는 제 2 컨트롤러(M2)를 가질 수 있다. 상기 중부 인쇄 회로 기판(230)은 도 1 의 와이어들, 도 1 의 제 2 접속 패드(CP2)들 및 도 1 의 제 1 컨트롤러(M1)를 통해서 제 1 내지 3 중부 반도체 칩들(15, 25, 35)과 전기적으로 서로 접속할 수 있다. 상기 중부 인쇄 회로 기판(230)은 도 1 의 와이어들, 도 1 의 제 2 접속 패드(CP2)들 및 도 1 의 제 2 컨트롤러(M2)를 통해서 제 1 내지 3 중부 반도체 칩들(15, 25, 3 5)과 전기적으로 서로 접속할 수 있다. 상기 중부 인쇄 회로 기판(230) 상에 도 8 의 상부 패키지(220)가 배치될 수도 있다. 상기 상부 패키지(220)는 상부 인쇄 회로 기판(180), 상부 칩 적층 구조물(210) 및 상부 보호막(215)을 가질 수 있다.

- [0059] 상기 상부 인쇄 회로 기판(180)은 상부 회로부(도면에 미 도시), 상부 패드(184)들 및 상부 솔더 볼(188)들을 가질 수 있다. 상기 상부 회로부는 중부 인쇄 회로 기판(230)의 중부 회로부와 동일하거나 다를 수 있다. 상기 상부 패드(184)들은 상부 인쇄 회로 기판(180) 아래에 위치해서 상부 회로부와 전기적으로 접속할 수 있다. 상기 상부 패드(184)들은 내부 접속 패드(235)들과 마주볼 수 있다. 상기 상부 솔더 볼(188)들은 내부 접속 패드(235)들 및 상부 패드(184)들과 접촉할 수 있다.

- [0060] 상기 상부 칩 적층 구조물(210)은 제 1 및 2 상부 접착제들(190, 200), 제 1 및 2 상부 반도체 칩들(195, 205), 및 상부 관통 실리콘 비아(209)를 가질 수 있다. 상기 제 1 및 2 상부 접착제들(190, 200)은 제 1 및 2 상부 반도체 칩들(195, 205) 아래에 배치될 수 있다. 상기 제 1 및 2 상부 반도체 칩들(195, 205)은 반도체 패키지 구조물(242) 내 상부 중심 영역(C1)에 배치될 수 있다. 상기 제 1 및 2 상부 반도체 칩들(195, 205)은 동일한 반도체 소자이거나 서로 다른 반도체 소자들일 수 있다.

- [0061] 상기 제 1 및 2 상부 반도체 칩들(195, 205)은 제 1 내지 3 중부 반도체 칩들(15, 25, 35)과 다를 수 있다. 상기 제 1 및 2 상부 반도체 칩들(195, 205)은 양 측면들의 각각을 동일 선 상에 위치시키는 형상 및 양 측면들을 통해서 서로를 노출시키는 형상 중 하나를 가질 수 있다. 상기 상부 관통 실리콘 비아(209)은 적어도 하나일 수 있다. 상기 상부 관통 실리콘 비아(209)는 제 1 및 2 상부 접착제들(190, 200), 제 1 및 2 상부 반도체 칩들 (195, 205)을 관통할 수 있다.

- [0062] 상기 제 1 및 2 상부 반도체 칩들(195, 205)은 상부 관통 실리콘 비아(209)를 통해서 전기적으로 서로 접속될 수 있다. 상기 상부 관통 실리콘 비아(209)는 상부 인쇄 회로 기판(180)의 상부 회로부와 접촉할 수 있다. 상기 상부 관통 실리콘 비아(209)는 도 2 와 동일한 형상 또는 도 2 와 다른 형상을 가질 수 있다. 상기 상부 관통 실리콘 비아(209)는 와이어들(도면에 미 도시)로 대체될 수도 있다. 상기 와이어들은 제 1 및 2 상부 반도체 칩들(195, 205)의 외부를 통해서 제 1 및 2 상부 반도체 칩들(195, 205)을 전기적으로 서로 접속시킬 수 있다.

- [0063] 상기 상부 관통 실리콘 비아(209)들이 와이어들로 대체되는 경우에, 상기 상부 인쇄 회로 기판(180)은 컨트롤러 (도면에 미 도시)를 가질 수 있다. 상기 상부 인쇄 회로 기판(180)은 와이어들, 접속 패드들(도면에 미 도시) 및 컨트롤러를 통해서 제 1 및 2 상부 반도체 칩들(195, 2055)과 전기적으로 서로 접속할 수 있다. 상기 상부 칩 적층 구조물(210)을 덮도록 상부 인쇄 회로 기판(180) 상에 상부 보호막(215)을 형성할 수 있다.

- [0064] 이 경우에, 상기 상부 패키지(220)는 하부 및 중부 패키지들(174, 83), 그리고 중부 인쇄 회로 기판(230)과 함 께 반도체 패키지 구조물(242)의 다기능화를 구현할 수 있다.

- [0065] 다음으로, 실시예들에 따르는 반도체 패키지 구조물의 형성방법은 도 3 내지 15 를 참조해서 설명하기로 한다.

- [0066] 도 3 내지 8 은 도 1 의 절단선 I-I'를 따라 취해서 반도체 패키지 구조물의 형성방법을 보여주는 단면도들이다. 도 3 내지 8 은 도 2 와 동일 부재에 대해서 동일한 참조 부호를 사용하기로 한다.

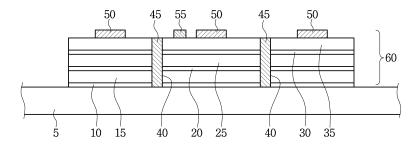

- [0067] 도 3 을 참조하면, 실시예들에 따라서 캐리어(5) 상에 제 1 중부 접착제(10) 및 제 1 중부 반도체 칩(15)을 차례로 형성할 수 있다. 상기 캐리어(5)는 제 1 중부 접착제(10) 및 제 1 중부 반도체 칩(15)의 지지부재(Support Member)일 수 있다. 상기 제 1 중부 접착제(10)는 절연 물질을 포함할 수 있다. 상기 제 1 중부 반도체 칩(15)은 휘발성 또는 비휘발성 반도체 소자를 포함할 수 있다. 상기 제 1 중부 반도체 칩(15) 상에 제 2 중부 접착제(20) 및 제 2 중부 반도체 칩(25)을 차례로 형성할 수 있다.

- [0068] 상기 제 2 중부 접착제(20)는 제 1 중부 접착제(10)와 동일할 수 있다. 상기 제 2 중부 반도체 칩(25)은 제 1 중부 반도체 칩(15)과 동일하거나 다를 수 있다. 계속해서, 상기 제 2 중부 반도체 칩(25) 상에 제 3 중부 접착제(30) 및 제 3 중부 반도체 칩(35)을 차례로 형성할 수 있다. 상기 제 3 중부 접착제(30)는 제 1 중부 접착제(10)와 동일할 수 있다. 상기 제 3 중부 반도체 칩(35)은 제 1 중부 반도체 칩(15)과 동일하거나 다를 수 있다. 상기 제 3 중부 반도체 칩(35) 상에 적어도 하나의 중부 접착제 및 적어도 하나의 중부 반도체 칩을 차례로 형성할 수 있다. 상기 제 1 내지 3 중부 접착제들(10, 20, 30), 및 제 1 내지 3 중부 반도체 칩들(15, 25, 35)에 중부 비아 홀(40)들을 형성할 수 있다.

- [0069] 상기 중부 비아 홀(40)들은 제 1 내지 3 중부 접착제들(10, 20, 30), 및 제 1 내지 3 중부 반도체 칩들(15, 25, 35)을 관통할 수 있다. 상기 중부 비아 홀(40)들에 중부 관통 실리콘 비아(45)들을 형성할 수 있다. 상기 중부 관통 실리콘 비아(45)들은 제 1 내지 3 중부 반도체 칩들(15, 25, 35)을 전기적으로 서로 접속시킬 수 있다. 상기 중부 관통 실리콘 비아(45)들은 도전 물질을 포함할 수 있다. 상기 제 3 중부 반도체 칩(35) 상에 중부 패드(50)들 및 중부 재 배선(55)들을 형성할 수 있다.

- [0070] 상기 중부 패드(50)들 및 중부 재 배선(55)들은 도전 물질을 포함할 수 있다. 상기 중부 패드(50)들은 제 3 중부 반도체 칩(35)과 전기적으로 접속할 수 있다. 상기 중부 재 배선(55)들은 중부 패드(50)들 및/ 또는 중부 관통 실리콘 비아(45)들과 전기적으로 접속할 수 있다. 이를 통해서, 상기 중부 관통 실리콘 비아(45)들 및 중부 패드(50)들은 제 1 내지 3 중부 접착제들(10, 20, 30), 제 1 내지 3 중부 반도체 칩들(15, 25, 35), 및 중부 재 배선(55)들과 함께 제 1 중부 칩 적층 구조물(60)을 형성할 수 있다.

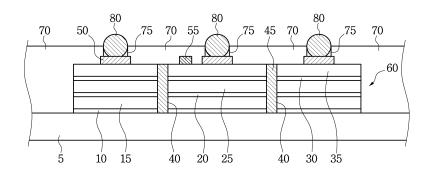

- [0071] 도 4 및 5 를 참조하면, 실시예들에 따라서, 상기 제 1 중부 칩 적층 구조물(60)을 덮도록 캐리어(5) 상에 중부 보호막(70)을 도 4 와 같이 형성할 수 있다. 상기 중부 보호막(70)은 에폭시 수지(epoxy resin)를 포함할 수 있다. 상기 중부 보호막(70) 상에 표도 및 식각 공정들을 수행할 수도 있다. 상기 레이저 조사를 수행할 수 있다. 상기 중부 보호막(70)에 중부 몰딩 홀(75)들을 도 4 와 같이 형성시킬 수 있다.

- [0072] 상기 식각 공정은 중부 보호막(70) 상에 건식 식각 에천트 또는 습식 식각 에천트를 적용할 수 있다. 상기 중부 몰딩 홀(75)들은 중부 패드(50)들을 노출시키도록 형성될 수 있다. 상기 중부 몰딩 홀(75)들에 중부 솔더 볼(80)들을 도 4 와 같이 형성할 수 있다. 상기 중부 솔더 볼(80)들은 도전 물질을 포함할 수 있다. 상기 중부 솔더 볼(80)들은 중부 보호막(70)의 상면으로부터 돌출하도록 형성될 수 있다. 상기 제 1 중부 접착제(10) 및 중부 보호막(70)으로부터 캐리어(5)를 도 5 와 같이 제거시킬 수 있다.

- [0073] 상기 제 1 중부 접착제(10)는 중부 보호막(70)으로부터 노출될 수 있다. 이를 통해서, 상기 제 1 중부 칩 적층 구조물(60), 중부 보호막(70) 및 중부 솔더 볼(80)들은 제 1 중부 패키지(83)를 도 5 와 같이 형성할 수 있다.

- [0074] 도 6 을 참조하면, 실시예에 따라서 하부 인쇄 회로 기판(90)을 준비할 수 있다. 상기 하부 인쇄 회로 기판(90)은 선택된 면에 외부 접속 패드(94)들 및 외부 접속 솔더 볼(98)들을 가질 수 있다. 상기 외부 접속 패드(94)들 및 외부 접속 솔더 볼(98)들은 도전 물질을 포함할 수 있다. 상기 외부 접속 솔더 볼(98)들은 외부 접속 패드(94)들 상에 배치될 수 있다. 상기 하부 인쇄 회로 기판(90) 상에 제 1 하부 접착제(100) 및 제 1 하부 반도체 칩(105)을 차례로 형성할 수 있다.

- [0075] 상기 제 1 하부 접착제(100) 및 제 1 하부 반도체 칩(105)은 하부 인쇄 회로 기판(90)의 선택된 면과 마주보는 면에 형성될 수 있다. 상기 제 1 하부 접착제(100)는 절연 물질을 포함할 수 있다. 상기 제 1 하부 반도체 칩(105)은 휘발성 또는 비휘발성 반도체 소자를 포함할 수 있다. 상기 제 1 하부 반도체 칩(105) 상에 제 2 하부 접착제(110) 및 제 2 하부 반도체 칩(115)을 차례로 형성할 수 있다. 상기 제 2 하부 접착제(110)는 제 1 하부 접착제(100)와 동일할 수 있다. 상기 제 2 하부 반도체 칩(115)은 제 1 하부 반도체 칩(105)과 동일하거나 다를 수 있다.

- [0076] 상기 제 2 하부 반도체 칩(115) 상에 제 3 하부 접착제(120) 및 제 3 하부 반도체 칩(125)을 차례로 형성할 수 있다. 상기 제 3 하부 접착제(120)는 제 1 하부 접착제(100)와 동일할 수 있다. 상기 제 3 하부 반도체 칩(125) 상에 적어도 하부 접착제 및 적어도 하나의 하부 반도체 칩을 차례로 형성할 수 있다. 상기 제 1 내지 3 하부 반도체 칩들(105, 115, 125)은 제 1 내지 3 중부 반도체 칩들(15, 25, 35)과 동일하거나 다를 수 있다. 상기 제 1 내지 3 하부 접착제들(100, 110, 120), 및 제 1 내지 3 하부 반도체 칩들(105, 115, 125)에 하부 비아 홀(130)들을 형성할 수 있다. 상기 하부 비아 홀(130)들은 제 1 내지 3 하부 접착제들(100, 110, 120), 및 제 1 내지 3 하부 반도체 칩들(105, 115, 125)에 하부 비아 홀(130)들을 형성할 수 있다.

- [0077] 상기 하부 비아 홑(130)들에 하부 관통 실리콘 비아(135)들을 형성할 수 있다. 상기 하부 관통 실리콘 비아 (135)들은 제 1 내지 3 하부 반도체 칩들(105, 115, 125)을 전기적으로 서로 접속시켜줄 수 있다. 상기 하부 관통 실리콘 비아(135)들은 도전 물질을 포함할 수 있다. 상기 제 3 하부 반도체 칩(125) 상에 하부 패드(140)들 및 하부 재 배선(145)들을 형성할 수 있다. 상기 하부 패드(140)들 및 하부 재 배선(145)들은 도전 물질을 포함할 수 있다. 상기 하부 패드(140)들은 제 3 하부 반도체 칩(125)과 전기적으로 접속할 수 있다.

- [0078] 상기 하부 재 배선(145)들은 하부 패드(140)들 및/ 또는 중부 관통 실리콘 비아(135)들과 전기적으로 접속할 수 있다. 이를 통해서, 상기 하부 관통 실리콘 비아(135)들 및 하부 패드(140)들은 하부 인쇄 회로 기판(90), 제 1 내지 3 하부 접착제들(100, 110, 120), 제 1 내지 3 하부 반도체 칩들(105, 115, 125), 및 하부 재 배선(145)들과 함께 제 1 하부 칩 적층 구조물(150)을 형성할 수 있다.

- [0079] 상기 제 1 하부 칩 적층 구조물(150)은 도 1 의 캐리어(5) 상에 형성시킨 후에 캐리어(5)로부터 하부 인쇄 회로 기판(90)으로 옮길 수도 있다. 상기 제 1 하부 칩 적층 구조물(150)을 덮도록 하부 인쇄 회로 기판(90) 상에 하부 보호막(160)을 형성할 수 있다. 상기 하부 보호막(160)은 중부 보호막(70)과 동일 물질을 포함할 수 있다. 상기 하부 보호막(160) 상에 표도 및 식각 공정들을 수행할 수도 있다.

- [0080] 상기 레이저 조사, 또는 포토 및 식각 공정들은 하부 보호막(160)에 하부 몰딩 홑(165)들을 형성시킬 수 있다. 상기 식각 공정은 하부 보호막(160) 상에 건식 식각 에천트 또는 습식 식각 에천트를 적용할 수 있다. 상기 하부 몰딩 홑(165)들은 하부 패드(140)들을 노출시키도록 형성될 수 있다. 상기 하부 몰딩 홑(165)들에 하부 솔더 볼(170)들을 형성할 수도 있다. 상기 하부 솔더 볼(170)들은 중부 솔더 볼(80)들과 동일 물질을 포함할 수 있다. 이 경우에, 상기 하부 솔더 볼(170)들은 도 4 의 중부 솔더 볼들을 사용하지 않는 경우에 형성될 수 있다. 상기 하부 솔더 볼(170)들은 도전 물질을 포함할 수 있다.

- [0081] 상기 하부 솔더 볼(170)들은 하부 보호막(160)의 상면으로부터 돌출하도록 형성될 수 있다. 이를 통해서, 상기 제 1 하부 칩 적층 구조물(150), 하부 보호막(160) 및 하부 솔더 볼(70)들은 제 1 하부 패키지(174)를 형성할 수 있다. 상기 하부 솔더 볼(170)들은 제 1 하부 패키지(174)로부터 제외될 수도 있다.

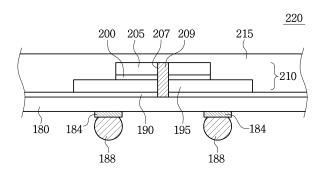

- [0082] 도 7 을 참조하면, 실시예들에 따라서, 상부 인쇄 회로 기판(180)을 준비할 수 있다. 상기 상부 인쇄 회로 기판(180)은 선택된 면에 상부 패드(184)들 및 상부 솔더 볼(188)들을 가질 수 있다. 상기 상부 패드(184)들 및 상부 솔더 볼(188)들은 도전 물질을 포함할 수 있다. 상기 상부 인쇄 회로 기판(180) 상에 제 1 상부 접착제(190) 및 제 1 상부 반도체 칩(195)을 차례로 형성할 수 있다. 상기 제 1 상부 접착제(190) 및 제 1 상부 반도체 칩(195)은 상부 인쇄 회로 기판(180)의 선택된 면와 마주보는 면 상에 형성될 수 있다.

- [0083] 상기 제 1 상부 접착제(190)는 절연 물질을 포함할 수 있다. 상기 제 1 상부 반도체 칩(195)은 휘발성 또는 비휘발성 반도체 소자일 수 있다. 상기 제 1 상부 반도체 칩(195) 상에 제 2 상부 접착제(200) 및 제 2 상부 반도체 칩(205)을 차례로 형성할 수 있다. 상기 제 2 상부 접착제(200)는 제 1 상부 접착제(190)와 동일할 수 있다. 상기 제 2 상부 반도체 칩(205)은 제 1 상부 반도체 칩(195)과 동일하거나 다를 수 있다. 상기 제 2 상부 반도체 칩(205) 상에 적어도 하나의 상부 접착제 및 적어도 하나의 상부 반도체 칩을 차례로 형성할 수 있다. 상기 제 1 및 2 상부 반도체 칩(195, 205)들은 제 1 내지 3 하부 반도체 칩들(105, 115, 125)과 다를 수 있다.

- [0084] 상기 제 1 및 2 상부 접착제들(190, 200), 및 제 1 및 2 상부 반도체 칩들(195, 205)에 상부 비아 홀(207)을 형성할 수 있다. 상기 상부 비아 홀(207)은 제 1 및 2 상부 접착제들(190, 200), 및 제 1 및 2 상부 반도체 칩들(195, 205)에 적어도 하나 형성될 수 있다. 상기 상부 비아 홀(207)에 상부 관통 실리콘 비아(209)를 형성할 수 있다. 상기 상부 관통 실리콘 비아(209)는 도전 물질을 포함할 수 있다.

- [0085] 상기 상부 관통 실리콘 비아(209)는 제 1 및 2 상부 접착제들(190, 200), 및 제 1 및 2 상부 반도체 칩들(195, 205)과 함께 상부 칩 적층 구조물(210)을 형성할 수 있다. 상기 상부 칩 적층 구조물(210)은 제 2 상부 반도체 칩(205) 상에 적어도 하나의 재 배선(도면에 미 도시)을 가질 수도 있다. 상기 상부 칩 적층 구조물(210)은 도 1 의 캐리어(5) 상에 형성시킨 후에 캐리어(5)로부터 상부 인쇄 희로 기판(180)으로 옮길 수도 있다. 상기 상부 칩 적층 구조물(210)을 덮도록 상부 인쇄 희로 기판(180) 상에 상부 보호막(215)을 형성할 수 있다. 상기 상부 보호막(215)은 도 4 의 중부 보호막(70)과 동일 물질을 포함할 수 있다. 이를 통해서, 상기 상부 보호막(215)은 상부 인쇄 희로 기판(180) 및 상부 칩 적층 구조물(210)과 함께 상부 패키지(220)를 형성할 수 있다.

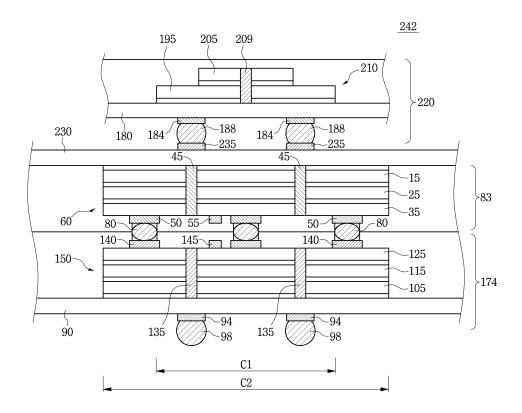

- [0086] 도 8 을 참조하면, 실시예들에 따라서, 도 6 의 제 1 하부 패키지(174) 상에 도 5 의 제 1 중부 패키지(83)를 적층시킬 수 있다. 이 경우에, 도 5 의 제 1 중부 패키지(83)의 하부측 및 상부측은 도 8 에서 변경될 수 있다. 상기 제 1 중부 패키지(83)의 중부 솔더 볼(80)들은 제 1 하부 패키지(174)의 하부 패드(140)들과 접촉할 수 있다. 상기 제 1 중부 패키지(83) 상에 중부 인쇄 회로 기판(230)을 형성할 수 있다. 상기 중부 인쇄 회로 기판(230)은 중부 관통 실리콘 비아(45)들과 전기적으로 접속할 수 있다. 상기 중부 인쇄 회로 기판(230)은 내부 접속 패드(235)들을 가질 수 있다. 상기 중부 인쇄 회로 기판(230) 상에 상부 패키지(220)가 적층될 수 있다.

- [0087] 상기 상부 패키지(220)의 상부 솔더 볼(188)들은 내부 접속 패드(235)들과 접촉할 수 있다. 이를 통해서, 상기 상부 패키지(220)는 제 1 하부 패키지(174) 및 제 1 중부 패키지(83)와 함께 제 1 반도체 패키지 구조물(242)을 형성할 수 있다. 이 경우에, 상기 제 1 하부 패키지(174)의 제 1 하부 칩 적층 구조물(150)은 제 1 중부 패키지(83)의 제 1 중부 칩 적층 구조물(60)과 함께 제 1 반도체 패키지 구조물(242) 내 하부 중심 영역(C2)에 형성될 수 있다. 상기 상부 패키지(220)의 상부 칩 적층 구조물(210)은 제 1 반도체 패키지 구조물(242) 내 상부 중심 영역(C1)에 형성될 수 있다.

- [0088] 상기 상부 패키지(220) 아래에 제 1 하부 패키지(174), 제 1 중부 패키지(83) 및 중부 인쇄 회로 기판(230)를 하나의 단위로 해서 적어도 한 번 반복적으로 적층시킬 수도 있다. 이 경우에, 상기 제 1 하부 패키지(174)의 외부 접속 솔더 볼(98)들은 중부 인쇄 회로 기판(230)의 내부 접속 솔더 볼(235)들에 접촉될 수 있다.

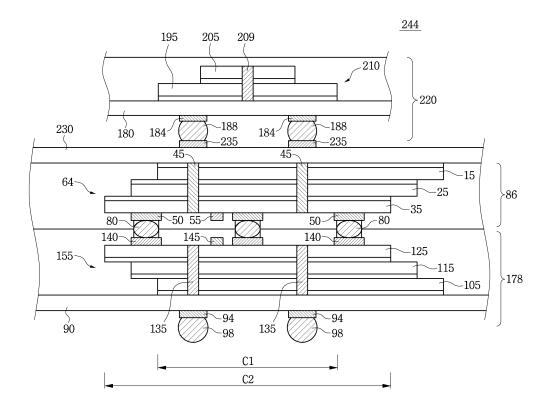

- [0089] 도 9 내지 13 은 도 1 의 절단선 I-I'를 따라 취해서 반도체 패키지 구조물의 형성방법을 보여주는 단면도들이다. 도 9 내지 13 은 도 3 내지 8 과 동일 부재에 대해서 동일한 참조 부호를 사용하기로 한다.

- [0090] 도 9 를 참조하면, 실시예들에 따라서 캐리어(5)를 준비할 수 있다. 상기 캐리어(5) 상에 제 1 내지 3 중부 접 착제들(10, 20, 30), 및 제 1 내지 3 중부 반도체 칩들(15, 25, 35)을 형성할 수 있다. 상기 제 1 내지 3 중부 접착제들(10, 20, 30)은 제 1 내지 3 중부 반도체 칩들(15, 25, 35) 아래에 형성될 수 있다. 상기 제 1 내지 3 중부 접착제들(10, 20, 30), 및 제 1 내지 3 중부 반도체 칩들(15, 25, 35)은 도 3 과 동일하게 형성될 수 있다.

- [0091] 이 경우에, 상기 제 2 중부 접착제(20) 및 제 2 반도체 칩(25)은 제 1 중부 접착제 및 반도체 칩(10, 15)으로부터 도 1 의 제 1 주변 영역(P1)으로 소정 길이(L) 만큼 연장할 수 있다. 상기 제 3 중부 접착제(30) 및 제 3 반도체 칩(35)은 제 2 중부 접착제 및 반도체 칩(20, 25)으로부터 도 1 의 제 1 주변 영역(P1)으로 소정 길이(L) 만큼 연장할 수 있다. 상기 제 1 중부 접착제 및 반도체 칩(10, 15)은 제 2 중부 접착제 및 반도체 칩(20, 25)과 단차(Step Differnce; SD)를 형성할 수 있다. 상기 제 2 중부 접착제 및 반도체 칩(20, 25)은 제 3 중부 접착제 및 반도체 칩(30, 35)과 단차(SD)를 형성할 수 있다.

- [0092] 상기 제 1 내지 3 중부 접착제들(10, 20, 30)은 양 측면들을 통해서 서로를 노출시킬 수 있다. 계속해서, 상기 제 1 내지 3 중부 접착제(10, 20, 30)들, 및 제 1 내지 3 중부 반도체 칩들(15, 25, 35)에 중부 비아 홀(40)들 및 중부 관통 실리콘 비아(45)들을 형성할 수 있다. 상기 제 3 중부 반도체 칩(35) 상에 중부 패드(50)들 및 중부 재 배선(55)들을 형성할 수 있다. 상기 중부 비아 홀(40)들, 중부 관통 실리콘 비아(45)들, 중부 패드(50)들 및 중부 재 배선(55)들은 도 3 과 동일하게 형성될 수 있다.

- [0093] 이를 통해서, 상기 중부 관통 실리콘 비아(45)들 및 중부 패드(50)들은 제 1 내지 3 중부 접착제들(10, 20, 30), 제 1 내지 3 중부 반도체 칩들(15, 25, 35), 및 중부 재 배선(55)들과 함께 제 2 중부 칩 적층 구조물 (64)을 형성할 수 있다.

- [0094] 도 10 및 11 을 참조하면, 실시예들에 따라서, 상기 제 2 중부 칩 적층 구조물(64)을 덮도록 캐리어(5) 상에 중부 보호막(70)을 도 10 과 같이 형성할 수 있다. 상기 중부 보호막(70)에 중부 몰딩 홀(75)들 및 중부 솔더 볼(80)들을 도 10 과 같이 형성할 수 있다. 상기 중부 보호막(70), 중부 몰딩 홀(75)들 및 중부 솔더 볼(80)들은 도 4 와 동일하게 형성될 수 있다. 계속해서, 상기 제 1 중부 접착제(10) 및 중부 보호막(70)으로부터 캐리어(5)를 도 11 과 같이 제거시킬 수 있다.

- [0095] 상기 제 1 중부 접착제(10)는 중부 보호막(70)으로부터 노출될 수 있다. 이를 통해서, 상기 제 2 중부 칩 적층 구조물(64), 중부 보호막(70) 및 중부 솔더 볼(80)들은 제 2 중부 패키지(86)를 도 11 과 같이 형성할 수 있다.

- [0096] 도 12 를 참조하면, 실시예에 따라서 하부 인쇄 회로 기판(90)을 준비할 수 있다. 상기 하부 인쇄 회로 기판 (90)은 선택된 면에 외부 접속 패드(94)들 및 외부 접속 솔더 볼(98)들을 가질 수 있다. 상기 하부 인쇄 회로 기판(90) 상에 제 1 내지 3 하부 접착제들(100, 110, 120), 및 제 1 내지 3 하부 반도체 칩들(105, 115, 125)을 차례로 형성할 수 있다. 상기 제 1 내지 3 하부 접착제들(100, 110, 120), 및 제 1 내지 3 하부 반도체 칩들 (105, 115, 125)은 하부 인쇄 회로 기판(90)의 선택된 면과 마주보는 면에 형성될 수 있다.

- [0097] 상기 제 1 내지 3 하부 접착제들(100, 110, 120)은 제 1 내지 3 하부 반도체 칩들(105, 115, 125) 아래에 형성될 수 있다. 상기 제 1 내지 3 하부 접착제들(100, 110, 120), 및 제 1 내지 3 하부 반도체 칩들(105, 115, 125)은 도 6 과 동일하게 형성될 수 있다. 이 경우에, 상기 제 2 하부 접착제(110) 및 제 2 하부 반도체 칩(115)은 제 1 하부 접착제 및 반도체 칩(100, 105)으로부터 도 1 의 제 1 주변 영역(P1)으로 소정 길이(L) 만큼 연장할 수 있다. 상기 제 3 하부 접착제(120) 및 제 2 하부 반도체 칩(125)은 제 2 하부 접착제 및 반도체 칩(110, 115)으로부터 도 1 의 제 1 주변 영역(P1)으로 소정 길이(L) 만큼 연장할 수 있다.

- [0098] 상기 제 1 하부 접착제 및 반도체 칩(100, 105)은 제 2 하부 접착제 및 반도체 칩(110, 115)과 단차(SD)를 형성할 수 있다. 상기 제 2 하부 접착제 및 반도체 칩(110, 115)은 제 3 하부 접착제 및 반도체 칩(120, 125)과 단차(SD)를 형성할 수 있다. 상기 제 1 내지 3 하부 접착제들(100, 110, 120)은 양 측면들을 통해서 서로를 노출시킬 수 있다. 상기 제 1 내지 3 하부 접착제(100, 110, 120)들, 및 제 1 내지 3 중부 반도체 칩들(105, 115, 125)에 하부 비아 홀(130)들 및 하부 관통 실리콘 비아(135)들을 형성할 수 있다.

- [0099] 상기 제 3 하부 반도체 칩(125) 상에 하부 패드(140)들 및 하부 재 배선(145)들을 형성할 수 있다. 상기 하부 비아 홀(130)들, 하부 관통 실리콘 비아(135)들, 하부 패드(140)들 및 하부 재 배선(145)들은 도 6 과 동일하게 형성될 수 있다. 상기 하부 관통 실리콘 비아(135)들 및 하부 패드(140)들은 하부 인쇄 회로 기판(90), 제 1 내지 3 하부 접착제들(100, 110, 120), 제 1 내지 3 하부 반도체 칩들(105, 115, 125), 및 하부 재 배선(145)들 과 함께 제 2 하부 칩 적층 구조물(155)을 형성할 수 있다. 상기 제 2 하부 칩 적층 구조물(155)은 도 1 의 캐리어(5) 상에 형성시킨 후에 캐리어(5)로부터 하부 인쇄 회로 기판(90)으로 옮길 수 있다.

- [0100] 상기 제 2 하부 칩 적층 구조물(155)을 덮도록 하부 인쇄 회로 기판(90) 상에 하부 보호막(160)을 형성할 수 있다. 상기 하부 보호막(160)에 하부 몰딩 홀(165)들 및 하부 솔더 볼(170)들을 형성할 수 있다. 상기 하부 보호막(160), 하부 몰딩 홀(165)들 및 하부 솔더 볼(170)들은 도 6 과 동일하게 형성될 수 있다. 이를 통해서, 상기

제 2 하부 칩 적층 구조물(155), 하부 보호막(160) 및 하부 솔더 볼(170)들은 제 2 하부 패키지(178)를 형성할 수 있다. 상기 하부 솔더 볼(170)들은 제 2 하부 패키지(178)로부터 제외될 수 있다.

- [0101] 도 13 을 참조하면, 실시예들에 따라서, 도 12 의 제 2 하부 패키지(178) 상에 도 11 의 제 2 중부 패키지(86) 를 적층시킬 수 있다. 이 경우에, 도 11 의 제 2 중부 패키지(86)의 하부측 및 상부측은 도 13 에서 변경될 수 있다. 상기 제 2 중부 패키지(86)의 중부 솔더 볼(80)들은 제 2 하부 패키지(178)의 하부 패드(140)들과 접촉할 수 있다. 상기 제 2 중부 패키지(86) 상에 중부 인쇄 회로 기판(230)을 형성할 수 있다. 상기 중부 인쇄 회로 기판(230)은 중부 관통 실리콘 비아(45)들과 전기적으로 접속할 수 있다.

- [0102] 상기 중부 인쇄 회로 기판(230)은 내부 접속 패드(235)들을 가질 수 있다. 상기 중부 인쇄 회로 기판(230) 상에 도 7 의 상부 패키지(220)가 적충될 수 있다. 상기 상부 패키지(220)의 상부 솔더 볼(188)들은 내부 접속 패드(235)들과 접촉할 수 있다. 이를 통해서, 상기 상부 패키지(220)는 제 2 하부 패키지(178) 및 제 2 중부 패키지(86)와 함께 제 2 반도체 패키지 구조물(244)을 형성할 수 있다.

- [0103] 이 경우에, 상기 제 2 하부 패키지(178)의 제 2 하부 칩 적층 구조물(155)은 제 3 하부 반도체 칩(125)을 기준으로 제 2 반도체 패키지 구조물(244) 내 하부 중심 영역(C2) 및 제 2 주변 영역(P2)에 형성될 수 있다. 상기 제 2 중부 패키지(86)의 제 2 중부 칩 적층 구조물(64)은 제 3 중부 반도체 칩(35)을 기준으로 제 2 반도체 패키지 구조물(244) 내 하부 중심 영역(C2) 및 제 2 주변 영역(P2)에 형성될 수 있다. 상기 상부 패키지(220)의 상부 칩 적층 구조물(210)은 제 2 반도체 패키지 구조물(244) 내 상부 중심 영역(C1)에 형성될 수 있다.

- [0104] 상기 상부 패키지(220) 아래에 제 2 하부 패키지(178), 제 2 중부 패키지(86) 및 중부 인쇄 회로 기판(230)를 하나의 단위로 해서 적어도 한 번 반복적으로 적충시킬 수도 있다. 이 경우에, 상기 제 2 하부 패키지(178)의 외부 접속 솔더 볼(98)들은 중부 인쇄 회로 기판(230)의 내부 접속 솔더 볼(235)들에 접촉될 수 있다.

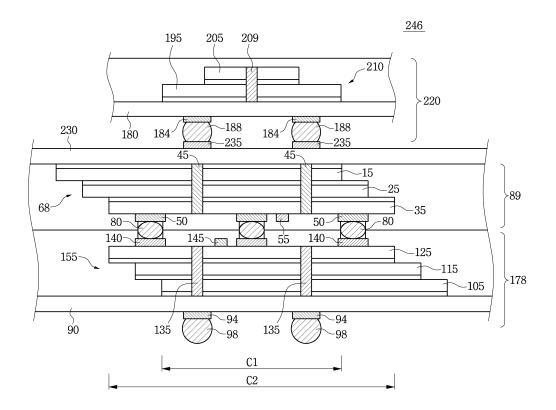

- [0105] 도 14 및 15 는 도 1 의 절단선 I-I'를 따라 취해서 반도체 패키지 구조물들의 형성방법을 보여주는 단면도 들이다. 도 14 및 15 는 도 3 내지 8 과 동일 부재에 대해서 동일한 참조 부호를 사용하기로 한다.

- [0106] 도 14 를 참조하면, 실시예들에 따라서, 도 12 의 제 2 하부 패키지(178) 상에 도 13 의 제 2 중부 패키지(86) 를 적층시킬 수 있다. 이 경우에, 도 13 의 제 2 중부 패키지(86)의 좌측 및 우측은 도 14 에서 변경될 수 있다. 이를 통해서, 도 13 의 제 2 중부 패키지(86)는 도 14 의 제 3 중부 패키지(89)로 대체될 수 있다. 상기 제 3 중부 패키지(89)는 제 3 중부 칩 적층 구조물(68)을 가질 수 있다. 상기 제 3 중부 패키지(89)는 제 2 중부 패키지(86)와 동일한 구성 요소들을 가질 수 있다.

- [0107] 상기 제 3 중부 패키지(89)의 중부 솔더 볼(80)들은 제 2 하부 패키지(178)의 하부 패드(140)들과 접촉할 수 있다. 상기 제 3 중부 패키지(89) 상에 중부 인쇄 회로 기판(230)을 형성할 수 있다. 상기 중부 인쇄 회로 기판(230)은 내부 접속 패드(235)들을 가질 수 있다. 상기 중부 인쇄 회로 기판(230) 상에 상부 패키지(220)가 적충될 수 있다. 상기 상부 패키지(220)의 상부 솔더 볼(188)들은 중부 인쇄 회로 기판(230)의 내부 접속 패드(235)들과 접촉할 수 있다.

- [0108] 상기 상부 패키지(220)는 제 2 하부 패키지(178) 및 제 3 중부 패키지(89)와 함께 제 3 반도체 패키지 구조물 (246)을 형성할 수 있다. 이 경우에, 상기 제 2 하부 패키지(178)의 제 2 하부 칩 적층 구조물(155)은 제 3 하부 반도체 칩(125)을 기준으로 제 3 반도체 패키지 구조물(246) 내 하부 중심 영역(C2) 및 제 2 주변 영역(P2)에 형성될 수 있다. 상기 제 3 중부 패키지(89)의 제 3 중부 칩 적층 구조물(68)은 제 3 중부 반도체 칩(35)을 기준으로 제 3 반도체 패키지 구조물(246) 내 하부 중심 영역(C2) 및 제 1 주변 영역(P1)에 형성될 수 있다.

- [0109] 상기 상부 패키지(220)의 상부 칩 적층 구조물(210)은 제 3 반도체 패키지 구조물(246) 내 상부 중심 영역(C1)에 형성될 수 있다. 상기 상부 패키지(220) 아래에 제 2 하부 패키지(178), 제 3 중부 패키지(89) 및 중부 인쇄회로 기판(230)를 하나의 단위로 해서 적어도 한 번 반복적으로 적층시킬 수도 있다. 이 경우에, 상기 제 2 하부 패키지(178)의 외부 접속 솔더 볼(98)들은 중부 인쇄 회로 기판(230)의 내부 접속 솔더 볼(235)들에 접촉될수 있다.

- [0110] 도 15 를 참조하면, 실시예들에 따라서, 도 12 의 제 2 하부 패키지(178) 상에 도 5 의 제 1 중부 패키지(83)를 적충시킬 수 있다. 상기 제 1 중부 패키지(83)의 중부 솔더 볼(80)들은 제 2 하부 패키지(178)의 하부 패드 (140)들과 접촉할 수 있다. 상기 제 1 중부 패키지(83) 상에 중부 인쇄 회로 기판(230)을 형성할 수 있다. 상기 중부 인쇄 회로 기판(230)은 내부 접속 패드(235)들을 가질 수 있다.

- [0111] 상기 중부 인쇄 회로 기판(230) 상에 상부 패키지(220)가 적층될 수 있다. 상기 상부 패키지(220)의 상부 솔더

볼(188)들은 중부 인쇄 회로 기판(230)의 내부 접속 패드(235)들과 접촉할 수 있다. 상기 상부 패키지(220)는 제 2 하부 패키지(178) 및 제 1 중부 패키지(83)와 함께 제 4 반도체 패키지 구조물(248)을 형성할 수 있다. 이 경우에, 상기 제 2 하부 패키지(178)의 제 2 하부 칩 적층 구조물(155)은 제 3 하부 반도체 칩(125)을 기준으로 제 4 반도체 패키지 구조물(248) 내 하부 중심 영역(C2) 및 제 2 주변 영역(P2)에 형성될 수 있다.

- [0112] 상기 제 1 중부 패키지(83)의 제 1 중부 칩 적층 구조물(60)은 제 3 중부 반도체 칩(35)을 기준으로 제 4 반도 체 패키지 구조물(248) 내 하부 중심 영역(C2)에 형성될 수 있다. 상기 상부 패키지(220)의 상부 칩 적층 구조물(210)은 제 4 반도체 패키지 구조물(246) 내 상부 중심 영역(C1)에 형성될 수 있다. 상기 상부 패키지(220) 아래에 제 2 하부 패키지(178), 제 1 중부 패키지(83) 및 중부 인쇄 회로 기판(230)를 하나의 단위로 해서 적어도 한 번 반복적으로 적층시킬 수도 있다.

- [0113] 이 경우에, 상기 제 2 하부 패키지(178)의 외부 접속 솔더 볼(98)들은 중부 인쇄 회로 기판(230)의 내부 접속 솔더 볼(235)들에 접촉될 수 있다. 더불어서, 도 13, 14 및 15 의 제 2 내지 4 반도체 패키지 구조물들(244, 246, 248)의 좌측 및 우측은 180°로 회전해서 변경될 수도 있다. 그리고, 도 6 의 제 1 하부 패키지(174) 상에 도 13 의 제 2 중부 패키지(86) 및 도 7 의 상부 패키지(220), 또는 도 14 의 제 3 중부 패키지(89) 및 도 7 의 상부 패키지(220)가 적충될 수도 있다.

- [0114] 상기 제 1 하부 패키지(174), 제 2 중부 패키지(86) 및 상부 패키지(220)의 좌측 및 우측은 180°로 회전해서 변경될 수 있다. 상기 제 1 하부 패키지(174), 제 3 중부 패키지(89) 및 상부 패키지(220)의 좌측 및 우측은 180°로 회전해서 변경될 수 있다.

#### 도면의 간단한 설명

- [0115] 도 1 은 실시예들에 따르는 반도체 패키지 구조물들을 보여주는 평면도이다.

- [0116] 도 2 는 도 1 의 절단선 I-I'를 따라 취해서 반도체 패키지 구조물을 보여주는 단면도이다.

- [0117] 도 3 내지 8 은 도 1 의 절단선 I-I'를 따라 취해서 반도체 패키지 구조물의 형성방법을 보여주는 단면도들이다.

- [0118] 도 9 내지 13 은 도 1 의 절단선 I-I'를 따라 취해서 반도체 패키지 구조물의 형성방법을 보여주는 단면도들이다.

- [0119] 도 14 및 15 는 도 1 의 절단선 I-I'를 따라 취해서 반도체 패키지 구조물들의 형성방법을 보여주는 단면도 들이다.

## 도면1

### 242,244,246,248

## 도면2

242 45-45~ P1 -15 -20 70--25 -30 -35 ≻83 60 -50 55~ 140-140-150-160 P2 >174 94 110 115 90 100 105 135 135 120 125 C2

## 도면4

# 도면5

## 도면8

## 도면11