## (19) 대한민국특허청(KR)

### (12) 등록특허공보(B1)

(51) Int. Cl.

**HO3L 7/089** (2006.01)

(21) 출원번호 10-2002-7016345

(22) 출원일자2002년11월29일심사청구일자2006년05월08일

번역문제출일자 **2002년11월29일** (65) 공개번호 **10-2003-0017528**

(43) 공개일자 2003년03월03일

(86) 국제출원번호 PCT/EP2001/005783

국제출원일자 2001년05월21일 (87) 국제공개번호 WO 2001/93418 국제공개일자 2001년12월06일

(30) 우선권주장

09/580,632 2000년05월30일 미국(US)

(56) 선행기술조사문헌

US06049233 A

US05631582 A

US04818950 A

US05103191 A

전체 청구항 수 : 총 22 항

(45) 공고일자 2008년02월26일

(11) 등록번호 10-0805997

(24) 등록일자 2008년02월14일

(73) 특허권자

#### 텔레호낙티에볼라게트 엘엠 에릭슨(피유비엘)

스웨덴 스톡홀롬 83 에스이-164

(72) 발명자

매티슨,스벤

스웨덴에스-23736브자레드외스탄배그3

해그버그,한스

스웨덴에스-21133말뫼그린보드가탄16

닐슨.매그너스

스웨덴에스-22472룬트플라이겔배겐241

(74) 대리인

장수길, 주성민

심사관 : 김자영

#### (54) 선형 데드-밴드-프리 디지털 위상 검출

#### (57) 요 약

PLL은 위상 검출기가 기준 클럭 신호와 피드백 신호 간의 위상차의 함수로서 위상 검출기 출력 신호를 발생하도록 배치된 위상 검출기, 루프 필터, 전압 제어 발진기, 및 주파수 분할기를 포함한다. 루프 필터는 상기 위상검출기 출력 신호로부터 주파수 제어 신호를 발생한다. 전압 제어 발진기는 주파수 제어 신호에 의해 제어된 주파수를 갖는 PLL 출력 신호를 발생한다. 또한, 주파수 분할기는 PLL 출력 신호로부터 피드백 신호를 발생한다. PLL은 또한, 기준 클럭 신호와 피드백 신호 간의 포지티브 및 네거티브 위상차 둘 다의 소정 범위에 대하여, 출력 신호가 상기 기준 클럭 신호와 상기 피드백 신호 간의 실질적으로 선형인 위상차 함수로서 발생되도록, 상기위상 검출기의 동작점을 유지하는 하나 이상의 회로 소자를 포함한다.

#### **대표도** - 도3

#### (81) 지정국

국내특허 : 아르메니아, 오스트리아, 오스트레일리 아, 아제르바이잔, 보스니아 헤르체고비나, 바베이 도스, 불가리아, 브라질, 벨라루스, 캐나다, 스위 스, 중국, 쿠바, 체코, 독일, 덴마크, 에스토니아, 대한민국, 카자흐스탄, 세인트루시아, 스리랑카, 리베이라, 레소토, 리투아니아, 룩셈부르크, 라트 비아, 몰도바, 마다가스카르, 마케도니아공화국, 몽고, 말라위, 멕시코, 노르웨이, 뉴질랜드, 슬로 베니아, 슬로바키아, 타지키스탄, 투르크맨, 터어 키, 트리니아드토바고, 우크라이나, 우간다, 우즈 베키스탄, 베트남, 폴란드, 포르투칼, 루마니아, 러시아, 수단, 스웨덴, 싱가포르, 그라나다, 가나, 감비아, 크로아티아, 인도, 인도네시아, 시에라리 온, 세르비아 앤 몬테네그로, 짐바브웨, 코스타리 카, 모로코, 탄자니아, 남아프리카, 아랍에미리트, 도미니카, 안티구와바부다, 알제리, 알바니아, 벨 리즈. 모잒비크

AP ARIPO특허: 케냐, 레소토, 말라위, 수단, 스와 질랜드, 우간다, 가나, 감비아, 짐바브웨, 시에라 리온, 탄자니아, 모잠비크

EA 유라시아특허 : 아르메니아, 아제르바이잔, 벨라루스, 키르키즈스탐, 카자흐스탄, 몰도바, 러시아, 타지키스탄, 투르크맨

EP 유럽특허: 오스트리아, 벨기에, 스위스, 독일, 덴마크, 스페인, 프랑스, 영국, 그리스, 아일랜드, 이탈리아, 룩셈부르크, 모나코, 네덜란드, 포르투 칼, 스웨덴, 핀란드, 사이프러스

OA OAPI특허 : 부르키나파소, 베닌, 중앙아프리카, 콩고, 코트디브와르, 카메룬, 가봉, 기니, 말리, 모리타니, 니제르, 세네갈, 차드, 토고, 기니 비사 우

#### 특허청구의 범위

#### 청구항 1

위상 검출기에 있어서,

제1 신호를 수신하는 제1 입력;

제2 신호를 수신하는 제2 입력; 및

상기 제1 신호와 상기 제2 신호 간의 위상차의 함수인 출력 신호를 발생하는 비교 회로

를 포함하며,

상기 제1 신호와 상기 제2 신호 간의 포지티브 및 네거티브 위상들 둘 다의 소정의 범위에 대하여 상기 제1 신호와 상기 제2 신호 간의 선형의 위상차 함수로서 출력 신호가 생성되도록, 상기 제1 신호와 상기 제2 신호 간의 비제로(nonzero) 출력 신호 및 대응하는 비제로 위상차를 갖는 위치로 상기 위상 검출기의 동작점을 시프트하는 동작점 회로를 더 포함하는 위상 검출기.

#### 청구항 2

제1항에 있어서,

상기 위상 검출기가 위상 동기 루프에 사용됨으로써 상기 위상 동기 루프의 출력 주파수는 상기 위상 검출기의 상기 출력 신호의 함수이며,

누설된(leak) 출력 신호에 의해 상기 위상 동기 루프의 상기 출력 주파수가 영향받지 않도록 상기 동작점 회로 가 상기 출력 신호의 소정의 부분을 누설시키는 위상 검출기.

#### 청구항 3

제1항에 있어서,

상기 출력 신호는 출력 전류이고.

상기 비교 회로는.

상기 제1 신호의 엣지에 응답하여 제1 차지 펌프 제어 신호를 어써트(assert)하는 제1 회로;

상기 제2 신호의 엣지에 응답하여 제2 차지 펌프 제어 신호를 어써트하는 제2 회로;

상기 제1 차지 펌프 제어 신호의 어써트에 응답하여 상기 출력 전류에 포지티브 전류를 부여하는 제1 차지 펌프;

상기 제2 차지 펌프 제어 신호의 어써트에 응답하여 상기 출력 전류에 네거티브 전류를 부여하는 제2 차지 펌프; 및

상기 제1 및 제2 차지 펌프 제어 신호들 둘 다가 어써트되는 것에 응답하여 상기 제1 및 제2 회로들의 각각에 리셋 신호를 제공하는 리셋 로직

을 포함하고,

상기 동작점 회로는,

상기 리셋 로직에 공급되는 상기 제1 및 제2 차지 펌프 제어 신호들 중 적어도 하나를 지연시키는 지연 회로를 포함하고, 상기 제1 차지 펌프 제어 신호가 상기 리셋 로직에 공급되는데 소요되는 시간은 상기 제2 차지 펌프 제어 신호가 상기 리셋 로직에 공급되는데 소요되는 시간과 동일하지 않은 위상 검출기.

#### 청구항 4

제3항에 있어서,

상기 지연 회로는 상기 리셋 로직에 공급되는 상기 제1 및 제2 차지 펌프 제어 신호들 중 하나만을 지연시키는 위상 검출기.

#### 청구항 5

제3항에 있어서,

상기 지연 회로는 상기 리셋 로직에 공급되는 상기 제1 및 제2 차지 펌프 제어 신호 둘 다를 지연시키는 위상 검출기.

#### 청구항 6

제1항에 있어서,

상기 출력 신호는 출력 전압이고,

상기 비교 회로는,

상기 제1 신호의 엣지에 응답하여 제1 전압 발생기 제어 신호를 어써트하는 제1 회로;

상기 제2 신호의 엣지에 응답하여 제2 전압 발생기 제어 신호를 어써트하는 제2 회로;

상기 제1 전압 발생기 제어 신호의 어써트에 응답하여 상기 출력 전압에 포지티브 전압을 부여하는 제1 전압 발생기;

상기 제2 전압 발생기 제어 신호의 어써트에 응답하여 상기 출력 전압에 네거티브 전압을 부여하는 제2 전압 발생기; 및

상기 제1 및 제2 전압 발생기 제어 신호들 둘 다가 어써트되는 것에 응답하여 상기 제1 및 제2 회로들의 각각에 리셋 신호를 제공하는 리셋 로직

을 포함하고,

상기 동작점 회로는,

상기 리셋 로직에 공급되는 상기 제1 및 제2 전압 발생기 제어 신호들 중 적어도 하나를 지연시키는 지연 회로를 포함하고, 상기 제1 전압 발생기 제어 신호가 상기 리셋 로직에 공급되는데 소요되는 시간은 상기 제2 전압 발생기 제어 신호가 상기 리셋 로직에 공급되는데 소요되는 시간과 동일하지 않은 위상 검출기.

#### 청구항 7

제6항에 있어서,

상기 지연 회로는 상기 리셋 로직에 공급되는 상기 제1 및 제2 전압 발생기 제어 신호 중 하나만을 지연시키는 위상 검출기.

#### 청구항 8

제6항에 있어서,

상기 지연 회로는 상기 리셋 로직에 공급되는 상기 제1 및 제2 전압 발생기 제어 신호 둘 다를 지연시키는 위상 검출기.

#### 청구항 9

PLL(phase-locked loop)에 있어서,

기준 클럭 신호를 수신하는 제1 입력;

피드백 신호를 수신하는 제2 입력; 및

상기 기준 클럭 신호와 상기 피드백 신호 간의 위상차의 함수인 위상 검출기 출력 신호를 발생하는 비교 회로를 포함하는 위상 검출기와,

상기 위상 검출기 출력 신호로부터 주파수 제어 신호를 발생하는 루프 필터와,

상기 주파수 제어 신호에 의해 제어되는 주파수를 갖는 PLL 출력 신호를 발생하는 회로와,

상기 PLL 출력 신호로부터 상기 피드백 신호를 발생하는 주파수 분할기와,

누설된 출력 신호에 의해 상기 PLL의 출력 주파수가 영향받는 것을 방지하기 위해, 상기 위상 검출기 출력 신호 와 상기 주파수 제어 신호 중 적어도 하나의 소정 부분을 누설시키는 하나 이상의 회로 소자

를 포함하는 PLL.

#### 청구항 10

제9항에 있어서,

상기 위상 검출기 출력 신호와 상기 주파수 제어 신호 중 적어도 하나의 소정 부분을 누설시키는 상기 하나 이상의 회로 소자는, 상기 위상 검출기 출력 신호의 소정 부분을 누설시키는 상기 루프 필터내의 하나 이상의 회로 소자를 포함하는 PLL.

#### 청구항 11

제9항에 있어서.

상기 주파수 제어 신호에 의해 제어되는 주파수를 갖는 상기 PLL 출력 신호를 발생하는 회로는 전압 제어 발진 기인 PLL.

#### 청구항 12

제9항에 있어서,

상기 주파수 제어 신호에 의해 제어되는 주파수를 갖는 상기 PLL 출력 신호를 발생하는 회로는 전류 제어 발진 기인 PLL.

#### 청구항 13

제1 신호와 제2 신호 간의 위상차를 검출하는 방법에 있어서,

상기 제1 신호와 상기 제2 신호 간의 위상차의 함수인 출력 신호를 발생하는 단계; 및

상기 제1 신호와 제2 신호 간의 포지티브 및 네거티브 위상차 둘 다의 소정 범위에 대하여, 상기 출력 신호가 상기 제1 신호와 제2 신호 간의 선형인 위상차의 함수로서 발생되도록 상기 위상 검출기의 동작점을 유지하는 단계

를 포함하는 위상차 검출 방법.

#### 청구항 14

제13항에 있어서,

상기 위상 검출기의 출력 신호의 함수인 주파수를 갖는 PLL 출력 신호를 발생하는 단계; 및

누설된 출력 신호에 의해 상기 PLL 출력 신호의 출력 주파수가 영향받는 것을 방지하도록 상기 출력 신호의 소 정 부분을 누설시키는 단계

를 더 포함하는 위상차 검출 방법.

#### 청구항 15

제13항에 있어서,

상기 출력 신호는 출력 전류이고,

상기 제1 신호와 상기 제2 신호 간의 위상차의 함수인 출력 신호를 발생하는 단계는,

상기 제1 신호의 엣지에 응답하여 제1 차지 펌프 제어 신호를 어써트하는 단계;

상기 제2 신호의 엣지에 응답하여 제2 차지 펌프 제어 신호를 어써트하는 단계;

상기 제1 차지 펌프 제어 신호의 어써트에 응답하여, 상기 출력 전류에 포지티브 전류를 제공하는 단계;

상기 제2 차지 펌프 제어 신호의 어써트에 응답하여, 상기 출력 전류에 네거티브 전류를 제공하는 단계; 및 어써트되는 상기 제1 및 제2 차지 펌프 제어 신호 둘 다에 응답하여, 상기 제1 및 제2 차지 펌프 제어 신호를 비활성화하는 단계

를 포함하고,

상기 위상 검출기의 동작점을 유지하는 단계는,

상기 비활성화 단계에 영향을 미치는 상기 제1 및 제2 차지 펌프 제어 신호 중 적어도 하나를 지연시키는 단계를 포함하고, 상기 제1 차지 펌프 제어 신호가 상기 비활성화 단계에 영향을 미치는 데 걸리는 시간은 상기 제2 차지 펌프 제어 신호가 상기 비활성화 단계에 영향을 미치는 데 걸리는 시간과 동일하지 않은 위상차 검출방법.

#### 청구항 16

제15항에 있어서,

상기 지연 단계는 상기 비활성화 단계에 영향을 미치는 상기 제1 및 제2 차지 펌프 제어 신호들 중 하나만을 지연시키는 단계를 포함하는 위상차 검출 방법.

#### 청구항 17

제15항에 있어서,

상기 지연 단계는 상기 비활성화 단계에 영향을 미치는 상기 제1 및 제2 차지 펌프 제어 신호 둘 다를 지연시키는 단계를 포함하는 위상차 검출 방법.

#### 청구항 18

제13항에 있어서,

상기 출력 신호는 출력 전압이고,

상기 제1 신호와 상기 제2 신호 간의 위상차의 함수인 출력 신호를 발생하는 단계는,

상기 제1 신호의 엣지에 응답하여 제1 전압 발생 제어 신호를 어써트하는 단계;

상기 제2 신호의 엣지에 응답하여 제2 전압 발생 제어 신호를 어써트하는 단계;

상기 제1 전압 발생 제어 신호의 어써트에 응답하여, 상기 출력 전압에 포지티브 전압을 제공하는 단계;

상기 제2 전압 발생 제어 신호의 어써트에 응답하여, 상기 출력 전압에 네거티브 전압을 제공하는 단계; 및 어써트되는 상기 제1 및 제2 전압 발생 제어 신호 둘 다에 응답하여, 상기 제1 및 제2 전압 발생 제어 신호를 비활성화하는 단계

를 포함하고,

상기 위상 검출기의 동작점을 유지하는 단계는,

상기 비활성화 단계에 영향을 미치는 상기 제1 및 제2 전압 발생 제어 신호 중 적어도 하나를 지연시키는 단계를 포함하고, 상기 제1 전압 발생 제어 신호가 상기 비활성화 단계에 영향을 미치는 데 걸리는 시간은 상기 제2 전압 발생 제어 신호가 상기 비활성화 단계에 영향을 미치는 데 걸리는 시간과 동일하지 않은 위상차 검출방법.

#### 청구항 19

제18항에 있어서,

상기 지연 단계는 상기 비활성화 단계에 영향을 미치는 상기 제1 및 제2 전압 발생 제어 신호들 중 하나만을 지 연시키는 단계를 포함하는 위상차 검출 방법.

#### 청구항 20

제18항에 있어서,

상기 지연 단계는 상기 비활성화 단계에 영향을 미치는 상기 제1 및 제2 전압 발생 제어 신호 둘 다를 지연시키는 단계를 포함하는 위상차 검출 방법.

#### 청구항 21

PLL 출력 신호를 발생하는 방법에 있어서,

기준 클럭 신호와 피드백 신호 간의 위상차의 함수인 위상 검출기 출력 신호를 발생하는 단계;

상기 위상 검출기 출력 신호로부터 주파수 제어 신호를 발생하는 단계;

상기 주파수 제어 신호에 의해 제어되는 주파수를 갖는 PLL 출력 신호를 발생하는 단계;

주파수 분할기를 사용하여 상기 PLL 출력 신호로부터 상기 피드백 신호를 발생하는 단계; 및

누설된 출력 신호에 의해 상기 PLL의 출력 주파수가 영향받는 것을 방지하도록 상기 위상 검출기 출력 신호와 상기 주파수 제어 신호 중 적어도 하나의 소정 부분을 누설시키는 단계

를 포함하는 PLL 출력 신호 발생 방법.

#### 청구항 22

제21항에 있어서,

상기 위상 검출기 출력 신호와 상기 주파수 제어 신호 중 적어도 하나의 소정 부분을 누설시키는 단계는, 루프 필터에서 상기 위상 검출기 출력 신호의 소정 부분을 누설시키는 단계를 포함하는 PLL 출력 신호 발생 방법.

#### 명 세 서

#### 배경기술

- 본 발명은 주파수 합성기 및 직접 변조에 관한 것으로, 특히 위상 동기 루프에 관한 것이며, 더욱 특정적으로는 위상 동기 루프에서 사용하기 위한 디지털 위상 검출기에 관한 것이다.

- 위상 동기 루프(PLL)는 공지되어 있으며, 무선 회로에 한정된 것은 아니지만 무선 회로를 포함하여 많은 형태의 회로에서 발진 신호를 생성하는데 유용하다. 디지털 통신 시스템에 있어서, 예를 들어 GSM 또는 DCS 시스템 하 에서 동작하는 이동 전화 통신에서, PLL은 반송(carrier) 신호의 연속 위상 변조(CPM)를 달성하기 위해 이용될 수 있다.

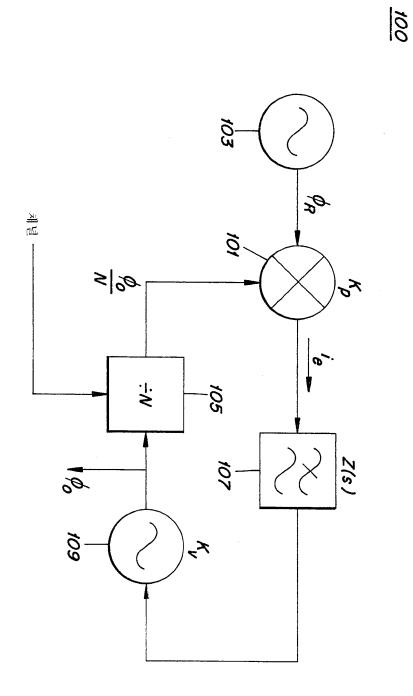

- <3> 도 1은 종래의 정수-분할(integer-devide) PLL(100)의 블록도이다. 위상 검출기(101)는 기준 발진기(103)에 의해 인가된 신호의 위상을 주파수 분할기(105)에 의해 인가된 피드백 신호의 위상과 비교한다. 위상 검출기의 출력은 두 입력 신호들 간의 위상차를 나타내며, 필터(107)에 의해 필터링된다. 다음에, 필터링된 출력은 전압 제어 발진기(VCO)(109)에 의해 생성된 출력 신호의 주파수를 제어하는데 이용된다. VCO(209)로부터의 출력 신호는, PLL로부터의 출력으로서 공급되는 것 뿐만 아니라, 주파수 분할기(105)의 입력으로서 제공되어서 피드백소의 소스가 된다. PLL(100)은 다음의 식에 의해 결정된다.

#### 수학식 1

<4>

<5>

$$i_e = K_p(\Phi_R - \frac{\Phi_o}{N})$$

$$\Phi_{o} = i_{e}Z(s) \frac{K_{v}}{s}$$

<6> 여기서, s, K<sub>P</sub>, Z(s), 및 K<sub>V</sub>는 각각 복소 주파수, 위상 검출 이득, 루프-필터 트랜스임피던스, 및 VCO 이득이고, φ<sub>R</sub>, φ<sub>0</sub>, 및 i<sub>e</sub>는 각각 기준 위상(또는 2πf=s<sup>\*</sup>φ인 주파수), VCO 위상, 및 위상 검출 에러 전류이다.

- <7> 상기 식을  $\phi_0$ 에 대해 풀면 공지된 결과인  $f_0=N\cdot f_R$ 의 결과를 산출하며, 즉 VCO 주파수는 기준 주파수의 정수배이다.

- N의 변화(예를 들어, 새로운 채널이 선택될 때)에 대한 루프 응답 시간이 1/f<sub>R</sub>에 비례하고(즉, 고정하는데 임의수의 기준 사이클이 소요됨), 최소 채널 간격이 f<sub>R</sub>이기 때문에, 기준 주파수의 선택에 있어서 충돌이 생긴다,즉,최소 채널 간격을 줄이기 위하여, f<sub>R</sub>을 낮은 값으로 설정하는 것이 바람직하다. 그러나, 이러한 설정은 더큰 루프 응답 시간을 야기시켜, 바람직하지 못하다.

- \*\*\*\* 채널 간격에서의 상기 제한을 피하기 위하여, 분율-N(fractional-N) PLL 이 고안되었다. 정수 분할기보다는 변수-계수(variable-modulus) 분할기를 이용함으로써, 더욱 유연한 분할비를 얻는 것이 가능하다. 예를 들어, 20에 의한 3개의 연속 분할에 후속하는 21에 의한 하나의 분할을 수행하는 것은 평균 분할 인수 (3·20+21)/4=20.25 및 채널 간격 f<sub>R</sub>/4의 결과를 가져온다. 그러나, 이러한 변수 계수 분할의 반복적 속성 때문에, VCO를 변조시키게 되는 의사 톤(spurious tones)이 생성될 것이다(여기서는, £±n·f<sub>R</sub>에서).

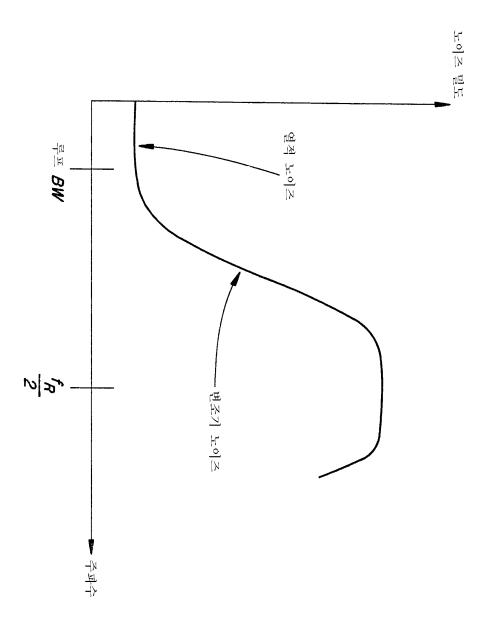

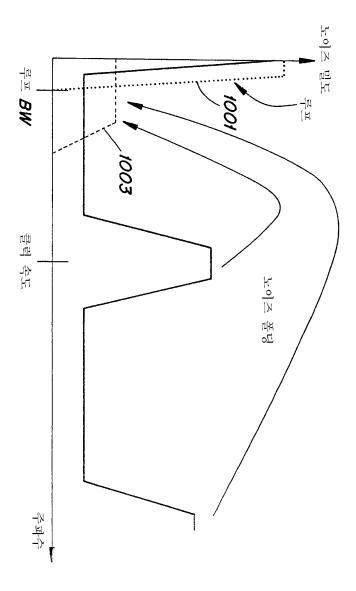

- <10> 최근에, 분율-N 분할기의 의사 응답을 형성하기 위해  $\Delta \Sigma$ 변조기가 이용되어 왔다. 전형적인  $\Delta \Sigma$ 노이즈 밀도 분포를 묘사하고 있는 그래프가 도 2에 도시되어 있다. 의사 톤은 PLL의 선폭을 훨씬 넘어, 주파수에서 벗어난 가장 의사적인 에너지를 갖는 의사 톤의 스펙트럼으로 대체되며, 이것은 주로  $f_R/2$  (여기서  $f_R$ 은  $\Delta \Sigma$  변조기의 클릭 속도임) 주위에 집중되어진다. 열적 노이즈 플로어(thermal noise floor)(예를 들어, 분할기 회로에 기인 하는 열적 노이즈) 또한 포함된다.  $\Delta \Sigma$  변조기에 의해 수행된 형상화의 결과로써, 이 의사 에너지는 PLL로부 터의 출력 신호에 실질적으로 감소된 영향을 줄 것이다.

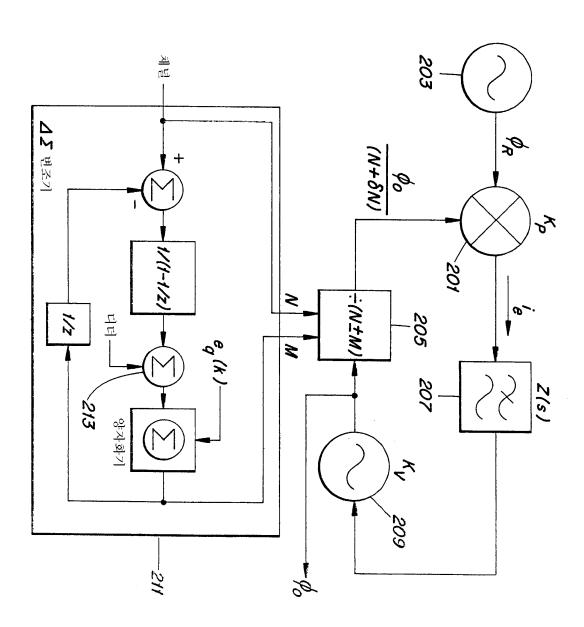

- <11> ΔΣ 분율-N PLL(200)의 예시적인 실시예가 도 3에 도시되어 있다. 위상 검출기(201), 기준 발진기(203), 필터 (207) 및 VCO(209)는 도 1에 대해 설명된 이들의 대응하는 요소들과 유사하므로, 여기서 상세한 설명을 할 필요는 없다. 이 경우에 주파수 분할기(205)는 N±M 범위에서 임의의 정수 계수로 분할할 수 있으며, N에 대한 값을 수취하기 위한 입력 및 M의 값을 수취하기 위한 다른 입력의 2개의 입력을 갖는다. 상술한 바와 같이 M의 값을 적절하게 변화시킴으로써, 효과적인 분배 계수 N+δN을 얻을 수 있다. ΔΣ 변조기(211)가 제공되어 소망하는 채널값을 수취하고, 그로부터 N 및 M에 대해 적절한 값들을 생성한다. 예시적인 실시예에서, 1차 ΔΣ변조기가 도시되지만 이것이 필수적인 것이 아니다.

- <12> 루프 응답(즉, 루프 대역폭이 너무 넓지 않으면)에 의해 ΔΣ 노이즈는 억제될 것이지만, ΔΣ 변조기 제한 사이클(즉, 매우 짧은 주기를 갖는 것과 관련된 반복 작용)로 인한 의사 톤을 피하기 위하여, 여분의 노이즈("디더(dither)")가 통상적으로 추가되어 ΔΣ 노이즈를 더 랜덤화시킨다. 이것은 도 3에서 디더값을 ΔΣ 노이즈에 합하는 합산 회로(213)에 의해 형성된다. 그 다음에, 결과되는 값은 양자화되어, 그 자신의 양자화 노이즈 eq(k)를 부가한다. ΔΣ 변조기(211)의 출력에서 생성되는 결과값 M은 주파수 분할기(205)의 계수 입력들 중의하나에 입력된다.

- <13> 노이즈 형성을 가능하게 하기 위하여, 분할 계수는 2개의 가장 가까운 정수 인자들로만 선택되어서는 안되며, 대신 예를 들어, N-M,..., N+M 사이에서 변화되어야 한다. 노이즈가 주파수에서 벗어나면, 이러한 여분의 계수 범위는 VCO 반송으로부터 벗어날 필요가 있다. 다시 말해서, 루프 필터는 ΔΣ 노이즈를 억제할 수 없게 될 것이다. 이러한 확장된 분할 계수 영역의 결과로써, 순간 위상 에러가 증가할 것이다. ΔΣ 루프 방정식은 다음과 같이 된다.

#### 수학식 2

<14>

<15>

$$i_e = K_p (\Phi_R - \frac{\Phi_o}{N + \delta N} + N_{\Delta\Sigma})$$

$$\Phi_{o} = i_{e}Z(s) - \frac{K_{v}}{s}$$

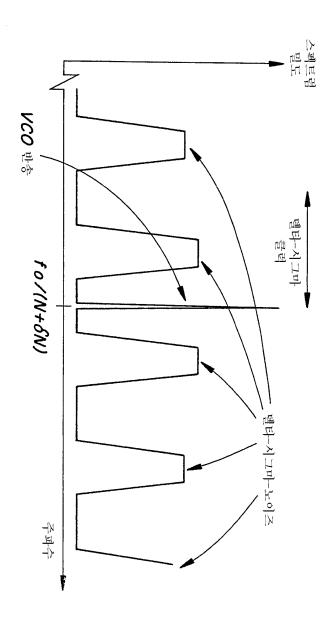

<16> 여기서, N+ $\delta$ N과 N $_{\Delta\Sigma}$ 는 각각 분수 분할비 및  $\Delta\Sigma$ 변조기 노이즈를 나타낸다. 도 4는 주파수 분할기(205)의 출력 스펙트럼을 도시하는 그래프이다.

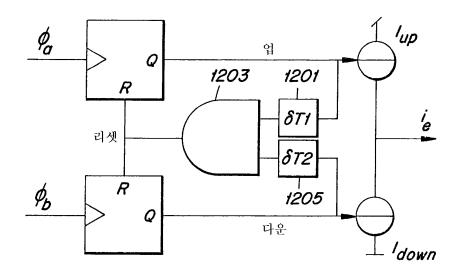

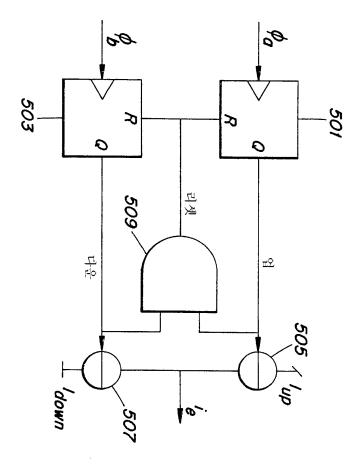

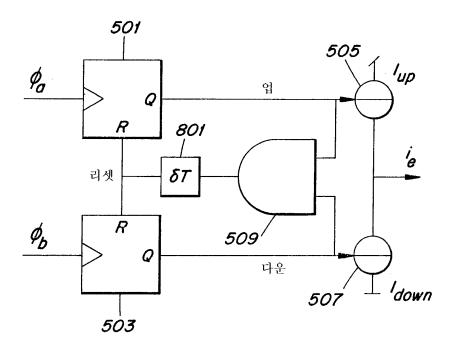

- <17> 도 5는 종래의 위상 검출기(201)의 전형적인 실시예의 블록도이다. 제1 및 제2 디지털 래치들(501, 503)을 사 용함으로써 다중 상태(도 5에 도시되지 않음), 및 그에 따른 위상 검출기(201)의 확장된 영역을 가능하게 할 수 있다. 동작시, 제1 래치(501)는 제1 차지 펌프(505)가 온인지 오프인지를 제어한다. 유사하게, 제2 래치(503) 는 제2 차지 펌프(507)가 온인지 오프인지를 제어한다. 제1 및 제2 차지 펌프(505, 507)는 직렬 접속되어 있으 며, 위상 검출기 출력 전류 ie는 두 차지 펌프 사이의 접속 점에서 제공된다. 위상 검출기 출력 전류 ie의 양은 제1 및 제2 차지 펌프(505, 507) 중의 하나 또는 둘다가 온 상태인지 또는 어느 것도 온이 아닌지의 여부에 관 련된다. ie가 비제로(non-zero)인 시간은 2개의 입력 신호들, φa와 φb 사이의 위상차의 함수이다. 이 신호들 각각은 제1 및 제2 래치들(501, 503) 중의 각각의 클럭 입력에 공급된다. 클럭 엣지를 나타내는 이들 신호들 중의 첫번째 신호는 대응하는 래치의 출력이 어써트(assert)되게 하고, 교대로 제1 및 제2 차지 펌프들(505, 507) 중의 대응하는 하나가 턴온되게 한다. 그 후에 나머지 입력 신호의 클럭 엣지가 어써팅될 때, 이것 또한 대응하는 래치의 출력이 어써팅되게 한다. 제1 및 제2 래치들(501, 503)의 둘 다의 출력은 논리 AND 게이트 (509)의 각각의 입력에 더 공급되며, 이 논리 AND 게이트(509)의 출력은 제1 및 제2 래치(501, 503) 둘 다의 RESET 입력으로 공급된다. 결과적으로, 양측 래치들(501, 503)의 출력이 어써팅되면, AND 게이트(509)의 출력 또한 어써팅되어 두 래치들(501, 503)를 리셋할 것이다. 그리고, 초기화되어 다음 사이클을 위해 상기 프로세 스를 반복한다. 그 결과, 출력 전류  $i_e$ 는 만약 제1 입력 신호  $\phi_a$ 가 제2 입력 신호  $\phi_b$ 보다 앞서면 양의 값(제1 차지 펌프(505)에 의해 공급됨)이 되고, 제2 입력 신호 Φ<sub>b</sub>가 제1 입력 신호 Φ<sub>a</sub> 보다 앞서면 음의 값(제2 차지 펌프(507)에 의해 공급됨)이 된다.

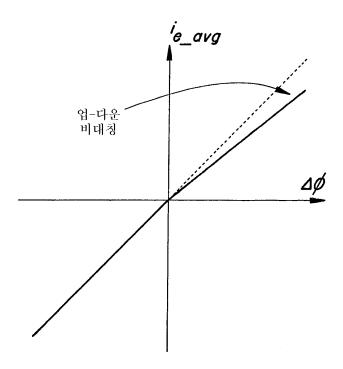

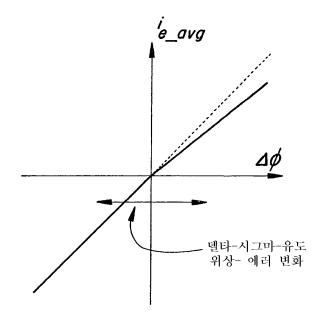

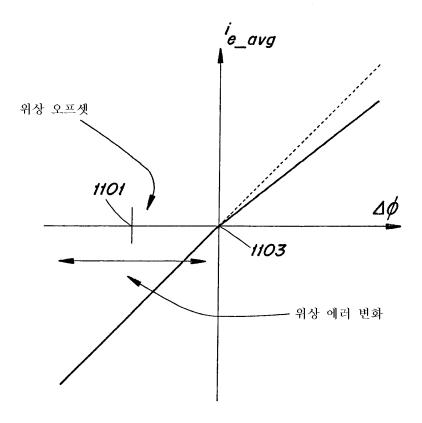

- <18> 전형적인 위상 검출 전달 함수가 도 6에 도시되어 있으며, 여기서 평균 위상 검출 출력 전류 i<sub>e,avg</sub>는 위상차 Δ Φ의 함수로써 도시된다. 도 5에 도시된 위상 검출기와 관련된 "데드-존(dead-zone)"은 도 6에는 도시되어 있 지 않다. 데드-존은, 그것을 다루는 방법으로서, 이하에서 더욱 상세히 논의된다.

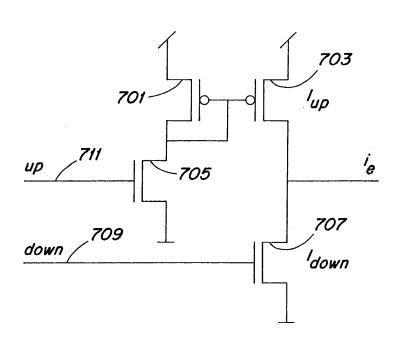

- <19> 위상 검출기 출력은 종종 고 임피던스의 오프 상태를 갖는 차지 펌프로 설계된다. 이 고 임피던스 오프 상태는 루프 필터를 집적기(integrator)로 효과적으로 변환시킨다(즉, 트랜스임피던스 Z(s)가 용량성이면). 차지 펌프 들(505, 507) 중의 어느 하나로써 이용될 수 있는 차지 펌프의 단순화된 회로도가 도 7에 도시되어 있다. 이 단순화된 설계에서, "다운" 스테이지에 대한 전류는 "다운" 신호(709)가 어써팅될 때, 트랜지스터(707)에 의해 흐르게 된다. "업" 스테이지에 대한 전류는, "업" 신호(711)가 어써팅될 때, 트랜지스터들(701, 703 및 705)의 전류 미러 구성에 의해 공급된다.

- <20> 도 3 및 도 5를 다시 참조하면, PLL(201)이 그 기준 Φ<sub>R</sub>을 적절하게 추적할 때, 2개의 입력 신호들간의 위상차 가 매우 작아지기 때문에, 위상 검출 래치들(501, 503) 둘 다는 거의 동시에 트리거된다. 리셋 신호는 제1 및 제2 래치들(501, 503)을 즉각적으로 리셋시키고, 그 결과 래치 출력에 짧은 스파이크만이 너무 빨리 나타나서, 제1 및 제2 차지 펌프들(505, 507) 각각을 턴온할 수 없다.

- <21> 실제로, 작은 위상 에러(즉, 추척 에러)가 있다고 하더라도, 제1 및 제2 래치들(501, 503)은, 차지 펌프들(505, 507)이 반응하기에는 너무 빨리 리셋할 것이다. 결과적으로, 위상 검출기 전달 함수는 원점 주위에 작은 데드-밴드(저이득 영역)에 의해 특징지어진다. 이 데드-밴드를 없애기 위한 공통 기술은 지연 회로(801)를 이용하는 것이며, 이 지연 회로(801)는 도 8에 도시된 바와 같이 리셋 신호에 지연 δΤ를 추가한다. 이러한 추가의 지연으로, 업 및 다운 펄스들은 각각 차지 펌프를 활성화시키는 데 충분히 길기 때문에, 데드 밴드를 제거할 수 있다.

- <22> 상술된 바와 같은 지연 회로(801)의 사용에도 불구하고, 문헌에서 보고된 ΔΣ-기초의 분율(fractional)-N PLL 은 종종 정수-분할 대응부(counterpart)에 비교되는 내부 노이즈 특성을 갖는다. 이는 셀룰러 전화와 같이, 요구되는 어플리케이션에서의 사용을 방지한다. 도 2에 도시된 바와 같이 노이즈가 루프 대역폭 밖에 있을 수 있다고 하더라도, 이 초과 노이즈의 근원은 ΔΣ 변조기 노이즈에 기인한다.

- <23> 따라서, 분율-N PLL의 노이즈 특성을 향상시키기 위한 구성 요소와 기술을 제공하는 것이 요구된다.

- <24> <발명의 개시>

- <25> 본 명세서에서 사용될 때, 용어 "포함한다" 및 "포함하는"은 명시된 특징, 정수, 단계 또는 구성요소의 존재를 특정하는 것으로 여겨지지만, 이들 용어의 사용은 하나 이상의 다른 특징, 정수, 단계, 구성요소 또는 그룹의 존재 또는 추가를 제외하지는 않는다는 것을 강조해야 한다.

- 본 발명의 일 양태에 따라, 전술된 목적 및 다른 목적은 제1 신호를 수신하는 제1 입력; 제2 신호를 수신하는 제2 입력; 상기 제1 신호와 상기 제2 신호 간의 위상차의 함수인 출력 신호를 생성하는 비교 회로를 포함하는 위상 검출기에서 달성된다. 출력 신호는 출력 전류 또는 대안으로 출력 전압의 형식일 수 있다. 스테디-스테이트(steady-state) 동작 동안에 선형 특성을 제공하기 위하여, 위상 검출기는 상기 제1 신호와 제2 신호 간의 포지티브 및 네거티브 위상차들 둘 다의 소정 범위에 대해, 상기 출력 신호가 상기 제1 신호와 상기 제2 신호간의 상기 위상차의 실질적인 선형 함수로서 발생하도록 상기 위상 검출기의 동작점을 유지하는 동작점 회로를 더 포함한다.

- <27> 동작점 회로는 임의의 대안적인 실시예일 수 있다. 예를 들어, 상기 위상 검출기가 위상 동기 루프에 사용됨으로써 상기 위상 동기 루프의 출력 주파수가 상기 위상 검출기의 상기 출력 신호의 함수가 되는 경우, 상기 누설된(leak) 출력 신호가 상기 위상 동기 루프의 상기 출력 주파수에 영향을 주지 못하도록 상기 동작점 회로가 상기 출력 신호의 미리 정의된 부분을 누설시킬 수 있다.

- (28) 대안적으로, 상기 출력 신호는 출력 전류이고, 상기 비교 회로는, 상기 제1 신호의 엣지에 응답하여 제1 차지 펌프 제어 신호를 어써트하는 제1 회로; 상기 제2 신호의 엣지에 응답하여 제2 차지 펌프 제어 신호를 어써트하는 제2 회로; 상기 제1 차지 펌프 제어 신호의 어써트에 응답하여 상기 출력 전류에 포지티브 전류를 부여하는 제1 차지 펌프; 상기 제2 차지 펌프 제어 신호의 어써트에 응답하여 상기 출력 전류에 네거티브 전류를 부여하는 제2 차지 펌프; 및 상기 제1 및 제2 차지 펌프 제어 신호 둘 다가 어써트되는 것에 응답하여 상기 제1 및 제2 회로들의 각각에 리셋 신호를 제공하는 리셋 로직을 포함하고, 상기 동작점 회로는, 상기 상기 리셋 로직에 공급되는 제1 및 제2 차지 펌프 제어 신호 중 적어도 하나를 지연시키는 지연 회로를 포함하고, 상기 제1 차지 펌프 제어 신호가 상기 리셋 로직에 공급되는데 소요되는 시간과 동일하지 않다. 이러한 대안에서, 상기 지연 회로는 상기 리셋 로직에 공급 되는 상기 제1 및 제2 차지 펌프 제어 신호를 중 하나만을 지연시키도록 설계될 수 있다. 대안적으로, 상기 제1 및 제2 차지 펌프 제어 신호 둘 다를 상기 리셋 로직에 공급하는 것으로부터 지연시킬 수 있다.

- <29> 또 다른 대안에서, 상기 출력 신호는 출력 전압이고, 상기 비교 회로는, 상기 제1 신호의 엣지에 응답하여 제1 전압 발생기 제어 신호를 어써트하는 제1 회로; 상기 제2 신호의 엣지에 응답하여 제2 전압 발생기 제어 신호를 어써트하는 제2 회로; 상기 제1 전압 발생기 제어 신호의 어써트에 응답하여 상기 출력 전압에 포지티브 전압을 부여하는 제1 전압 발생기; 상기 제2 전압 발생기 제어 신호의 어써트에 응답하여 상기 출력 전압에 네거티브 전압을 부여하는 제2 전압 발생기; 및 상기 제1 및 제2 전압 발생기 제어 신호들 둘 다가 어써트되는 것에 응답하여 상기 제1 및 제2 회로들의 각각에 리셋 신호를 제공하는 리셋 로직을 포함하고, 상기 동작점 회로는, 상기리셋 로직에 공급되는 상기 제1 및 제2 전압 발생기 제어 신호들 중 적어도 하나를 지연시키는 지연 회로를 포함할 수 있고, 상기 제1 전압 발생기 제어 신호가 상기 리셋 로직에 공급되는데 소요되는 시간은 상기 제2 전압 발생기 제어 신호가 상기 리셋 로직에 공급하는 것을 지연하도록 설계될 수있다. 대안에서, 상기 리셋 로직에 공급되는 상기 제1 및 제2 전압 발생기 제어 신호 중 하나를 리셋 로직에 공급하는 것을 지연하도록 설계될 수있다. 대안에서, 상기 리셋 로직에 공급되는 상기 제1 및 제2 전압 발생기 제어 신호 중 하나를 리셋 로직에 공급하는 것을 지연하도록 설계될 수있다. 대안에서, 상기 리셋 로직에 공급되는 상기 제1 및 제2 전압 발생기 제어 신호 둘 다를 지연할 수 있다.

- <30> 위상 검출기가 위상 동기 루프에서 사용되는 또 다른 대안적인 실시예에서, 위상 검출기의 선형 동작은, 위상 동기 루프에서, 누설 출력 신호가 상기 위상 동기 루프의 상기 출력 주파수에 영향을 미치는 것을 방지하기 위하여 제어가능한 발진기 회로(예를 들어, 전압 제어 발진기 회로 또는 전류 제어 발진기)를 제어하는 주파수 제어 신호 및 위상 검출기 출력 신호 중 적어도 하나의 소정의 부분을 누설하는 하나 이상의 회로 소자를 포함함으로써 달성될 수 있다. 예를 들어, 이러한 누설은 상기 위상 검출기 출력 신호의 소정의 부분을 누설하는 상기 루프 필터에서 하나 이상의 회로 소자에 의해 행해지도록 설계될 수 있다.

#### 발명의 상세한 설명

- <46> 이제 본 발명의 다양한 특징이 도면을 참조하여 설명되고, 유사한 부분은 동일한 참조 부호로 식별된다.

- <47> 본 발명자의 자세한 조사로, ΔΣ변조기 노이즈가 루프 통과대역 밖에 있도록 설계될 때에도, 예상보다 높은 PLL 위상 노이즈가 얻어짐을 알 수 있었다. 본 발명자의 다른 분석은 차지-펌프 비대칭(예를 들어, 도 7과 같이 차지 펌프에서 트랜지스터의 부정합(mismatch)에 기인함)에 기인할 수 있음을 보였다. 이러한 비대칭은 위상 검출기 전달 함수의 그래프를 도시하는 도 9에 도시될 수 있다. 특히, 평균 PLL 출력 전류(ie\_avg)에서 변화속도는 네거티브 위상차에 대한 것과 포지티브 위상차에 대한 것이 다르다. 이 비대칭은 ΔΣ변조기 노이즈가차지-펌프에 의해(즉, 짝수 차수 비선형성) 정류되도록 한다. 이 비선형 프로세스는 DC(제로 주파수) 주위에서

2배의 대역폭에서 정류된  $\Delta \Sigma$ 변조기 노이즈를 중심으로 한다. 이는 도 10에 도시된 바와 같이, 종래의 PLL의 출력에서 노이즈 밀도 스펙트럼의 그래프일 수 있다. 루프 전달은 점선(1001)에 의해 나타나고 다운 변환 (down-converted) 노이즈는 일점쇄선(1003)에 의해 나타내어진다. 도면에 도시된 바와 같이, 일반적으로 루프 대역폭 밖의 주파수에서 생성된 노이즈는 정류에 기인하여 루프 대역폭 내로 중첩된다(fold back). 이는, 차례로 VCO를 변조하여, 초과 VCO 위상 노이즈를 야기시킨다. 이 정류 프로세스는 항상 차지-펌프 기초의 위상 검출기에 존재한다. 그러나,  $\Delta \Sigma$ 변조기가 정규 정수-N, 또는 비- $\Delta \Sigma$ 변조기 분율-N, 루프보다 훨씬 큰 순간 위상 에러(왜냐하면 이들은 분율-N 의사 톤이 보다 고-주파수 성분을 포함하도록 형성하기 때문임)를 야기한다. 주파수 합성기 PLL이 예를 들어, GSM 송수신기에서 위상 또는 주파수 변조를 생성하는데 사용될 때, 에러 신호크기의 문제가 더 악화될 수 있다.

- 본 발명은 포지티브 및 네거티브 위상차 둘 다가 선형 영역에서 차지-펌프 동작을 유지하도록 위상 검출기 차지 펌프의 동작점을 시프트함으로써 차지-펌프 비대칭 문제를 해결한다. 도 11은 차지 펌프 전달 함수를 도시한다. 예를 들어, 스테디-스테이트점(1101)으로 동작점을 시프트함으로써, 위상 에러가 기점(1103)에서 비 선형성으로 선회하지(traverse) 않도록 충분히 작아지게 만들어질 수 있는 것임을 알 수 있다. 기점(1103)으로 부터 떨어짐으로써, (대부분) 구분(piece-wise) 선형 차지-펌프 전달의 한 세그먼트만이 활성화될 것이고 더욱 선형적인 위상 검출기 응답을 얻을 수 있다. 예를 들면, 주파수 변화에 의해 에러가 보다 크게 발생할 경우, 위상 검출기는 정상적인 방식으로 동작한다. 동작점 오프셋은 동기된 상태(locked condition)동안에만 중요할 것이다.

- <49> 위상 검출기 오프셋은 많은 선택적인 방법들 중 임의의 방법으로 구현될 수 있고 선택된 특정 방법은 본 발명에서는 필수적이지 않다. 일 실시예에서, 이는 PLL, 예를 들면, 루프 필터 Z(s) 내에 일정한 누설 전류를 추가함으로써 구현될 수 있다. 그러나, 이러한 누설 전류는 루프 필터와 독립적으로 하는 것이 바람직하다.

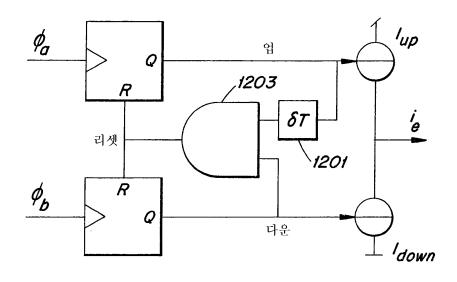

- <50> 대안의 실시예에서, 2개의 래치 출력들 중 하나에만 작용하도록 데드-밴드 지연이 시프트된다, 예를 들면, 도 12a는 지연 회로(1201)가 "업" 신호와 로직 AND 게이트(1203)의 제1 입력 사이에 개재되어 있는 선형 데드-밴드-프리 디지털 위상 검출기(1200)를 나타낸다.

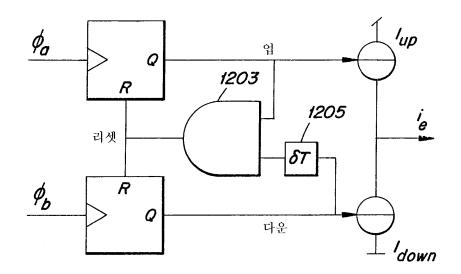

- <51> 도 12b에 나타낸, 대안의 실시예에서는, 지연 회로(1205)가 "다운" 신호와 로직 AND 게이트(1203)의 제2 입력 사이에 개재되도록 선형 데드-밴드-프리 디지털 위상 검출기(1225)가 배치된다.

- <52> 도 12c에 도시된, 다른 대안의 실시예에서는, 제1 지연 회로(1201)는 "업" 신호와 로직 AND 게이트(1203)의 제1 입력 사이에 개재되고, 제2 지연 회로(1205)는 "다운" 신호와 로직 AND 게이트(1203)의 제2 입력 사이에 개재되 도록 선형 데드-밴드-프리 디지털 위상 검출기(1250)가 배치된다. 이 실시예에서, 제1 지연 회로(1201)에 의해 부여되는 지연은 제2 지연 회로(1203)에 의해 부여된 지연과 동일하지 않아야 한다.

- <53> 도 12a, 12b 및 12c에 나타낸 선택적인 실시예들의 각각에서는, 위상 검출기용 리셋 신호를 생성하는 로직 AND 게이트에 공급되는 "업" 및 "다운" 신호들에 대해 지연이 비대칭적이다. 지연 비대칭을 M/f<sub>0</sub> (즉, VCO의 출력 주파수의 M개 사이클과 같은 시간량)와 가깝게 하거나 또는 보다 크게함으로써, 모든 Δ Σ 노이즈는 위상 검출기 출력 전류 제로 크로싱의 한 측에 한정될 것이다. 지연은 f<sub>R</sub> 및 f<sub>0</sub>가 지연 비대칭에 대응하는 일정한 위상 오프 셋을 갖도록 하나, 이것은 전형적인 주파수 합성기 응용에서는 문제가 되지 않는다.

- <54> 본 발명은 특정 실시예를 참조하여 설명되었으나, 상술한 바람직한 실시예의 형태와는 다른 특정 형태로 본원이 구현될 수 있다는 것은 본 기술 분야의 통상의 지식을 가진 자에게는 용이하게 자명할 것이다. 이는 본원의 범주로부터 벗어남이 없이 이루어질 수 있다.

- <55> 예를 들면, 본 기술 분야의 통상의 지식을 가진 자는, 전압 제어 발진기를 사용하는 위상 동기 루프가 설명되었으나 이러한 측면은 본원 발명에 필수적이지 않고, 위상 검출과 연관된 본원의 개념은 전압 제어 발진기 대신에 전류 제어 발진기를 사용하는 위상 동기 루프에 적용될 수 있고, 각 경우에서 이러한 구성 요소들은 루프 필터에 의해 발생되는 주파수 제어 신호에 의해 제어되는 주파수를 갖는 위상 동기 루프 출력 신호를 생성하는 회로로 생각될 수 있다는 것을 인식할 것이다.

- <56> 또한, 상술한 실시예들은 차지 펌프를 사용하고, 2개의 신호들 간의 위상차의 실질적인 선형 함수로 변화하는 출력 전류를 생성한다. 그러나, 본원 발명의 선택적인 실시예들은, 출력 전류 대신, 2개의 신호들 간의 위상차의 실질적인 선형 함수로서 변화하는 출력 전압을 생성하도록 고안될 수도 있다. 이러한 경우에, 차지 펌프 이외의 전압 발생기가 사용될 수 있다. 출력 전압은 위상 동기 루프 내의 VCO를 제어하기 위한 소스 신호로서 역

할을 할 수 있거나, 또는 출력 전압은 VCO 대신에 전류 제어 발진기를 사용하는 이러한 실시예들에 대해 변화하는 전류로 선택적으로 변환될 수 있다.

<57> 따라서, 바람직한 실시예는 단지 예시적이며 어떤 경우에도 한정적으로 생각되어서는 안된다. 본원의 범주는, 앞선 상세한 설명보다는 첨부되는 청구범위에 의해 주어지고, 청구범위의 범위 내에 포함되는 모든 변형 및 동 등물들은 본원에 포함되는 것으로 의도된다.

#### 도면의 간단한 설명

- <31> 본 발명의 목적 및 장점은 도면에 대한 하기의 상세한 설명을 읽음으로써 이해될 것이다.

- <32> 도 1은 종래의 정수-분할 위상-동기 루프의 블록도.

- <33> 도 2는 전형적인 △∑ 노이즈 밀도 분포를 도시하는 그래프.

- <34> 도 3은 ΔΣ분율-N PLL의 예시적인 실시예의 블록도.

- <35> 도 4는 주파수 분할기의 출력 스펙트럼을 도시하는 그래프.

- <36> 도 5는 종래의 위상 검출기의 전형적인 실시예의 블록도.

- <37> 도 6은 전형적인 위상-검출기 전달 함수의 그래프.

- <38> 도 7은 위상 검출기에서 차지 펌프 중 하나로서 사용될 수 있는 차지 펌프의 간략화된 연출을 나타내는 블록도.

- <39> 도 8은 리셋 신호에 대칭적 지연을 추가하기 위해 지연 회로를 사용하는 종래의 디지털 위상 검출기의 블록도.

- <40> 도 9는 위상-검출기 전달 함수의 그래프.

- <41> 도 10은 종래의 PLL의 출력에서 노이즈 밀도 스펙트럼의 그래프.

- <42> 도 11은 차지-펌프 전달 함수를 도시하는 그래프.

- <43> 도 12a는 지연 회로가 로직 AND 게이트의 "업" 입력에 위치되는 선형 데드-밴드-프리(dead-band-free) 디지털 위상 검출기를 도시하는 도면.

- <44> 도 12b는 지연 회로가 로직 AND 게이트의 "다운" 입력에 위치되도록 배열된 선형 데드-밴드-프리 디지털 위상 검출기를 도시하는 도면.

- <45> 도 12c는 제1 지연 회로가 로직 AND 게이트의 "업" 입력에 위치되고, 제2 지연 회로가 로직 AND 게이트의 "다운" 입력에 위치되도록 배열된 선형 데드-밴드 프리 디지털 위상 검출기를 도시하는 도면.

## 도면1

(종래 기술)

도면2

200

도면4

(종래 기술)

201

## 도면7

## (종래 기술)

### 도면9

### 도면12a

# <u>1200</u>

## 도면12b

## 1225

## 도면12c

# <u>1250</u>