# (19) 대한민국특허청(KR) (12) 등록특허공보(B1)

| (51) Int. CI. <sup>6</sup><br>GO1R 31/26 |                                                | (45) 공고일자<br>(11) 등록번호 | 1999년06월 15일<br>10-0195680      |

|------------------------------------------|------------------------------------------------|------------------------|---------------------------------|

|                                          |                                                | (24) 등록일자              | 1999년02월 12일                    |

| (21) 출원번호<br>(22) 출원일자                   | 10-1996-0001221<br>1996년01월20일                 | (65) 공개번호<br>(43) 공개일자 | 특 1996-0029805<br>1996년 08월 17일 |

| (30) 우선권주장                               | 95-026175 1995년01월20일<br>95-026175 1995년01월20일 | 일본(JP)<br>일본(JP)       |                                 |

| (73) 특허권자                                | 닛본 덴기 가부시끼가이샤                                  | 가네꼬 히사시                |                                 |

| (72) 발명자                                 | 일본국 도꾜도 미나도꾸 시!<br>사나다마사루                      | 바 5쪼메 7방 1고            |                                 |

| (74) 대리인                                 | 일본국 도꾜도 미나도꾸 시I<br>구영창, 장수길                    | 바 5쪼메 7-1 닛본덴기         | 가부시끼가이샤 내                       |

|                                          |                                                |                        |                                 |

심사관 : 권호영

## (54) 비정상 전류를 이용하는 고장 블럭 검출 시스템

#### 요약

다수의 논리 블록들( $B_1$ ,  $B_2$ , ...)에 의해 형성된 반도체 소자에서, 다수의 기능 검사 패턴[FTP(ADD)]이 발생된 후 상기 반도체 소자에 전송되어, 비정상 전류( $I_{deq}$ )가 반도체 소자를 통해 흐르는지의 여부가 판정된다. 비정상 전류가 검출되면, 기능 검사 패턴과 그것에 의해 동작되는 논리 블록들을 저장하는 테이블에 따라 고장 블록이 판정된다.

### 대표도

#### 명세서

[발명의 명칭]

비정상 전류를 이용하는 고장 블록 검출 시스템

[도면의 간단한 설명]

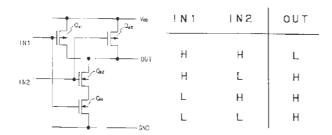

제1도(a)는 정상 2입력 CMOS NAND 회로를 도시한 회로도.

제1도(b)는 제1도(a)의 NAND 회로의 진리표.

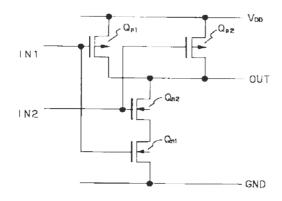

제2도(a)는 비정상 2입력 CMOS NAND 회로를 도시한 회로도.

제2도(b)는 제2도(a)의 NAND 회로의 진리표.

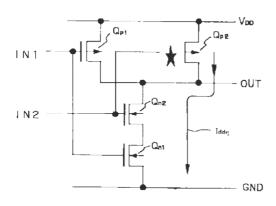

제3도는 본 발명에 따른 고장 블록 검출 장치의 한 실시예를 도시한 블록회로도.

제4도는 기능검사 패턴과 동작 블록 간의 관계를 나타내는 테이블.

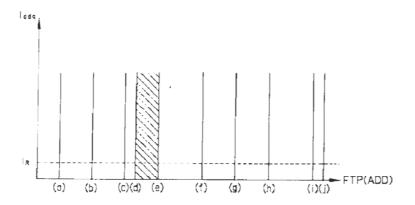

제5도는 정지 V<sub>DD</sub> 전원 전류 (quiesecent V<sub>DD</sub> supply current; I<sub>ddq</sub>)를 나타내는 그래프.

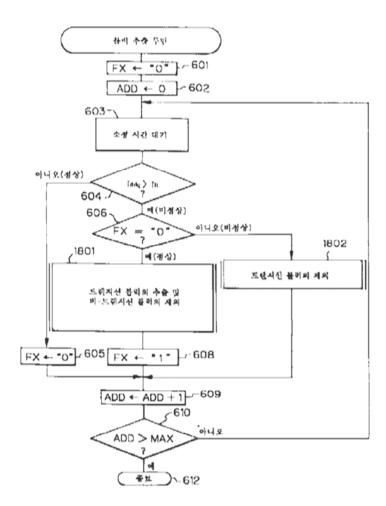

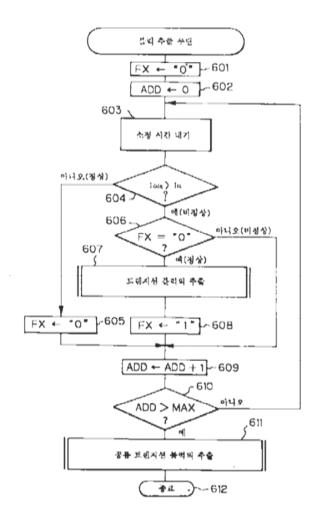

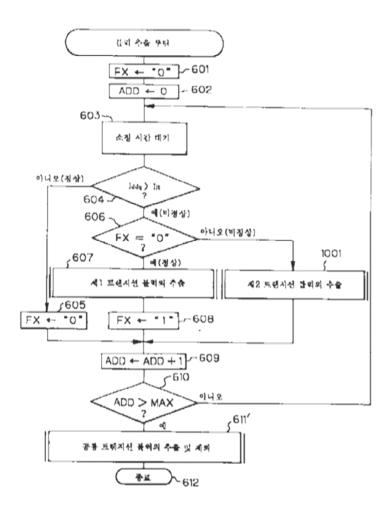

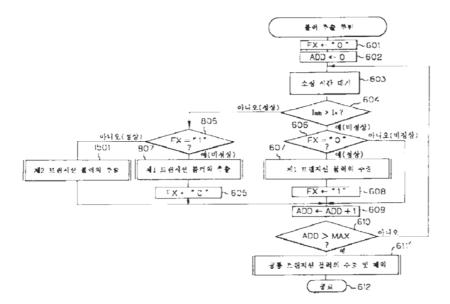

제6도는 제3도 제어 회로의 제1동작을 나타내는 흐름도.

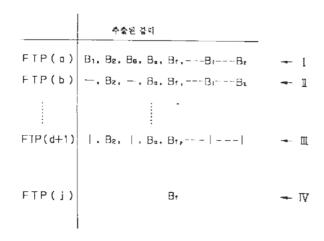

제7도는 비정상 전류(abnormal current;  $I_{ddq}$ )가 검출될 때 제6도의 흐름도의 동작에 의해 추출된 트랜지 션 블록을 나타내는 테이블.

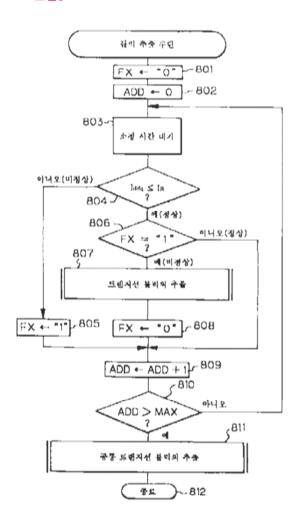

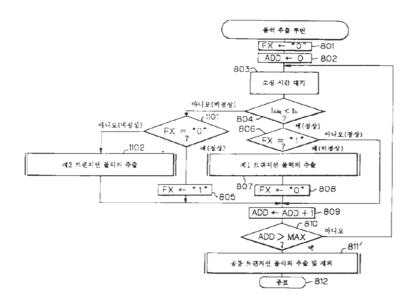

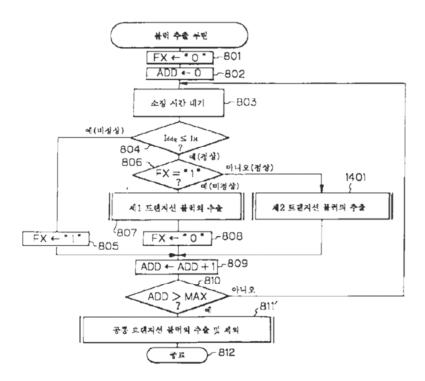

제8도는 제3도의 제어 회로의 제2동작을 나타내는 흐름도.

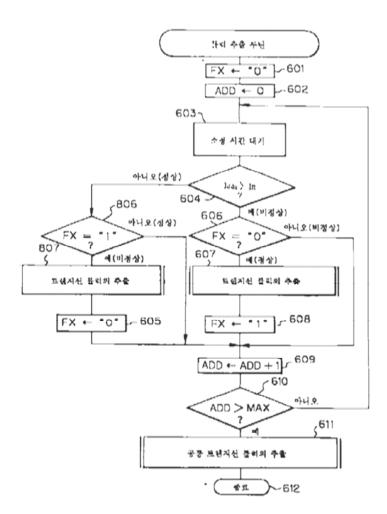

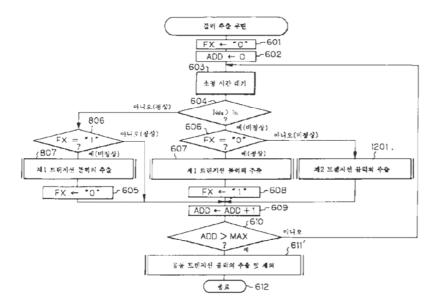

제9도는 제3도의 제어 회로의 제3동작을 나타내는 흐름도.

제10도는 제3도의 제어 회로의 제4동작을 나타내는 흐름도.

제11도는 제3도의 제어 회로의 제5동작을 나타내는 흐름도.

제12도는 제3도의 제어 회로의 제6동작을 나타내는 흐름도.

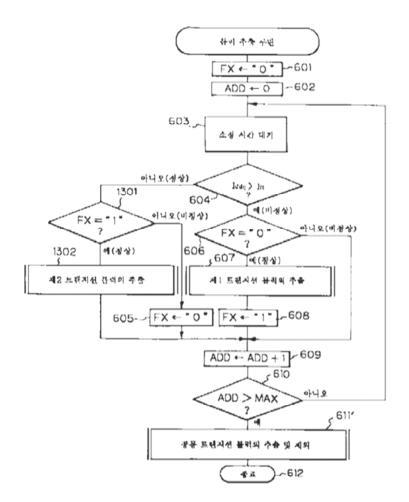

제13도는 제3도의 제어 회로의 제7동작을 나타내는 흐름도.

제14도는 제3도의 제어 회로의 제8동작을 나타내는 흐름도.

제15도는 제3도의 제어 회로의 제9동작을 나타내는 흐름도.

제16도는 제3도의 제어 회로의 제10동작을 나타내는 흐름도.

제17도는 비정상 전류 I<sub>ddq</sub> 가 검출될 때 제16도의 흐름도의 동작에 의해 추출된 트랜지션 블록을 나타내는 테이블.

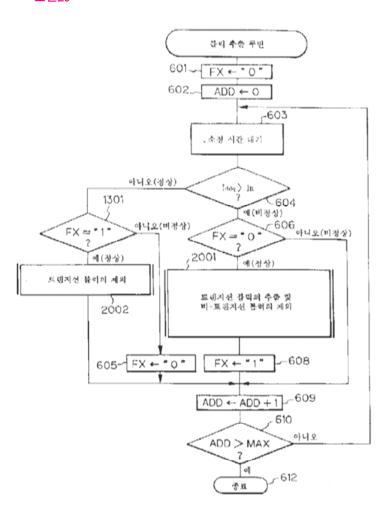

제18도는 제3도의 제어 회로의 제11동작을 타나내는 흐름도.

제19도는 비정상 전류 I<sub>ddq</sub> 가 검출될 때 제18도의 흐름도의 동작에 의해 추출된 트랜지션 블록을 나타내는 테이블.

제20도는 제3도의 제어 회로의 제12동작을 타나내는 흐름도.

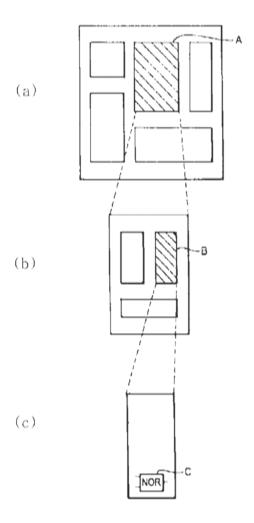

제21도(a), 제21도(b) 및 제21도(c)는 본 발명이 적용된 검사 시스템을 설명하는 구상도.

\* 도면의 주요부분에 대한 부호의 설명

1 : 반도체 소자 2 : 메모리

3 : 타이밍 발생기 4 : 패턴 발생 회로

5 : 포맷 제어기 6 : PIN 일렉트로닉스 유닛

8 : 전류 검출기 9 : 제어회로 10 : 입력장치 11 : 출력장치

[발명의 상세한 설명]

본 발명은 다수의 논리 블록들로 형성된 CMOS 소자와 같은 반도체 소자에서 고장 블록(fault block)을 검출하기 위한 시스템에 관한 것이다.

반도체 소자를 검사하는 종래 기술의 시스템에서, 소자는 기능 검사 패턴을 사용하여 구동되며, 그 결과, 소자의 출력들에서 출력 패턴이 구해진다. 그 후, 출력 패턴은 기대 패턴과 비교된다. 따라서, 출력패턴이 기대 패턴과 일치하는 지의 여부에 따라 소자가 정상인지 또는 비정상인에 대한 판정이 이루어진다.

소자가 비정상이라고 판정된 후, 고장 지점은 기능 검사 패턴(functional test pattern)과 가상 고장에 대한 출력 패턴간의 관계를 저장하는 고장 사전(fault dictionary)에 따라 평가된다.

고장 사전은 고장 시뮬레이션을 수행함으로써 얻는다.

그러나, 상술된 종래 기술의 검사 장치에서, 소자가 고도로 집적화되면, 고장 사전을 완성하기 위해 다량의 고장 시뮬레이션이 요구된다.

게다가, 고장 사전의 용량은 매우 크다. 예를 들어,  $V_0 \propto L^{2-3}$  여기서,  $V_0$ 는 고장 사전의 용량이며; L은 소자 내의 논리회로의 개수이다.

따라서, 고도로 집적화된 반도체 소자의 고장지점을 판정하기란 실질적으로 어렵다.

본 발명의 목적을 고도로 집적화된 반도체 소자의 고장 지점을 효과적으로 판정할수 있도록 하는 데 있다.

본 발명에 따르면, 다수의 논리 블록들로 형성된 반도체 소자에서, 다수의 기능 검사 패턴이 발생되어 반도체 소자에 전송되며, 비정상 전류가 반도체 소자를 통해 흐르는지의 여부가 판정된다. 비정상 전류 가 검출되면, 기능 검사 패턴 및 이기능 검사 패턴에 의해 동작되는 논리 블록들을 저장하기 위한 테이 블에 따라서 고장 블록이 판정된다.

고장 블록이 판정된 후, 종래 기술의 검사 시스템에 의해 고장 블록 내의 고장 지점이 평가된다. 이 경우, 종래 기술의 검사 시스템은 대량의 고장 사전이 필요치 않다.

이제, 첨부된 도면을 참조하여 본 발명을 상세히 설명하고자 한다.

먼저, 제1도(a), 제1도(b), 제2도(a) 및 제2도(b)를 참조하여 본 발명의 원리가 설명될 것이다.

정상 2입력 CMOS NAND 회로가 도시된 제1도(a)에서는, P-채널 MOS 트랜지스토  $Q_{p1}$  및  $Q_{p2}$ 가 전원단자  $V_{DD}$ 와 출력 단자 OUT 사이에 병렬로 접속되어 있으며, N-채널 MOS 트랜지스터  $Q_{n1}$  및  $Q_{n2}$  가 출력단자 OUT와 접지 단자 GND 사이에 직렬로 접속되어 있다. 트랜지스터  $Q_{p1}$  및  $Q_{n1}$  은 입력 단자 IN1의 전압에 의해 제어되며, 트랜지스터  $Q_{p2}$  및  $Q_{n2}$  은 입력단자 IN2의 전압에 의해 제어된다. 제1도(a)의 NAND 회로의 진리표가 제1도(b)에 도시되어 있다.

제1도(a)에서, 전원 단자  $V_{00}$  로부터 접지 단자 GND 로 흐르는 정지(quiescent)  $V_{00}$  전원 전류  $I_{ddq}$  는 존

재하지 않는다. 즉, 정지 V₀ 전원 전류 Iೄ는 정상 상태이다.

제2도(a)에서는 비정상 2입력 CMOS NAND 회로를 도시하며, P-채널 MOS 트랜지스터  $Q_{p2}$ 는 정상적으로 ON 상태에 있도록 P-채널 MOS 트랜지스터  $Q_{p2}$ 의 게이트가 개방된다고 가정한다. 그 결과, 입력 단자 IN1 및 IN2에서의 전압이 모두 하이이면, 관통 전류(penetration current), 즉 다량의 정지  $V_{DD}$  전원 전류  $I_{ddq}$ 가 흐른다. 즉, 정지  $V_{DD}$  전원 전류  $I_{ddq}$ 는 비정상상태에 있다.

또한, 제2도(a)에서, 입력 단자 IN1 및 IN2 에서의 전압이 모두 하이이면, 출력 단자 OUT 에서의 전압 Vout 는

$V_{out} = V_{DD} \cdot (2Z_n)/(Z_p + 2\cdot Z_n) > V_{th}$

여기서,  $Z_p$ 는 P-채널 트랜지스터 Q p2의 임피던스이며;  $Z_n$ 은 N-채널 트랜지스터 Q n1 및 Q n2의 임피던스이며;  $V_{th}$ 는 CMOS 인버터의 논리 임계 전압이다.

따라서, 제2도(a)의 NAND 회로의 진리표가 제2도(b)에 도시된다.

그러므로, 일반적으로, CMOS 소자와 같은 반도체 소자가 내부에 물리적 고장을 가지고 있으면, 그것을 통해 비정상 정지 V<sub>DD</sub> 전원 전류가 흐른다(참고: 엠. 사나다(M. Sanada)의 New Application of Laser Beam to Failure Anaysis of LSI with Mutil-Metal Layers, Microelectronics and Reliability, 제33권 7호, pp. 993-1009, 1993, 및 엠. 사나다의 Evaluation and Detection of CMOS-LSI with Abnormal IDDQ, Microelectronics and Reliability, 제35권 3호, pp. 619-629, 1995).

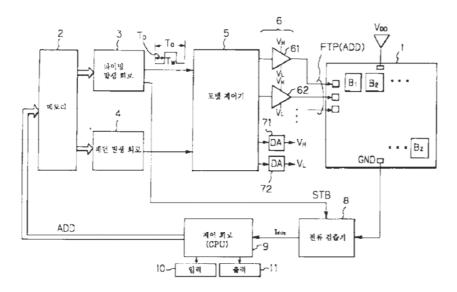

제3도에서는 본 발명의 실시예를 도시하며, 참조 번호(1)는 다수의 논리 블록 B1, B2, ···Bz을 포함하는 CMOS LSI 소자와 같은 반도체 소자를 나타낸다. 반도체 소자(1)에 기능 검사 패턴(functional test pattern: FTP)이 제공된다. 기능 검사 패턴은 메모리(2), 타이밍 발생회로(3), 패턴 발생 회로(4), 포맷제어기(5) 및 반도체 소자(1)의 입력패드에 접속된 PIN 일렉트로닉스 유닛(61, 62, ···)에 의해 발생된다.

타이밍 발생 회로(3)는 검사 속도 To, 지연시간  $T_0$  및 펄스폭 Tw을 정의하기 위해 타이밍 신호를 발생한다. 또한, 타이밍 발생 회로(3)는 스트로브 신호 STB를 발생시켜 이 신호를 반도체 소자(1)내의 전원단자  $V_{00}$ 로부터 접지 단자 GND 로 흐르는 정지  $V_{00}$  전원 전류  $I_{ddq}$ 를 검출하기 위해 전류 검출기(8)에 전송한다

패턴 발생 회로(4)는 일반적으로 압축된 메모리(2)로부터 판독된 데이터에 따라 실제 패턴 신호를 발생한다.

각각의 PIN 일렉트로닉스 유닛(61, 62, …)은 디지털/아날로그(D/A) 변환기 (71 및 72)에 의해 각각 발생된 전압  $V_H$  및  $V_I$ 에 의해 전원 공급된다. 예를 들어, PIN 일렉트로닉스 유닛(61)에 0이 인가되면, 대응입력 패드에 전압  $V_I$ (=0V)이 인가된다. PIN 일렉트로닉스 유닛(61)에 1이 인가되면, 대응입력 패드에 전압  $V_h$ 가 인가된다.

메모리(2)는 중앙 처리 유닛(CPU), ROM, RAM 등을 포함하는 제어 회로(9)로부터 어드레스 신호 SADD를 수신한다. 그러므로, 어드레스 신호 SADD의 내용 ADD이 제어 회로(9)에 의해 증가되면, 기능 검사 패턴이 차례로 발생되어 반도체 소자(1)에 전송된다.

동시에, 제어 회로(9)는 전류 검출기(8)를 통해 반도체 소자(1)를 통해 흐르는 정지  $V_{DD}$  전원 전류  $I_{ddq}$ 를 모니터한다.

또한, 키보드 또는 다른 제어기와 같은 입력 장치(10) 및 CRT와 같은 출력장치(11)가 제어회로(9)에 접속되어 있다.

제4도에 도시된 바와 같이, 기능검사 패턴 FTP(ADD) 및 기능검사 패턴 FTP(ADD)에 의해 동작되는 블록 간의 관계를 나타내는 테이블이 제어 회로(9)의 RAM 에 기억되어 있다. 이러한 블록은 게이트 어레이 기 술과 같은 응용 주문형 집적회로(application specific integrated circuits; ASIC) 기술을 이용하여 설 계되므로, 상술된 관계가 미리 인지될 수 있다는 것을 주지하라.

제5도는, 기능 검사 패턴 FTP(ADD) 대 정지  $V_{DD}$  전원 전류  $I_{ddq}$ 의 예를 도시하는데, 기능 검사 패턴 FTP(a), FTP(b), …, FTP(j)가 반도체 소자(1)에 제공되면, 전류  $I_{ddq}$ 는 매우 크다[즉, 비정상(abnormal)].

제어 회로(9)의 제1 동작은 고장 지점이 하나 이상의 트랜지션 블록 내에 존재한다고 판단되므로, 정지  $V_{00}$  전원 전류  $I_{deq}$ 가 정상에서 비정상으로 변경될 때 트랜지션 블록 추출이 수행된다. 제1 동작은 제6도에 도시되어 있다.

먼저, 단계(601)에서, 플래그 FX는 리셋되어(FX=0), 전류 정지 I<sub>dd</sub> 전원 전류 I<sub>ddq</sub>가 정상이라는 것을 나타낸다. FX=0은 정지 Vdd 전원 전류 I<sub>ddq</sub>가 정상이라는 것을 의미하며, FX=1은 정지 V<sub>DD</sub> 전원 전류 I<sub>ddq</sub>가 비정상이라는 것을 의미한다는 것을 주지하라. 또한, 단계(602)에서는, 어드레스 ADD가 클리어된다.

단계(603)에서는, 반도체 소자(1)가 어드레스 ADD의 기능검사 패턴 FTP에 응답하여 새로운 정지  $V_{00}$  전원 전류  $I_{ddd}$ 를 발생할 수 있도록, 소정의 기간이 경과하는 동안 대기한다. 소정의 시간이 경과한 후, 제어

는 단계(604)로 진행한다.

단계(604)에서,  $I_{ddq}$   $I_{R}$ (한정값)가 만족되는 지의 여부가 판정된다.  $I_{ddq} \leq I_{R}$  이면, 정지  $V_{DD}$  전원 전류  $I_{ddq}$ 가 정상이라는 것을 의미하고, 제어는 플래그 FX를 리셋시키는 단계(605)로 진행한다. 반면에,  $I_{ddq}$   $I_{R}$  이면, 정지  $V_{DD}$  전원 전류  $I_{ddq}$ 가 비정상이라는 것을 의미하고, 제어는 단계(606 내지 608)로 진행한다.

단계(606)에서, FX가 0인지의 여부가 판정된다. FX=0이면, 이것은 정지  $V_{00}$  전원 전류  $I_{deq}$ 가 정상에서 비 정상으로 전환되었음을 의미한다. 그러므로, 단계(607)에서, 기능 검사 패턴 FTP(ADD-1)과 기능검사 패턴 FTP 사이의 트랜지션 블록들이 제4도에 도시된 테이블을 참조하여 추출된다. 그 후, 제어는 플래그 FX를 세트시키는 단계(608)로 진행한다. 또한, 단계(606)에서, FX=1이면, 제어는 단계(609)로 바로 진행한다.

단계 (609 및 610)는 ADD가 그것의 최대치 MAX에 도달할 때까지 단계)603에서 608까지)에서의 동작을 반복한다. 따라서, 제7도에 도시된 바와 같이, 제5도의 기능 검사 패턴들 에 FTP(a-1), FTP(b-1), FTP(c-1), FTP(d-1), FTP(f-1), FTP(g-1), FTP(h-1), FTP(i-1) 및 FTP(j-1)에 대하여 기능 검사 패턴들 FTP(a), FTP(b), FTP(c), FTP(d), FTP(e), FTP(f), FTP(g), FTP(h), FTP(i) 및 FTP(j)에 대한 트랜지션 블록들이 구해진다.

단계(611)에서, 공통 트랜지션 블록들은 단계(607)에서 추출된 트랜지션 블록들로부터 추출된다. 예를 들어, 블록  $B_{\rm f}$  는 제7도에 도시된 트랜지션 블록으로부터 추출된다.

그 후, 제6도의 루틴은 단계(612)에 의해 완료된다.

제어 회로(9)의 제2 동작은 고장 지점이 하나 이상의 트랜지션 블록 내에 존재한다고 판단되므로, 정  $V_{00}$  전원 전류  $I_{ddq}$  가 비정상에서 정상으로 전환될 때 트랜지션 블록을 추출하도록 행해진다. 제2 동작은 제8도에 도시되어 있다.

먼저, 단계(801)에서, 플래그 FX는 리셋되어(FX=0), 전류 정지 I<sub>dd</sub> 전원 전류 I<sub>ddq</sub>가 정상이라는 것을 나타낸다. 또한, 단계(802)에서, 어드레스 ADD가 클리어 된다.

단계(803)에서는, 반도체 소자(1)가 어드레스 ADD의 기능 검사 패턴 FTP에 응답하여 새로운 정지  $V_{00}$  전원 전류  $I_{ddq}$ 을 발생하도록 소정의 시간이 경과하기를 기다린다. 소정의 시간이 경과한 후, 제어는 단계(804)로 진행한다.

단계(804)에서,  $I_{ddq} \leq I_R$ 가 만족되는 지의 여부가 판정된다.  $I_{ddq} I_R$  이면 정지  $V_{DD}$  전원 전류  $I_{ddq}$ 가 비정상이라는 것을 의미하고 제어는 플래그 FX를 세트시키는 단계(805)로 진행한다. 반면에,  $I_{ddq} \leq I_R$  이면 정지  $V_{DD}$  전원 전류  $I_{dda}$ 가 정상이라는 것을 의미하고 제어는 단계(806 내지 808)로 진행한다.

단계(806)에서, FX가 1인지의 여부가 판정된다. FX=1이면, 이것은 정지  $V_{00}$  전원 전류  $I_{doq}$ 가 비정상에서 정상으로 전환되었음을 의미한다. 그러므로, 단계(807)에서, 기능 검사 패턴 FTP(ADD-1)과 기능 검사 패턴 FTP(ADD) 사이의 트랜지션 블록들이 제4도에 도시된 테이블을 참조하여 추출된다. 그 후, 제어는 플래그 FX를 세트시키는 단계(808)로 진행한다. 또한, 단계(806)에서, FX=0 이면, 제어는 단계(809)로 바로 진행한다.

단계(809 및 810)는 ADD가 그것의 최대치 MAX에 도달할 때까지 단계(803 내지 808)에서 동작을 반복한다. 따라서, 제5도의 기능검사 패턴들 FTP(a), FTP(b), FTP(c), FTP(d), FTP(f), FTP(g), FTP(h), FTP(i) 및 FTP(j)에 대하여 기능검사 패턴들 FTP(a+1), FTP(b+1), FTP(c+1), FTP(c+1), FTP(g+1), FTP(h+1), FTP(i+1) 및 FTP(j+1)에 대한 트랜지션 블록들이 구해진다.

단계(811)에서, 공통 트랜지션 블록들은 단계(807)에서 추출된 트랜지션 블록 들로부터 추출된다. 예를 들어, 블록  $B_f$  는 트랜지션 블록들로부터 추출된다.

그 후, 제8도의 루틴은 단계(812)에 의해 완료된다.

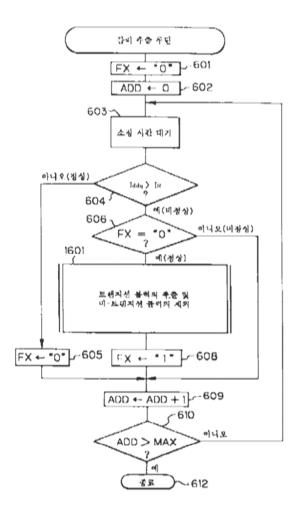

제어 회로(9)의 제3 동작은 고장 지점이 소정의 트랜지션 블록들 내에 포함다고 판단되므로, 정지  $V_{00}$  전원 전류  $I_{dea}$ 가 정상에서 비정상으로, 및 그 반대로 전환될 때 트랜지션 블록을 추출하도록 수행된다. 제3 동작은 제9도에 도시되어 있다.

제9도에서는, 제8도의 단계(806 및 807)를 제6도의 루틴에 추가한다. 이 루틴에 따르며, 제9도의 단계(611)에서 얻은 공통 트랜지션 블록들의 수는 제6도의 단계(611) 또는 제8도의 단계(811)에서 얻은 공통 트랜지션 블록들의 수에 비해 감소될 수 있다.

제어회로(9)의 제4 동작은 정지  $V_{00}$  전원 전류  $I_{dot}$ 가 정상에서 비정상으로 전환될 때 제1 트랜지션 블록들을 추출하도록 행해지고, 정지  $V_{00}$  전원 전류  $I_{dot}$ 가 계속 비정상이면 제2 트랜지션 블록들을 추출하도록 행해진다. 이 경우, 고장 지점은 하나 이상의 제1 트랜지션 블록들 내에 존재하지만, 소정의 제2 틀랜지션 블록들에서 제외된다고 판단된다. 제4 동작은 제10도에 도시되어 있다.

제10도에서, 제6도의 루틴에 단계(1001)가 추가되며, 제6도의 단계(611)는 단계(611')로 변형된다.

즉, ADD가 그것의 최대치 MAX에 도달할 때까지 단계(607)에서의 동작이 반복되면, 제5도의 기능검사 패턴들 FTP(a-1), FTP(b-1), FTP(c-1), FTP(d-1), FTP(f-1), FTP(g-1), FTP(h-1), FTP(i-1) 및 FTP(j-1)에 대하여 기능 검사 패턴들 FTP(a), FTP(b), FTP(c), FTP(d), FTP(e), FTP(f), FTP(g), FTP(h), FTP(i) 및

FTP(j)에 대한 제1 트랜지션 블록들이 구해진다.

또한, 단계(1001)에서의 동작이 ADD가 MAX에 도달할 때까지 반복되면, 제5도의 기능 검사 패턴 FTP(d), FTP(d+1), …, FTP(e-1) 에 대하여 기능 검사 패턴 FTP(d+1), FTP(d+2), …, FTP(e)에 대한 제2 트랜지션 블록들이 구해진다.

더욱이, 단계(611')에서, 공통 트랜지션 블록들은 단계(607)에서 추출된 제1 트랜지션 블록으로부터 추출되며, 단계(1001)에서 추출된 제2 트랜지션 블록들은 공통 트랜지션 블럭들에서 제외된다. 제10도에 따르면, 제10도의 단계(611')에서 얻은 공통 트랜지션 블록들의 수는 제6도의 단계(611)에서 얻은 공통 트랜지션 블록들의 수는 제6도의 단계(611)에서 얻은 공통 트랜지션 블록들의 수에 비해 감소될 수 있다.

제어 회로(9)의 제5 동작은 정지  $V_{00}$  전원 전류  $I_{ddq}$ 가 비정상에서 정상으로 변경될 때 제1 트랜지션 블록들을 추출하도록 행해지며, 정지  $V_{00}$  전원 전류  $I_{ddq}$ 가 계속 비정상이면 제2 트랜지션 블록들을 추출하도록 행해진다. 또한, 이 경우, 고장 지점은 하나 이상의 제1 트랜지션 블록들 내에 존재하지만, 소정의 제2 틀랜지션 블록들에서 제외된다고 판단된다. 제5 동작은 제11도에 도시되어 있다.

제11도에서, 제8도의 루틴에 단계(1101 및 1102)가 추가되며, 제8도의 단계(811)는 단계(811')로 변형된다.

즉, ADD가 그것의 최대치 MAX에 돋달할 때까지 단계(807)에서의 동작이 반복되면, 제5도의 기능검사 패턴들 FTP(a), FTP(b), FTP(c), FTP(e), FTP(f), FTP(g), FTP(h), FTP(i) 및 FTP(j)에 대하여 기능검사 패턴들 FTP(a+1), FTP(b+1), FTP(c+1), FTP(e+1), FTP(f+1), FTP(g+1), FTP(h+1), FTP(i+1) 및 FTP(j+1)에 대한 제1 트랜지션 블록들이 구해진다.

또한, ADD가 MAX에 도달할 때까지 단계(1102)에서의 동작이 반복되면, 제5도의 기능 검사 패턴 FTP(d), FTP(d+1), …, FTP(e-1) 에 대하여 기능 검사 패턴 FTP(d+1), FTP(d+2), …, FTP(e)에 대한 제2 트랜지션 블록들이 구해진다.

더욱이, 단계(811')에서, 공통 트랜지션 블록들은 단계(807)에서 추출된 제1 트랜지션 블록으로부터 추출되며, 단계(1102)에서 추출된 제2 트랜지션 블록들은 공통 트랜지션 블록 들에서 제외된다. 제11도에 따르면, 제11도의 단계(811')에서 구해진 공통 트랜지션 블록들의 주는 제8도의 단계(811)에서 구해진 공통 트랜지션 블록들의 주는 제8도의 단계(811)에서 구해진 공통 트랜지션 블록 들의 수에 비해 감소될 수 있다.

제어 회로(9)의 제6 당작은 정지  $V_{00}$  전원 전류  $I_{ddq}$ 가 정상에서 비정상으로 및 그 반대로 전환될 때 제1 트랜지션 블록들을 추출하도록 행해지며, 정지  $V_{00}$  전원 전류 $I_{ddq}$ 가 계속 비정상이면 제2 트랜지션 블록들을 추출하도록 행해진다. 또한, 이 경우, 고장 지점은 하나 이상의 제1 트랜지션 블록들 내에 존재하지만, 소정의 제2 트랜지션 블록들에서 제외된다고 판단된다. 제6 동작은 제12도에 도시되어 있다.

제12도에서, 제9도의 루틴에 단계(1201)가 추가되며, 제9도의 단계(6110)는 단계(611')로 변형된다.

즉, ADD가 그것의 최대치 MAX에 도달할 때까지 단계(607 및 907)에서의 동작이 반복되면, 제5도의 기능검사 패턴들 FTP(a-1), FTP(b-1), FTP(c-1), FTP(d-1), FTP(f-1), FTP(g-1), FTP(h-1), FTP(i-1) 및 FTP(j-1),에 대하여 기능 검사 패턴들 FTP(a), FTP(b), FTP(c), FTP(d), FTP(f), FTP(g), FTP(h), FTP(i) 및 FTP(j)에 대한 제1 트랜지션 블록들, 그리고 제5도의 기능검사 패턴들 FTP(a), FTP(b), FTP(c), FTP(e), FTP(f), FTP(g), FTP(h), FTP(i) 및 FTP(j)에 대하여 기능 검사 패턴들 FTP(a+1), FTP(b+1), FTP(c+1), FTP(c+1), FTP(c+1), FTP(f+1), FTP(g+1), FTP(i+1) 및 FTP(j+1)에 대한 제1 트랜지션 블록들이 구해진다. 또한, ADD가 MAX에 도달할 때까지 단계(1201)에서의 동작이 반복되면, 제5도의 기능검사 패턴 FTP(d), FTP(d+1), …, FTP(e-1) 에 대하여 기능 검사 패턴 FTP(d+1), FTP(d+2), …, FTP(e)에 대한 제2 트랜지션 블록들이 구해진다.

더욱이, 단계(611')에서는, 공통 트랜지션 블록들이 단계(607 및 807)에서 추출된 제1 트랜지션 블록들에서 제외된다. 제12도에 따르면, 제12도의 단계(611')에서 구해진 공통 트랜지션 블럭으로부터 추출되며, 또한 단계(1001)에서 추출된 제2트랜지션 블럭들이 공통 트랜지션 블록들의 수는 제9도의 단계(611)에서 구해진 공통 트랜지션 블록들의 수에 비해 감소될 수 있다.

제어 회로(9)의 제7 동작은 정지  $V_{00}$  전원 전류  $I_{ddq}$ 가 정상에서 비정상으로 전환될 때 제1 트랜지션 블록들을 추출하도록 행해지며, 정지  $V_{00}$  전원 전류  $I_{ddq}$ 가 계속 정상이면 제2 트랜지션 블록들을 추출하도록 행해진다. 이 경우, 고장 지점은 하나 이상의 제1 트랜지션 블록들 내에 존재하지만, 소정의 제2 트랜지셔 블록들에서 제외된다고 판단된다. 제7동작은 제13도에 도시되어 있다.

제13도에서, 제6도의 루틴에 단계(1301 및 1302)가 추가되며, 제6도의 단계(611)는 단계(611')로 변형된다.

즉, ADD가 그것의 최대치 MAX에 도달할 때까지 단계(607)에서의 동작이 반복되면, 제5도의 기능검사 패턴들 FTP(a-1), FTP(b-1), FTP(c-1), FTP(d-1),FTP(f-1), FTP(g-1), FTP(h-1), FTP(i-1) 및 FTP(j-1), 에 대하여 기능 검사 패턴들 FTP(a), FTP(b), FTP(c), FTP(d), FTP(f), FTP(g), FTP(h), FTP(i) 및 FTP(j)에 대한 제1 트랜지션 블록들이 구해진다.

또한, ADD가 MAX에 도달할 때가지 단계(1302)에서의 동작이 반복되면, 제5도의 기능검사 패턴 FTP(0), FTP(1), …에 대하여 기능 검사 패턴 FTP(1), FTP(2), …에 대한 제2 트랜지션 블록들이 구해진다.

더욱이, 단계(611')에서, 공통 트랜지션 블록들은 단계(607)에서 추출된 제1 트랜지션 블록으로부터 추출되며, 또한 단계(1302)에서 추출된 제2 트랜지션 블록들은 공통 트랜지션 블록들에서 제외된다. 또한 제13도에 따르면, 제13도의 단계(611')에서 구해진 공통 트랜지션 블록들의 수는 제6도의 단계(611)에서 구해진 공통 트랜지션 블록들의 수에 비해 감소될 수 있다.

제어 회로(9)의 제8 동작은 정지  $V_{DD}$  전원 전류  $I_{ddq}$ 가 비정상에서 정상으로 전환될 때 제1 트랜지션 블록

들을 추출하도록 행해지며, 정지  $V_{00}$  전원 전류  $I_{ddq}$ 가 계속 정상이면 제2 트랜지션 블록들을 추출하도록 행해진다. 이 경우, 고장 지점은 하나 이상의 제1 트랜지션 블록들 내에 존재하지만, 소정의 제2 트랜지셔 블록들에서 제외된다고 판단된다. 제8동작은 제14도에 도시되어 있다.

제14도에서, 제8도의 루틴에 단계(1301 및 1402)가 추가되며, 제8도의 단계(811)는 단계(811')로 변형된다

즉, ADD가 그것의 최대치 MAX에 도달할 때까지 단계(807)에서의 동작이 반복되면, 제5도의 기능검사 패턴들 FTP(a), FTP(b), FTP(c), FTP(e), FTP(f), FTP(g), FTP(h), FTP(i) 및 FTP(j)에 대하여 기능검사 패턴들 FTP(a+1), FTP(b+1), FTP(c+1), FTP(e+1), FTP(f+1), FTP(g+1), FTP(h+1), FTP(i+1) 및 FTP(j+1)에 대한 제1 트랜지션 블록들이 구해진다.

또한, ADD가 MAX에 도달할 때가지 단계(1401)에서의 동작이 반복되면, 제5도의 기능검사 패턴 FTP(0), FTP(1), …에 대하여 기능 검사 패턴 FTP(1), FTP(2), …에 대한 제2 트랜지션 블록들이 구해진다.

더욱이, 단계(811')에서, 공통 트랜지션 블록들은 단계(807)에서 추출된 제1 트랜지션 블록으로부터 추출되며, 또한 단계(1401)에서 추출된 제2 트랜지션 블록들은 공통 트랜지션 블록들에서 제왼된다. 또한 제14도에 따르면, 제14도의 단계(811')에서 구해진 공통 트랜지션 블록들의 수는 제8도의 단계(811)에서 구해진 공통 트랜지션 블록들의 수는 제8도의 단계(811)에서 구해진 공통 트랜지션 블록들의 수에 비해 감소될 수 있다.

제어 회로(9)의 제9동작은 정지  $V_{00}$  전원 전류  $I_{odq}$ 가 정상에서 비정상으로 전환될 때 제1 트랜지션 블록들을 추출하도록 행해지며, 정지  $V_{00}$  전원 전류  $I_{odq}$ 가 계속 정상이면 제2 트랜지션 블록들을 추출하도록 행해진다. 또한, 이 경우, 고장 지점은 하나 이상의 제1 트랜지션 블록들 내에 존재하지만, 소정의 제2 트랜지션 블록들에서 제외된다고 판단된다. 제9동작은 제15도에 도시되어 있다.

제15도에서, 제9도의 루틴에 단계(1501)가 추가되며, 제9도의 단계(611)는 단계(611')로 변형된다.

즉, ADD가 그것의 최대치 MAX에 도달할 때까지 단계(607 및 807)에서의 동작이 반복되면, 제5도의 기능검사 패턴들 FTP(a-1), FTP(b-1), FTP(c-1), FTP(d-1), FTP(f-1), FTP(g-1), FTP(h-1), FTP(i-1) 및 FTP(j-1),에 대하여 기능 검사 패턴들 FTP(a), FTP(b), FTP(c), FTP(e), FTP(f), FTP(g), FTP(h), FTP(i) 및 FTP(j)에 대한 제1 트랜지션 블록, 그리고 제5도의 기능검사 패턴들 FTP(a), FTP(b), FTP(c), FTP(e), FTP(f), FTP(g), FTP(h), FTP(i) 및 FTP(j)에 대하여 기능검사 패턴들 FTP(a+1), FTP(b+1), FTP(c+1), FTP(c+1), FTP(e+1), FTP(f+1), FTP(f+1), FTP(h+1), FTP(i+1) 및 FTP(J+1)에 대한 제1 트랜지션 블록들이 구해진다. 또한 ADD가 MAX에 도달할 때까지 단계(1501)에서의 동작이 반복되면, 제5도의 기능검사 패턴 FTP(0), FTP(1), …에 대하여 기능 검사 패턴 FTP(1), FTP(2), …에 대한 제2 트랜지션 블록들이 구해진다.

더욱이, 단계(611')에서, 공통 트랜지션 블록들은 단계(607 및 807)에서 추출된 제1 트랜지션 블록으로 부터 추출되며, 또한 단계(1501)에서 추출된 제2 트랜지션 블록들은 공통 트랜지션 블록들에서 제외된 다. 또한 제15도에 따르면, 제15도의 단계(611')에서 구해진 공통 트랜지션 블록들의 수는 제9도의 단계(611)에서 구해진 공통 트랜지션 블록들의 수에 비해 감소될 수 있다.

제6도, 제8도 및 제9도에 도시된 바와 같이, 상술된 동작들에서, 단계(607 및 807)에서의 트랜지션 블록들의 추출은 단계(611 및 811)에서의 공통 트랜지션 블록들의 추출과 개별적으로 수행된다. 그러나, 이러한 2종류의 추출은 동시에 수행될 수 있다. 그러므로, 제어 회로(9)의 RAM이 효과적으로 사용된다. 예를 들어, 이러한 목적을 위해, 제6도의 루틴은 제16도의 루틴으로 변형된다.

제16도에서, 제6도의 단계(607) 대신에 단계(1601)가 제공되며, 제6도의 단계(611)는 생략된다. 즉, ADD=a 이면, 단계(1601)에서, 기능검사 패턴 FTP(a-1)과 FTP(a)사이의 트랜지션 블록들 B<sub>1</sub>, B<sub>2</sub>, B<sub>6</sub>, B<sub>a</sub>, B<sub>f</sub>, …, B<sub>z</sub> 이 추출되어 제17도에서 화살표 I 로 나타낸 바와 같이, RAM 내에 저장된다. 다음에, ADD=b이면, 단계(1601)에서, 기능검사 패턴 FTP(b-1)과 FTP(b) 사이의 트랜시젼 블록들 B<sub>2</sub>, B<sub>f</sub>, … 이 추출되면, 비-트랜지션 블록들 B<sub>1</sub>, B<sub>6</sub>, B<sub>a</sub>, …, B<sub>z</sub>은 제17도에서 화살표 II로 나타낸 바와 같이, RAM에서 제외된다.

마지막으로, ADD=j이면, 단계(1601)에서, 블록 B<sub>f</sub> 은 제17도에서 화살표 IV로 나타낸 바와 같이, RAM 내 에 남는다

따라서. 고장 블록 B<sub>f</sub> 은 제6도의 루틴에서와 유사한 방식으로 제13도의 루틴에 의해 검출된다.

또한 제10도, 제11도 및 제12도에 도시된 바와 같이, 상술된 동작들에서, 단계(607, 807 및 1201)에서의 트랜지션 블록들의 추출은 단계(611' 및 811')에서 트랜지션 블록들의 추출 및 제외와 개별적으로 수행 된다. 그러나, 이러한 2 종류의 동작들은 동시에 수행될 수 있다. 그러므로, 제어 회로(9)의 RAM이 효과 적으로 사용된다. 예를 들어, 이러한 목적을 위해, 제10도의 루틴은 제18도의 루틴으로 변형된다.

제18도에서, 제10도의 단계(607 및 1001) 대신에 단계(1801 및 1802)가 제공되며, 제10도의 단계(611')는 생략된다. 즉, ADD=a 이면, 단계(1801)에서, 기능 검사 패턴 FTP(a-1)과 FTP(a)사이의 트랜지션 블록들 B<sub>1</sub>, B<sub>2</sub>, B<sub>6</sub>, B<sub>a</sub>, B<sub>f</sub>, …, B<sub>z</sub> 이 추출되어 제19도에서 화살표 I 로 나타낸 바와 같이, RAM 내에 저장된다. 다음에, ADD=b이면, 단계(1801)에서, 기능검사 패턴 FTP(b-1)과 FTP(b) 사이의 트랜지션 블록들 B<sub>2</sub>, B<sub>a</sub>, B<sub>f</sub>, … 이 추출되면, 비-트랜지션 블록들 B<sub>1</sub>, B<sub>6</sub>, B<sub>a</sub>, …, 은 제19도에서 화살표 II로 나타낸 바와 같이, RAM에서 제외된다. 다음에, ADD=d+1이면, 단계(1802)에서, 기능검사 패턴 FTP(d+1)과 FTP(d) 사이의트랜지션 블록들 B<sub>f</sub>, …이 추출되며, 비-트랜지션 블록들 B<sub>i</sub>, …, B<sub>z</sub> 은 제19도에서 화살표 III로 나타난바와 같이 RAM에서 제외된다.

다음에, ADD = c이면, 단계(1601)에서, 기능 검사 패턴 FTP(c-1)과 FTP(c)사이의 트랜지션 블럭들 B<sub>f</sub>,…

이 추출되며, 비-트랜지션 블럭들 B<sub>2</sub>…은 제17도에서 화살표 III로 나타낸 바와 같이, RAM에서 제외된다.

마지막으로, ADD=j이면, 단계(1501)에서, 블록 B<sub>f</sub> 은 제19도에서 화살표 IV로 나타낸 바와 같이, RAM 내 에 남는다.

따라서, 고장 블록 B<sub>f</sub> 은 제6도의 루틴에서와 유사한 방식으로 제15도의 루틴에 의해 검출된다.

더욱이, 제13, 14 및 15도에 도시된 바와 같이, 상술된 동작들에서, 단계(607, 807 및 1501)에서의 트랜지션 블록들의 추출은 단계(611' 및 811')에서 트랜지션 블록들의 추출 및 제외와 개별적으로 수행된다. 그러나, 이러한 2종류의 동작들은 동시에 수행될 수 있다. 그러므로, 제어 회로(9)의 RAM이 효과적으로 사용된다. 예를 들어, 이러한 목적을 위해, 제13도의 루틴은 제20도의 루틴으로 변형된다. 제20도에서, 제13도의 단계(607 및 1302) 대신에 각각 단계(2001 및 2002)가 제공되며, 제13도의 단계(611')은 생략된다.

본 발명은 제21도(a), 제21도(b), 제21도(c)에서 도시된 바와 같은 계층 검사 시스템에 응용될 수 있다. 먼저, 상술된 실시예들 중 하나가 제21도(a)에 도시된 바와 같이 다수의 큰 블록으로 분리되는 반도체 소자에 적용되어, 고장 블록A가 발견된다. 다음에, 상술한 실시예들 중 하나가 제21도(b)에 도시된 다수 의 작은 블록들로 더 분리 되는 고장 블록 A에 적용되어, 고장 서브-블럭 B이 발견된다. 마지막으로, 제21도(c)에 도시된 바와 같이, 고장 지점과 같은 NOR 회로와 같은 기본 논리 회로 C를 발견하도록 논리 시뮬레이션이 수행된다.

본 발명에 따라 상술된 바와 같이, 반도체 소자 내의 공장 블록은 기능 검사 패턴에 응답하여 정지  $V_{00}$  전원 전류를 이용하여 판정되기 때문에, 반도체 소자 내의 고장시점, 즉 고장 블록내의 고장 지점은 대량의 고장 사전을 사용하지 않고도 검출될 수 있다.

#### (57) 청구의 범위

#### 청구항 1

다수의 논리 블록들(B<sub>1</sub>, B<sub>2</sub>, ···)에 의해 형성된 반도체 소자에서 고장 블록을 검출하기 위한 시스템에 있어서, 다수의 기능검사 패턴[FTP(ADD)]과 상기 다수의 기능 검사 패턴에 의해 동작되는 상기 논리 블록들 중 동작가능한 논리 블록들 간의 관계를 저장하는 테이블 수단; 상기 다수의 기능 검사 패턴들을 순 차적으로 발생시켜 상기 다수의 기능 검사 패턴을 상기 반도체 소자로 전송하는 수단; 상기 다수의 기능 검사 패턴들에 의해 생성되어 상기 반도체 소자를 통해 흐르는 전류(I<sub>ddq</sub>)가 소정 값보다 큰지의 여부를 검출하는 수단; 상기 검출 수단에 의해서 검출된 상기 전류에 따라 상기 반도체 소자가 정상에서 비정상으로 전환되었는지의 여부를 판정하는 수단; 상기 반도체 소자가 정상에서 비정상으로 전환될 때마다 상기 테이블 수단에 따라 상기 동작가능한 논리 블럭들 중에서 트랜지셔 블록들(transition blocks)을 추출하는 제1 트랜지션 블록 추출 수단; 및 상기 제1 트랜지션 블록 추출 수단에 의해 추출된 다수 그룹의 상기 트랜지션 블록들 중에서 상기 고장 블록인 적어도 하나의 공통 블록을 추출하는 고장 블록 추출 수단의 포함하는 고장 블록 검출 시스템.

#### 청구항 2

제1항에 있어서, 상기 검출 수단에 의해서 검출된 상기 전류에 따라 상기 반도체 소자가 비정상에서 정 상으로 전환되었는지의 여부를 판정하는 수단; 및 상기 반도체 소자가 비정상에서 정상으로 전환될 때마 다 상기 테이블 수단에 따라 상기 동작가능한 논리 블록들 중에서 트랜지션 블록들을 추출하는 제2 트랜 지션 블록 추출 수단을 더 포함하며, 상기 고장 블록 추출 수단은 상기 제1 및 제2 트랜지션 블록 추출 수단에 의해 추출된 다수 그룹의 상기 트랜지션 블록들 중 상기 고장 블록인 적어도 하나의 공통 블록을 추출하는 고장 블록 검출 시스템.

#### 청구항 3

제1항에 있어서, 상기 검출 수단에 의해서 검출된 상기 전류에 따라 상기 반도체소자가 계속 비정상인지의 여부를 판정하는 수단; 및 상기 반도체 소자가 계속 비정상일 때마다 상기 테이블 수단에 따라 상기 동작가능한 논리 블록들 중에서 트랜지션 블록들을 추출하는 또 다른 트랜지션 블록 추출 수단을 더 포함하며, 상기 고장 블록 추출 수단은 적어도 하나의 공통 블록으로부터 상기 또 다른 트랜지션 블록 추출 수단에 의해 추출된 상기 트랜지션 블록들을 제외시키는 고장 블록 검출 시스템.

#### 청구항 4

제2항에 있어서, 상기 검출 수단에 의해서 검출된 상기 전류에 따라 상기 반도체 소자가 계속 비정상인 지의 여부를 판정하는 수단; 및 상기 반도체 소자가 계속 비정상일 때마다 상기 테이블 수단에 따라 상 기 동작가능한 논리 블럭들 중에서 트랜지션 블록들을 추출하는 제3 트랜지션 블록 추출 수단을 더 포함 하며, 상기 고장 블록 추출 수단은 상기 적어도 하나의 공통된 블록으로부터 상기 제3 트랜지션 블럭 추 출 수단에 의해 추출된 상기 트렌지션 블록들을 제외시키는 고장 블록 검출 시스템.

### 청구항 5

제1항에 있어서, 상기 검출 수단에 의해서 검출된 상기 전류에 따라 상기 반도체 소자가 계속 정상인지의 여부를 판정하는 수단; 및 상기 반도체 소자가 계속 정상일 때마다 상기 테이블 수단에 따라서 상기논리 블록들 중에서 트랜지션 블록들을 추출하는 또 다른 트랜지션 블록 추출 수단을 더 포함하며, 상기고장 블록 추출 수단은 상기 적어도 하나의 공통된 블록으로부터 상기 또 다른 트랜지션 블록 추출 수단에 의해 추출된 상기 트렌지션 블록들을 제외시키는 고장 블록 검출 시스템.

#### 청구항 6

제2항에 있어서, 상기 검출 수단에 의해서 검출된 상기 전류에 따라서 상기 반도체 소자가 계속 정상인 지의 여부를 판정하는 수단; 및 상기 반도체 소자가 계속 정상일 때마다 상기 테이블 수단에 따라서 상 기 동작 가능한 논리 블록들 중에서 트랜지션 블록들을 추출하는 제3 트랜지션 블록 추출 수단을 더 포 함하며, 상기 고장 블록 추출 수단은 상기 적어도 하나의 공통된 블록으로부터 상기 제3 트랜지션 블록 추출 수단에 의해 추출된 상기 트렌지션 블록들을 제외시키는 고장 블록 검출 시스템.

#### 청구항 7

다수의 논리 블록들(B<sub>1</sub>, B<sub>2</sub>, …)에 의해 형성된 반도체 소자에서 고장 블록을 검출하기 위한 시스템에 있어서, 다수의 기능 검사 패턴[FTP(ADD)]과 상기 다수의 기능 검사 패턴에 의해 동작되는 상기 논리 블럭의 관계를 저장하는 테이블 수단; 상기 다수의 기능 검사 패턴을 순차적으로 발생시켜 상기 다수의 기능 검사 패턴을 상기 반도체 소자로 전송하는 수단; 상기 다수의 기능 검사 패턴들에 의해서 생성되어 상기반도체 소자를 통해 흐르는 전류(Idda)가 소정값보다 큰지의 여부를 검출하는 수단; 상기 검출 수단에 의해서 검출된 전류에 따라서 상기 반도체 소자가 정상에서 비정상으로 전환되었는지의 여부를 판정하는 수단; 상기 반도체 소자가 제1 시간 동안 정상에서 비정상으로 전환될 때 상기 테이블 수단에 따라 상기논리 블록들 중에서 제1 트랜지션 블록들을 추출하는 제1 트랜지션 블럭 수출 수단; 및 상기 제1 트랜지션 블록 추출 수단이 상기 제1 트랜지션 블록들을 추출한 후, 상기 반도체 소자가 정상에서 비정상으로 전환될 때 상기 테이블 수단에 따라 상기는리 블록들 중에서 비-트랜지션 블록들을 추출하는 제2 트랜지션 블록 추출 수단을 포함하며, 상기 제2 트랜지션 블록 추출 수단은 상기 제1 트랜지션 블록들로부터 상기 비-트랜지션 블록들을 제외시켜서 상기 제1 트랜지션 블록들에서 상기 고장 블록을 구하는 고장 블록 검출 시스템.

#### 청구항 8

다수의 논리 블록들(B<sub>1</sub>, B<sub>2</sub>, ···)에 의해 형성된 반도체 소자에서 고장 블록을 검출하기 위한 시스템에 있어서, 다수의 기능 검사 패턴[FTP(ADD)]과 상기 다수의 기능 검사 패턴에 의해 동작되는 상기 논리 블럭관계를 저장하는 테이블 수단; 상기 다수의 기능 검사 패턴을 순차적으로 발생시켜 상기 다수의 기능 검사 패턴을 상기 반도체 소자로 전송하는 수단; 상기 다수의 기능 검사 패턴들에 의해서 생성되어 상기반도체 소자를 통해 흐르는 전류(Idda)가 소정값보다 큰 지의 여부를 검출하는 수단; 상기 검출 수단에의해서 검출된 전류에 따라서 상기 반도체 소자가 정상에서 비정상으로 전환되었는지의 여부를 판정하는수단; 상기 반도체 소자가 제1 시간 동안 정상에서 비정상으로 전환되었는지의 여부를 판정하는수단; 상기 반도체 소자가 제1 시간 동안 정상에서 비정상으로 전환될 때 상기 테이블 수단에 따라 상기논리 블록들 중에서 제1 트랜지션 블록들을 추출하는 제1 트랜지션 블럭 수출 수단; 및 상기 제1 트랜지션 블록 추출수단이 상기 제1 트랜지션 블록들을 추출한 후, 상기 반도체 소자가 정상에서 비정상으로 전환될 때 상기 테이블 수단에 따라 상기논리 블록들 중에서 비-트랜지션 블록들을 추출하는 제2 트랜지션 블록 추출 수단을 포함하며, 상기 제2 트랜지션 블록 추출 수단은 상기 제1 트랜지션 블록들로부터 상기 비-트랜지션 블록들을 제외시켜서 상기 제1 트랜지션 블록들에서 상기 고장 블록을 구하는 고장 블록 검출 시스템.

#### 청구항 9

제7항에 있어서, 상기 검출 수단에 의해서 검출된 상기 전류에 따라 상기 반도체 소자가 계속 정상인지의 여부를 판정하는 수단; 및 상기 반도체 소자가 계속 정상일 때마다 상기 테이블 수단에 따라서 상기논리 블록들 중에서 트랜지션 블록들을 추출하는 또 다른 트랜지션 블록 추출 수단을 더 포함하며, 상기제3 트랜지션 블록 추출 수단은 상기 제1 트랜지션 블록 들로부터 상기 제3 트랜지션 블록 추출 수단에 의해 추출된 상기 제2트랜지션 블록들을 제외시키는 고장 블록 검출 시스템.

#### 청구항 10

제7항에 있어서, 상기 검출 수단에 의해서 검출된 상기 전류에 따라 상기 반도체 소자가 계속 정상인지의 여부를 판정하는 수단; 및 상기 반도체 소자가 계속 비정상일 때마다 상기 테이블 수단에 따라서 상기 논리 블록들 중에서 제2 트랜지션 블록들을 추출하는 제3 트랜지션 블록추출 수단을 더 포함하며, 상기 제3 트랜지션 블록 추출 수단은 상기 제1 트랜지션 블록 들로부터 상기 제3 트랜지션 블록 추출 수단에 의해 추출된 상기 제2트랜지션 블록들을 제외시키는 고장 블록 검출 시스템.

#### 청구항 11

제6항에 있어서, 상기 검출 수단에 의해서 검출된 상기 전류에 따라 상기 반도체 소자가 계속 정상인지의 여부를 판정하는 수단; 및 상기 반도체 소자가 계속 정상일 때마다 상기 테이블 수단에 따라서 상기논리 블록들 중에서 제2 트랜지션 블록들을 추출하는 제3 트랜지션 블록추출 수단을 더 포함하며, 상기제3 트랜지션 블록 추출 수단은 상기 제1 트랜지션 블록 들로부터 상기 제3 트랜지션 블록 추출 수단에의해 추출된 상기 제2트랜지션 블록들을 제외시키는 고장 블록 검출 시스템.

#### 청구항 12

제7항에 있어서, 상기 검출 수단에 의해서 검출된 상기 전류에 따라 상기 반도체 소자가 계속 정상인지의 여부를 판정하는 수단; 및 상기 반도체 소자가 계속 정상일 때마다 상기 테이블 수단에 따라서 상기논리 블록들 중에서 제2 트랜지션 블록들을 추출하는 제3 트랜지션 블록추출 수단을 더 포함하며, 상기제3 트랜지션 블록 추출 수단은 상기 제1 트랜지션 블록 들로부터 상기 제3 트랜지션 블록 추출 수단에의해 추출된 상기 제2트랜지션 블록들을 제외시키는 고장 블록 검출 시스템.

### 청구항 13

반도체의 다수의 논리 블록에서 고장 논리 블록을 검출하기 위한 방법에 있어서, (a) 다수의 기능 검사패턴과 상기 다수의 논리 블록들의 세트 간의 관계를 저장하는 단계 - 상기 관계는 상기 다수의 기능 검사 패턴 각각이 실제로 검사하는 상기 다수의 논리 블록들 중 어떤 세트를 정의함 -; (b) 상기 다수의

검사 패턴들 중 하나를 발생하여 대응하는 상기 다수의 논리 블록들의 세트를 검사하는 단계; (c) 상기 다수의 테스트 패턴들중 상기 하나에 의해서 발생된 상기 반도체의 출력 전류를 검출하는 단계; (d) 상기 출력 전류가 임계값 이상인지의 여부를 판정하는 단계; (e) 상기 출력 전류와 상기 임계값 간의 소정의 관계가 충족되는 경우 상기 다수의 논리 블록들의 세트를 추출하는 단계; (f) 상기 다수의 검사 패턴들 모두가 발생될 때까지 단계(b)로 복귀하는 단계 및; (g) 상기 고장 논리 블록으로서, 상기 추출된 모든 다수의 논리 블록들의 세트로부터 적어도 하나의 공통 논리 블록을 추출하는 단계;를 포함하는 고장 논리 블록 검출 방법.

#### 청구항 14

제13항에 있어서, 상기 단계(d)는 상기 출력 전류가 상기 임계값 이상일 때는 상기 출력 전류를 비정상으로 분류하고, 상기 출력 전류가 상기 임계값 이하일 때는 상기 출력 전류를 정상으로 분류하는 단계를 더 포함하고, 단계 (e)의 상기 소정의 관계는, (i) 정상 분류로부터 비정상분류로의 전환, (ii) 비정상분류로부터 정상분류로의 전환, (iii) 정상 분류로부터 비정상분류로의 전환 및 그 역전환 (iv) 계속 비정상 분류, 및 (v) 계속 정상 분류 중 적어도 하나인 고장 논리 블록 검출 방법.

#### 도면

#### 도면1a

## 도면1b

| LN 1 | N 2 | оит |

|------|-----|-----|

| Н    | Н   | L,  |

| Н    | L   | Н   |

| L    | Н   | н   |

| L    | L   | н   |

## 도면2a

# 도면2b

| IN 1 | I N 2 | OUT |  |

|------|-------|-----|--|

| Н    | н     | н   |  |

| н    | L     | н   |  |

| L    | Н     | н   |  |

| L    | L     | н   |  |

# *도면3*

# 도면4

| FTP(ADD) | 동작 가능한 유러                                                                            |      |  |

|----------|--------------------------------------------------------------------------------------|------|--|

| FTP(0)   | B1, B3, B6, Bd. Br                                                                   | 8.   |  |

| FTP(1)   | Bs. Br. Bg. 8k. Bk                                                                   | . D. |  |

| FTP(2)   | B1, B3, B6, Ba, B2,                                                                  | . 8∗ |  |

|          |                                                                                      |      |  |

| FTP(MAX) | B <sub>3</sub> , B <sub>6</sub> , B <sub>8</sub> , B <sub>9</sub> , B <sub>3</sub> , | . 8. |  |

도면7

|        | Bı | 82 |     | Br |   | Bz |

|--------|----|----|-----|----|---|----|

| FTP(a) | 0  | 0  |     | 0  |   | 0  |

| FTP(b) | _  | 0  |     | 0  |   |    |

| FTP(c) | _  |    |     | 0  |   | _  |

| l I    |    |    | - ! |    |   |    |

| 1      |    |    | i   |    | 1 |    |

| ī      |    |    | - j |    |   |    |

| FTP(j) | _  | -  |     | 0  |   | -  |

|        | 추출된 불러                                                                               |              |

|--------|--------------------------------------------------------------------------------------|--------------|

| -      |                                                                                      |              |

| FTP(a) | B1, B2, B6, B6, B1, Bz                                                               | <b>→</b> - [ |

| FTP(b) | B <sub>1</sub> , B <sub>2</sub> , B <sub>6</sub> , B <sub>6</sub> , B <sub>7</sub> , | <b>→</b> Ⅱ   |

| FTP(c) | , -,   ,   , Br,                                                                     | <b>→</b> I   |

|        |                                                                                      |              |

| :      | :                                                                                    |              |

| FTP(j) |                                                                                      | <u>→</u> 1∆  |

|        |                                                                                      |              |