(19) **日本国特許庁(JP)**

# (12) 特 許 公 報(B2)

(11) 特許番号

特許第5607985号 (P5607985)

(45) 発行日 平成26年10月15日(2014.10.15)

(24) 登録日 平成26年9月5日(2014.9.5)

(51) Int.Cl. F 1

**HO2M 3/155 (2006.01)** HO2M 3/155 P **HO2M 7/12 (2006.01)** HO2M 7/12 Q

請求項の数 16 (全 18 頁)

(21) 出願番号 特願2010-95915 (P2010-95915) (22) 出願日 平成22年4月19日 (2010.4.19) (65) 公開番号 特開2011-229255 (P2011-229255A)

(43) 公開日 平成23年11月10日 (2011.11.10) 審査請求日 平成25年2月14日 (2013.2.14) ||(73)特許権者 302062931

ルネサスエレクトロニクス株式会社

神奈川県川崎市中原区下沼部1753番地

||(74)代理人 100080001

弁理士 筒井 大和

|(72)発明者 鮎川 一仁

神奈川県川崎市中原区下沼部1753番地

ルネサスエレクトロニクス株式会社内

(72) 発明者 笠井 宣利

神奈川県川崎市中原区下沼部1753番地 ルネサスエレクトロニクス株式会社内

(72) 発明者 飯島 大輔

神奈川県川崎市中原区下沼部1753番地 ルネサスエレクトロニクス株式会社内

最終頁に続く

(54) 【発明の名称】電源装置および半導体装置

### (57)【特許請求の範囲】

## 【請求項1】

交流電圧を直流電圧に変換する電源装置であって、

出力端子及びグラウンド端子と、

前記交流電圧が入力されるダイオードブリッジと、

前記ダイオードブリッジの出力に接続されたインダクタと、

前記インダクタにそのアノードが電気的に接続され、前記出力端子にそのカソードが電気的に接続されたダイオードと、

前記出力端子およびグラウンド端子間に電気的に接続された容量と、

前記ダイオードのアノードと前記グラウンド端子間に電気的に接続されたスイッチと、

前記出力端子と前記グラウンド端子間の電圧を分圧する分圧回路と、

前記分圧回路の出力電圧と基準電圧との差を増幅する誤差増幅器と、

前記誤差増幅器の出力を電流に変換する発振周波数制御回路と、

前記発振周波数制御回路の出力電流から三角波を出力する三角波発生回路と、

前記三角波発生回路の出力する三角波に基づき前記スイッチを開閉する PWM制御回路を含み、

前記三角波発生回路は、キャパシタを含み、前記キャパシタの充放電によって三角波を 出力し、

前記三角波発生回路は、2つの出力を持つ第1のカレントミラー回路及び1つの出力を 持つ第2のカレントミラー回路を含み、

20

前記第2のカレントミラー回路の電流出力は前記第1のカレントミラー回路の一方の電流出力を複製するものであり、

前記第1のカレントミラー回路の他方の電流出力と前記第2のカレントミラー回路の電流出力とをMOSFETを介して接続し、

前記MOSFETは、前記MOSFET及び前記第2のカレントミラー回路の電流出力の接続点に接続された前記キャパシタの充放電を行うことを特徴とする電源装置。

#### 【請求項2】

請求項1記載の電源装置において、

前記三角波発生回路は定電圧が入力されるオペアンプを有し、

前記オペアンプは、前記キャパシタ、前記第2のカレントミラー回路の電流出力及び前記MOSFETの接続点の電圧と前記定電圧を対比し、前記MOSFETを開閉することで前記キャパシタの充放電を行うことを特徴とする電源装置。

#### 【請求項3】

請求項2記載の電源装置において、

前記第2のカレントミラー回路の電流出力、前記MOSFET及び前記オペアンプの接続点の電圧を前記三角波として出力することを特徴とする電源装置。

#### 【請求項4】

請求項1記載の電源装置において、

前記発振周波数制御回路はトランジスタを有し、前記トランジスタのゲート端子に前記誤差増幅器の出力が入力されることを特徴とする電源装置。

#### 【請求項5】

請求項4記載の電源装置において、

前記トランジスタのコレクタ端子に第3のカレントミラー回路が接続され、前記第3のカレントミラー回路の電流出力が前記発振周波数制御回路の出力となることを特徴とする電源装置。

## 【請求項6】

請求項4記載の電源装置において、

前記発振周波数制御回路は更に定電流源を有し、

前記トランジスタのコレクタ端子に第4のカレントミラー回路が接続され、

前記定電流源の出力電流から前記第4のカレントミラー回路の出力を引いた電流が前記 発振周波数制御回路の出力電流となることを特徴とする電源装置。

## 【請求項7】

請求項6記載の電源装置において、

前記発振周波数制御回路は更に前記トランジスタのエミッタ端子に接続されたクランプ 回路を有することを特徴とする電源装置。

## 【請求項8】

請求項1記載の電源装置において、

該電源装置はインターリーブ電流連続モード方式であって、

前記PWM制御回路は各系統のスイッチをそれぞれ制御することを特徴とする電源装置

## 【請求項9】

電源装置の力率改善用の半導体装置であって、

前記電源装置の出力電圧に応じて変化する電圧が入力され基準電圧との差を増幅する誤差増幅器と、

前記誤差増幅器の出力を電流に変換する発振周波数制御回路と、

前記発振周波数制御回路の出力電流から三角波を出力する三角波発生回路と、

前記三角波発生回路の出力する三角波に基づき前記電源装置のスイッチを開閉するPWM制御回路とを含み、

前記三角波発生回路は、キャパシタを含み、前記キャパシタの充放電によって三角波を出力し、

10

20

30

40

(3)

前記三角波発生回路は、さらに、2つの出力を持つ第1のカレントミラー回路及び1つ の出力を持つ第2のカレントミラー回路を含み、

前記第2のカレントミラー回路の電流出力は前記第1のカレントミラー回路の一方の電流出力を複製するものであり、

前記第1のカレントミラー回路の他方の電流出力と前記第2のカレントミラー回路の電流出力とをMOSFETを介して接続し、

前記MOSFETは、前記MOSFET及び前記第2のカレントミラー回路の電流出力の接続点に接続された前記キャパシタの充放電を行うことを特徴とする半導体装置。

### 【請求項10】

請求項9記載の半導体装置において、

前記三角波発生回路は定電圧が入力されるオペアンプを有し、

前記オペアンプは、前記キャパシタ、前記第2のカレントミラー回路の電流出力及び前記MOSFETの接続点の電圧と前記定電圧を対比し、前記MOSFETを開閉することで前記キャパシタの充放電を行うことを特徴とする半導体装置。

## 【請求項11】

請求項10記載の半導体装置において、

前記第2のカレントミラー回路の電流出力、前記MOSFET及び前記オペアンプの接続点の電圧を前記三角波として出力することを特徴とする半導体装置。

#### 【請求項12】

請求項9記載の半導体装置において、

前記発振周波数制御回路はトランジスタを有し、前記トランジスタのゲート端子に前記誤差増幅器の出力が入力されていることを特徴とする半導体装置。

### 【請求項13】

請求項12記載の半導体装置において、

前記トランジスタのコレクタ端子に第3のカレントミラー回路が接続され、前記第3のカレントミラー回路の電流出力が前記発振周波数制御回路の出力となることを特徴とする半導体装置。

### 【請求項14】

請求項12記載の半導体装置において、

前記発振周波数制御回路は更に定電流源を有し、

前記トランジスタのコレクタ端子に第4のカレントミラー回路が接続され、

前記定電流源の出力電流から前記第4のカレントミラー回路の出力を引いた電流が前記 発振周波数制御回路の出力電流となることを特徴とする半導体装置。

## 【請求項15】

請求項14記載の半導体装置において、

前記発振周波数制御回路は更に前記トランジスタのエミッタ端子に接続されたクランプ回路を有することを特徴とする半導体装置。

### 【請求項16】

請求項9記載の半導体装置において、

該電源装置はインターリーブ電流連続モード方式であって、

前記PWM制御回路は各系統のスイッチをそれぞれ制御することを特徴とする半導体装置。

## 【発明の詳細な説明】

### 【技術分野】

## [0001]

本発明は、電源装置およびそれに用いられる半導体装置、特に力率改善回路を有する電源装置に関する。

## 【背景技術】

#### [0002]

サーバ、家電などに用いられる電源装置においては、交流(AC)を直流(DC)に変

10

20

\_\_\_

30

40

換する際に、入力電圧と入力電流の波形の違いによって無効な電力が発生するという問題がある。また、入力電圧と入力電流の波形の違いによって高調波電流が発生し、他の電気機器などにノイズの影響を与えるといった問題も懸念されている。この問題の対策として、入力電流の波形を入力電圧と同様な位相や波形に整形する力率改善(PFC(Power Factor Correction))が行われている。

### [0003]

特開平10-174428号公報(特許文献1)、特開2009-261042号公報(特許文献2)および特開2007-195282号公報(特許文献3)には、力率改善回路の例が記載されている。

【先行技術文献】

10

20

30

40

50

## 【特許文献】

[0004]

【特許文献 1 】特開平 1 0 - 1 7 4 4 2 8 号公報

【特許文献2】特開2009-261042号公報

【特許文献3】特開2007-195282号公報

【発明の概要】

【発明が解決しようとする課題】

[0005]

電源装置においては、スイッチとして用いられるMOSFETなどのターンON/OFF時のゲート駆動電流やドレイン電圧やドレイン電流の変化に伴う損失(スイッチング損失)が発生し、これによって電力変換効率の低下が問題となる。スイッチング損失は、スイッチング周波数が低いほど、すなわち単位時間当たりのスイッチング回数が少ないほど損失が小さくなる。しかし単純に単位時間当たりのスイッチング回数を少なくすると、電源装置のインダクタや出力平滑容量を大きくする必要があり、実装面積の増大につながることから実用的ではない。

[0006]

本発明の目的の一つは、力率改善回路を有する電源装置およびそれに用いられる半導体装置の特性を向上させる手段を提供することにある。

[0007]

本発明の前記並びにその他の目的と新規な特徴は、本明細書の記述及び添付図面から明らかになるであろう。

【課題を解決するための手段】

【0008】

本願において開示される発明のうち、代表的なものの概要を簡単に説明すれば、次の通 りである。

[0009]

本発明の代表的な実施の形態に関わる電源装置は、出力端子の電圧を分圧する分圧回路の出力電圧と第1の基準電圧との差を増幅する誤差増幅器と、誤差増幅器の出力を電流に変換する発振周波数制御回路と、この発振周波数制御回路の出力電流から三角波を出力する三角波発生回路と、三角波発生回路の出力する三角波に基づきスイッチを開閉するPWM制御回路と、を含むPFCコントローラを有することを特徴とする。

**[** 0 0 1 0

この電源装置において、三角波発生回路はキャパシタを含み、キャパシタの充放電によって三角波を出力することを特徴としても良い。

[0011]

この電源装置において、キャパシタには2つの出力を持つ第1のカレントミラー回路及び1つの出力を持つ第2のカレントミラー回路を含み、この第2のカレントミラー回路の電流出力は第1のカレントミラー回路の一方の電流出力を複製するものであり、第1のカレントミラー回路の他方の電流出力と第2のカレントミラー回路の電流出力とをMOSFETを介して接続し、このMOSFETはMOSFET及び第2のカレントミラー回路の

電流出力の接続点に接続されたキャパシタの充放電を行うことを特徴としても良い。

#### [0012]

この電源装置において、三角波発生回路は定電圧が入力されるコンパレータを有し、このコンパレータは、キャパシタ、第2のカレントミラー回路の電流出力及びMOSFET の接続点の電圧とこの定電圧を対比し、MOSFETを開閉することでキャパシタの充放電を行うことを特徴としても良い。

#### [0013]

この電源装置において、第2のカレントミラー回路の電流出力、MOSFET及びコンパレータの接続点の電圧を三角波として出力することを特徴としても良い。

#### [0014]

この電源装置において、発振周波数制御回路はトランジスタを有し、トランジスタのゲート端子に誤差増幅器の出力が入力されることを特徴としても良い。

#### [0015]

この電源装置において、トランジスタのコレクタ端子に第3のカレントミラー回路が接続され、第3のカレントミラー回路の電流出力が発振周波数制御回路の出力となることを特徴としても良い。

#### [0016]

この電源装置において、発振周波数制御回路は更に定電流源を有し、トランジスタのコレクタ端子に第4のカレントミラー回路が接続され、定電流源の出力電流から第4のカレントミラー回路の出力を引いた電流が発振周波数制御回路の出力電流となることを特徴としても良い。

#### [0017]

この電源装置において、発振周波数制御回路は更にトランジスタのエミッタ端子に接続されたクランプ回路を有することを特徴としても良い。

#### [0018]

この電源装置において、該電源装置はインターリーブ電流連続モード方式であって、PWM制御回路は各系統のスイッチをそれぞれ制御することを特徴としても良い。

#### [0019]

本発明の代表的な実施の形態に関わる電源装置は、出力電流測定用抵抗と、この出力電流測定用抵抗の電圧を増幅する電位差増幅器と、電位差増幅器の出力電流から三角波を出力する三角波発生回路と、三角波発生回路の出力する三角波に基づきスイッチを開閉するPWM制御回路を含むPFCコントローラを有することを特徴とする。

#### 【発明の効果】

## [0020]

力率改善回路を有する電源装置およびそれに用いられる半導体装置の特性を向上させる ことができる。

## 【図面の簡単な説明】

### [0021]

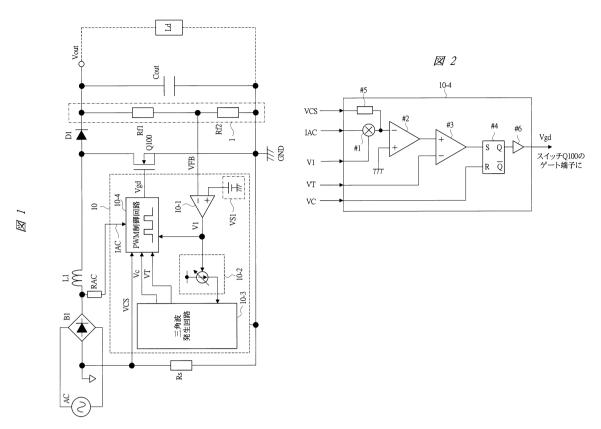

【図1】本発明の第1の実施の形態に関わる電源装置の構成を表す回路図である。

【図2】PFCコントローラの構成を表す回路図である。

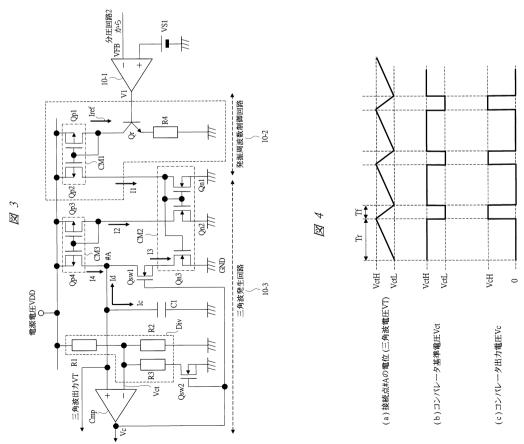

【図3】本発明の第1の実施の形態に関わる発振周波数制御回路、三角波発生回路の具体的構成を表す回路図である。

【図4】本発明の第1の実施の形態に関わる、三角波発生回路の動作説明図である。

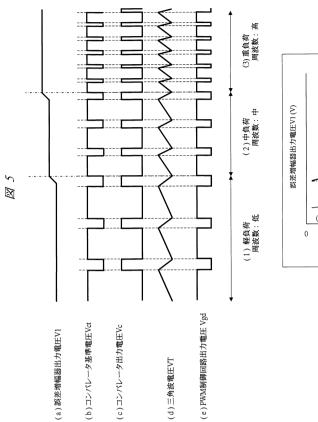

【図5】発振周波数制御回路の周波数変化を説明するためのグラフである。

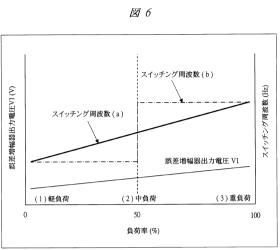

【図 6 】負荷率と誤差増幅器の出力電圧及びスイッチング周波数の関係を示すグラフである。

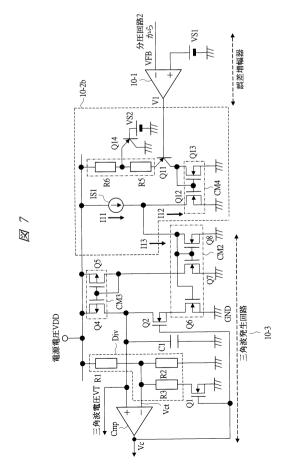

【図7】本発明の第2の実施の形態に関わる発振周波数制御回路、三角波発生回路の具体 的構成を表す回路図である。

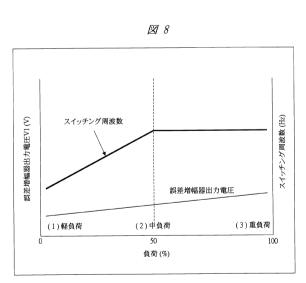

【図8】本発明の第2の実施の形態に関わる発振周波数制御回路の周波数変化を説明する ためのグラフである。 10

20

30

40

【図9】本発明の第2の実施の形態に関わる発振周波数制御回路を適用したPFCコントローラの出力を表すグラフである。

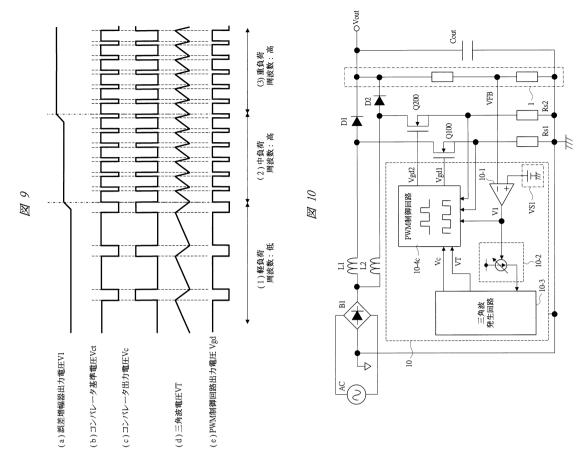

【図10】本発明の第3の実施の形態に関わる電源装置の構成を表す回路図である。

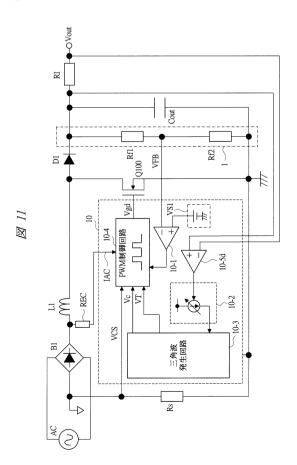

【図11】本発明の第4の実施の形態に関わる電源装置の構成を表す回路図である。

【発明を実施するための形態】

[0022]

以下の実施の形態においては、便宜上その必要があるときは、複数のセクションまたは 実施の形態に分割して説明する。しかし、特に明示した場合を除き、それは互いに無関係 なものではなく、一方は他方の一部又は全部の変形例、詳細、補足説明などの関係にある 。また、以下の実施の形態において、要素の数など(個数、数値、量、範囲などを含む) に言及する場合、特に明示した場合及び原理的に明らかに特定の数に限定される場合など を除き、その特定の数に限定されるものでなく、特定の数以上でも以下でも良い。

[0023]

さらに、以下の実施の形態において、その構成要素は、特に明示した場合及び原理的に明らかに必須であると考えられる場合を除き、必ずしも必須のものでないことは言うまでもない。また、実施の形態の各機能ブロックを構成する回路素子は、特に制限されないが、CMOS(相補型電界効果トランジスタ)等の集積回路技術によって、単結晶シリコンのような半導体基板上に形成される。なお、実施の形態で、MOSFET(Metal Oxide Semiconductor Field Effect Transistor)と記載した場合、ゲート絶縁膜として非酸化膜を除外するものではない。また、MOSFETのゲート長およびゲート幅をそれぞれしおよびWという記号を用いて表す。W/Lはゲート長に対するゲート幅の比を表している。

[0024]

以下、図を用いて本発明の実施の形態を説明する。

[0025]

(第1の実施の形態)

< < 電源装置概略 > >

図1は、第1の実施の形態に関わる電源装置の構成を表す回路図及びこの電源装置に接続される負荷 L d を示している。

[0026]

この電源装置は、ダイオードブリッジB1、インダクタL1(昇圧インダクタ、コイル、昇圧コイル)、ダイオードD1、分圧回路1、出力平滑容量Cout、電流検出抵抗Rs、抵抗RACの他に、PFCコントローラ10(PFCコントローラIC、力率改善コントローラ、力率改善コントローラIC、半導体装置)、スイッチQ100を含む。このようにPFCコントローラを用いて力率改善対策を行っている電源装置はアクティブフィルタ方式とも呼ばれる。なお、ダイオードブリッジB1は4個のダイオードをブリッジ状に接続した全波整流回路であるが、図1のように省略した形で表している。

[0027]

インダクタL1は、入力電圧(ダイオードブリッジB1の出力電圧)の昇圧のために用いられる。インダクタL1にはスイッチQ100が接続されている。スイッチQ100としては、MOSFET又はIGBT(Insulated Gate Bipolar Transistor)等の素子が使用される。ダイオードD1は、電流の流れを一方向に制御するための整流用の受動素子である。

[0028]

分圧回路1は抵抗Rf1及びRf2からなる。出力端子の電圧Voutとグラウンドレベルとの電位差を分圧し、電圧情報VFB(=Vout×Rf2/(Rf1+Rf2))としてPFCコントローラ10に出力する。

[0029]

電流検出抵抗Rsは、ダイオードブリッジB1と接地電位間の電圧(電流情報出力VCS)を検出するための接地抵抗である。

10

20

30

40

#### [0030]

電流検出抵抗RACは電流出力情報IACを検出するための抵抗である。電流検出抵抗RACの一端はダイオードブリッジB1とインダクタL1の接続点に接続され、他端はPWM制御回路10-4中の掛算器#1に入力される。

## [0031]

電流検出情報IACは電流検出抵抗RACの抵抗値と電流検出抵抗RACの両端の電位差で決定される電圧である。

## [0032]

PFCコントローラ10は、電圧情報VFB及び電流情報出力VCSを入力として、スイッチQ100のスイッチングを行う制御回路である。

[0033]

本実施の形態のPFCコントローラ10は、誤差増幅器10-1、発振周波数制御回路10-2、三角波発生回路10-3、PWM制御回路10-4を含む。特に限定されるわけではないが、PFCコントローラ10を構成するこれらの回路は一つの半導体チップ(半導体基板)内に形成されている。

[0034]

誤差増幅器10-1は、分圧回路1の出力電圧(電圧情報VFB)と基準電圧VS1の差分を増幅するオペアンプである。オペアンプのゲインをAとすると、この誤差増幅器10-1の出力電圧V1は

$V 1 = A \times (V S 1 - V F B)$

で表される。電源装置に接続される負荷 L d が重い場合(言い換えれば負荷 L d での消費電力が大きい場合)、出力電圧 V o u t が低下し V F B が低くなる。このため、 V 1 は高くなる。逆に、電源装置に接続される負荷が軽い場合(言い換えれば負荷 L d での消費電力が小さい場合)、 V 1 は低くなる。すなわち、負荷 L d に応じて誤差増幅器 1 0 - 1 の出力電圧 V 1 は負荷 L d に応じて連続的に変化することが一つの特徴である。

[0035]

発振周波数制御回路 1 0 - 2 は、誤差増幅器 1 0 - 1 の出力電圧 V 1 に基づき内部で有する定電流源の出力を調整し、三角波発生回路 1 0 - 3 を制御する制御回路である。

[0036]

三角波発生回路10-3は、PWM制御回路10-4に対して三角波(ランプ波)電圧 VTを出力する三角波発生回路である。

**[** 0 0 2 7 **]**

PWM制御回路10-4は、スイッチQ100のOn(導通状態)/Off(非導通状態)を行うため、スイッチQ100のゲート端子に入力される信号のパルス幅を変化させる制御回路である。

[0038]

スイッチQ100がOnの時にインダクタL1にエネルギーが蓄積され、Offのときに入力電圧とインダクタL1のエネルギーが加算される。そして、このエネルギーを電流として、ダイオードD1を介して、出力平滑容量Coutに供給する。これによって入力電圧を昇圧することができる。また、このスイッチQ100のOn/Off比(デューティ比)を調整することで出力電圧Voutの値を調整することができる。

[0039]

< < P W M 制御回路 > >

図2は、このPWM制御回路10-4の構成を表す回路図である。

[0040]

この P W M 制御回路 1 0 - 4 は、掛算器 # 1、誤差増幅器 # 2、コンパレータ # 3、フリップフロップ # 4、抵抗 # 5、バッファ # 6 を含んでいる。

[0041]

掛算器(乗算器)#1は、誤差増幅器10-1の出力電圧V1と電流検出抵抗RACの

20

10

30

40

出力電圧を掛け合わせ、その積に比例する電圧を出力するアナログ乗算器である。

#### [0042]

誤差増幅器 # 2 は、掛算器の出力と接地電圧との誤差を増幅する誤差増幅器である。この際、誤差増幅器 # 2 に入力される掛算器の出力は抵抗 # 5 を介して電流情報出力 V C S が結合される。これにより、抵抗 R S を介して抵抗 # 5 にかかる電圧によって誤差増幅器 # 2 に帰還がかかる。

#### [0043]

コンパレータ#3は、誤差増幅器#2の出力電圧と、三角波発生回路10-3の出力する三角波電圧VTを対比しその誤差を出力する比較器である。

#### [0044]

フリップフロップ#4は、スイッチQ100のOn/Off制御端子(ゲート端子)を駆動するためのRSフリップフロップ回路である。フリップフロップ#4のセット端子には上記コンパレータ#3の出力が「1」になることで1を出力し、フリップフロップ#4のリセット端子に入力されるリセットパルスが入力される(=リセット端子が「1」になる)ことでフリップフロップ#4は「0」を出力する。

#### [0045]

バッファ#6は、スイッチQ100のOn/Off制御端子を駆動可能なように、所定の範囲の入力電圧に対して線形の出力電圧Vgdを出力するアナログバッファ回路である。この出力電圧Vgdは誤差増幅器10-1の出力電圧V1に応じて連続的に変化する。

## [0046]

< < 発振周波数制御回路および三角波発生回路 > >

図3は、第1の実施の形態に関わる発振周波数制御回路10-2、三角波発生回路10-3の具体的構成を表す回路図である。

#### [0047]

発振周波数制御回路 1 0 - 2 は、抵抗 R 4 、トランジスタ Q r 及びカレントミラー回路 C M 1 を構成する P チャネル型の M O S F E T Q p 1 と Q p 2 より構成される。

#### [0048]

トランジスタQrはエミッタフォロワ出力となっている。トランジスタQrは、そのゲート端子に印加される電圧(=誤差増幅器10-1の出力電圧)によって抵抗R4に流れる電流及び参照電流Irefを調整する。トランジスタQrとしてはバイポーラトランジスタまたはMOSFETが使用される。

## [0049]

## [0050]

三角波発生回路10-3は入力電流(図上ではI1)を三角波発生回路10-3の主動作部に引き込むためのカレントミラー回路CM2及びカレントミラー回路CM3を含む。

### [0051]

カレントミラー回路 CM2 はN チャネル型のMOSFETQn1、<math>Qn2、Qn3から構成される。また、カレントミラー回路 CM3 はP チャネル型のMOSFETQp3、Qp4 から構成される。

## [0052]

カレントミラー回路 C M 2 の M O S F E T Q n 1 のドレイン端子には、発振周波数制御回路 1 0 - 2 の出力電流 I 1 が入力される。この電流 I 1 に応じて、M O S F E T Q n 2 に電流 I 2、M O S F E T Q n 3 に電流 I 3 が流れる。電流 I 1 と I 2 の比は、M O S F E T Q n 1 および Q n 2 のそれぞれのW / L の比によって決定される。同様に電流 I 1 と I 3 の比は M O S F E T Q n 1 および Q n 3 のそれぞれのW / L の比によって決定される。さらに、上記の電流 I 2 に応じて、M O S F E T Q p 4 に電流 I 4 が流れる。電流 I 2

10

20

30

40

10

20

30

40

50

とI4の比は、MOSFETQp3及びQp4のそれぞれのW/Lの比によって決定される。

## [0053]

MOSFETQp4のドレイン端子とMOSFETQn3のドレイン端子はMOSFETQsw1を介して電気的に接続される。MOSFETQp4とMOSFETQsw1の接続点#Aの電圧がコンパレータCmpに入力される。また、接続点#AにはキャパシタC1が接続されている。後述するように、キャパシタC1を用いて電化を蓄積及び放電を繰り返すことで、接続点#Aの電圧を変化させ、三角波電圧VTを生成する。

### [0054]

MOSFETQsw1は、MOSFETQp4のドレイン端子とMOSFETQn3との電気的な接続を切り替えるスイッチである。後述するコンパレータCmpの出力電圧VcがMOSFETQsw1のゲート端子に入力される。

#### [0055]

MOSFETQsw1がOff(非導通状態)の時には、MOSFETQp4を流れる電流I4の大部分はキャパシタC1方面へ流れこむ。これは接続点#Aに接続されるコンパレータCmpなどの回路がハイインピーダンスとみなされるからである。よって、キャパシタC1に流れ込む電流をIcとすればI4 Icの関係となる。この電流Icにより、キャパシタC1に電化が蓄えられ、接続点#Aの電圧(三角波電圧VT)が上昇する。

## [0056]

一方、MOSFETQsw1がOn(導通状態)の時、キャパシタC1に蓄積された電荷がMOSFETQsw1及びQn3を介してグラウンドGNDに流れる。MOSFETQp4から接続点#Aに流れる電流をI4、キャパシタC1から接続点#Aに流れる電流をId、MOSFETQsw1及びQn3を流れる電流をI3とすれば、

#### Id = I3 - I4

の関係が成り立つ。ここで、カレントミラー回路 CM3 においては電流 I4 の値は 0 にならないため、キャパシタ C1 に蓄積された電荷を放電するためには、電流 I3 の値を電流 I4 の値より大きくする必要がある。一例として、電流 I1 、I2 および I4 の値が同程 度となるように MOSFETQn1、Qn2、Qp3 および Qp4 の W/L が設定されている場合を考える。この場合、MOSFETQn1のW/L に対し MOSFETQn3の W/L を大きくし、電流 I3 の値を電流 I1 の値よりも大きくすることができる。

## [0057]

すなわち、電流 I 3 > 電流 I 4 とすることで、キャパシタ C 1 に蓄積された電荷が放電され、これに伴い、接続点 # A の電位(三角波電圧 V T ) が低下する。

## [0058]

抵抗 R 1 、 R 2 、 R 3 からなる分圧回路 D i v はコンパレータ C m p の基準電圧 V c t を生成する分圧回路である。

### [0059]

N チャネル型の M O S F E T Q s w 2 は、抵抗 R 2 と R 3 を並列接続するかを決定するスイッチである。 M O S F E T Q s w 2 が O f f (非導通状態)の時、基準電圧 V c t は電源電圧 V D D を抵抗 R 1 と R 2 で分圧した値 V c t H = V D D x R 2 / (R 1 + R 2)となる。一方、 M O S F E T Q s w 2 が O n (導通状態)となると、抵抗 R 2 と R 3 が並列接続され、基準電圧 V c t の値は、 V c t L = V D D x R 2 R 3 / (R 1 + R 2)(R 2 + R 3)に低下する。ここで、電源電圧 V D D の一例としては、 5 V 程度が用いられる

## [0060]

コンパレータCmpは、基準電圧Vct及び接続点#Aの電圧を比較するためのコンパレータである。コンパレータCmpは、接続点#Aの電圧が基準電圧Vctより低い時にはLowレベルの信号(電圧0)を出力し、高い時にはHighレベルの電圧(電圧VcH)を出力する。コンパレータCmpの出力電圧Vcによって、MOSFETQsw1お

10

20

30

40

50

よびMOSFETQsw2のOn/Offを制御する。

### [0061]

< < 三角波発生回路動作 > >

図3および図4を用いて、接続点#Aの電圧(三角波電圧VT)の変化を説明する(初期状態としてMOSFETQsw1およびQsw2がOff、基準電圧Vctが上述のVctHの場合を考える)。

#### [0062]

(1) MOSFETQsw1がOffの時、キャパシタC1に電流Icが流れ、電荷が蓄積されることで接続点#Aの電圧が上昇する(Trの期間)。

#### [0063]

(2)接続点#Aの電圧が上述の基準電圧VctHに到達すると、コンパレータCmpの出力電圧VcはHigh(電圧VcH)となる。

#### [0064]

(3)コンパレータCmpの出力電圧VcがHighとなると、MOSFETQsw1がOnになり、キャパシタC1から電荷が放電され、接続点#Aの電圧が下降する。さらに、MOSFETQsw2がOnとなり、基準電圧Vctは上述のVctLとなる(Tfの期間)。

#### [0065]

(4)接続点#Aの電圧が基準電圧VctLまで下降すると、コンパレータCmpの出力電圧VcはLow(電圧0)となる。

#### [0066]

(5) コンパレータ C m p の出力電圧 V c が L o w になると、 M O S F E T Q s w 1 および Q s w 2 が O f f となり、基準電圧 V c t が V c t H となる。

#### [0067]

以上の(1)~(5)を繰り返すことによって、接続点#Aの電圧は図4(a)に示すような三角波となる。

## [0068]

< < スイッチング周波数の負荷率依存性 > >

図5は、図1中の負荷Ldが(1)軽負荷のとき、(2)中負荷のとき、(3)重負荷のときの、(a)誤差増幅器10-1の出力電圧V1、(b)コンパレータCmpの基準電圧Vct、(c)コンパレータCmpの出力電圧Vc、(d)三角波電圧VT(図3中の接続点#Aの電圧)、(e)PWM制御回路10-4の出力電圧Vgdを示す図である

## [0069]

(1)軽負荷のとき、(2)中負荷のとき、(3)重負荷のとき、の3パターンに分けて説明する。

## [0070]

(1)上述したように、軽負荷のときは、誤差増幅器10-1の出力電圧V1は低い値となる。従って、図3中の電流Irefの値が小さくなり、これに応じて電流I1~I4の値も小さくなる。これに伴い、キャパシタC1への電荷の蓄積時間およびキャパシタC1からの放電時間が長くなるので、図4中のTrおよびTfが長くなる。これによって、三角波発生回路10-3の出力電圧VTの周波数が低くなる。この結果、スイッチQ100のOn/Offを制御する信号であるPWM制御回路10-4の出力電圧Vgdの周波数が低くなる。すなわち、スイッチQ100のスイッチング周波数が低くなる。ここで、軽負荷とは一例として負荷率が20%程度を言う。

## [0071]

これに対し、(3)重負荷のときは、誤差増幅器10-1の出力電圧V1は高い値となるため、(1)の場合とは逆に、スイッチQ100のスイッチング周波数は高くなる。(2)中負荷のときは、スイッチQ100のスイッチング周波数は上記(1)と(3)の中間の周波数となる。ここで、上記の周波数の一例を示すと、(1)30KHz、(2)5

0 K H z 、 (3) 100 K H z 程度である。

## [0072]

上述したように、誤差増幅器10-1の出力電圧V1は負荷Ldに応じて連続的に変化 するものである。さらに、PWM制御回路10-4の出力電圧Vgdは誤差増幅器10-1の出力電圧V1に応じて連続的に変化するから、PWM制御回路10-4の出力電圧V gdは負荷Ldに応じて連続的に変化する。これにより、負荷Ldに応じて、スイッチO 1 0 0 の O n / O f f を制御する信号である P W M 制御回路 1 0 - 4 の出力電圧 V g d の 周波数(スイッチング周波数)を連続的に変化させることが可能となるのである。

### [0073]

以上のような構成を取ることで、次に述べる回路動作が可能となる。

## [0074]

図6は、電源装置の負荷率と誤差増幅器10-1の出力電圧V1及びスイッチング周波 数の関係を示すグラフである。ここで、負荷率とは電源装置の最大定格負荷に対する現在 の負荷の比、言い換えれば電源装置の最大定格電力に対する現在の電力の比である。電源 装置の最大定格電力に対する図1の負荷Ldとの比とも言える。最大定格の数値例として は、パーソナルコンピューター用電源装置で500W程度、エアコン用電源装置では20 00W程度である。図6中の(1)軽負荷、(2)中負荷、(3)重負荷の数値を挙げるなら、 例えば以下のようになる。パーソナルコンピューター用電源装置においては、(1)負荷: 0~150W、負荷率:0~30%、(2)負荷:150W~350W、負荷率:30%~ 7 0 %、(3)負荷: 3 5 0 W ~ 5 0 0 W、負荷率: 7 0 % ~ 1 0 0 % 程度となる。エアコ ン用電源装置においては、(1)負荷:0~500W、負荷率:0~25%(2)負荷:50 0W~1000W、負荷率:25%~50%、(3)負荷:1000W~2000W、負荷 率:50%~100%程度となる。

#### [0075]

グラフ中、実線(a)は、本実施の形態に関わる電源装置の負荷率とスイッチング周波 数の関係を表している。参考として、一点鎖線(b)に特許文献1記載の電源装置の負荷 率とスイッチング周波数の関係を示す。

#### [0076]

本実施の形態では、負荷率に応じて誤差増幅器10-1からの出力電圧V1がリニアに 変化する。すなわち、誤差増幅器10-1によって、電源装置に接続される負荷の重さを 判別し、出力電圧V1として出力しているとも言える。これによって、負荷が軽い時には スイッチング周波数を低く、負荷が重い時にはスイッチング周波数が高くなるように、ス イッチング周波数をリニアに変化させることができる。

## [0077]

これに対し、特許文献1記載の電源装置においては、スイッチング周波数は2値のみを 取るものであり、負荷率に応じてスイッチング周波数がリニアに変化することはない。

## [0078]

本実施の形態のPFCコントローラを有する電源装置を用いれば、重負荷でのスイッチ ング周波数は高く保つことができる。このため、インダクタL1や出力平滑容量Cout の値を大きくする必要が無い。よって、電源装置の実装面積を増大させることが無い。ま た、軽負荷の状態においてスイッチQ100のスイッチング周波数を低下させることがで きる。このため、軽負荷での電力変換効率を向上させることができる。従って、従来問題 となっていた軽負荷での電力変換効率を向上させることによって、広範囲な負荷において 高い電力変換効率を実現することができる。

### [0079]

本実施の形態のPFCコントローラを有する電源装置を、例えばエアコンのような家電 製品に用いた場合には、この家電製品の電源投入時に必要な最大電力時の電力変換効率向 上に加え、定常負荷における電力変換効率も向上することができる。

### [0800]

また、ENERGY STAR(アメリカ環境保護局が推進する、電気機器の省電力化

10

20

30

40

プログラム)や80 p l u s (80 p l u s プログラム(w w w .80 p l u s .org)が推進する電力機器の省電力化プログラム)等の規格を満足することができる。

#### [0081]

(第2の実施の形態)

次に、第2の実施の形態について図を用いて説明する。

#### [0082]

図7は第2の実施の形態に関わる発振周波数制御回路、三角波発生回路の具体的構成を 表す回路図である。

### [0083]

本実施の形態では、第1の実施の形態同様、基本構成は図1の構成を取る。このうち誤差増幅器10-1、三角波発生回路10-3及びPWM制御回路10-4は第1の実施の形態同様である。従って、ここでは発振周波数制御回路10-2bについてのみ説明する

## [0084]

発振周波数制御回路 1 0 - 2 b はトランジスタ Q 1 1 のほかに、M O S F E T Q 1 2 、 Q 1 3 を含むカレントミラー回路 C M 4 、定電流源 I S 1 、抵抗 R 5 、 R 6 、トランジスタ Q 1 4 、基準電圧 V S 2 を含んで構成される。

#### [0085]

誤差増幅器 1 0 - 1 の出力をトランジスタ Q 1 1 のゲート端子に入力するのは第 1 の実施の形態同様である。

#### [0086]

トランジスタQ11のエミッタ端子には負荷抵抗となる抵抗R5、R6が接続され、エミッタフォロワ出力となっている。

#### [0087]

カレントミラー回路 C M 4 は M O S F E T Q 1 3 のドレイン端子に流れる電流を M O S F E T Q 1 2 側のドレイン端子に複製する。

### [0088]

定電流源IS1は一定の電流I11を流す定電流源である。この電流I11とカレントミラー回路CM4に流れる電流(ここではI12とする)、発振周波数制御回路10-2 bの出力電流I13は以下の関係を持つ。

### [0089]

I 1 1 = I 1 2 + I 1 3

またこの式を変形すると以下のようになる。

### [0090]

I 1 3 = I 1 1 I 1 2

これにより、カレントミラー回路 C M 4 に入力される電流が小さいほど三角波発生回路 1 0 - 3 に入力される電流は大きくなることが理解できる。

### [0091]

次に、基準電圧VS2及びトランジスタQ14よりなるクランプ回路について説明する

## [ 0 0 9 2 ]

このクランプ回路は、トランジスタQ14のエミッタ端子が抵抗R5及び抵抗R6の接続点に接続される。この結果、トランジスタQ14のエミッタ端子の電圧よりトランジスタQ11のエミッタ端子の電圧が高い場合にはカレントミラー回路CM4には電流は流れない。すなわち、誤差増幅器10-1の出力が該クランプ回路で規定する電圧以上の場合には、三角波発生回路10-3の三角波出力及びPWM制御回路10-4の発振周波数は一定となる。逆にある誤差増幅器10-1の出力が、該クランプ回路で規定する電圧以下になってから、リニアにPWM制御回路10-4の発振周波数の低下が始まることとなる

[0093]

50

20

10

30

次に動作についてグラフを用いて説明する。

### [0094]

図8は、第2の実施の形態に関わる発振周波数制御回路10-2bの周波数変化を説明するためのグラフである。また図9は、第2の実施の形態に関わる発振周波数制御回路10-2bを適用したPFCコントローラ10の出力を表すグラフである。

#### [0095]

図8を見ても分かるとおり、本実施の形態の発振周波数制御回路10-2bでは負荷が一定の値までは線形に誤差増幅器10-1の出力電圧も増加する。また三角波発生回路10-3の三角波出力、PWM制御回路10-4の発振周波数も比例して増加する。

## [0096]

しかし、誤差増幅器 1 0 - 1 の出力が図 7 のクランプ回路により定義される電圧以上になると(図上では負荷(2))となると、それ以上は三角波発生回路 1 0 - 3 の三角波出力、PWM制御回路 1 0 - 4 の発振周波数は増加しない(図 8 及び図 9 参照)。

## [0097]

三角波発生回路10-3の三角波出力については図9の(2)及び(3)を見れば明確になる。すなわち、誤差増幅器10-1の出力が一定以上になると三角波発生回路10-3の三角波電圧VT、PWM制御回路10-4の発振周波数は変わらないことが分かる。

#### [0098]

これにより、一定以上、スイッチQ100の周波数を上げることなく、スイッチング損失を改善することが可能となる。

[0099]

(第3の実施の形態)

次に第3の実施の形態について説明する。

[0100]

本実施の形態では、連続モードのインターリーブ方式 P F C コントローラに適用することを想定したものである。ここで、連続モードとは、インダクタ電流が重畳している状態で、スイッチを動作するモードである。インターリーブ方式とは、対となる 2 つのスイッチを交互に動作させる方式である。

## [0101]

図10は、第3の実施の形態に関わる電源装置の構成を表す回路図である。

[0102]

本実施の形態では、インターリーブ方式であるために、インダクタの充放電をスイッチで行う構成を2系統有する。一つがインダクタL1、ダイオードD1及びスイッチQ10の系統であり、もう一つがインダクタL2、ダイオードD2及びスイッチQ200の系統である。

[0103]

制御する対象が二つに増えることに対応して、 P W M 制御回路 1 0 - 4 も P W M 制御回路 1 0 - 4 c に置き換えられる。

[0104]

PWM制御回路10-4 c は、PWM制御回路10-4の入力信号に加え、スイッチQ100及びスイッチQ200の電圧情報も入力されることとなる。各スイッチの電圧情報を検出するために、各スイッチの接地側に抵抗が挿入される。図ではスイッチQ100の系統には抵抗Rs1が、スイッチQ200の系統には抵抗Rs2がそれぞれ挿入されている。この抵抗の抵抗値はRs1=Rs2であるとPWM制御回路10-4 c 内での制御にバイアスをかける必要が無い。しかし、目的に応じて抵抗Rs1及び抵抗Rs2の抵抗値にバイアスをかけても良い。

[0105]

この各スイッチの電圧情報に基づき、 PWM制御回路 1 0 - 4 c は各スイッチの状況に対応して制御することが可能となる。

[0106]

10

20

30

40

PWM制御回路10-4cはスイッチQ100、Q200を制御するために、2系統の出力を持つ。

### [0107]

このように構成することで、連続モードのインターリーブ方式のPFCコントローラを用いた電源装置でもスイッチング周波数を低下させスイッチング損失を改善することが可能となる。

#### [0108]

(第4の実施の形態)

第4の実施の形態について説明する。本実施の形態では、制御の際の基準となる信号を 、分圧回路1の電圧に代えて出力端子の電流とする点に特徴がある。

[0109]

図11は、第4の実施の形態に関わる電源装置の構成を表す回路図である。

#### [0110]

この第4の実施の形態では出力端子直前に出力電流測定用抵抗RIを挿入する。また、これまでの実施の形態では、誤差増幅器10-1の出力を発振周波数制御回路10-2(10-2bの適用も可能)に入力していた。これに対し、本実施の形態では電位差増幅器10-5dを新設する。そして出力電流測定用抵抗RIの前後の電圧を電位差増幅器10-5dで増幅し発振周波数制御回路10-2に入力することで、出力電流測定用抵抗RIに流れる電流に基づきPFCコントローラ10の制御を行うことを特徴とする。

[0111]

このような構成を取ることでも、スイッチング周波数を低下させることが可能となる。

#### [0112]

なお図11は第1の実施の形態に対して本実施の形態の技術的思想を適用したものであるが、第2の実施の形態に対して適用することも可能である。

#### [0113]

以上、本発明者によってなされた発明を実施の形態に基づき具体的に説明したが、本発明は前記の実施の形態に限定されるものではなく、その要旨を逸脱しない範囲で種々変更が可能であることは言うまでもない。

## 【符号の説明】

## [0114]

1...分圧回路、10...PFCコントローラ、

10-1...誤差増幅器、10-2、10-2b...発振周波数制御回路、

10-3...三角波発生回路、10-4、10-4 c... P W M 制御回路、

1 0 - 5 d ... 電位差増幅器、

CM1、CM2、CM3、CM4…カレントミラー回路、Cmp…コンパレータ、

Cout...出力平滑容量、D1、D2...ダイオード、L1、L2...インダクタ、

C 1 ... キャパシタ、

Q1、Q2、Q4、Q5、Q6、Q7、Q8、

Q 1 1、Q 1 2、Q 1 3、Q 1 4、Q p 1、Q p 2、Q p 3、Q p 4、Q n 1、 Q n 2、Q n 3、Q s w 1、Q s w 2、Q r ... M O S F E T、

Q 1 0 0 ... スイッチ、

R 1、R 2、R 3、R 4、R 5、R 6、R f 1、R f 2 ...抵抗、

R s ... 電流検出抵抗、 R I ... 出力電流測定用抵抗、 V S 1 、 V S 2 ... 基準電圧、

# 1 ... 掛算器、 # 2 ... 誤差増幅器、 # 3 ... コンパレータ、

# 4 ... フリップフロップ、# 5 ... 抵抗、# 6 ... バッファ。

10

20

30

30

【図1】 【図2】

【図3】 【図4】

【図5】 【図6】

【図7】 【図8】

【図9】 【図10】

【図11】

## フロントページの続き

## 審査官 神山 貴行

(56)参考文献 特開2004-282958(JP,A)

特開2002-320379(JP,A)

特開2007-195282(JP,A)

特開2009-100607(JP,A)

(58)調査した分野(Int.CI., DB名)

H02M 3/00~3/44

H02M 7/00~7/40