# (19) World Intellectual Property Organization International Bureau

#

#### (43) International Publication Date 18 September 2008 (18.09.2008)

# (10) International Publication Number $WO\ 2008/112207\ A2$

(51) International Patent Classification: *G06F 9/308* (2006.01) *G06F 9/30* (2006.01)

(21) International Application Number:

PCT/US2008/003178

(22) International Filing Date: 7 March 2008 (07.03.2008)

(25) Filing Language: English

(26) Publication Language: English

(30) Priority Data:

| 60/906,000 | 9 March 2007 (09.03.2007)    | US |

|------------|------------------------------|----|

| 11/818,452 | 14 June 2007 (14.06.2007)    | US |

| 11/818,449 | 14 June 2007 (14.06.2007)    | US |

| 11/998,994 | 3 December 2007 (03.12.2007) | US |

- (71) Applicant (for all designated States except US): ANA-LOG DEVICES, INC. [US/US]; One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106 (US).

- (72) Inventors; and

- (75) Inventors/Applicants (for US only): OLOFSSON, Andreas, D. [SE/US]; 36 Hill Street, Lexington, MA 02421 (US). JACOBS, Christopher [US/US]; 26 Reverend Houston Drive, Bedford, NH 03110 (US). KETTLE, Paul [US/US]; P. O. Box 15222, Boston, MA 02215 (US).

- (74) Agent: ABRAHAMSEN, Robert, M.; Wolf, Greenfield & Sacks, P.C., Federal Reserve Plaza, 600 Atlantic Avenue, Boston, MA 02210-2206 (US).

- (81) Designated States (unless otherwise indicated, for every kind of national protection available): AE, AG, AL, AM, AO, AT, AU, AZ, BA, BB, BG, BH, BR, BW, BY, BZ, CA, CH, CN, CO, CR, CU, CZ, DE, DK, DM, DO, DZ, EC, EE, EG, ES, FI, GB, GD, GE, GH, GM, GT, HN, HR, HU, ID, IL, IN, IS, JP, KE, KG, KM, KN, KP, KR, KZ, LA, LC, LK, LR, LS, LT, LU, LY, MA, MD, ME, MG, MK, MN, MW, MX, MY, MZ, NA, NG, NI, NO, NZ, OM, PG, PH, PL, PT, RO, RS, RU, SC, SD, SE, SG, SK, SL, SM, SV, SY, TJ, TM, TN, TR, TT, TZ, UA, UG, US, UZ, VC, VN, ZA, ZM, ZW.

- (84) Designated States (unless otherwise indicated, for every kind of regional protection available): ARIPO (BW, GH, GM, KE, LS, MW, MZ, NA, SD, SL, SZ, TZ, UG, ZM, ZW), Eurasian (AM, AZ, BY, KG, KZ, MD, RU, TJ, TM), European (AT, BE, BG, CH, CY, CZ, DE, DK, EE, ES, FI, FR, GB, GR, HR, HU, IE, IS, IT, LT, LU, LV, MC, MT, NL, NO, PL, PT, RO, SE, SI, SK, TR), OAPI (BF, BJ, CF, CG, CI, CM, GA, GN, GQ, GW, ML, MR, NE, SN, TD, TG).

#### **Published:**

without international search report and to be republished upon receipt of that report

#### (54) Title: SOFTWARE PROGRAMMABLE TIMING ARCHITECTURE

(57) Abstract: An apparatus for generating a digital signal pattern may comprises a memory, a program sequencer, first and second circuits, and an event execution unit. The memory may have stored therein a plurality of instructions that, when executed, cause a digital signal pattern to be generated on a plurality of nodes. The program sequencer may be configured to control a sequence in which the plurality of instructions are retrieved from the memory and executed. The first circuit may sequentially step through a plurality of different output states in response to a clock signal. The second circuit may identify an output event when an output state of the first circuit corresponds to an output state identified by retrieved instructions of a particular type. The event execution unit may control states of signals on the plurality of nodes in a manner specified by the retrieved instructions of the particular type in response to the second circuit identifying an output event.

WO 2008/112207 PCT/US2008/003178

# SOFTWARE PROGRAMMABLE TIMING ARCHITECTURE

This application relates to the subject matter disclosed in each of (1) U.S. Provisional Application Ser. No. 60/906,000, filed March 9, 2007 ("the '000 application"), (2) U.S. Patent Application Ser. No. 11/818,449, filed June 14, 2007 ("the '449 application), (3) U.S. Patent Application Ser. No. 11/818,452, filed June 14, 2007 ("the '452 application), and (4) U.S. Patent Application Ser. No. 11/998,994, filed December 3, 2007 ("the '994 application"). The entire contents of each of the '000, '449, '452, and '994 applications are incorporated herein by reference.

10

5

#### BACKGROUND

In a variety of applications, there is a need for generating timing pulses in an efficient manner. Such applications may include, for example, CCD timing interface chips, lens drivers, stepper motors, and display drivers. Such applications generally call for a very low cost and lower power solution, but need to run with fine clock cycle resolution on the timing pulse generation. Micro-controllers generally do not have the fine clock cycle or instruction width needed to generate a sufficient number of output pulses on a pixel by pixel basis.

#### **SUMMARY**

20

25

30

15

According to one aspect of the present invention, a method for generating a digital signal pattern involves retrieving from memory an instruction comprising a first field representing a vector including a plurality of bits that are to be used to control states of signals on a corresponding plurality of nodes and a second field identifying a specified output state of a circuit that sequentially steps through a plurality of different output states in response to a clock signal. In response to determining that the output state of the circuit corresponds to the specified output state, the signals on the plurality of nodes are controlled in the manner specified by the corresponding ones of the plurality of bits in the first field.

According to another aspect, a method for generating a digital signal pattern involves retrieving from memory an instruction comprising a first field representing a vector including a plurality of bits that are to be used to control states of signals on a corresponding plurality of nodes and a second field identifying a criterion for determining an occasion on which the plurality of bits are to be controlled as specified by the vector. The instruction is executed so as to simultaneously control the signals on the plurality of nodes in the manner specified by

WO 2008/112207 2 PCT/US2008/003178

the corresponding ones of the plurality of bits in the field in response to determining that the criterion has been met.

5

10

15

20

25

30

According to another aspect, apparatus for generating a digital signal pattern comprises a memory, a program sequencer, first and second circuits, and an event execution unit. The memory has stored therein a plurality of instructions that, when executed, cause a digital signal pattern to be generated on a plurality of nodes. The program sequencer is configured to control a sequence in which the plurality of instructions are retrieved from the memory and executed. The first circuit sequentially steps through a plurality of different output states in response to a clock signal. The second circuit identifies an output event when an output state of the first circuit corresponds to an output state identified by retrieved instructions of a particular type. The event execution unit controls states of signals on the plurality of nodes in a manner specified by the retrieved instructions of the particular type in response to the second circuit identifying an output event.

According to another aspect, a circuit comprises a clock cycle counter circuit, a memory, and a clock cycle count comparison circuit. The clock cycle counter circuit is configured to produce an output count. The memory configured to store at least first and second count values. The cycle count comparison circuit is configured to compare the output count with each of the first and second stored count values and to generate a particular type of output event at a node if the output count corresponds to either of the first and second stored count values.

According to another aspect, a method comprises steps of producing a output count in response to a clock signal, comparing the output count with each of first and second stored count values, and generating a particular type of output event at a node if the output count corresponds to either of first and second stored count values.

According to another aspect, a circuit comprises a digital pattern generator, a general purpose output controller, at least one memory element, and a selection circuit. The digital pattern generator is configured to generate a pattern of digital signals at M nodes. The general purpose output controller is configured to generate general purpose digital signals at N nodes. The at least one memory element is configured to store particular values for M outputs of the circuit corresponding to the M nodes of the digital pattern generator and for N outputs of the circuit corresponding to the N nodes of the general purpose output controller. The selection circuit is configured to select, independently for each of the M outputs of the circuit, whether the particular value stored in the at least one memory element or the corresponding output signal of the digital pattern generator is provided on that output, and is

further configured to select, independently for each of the N outputs of the circuit, whether the standby value stored in the at least one memory element or the corresponding output signal of the general purpose output controller is provided on that output.

# BRIEF DESCRIPTION OF THE DRAWINGS

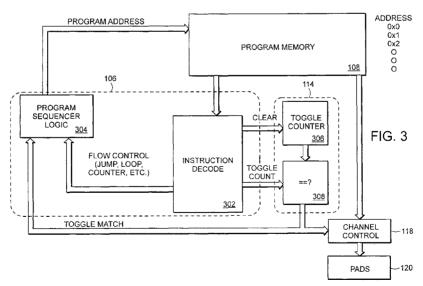

Fig. 1 is an architecture block diagram of a digital pattern processor (DPP) that embodies various aspects of the invention;

5

10

15

20

25

30

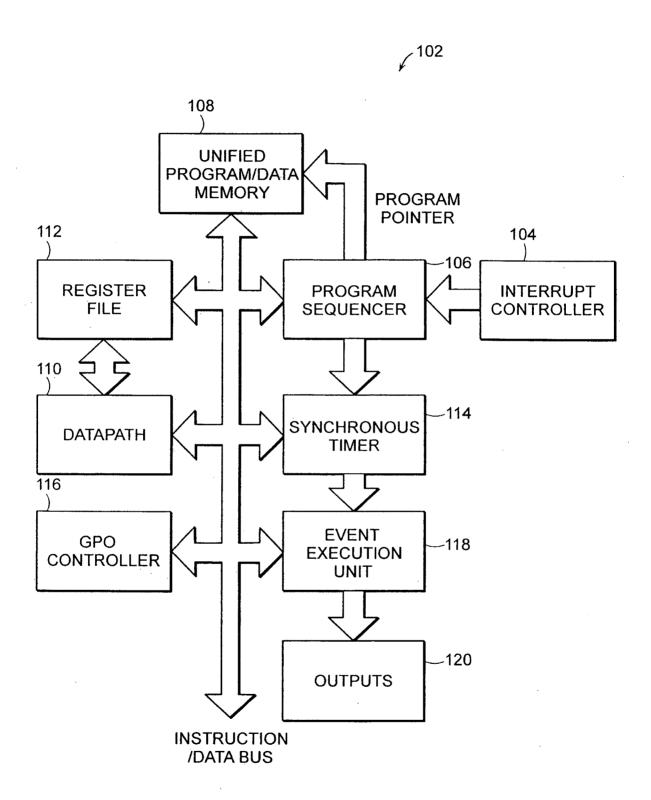

- Fig. 2 shows an illustrative example of how the DPP may be employed in a typical micro-controller system on a chip;

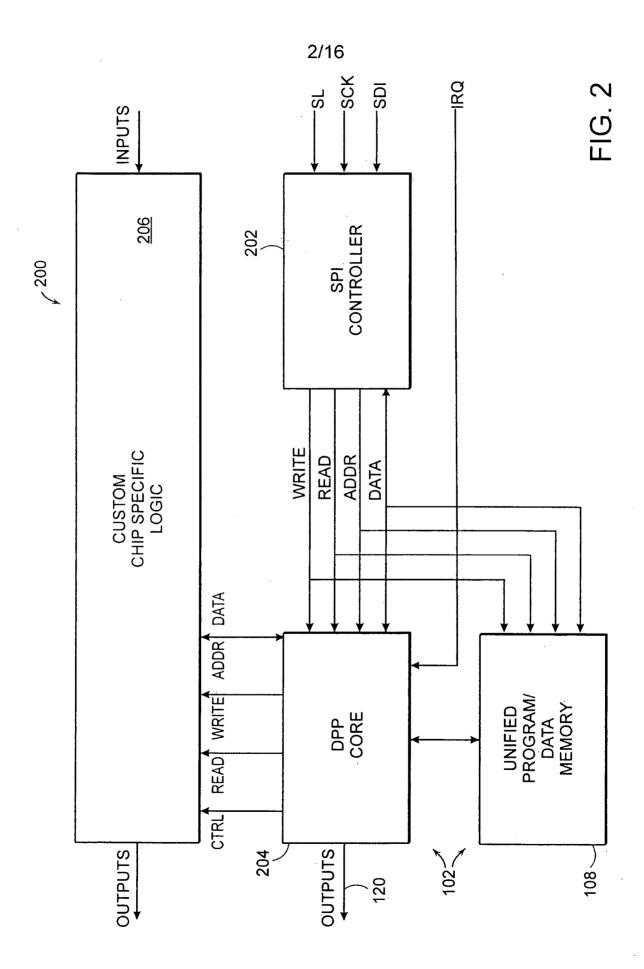

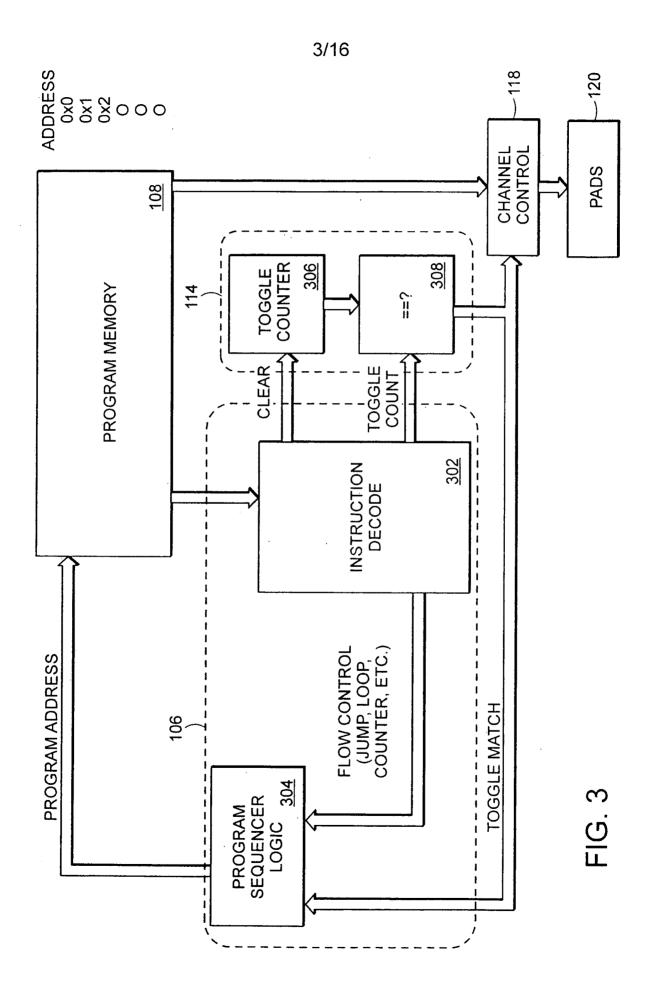

- Fig. 3 is a functional block diagram illustrating various components of the DPP that may operate together to control toggling of its outputs;

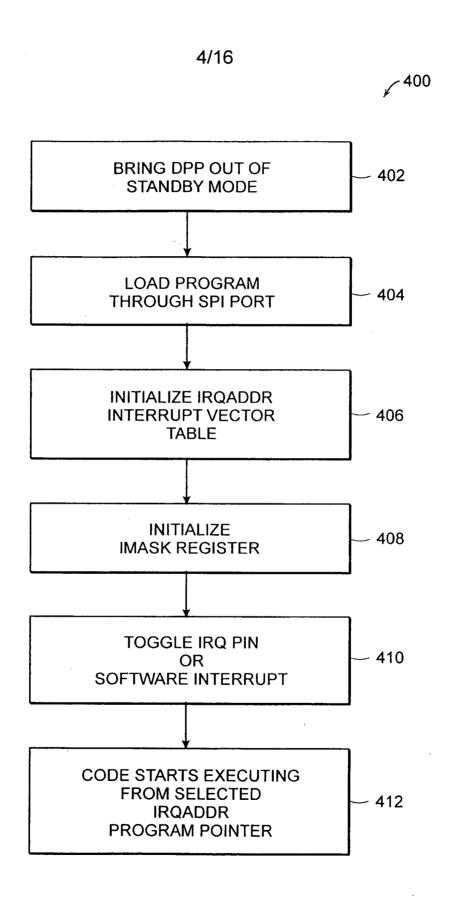

- Fig. 4 shows an illustrative example of a program execution sequence that may be used by the DPP to load and execute code;

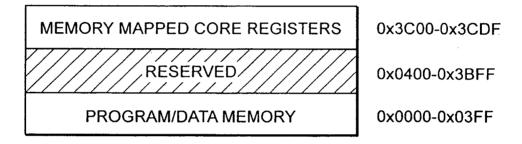

- Fig. 5 shows an illustrative example of a core memory map for the DPP;

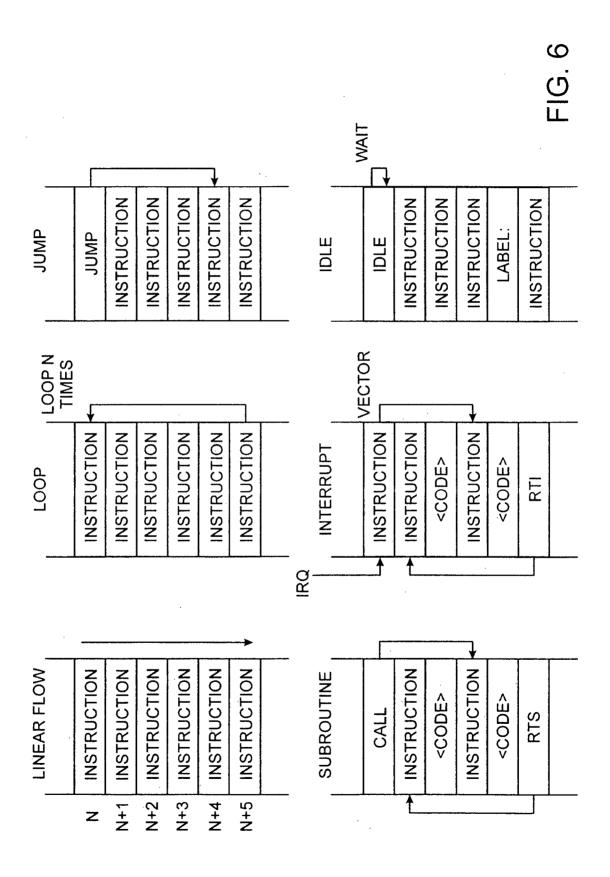

- Fig. 6 shows several examples of program sequence structures that may be supported by the DPP;

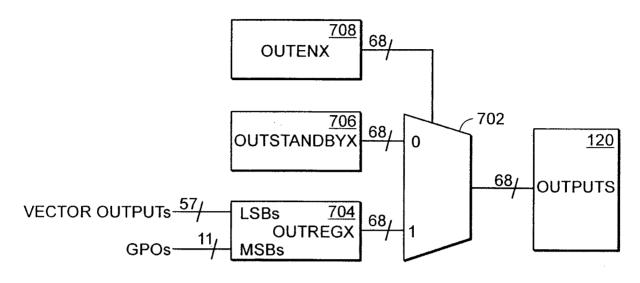

- Fig. 7 shows an example of a hardware control mechanism that may by used to enable and disable the outputs of the DPP on a pin by pin basis;

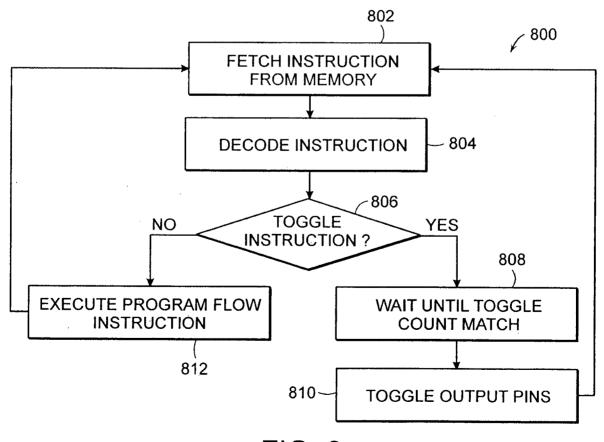

- Fig. 8 is a flowchart illustrating an example of an execution flow that may be used to generate toggle pulses on the outputs of the DPP;

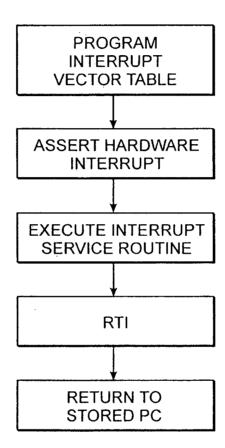

- Fig. 9 illustrates an example of basic steps that may be involved in executing an interrupt service routine (ISR) using the DPP;

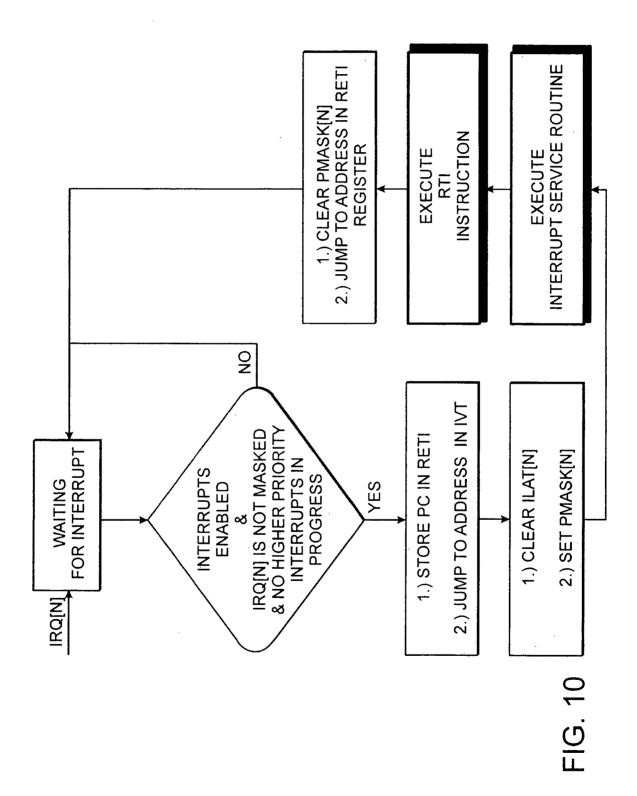

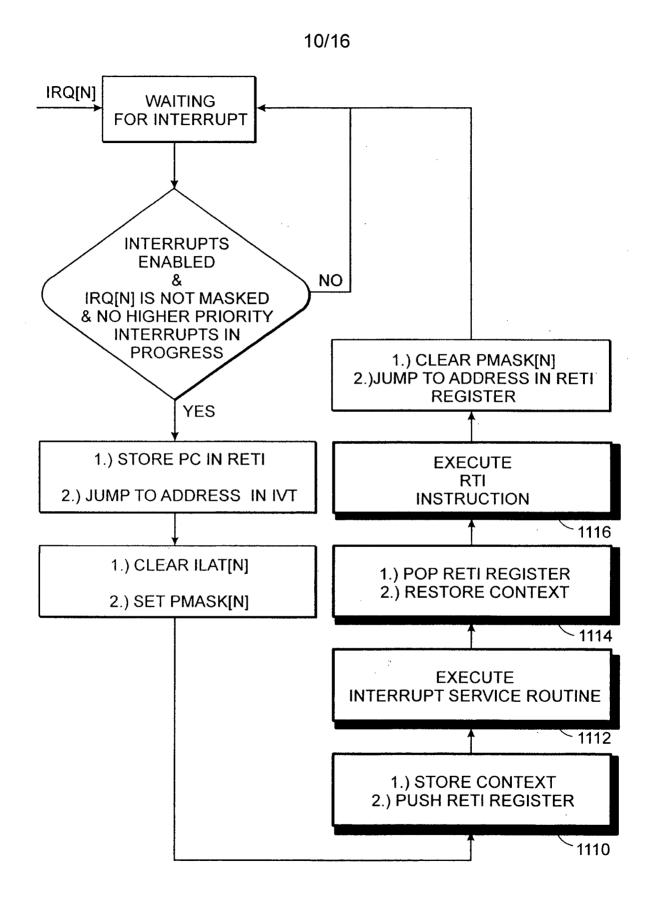

- Figs. 10-11 illustrate examples of how nested and non-nested interrupts, respectively, may be latched and executed in the DPP;

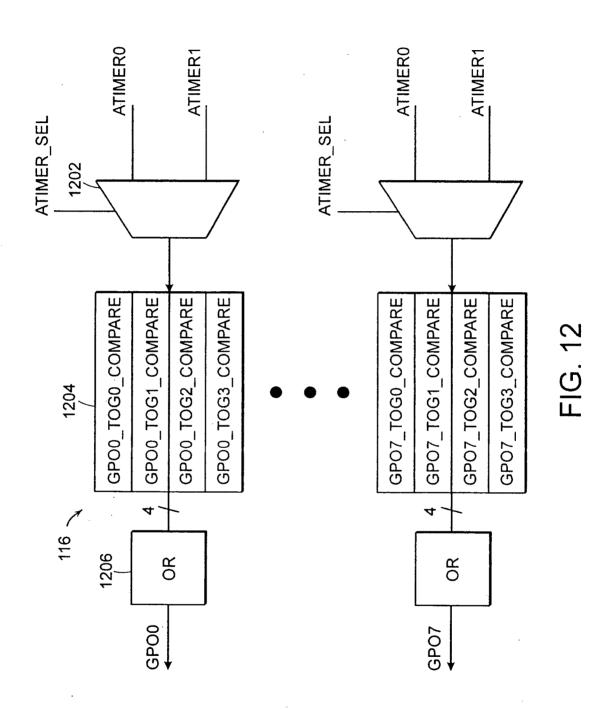

- Fig. 12 shows a high-level diagram of an example embodiment of the GPO controller of the DPP;

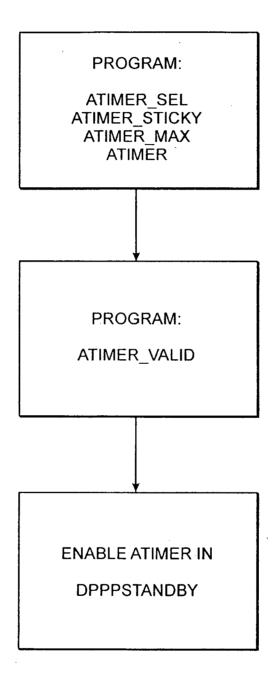

- Fig. 13 illustrates an example of a programming sequence that may be used to configure the GPO controller;

- Fig. 14 illustrates an example of a set of specialized instructions that may be executed by the DPP to generate timing signals;

- Fig. 15 illustrates an example of a simple program that may be executed using the instructions of Fig. 14 to perform fast vertical clocking of an image sensor;

- Fig. 16 illustrates an example of another simple program that may be executed by the DPP using the instructions of Fig. 14 to readout a single line of data from an image sensor;

WO 2008/112207 4 PCT/US2008/003178

Fig. 17 illustrates an example of a more complex program that may be executed by the DPP using the instructions of Fig. 14 to read out image sensor data from a full frame with several regions;

Fig. 18 shows an example of a program instruction configuration that may be used in the DPP; and

5

10

15

20

25

30

Fig. 19 shows an example of how various instructions may be stored at particular locations in the memory of the DPP, and accessed by a program sequencer, so as to enable certain of the functionality described herein.

#### **DETAILED DESCRIPTION**

An illustrative embodiment of a digital pattern processor (DPP) is disclosed which comprises a reduced instruction set computer (RISC) with a unified program and data memory. In some embodiments, the DPP may have eight sixteen-bit general purpose registers used for data and pointer manipulation. To aid in timing generation applications, the DPP may also have a synchronous timer integrated into the program flow, two asynchronous counters for general purpose output (GPO) toggle creation, and a sixteen-input maskable interrupt controller.

As described below, in some embodiments, the architecture may have a compact and efficient instruction set, optimized for control and timing generation applications. The instruction set may, for example, be divided into the following four basic instruction types: (1) program flow instructions, (2) arithmetic instructions, (3) load/store instructions, and (4) pattern generation instructions. The program flow instructions may be used to control the flow of the program and form the framework for all software development on the DPP. The program flow instructions may thus provide support for looping, sub-routines, software interrupts, and branching. The arithmetic instructions may be used for general control flow, and for all control and data computation. The load/store instructions may be used for writing data to and reading data from the unified data/program memory, for saving and restoring registers in nested interrupt service routines, and for managing register data in nested sub routines. The pattern generation instructions may comprise an extended instruction set for generating a set of parallel output toggles very efficiently. The execution of these instructions may, for example, be controlled by an internal clock cycle counter that synchronizes the program fetch and execution with output pin toggling. In some embodiments, the DPP may have only a single state machine and all outputs of the DPP may be driven simultaneously.

WO 2008/112207 5 PCT/US2008/003178

In some embodiments, the DPP may be configured to fetch and execute one instruction per clock cycle, and may be parameter scalable to allow for easy optimization in different applications. In some embodiments, the DPP architecture may additionally or alternatively be used in conjunction with a generic serial interface and an interrupt controller to create a general purpose CPU subsystem.

5

10

15

20

25

30

As described below, a simple programming model may be employed that uses an intuitive assembly programming language, a unified register file for all variable manipulation, and a shallow, e.g., two cycle, pipeline. To aid in programming the part from external sources, all registers and memory locations may be memory mapped in a single coherent memory architecture. The applications in which the DPP may be used need not be determined by its hardware configuration; it may be programmable for virtually any application. The DPP may serve as a timing generator or other pattern signal generating device in any of a number of possible environments, and need not be configured specifically as an image sensor interface chip or for some other specific purpose. Examples of possible applications for a DPP such as that disclosed include CCD timing generation, lens driver controllers, LCD timing generators, ultra low power signal processing applications, mixed signal SOC micro-controllers, and motor control applications.

Because the DPP may be largely software based, it may be readily scaled for a particular application by employing a larger memory and/or employing a larger number of addresses. The DPP may also be significantly less expensive than logic-based architectures. In some embodiments, the DPP need not include vertical synchronization (VD) or horizontal synchronization (HD) counters inside the chip, thus allowing for the line and pixel count to be determined by the user so as to meet the specific needs of a particular image sensor when the DPP is used for such a purpose.

Fig. 1 is an architecture block diagram showing several operational units of an illustrative embodiment of a digital pattern processor (DPP) 102. In the example shown, the DPP 102 comprises an interrupt controller 104, a program sequencer 106, a memory 108, a datapath 110, a register file 112, a synchronous timer 114, a general purpose output (GPO) controller 116, and an event execution unit 118.

The interrupt controller 104 may, for example, process sixteen independent interrupts and exceptions to redirect the program pointer to one of the sixteen entries in an interrupt vector table (IVT), described below.

The program sequencer 106 may provide addresses to the program memory 108 and control the flow of the program being executed. The program sequencer 106 may further

WO 2008/112207 6 PCT/US2008/003178

comprise at least one, and preferably three or more, loop counters to control loops in the executed program, as described below.

The memory 108 may comprise a unified program/data memory that can be accessed by read and write operations both from the DPP 102 and from an external host (not shown).

The register file 112 may, for example, comprise a general purpose register file with eight sixteen-bit registers. The datapath 110 may read values from the register file 112 and return results to the register file 112, and may thus be used for "load/store" instructions and "arithmetic" instructions.

5

10

15

20

25

30

The synchronous timer 114 may generate timing events during the program flow using specialized instructions. It may, for example, comprise a free-running sixteen-bit clock cycle counter (also referred to herein as a "toggle counter" or "synchronous timer" or "STIMER") which updates on every rising edge of the DPP clock. As explained in more detail below, an output event may be generated when the current instruction is a toggling instruction and the counter value specified in the toggling instruction matches the current value of the toggle counter. From the time that the toggle instruction is fetched to the time that the toggle event occurs, the DPP 102 may be kept in a hold state. The toggle match may, for example, cause an instruction-specified number of outputs 120 of the DPP 102 to toggle, and also cause the program pointer to advance to the next sequential program address.

The GPO controller 116 may permit programming of independent timing pulses on a set of general purpose output pins, for example, using two free-running thirty-two-bit cycle counters.

The event execution unit 118 may, for example, toggle the outputs 120 every time an event is generated by the programmable toggle instructions or by the GPO controller 116. The event execution unit 118 may also selectively enable outputs and manage standby polarities for all of the outputs 120 on a per pin basis.

Fig. 2 shows an illustrative example of how the DPP 102 may be employed in a typical micro-controller system-on-a-chip (SOC) 200. As shown, an SPI controller 202 may receive serial data from the chip interface and convert it to parallel read and write transactions for the on-chip memory 108 and for a DPP core 204 (which may, for example, comprise all of the other components of the DPP 102 shown in Fig. 1). In the example shown, the DPP core 204 is further connected to custom chip-specific logic 206 embedded on the chip 200, thus allowing the DPP 102 to directly control not only the outputs 120 of the chip 200 but also any embedded on-chip custom logic 206. By creating a single uniform memory architecture, the DPP core 204 may thus access any register or memory location,

WO 2008/112207 7 PCT/US2008/003178

including the unified/program memory 108 and reserved memory space within the custom chip specific logic 206.

5

10

15

20

25

30

Fig. 3 is a functional block diagram illustrating various components of the DPP 102 that may operate together to control toggling of the outputs 120. As shown, the program sequencer 106 may comprise an instruction decoding section 302 and a program sequencing logic section 304 that together are responsible for fetching instructions from the memory 108, decoding the fetched instructions, and controlling the synchronous timer 114 so as to appropriately generate toggle events. In the example shown, the synchronous timer 114 comprises a toggle counter 306 and a comparator 308. The comparator 308 may, for example, determine when the toggle counter 114 has reached a specified "toggle count" value. As noted above, the toggle counter 306 may, for example, comprise a sixteen-bit free-running clock cycle counter. An illustrative example of an execution flow that may be employed by these components to generate toggle pulses on the outputs 120 is discussed below in connection with Fig. 8.

As noted above, the DPP 102 may execute a program stored, for example, in the on-chip program memory 108. Fig. 4 shows an illustrative example of a program execution sequence 400 that may be used by the DPP 102 to load and execute code. The start of the code execution may, for example, be initiated by an off-chip host processor, either by setting a hardware interrupt pin or by writing to an interrupt latch (ILAT) register, as described below. As shown, the sequence 400 may begin at a step 402, where the DPP 102 is brought out of standby mode. Next the sequence may proceed to a step 404, where an appropriate program may be loaded through an SPI port (e.g., via the SPI controller 202 shown in Fig. 2). Next, an IRQADDR interrupt vector table and an IMASK register (see Table 2 below) may be initialized at the steps 406 and 408, respectively. The sequence 400 may then proceed to a step 410, where an IRQ pin is toggled or a software interrupt occurs. Finally, the sequence 400 may begin executing code from the selected IRQADDR program pointer.

The DPP 102 may, for example, support two different data formats: sixteen bits signed data and sixteen bits unsigned data. For signed sixteen bit integer data, the most significant bit (MSB) and the fifteen least significant bits (LSBs) may, for example, represent values from "-32768" to "32767." For unsigned sixteen bit integer data, all bits may, for example, be interpreted as unsigned bits, providing a range of "0" to "65535." The sixteen bits signed data may, for example, be used for all arithmetic operations, while the sixteen bits unsigned data may be used for toggle instructions, load store instructions, and program flow instructions.

WO 2008/112207 8 PCT/US2008/003178

The following is a brief overview of the syntax convention used in the illustrative examples of the DPP assembly language that are described below. (1) The instruction syntax is case insensitive. Upper and lower case letters can be used and interchanged arbitrarily. For example R0 and r0 both refer to the register R0. The only exception to this convention is in defining and using macros, which are case sensitive. (2) White space can appear anywhere between legal assembly tokens and is removed during assembly pre processing. Tokens include numbers, register names, instructions, keywords, and identifiers. (3) <IMM16> refers to a sixteen bit immediate value provided by the instruction line. (4) {this | that} in the instruction syntax means that either "this" or "that" must be specified in the instruction line. (5) RD, RM, RS, RN specify any one of the eight general purpose registers. (6) MMR specifies one of the memory mapped registers described in the register tables. (7) A semicolon must be used to terminate every instruction. (8) Labels are supported by using the format <LABEL: >. The label can be placed on its own line in the assembly code or on the same line as an instruction. It is illegal to place two labels on the same line. An example of legal use of labels is given below:

LABEL1: <code> LABLE2: <code>

20

15

5

10

(9) End of line comments use the double slash token ("//"). The double slash indicates that everything from the token until the end of the line should be ignored. (10) General comments begin with a ("/\*") token and end with a ("\*/") token and may extend over several lines. (11) Instruction options are specified at the end of the instruction, but before the semi-colon, surrounded by parentheses. For example, toggle\_vector(0:V1) (c);. (12) Assembler supported number format examples are given as follows:

Hexadecimal: 0xABCD,

Decimal: 33 and -33, and

Binary: b#10010101.

30

35

25

In some embodiments, the DPP may have a unified memory map for program instructions, data parameters, and all DPP related registers. The memory architecture may, for example, be sixteen-bit addressable, resulting in a maximum of "65536" address locations. The smallest addressable word in the architecture may, for example, be sixteen bits wide. Fig. 5 shows an illustrative example of a core memory map 500 for the DPP 102. In the example shown, the program memory is "1024" deep. In some embodiments, all DPP core registers may be memory mapped registers (MMR), which can be accessed by load-store

WO 2008/112207 9 PCT/US2008/003178

instructions and external transactions. The absolute address locations shown in Fig. 5 may, for example, refer to the access of memory and registers from the DPP core itself. When accessing the memory mapped registers and memory from an external host, an offset may be added to the address values shown.

5

10

15

20

25

30

The DPP instructions may, for example, be N \* sixteen-bits wide, and depend on the width of the software programmable output vector supported by the specific chip. In some embodiments, the instruction widths supported by the DPP core may, for example, be "32-128" in sixteen-bit increments. When loading the program into the program memory 108 through the SPI port at startup, instruction lines may be loaded sixteen bits at a time. Instructions may, for example, be fetched on even N \* sixteen-bit boundaries, so all instructions may be stored in the program memory accordingly. Data parameters may be stored in memory as sixteen bit values at any memory location.

In some embodiments, all memory mapped registers (MMRs) may be accessed either by an external transaction or by a DPP generated load-store transaction. In addition, all MMRs may, for example, be loaded with sixteen-bit immediate values, through the immediate load instruction. Some registers may have additional functionality and access modes, which are described in the register tables below.

The DPP registers may, for example, be divided into five different groups: (1)

General Purpose Registers, (2) Interrupt Control Registers, (3) Output Control Registers, (4)

GPO Control Registers, and (5) a GPO Toggle Table.

The General Purpose Registers may, for example, comprise eight general purpose registers used for temporary storage of pointers, variables, and counters. They may, for instance, be used by all arithmetic instructions, load-store instructions, and toggle instructions. The Interrupt Control Registers may include ILAT, IMASK, and PMASK registers which control the execution and priority of interrupts and exceptions. A set of sixteen interrupt address registers may also form an interrupt vector table (IVT), which may be used to configure the start addresses of up to sixteen separate interrupt service routines (ISRs). The Output Control Registers may control the outputs of the DPP 102. All outputs of the DPP 102 may, for example, have a direct access bit, an enable bit, and a standby value bit that can be controlled by writing to the appropriate register. In some embodiments, some outputs may be controlled by the parallel toggle instructions, while others may be controlled by the GPO controller. In addition, in some embodiments, all outputs may be forced to explicit values by writing appropriate data to the OUTREG, OUTEN, and/or OUTSTANDBY registers. The GPO Control Registers may control the behavior of the free

running GPO controller. They may, for example, control the wrap around values of the timers and validate the entries in a GPO toggle table. The GPO Toggle Table may, for example, comprise registers that provide a table of toggle values to which a pair of cycle counters, ATIMER0 and ATIMER1 (described below), are compared. Each toggle entry may, for instance, be validated by a valid bit in the ATIMER\_VALID register.

Tables 1-5 below list examples of memory mapped registers that may be employed in the DPP 102. The tables contain the mnemonic name of register, the memory address of the register, access modes, reset states, and a description. In the access column, "R" refers to Read access and "W" refers to Write access. "NA" in all columns refers to non-applicable.

Table 1: Examples of General Purpose Registers

|            | I care est total and analysis | V. P   |         |                                                                                                                                                                                    |

|------------|-------------------------------|--------|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME       | ADDRESS                       | ACCESS | DEFAULT | DESCRIPTION                                                                                                                                                                        |

| R0         | 0x3C00                        | R/W    | None    | General Purpose Register                                                                                                                                                           |

| R1         | 0x3C01                        | R/W    | None    | General Purpose Register                                                                                                                                                           |

| R2         | 0x3C02                        | R/W    | None    | General Purpose Register                                                                                                                                                           |

| R3         | 0x3C03                        | R/W    | None    | General Purpose Register                                                                                                                                                           |

| R4         | 0x3C04                        | R/W    | None    | General Purpose Register                                                                                                                                                           |

| R5         | 0x3C05                        | R/W    | None    | General Purpose Register                                                                                                                                                           |

| R6         | 0x3C06                        | R/W    | None    | General Purpose Register                                                                                                                                                           |

| R7         | 0x3C07                        | R/W    | None    | General Purpose Register                                                                                                                                                           |

| PC         | 0x3C08                        | R/W    | 0x0     | Instruction Fetch Pointer Register                                                                                                                                                 |

| RETS       | 0x3C09                        | R/W    | 0x0     | Sub-routine return register. A CALL instruction writes the next sequential PC to the register. An RTS instruction copies the content of the RETS register to the PC register.      |

| RETI       | 0x3C0A                        | R/W    | 0x0     | Interrupt return register. An interrupt event causes the next PC address to be written to the RETI. An RTI instruction copies the content of the RETI register to the PC register. |

| DPPSTANDBY | 0x3C0B                        | R/W    | 0x0     | Controls the standby modes of the DPP. [0]=DPPEN [1]=GPOEN [2]=GPOOUTEN [3]=VECTOROUTEN [4]=STIMEREN [5]=ATIMER0EN [6]=ATIMER1EN                                                   |

10

5

WO 2008/112207 11 PCT/US2008/003178

|            | · · · · · · · · · · · · · · · · · · · | ,        | ·             |                                                           |

|------------|---------------------------------------|----------|---------------|-----------------------------------------------------------|

|            |                                       |          |               | Monitors status of DPP. [0]=Toggle instruction in process |

|            |                                       | <u> </u> |               | [1]=Reserved                                              |

|            |                                       |          | 1             | [2]=SPI transaction pending                               |

|            |                                       |          |               |                                                           |

|            |                                       | 1        |               | [3]=Reserved                                              |

|            |                                       |          |               | [4]=DPP in idle state                                     |

|            |                                       |          |               | [5]=DPP in single step mode                               |

|            |                                       |          |               | [6]=Global Interrupt Disable Bit                          |

|            |                                       |          |               | [7]=Reserved                                              |

|            |                                       |          |               | [8]=Skipped vector flag (sticky)                          |

|            |                                       |          |               | [9]=STIMER wraparound (sticky)                            |

|            |                                       |          |               | [10]=ATIMER0 wraparound (sticky)                          |

|            |                                       |          |               | [11]=ATIMER1 wraparound (sticky)                          |

|            |                                       |          |               | [12]=Illegal opcode indication (sticky)                   |

|            |                                       | 1        |               | [13]=Indication of interrupt when not in                  |

| 1          |                                       |          |               | idle (sticky)                                             |

|            |                                       |          |               | [14]=Indication that SPI transaction                      |

|            |                                       | 1        |               | was lost (sticky)                                         |

| DDDOTATUS  | 0.2000                                | R/W      | 0x0           | [15]=Reserved                                             |

| DPPSTATUS  | 0x3C0C                                | IK/VV    | UXU           | Monitors status of DPP datapath.                          |

|            |                                       |          |               | Register is updated by all arithmetic                     |

|            |                                       |          |               |                                                           |

|            | 1                                     |          |               | instructions.                                             |

| ľ          |                                       |          |               | [0]=Zero Flag                                             |

|            |                                       | ľ        |               | [1]=Negative Flag                                         |

|            |                                       |          |               | [2]=Overflow Flag (sticky)                                |

| ASTATUS    | 0x3C0D                                | R/W      | 0x0           | [15-3]=Reserved                                           |

|            |                                       | İ        |               | Controls hardware debugging of the                        |

|            | 1                                     |          |               | DPP. All bits are self-resetting.                         |

|            |                                       |          | ļ             | [0]=HALT: Halts the and places it in                      |

|            |                                       |          | 1             | single step mode                                          |

|            |                                       |          |               | [1]=SINGLESTEP: Advances PC to                            |

|            |                                       | İ        |               | next instruction and remains in single                    |

|            |                                       |          |               | step mode                                                 |

|            |                                       |          |               | [2]=RESUME: Brings DPP out of                             |

|            |                                       |          |               | single step mode and resumes normal                       |

|            |                                       |          |               | operation                                                 |

| DPPDEBUG   | 0x3C0E                                | lw       | 0x0           | [15:3]=Reserved                                           |

| DITBLBOO   | OXOGOL                                | +        |               |                                                           |

|            |                                       |          | ĺ             |                                                           |

| DECED/ED   | 0.2005                                | l NA     | NA            | NA NA                                                     |

| RESERVED   | 0x3C0F                                | NA       | INA.          | Pixel Counter register. The register                      |

|            |                                       |          |               | can be cleared by toggle instructions                     |

|            |                                       |          |               |                                                           |

|            |                                       |          |               | and is updated automatically on every                     |

| STIMER     | 0x3C10                                | R/W      | 0xFFFF        | cycle when STIMER_EN is set.                              |

|            |                                       |          |               | Max count for STIMER. The STIMER                          |

|            |                                       | ]        |               | wraps around upon reaching                                |

| STIMER_MAX | 0x3C11                                | R/W      | 0xFFFF        | STIMER_MAX.                                               |

|            | 1 0 0040                              | 1        | 1             | •                                                         |

| RESERVED   | 0x3C12-<br>0x3C1F                     | NA NA    | <sub>NA</sub> | NA                                                        |

WO 2008/112207 12 PCT/US2008/003178

Table 2: Examples of Interrupt Controller Registers

| NAME       | ADDRESS | ACCESS | DEFAULT | DESCRIPTION                                                                         |

|------------|---------|--------|---------|-------------------------------------------------------------------------------------|

|            |         |        |         | Controls masking of all interrupts. The                                             |

|            |         |        |         | order of the interrupt bits are:                                                    |

|            |         |        |         | [0]=Debug Emulation                                                                 |

|            |         |        |         | [1]=Software Exception                                                              |

| 10.4.4.014 | 0000    | D 44/  | 0x0000  | [2]=Reserved                                                                        |

| IMASK      | 0x3C20  | R/W    | 0x0000  | [15-3]=General Purpose Interrupts Controls priority of interrupts being             |

|            |         |        |         | serviced. Bits in the register are set                                              |

|            |         |        |         | when interrupt service routine starts                                               |

|            |         |        |         | executing and are cleared by an RTI or                                              |

| PMASK      | 0x3C21  | R/W    | 0x0000  | RDS instruction.                                                                    |

|            |         |        |         | Latches incoming interrupts. Bits in the                                            |

|            |         |        |         | register are set when rising edge                                                   |

|            |         |        |         | interrupts are detected and are cleared                                             |

|            |         |        |         | at the start of the interrupt service                                               |

| ILAT       | 0x3C22  | R/W    | 0x0000  | routine.                                                                            |

|            | !       |        |         | Alias that allows for setting specific bits of the ILAT. The operation performed is |

|            | ļ       |        | ļ       | a read-modify-write operation. The new                                              |

|            |         | ļ      |         | ILAT value is the OR function of the old                                            |

| ILATSET    | 0x3C23  | l w    | NA      | ILAT and the value being written.                                                   |

| ILATOLI    | 0.0020  |        | 147     | Alias that allows for clearing specific                                             |

|            |         |        | ŀ       | bits of the ILAT. The operation                                                     |

|            |         | İ      |         | performed is a read-modify-write                                                    |

|            |         |        | 1       | operation. The new ILAT value is the                                                |

|            |         |        |         | ANDNOT function of the old ILAT and                                                 |

| ILATCLR    | 0x3C24  |        | NA      | the value being written.                                                            |

| IRQ0ADDR   | 0x3C30  | W      | None    | Vector for IRQ0                                                                     |

| IRQ1ADDR   | 0x3C31  | W      | None    | Vector for IRQ1                                                                     |

| IRQ2ADDR   | 0x3C32  | W      | None    | Vector for IRQ2                                                                     |

| IRQ3ADDR   | 0x3C33  | W      | None    | Vector for IRQ3                                                                     |

| IRQ4ADDR   | 0x3C34  | W      | None    | Vector for IRQ4                                                                     |

| IRQ5ADDR   | 0x3C35  | W      | None    | Vector for IRQ5                                                                     |

| IRQ6ADDR   | 0x3C36  | W      | None    | Vector for IRQ6                                                                     |

| IRQ7ADDR   | 0x3C37  | W      | None    | Vector for IRQ7                                                                     |

| IRQ8ADDR   | 0x3C38  | W      | None    | Vector for IRQ8                                                                     |

| IRQ9ADDR   | 0x3C39  | W      | None    | Vector for IRQ9                                                                     |

| IRQ10ADDR  | 0x3C3A  | W      | None    | Vector for IRQ10                                                                    |

| IRQ11ADDR  | 0x3C3B  | W      | None    | Vector for IRQ11                                                                    |

| IRQ12ADDR  | 0x3C3C  | W      | None    | Vector for IRQ12                                                                    |

| IRQ13ADDR  | 0x3C3D  | W      | None    | Vector for IRQ13                                                                    |

| IRQ14ADDR  | 0x3C3E  | W      | None    | Vector for IRQ14                                                                    |

| IRQ15ADDR  | 0x3C3F  | W      | None    | Vector for IRQ15                                                                    |

WO 2008/112207 13 PCT/US2008/003178

Table 3: Examples of Output Control Registers

| NAME        | ADDRESS | ACCESS | DEFAULT | DESCRIPTION                                           |

|-------------|---------|--------|---------|-------------------------------------------------------|

| OUTREG0     | 0x3C40  | R/W    | 0x0000  | Direct Access register for DPP outputs Bits[15:0]     |

| OUTREG1     | 0x3C41  | R/W    | 0x0000  | Direct Access register for DPP outputs Bits[31:16]    |

| OUTREG2     | 0x3C42  | R/W    | 0x0000  | Direct Access register for DPP outputs<br>Bits[47:32] |

| OUTREG3     | 0x3C43  | R/W    | 0x0000  | Direct Access register for DPP outputs Bits[63:48]    |

| OUTREG4     | 0x3C44  | R/W    | 0x0000  | Direct Access register for DPP outputs<br>Bits[79:64] |

| OUTEN0      | 0x3C48  | R/W    | 0x0000  | Enable register for DPP outputs Bits[15:0]            |

| OUTEN1      | 0x3C49  | R/W    | 0x0000  | Enable register for DPP outputs Bits[31:16]           |

| OUTEN2      | 0x3C4A  | R/W    | 0x0000  | Enable register for DPP outputs<br>Bits[47:32]        |

| OUTEN3      | 0x3C4B  | R/W    | 0x0000  | Enable register for DPP outputs Bits[63:48]           |

| OUTEN4      | 0x3C4C  | R/W    | 0x0000  | Enable register for DPP outputs Bits[79:64]           |

| OUTSTANDBY0 | 0x3C50  | R/W    | 0x0000  | Standby register for DPP outputs Bits[15:0]           |

| OUTSTANDBY1 | 0x3C51  | R/W    | 0x0000  | Standby register for DPP outputs Bits[31:16]          |

| OUTSTANDBY2 | 0x3C52  | R/W    | 0x0000  | Standby register for DPP outputs Bits[47:32]          |

| OUTSTANDBY3 | 0x3C53  | R/W    | 0x0000  | Standby register for DPP outputs Bits[63:48]          |

| OUTSTANDBY4 | 0x3C54  | R/W    | 0x0000  | Standby register for DPP outputs Bits[79:64]          |

WO 2008/112207 14 PCT/US2008/003178

Table 4: Examples of GPO Controller Registers

|                |         |        | CALL CALL |                                                                                                                                         |

|----------------|---------|--------|-----------|-----------------------------------------------------------------------------------------------------------------------------------------|

| NAME           | ADDRESS | ACCESS | DEFAULT   | DESCRIPTION                                                                                                                             |

|                |         |        |           | Low 16-bits of ATIMER0. The counter is updated every clock cycle when the GPO controller is enabled and                                 |

| ATIMERO_L0     | 0x3C60  | R/W    | 0xFFFF    | ATIMER0 is enabled                                                                                                                      |

| ATIMER0_HI     | 0x3C61  | R/W    | 0xFFFF    | High 16-bits of ATIMER0.                                                                                                                |

|                |         |        |           | Low 16-bits of ATIMER0 max count. The ATIMER0 wraps around to zero                                                                      |

| ATIMERO_MAX_LO | 0x3C62  | R/W    | 0xFFFF    | when the max count is reached.                                                                                                          |

| ATIMERO_MAX_HI | 0x3C63  | R/W    | 0xFFFF    | High 16-bits of ATIMER0 max count.                                                                                                      |

| ATIMER1 LO     | 0x3C64  | R/W    | 0xFFFF    | Low 16-bits of ATIMER1. The counter is updated every clock cycle when the GPO controller is enabled and the ATIMER1 is enabled          |

| ATIMER1 HI     | 0x3C65  | R/W    | 0xFFFF    | High 16-bits of ATIMER1.                                                                                                                |

| A THURST THE   |         |        |           | Low 16-bits of ATIMER1 max count. The ATIMER1 wraps around to zero                                                                      |

| ATIMER1_MAX_LO | 0x3C66  | R/W    | 0xFFFF    | when the max count is reached.                                                                                                          |

| ATIMER1_MAX_HI | 0x3C67  | R/W    | 0xFFFF    | High 16-bits of ATIMER1 max count.                                                                                                      |

| ATIMER_VALID0  | 0x3C68  | R/W    | 0x0000    | Enables GPO toggle entries [3:0]=TOGGLE3-0 FOR GPO0 [7:4]=TOGGLE3-0 FOR GPO1 [11:8]=TOGGLE3-0 FOR GPO2 [15:12]=TOGGLE3-0 FOR GPO3       |

| ATIMER VALID1  | 0x3C69  | R/W    | 0x0000    | Enables GPO toggle entries [3:0]=TOGGLE3-0 FOR GPO4 [7:4]=TOGGLE3-0 FOR GPO5 [11:8]=TOGGLE3-0 FOR GPO6 [15:12]=TOGGLE3-0 FOR GPO7       |

| ATIMER_VALID2  | 0x3C6A  | R/W    | 0×0000    | Enables GPO toggle entries [3:0]=TOGGLE3-0 FOR GPO8 [7:4]=TOGGLE3-0 FOR GPO9 [11:8]=TOGGLE3-0 FOR GPO10 [15:12]=TOGGLE3-0 FOR GPO11     |

| ATIMER VALID3  | 0x3C6B  | R/W    | 0x0000    | Enables GPO toggle entries [3:0]=TOGGLE3-0 FOR GPO12 [7:4]=TOGGLE3-0 FOR GPO13 [11:8]=TOGGLE3-0 FOR GPO14 [15:12]=TOGGLE3-0 FOR GPO15   |

| ATIMER_STICKY0 | 0x3C6C  | R/W    | 0×0000    | Sticky enable GPO toggle entries [3:0]=TOGGLE3-0 FOR GPO0 [7:4]=TOGGLE3-0 FOR GPO1 [11:8]=TOGGLE3-0 FOR GPO2 [15:12]=TOGGLE3-0 FOR GPO3 |

| ATIMER STICKY1 | 0x3C6D  | RW     | 0x0000    | Sticky enable GPO toggle entries [3:0]=TOGGLE3-0 FOR GPO4 [7:4]=TOGGLE3-0 FOR GPO5 [11:8]=TOGGLE3-0 FOR GPO6 [15:12]=TOGGLE3-0 FOR GPO7 |

| ATIMER_STICKY2 | 0x3C6E | R/W | 0x0000 | Sticky enable GPO toggle entries. [3:0]=TOGGLE3-0 FOR GPO8 [7:4]=TOGGLE3-0 FOR GPO9 [11:8]=TOGGLE3-0 FOR GPO10 [15:12]=TOGGLE3-0 FOR GPO11                                                              |

|----------------|--------|-----|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ATIMER_STICKY3 | 0x3C6F | R/W | 0x0000 | Sticky enable GPO toggle entries. [3:0]=TOGGLE3-0 FOR GPO12 [7:4]=TOGGLE3-0 FOR GPO13 [11:8]=TOGGLE3-0 FOR GPO14 [15:12]=TOGGLE3-0 FOR GPO15                                                            |

|                |        |     |        | Selects ATIMER0 or ATIMER1 for each GPO pin. A one specifies that ATIMER1 is used for comparisons. [0]=GPO0 [1]=GPO1 [2]=GPO2 [3]=GPO3 [4]=GPO4 [5]=GPO5 [6]=GPO6 [7]=GPO7 [8]=GPO8 [9]=GPO9 [10]=GPO10 |

| ATIMER SEL     | 0x3C70 | R/W | 0x0000 | [15:11]=RESERVED                                                                                                                                                                                        |

WO 2008/112207 16 PCT/US2008/003178

Table 5: Example of a GPO Toggle Entry Table (The complete table could continue in the same fashion for all remaining GPO pins)

| NAME         | ADDRESS | ACCESS | DEFAULT | DESCRIPTION                            |

|--------------|---------|--------|---------|----------------------------------------|

| GPO0_TOG0_LO | 0x3C80  | W      | none    | Low 16 bits of toggle0 entry for GPO0  |

| GPO0_TOG0_HI | 0x3C81  | W      | none    | High 16 bits of toggle0 entry for GPO0 |

| GPO0_TOG1_LO | 0x3C82  | w      | none    | Low 16 bits of toggle1entry for GPO0   |

| GP00_TOG1_HI | 0x3C83  | w      | none    | High 16 bits of toggle1entry for GPO0  |

| GPO0_TOG2_LO | 0x3C84  | W      | none    | Low 16 bits of toggle2entry for GPO0   |

| GPO0_TOG2_HI | 0x3C85  | w      | none    | High 16 bits of toggle2entry for GPO0  |

| GP00_T0G3L0  | 0x3C86  | w      | none    | Low 16 bits of toggle3entry for GPO0   |

| GPO0_TOG3HI  | 0x3C87  | W      | none    | High 16 bits of toggle3entry for GPO0  |

| GPO1_TOG0_LO | 0x3C88  | W      | none    | Low 16 bits of toggle0 entry for GPO1  |

| GPO1_TOG0_HI | 0x3C89  | W      | none    | High 16 bits of toggle0 entry for GPO1 |

| GPO1 TOG1 LO | 0x3C8A  | w      | none    | Low 16 bits of toggle1entry for GPO1   |

| GPO1_TOG1_HI | 0x3C8B  | W      | none    | High 16 bits of toggle1entry for GPO1  |

| GPO1_TOG2_LO | 0x3C8C  | w      | none    | Low 16 bits of toggle2entry for GPO1   |

| GPO1_TOG2_HI | 0x3C8D  | w      | none    | High 16 bits of toggle2entry for GPO1  |

| GPO1_TOG3LO  | 0x3C8E  | w      | none    | Low 16 bits of toggle3entry for GPO1   |

| GPO1_TOG3HI  | 0x3C8F  | W      | none    | High 16 bits of toggle3entry for GPO1  |

# Program Sequencer

5

10

As noted above, the program sequencer 106 of the DPP 102 may control the flow of the program execution. The program sequencer 106 may, for example, generate a fetch address for the program memory, receive the instruction from memory, decode the instruction, send control signals to the rest of the DPP units, and finally generate the next fetch address to be sent to the program memory. The program flow in the DPP may be typically linear, with the processor executing program instructions sequentially. The linear

flow may, however, vary occasionally when the program uses non-sequential program structures, such as those illustrated in Fig. 6.

As shown, examples of such non-sequential program structures that may be supported by the DPP 102 include "loops," "subroutines," "jumps," "interrupts and exceptions," and "idle." For loops, one sequence of instructions may, for example, execute several times using general purpose registers, arithmetic instructions, and conditional branching instructions. For subroutines, the processor may, for example, temporarily interrupt sequential flow to execute instructions from another part of memory. After completing the subroutine, the program flow may return to the instruction following the CALL instruction used execute the subroutine program. For jumps, program flow may, for example, transfer permanently to another part of memory. For interrupts and exceptions, a runtime event or instruction may, for example, trigger the execution of a subroutine. The program may, for instance, jump to the address specified in the interrupt vector table (IVT). For idle structures, an instruction may, for example, cause the processor to stop operating and hold its current state until an interrupt occurs. Then the processor may service the interrupt and continue normal execution.

The program sequencer 106 may manage execution of these program structures by selecting the address of the next instruction to execute. For example, the program pointer, also referred to as the program counter (PC), may couple with the RETS and RETI registers, which store return addresses for subroutines and interrupt service routines. In some embodiments, all addresses generated by the sequencer may, for example, be sixteen-bit memory instruction addresses. The program sequencer 106 may also support both conditional and non-conditional branching.

#### Branches

5

10

15

20

25

30

A branch may occur, for example, when a JUMP or CALL instruction begins execution at a new location other than the next sequential address. A JUMP or CALL instruction may, for example, transfer program flow to another memory location. In some embodiments, the difference between a JUMP and a CALL may be that a CALL may automatically write the next sequential program address into the RETS register. This push operation may make the address available for the CALL instruction's matching return instruction (RTS), allowing easy return from the subroutine. An RTS instruction may, for example, copy the content of the RETS register to the PC register and fetch a new instruction from that address.

In some embodiments, a JUMP instruction may be conditional, depending on the arithmetic flags set in the ASTATUS register (see Table 1 above) and the conditional options

WO 2008/112207 18 PCT/US2008/003178

used by the instruction. The ASTATUS register may, for example, be updated by every arithmetic instruction. In certain embodiments, if no condition is specified, the branch may always be taken. As an example, the supported conditions in the conditional instruction, *if* {!}

- o EQ: Equal to Zero. Evaluates as true if the zero flag in the ASTATUS register is 1 and the negative flag in the ASTATUS register is 0.

- o LT: Less than Zero. Evaluates as true if the zero flag in the ASTATUS register is 0 and the negative flag in the ASTATUS register is 1.

- o LTE: Less than or Equal to Zero. Evaluates as true if the zero or negative flag in the ASTATUS register is 1.

- o !: Indicates that the condition should evaluate to false for the branch to be taken.

In some embodiments, all types of JUMP and CALL instructions may be executed using absolute sixteen-bit addresses.

#### Subroutines

5

10

15

20

Subroutines may be code sequences that are constructed with the CALL and RTS instructions. Assuming that a stack pointer has been initialized properly, a typical subroutine call may, for example, include the following steps: (1) pass a parameter to a register used as an input by the subroutine, (2) execute the CALL instruction, (3) push all registers modified by the function onto the stack, (4) execute the body of subroutine, (5) pop the values from the stack back to their original registers, (6) execute the RTS instruction, and (7) Return to next sequential instruction following original CALL instruction.

An example of the sub-routine definition and usage is given below.

```

25

/* parent function */

/*R0=0*/

/*R1 used as stack pointer*/

/*R4 used as input/output parameter*/

/*R6 used as temporary register*/

R4 = 0x1234;

/*pass a parameter */

30

/*execute subroutine*/

CALL(MYFUNCTION);

/*save return value to memory location RESULTO */

[R0+RESULT0] = R4;

JUMP(SOMEWHERE);

/*jump to elsewhere in code*/

/*subroutine label */

MYFUNCTION:

/*pushing R6 register onto stack since this register is

[--R1]=R6;

35

modified*/

/*loading data0 from data memory to R6*/

R6=[R0+DATA0];

/*Adding R6 to register passed*/

R4=R4+R6;

/*popping R6 from stack to restore state on exit from

R6 = [R1 + +];

40

subroutine */

/* return from subroutine */

RTS;

```

In addition to redirecting the program flow to the MYFUNCTION subroutine above,

a CALL instruction may also write the return address into the RETS register automatically. The RETS register may hold the address where program execution is to resume after the RTS instruction executes. In the above example, this is the location that holds the "[R0+RESULT0] = R4;" instruction. The return address need not be passed to the stack in the background. Rather, the RETS register may function as single-entry hardware stack. This scheme may thus enable "leaf functions" (subroutines that do not contain further CALL instructions) to execute with less possible overhead, as no bus transfers need to be performed. If a subroutine calls other subroutines, it may temporarily push the content of the RETS and other registers used by the master subroutine onto the stack.

In some embodiments, the push and pop instructions may be omitted from the subroutines by instituting a programming methodology in which certain registers are dedicated as temporary variables and subroutine arguments. For instance, if the R6 register in the above example did not have to be restored for the main code, the push and pop instructions could have been omitted.

#### Standby Register (DPPSTANDBY)

5

10

15

20

25

30

The DPPSTANDBY register (see Table 1 above) may, for example, selectively enable all major features of the DPP 102. In some embodiments, all functionality may be turned off (0x0000) at reset by default, and before any DPP related operation can take place, the appropriate functions may be enabled in the DPPSTANDBY register. To enable a specific function, the corresponding bit may be set to "1" in the standby register. In some embodiments, the functionality of the individual bits of the DPPSTANDBY may, for example, be as follows:

- [0]→DPPEN: Enable bit for the DPP. When the bit is cleared, only the DPPSTANDBY register is being clocked. In order to enable the program sequencer and the rest of the DPP, the DPPEN bit must be set.

- [1]→GPOEN: Enable bit for the GPO controller. The GPO controller contains the functionality of the ATIMER\* registers and GPO\* registers. When the bit is cleared, the clock to the GPO controller is completely disabled. As a result, ATIMER0 and ATIMER1 are not updated on the rising edge of the clock and the registers are unresponsive to register write transactions.

- [2]→GPOOUTEN: Enable bit for the GPO outputs from the DPP. When this bit is cleared, the GPO output levels are taken from the OUTSTANDBY register. When the bit is set, the GPO driven output levels are taken from the OUTREG register. This

bit functions as an override bit for the OUTEN registers. The bit can be used to quickly enable and disable all GPO outputs in one clock cycle.

- [3]→VECTOROUTEN: Enable bit for the vector outputs from the DPP. When this bit is cleared, the vector output levels are taken from the OUTSTANDBY register. When the bit is set, the vector driven output levels are taken from the OUTREG register. This bit functions as an override bit for the OUTEN registers. The bit can be used to quickly enable and disable all vector driven outputs in one clock cycle.

- [4]→STIMEREN: Enable bit for the synchronous timer. The timer updates on every rising edge of the DPP clock as long as the STIMEREN bit is set. The STIMER can be stopped with the STIMEREN bit to reduce power and to reduce noise.

- [5]→ATIMER0EN: Enable bit for ATIMER0. The timer updates on every rising edge of the DPP clock as long as the ATIMER0EN bit is set and the GPOEN bit is set. The ATIMER0 can thus be stopped selectively to reduce power and reduce noise.

- [6]→ATIMER1EN: Enable bit for ATIMER1. The timer updates on every rising edge of the DPP clock as long as the ATIMER1EN bit is set and the GPOEN bit is set. The ATIMER1 can thus be stopped selectively to reduce power and noise.

#### Program Flow Status Register (DPPSTATUS)

The DPPSTATUS register (see Table 1 above) may, for example, contain information regarding the present execution status of different units of the DPP 102 and may be used to debug run away code and faulty hardware configurations. The eight least significant bits (LSBs) of the DPPSTATUS register may, for instance, contain status flags that are updated on every clock cycle or on every use of certain specific instructions or transactions. The eight most significant bits (MSBs) may, for example, be sticky bits, which, once set, can be reset only by a reset event or by explicitly writing to the DPPSTATUS register. In some embodiments, the functionality of the individual DPPSTATUS bits may, for example, be as follows:

#### **IMMEDIATE BITS:**

5

15

20

25

30

- [0]→TOGGLE\_PENDING: A set bit indicates that a toggle instruction has been executed and the DPP is waiting for a toggle count match to continue the program execution.

- [2]→EXT\_TRANS\_PENDING: An external transaction tried to access the memory but was delayed in a one stage transaction buffer until the DPP stops accessing the memory.

- [4]→IDLE: The DPP is currently in an idle state awaiting an external interrupt signal to start code execution.

• [5] SINGLESTEP\_MODE: The DPP is in single step mode and will advance one instruction at a time. The mode is reached by inserting a breakpoint instruction in the program or by writing to the DPPDEBUG register.

#### STICKY BITS:

5

10

20

35

- [8] SKIPPED\_MATCH: Indicates that a toggle instruction was executed, for which the toggle count value was less than the STIMER at the time of the initial execution. This is generally an undesirable situation and is thus flagged.

- [9] > STIMER\_WRAPAROUND: Indicates that the STIMER wrapped around from STIMER MAX to zero.

- [10]→ATIMER0\_WRAPAROUND: Indicates that the ATIMER0 wrapped around from ATIMER0\_MAX to zero.

- [11]→ATIMER1\_WRAPAROUND: Indicates that the ATIMER1 wrapped around from ATIMER1 MAX to zero.

- [12] > ILLEGAL\_OPCODE: Indicates that an illegal opcode was entered. This bit can be used for software debugging to indicate execution of an uninitialized program memory or a jump to a data section of the memory.

- [13]→INTERRUPT: Indicates that the normal program flow was interrupted by an external interrupt while the DPP was running. In very timing exact applications, this is generally an undesirable situation as it would indicate that the foreground process or the interrupt process would get delayed. For most applications, this bit can be ignored since DPP supports nested as well as non-nested interrupts, and the correct program flow order is guaranteed under all interrupt sequences.

- [14]→EXT\_LOST: Indicates that an external transaction was lost. If an external transaction and an internal transaction arrive at the memory simultaneously, the DPP transaction has preference. The external transaction then gets latched into a one stage buffer until the DPP stops accessing the memory. If a second external transaction arrives before the first transaction has been completed, it overwrites the first instruction in the transaction buffer, causing the first transaction to be permanently lost.

- Bits 15, 7, 6, 3, 1 of the DPPSTATUS may be reserved and can thus be ignored for he purposes of this description.

# Arithmetic Status Register (ASTATUS)

The ASTATUS register (see Table 1 above) may, for example, monitor the result of the most recently executed arithmetic instruction. In some embodiments, for example, the

WO 2008/112207 22 PCT/US2008/003178

following flags may be used by the conditional branch instruction, and may also be used for general program monitoring.

- [0]→ZERO\_FLAG: This bit is set when all bits of the arithmetic instruction result are zero.

- [1] NEGATIVE\_FLAG: This bit is set when the most significant bit of the arithmetic instruction result is 1.

- [2]→OVERFLOW\_FLAG: This bit is set when the most significant bit of the two input operands are the same and the most significant bit of the result is different from the that of the two input operands. Overflow could occur in addition when adding two large positive numbers or adding two large negative numbers, but could not happen when adding a positive and negative number.

# Output Control Register (OUTREGx, OUTENx, OUTSTANDBYx)

The output control registers (see table 3 above) may, for example, directly control the outputs of the DPP 102. Each DPP output may, for instance, be controlled by one bit in each of the OUTREG, OUTEN, and OUTSTANDBY registers. In some embodiments, there may, for example, be five each of the OUTREG, OUTEN, and OUTSTANDBY registers, each sixteen-bits wide and controlling sixteen outputs. Outputs from the GPO controller and the toggle instructions may, for instance, be combined to form a single wide output vector that may be controlled by the output control registers. The GPO driven outputs may, for example, be situated above the MSB of the vector driven outputs in the final output vector. For example, if there are fifty-seven pins driven by the programmable vector toggle instructions and eleven pins driven by the GPO controller, the DPP output mapping may be:

- Bits 0 to 56 are driven by the programmable vector toggle instructions

- Bits 57 to 67 are driven by the GPO controller

In the code example below, bit zero and bit fifty-seven would be enabled, while keeping all other outputs placed in a standby state.

OUTEN0=0x0001; //Bits 15-0 OUTEN3=0x0400; //Bits 48-63

5

20

25

Fig. 7 shows an example of a hardware control mechanism including a multiplexer 702 that may by used in conjunction with the OUTREG register 704, the OUTSTANDBY register 706, and the OUTEN register 708 to enable and disable the outputs 120 on a pin by pin basis. In some embodiments, all of the outputs 120 may, by default, wake up in a disabled state with the default standby polarity set to zero. In the example of Fig. 7, each of the sixty-eight bits of the OUTENX register 708 controls whether a corresponding bit of the

WO 2008/112207 23 PCT/US2008/003178

OUTSTANDBY register 706 or a corresponding bit of the OUTREGX register 704 is provided on a corresponding one of the outputs 120. Thus, by writing appropriate values to the OUTENX register 708, selected subsets of either or both of the vector outputs and the GPO driven outputs may be provided on the outputs 120, with the states of the other outputs being set based upon the corresponding bits of the OUTSTANDBYX register 706. This arrangement may therefore allow an additional level of flexibility in controlling the content of the outputs 120 in certain circumstances, for example, in embodiments where it may be relatively difficult to reconfigure the logic that controls the vector toggle instructions and/or the logic that controls the GPO outputs.

# Synchronous Timing Engine

5

10

15

20

25

30

As discussed above in connection with Fig. 3, the synchronous timer 114 may, for example, comprise a free running clock cycle counter, e.g., toggle counter 306, and a cycle counter comparator 308 that may be integrated into the program sequencer 106. When the DPP 102 encounters a special toggling instruction, the DPP program counter may, for example, be stalled until the toggle counter 306 reaches the value specified in the toggling instruction line. When a match is found, an indication may be sent to the DPP's output event execution unit 118, and the outputs 120 may be toggled according to the type of toggling instruction and the data bits set in the instruction line.

The DPP architecture may, for example, support the following instruction types: (1) TOGGLE\_VECTOR and (2) FORCE\_VECTOR. In some embodiments, the DPP 102 may advantageously support a very wide instruction word, so every one of the software driven outputs can be toggled or forced to particular values with a single instruction. After the outputs have been toggled or forced, the program counter may advance to the next sequential instruction line, and the program fetching may resume to normal operation.

Fig. 8 is a flowchart illustrating an example of an execution flow 800 that may be used to generate toggle pulses on the outputs 120. As shown, at steps 802 and 804, an instruction is fetched from the program memory 108 and decoded for execution. If, at a step 806, it is determined that the instruction is a "toggle" instruction, then the flow 800 proceeds to a step 808, where it waits until the comparator 308 has determined that the toggle counter 306 has reached the "toggle count" specified in the instruction. Once the toggle counter 306 has reached the specified toggle count, the flow proceeds to a step 810, where certain outputs 120 of the DPP 102 are simultaneously toggled in the manner specified by the instruction. The flow then returns to the steps 802 and 804 where the next program instruction is fetched and decoded.

WO 2008/112207 24 PCT/US2008/003178

If, at the step 806, it is determined that the fetched instruction is not a toggle instruction, then the routine proceeds to a step 812, where the instruction is carried out to as to control the program flow in the manner specified. Examples of the manner in which particular toggle instructions and program flow instructions may be configured and carried out in various embodiments are described below. Accordingly, using the configuration and functionality illustrated in Figs. 3 and 8, the toggle counter 306 and a custom toggle instruction set (described below) may be used to keep the DPP 102 in lock step execution. Advantageously, in the example shown, the flow is capable of toggling all output pins on any given clock cycle. In some embodiments, a single instruction may be defined for toggling all of the bits.

The toggle counter 306 may be reset, for example, by explicitly writing to the STIMER register (see Table 1 above) or by using the "(C)" option with a toggle instruction, as described below. By using the "(C)" option, the toggle counter 306 may be cleared before the instruction is executed. For example, in some embodiments, executing the instruction shown below may cause the toggle counter 306 to be reset and the pins V1 and V2 to toggle immediately:

TOGGLE\_VECTOR (0: V1, V2) (C);

5

10

15

20

25

30

The counter's maximum count value may, for example, be "65535." When the counter reaches its maximum value, the counter may wrap around and start counting from zero. When this occurs, the sticky wraparound flag may be raised in the DPP status register, DPPSTATUS. To help in program debugging, if the STIMER value is less than the toggle value programmed in the toggle instruction, the sticky skipped-vector status flag may be set in the DPP status register.

### Synchronous Timer Configuration Registers

The DPP synchronous timer 306 may, for example, have two registers with direct control over the toggle matching: STIMER and STIMER\_MAX (see Table 1 above). In addition, in some embodiments, the counter 306 may also be stopped and started by writing to the DPPSTANDBY register. The STIMER register may, for example, represent the free running clock cycle counter and may be incremented on every rising edge of the clock as long as the enable bit for the counter, STIMEREN, is set in the DPPSTANDBY register. The STIMER register may, for example, be written to explicitly using a load immediate instruction, a load MMR instruction, a POP instruction, or an externally generated write transaction. The register may also be cleared, for example, by using the "(C)" option in one of the toggle instructions.

The STIMER\_MAX register may, for example, control the wraparound value of the toggle counter 306. The default may be for the toggle counter 306 to wraparound when it reaches 0xFFFF, for example. In some embodiments, by programming this value, the maximum value of the toggle counter 306 may be modified, thus shortening maximum count in certain applications.

### Interrupt Controller

5

10

15

20

25

30

The interrupt controller 104 of the DPP 102 may manage the execution and priority of interrupts and exceptions. An "interrupt" is an event that changes normal processor instruction flow and is asynchronous to program flow. The DPP interrupt controller 104 may, for example, support up to sixteen independent interrupt service routines. In some embodiments, the main components of the interrupt control system may, for example, include the following:

- Interrupt Vector Table: Comprising a set of sixteen sixteen-bit program pointers, one for each interrupt.

- ILAT: Latches all interrupt events regardless of masking

- IMASK: Allows for user controller masking of interrupts

- PMASK: Keeps track of interrupt service routine execution in case of nested interrupts.

- RETI: Hardware registers that stores the next sequential PC whenever an interrupt service routine starts executing

- RTI Instruction: Together with RETI, provides a method for returning to the PC executed before the interrupt happened.

Fig. 9 illustrates an example of basic steps that may be involved in executing an interrupt service routine (ISR) using the DPP 102.