# (19)中华人民共和国国家知识产权局

# (12)实用新型专利

(10)授权公告号 CN 210296297 U (45)授权公告日 2020.04.10

(21)申请号 201921741191.1

(22)申请日 2019.10.16

(73)专利权人 长鑫存储技术有限公司 地址 230000 安徽省合肥市经济技术开发 区翠微路6号海恒大厦630室

(72)发明人 韩清华

(74)专利代理机构 北京律智知识产权代理有限 公司 11438

代理人 龙威壮 孙宝海

(51) Int.CI.

*H01L* 21/336(2006.01) *H01L* 29/78(2006.01)

(ESM)同样的发明创造已同日申请发明专利

权利要求书1页 说明书6页 附图11页

#### (54)实用新型名称

存储器及半导体器件

#### (57)摘要

本实用新型公开一种存储器及半导体器件。 该半导体器件包括:衬底,在所述衬底上设置绝 缘的基台;鳍,设置于所述基台上表面;第一介电 层,设置在相邻的鳍之间,使各个鳍独立存在;晶 体管,设置在鳍内,与鳍成一定的角度交叉。可以 采用体硅为衬底制作半导体器件,并且整个制作 工艺简单,该低漏电流的半导体器件的成本较 低。

1.一种半导体器件,其特征在于,包括:

衬底,在所述衬底上设置绝缘的基台;

鳍,设置于所述基台上表面;

第一介电层,设置在相邻的鳍之间,使各个鳍独立存在;

晶体管,设置在鳍内,与鳍成一定的角度交叉。

- 2.根据权利要求1所述的半导体器件,其特征在于,所述鳍为竖板状,所述基台为沿所述鳍的底部延伸的条形凸台。

- 3.根据权利要求2所述的半导体器件,其特征在于,所述基台与鳍相连的竖直部分的厚度的取值范围为10-100nm。

- 4.根据权利要求2所述的半导体器件,其特征在于,所述基台的水平部分的厚度的取值范围为5-60nm。

- 5.根据权利要求1所述的半导体器件,其特征在于,所述晶体管为三极管或二极管。

- 6.根据权利要求1所述的半导体器件,其特征在于,所述鳍与所述第一介电层之间还设置有保护膜。

- 7.根据权利要求6所述的半导体器件,其特征在于,所述保护膜为氮化硅。

- 8.根据权利要求1所述的半导体器件,其特征在于,所述衬底为硅、碳化硅或锗硅衬底。

- 9.根据权利要求1所述的半导体器件,其特征在于,所述晶体管与鳍成一定的角度为15度到90度。

- 10.一种存储器,其特征在于,包括如权利要求1至9任一项所述的半导体器件。

# 存储器及半导体器件

#### 技术领域

[0001] 本实用新型总体来说涉及一种半导体技术,具体而言,涉及一种存储器及半导体器件。

### 背景技术

[0002] DRAM存储器中的存储单元对晶体管漏电流特别敏感,晶体管的漏电流越小则存储单元的保留时间(retention time)和感测裕度(sensing margin)越好。其中,栅诱导漏极泄漏电流(GIDL)对晶体管的可靠性影响较大。

[0003] 在半导体制作工艺中,通常采用S0I (Silicon-On-Insulator) 技术来实现降低晶体管的漏电流的效果。S0I技术通常是在绝缘体上形成一层半导体薄膜,然后再在半导体薄膜上制作出晶体管,这样能显著降低晶体管的漏电流的产生。但是由于S0I衬底的加工难度大、成本较高,采用S0I技术加工出的半导体芯片的成本也相应较高。成本过高的S0I技术不宜用于生产DRAM (动态随机存取存储器) 存储器。

[0004] 因此,亟需一种能在体硅上加工出漏电流小的晶体管的生产工艺。

[0005] 在所述背景技术部分公开的上述信息仅用于加强对本实用新型的背景的理解,因此它可以包括不构成对本领域普通技术人员已知的现有技术的信息。

## 实用新型内容

[0006] 在实用新型内容部分中引入了一系列简化形式的概念,这将在具体实施方式部分中进一步详细说明。本实用新型内容部分并不意味着要试图限定出所要求保护的技术方案的关键特征和必要技术特征,更不意味着试图确定所要求保护的技术方案的保护范围。

[0007] 本实用新型的一个主要目的在于克服上述现有技术的至少一种缺陷,提供一种半导体器件,其包括:

[0008] 衬底,在所述衬底上设置绝缘的基台:

[0009] 鳍,设置于所述基台上表面:

[0010] 第一介电层,设置在相邻的鳍之间,使各个鳍独立存在;

[0011] 晶体管,设置在鳍内,与鳍成一定的角度交叉。

[0012] 根据本实用新型的一个实施例,所述鳍为竖板状,所述基台为沿所述鳍的底部延伸的条形凸台。

[0013] 根据本实用新型的一个实施例,所述基台与鳍相连的竖直部分的厚度的取值范围为10-100nm。

[0014] 根据本实用新型的一个实施例,所述基台的水平部分的厚度的取值范围为5-60nm。

[0015] 根据本实用新型的一个实施例,所述晶体管为三极管或二极管。

[0016] 根据本实用新型的一个实施例,所述鳍与所述第一介电层之间还设置有保护膜。

[0017] 根据本实用新型的一个实施例,所述保护膜为氮化硅。

- [0018] 根据本实用新型的一个实施例,所述衬底为硅、碳化硅或锗硅衬底。

- [0019] 根据本实用新型的一个实施例,所述晶体管与鳍成一定的角度为15度到90度。

- [0020] 本实用新型还提出了一种存储器,其包括如上所述的半导体器件。

- [0021] 由上述技术方案可知,采用上述半导体器件的优点和积极效果在于:

[0022] 鳍的底部具有绝缘的基台,鳍的两侧具有绝缘的第一介电层,因此鳍被绝缘材料所包围,实现了鳍与衬底之间的绝缘。以鳍为基底,在鳍内制作出晶体管,晶体管相应地也被绝缘材料所包围,晶体管的漏电流减小,尤其是栅诱导漏极泄漏电流(GIDL)能显著降低。由于可以采用体硅为衬底制作该半导体器件,并且整个制作工艺简单,低漏电流的半导体器件的成本较低。这种方法特别适合制作DRAM存储器。

#### 附图说明

[0023] 通过结合附图考虑以下对本实用新型的优选实施例的详细说明,本实用新型的各种目标、特征和优点将变得更加显而易见。附图仅为本实用新型的示范性图解,并非一定是按比例绘制。在附图中,同样的附图标记始终表示相同或类似的部件。其中:

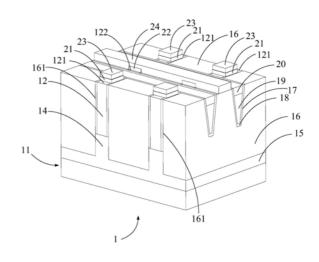

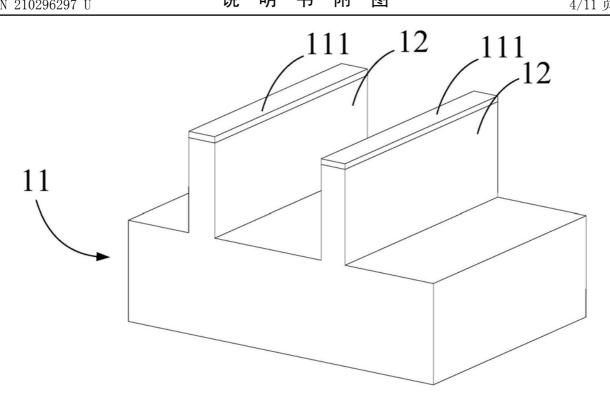

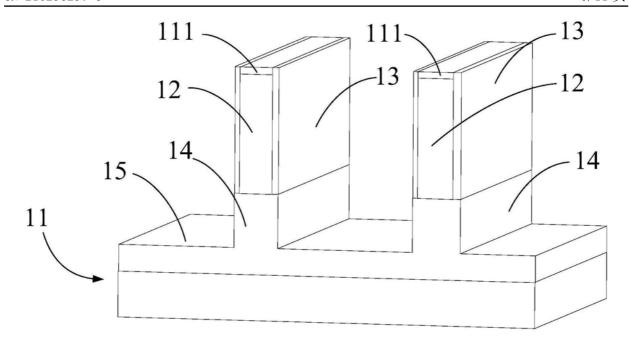

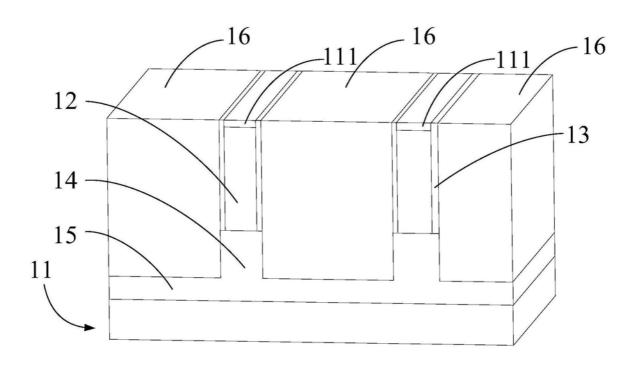

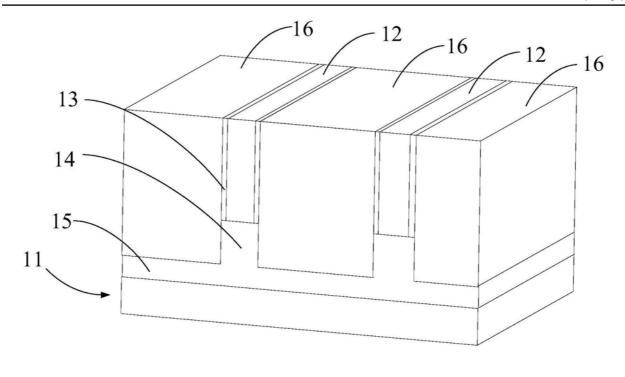

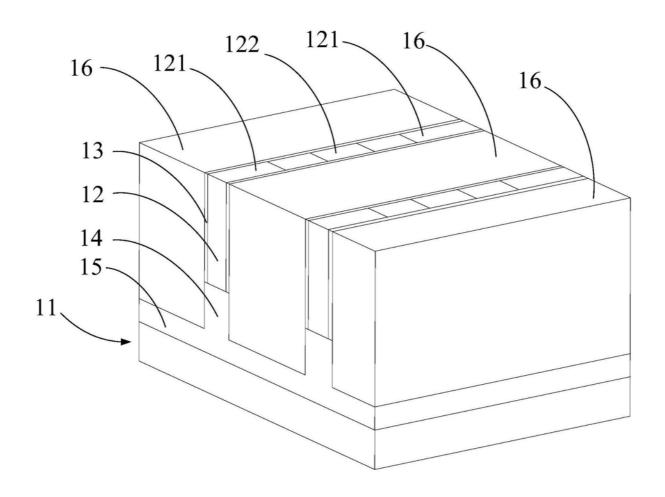

[0024] 图1是根据一示例性实施方式示出的一种半导体器件的立体示意图;

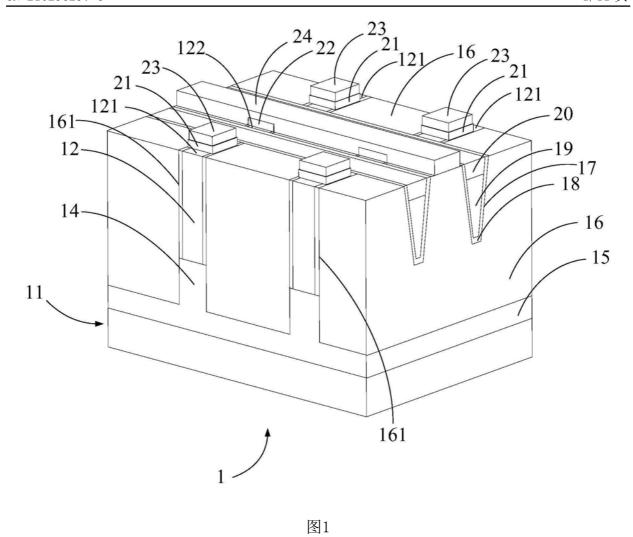

[0025] 图2是根据一示例性实施方式示出的一种半导体器件的全剖示意图;

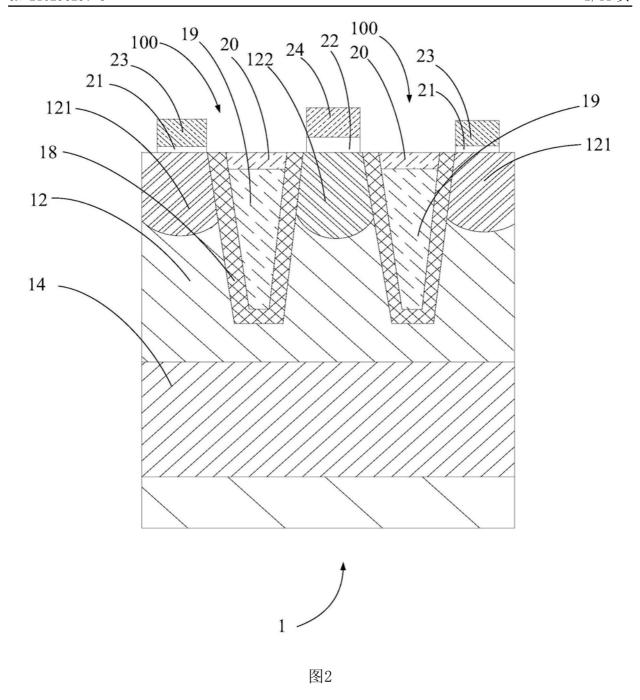

[0026] 图3是根据一示例性实施方式示出的一种制造半导体器件的方法的流程图;

[0027] 图4是根据一示例性实施方式示出的进行步骤S1后的半导体器件半成品的全剖示意图:

[0028] 图5是根据一示例性实施方式示出的进行步骤S2后的半导体器件半成品的全剖示 意图:

[0029] 图6是根据一示例性实施方式示出的进行步骤S31后的半导体器件半成品的全剖示意图;

[0030] 图7是根据一示例性实施方式示出的进行步骤S32后的半导体器件半成品的全剖示意图;

[0031] 图8是根据一示例性实施方式示出的进行步骤S4后的半导体器件半成品的全剖示 意图:

[0032] 图9是根据一示例性实施方式示出的进行步骤S5后的半导体器件半成品的全剖示 意图:

[0033] 图10是根据一示例性实施方式示出的进行步骤S6后的半导体器件半成品的全剖示意图:

[0034] 图11是根据一示例性实施方式示出的进行步骤S71后的半导体器件半成品的全剖示意图;

[0035] 图12是根据一示例性实施方式示出的进行步骤S72后的半导体器件半成品的全剖示意图;

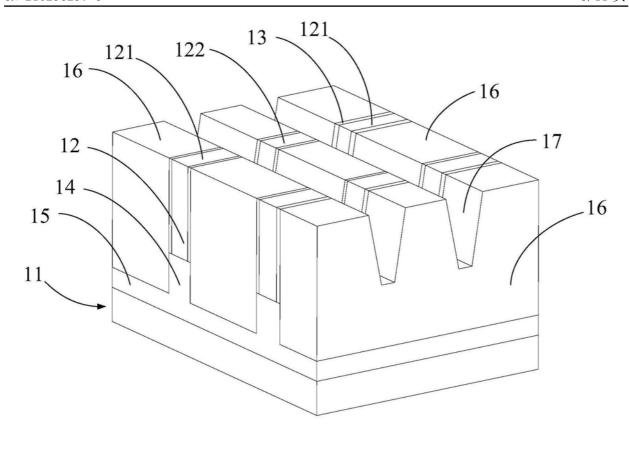

[0036] 图13是根据一示例性实施方式示出的进行步骤S73中沉积第二介电层后的半导体器件半成品的全剖示意图:

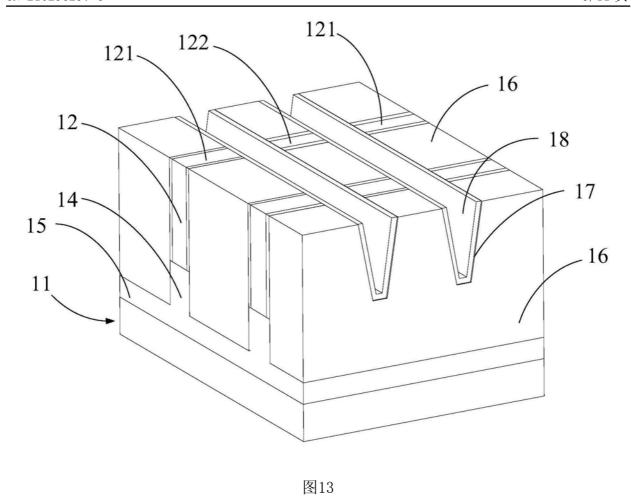

[0037] 图14是根据一示例性实施方式示出的进行步骤S73中形成第一电极后的半导体器件半成品的全剖示意图:

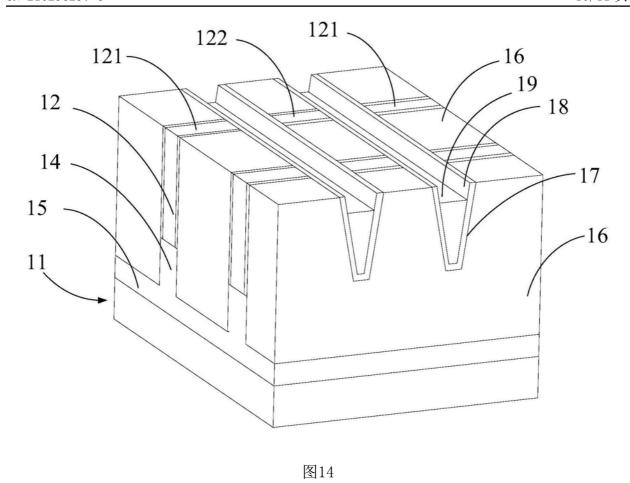

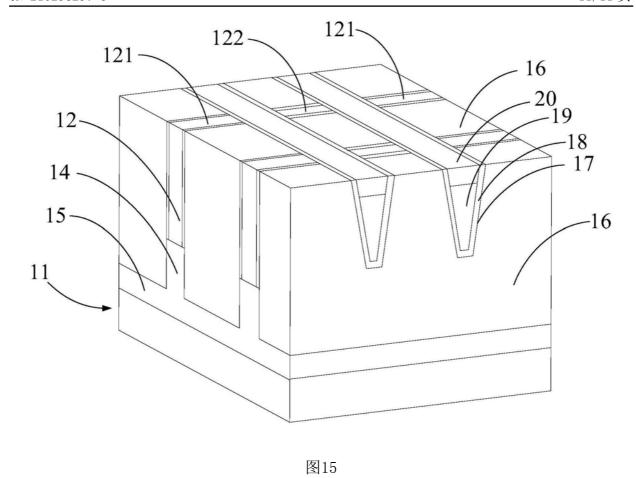

[0038] 图15是根据一示例性实施方式示出的进行步骤S73中沉积第三介电层后的半导体器件半成品的全剖示意图;

[0039] 其中,附图标记说明如下:

[0040] 1、半导体器件;11、衬底本体;111、保护层;100、晶体管;12、鳍;121、第一掺杂区;122、第二掺杂区;13、保护膜;14、基台;15、绝缘层;16、第一介电层;17、沟槽;18、第二介电层;19、第一电极;20、第三介电层;21、第一多晶硅层;22、第二多晶硅层;23、第二电极;24、第三电极;161、缝隙。

## 具体实施方式

[0041] 现在将参考附图更全面地描述示例实施方式。然而,示例实施方式能够以多种形式实施,且不应被理解为限于在此阐述的实施方式;相反,提供这些实施方式使得本实用新型将全面和完整,并将示例实施方式的构思全面地传达给本领域的技术人员。图中相同的附图标记表示相同或类似的结构,因而将省略它们的详细描述。

[0042] 本实施例公开了一种存储器。该存储器可以是DRAM存储器。该储存器中包括至少一个半导体器件1,图1和图2展示了该半导体器件1。

[0043] 参照图3,图3显示了本实施例中的一种半导体器件1的制作方法。该制作方法包括步骤S1~步骤S7。

[0044] 参照图4,步骤S1:在衬底的表面蚀刻出鳍12;

[0045] 衬底可以为衬底为硅、碳化硅或锗硅衬底。该衬底优选为体硅,体硅的成本低廉。衬底可以是大致的平板状。衬底的表面上预先形成一层保护层111,保护层111可以是氮化硅薄膜。在蚀刻衬底时可以是采用干刻法或湿刻法将在衬底上不需要形成鳍12的区域进行蚀刻,而对需要形成鳍12的区域进行保留,从而在蚀刻薄衬底后形成凸出于衬底本体11表面的鳍12。

[0046] 单个鳍12构造为竖板结构,该竖板不限于限制为平板,竖板的表面也不限于平面,竖板的表面还可以是曲面等不规则的面,在此不做限制。鳍12优选为直条形的竖板。衬底是N阱型或P阱型衬底。P阱型衬底中注入了三价杂质离子,例如掺入硼、铟、镓离子,N阱型衬底中注入了五价杂质离子,例如磷、砷、锑离子。鳍12的导电类型与衬底相同,即两者同为P阱型或N阱型。

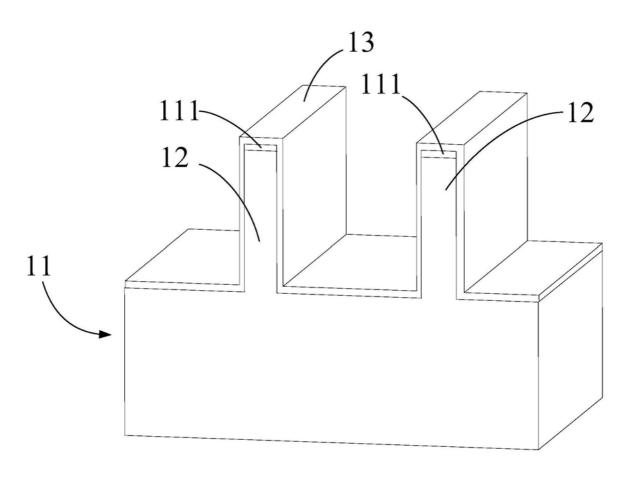

[0047] 参照图5,步骤S2:在鳍12上形成一层用于防止鳍12氧化的保护膜13;

[0048] 保护膜13完全覆盖鳍12,图1以及图5~15中均未展示出覆盖在鳍12侧端面上的保护膜13。保护膜13可以是通过化学气相沉积工艺在鳍12的表面上形成的。保护膜13覆盖在鳍12的各个侧壁和顶壁上。保护膜13的厚度可以是3~5nm。保护膜13优选为硅的氮化物,例如氮化硅。氮化硅可以是由二氯硅烷(SiH<sub>2</sub>C1<sub>2</sub>)和氨气(NH<sub>3</sub>)在高温下反应生成的。

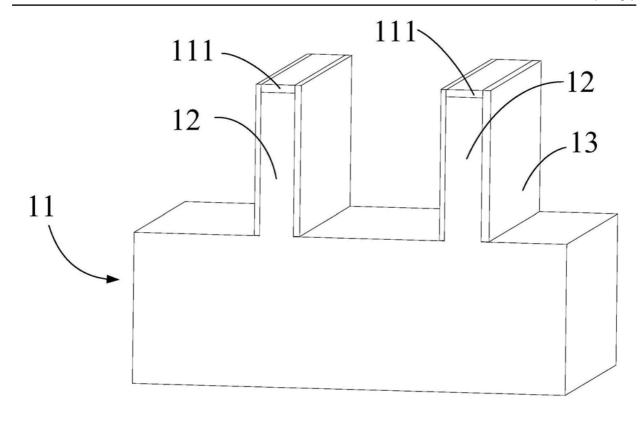

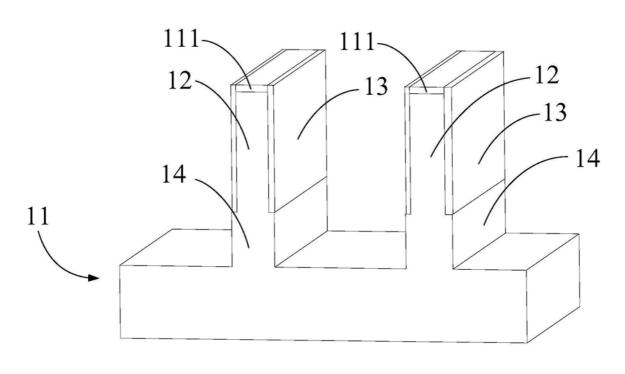

[0049] 参照图6、7,步骤S3:至少对鳍12周围的衬底本体11进行蚀刻,以在鳍12底部形成凸出于衬底本体11的基台14;

[0050] 对鳍12周围的衬底本体11进行蚀刻,使得该衬底进一步变薄从而使得鳍12下方的部分暴露出来形成基台14。基台14凸出于衬底主体。基台为沿鳍的底部延伸的条形凸台。在蚀刻衬底的过程中,需要避免将鳍12上的保护膜13蚀刻掉,优选采用干刻法进行蚀刻。

[0051] 参照图8,步骤S4:氧化基台14;

[0052] 在该步骤中,可以是通过热氧化的方法将基台14氧化。先将衬底置于氧化炉内,将氧化炉中充满干燥的氧气,然后将氧化炉内温度升高以使得氧气氧化衬底上未覆盖保护膜13的基台14。基台14通常需要完全被氧化。由于在基台14的热氧化过中,通常会将衬底未覆盖保护膜13的区域的表面都氧化而形成一层绝缘层15。此时,该绝缘层15和基台14均为硅的氧化物,例如二氧化硅。而鳍12上覆盖了保护膜13,该保护膜13能防止鳍12被氧化。

[0053] 基台与鳍相连的竖直部分的厚度的取值范围为10-100nm,基台的水平部分的厚度的取值范围为5-60nm,氧化的温度的取值范围为500-1200°、这样,基台的材质能被完全氧化成二氧化硅。采用热氧化方法制备的二氧化硅是无定形结构,电阻率高达 $1\times10^{14}\sim1\times10^{16}$   $\Omega$  gcm,基台具有较好的绝缘性能。

[0054] 参照图9,步骤S5:在该衬底的表面沉积第一介电层16,该第一介电层16的厚度至少大于基台14的高度;

[0055] 第一介电层16的材料可以是硅的氧化物,例如二氧化硅。第一介电层16可以由化学气相沉积工艺制成。第一介电层16可以是由二氯硅烷(SiH<sub>2</sub>Cl<sub>2</sub>)和臭氧(0<sub>3</sub>)在高温下反应生成的。第一介电层16的厚度大于基台14的高度。这样,鳍12的两侧均填充有第一介电层16。鳍12嵌入在第一介电层16的缝隙161中。

[0056] 参照图10,步骤S6:去除鳍顶部的保护膜并使第一介电层16的上表面与鳍12的顶面平齐:

[0057] 可以是采用抛光制程来使得第一介电层16的上表面与鳍12的顶面平齐。该抛光制程可以是采用化学机械抛光制程(Chemical Mechanical Polishing,CMP)。在抛光制程中还能去除鳍12顶部的保护膜13和保护层111以使得鳍12顶部暴露出来。

[0058] 参照图1、2,步骤S7:在鳍12内制作出晶体管100;

[0059] 在该步骤中,可以采用现有的晶体管制作工艺以鳍12为基底在鳍12内加工出晶体管100。晶体管100与鳍12成一定的角度交叉,该角度优选为15度到90度。该晶体管100可以是三极管,也可以是二极管。鳍12的底部具有绝缘的基台14,鳍12的两侧具有绝缘的第一介电层16,因此鳍12被绝缘材料所包围,实现了鳍12与衬底之间的绝缘。以鳍12为基底,在鳍12内制作出晶体管100,晶体管100相应地也被绝缘材料所包围,晶体管100的漏电流减小。尤其是,当晶体管为三极管时,栅诱导漏极泄漏电流(GIDL)能显著降低。由于该方法可以采用体硅为衬底制作半导体器件1,并且整个制作工艺简单,采用该方法所制成的低漏电流半导体器件1的成本较低。这种方法特别适合制作DRAM存储器。

[0060] 进一步地,步骤S7包括步骤S71~S74。

[0061] 参照图11、图2,步骤S71:对鳍12进行离子注入以在鳍12的顶端形成第一掺杂区121和第二掺杂区122,第一掺杂区121和第二掺杂区122均与鳍12的导电类型相反;

[0062] 从鳍12的顶部对鳍12进行离子注入,以在鳍12的顶端形成第一掺杂区121和第二掺杂区122。第一掺杂区121和第二掺杂区122均为P型掺杂或均为N型掺杂。P型掺杂的第一掺杂区121和第二掺杂区122中注入了三价杂质离子,例如掺入硼、铟、镓离子;N型掺杂的第一掺杂区121和第二掺杂区122中注入了五价杂质离子,例如磷、砷、锑离子。当鳍12为P阱型时,第一掺杂区121和第二掺杂区122均为N型掺杂;当鳍12为N阱型时,第一掺杂区121和第二掺杂区122均为P型掺杂。在本实施例中第一掺杂区121、第二掺杂区122均为N型掺杂,鳍12为N阱型。第一掺杂区121和第二掺杂区122可以是通过同一次离子注入工艺形成的。第一

掺杂区121和第二掺杂区122也可以是分别通过两次离子注入工艺形成的。第一掺杂区121和第二掺杂区122均位于鳍12的顶端。第一掺杂区121和第二掺杂区122沿鳍12的长度方向相互分开。

[0063] 参照图12,步骤S72:对鳍12进行蚀刻以在第一掺杂区121和第二掺杂区122之间形成沟槽17,该沟槽17的底部不延伸到基台14。

[0064] 可以是采用干刻法对鳍12进行蚀刻。鳍12上形成的沟槽17沿垂直于鳍12的板面方向贯穿该鳍12。该沟槽17将第一掺杂区121和第二掺杂区122分隔开来。沟槽17并不将鳍12完全断开,沟槽17底部的鳍12形成马鞍鳍(Saddle Fin)。第一掺杂区121和第二掺杂区122的深度均小于该沟槽17的深度。该沟槽17的宽度优选小于深度。该沟槽17的横截面优选为梯形,该梯形的上底宽于下底。

[0065] 步骤S73:参照图13,在沟槽17的内壁上沉积第二介电层18,参照图14,向沟槽17内 沉积金属材料以形成第一电极19;

[0066] 在沟槽17的内壁上沉积绝缘材料以在沟槽17的内壁上形成一层第二介电层18。第二介电层18的材料可以是硅的氧化物,例如二氧化硅。第二介电层18不填充满沟槽17的内壁。第二介电层18附着在沟槽17的内壁上后,再在第二介电层18的表面沉积金属材料以在沟槽17内形成第一电极19。第二介电层18将金属材料和鳍12分隔开来。第一电极19的制作材料可以是钨、铜、铝、金、银等金属材料。

[0067] 参照图1、2,步骤S74:在第一掺杂区121上沉积第一多晶硅层21,在第二掺杂区122上沉积第二多晶硅层22;在第一多晶硅层21上沉积金属材料以形成第二电极23,在第二多晶硅层22上沉积金属材料以形成第三电极24。

[0068] 第一多晶硅层21和第二多晶硅层22的材料均为多晶硅,均可以采用化学气相沉积工艺制成。制作第二电极23和第三电极24的材料可以是钨、铜、铝、金、银等金属材料。第一多晶硅层21设置在第一掺杂区121和第二电极23之间。第二多晶硅层22设置在第二掺杂区122和第三电极24之间。这样,在鳍12内形成一晶体管100,该晶体管100的栅极是第一电极19、漏极是第二电极23、源极是第三电极24。

[0069] 进一步地,在步骤S1中,在衬底的表面蚀刻出多条鳍12,鳍12之间相互平行;

[0070] 在步骤S2中,在每个鳍12上均沉积一层的保护膜13:

[0071] 在步骤S3中,在对鳍12周围的衬底本体11进行蚀刻时,还蚀刻相邻两条鳍12之间区域的衬底本体11:

[0072] 在步骤S5中,在沉积第一介电层16时,第一介电层16至少填充满相邻两条所述鳍12之间的间隙:

[0073] 在步骤S6中,将所有鳍12顶部的保护膜13都去除;

[0074] 在步骤S7中,在每个鳍12内制作出至少一个晶体管100;

[0075] 这样加工后,能在每个鳍12内均制作出晶体管100,两个相邻鳍12之间的第一介电层16形成浅槽隔离区,浅槽隔离区能有效的将相邻两个鳍12上的晶体管100隔离开,同时减小漏电流的发生。

[0076] 进一步地,在步骤S71中,对鳍12进行离子注入时,第一掺杂区121至少形成两个,第二掺杂区122设置在每两个相邻的第一掺杂区121之间;

[0077] 在步骤S72中,对鳍12进行蚀刻时,在相邻的第一掺杂区121和第二掺杂区122之间

均蚀刻出沟槽17;

[0078] 在步骤S73中,在每个沟槽17内均沉积第二介电层18,然后在每个沟槽17内沉积金属材料以在每个沟槽17内均形成一个第一电极19;

[0079] 在步骤S74中,在每个第一掺杂区121上均乘积一层第一多晶硅层21,在每个第一多晶硅层21上均形成一个第二电极23;

[0080] 这样,每个鳍12内形成两个晶体管100,两个晶体管100共用一个第三电极24作为源极,两个晶体管100的栅极分别为两个第一电极19,两个晶体管100的漏极分别为两个第二电极23。两个晶体管100共用一个源极能减小晶体管100的总面积,缩小器件的尺寸。该存储器中还包括至少两个存储电容,这两个晶体管的第二电极23均能作为存储电容接触端来分别连接两个存储电容,两个晶体管100能分别对两个存储电容进行控制。

[0081] 进一步地,在步骤S72中,同时对鳍12和第一介电层16进行蚀刻以使得沟槽17能贯通多个鳍12;

[0082] 在步骤S73中,第一电极19形成一条沿沟槽17延伸的金属线,该金属线贯穿多个鳍12;

[0083] 在步骤S74中,第三电极24形成一条覆盖位于不同鳍12上的第二多晶硅层22的金属线。

[0084] 这样,第一电极19形成的金属线可以作为存储器的字线,第三电极24形成的金属线可以作为存储器的位线。字线为高电平时其所连接的晶体管100均导通,字线为低电平时则其所连接的晶体管100均截止。

[0085] 进一步地,步骤S3包括步骤S31和步骤S32。

[0086] 参照图6,步骤S31:对保护膜13进行蚀刻,仅保留覆盖在鳍12上的保护膜13。

[0087] 参照图7,步骤S32:对鳍12周围的衬底本体11进行蚀刻以在鳍12的底部形成凸出于衬底本体11的基台14。

[0088] 由于保护膜13和衬底本体11的材料不相同,将蚀刻分成两次,每次蚀刻更具有针对性则更有利于提高蚀刻的精度。

[0089] 进一步地,参照图15,步骤S73中,在形成第一电极19后,还在第一电极19上表面沉积一层覆盖第一电极19的第三介电层20。

[0090] 第三介电层20具有绝缘性,第三介电层20的材料可以是氮化硅。第三介电层20能使得第一电极19与第一电极19上方的其他部件绝缘。第三介电层20的表面优选为与第一介电层16的表面平齐。

[0091] 在另一个优选的实施例中,所采用的衬底为S0I(Silicon-On-Insulator)绝缘衬底。

[0092] 尽管已经参照某些实施例公开了本实用新型,但是在不背离本实用新型的范围和范畴的前提下,可以对所述的实施例进行多种变型和修改。因此,应该理解本实用新型并不局限于所阐述的实施例,其保护范围应当由所附权利要求的内容及其等价的结构和方案限定。

图3

图4

图5

图7

图8

图9

图10

图11

图12

18

19