# WORLD INTELLECTUAL PROPERTY ORGANIZATION International Bureau

### INTERNATIONAL APPLICATION PUBLISHED UNDER THE PATENT COOPERATION TREATY (PCT)

(51) International Patent Classification 5:

H04L 7/00, H03D 3/24

(11) International Publication Number:

WO 93/20633

/00, H03D 3/24

(43) International Publication Date:

14 October 1993 (14.10.93)

(21) International Application Number:

PCT/US93/00633

**A1**

(22) International Filing Date:

25 January 1993 (25.01.93)

(30) Priority data:

858,821

27 March 1992 (27.03.92) US

Published

With international search report.

(81) Designated States: CA, CZ, FI, GB, KR.

(71) Applicant: MOTOROLA, INC. [US/US]; 1303 East Algonquin Road, Schaumburg, IL 60196 (US).

(72) Inventors: LAROSA, Christopher, P.; 1935 N. Hicks Road #105, Palatine, IL 60074 (US). CARNEY, Michael, J.; 812 Carriage Lane #1, Palatine, IL 60074 (US).

(74) Agents: PARMELEE, Steven, G. et al.; Motorola, Inc., Intellectual Property Dept./KWD, 1303 E. Algonquin Road, Schaumburg, IL 60196 (US).

(54) Title: METHOD AND APPARATUS FOR MODIFYING A DECISION-DIRECTED CLOCK RECOVERY SYSTEM

(57) Abstract

The present disclosure includes a discussion of a decision-directed clock recovery system which includes circuitry to prevent false-locking and accelerate acquisition on a known symbol patterns. The clock recovery system has at least two control circuits. Each control circuit has an effective bandwidth and also generates a clock signal. The clock recovery system samples the received data signal using at least two clock signals (573, 575), forming a corresponding first and second sampled signal. The sampled signals are used to generate corresponding symbol decisions (581, 583). The symbol decision signals are processed to detect a known symbol pattern in the received data signal (513). Upon detection of the known bit sequence, the characteristics of the clock recovery system are modified, namely, the effective bandwidth of the control circuits are modified (527).

## FOR THE PURPOSES OF INFORMATION ONLY

Codes used to identify States party to the PCT on the front pages of pamphlets publishing international applications under the PCT.

| AT | Austria                  | FR  | France                       | MR | Mauritania               |

|----|--------------------------|-----|------------------------------|----|--------------------------|

| AU | Australia                | GA  | Gabon                        | MW | Malawi                   |

| BB | Barbados                 | GB  | United Kingdom               | NL | Netherlands              |

| BE | Belgium                  | GN  | Guinca                       | NO | Norway                   |

| BF | Burkina Faso             | GR  | Greece                       | NZ | New Zealand              |

| BG | Bulgaria                 | HU  | Hungary                      | PL | Poland                   |

| BJ | Benin                    | ΙE  | Ireland                      | PT | Portugal                 |

| BR | Brazil                   | IT  | Italy                        | RO | Romania                  |

| CA | Canada                   | JР  | Japan                        | RU | Russian Federation       |

| CF | Central African Republic | KP  | Democratic People's Republic | SD | Sudan                    |

| CG | Congo                    |     | of Korea                     | SE | Sweden                   |

| CH | Switzerland              | KR  | Republic of Korea            | SK | Slovak Republic          |

| Cl | Côte d'Ivoire            | KZ  | Kazakhstan                   | SN | Scnegal                  |

| CM | Camuroon                 | L.F | Liechtenstein                | SU | Soviet Union             |

| cs | Czechoslovakia -         | LK  | Sri Lanka                    | TD | Chad                     |

| CZ | Czech Republic           | LU  | Luxembourg                   | TG | Togo                     |

| DE | Germany                  | MC  | Monaco                       | UA | Ukraine                  |

| DK | Denmark                  | MC  | Madagascar                   | US | United States of America |

| ES | Spain                    | MI. | Mali                         | VN | Viet Nam                 |

| FI | Finland                  | MN  | Mongolia                     | •  |                          |

## Method and Apparatus for Modifying a Decision-Directed Clock Recovery System

#### Field of the Invention

10

5

This invention generally relates to clock recovery circuitry and more specifically to a method and apparatus for modifying a decision-directed clock recovery system to prevent false-locking and accelerate acquisition on a known symbol pattern.

15

20

25

30

#### Background of the Invention

Recently in the field of radio frequency (RF) communications, there has been an increased demand for digitally encrypted voice and high speed data communications. Since the RF spectrum is inherently limited, one must devise a new system concept and organizational features to accommodate the increased demand. A time division multiple access (TDMA) system is one such system which offers more efficient spectrum utilization and increased capacity.

In its simplest form, a TDMA system is comprised of a transmitting base station, which is capable of time multiplexing messages from at least two users on a single RF channel, and one or more remote receiving stations capable of receiving at least one of the time multiplexed messages.

10

15

20

25

Typically, the receiving station would be a mobile or portable radiotelephone capable of transmitting a TDMA message to the base station on a second RF channel.

In a TDMA system, like most digital communications systems, it is necessary to establish a reference clock in the receiving station that is continuously synchronized with the transmit clock to accurately recover the digital data transmitted between the two points. Continuous bit synchronization, as used herein, means that the frequency and phase of the received clock signal must accurately track that of the transmit clock.

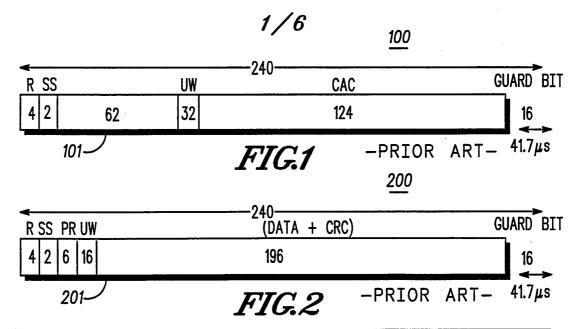

One implementation of a TDMA system uses a time division duplex (TDD) slot structure. The TDD system uses one RF channel to send control and communication information between two points. FIG. 1 is an illustration of a control slot 100 for a particular application. This application requires that symbol synchronization for the control slots 100 be carried out independently for each slot. To aid in the synchronization a 62 bit preamble 101 is provided at the start of each slot 100. A conventional decision-directed clock recovery system would have two problems with this slot structure. First, the 62-bit (31-symbols for quadrature phase shift keying modulation) preamble 101 does not provide sufficient time for symbol timing acquisition. Second, the 62-bit preamble has false-lock points which can cause a decision-directed system to move toward an incorrect sampling phase. Thus, the conventional clock recovery approach for the control slots 100 would be to correlate the detected signal with the known bit pattern.

10

15

FIG. 2 is an illustration of a communications slot 200 for a specific application. The communications slot 200 has an extremely short preamble pattern 201 of 6 bits. A correlator-based clock recovery system would not be appropriate for the communication slot 200 because it requires a longer preamble to lock onto the received data signal. As a result, the conventional solution to the clock recovery problem would be to use a correlation-based system for the control slots 100 and a decision-directed clock recovery scheme for the communications slots 200. However, two different system implementations would result in excessive power consumption, size and complexity.

A desirable system would be a unified solution to the symbol synchronization problem which does not require two distinct solutions, namely, a correlation based approach and a decision-directed approach.

#### Summary of the Invention

The present invention encompasses a method of modifying a decision-directed clock recovery system to prevent false-locking and accelerate acquisition on a known symbol pattern. The clock recovery system has at least two control circuits. Each control circuit has an effective bandwidth and also generates a clock signal. The invention samples the received data signal using the two clock signals, forming a corresponding first and second sampled signal. The sampled signals are used to generate corresponding symbol decisions. The symbol decision signals are processed to detect a known symbol pattern in the received data signal. Upon detection of

the known bit sequence, the characteristics of the clock recovery system are modified.

## Brief Description of the Drawings

5

20

- FIG. 1 is an illustration of a control time slot as used by the present invention.

- FIG. 2 is an illustration of a communications slot as used by the present invention.

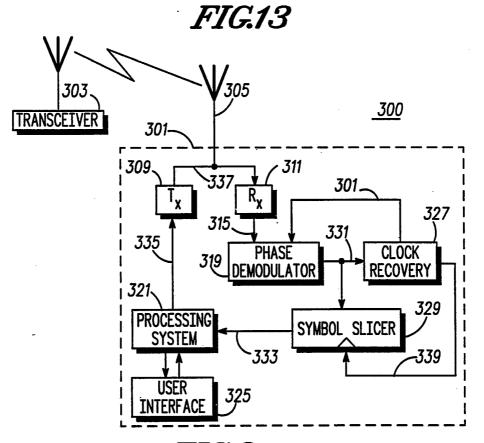

- 10 FIG. 3 is a block diagram of a radiotelephone communications system in accordance with the present invention.

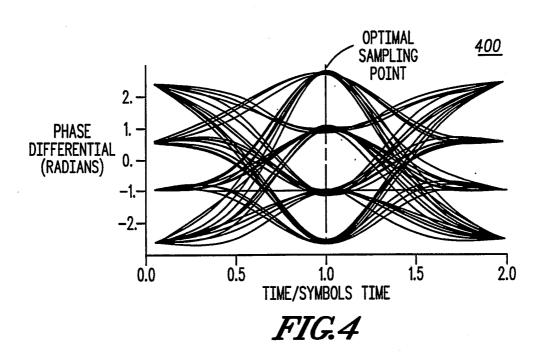

- FIG. 4 is an eye diagram of  $\pi/4$  QPSK data at the output of a differential detector.

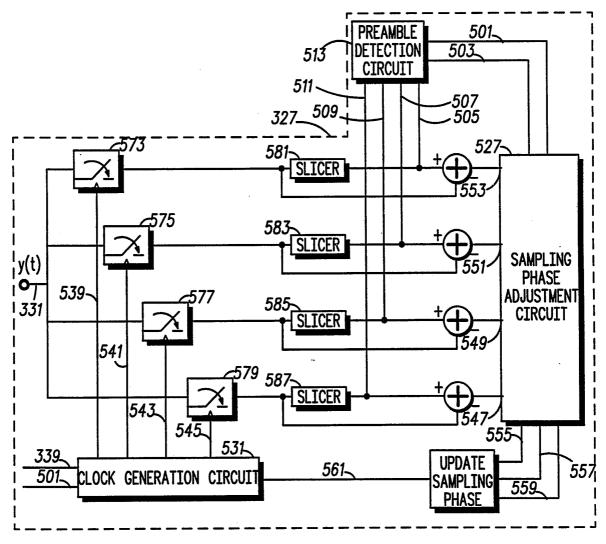

- FIG. 5 is a block diagram of the clock recovery system in accordance with the present invention.

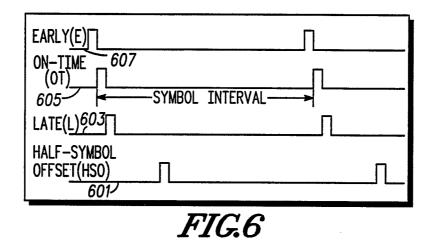

- FIG. 6 is a diagram illustrating multiple phase offset clocks in accordance with the present invention.

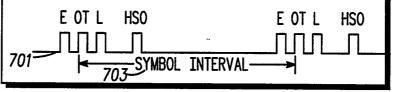

- FIG. 7 is an example of a non-uniform sampling clock combining the individual clocks of FIG. 6 in accordance with the present invention.

- FIG. 8 is an example of a preamble detection circuit in accordance with the present invention.

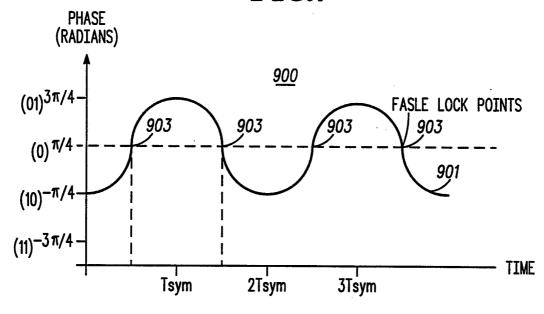

- FIG. 9 is illustrates a known symbol sequence at the output of a differential phase demodulator in accordance with the present invention.

- FIG. 10 is process flow chart illustrating the modification characteristics to the clock recovery circuitry in accordance with the present invention.

10

15

20

25

30

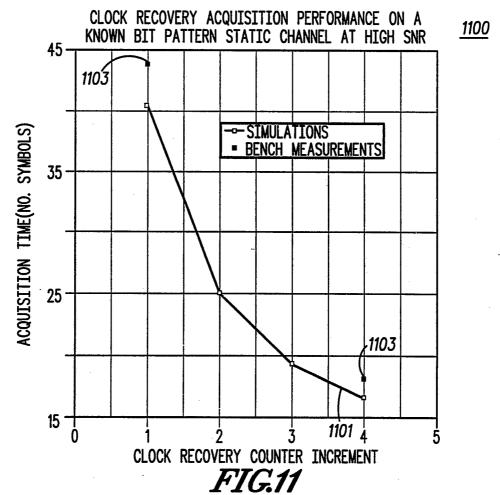

FIG. 11 is a graph representing the performance of the present invention.

FIG. 12 is a detailed block diagram of a sampling phase adjustment circuit in accordance with the present invention.

FIG. 13 is a table indicating performance of a clock recovery system in accordance with the present invention.

#### Description of a Preferred Embodiment

The preferred embodiment encompasses a digital receiver of a radiotelephone. The digital receiver includes a decision-directed clock recovery circuit for use in demodulating the received signal. The clock recovery circuitry is modified to have a decision-directed clock recovery mode and a preamble detection mode to allow for flexibility in acquiring synchronization between a received data signal and a clock recovered signal.

The present invention encompasses the preamble detection circuit and corresponding modification to the sampling phase adjustment circuit which controls the loop bandwidths of the control circuits. The preferred embodiment has four clock recovery control circuits, each corresponding to one of four clock signals. However, only two such circuits are required to gain the benefit of the present invention. When random data is detected, the circuit operates in the decision-directed mode. Upon detecting a known symbol pattern, the circuit enters the preamble detection mode. In this mode, a false-lock state detected in any one of the four control circuits sets the effective bandwidth of that control circuit to 0, freezing the clock recovery system from further phase adjustment. If a fast

10

15

20

25

acquisition state is detected in the preamble detection mode, then the effective bandwidths of the control circuits are increased to 4 times their nominal bandwidths, providing quick adjustment to the desired phase of the received data signal.

FIG. 3 is a block diagram of a radiotelephone system which employs the present invention. In the radiotelephone system, the fixed site transceiver 303 sends and receives radio frequency (RF) signals to and from mobile and portable radiotelephones contained within a fixed geographic area. The radiotelephone 301 is one such radiotelephone served by the fixed site transceiver 303.

While receiving signals from the fixed site transceiver 303, the radiotelephone 301 uses the antenna 305 to couple the RF signal and to convert the RF signal into an electrical radio frequency signal 337. The electrical RF signal is received by the radio receiver 311 for use within the radiotelephone 301. The receiver 311 generates an intermediate frequency (IF) signal 315. This signal 315 is input into the phase demodulator 319. The phase demodulator 319 outputs a phase demodulated signal 331 for use by the clock recovery circuitry 327 and the symbol slicer 329. The clock recovery circuitry 327 outputs the sampling clock 339 to the symbol slicer 329. The phase demodulator signal 331 is also used as the received data signal for the symbol slicer 329. The symbol slicer in turn outputs a symbol signal 333 for use by the processor 321. The processor 321 formats the symbol signal 333 into voice and/or data for the user interface 325. The user interface 325 contains a microphone, a speaker and a keypad.

25

Upon transmission of RF signals from the portable radiotelephone 301 to the fixed site transceiver 303, the voice and/or data signals from the user interface 325 are processed by the processor 321. The processed signals are input into the transmitter 309. The transmitter 309 converts the processed signals into electrical RF signals. The electrical RF signals are converted into RF signals and output by the antenna 575. The RF signals are received by the fixed site transceiver 303, which interfaces to the land-line telephone signals.

10 FIG. 4 is an illustration of an eye diagram of a π/4 quadrature phase shift keying (QPSK) signal at the output of a differential detector contained within the phase demodulator 319. This signal is representative of the data output on the phase demodulated signal 331. For accurate recovery of the symbols transmitted between the transceiver 303 and the portable radiotelephone 301, the sampling clock 339 should sample the received data signal 331 at or near the optimal sampling point as illustrated in FIG. 4. Sampling at points other than the optimal location can cause degraded bit error rate (BER) performance.

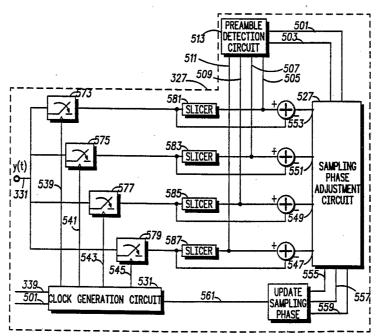

FIG. 5 is a detailed block diagram of the clock recovery circuitry 327 utilized in the preferred embodiment. The clock recovery circuitry uses the phase demodulator output signal y(t) 331 to recover the clock signals. In the preferred embodiment, the clock generation circuit 331 generates four individual clock signals 539, 541, 543, 545. These clocks are used to sample and hold the phase demodulator output signal y(t) 331. Other equally sufficient implementations of the present invention may generate two or more clock signals to

10

15

20

25

30

perform the phase adjustments according to the present invention.

For purposes of description, the preferred embodiment has four individual control circuits. Each control circuit utilizes one of the four clock signals 539, 541, 543, 545 with the corresponding sample and hold circuits, 573, 575, 577, 579 and the corresponding slicers 581, 583, 585, 587. Each of the control circuits has an equivalent loop bandwidth which is determined by the sampling phase adjustment circuit 527.

The relative phases, as used in the preferred embodiment, of the four clock signals 539, 541, 543, 545 are shown in FIG. 6. The on-time signal 605 has a clock pulse once each symbol interval. The early clock signal 607 generates a clock pulse at intervals equal to the intervals of the on-time signal 605, but shifted in phase by 1/8 of a symbol time before the on-time signal 605. The late clock signal 603 is equal in frequency and shifted by 1/8 of a symbol interval later than the on-time signal

605. The half- symbol offset clock signal 601 is identical to the on-time signal in frequency and shifted by 1/2 a symbol interval. The non-uniform sampling clock 701 of FIG. 7 is used to sample the phase within the phase demodulator 319. It is formed by ORing the four individual clocks 601, 603, 605, and 607. Other equally sufficient implementations may be used by varying the phase offsets but are still considered within the essence of the invention disclosed herein.

These four clock signals 601, 603, 605, and 607 are used to sample the phase demodulator output signal 331 with the sample and hold circuits 573, 575, 577, 579. These sampled phases are then input into the slicer and adder combination to form error signals 547, 549, 551, 553. The error signal is

10

15

20

25

formed by taking the difference between the sampled detector output signal and the nearest corresponding decision point, i.e., the slicer output.

The error signals 547, 549, 551, 553, are input into the sampling phase adjustment circuitry 527. The sampling phase adjustment circuit 527 is used to advance or retard the four symbol clocks to minimize the error at the on-time sampling point. At the output of the four slicers, 581, 583, 585, 587 is the symbol output signals 505, 507, 509, 511.

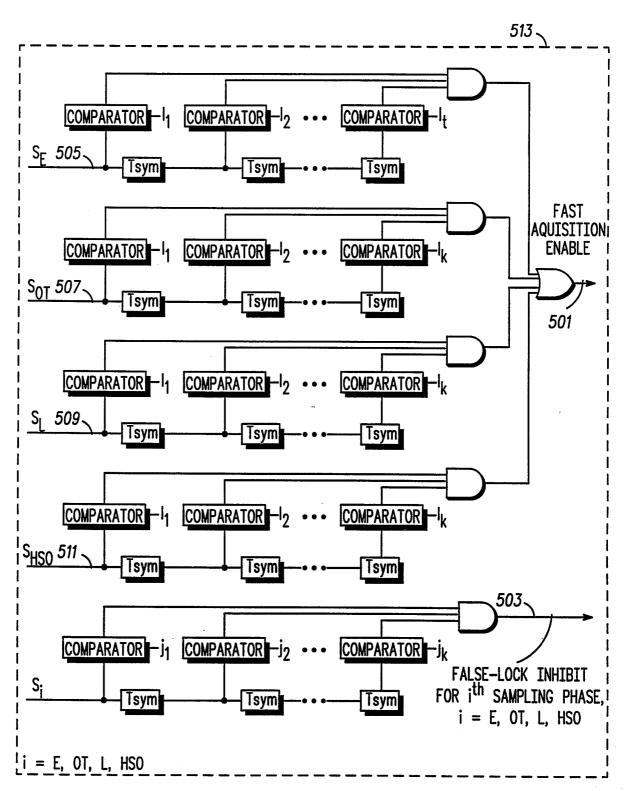

The preamble detection circuit 513 is utilized to detect the presence of the known symbol pattern, namely, the 62-bit preamble 101 of the control slot 100. The preamble detection circuit is also utilized to detect potential false-lock points at each of the four clock phases. At the output of the preamble detection circuit 513 there is the fast acquisition enable control signal 501 and 4 false-lock inhibit control signals 503 which correspond to each of the 4 control circuits.

The preamble detection circuit 513 recognizes when the known bit pattern is being received and upon recognition, automatically alters the clock adjustment decision rules so as to prevent false-locking and accelerate adjustments toward the optimal sampling phase. The preamble detector circuit 513 examines the outputs of the 4 symbol slicers to determine whether or not the preamble pattern is being detected at any of the four sampling phases. The preamble detection circuit 513 then utilizes this information to generate the fast acquisition enable control signal 501 and the false-lock inhibit control signals 503.

The preamble detection circuit 513 operates by detecting a portion of the preamble symbol sequence 101 and/or the

10

15

20

2.5

30

corresponding false-lock symbol sequence at one or more of the four clock sampling phases. A generalized preamble detection circuit is illustrated in FIG. 8. This circuit will enable fast acquisition mode whenever the symbol pattern I1, I2, . . ., Ik is detected at any of the 4 sampling phases of the clock signal. This pattern can be a portion of the actual preamble sequence 101 or the corresponding false-lock pattern. The preamble detection circuit 513 will also determine which of the 4 sampling phases, if any, are currently detecting the false-lock pattern  $J_1, J_2, \ldots J_k$ . The preamble detection circuit does not necessarily need to detect the entire preamble sequence and/or corresponding false-lock symbol pattern. The number of stages in the preamble detection circuit (k) is selected to ensure a high probability of preamble false-lock detection during the known sequence while minimizing the probability of detection on random data. In the preferred embodiment, k is equal to 4. The fast acquisition enable control signal 501 and the 4 falselock inhibit control signals 503 are then input into the sampling phase adjustment circuit 527.

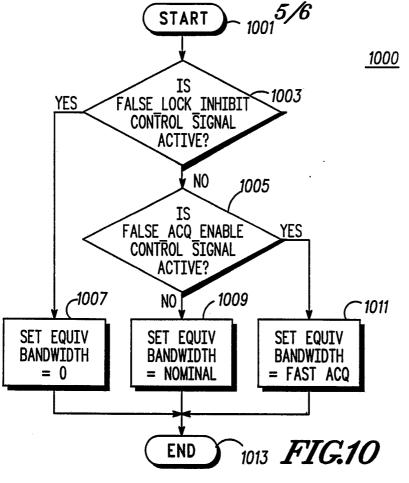

The modification of the decision-directed clock recovery system occurs within the sampling phase adjustment circuit 527. The method of modification is illustrated in the process flow chart of FIG. 10. The process flow chart 1000 begins by monitoring the false-lock inhibit control signal 503 and the fast acquisition enable control signal 501, both of which have an active and an inactive state. The process flow chart 1000 illustrated in FIG. 10 operates on the portion of each of the four control circuits contained within the sampling phase adjustment circuit 527. At decision block 1003, the process flow chart 1000 determines if the false-lock inhibit signal 503 is

10

15

20

25

30

active. If the false-lock inhibit control signal is active, the equivalent bandwidth of the control circuit is set equal to zero at the functional block 1007, effectively locking the corresponding clock recovery control circuit at its current phase. Upon detecting a false-lock inhibit signal in an inactive state at decision block 1003 the process continues to decision block 1005. At decision block 1005 the process determines if the fast acquisition enable control signal is active. If the fast acquisition enable control signal is active, then the equivalent bandwidth of the given control circuit is set equal to the fast acquisition bandwidth at functional block 1011. The fast acquisition bandwidth allows quick acquisition to the desired sampling phase. If at decision block 1005 it is determined that the fast acquisition enable control signal 501 is inactive, then the equivalent bandwidth of the given control circuit is set equal to a nominal value at functional block 1009.

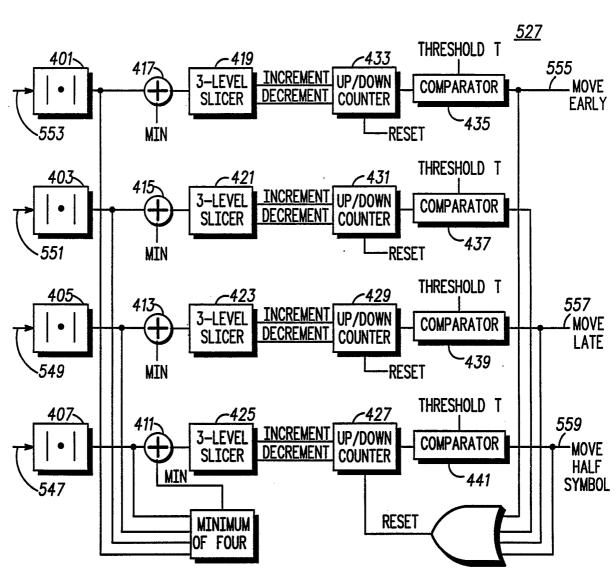

FIG. 12 is a block diagram illustrating one possible implementation of the sampling phase adjustment circuits 527 illustrated in FIG.5. The first function of the sampling phase adjustment circuit 527 is to determine the magnitude of each error signal 547, 549, 551, 553, within the blocks 401, 403, 405, 407. Next, the smallest error magnitude signal is selected and called the minimum error value. This minimum error value is subtracted from each of the four error signals 547, 549, 551, 553, resulting in four normalized error magnitude signals. A three-level decision is then made for each sampling phase as a function of how its error magnitude compares to the minimum error magnitude. If the error magnitude signal is sufficiently close to the minimum value, or the normalized error magnitude is less than a threshold Δ1, then the

10

15

20

25

corresponding counter is incremented. If the error magnitude is large relative to the minimum value, or the normalized error magnitude is greater than a second threshold  $\Delta_2$ , then the corresponding counter is decremented. Finally, if the normalized error magnitude falls within the middle region, greater than the first threshold  $\Delta_1$ , and less than or equal to the second threshold  $\Delta_2$ , then the counter is held constant.

The first of the four counters 433, 431, 429, 427, to reach a predetermined positive threshold has demonstrated that its error magnitude is consistently smaller than that of the other three sampling phases; hence, the appropriate clock adjustment decision is then made. This is carried out in the block diagram by having the output value of the counters input into the comparators 435, 437, 439 441. Here, the output values of the counters are compared to the predetermined threshold, T. If one of the counters reaches the threshold, then all of the counters 433, 431, 429, 427 are reset to zero, restarting the averaging process for the phase adjustment circuit. The reset function is implemented by ORing the outputs of the four comparators within the 4-input OR gate 443, which is then tied to the reset inputs of each of the four counters, 433, 431, 429, 427. The output of the first comparator 435 is equal to the move early phase adjustment signal 555. The output of the second comparator 437 is not tied to a shifting signal because the desired phase has already been obtained. The output of the third comparator 439 is the signal 557 of FIG. 5, which is a move late phase adjustment signal. The output of the fourth comparator 441 is the move half symbol phase adjustment signal 559.

The modifications to control the bandwidths as illustrated by the process flow chart of FIG. 10 are implemented by modifying the incremental steps of the up/down counters 427, 429, 431, 433. Setting the effective bandwidth equal to zero as illustrated in functional block 1007 is equivalent to preventing a counter from incrementing. Setting the effective bandwidth to the fast acquisition bandwidth as illustrated in functional block 1011 is equivalent to increasing the incremental counter steps of the four up/down counters 427, 429, 431, 433 to m, where m is an integer greater than 1. In the preferred embodiment m is equal to 4. Setting the effective bandwidth to the nominal bandwidth as illustrated in functional block 1009 is equivalent to maintaining the incremental counter steps of the four up/down counters 427, 429, 431, 433 at the nominal value of 1.

The invention described herein has been simulated and bench tested to verify its impact on acquisition performance in the given specified system. FIG. 11 plots acquisition time as a function of the up/down counter increment value m. This plot clearly illustrates that increasing the value of m reduces the time required to acquire symbol timing on the preamble pattern. In the preferred embodiment, the value of m equal to 4 has been selected; this value provides satisfactory acquisition performance without degrading steady state bit error rate (BER) performance on random data. As the results of FIG. 11 demonstrate the fast acquisition feature has reduced the acquisition time by about a factor of 3 for the known bit pattern. Moreover, this fast acquisition feature does not degrade acquisition performance for random data; this is demonstrated by the results of the table in FIG. 13. In addition

to improved symbol timing acquisition performance, the invention also offers false-lock protection. The implementation of the preamble detection mechanism eliminated adjustments to a false-lock point for all measured bench trials.

5 What is claimed is:

10

15

1. A method of modifying a decision-directed clock recovery system to prevent false-locking and accelerate acquisition on a known symbol pattern, the clock recovery system having at least a first and a second control circuit, each control circuit generating a corresponding clock signal and each control circuit having an equivalent loop bandwidth, the method comprising the steps of:

sampling a first received signal using at least said first and said second clock signals, forming a corresponding first and second sampled signal;

generating at least a first and a second symbol decision signal for each of said first and said second sampled signal;

detecting, responsive to said first and said second symbol decision signals, a presence of a known symbol pattern in the first received signal; and

modifying, responsive to said step of detecting, the characteristics of the clock recovery system.

2. A method of modifying in accordance with claim 1 wherein said step of detecting further comprises the steps of: comparing each of said at least first and second symbol decision signals to a first selective portion of the known symbol pattern;

generating, responsive to said first step of comparing, a corresponding first and second false-lock inhibit control signal, each having an active and an inactive state;

comparing each of said at least first and second symbol decision signals to a second selective portion of the known symbol pattern; and

generating, responsive to said second step of comparing, a corresponding first and second fast acquisition enable control signal, each having an active and an inactive state.

15

20

25

10

5

- 3. A method of modifying in accordance with claim 2 wherein said step of modifying further comprises the steps of: detecting said active state of said first false-lock inhibit control signal;

- setting, responsive to said first step of detecting, the first control circuit's equivalent loop bandwidth to a first predetermined value;

detecting said active state of said second false-lock inhibit control signal; and

setting, responsive to said second step of detecting, the second control circuit's equivalent loop bandwidth to a first predetermined value.

4. A method of modifying in accordance with claim 3 wherein said step of modifying further comprises the steps of: detecting said inactive state of said first false-lock inhibit

control signal and said inactive state of said first fast acquisition enable control signal;

setting, responsive to said first step of detecting, the first control circuit's equivalent loop bandwidth to a second predetermined value;

detecting said inactive state of said second false-lock inhibit control signal and said inactive state of said second fast acquisition enable control signal; and

setting, responsive to said second step of detecting, the second control circuit's equivalent loop bandwidth to a second predetermined value.

15

25

10

5

5. A method of modifying in accordance with claim 4 wherein said step of modifying further comprises the steps of:

detecting said inactive state of said first false-lock inhibit control signal and said active state of said first fast acquisition enable control signal;

enable control signal;

setting, responsive to said first step of detecting, the first

control circuit's equivalent loop bandwidth to a third

predetermined value;

detecting said inactive state of said second false-lock inhibit control signal and said active state of said second fast acquisition enable control signal; and

setting, responsive to said second step of detecting, the second control circuit's equivalent loop bandwidth to a third predetermined value.

15

20

25

| 6. A method of modifying in accordance with claim 1               |

|-------------------------------------------------------------------|

| wherein said step of detecting further comprises the steps of:    |

| comparing each of said at least first and second symbol           |

| decision signals to a first selective portion of the known symbol |

| pattern; and                                                      |

generating, responsive to said step of comparing, a corresponding first and second fast acquisition enable control signal, each having an active and an inactive state.

7. A method of modifying in accordance with claim 6

wherein said step of modifying further comprises the steps of:

detecting said active state of said first fast acquisition

enable control signal;

setting, responsive to said step of detecting, the first control circuit's equivalent loop bandwidth to a fourth predetermined value;

detecting said active state of said second fast acquisition enable control signal; and

setting, responsive to said second step of detecting, the second control circuit's equivalent loop bandwidth to a fourth predetermined value.

8. A method of modifying in accordance with claim 7 wherein said step of modifying further comprises the steps of: detecting said inactive state of said first fast acquisition enable control signal;

setting, responsive to said step of detecting, the first control circuit's equivalent loop bandwidth to a fifth predetermined value;

ø

detecting said inactive state of said second fast acquisition enable control signal; and

setting, responsive to said second step of detecting, the second control circuit's equivalent loop bandwidth to a fifth predetermined value.

ø

5

10

15

9. A radiotelephone including a receiver and at least a first and a second control circuit, the control circuits generating a corresponding first and second clock signal and each control circuit having an equivalent loop bandwidth, the receiver capable of receiving at least a first data signal, the first received data signal having a phase, the radiotelephone comprising:

means for sampling the first received data signal using at least the first and the second clock signals, forming a corresponding first and second sampled signals;

means for generating at least a first and a second symbol decision signal for each of said first and said second sampled signals;

means for detecting, responsive to said first and said second symbol decision signals, a presence of a known symbol pattern in the first received signal; and

means for modifying, responsive to said means for detecting, the equivalent loop bandwidth of the control circuits.

15

10. A radiotelephone in accordance with claim 9 wherein said means for detecting further comprises:

means for comparing each of said at least first and second symbol decision signals to a first selective portion of the known symbol pattern;

means for generating, responsive to said first means for comparing, a corresponding first and second false-lock inhibit control signal, each signal having an active and an inactive state;

means for comparing each of said at least first and second symbol decision signals to a second selective portion of the known symbol pattern; and

means for generating, responsive to said second means for comparing, a corresponding first and second fast acquisition enable control signal, each signal having an active and an inactive state.

| TRANSMITTED DATA              | ACQUISITION TIME<br>WITHOUT FAST—ACQUISITION<br>FEATURE (#SYMBOLS) | ACQUISITION TIME WITH FAST-ACQUISITION FEATURE (#SYMBOLS) |  |

|-------------------------------|--------------------------------------------------------------------|-----------------------------------------------------------|--|

| 1001 REPEATING BIT<br>PATTERN | 44.0                                                               | 17.4                                                      |  |

| RANDOM DATA                   | 78.75                                                              | 77.0                                                      |  |

FIG.3

2/6

FIG.5

E OT L HS0

FIG.7

FIG.9

FIG.8

FIG.12

#### INTERNATIONAL SEARCH REPORT

International application No. PCT/US93/00633

| 1                    |                                                                                                                                                                                                                                               |                                                                                                                  |                                  |  |

|----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------|----------------------------------|--|

| US CL                | :H04L 7/00; H03D 3/24<br>:375/108, 116, 118, 119                                                                                                                                                                                              |                                                                                                                  |                                  |  |

| <del></del>          | o International Patent Classification (IPC) or to both                                                                                                                                                                                        | national classification and IPC                                                                                  |                                  |  |

|                      | LDS SEARCHED                                                                                                                                                                                                                                  |                                                                                                                  |                                  |  |

| Minimum d            | ocumentation searched (classification system followed                                                                                                                                                                                         | by classification symbols)                                                                                       |                                  |  |

| U.S. :               | 375/108, 116, 118, 119; 375/106, 114                                                                                                                                                                                                          |                                                                                                                  |                                  |  |

| Documentat           | tion searched other than minimum documentation to the                                                                                                                                                                                         | extent that such documents are included                                                                          | in the fields searched           |  |

|                      |                                                                                                                                                                                                                                               |                                                                                                                  |                                  |  |

| Electronic d         | lata base consulted during the international search (na                                                                                                                                                                                       | me of data base and, where practicable                                                                           | , search terms used)             |  |

| APS - clo            | ck recovery, false lock, preamble detection, synchron                                                                                                                                                                                         | nizer, phase adjustment                                                                                          |                                  |  |

| C. DOC               | UMENTS CONSIDERED TO BE RELEVANT                                                                                                                                                                                                              |                                                                                                                  |                                  |  |

| Category*            | Citation of document, with indication, where ap                                                                                                                                                                                               | propriate, of the relevant passages                                                                              | Relevant to claim No.            |  |

| A                    | US, A, 4,821,297 (BERGMANN ET figure 1 and col. 3, line 20 to col. 5,                                                                                                                                                                         |                                                                                                                  | 1, 9                             |  |

| A                    | US, A, 4,386,323 (JANSEN) 31 May 2, line 22 to col. 3, line 22.                                                                                                                                                                               | 1983. See figure 1 and col.                                                                                      | 1, 9                             |  |

| A                    | US, A, 4,012,598 (WILEY) 15 March 3, line 18 to col. 4, line 68.                                                                                                                                                                              | 1977. See figure 1 and col.                                                                                      | 1, 9                             |  |

| A                    | US, A, 4,672,639 (TANABE ET AL. and col. 3, line 15 to col. 4, line 9.                                                                                                                                                                        | 09 June 1987. See figure 1                                                                                       | 1, 9                             |  |

|                      |                                                                                                                                                                                                                                               |                                                                                                                  |                                  |  |

|                      |                                                                                                                                                                                                                                               |                                                                                                                  |                                  |  |

|                      |                                                                                                                                                                                                                                               |                                                                                                                  |                                  |  |

| X Furth              | ner documents are listed in the continuation of Box C                                                                                                                                                                                         | . See patent family annex.                                                                                       |                                  |  |

| 1                    | * Special categories of cited documents:  "T" later document published after the international filing date or priority date and not in conflict with the application but cited to understand the principle or theory underlying the invention |                                                                                                                  |                                  |  |

| to                   | be part of particular relevance rlier document published on or after the international filing date                                                                                                                                            | "X" document of particular relevance; th                                                                         | e claimed invention cannot be    |  |

| "L" do               | cument which may throw doubts on priority claim(s) or which is                                                                                                                                                                                | considered novel or cannot be conside<br>when the document is taken alone                                        | rea to invoive an inventive step |  |

| spo                  | ed to establish the publication date of another citation or other ecial reason (as specified)  cument referring to an oral disclosure, use, exhibition or other                                                                               | "Y" document of particular relevance; the considered to involve an inventive combined with one or more other suc | step when the document is        |  |

| me                   | cument published prior to the international filing date but later than                                                                                                                                                                        | being obvious to a person skilled in to  document member of the same patent                                      | he art                           |  |

| the                  | priority date claimed actual completion of the international search                                                                                                                                                                           |                                                                                                                  |                                  |  |

| 01 APRIL             |                                                                                                                                                                                                                                               | 16 APR 1993                                                                                                      | ······                           |  |

| Name and r           | nailing address of the ISA/US                                                                                                                                                                                                                 | Authorized officer //////                                                                                        | : labilitie                      |  |

| Commissio<br>Box PCT | Commissioner of Patents and Trademarks                                                                                                                                                                                                        |                                                                                                                  |                                  |  |

| Washington           | n, D.C. 20231                                                                                                                                                                                                                                 |                                                                                                                  |                                  |  |

| racsimile N          | Io. NOT APPLICABLE                                                                                                                                                                                                                            | Telephone No. (703) 305-4899                                                                                     |                                  |  |

Form PCT/ISA/210 (second sheet)(July 1992)\*

#### INTERNATIONAL SEARCH REPORT

International application No. PCT/US93/00633

| Category* | Citation of document, with indication, where appropriate, of the relevant passages               | Relevant to claim No. |

|-----------|--------------------------------------------------------------------------------------------------|-----------------------|

| A         | US, A, 4,242,755 (GAUZAN) 30 December 1980. See figure 1 and col. 3, line 25 to col. 4, line 25. | 1, 9                  |

| A         | US, A, 4,890,299 (DOLIVO ET AL.) 26 December 1989. See col. 3, line 33 to col. 4, line 9.        | 1, 9                  |

| A         | US, A, 4,667,333 (BUTCHER) 19 May 1987. See col. 2, line 36 to col. 4, line 12.                  | 1, 9                  |

|           |                                                                                                  |                       |

|           |                                                                                                  |                       |

|           |                                                                                                  |                       |

|           |                                                                                                  |                       |

|           |                                                                                                  |                       |

|           | •                                                                                                |                       |

|           |                                                                                                  |                       |

|           | ,                                                                                                |                       |

|           |                                                                                                  |                       |

|           |                                                                                                  |                       |

|           |                                                                                                  |                       |

|           |                                                                                                  |                       |

|           |                                                                                                  |                       |

|           |                                                                                                  |                       |

|           |                                                                                                  |                       |

|           |                                                                                                  |                       |