## (19) **日本国特許庁(JP)**

# (12) 公 開 特 許 公 報(A)

(11)特許出願公開番号

特開2009-253249 (P2009-253249A)

(43) 公開日 平成21年10月29日(2009, 10, 29)

| (51) Int.Cl. |                    | FΙ     |       |      | テーマコード (参考) |

|--------------|--------------------|--------|-------|------|-------------|

| HO1L 21/768  | (2006.01)          | HO1L 2 | 21/90 | C    | 4M1O4       |

| HO1L 21/28   | (2006.01)          | HO1L 2 | 21/90 | A    | 5FO33       |

| HO1L 21/824  | 2 <i>(2006.01)</i> | HO1L 2 | 21/28 | L    | 5F083       |

| HO1L 27/108  | (2006.01)          | HO1L 2 | 27/10 | 621C |             |

|           |                              | 審查請求      | 未請求                 | 請求項    | の数 8 | ΟL   | (全   | 13 頁) |  |

|-----------|------------------------------|-----------|---------------------|--------|------|------|------|-------|--|

| (21) 出願番号 | 特願2008-103284 (P2008-103284) | (71) 出願人  | 500174247           |        |      |      |      |       |  |

| (22) 出願日  | 平成20年4月11日 (2008.4.11)       |           | エルピーダメモリ株式会社        |        |      |      |      |       |  |

|           |                              |           | 東京都中央区八重洲2-2-1      |        |      |      |      |       |  |

|           |                              | (74) 代理人  | 100096231           |        |      |      |      |       |  |

|           |                              |           | 弁理士 稲垣 清            |        |      |      |      |       |  |

|           |                              | (72) 発明者  | 小林 宏尚               |        |      |      |      |       |  |

|           |                              |           | 東京都中央区八重洲2-2-1 エルピー |        |      |      |      |       |  |

|           |                              | ダメモリ株式会社内 |                     |        |      |      |      |       |  |

|           |                              | Fターム (参   | 考) 4M10             | 4 BB01 | BB18 | DD04 | DD07 | GG09  |  |

|           |                              |           |                     | GG10   | GG14 | GG16 | HH14 |       |  |

|           |                              |           | 5F03                | 80HH & | HH19 | JJ04 | JJ19 | KK01  |  |

|           |                              |           |                     | KK19   | NN40 | PP06 | QQ09 | QQ28  |  |

|           |                              |           |                     | QQ31   | QQ37 | QQ48 | QQ49 | RR04  |  |

|           |                              |           |                     | RR06   | SS11 | TT06 | TT08 | XX03  |  |

|           |                              |           | 5F08                | 3 AD24 | JA39 | JA56 | MA02 | MA06  |  |

|           |                              |           |                     | MA17   | NA01 | PR29 |      |       |  |

(54) 【発明の名称】半導体装置、その製造方法、及び、データ処理システム

## (57)【要約】

【課題】配線層の表面を被覆する配線保護膜の設計厚み を小さくし、配線層とセルフアラインプロセスで形成さ れるビアプラグの間隔を縮小し、半導体装置を微細化す る。

【解決手段】キャップ層16及びサイドウオール層17 から成る保護膜で被覆された配線層15の上部に、配線 層15と同じレイアウトパターンで延びるダミーマスク 層20、21を形成する。ビアプラグ22を、配線層1 5及びその保護膜16、17と自己整合的に形成するセ ルフアラインプロセスに際して、エッチングされるキャ ップ層16の膜厚を小さくし、ビアプラグ22の設計間 隔を縮小することで、半導体装置10を微細化する。

【選択図】図1

#### 【特許請求の範囲】

## 【請求項1】

それぞれの表面が絶縁保護膜で被覆される複数の配線を含み、全体が第1の層間絶縁膜 に覆われた第1の配線層と、

前記第1の層間絶縁膜と異なる材料で形成され、それぞれが前記第1の層間絶縁膜の上 部 で 前 記 複 数 の 配 線 と 同 じ レ イ ア ウ ト で 延 び る 複 数 の ダ ミ - 絶 縁 膜 と 、

前記複数の配線のうち隣接する2つの配線の間で、前記第1の層間絶縁膜を貫通し、前 記 隣 接 す る 2 つ の 配 線 及 び 対 応 す る 絶 縁 保 護 膜 と 自 己 整 合 的 に 形 成 さ れ た 導 電 性 プ ラ グ と を備えることを特徴とする半導体装置。

#### 【請求項2】

10

前記導電性プラグは、前記隣接する2つの配線の上部に形成された、隣接する2つのダ ミー絶縁膜と自己整合的に形成されている、請求項1に記載の半導体装置。

#### 【請求頃3】

前記絶縁保護膜がシリコン窒化膜であり、前記第1の層間絶縁膜がシリコン酸化膜であ る、請求項1又は2に記載の半導体装置。

#### 【請求項4】

DRAM装置として構成される、請求項1~3の何れか一に記載の半導体装置。

#### 【請求項5】

前記絶縁保護膜が、前記複数の配線の上部を覆うキャップ層と、前記複数の配線の側面 を覆うサイドウオール層とを含み、前記複数のダミー絶縁膜が、前記キャップ層の上方で 延びる中央部分と、前記サイドウオール層の上方で延びるサイド部分とを含む、請求項1 ~ 3の何れかーに記載の半導体装置。

## 【請求項6】

前記ダミー絶縁膜を覆う第2の層間絶縁膜を更に備え、該第2の層間絶縁膜の内部には 、前記導電性プラグに接続されたキャパシタが形成されている、請求項1~5の何れかー に記載の半導体装置。

# 【請求項7】

データプロセッサ、及び、前記データプロセッサに接続されたメモリを有するデータ処 理システムであって、

前記メモリが、

30

20

それぞれの表面が絶縁保護膜で被覆される複数の配線を含み、全体が第1の層間絶縁膜 に覆われた第1の配線層と、

前記第1の層間絶縁膜と異なる材料で形成され、それぞれが前記第1の層間絶縁膜の上 部 で 前 記 複 数 の 配 線 と 同 じ レ イ ア ウ ト で 延 び る 複 数 の ダ ミ ー 絶 縁 膜 と 、

前記複数の配線のうち隣接する2つの配線の間で、前記第1の層間絶縁膜を貫通し、前 記 隣 接 す る 2 つ の 配 線 及 び 対 応 す る 絶 縁 保 護 膜 と 自 己 整 合 的 に 形 成 さ れ た 導 電 性 プ ラ グ と を備えることを特徴とするデータ処理システム。

## 【請求項8】

表面が絶縁保護膜で被覆された複数の配線を含む第1の配線層を形成する工程と、

前記第1の配線層を覆って第1の層間絶縁膜を形成する工程と、

40

前記第1の層間絶縁膜上で前記複数の配線と同じレイアウトで延びるダミー絶縁膜を形

前記 複数の配線及び該複数の配線を被覆する絶縁保護膜と自己整合的に、前記第1の層 間絶縁膜を貫通するビアホールを形成する工程と、

前記ビアホール内にビアプラグを形成する工程とを有することを特徴とする半導体装置 の製造方法。

# 【発明の詳細な説明】

## 【技術分野】

# [0001]

本発明は、半導体装置、その製造方法、及び、データ処理システムに関し、更に詳しく

は、表面が保護絶縁膜で被覆された配線を有する半導体装置、その製造方法、及び、前記半導体装置を含むデータ処理システムに関する。

# 【背景技術】

## [0002]

近年、半導体装置の微細化が進むにつれ、ホールパターンをフォトリソグラフィ単独で 形成することが困難になっている。特に、DRAM装置のようなメモリ製品のセルアレイ 内では、最小ピッチで配置された配線層のスペース部に、同じく最小ピッチで並んだホー ルパターンを、その配線層とショートさせずに形成する必要がある。そのため、ホールサ イズの微細化は顕著となり、フォトリソグラフィでの形成が困難な状況となってきた。従 来は、その解決方法として、配線層の表面を被覆するようにして形成されたシリコンナイ トライド(SiN)保護膜をマスクとして、それに直交する形のスリットパターンを用い て選択エッチングすることによりホールパターンを形成する微細ホールパターン形成方法 が採用されている。選択エッチングでは、SiNに対して高い選択比で層間絶縁膜をエッ チングして、スリットパターンに対応するスリット溝を形成し、そのスリット溝の中に導 電性材料を埋め込む。次いで、配線層の表面を被覆するSiN膜をストッパとして、余分 な導電性材料をCMPによって除いて、導電性材料を個々のビアプラグに分離する。しか し、この方法では、マスクとなるSiN膜が、配線層加工時のエッチング、スリット溝の 開口時のエッチング、及び、CMPによる研磨と、複数回にわたって削られるため、最終 的に配線層を露出させないようにSiNの残膜を確保することが困難であった。また、残 膜を確保するために、このSiN膜の初期膜厚を増やすと、最小ピッチで配置された配線 層間の狭スペースを絶縁膜で埋めることが困難になる。このため、配線を保護するSiN 膜 の 膜 厚 の 確 保 が 、 半 導 体 装 置 の 微 細 化 に 障 害 と な る と い う 問 題 が あ っ た 。

#### [00003]

特許文献1は、上記問題を解決する手法を記載している。該特許文献では、DRAM装置のビット線を構成する配線層の表面を被覆するSiN保護膜を覆う層間絶縁膜の上に、NSG(non-siliconglass)から成るエッチストッパ膜を全面に形成し、その上にストレージノードを収容する厚い層間絶縁膜を形成している。層間絶縁膜のエッチングに際しては、エッチストッパ膜がSiN保護膜のエッチングを防止するので、SiN保護膜の膜厚減少が防止できる。層間絶縁膜がエッチングされたら、次いでエッチストッパ膜をエッチングし、更に、ビット線に対して自己整合エッチングを行って、シリコン基板の拡散層に達するコンタクトホールを形成する。エッチストッパ膜には、SigN₄膜などが使用される。

【特許文献1】特開2001-298082号公報

# 【発明の開示】

【発明が解決しようとする課題】

#### [0004]

上記特許文献に記載の方法によると、キャパシタと下地ノードを接続するためのコンタクトを形成する際のエッチングにおいては、配線層の表面を被覆するSiN保護膜のエッチング量は少なくなる。しかし、微細化が進むと、ストレージノードの穴径は小さくなり、その深さはますます増加するため、このようなキャパシタ形成用のエッチングと、下地ノードと接続するためのコンタクトを形成するエッチングとを同時に行う方法では、エッチング時のアスペクト比が大幅に増加してしまい、エッチングそのものが困難となる上に、他のノードとのショートや下地接続ノードに対する踏み外しを回避するための合わせ、寸法制御が困難になり、メモリセルの微細化にとって障害となる。

#### [00005]

本発明は、上記に鑑み、コンタクトホール形成の際の自己整合エッチングにあたり、まずホールパターンの代わりにスリットパターンを採用することにより、微細化した際のフォトリソグラフィでの解像性を向上させるとともに、スリットの延在方向への寸法精度、合わせずれの問題も回避することを可能とする。深さ方向もコンタクト形成だけを考慮した深さに設定可能でエッチング時のアスペクト比を最小限に抑えることが出来、更にその

10

20

30

- -

40

スリット分離の際に行う CMP用のマスクとなるダミー絶縁膜を配線を被服する絶縁保護膜とは別に設けることにより、SiN保護膜の残膜を確保することを可能とし、これらによって微細化を容易にした半導体装置、その製造方法、及び、そのような半導体装置を含むデータシステムを提供することを目的とする。

## 【課題を解決するための手段】

## [0006]

上記目的を達成するために、本発明は、それぞれの表面が絶縁保護膜で被覆される複数の配線を含み、全体が第1の層間絶縁膜に覆われた第1の配線層と、

前記第1の層間絶縁膜と異なる材料で形成され、それぞれが前記第1の層間絶縁膜の上部で前記複数の配線と同じレイアウトで延びる複数のダミー絶縁膜と、

前記複数の配線のうち隣接する2つの配線の間で、前記第1の層間絶縁膜を貫通し、前記隣接する2つの配線及び対応する絶縁保護膜と自己整合的に形成された導電性プラグとを備えることを特徴とする半導体装置を提供する。

## [0007]

また、本発明は、データプロセッサ、及び、前記データプロセッサに接続されたメモリを有するデータ処理システムであって、

前記メモリが、

それぞれの表面が絶縁保護膜で被覆される複数の配線を含み、全体が第1の層間絶縁膜に覆われた第1の配線層と、

前記第1の層間絶縁膜と異なる材料で形成され、それぞれが前記第1の層間絶縁膜の上部で前記複数の配線と同じレイアウトで延びる複数のダミー絶縁膜と、

前記複数の配線のうち隣接する2つの配線の間で、前記第1の層間絶縁膜を貫通し、前記隣接する2つの配線及び対応する絶縁保護膜と自己整合的に形成された導電性プラグとを備えることを特徴とするデータ処理システムを提供する。

#### [00008]

更に、本発明は、表面が絶縁保護膜で被覆された複数の配線を含む第1の配線層を形成する工程と、

前記第1の配線層を覆って第1の層間絶縁膜を形成する工程と、

前記第1の層間絶縁膜上で前記複数の配線と同じレイアウトで延びるダミー絶縁膜を形成する工程と、

前記複数の配線及び該複数の配線を被覆する絶縁保護膜と自己整合的に、前記第1の層間絶縁膜を貫通するビアホールを形成する工程と、

前記ビアホール内にビアプラグを形成する工程とを有することを特徴とする半導体装置の製造方法を提供する。

## 【発明の効果】

## [0009]

本発明の半導体装置、データ処理システム、及び、本発明の製造方法で得られた半導体装置では、導電性プラグを収容するコンタクトホールや、ビアホールの形成のための第1の層間絶縁膜のエッチングに際して、そのパターンが第1の配線層と直交するスリットパターンであるため、その方向への合わせずれは問題とならず、また、ラインパターンであるため、微細化に対するフォトリソグラフィの解像マージン、エッチングでの開口性確保も容易である。更にスリットエッチング時、及びコンタクト分離用CMPの際に、第1の配線層と同じレイアウトで各配線の上方に形成されたダミー絶縁膜によって、各配線の絶縁保護膜が保護されるので、絶縁保護膜の膜厚の減少が抑制できる。このため、配線、導電性プラグの寸法、間隔を縮小していった際の加工マージンを確保することができ、半導体装置やデータ処理システムのメモリの微細化が容易になる。

# 【発明を実施するための最良の形態】

## [0010]

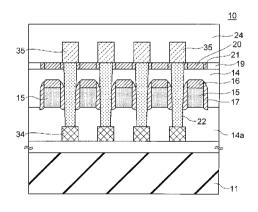

以下、本発明の例示的な実施形態について詳細に説明する。なお、全図を通して同様な要素には同様な符号を付して示した。図1は、本発明の第1の実施形態に係る半導体装置

10

20

30

40

の断面図である。図 2 は、その半導体装置のパターンレイアウトを示す。なお、図 1 は図 2 の I - I 線に沿う断面図である。

#### [0011]

図1及び図2において、半導体装置10は、半導体基板11と、その上部に形成される第1~第3の配線層34、15、35と、これら配線層の間を絶縁する第1~第4の層間絶縁膜14a、14、19、24と、第2の層間絶縁膜14と第4の層間絶縁膜24との間に挟まれ、第2の配線層15の各配線の上方に形成されたダミーマスク層20、21と、第1の配線層34と第3の配線層35とを接続するビアプラグ22とを有する。ビアプラグ22は、第2の配線層15に含まれる隣接する各2つの配線間を貫通している。

## [0012]

第2の配線層15の各配線には、SiN膜からなるキャップ層16、及び、サイドウオール層17を含むシシリコンナイトライド(SiN)保護膜が形成されており、これらのSiN保護膜によって第2の配線層15の各配線の表面が覆われている。ダミーマスク層は、SiN膜から成り、第2の配線層15の各配線を上方から覆い、且つ、各配線と同じパターンレイアウトを有し、各配線のルート上に延びている。ダミーマスク層20、21は、SiN保護膜のキャップ層16に平面的に重なる位置に形成された中央部分20と、サイドウオール層17に平面的に重なる位置に形成されたサイド部分21とから構成される。

## [0013]

本実施形態の半導体装置10では、まず、ビアホールを形成する際にホールパターンの代わりにスリットパターン28を採用している。これにより、微細化した際のフォトリゾグラフィでの解像性を向上させるとともに、スリットの延在方向への寸法精度、合わせずれの問題を回避することを可能としている。更に、狭いピッチで配線された第2の配線層15の上方に、その配線層のレイアウトと同じレイアウトを有するダミーマスク層20、21を形成している。この構成により、第2の配線層15及びSiN保護膜16、17をお配線構造と自己整合的にビアホールを形成するためのスリットパターン28をセフラインエッチングする際、ダミーマスク層20、21がそのエッチストッパ層となるアラインエッチングする際に行われるCMPのストッパ層としても機能することにより、その後のビア分離の際に行われるCMPのストッパ層とし、一個にすることで開口とCMPでのすりを組みため、その下方で第2の配線層15を保護するSiN保護膜16、17の膜厚減少を組みため、その下方で第2の配線層15を保護するSiN保護膜の膜厚減少を最小限にすることを可能とし、半導体装置の微細化が容易になる。

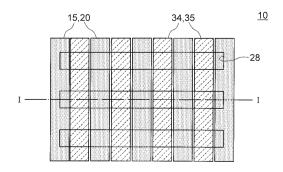

#### [0014]

図2に示すように、第2の配線層15の各配線とダミーマスク層の中央部分20とは、同じレイアウト上に位置し、第1の配線層34と第3の配線層35とは、同じレイアウト上に位置し、図示しないビアプラグ22は、第1の配線層と第3の配線層とを接続している。なお、同図に示した符号28は、ビアプラグ22を収容するホールパターンを形成する際に用いるスリットパターンを示し、また、そのスリットパターンによって第3の絶縁膜19に形成されるスリット溝を示している。

#### [0015]

本実施形態では、上記構造の作製にあたり、ビアプラグ22を収容するビアホールをエッチング形成する際に、第3の層間絶縁膜19の部分では、第2の配線層15の各配線と直交する方向に延びるスリット溝28(図2)を形成し、第1及び第2の層間絶縁膜14a、14の部分では、絶縁膜を貫通するビアホールとして形成する。本明細書では、以下、スリット溝28とスルーホール29とを含むパターンをホールパターンと呼ぶ。このホールパターンを形成した後に、全面に導電材料を堆積し、スルーホール29及びスリット溝28を埋め込む。次いで、CMPプロセスを用いて、堆積した導電材料を研磨し、この際にSiN膜から成るダミーマスク層20、21をエッチストップ層として用いる。この СMP研磨によって、スリット溝28の部分の導電材料が除かれて各ビアプラグが分離される。この工程により、第1の配線層34の各配線と、第3の配線層35の対応する配線 10

20

30

40

10

20

30

40

50

とを接続するビアプラグ22が得られることになる。

## [0016]

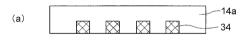

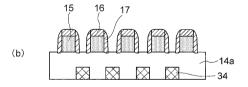

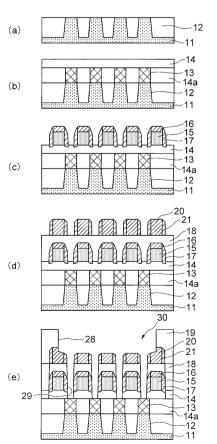

図3及び図4を参照して、上記実施形態に係る半導体装置を製造するプロセスを更に詳細に説明する。なお、これらの図では、半導体基板を含む、第1の配線層の下層構造の図示を省略している。まず、半導体基板の上方に、パターニングされた第1の配線層34、及び、第1の配線層34を覆う第1の層間絶縁膜14aを形成する(図3(a))。次いで、その上に、パターニングされたキャップ層16及び第2の配線層15を形成し、更に、このキャップ層16及び第2の配線層15の別壁にCVD法及びエッチバック法でサイドウオール層17を形成し、キャップ層16と共に、配線層15のSiN保護膜とする(図3(b))。

# [0017]

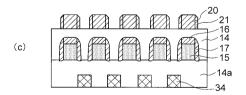

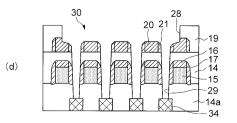

その後、第2の層間絶縁膜14を堆積し、その上に、第2の配線層15の各配線と同じレイアウトパターンを有するダミーマスク層20、21を形成する(図3(c))。ダニーマスク層20、21の形成では、まず、中央部分20をSiN膜の堆積及びパターで形成し、次いでサイド部分21をSiN膜の堆積及びエッチバックによって形成マスク層とし、次いでサイド部分21をSiN膜の堆積して後のエッチング用ハードマスク層としてアモルファスカーボン、プラズマSiON膜を堆積し(図示せず)、図2にスリット溝28のパターンを有するフォトレジストパターン(図示せず)を形成ずる。このフォトレジストパターン、及び前記ハードマスク層をマスクとして、且つて、ダモスク層20、21、及び、SiN保護膜16、17を含む第2の配線層15とビアングを行い、第3~第1の層間絶縁膜19、14、14aを貫通するエッチングでは、SiN膜に対して高い選択性を有するエッチングの合配線で第3の層間絶縁膜19内で第2の配線層15の路接する合とのといるで第3の層間絶縁膜19内で第2の配線層15の路接する名と、第2の配線層15の路接する名とから成るホールパターン30が形成される(図3(d))。

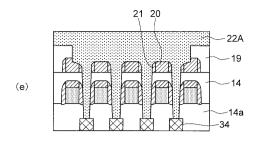

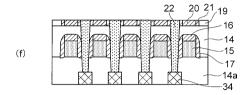

# [ 0 0 1 8 ]

その後、タングステン(W)層22Aを全面に堆積する(図4(e))。引き続き、CMP法によってW層22Aを研磨し、ダミーマスク層20、21をストッパとすることで、分離されたビアプラグ22が得られる(図4(f))。その後、ビアプラグ22の頂部に接する第3の配線層35を、研磨されたダミーマスク層20、21及び第3の層間絶縁膜19上に形成する。次いで、第4の層間絶縁膜24を全面に堆積する(図4(g))。【0019】

上記実施形態では、第2の配線層15の下部構造は、任意の構造のものが採用できる。 また、第2の配線層をゲート電極として構成し、第1の配線層を半導体基板内に形成され た拡散層として構成することも出来る。

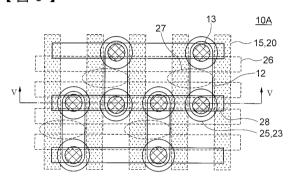

# [0020]

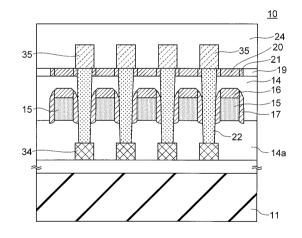

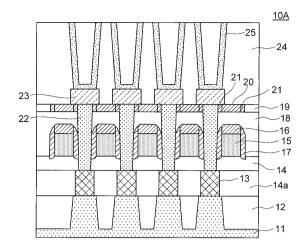

図5及び図6はそれぞれ、本発明の第2の実施形態に係る半導体装置の断面図、及び、その半導体装置のレイアウトパターンを示す平面図である。図5は、図6のV・V線に沿う断面図である。なお、図6には、エッチングの際に形成されるスリット溝28が示してある。本実施形態の半導体装置は、DRAM装置として構成される。DRAM装置10Aは、半導体基板11上に形成されており、半導体基板11は、素子分離領域12を構成する絶縁膜によって活性領域が区画されている。DRAM装置10Aは、第1~第5の層間絶縁膜14a、14、18、19、24と、ゲート電極26を構成する第1の配線層と、第2の層間絶縁膜14上に形成され、ビット線を構成する第2の配線層15と、第3の層間絶縁膜18上に、第2の配線層15の各配線に対応して配設されるダミーマスク層20、21上に形成されたランディングパッド23と、ランディングパッド23上に形成されたキャパシタノード25を有するキャパシタとを備える。

#### [ 0 0 2 1 ]

素子分離領域12で区画された活性領域の拡散層上には、下部電極(コンタクトプラグ

10

20

30

40

50

) 13が形成される。下部電極13とランディングパッド23とは、ビアプラグ22を介して接続される。下部電極13とランディングパッド23とに上下方向に挟まれた位置には、第2の配線層15が形成されている。ビアプラグ22は、第2の配線層15を構成する隣接する各2つのビット線の間に、セルフアラインプロセスを利用して形成されている

# [0022]

第2の配線層15を構成する各ビット線は、配線のパターニングに際してマスクとなるキャップ層16と、サイドウオール層17とによって覆われ、保護されている。キャップ層16及びサイドウオール層17は、第2の配線層15を保護するSiN保護膜を構成する。ダミーマスク層は、第2の配線層15のキャップ層16及びサイドウオール層17にそれぞれ対応する中央部分20及びサイド部分21から成り、ビット線と同じレイアウトパターンで配置されている。キャップ層16及びサイドウオール層17は、ビット線15とダミーマスク層の中央部分20とにミスアライメントが生じた際には、ビット線15とビアプラグ22とのショートを防止する配線保護層として機能する。図6には、半導体装置の全体レイアウトを示すために、第2の配線層と直交方向に延びるゲート電極26と、ゲート電極の間にこれらとセルフアライメントで形成されるソースコンタクト27とが示されている。

## [0023]

本実施形態のDRAM装置10Aでは、狭いピッチで配線されたビット線を構成する第2の配線層15の上方に、ビット線のレイアウトと同じレイアウトを有するダミーマスク層20、21を形成している。この構成により、ビット線15及びSiN保護膜16、17を含む配線構造と自己整合的にビアホールを形成する際、スリット開口とCMPでのすりきりを組み合わせたビア開口プロセスにて最も問題となるCMPすりきり時のビット線15を保護するSiN保護膜16、17の膜厚減少が防止できる。このため、ビット線15を覆うSiN保護膜16、17の設計厚みを小さくでき、ビアプラグ22の設計上の間隔を小さくできるので、半導体装置の微細化が容易になる。

#### [0024]

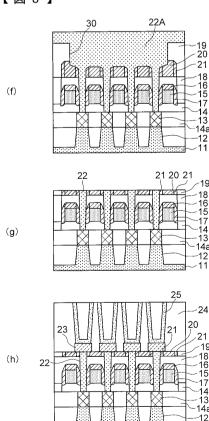

図7及び図8を参照しながら、第2の実施形態に係る半導体装置であるDRAM装置の製造プロセスを説明する。まず、半導体基板11の表面部分に、通常の素子分離(STI)領域12を形成し、半導体基板11を、複数の活性領域に区画する(図7(a))。次いで、活性領域に、ソース・ドレイン拡散層及びゲート電極を含むMISFET(図示せず)を形成する。次いで、CVD法によりシリコン酸化膜を成膜し、CMP法により平坦化して第1の層間絶縁膜14aを形成する。その後、フォトリソグラフィ、及び、ドライエッチングにより、第1の層間絶縁膜14aをパターニングして、活性領域の拡散層上にコンタクトホールを開口する。コンタクトホール内を含む第1の層間絶縁膜14a上にポリシリコンを堆積し、CMP法により分離して下部電極13を形成する。その後、更にCVD法によりシリコン酸化膜を成膜し、CMP法により平坦化して第2の層間絶縁膜14を形成する(図7(b))。

# [0025]

その後、CVD法などにより、タングステン(W)膜、及び、SiN膜を堆積し、フォトリソグラフィ、及び、ドライエッチングにより、ビット線15、及び、キャップ層16を形成する。更に、CVD法によりSiN膜を堆積し、エッチバックによりサイドウオール層17を形成する。これによって、SiN保護膜によって表面が保護されたビット線から成る第2の配線層15が得られる(図7(c))。続いて、その上にCVD法などにより、シリコン酸化膜を成膜し、CMP法により平坦化することにより第3の層間絶縁膜18を形成する。

#### [0026]

次に、CVD法などによりSiN膜を堆積し、フォトリソグラフィ、及び、ドライエッチングによりダミーマスク層の中央部分20を形成する。中央部分20は、ビット線15と同じレイアウトパターンとなるようにパターニングする。次いで、CVD法などにより

SiN膜を堆積し、エッチバック法によりダミーマスク層のサイド部分21を形成する(図7(d))。次に、CVD法などによりシリコン酸化膜を成膜し、CMP法により平坦化することにより、第4の層間絶縁膜19を形成する。その上に、後のドライエッチング用ハードマスク層としてアモルファスカーボン、プラズマSiON膜を堆積した後(図示せず)、フォトリソグラフィ、及び、ドライエッチングにより、第4~第2の層間絶縁膜19、18、14をエッチングする。このエッチングには、図6に示したスリット溝28のパターンを有するフォトレジストマスク、及び前記ハードマスク層をエッチングマスクとし、且つ、SiNに対して高い選択比で第4~第2の層間絶縁膜19、18、14をパターニングする。これにより、第4の層間絶縁膜19に形成されたスリット溝28と、第2及び第3の層間絶縁膜に形成されたスルーホール29とから成るホールパターン30が形成される(図7(e))。これによって、下部電極13の頂部が開口する。

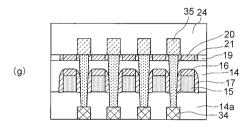

[0027]

次いで、スリット溝28及びスルーホール29を含むホールパターン30内を含む全面にタングステン層22Aを堆積する(図8(f))。更に、ダミーマスク層20、21をストッパとして、タングステン層22AをCMP法により研磨することで、スリット溝28内のタングステン層を除去し、相互に分離されたビアプラグ22を形成する(図8(g))。次に、CVD法によりタングステン膜を成膜し、フォトリソグラフィ、及び、ドライエッチングによりランディングパッド23を形成する。その後は、通常のDRAMのキャパシタ形成プロセスにより、キャパシタを収容する第5の層間絶縁膜24、及び、キャパシタノード25を形成する(図8(h))。その後は、公知のプロセスを採用することにより、DRAM装置を完成させる。

[0028]

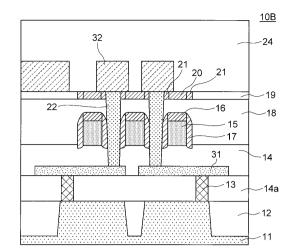

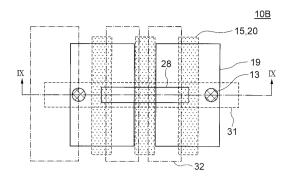

図9は、本発明の第3の実施形態に係る半導体装置を示す断面図である。また、図10は、図2などと同様に、本実施形態の半導体装置のレイアウトパターンを示している。なお、図9は、図10のIX-IX線に沿う断面図である。

[0029]

本実施形態の半導体装置は、本発明の構成をロジック回路に適用した例であり、第2の実施形態における下部電極13、ビット線15、ランディングパッド23を、タングステンやアルミニウム、銅などで形成された配線層に置き換えている。半導体装置10Bは、以下の工程により製造される。まず、半導体基板11上に、通常の半導体装置の製造工程で用いられるSTIプロセスにより素子分離領域12を形成して、活性領域を区画する。その後、活性領域にソース・ドレイン拡散層、及び、ゲート電極を有するMISFET(図示せず)を形成する。次いで、CVD法などによりシリコン酸化膜を成膜し、CMP法により平坦化することにより、第1の層間絶縁膜14aを形成する。

[0030]

次に、フォトリソグラフィ、及びドライエッチングにより活性領域内の拡散層上にコンタクトホールを開口する。次いで、CVD法などにより、このコンタクトホール内にタングステンを埋め込み、CMP法などを用い、第1の層間絶縁膜14a上のタングステンを除去することにより、コンタクトプラグ13を形成する。次に、CVD法などによりタングステンを成膜し、フォトリソグラフィ、及び、ドライエッチングにより第1の配線層31を形成する。その後、CVD法などによりシリコン酸化膜を成膜し、CMP法により平坦化することにより第2の層間絶縁膜14を形成する。

[0031]

次に、CVD法などによりタングステン及びSiN膜を堆積し、フォトリソグラフィ、及び、ドライエッチングにより第2の配線層15、SiN膜から成るキャップ層16を形成する。その後、CVD法などによりSiN膜を堆積し、エッチバック法によりサイドウオール層17を形成する。次に、CVD法などによりシリコン酸化膜を成膜し、CMP法により平坦化することにより第3の層間絶縁膜18を形成する。その後、CVD法などによりSiN膜を堆積しフォトリソグラフィ、及び、ドライエッチングによりダミーマスク層の中央部分20を形成する。ダミーマスク層の中央部分20は、前記第2配線層15と

10

20

30

40

10

20

30

40

50

全く同じレイアウトパターンに形成する。その後、 C V D 法などにより S i N 膜を堆積し 、エッチバック法によりダミーマスク層のサイド部分 2 1 を形成する。

## [0032]

次に、CVD法などによりシリコン酸化膜を成膜し、CMP法により平坦化することにより第4の層間絶縁膜19を形成する。その上に、後のドライエッチング用ハードマスク層としてアモルファスカーボン、プラズマSiON膜を堆積した後(図示せず)、フォトリソグラフィ、及び、ドライエッチングにより、第2の配線層15及びダミーマスク層20、21に直交したスリットパターン28とスルーホール29とを含むホールパターンを、第4~第2絶縁膜19、18、14中に開口する。このドライエッチングでは、SiNに対して高選択性を有するエッチングプロセスを採用する。このドライエッチングでは、ダミーマスク層20、21、キャップ層16、及び、サイドウオール層17がマスクとなり、スリットパターン28を含むホールパターンがセルフアラインプロセスで開口される

[0033]

引き続き、スリッパターントを含むホールパターン内を、 C V D 法などによりタングステンで埋め込む。次いで、ダミーマスク層 2 0 、 2 1 をストッパとして C M P を行い、各スルーホール 2 9 内のタングステンを相互から切り離して、ビアプラグ 2 2 を形成する。 【 0 0 3 4 】

次に、アルミニウム膜を成膜し、フォトリソグラフィ、及び、ドライエッチングにより第3の配線層32を形成し、その後、CVD法などによりシリコン酸化膜を成膜し、CMP法により平坦化することにより、第5の層間絶縁膜24を形成する。これによって、図9に示すロジック回路を構成する半導体装置10Bを得る。

[ 0 0 3 5 ]

本実施形態では、半導体製品で用いられるロジック回路の信号線において、狭スペースで形成された信号配線層のスペース部に、その信号線とショートすることなくセルフアラインでビアプラグを形成することが出来る。このため、狭いスペースで信号配線層を挟んで形成された上下層の信号線の間の接続が可能になる。掛かる構成により、信号線の接続にあたり、より多様な接続関係を可能とし、レイアウト面積を減少させることも出来る。【0036】

また、上記実施形態において、配線層やビアプラグに用いられる材料も、銅などといった導電性材料であれば使用可能である。さらに、スリットパターンを含むホールパターンをセルフアラインプロセスで開口するにあたっては、上記実施形態で用いたSiN以外であってもよく、ドライエッチングやCMPに際して、酸化膜のエッチングレートや研磨レートよりも遅い絶縁膜であればストッパ膜として採用できる。

[0037]

従来は、配線層の保護膜の厚みについては、配線層加工時、ビアホール開口時、及び、CMP時の全ての工程段階での膜厚の減少を考慮してその膜厚を設定する必要があったが、本実施形態では、実質的に配線層のパターニングの際の膜厚減少のみを考慮した膜厚に設定できる。このため、ビアホール内に形成されるビアプラグの配列ピッチを小さく設計でき、半導体装置の更なる高密度化が可能になる。また、本発明の構造を、半導体製品のロジック回路内の配線構造に用いることにより、信号線の接続にあたり、より多様な接続関係を可能とするため、ロジック回路においても、レイアウト面積を縮小させることが出来る。

[0038]

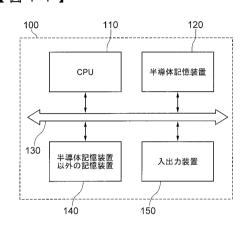

図11は、本発明の第4の実施形態に係る半導体装置の構成を示すブロック図である。本半導体装置は、前記第2の実施形態に係るDRAM装置(半導体記憶装置)を含むデータ処理システムを構成する。データ処理システム100は、CPU(Central Processing Unit)110と、半導体記憶装置120と、半導体記憶装置以外の記憶装置140と、入出力装置150とを備えている。図11では、CPU110はシステムバス130を介して半導体記憶装置120に接続されているが、システムバス130を介さずにローカル

なバスによって接続されても良い。システムバス130は、図面の簡略化のため1本のみ を描いているが、実際は複数のバスを含み、これらは必要に応じてコネクタなどを介し、 シリアルないしパラレルに接続される。なお、図示したように、必要に応じて第2の実施 形態の半導体記憶装置以外の記憶装置140や、入出力装置150がシステムバス130 に接続される。

## [0039]

入出力装置150には、例えば液晶ディスプレイなどのディスプレイデバイスが含まれ る。半導体記憶装置以外の記憶装置140には、ハードディスクやMOドライブなどが含 まれる.しかし、これらには限定されない。入出力装置150には、入力装置と出力装置 のいずれか一方のみの場合も含まれる。半導体記憶装置 1 2 0 は、例えば R A M (Random Access Memory) や R O M (Read Only Memory) であり、具体的には S R A M (Static R andom-Access-Memory), S D R A M (Synchronous Dynamic Random-Access-Memory), D D R - S D R A M (Double Data Rate Synchronous Dynamic Random-Access-Memory) DDR2-SDRAM (Double Data Rate 2 Synchronous Dynamic Random-Access-Mem ory), DDR3-SDRAM (Double Data Rate 3 Synchronous Dynamic Random-Acces s-Memory ) 等の D R A M 、 フラッシュメモリ 等の半 導 体 素 子 か ら 構 成 さ れ る 記 憶 媒 体 で あ る。さらに、各構成要素の個数は、図11では簡略化のため、1つの記載にとどめている が、それには限定されず、全てまたはいずれかの要素が複数個の場合も含まれる。

#### [0040]

本発明の半導体装置としては、DRAM装置の他に、NAND型フラッシュメモリなど のメモリ機能を有する半導体記憶装置、マイクロプロセッサーなどのロジック機能を有す る 半 導 体 装 置 、 そ れ ら の 2 つ 以 上 が 混 載 さ れ た 任 意 の シ ス テ ム を 構 成 す る 半 導 体 装 置 な ど が挙げられる。

#### [0041]

本発明を特別に示し且つ例示的な実施形態を参照して説明したが、本発明は、その実施 形態及びその変形に限定されるものではない。当業者に明らかなように、本発明は、添付 の ク レ ー ム に 規 定 さ れ る 本 発 明 の 精 神 及 び 範 囲 を 逸 脱 す る こ と な く 、 種 々 の 変 更 が 可 能 で ある。

【図面の簡単な説明】

[0042]

- 【図1】本発明の第1の実施形態に係る半導体装置の断面図。

- 【 図 2 】 図 1 の 半 導 体 装 置 の パ タ ー ン レ イ ア ウ ト を 示 す 平 面 図 。

- 【図3】(a)~(d)は、第1の実施形態の半導体装置の製造工程を順次に示す断面図

- 【図4】(e)~(g)は、図3に続く工程を順次に示す断面図。

- 【図5】本発明の第2の実施形態に係る半導体装置の断面図。

- 【 図 6 】 図 5 の 半 導 体 装 置 の パ タ ー ン レ イ ア ウ ト を 示 す 平 面 図 。

- 【図7】(a)~(e)は、第2の実施形態の半導体装置の製造工程を順次に示す断面図

【図8】(f)~(h)は、図7に続く工程を順次に示す断面図。

- 【図9】本発明の第3の実施形態に係る半導体装置の断面図。

- 【 図 1 0 】 図 9 の 半 導 体 装 置 の パ タ ー ン レ イ ア ウ ト を 示 す 平 面 図 。

- 【 図 1 1 】 本 発 明 の 第 4 の 実 施 形 態 に 係 る 半 導 体 装 置 の ブ ロ ッ ク 図 。

【符号の説明】

[0043]

- 10,10A、10B:半導体装置

- 1 1 : 半導体基板

- 1 2 : 素子分離領域

- 13:下部電極(コンタクトプラグ)

- 14 a、14、18、19、24: 絶縁膜

10

20

30

40

15:第2の配線層 16:キャップ層

17:サイドウオール層

20、21:ダミーマスク層

22:ビアプラグ

23:ランディングパッド

25:キャパシタノード

2 6 : ゲート電極

27:ソースコンタクト

28:スリット溝(スリットパターン)

2 9:スルーホール3 0:ホールパターン3 1:第1の配線層3 2:第3の配線層3 4:第1の配線層

3 5 : 第 3 の配線層

# 【図1】

# 【図2】

# 【図3】

# 【図4】

# 【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】