#### (19) **日本国特許庁(JP)**

# (12) 公 開 特 許 公 報(A)

(11)特許出願公開番号

特開2018-133592 (P2018-133592A)

(43) 公開日 平成30年8月23日(2018.8.23)

(51) Int. Cl.

FL

テーマコード (参考)

HO1L 29/786

(2006, 01)

HO1L 29/78 612B 5F110

HO1L 29/78 618B

審査請求 有 請求項の数 4 〇L (全 50 頁)

(21) 出願番号 特願2018-97771 (P2018-97771) (71) 出願人 000153878 (22) 出願日 平成30年5月22日 (2018.5.22) 株式会社半導体エネルギー研究所 (62) 分割の表示 特願2016-133240 (P2016-133240) 神奈川県厚木市長谷398番地 (72) 発明者 の分割 山崎 舜平 平成22年8月26日 (2010.8.26) 神奈川県厚木市長谷398番地 株式会社 原出願日 特願2009-196618 (P2009-196618) (31) 優先権主張番号 半導体エネルギー研究所内 平成21年8月27日 (2009.8.27) (72) 発明者 坂田 淳一郎 (32) 優先日 (33) 優先権主張国 日本国(JP) (72) 発明者 津吹 将志

神奈川県厚木市長谷398番地 株式会社

半導体エネルギー研究所内

神奈川県厚木市長谷398番地 株式会社

半導体エネルギー研究所内

(72) 発明者 秋元 健吾

神奈川県厚木市長谷398番地 株式会社

半導体エネルギー研究所内

最終頁に続く

## (54) 【発明の名称】表示装置

## (57)【要約】

【課題】同一基板上の画素回路及び駆動回路を該回路の 特性にそれぞれ合わせた構造の異

なるトランジスタで形成し、表示特性の優れた表示装置 を提供する。

【解決手段】同一基板上に画素部と駆動回路部を有し、 該駆動回路部は、ゲート電極層、

ソース電極層及びドレイン電極層が金属膜によって構成 され、且つチャネル層が酸化物半

導体によって構成された駆動回路用トランジスタを有す る。また、当該画素部は、ゲート

電極層、ソース電極層及びドレイン電極層が酸化物導電 体によって構成され、且つ半導体

層が酸化物半導体によって構成された画素用トランジス タを有する。該画素用トランジス

タは透光性を有する材料で形成されており、高開口率の 表示装置を作製することができる

【選択図】図3

#### 【特許請求の範囲】

## 【請求項1】

ゲート電極層と、

ゲート絶縁層と、

酸化物半導体層と、

ソース電極層及びドレイン電極層と、

酸化物絶縁層と、を有し、

前記酸化物半導体層は、前記ソース電極層と接する第1の領域と、前記ドレイン電極層と接する第2の領域と、を有し、

前記ソース電極層及び前記ドレイン電極層は、金属であり、

前記酸化物絶縁層は、前記酸化物半導体層と接する領域を有し、

前記第1の領域は、前記第1の領域の酸素の前記ソース電極層への移動によりn型化されている領域を有し、

前記第2の領域は、前記第2の領域の酸素の前記ドレイン電極層への移動により n 型化されている領域を有し、

前記ソース電極層の前記第1の領域に接する領域は、前記金属の酸化物が形成され、

前記ドレイン電極層の前記第2の領域に接する領域は、前記金属の酸化物が形成されていることを特徴点とする表示装置。

#### 【請求項2】

請求項1において、

前記酸化物半導体層の、前記第1の領域及び前記第2の領域における厚さは、15nm以上50nm以下であり、

前記第1の領域の、前記ソース電極層との界面はn型化されており、

前記第2の領域の、前記ドレイン電極層との界面はn型化されていることを特徴とする表示装置。

## 【請求項3】

請求項1において、

前記酸化物半導体層の、前記第1の領域及び前記第2の領域における厚さは、15nm 未満であり、

前記第1の領域の、前記ソース電極層との界面及び前記ソース電極層との界面以外の領域はn型化されており、

前記第2の領域の、前記ドレイン電極層との界面及び前記ドレイン電極層との界面以外の領域はn型化されていることを特徴とする表示装置。

## 【請求項4】

請求項1乃至3のいずれか一項において、

前記金属は、Ti、Mo、W、Al、Cr、Cu、Ta、から選ばれた元素、又はこれらの元素を成分とする合金、又はこれらの元素を組み合わせた合金によって構成されている表示装置。

【発明の詳細な説明】

# 【技術分野】

[ 0 0 0 1 ]

本発明は酸化物半導体を用いる表示装置に関する。

#### 【背景技術】

## [0002]

近年、絶縁表面を有する基板上に形成された半導体薄膜を用いてトランジスタを構成する技術が注目されている。トランジスタはICや電気光学装置のような電子デバイスに広く応用され、特に画像表示装置のスイッチング素子として開発が急がれている。金属酸化物は多様に存在しさまざまな用途に用いられている。酸化インジウムはよく知られた材料であり、液晶ディスプレイなどで必要とされる透明電極材料として用いられている。

#### [0003]

50

10

20

30

20

30

40

50

金属酸化物の中には半導体特性を示すものがある。半導体特性を示す金属酸化物としては、例えば、酸化タングステン、酸化錫、酸化インジウム、酸化亜鉛などがあり、このような半導体特性を示す金属酸化物をチャネル形成領域とするトランジスタが既に知られている(特許文献1及び特許文献2)。

[0004]

また、酸化物半導体を適用したトランジスタは、比較的電界効果移動度が高い。そのため、当該トランジスタを用いて、表示装置などの駆動回路を構成することもできる。

【先行技術文献】

【特許文献】

[00005]

【特許文献 1 】特開 2 0 0 7 - 1 2 3 8 6 1 号公報

【特許文献2】特開2007-96055号公報

【発明の概要】

【発明が解決しようとする課題】

[0006]

表示装置等において、画素部(画素回路とも言う)と駆動回路部を同一基板上に形成する場合、画素部に用いるトランジスタには、優れたスイッチング特性、例えばオンオフ比が大きいことが要求され、駆動回路に用いるトランジスタには高速動作が要求される。

[0007]

特に、表示装置の画素密度が高い程、表示画像の書き込み時間が短くなるため、駆動回路に用いるトランジスタは高速で動作することが好ましい。また、画素部においては、画素密度が高いほど開口率が小さくなる問題があった。

[00008]

従って、本明細書で開示する本発明の一態様は、上記課題を解決する表示装置及びその作 製方法に関する。

【課題を解決するための手段】

[0009]

本明細書で開示する本発明の一態様は、同一基板上に画素部と、駆動回路部と、を有し、 画素部は、第1のゲート電極層と、第1のゲート電極層上にゲート絶縁層と、ゲート絶縁 層上に第 1 のゲート電極層と一部が重なる第 1 のソース電極層及び第 1 のドレイン電極層 と、ゲート絶縁層上に第1のソース電極層及び第1のドレイン電極層と一部が重なる第1 の酸化物半導体層と、を含む第1のトランジスタと、第1のソース電極層、第1のドレイ ン電極層、及び第1の酸化物半導体層上に第1の酸化物絶縁層と、第1の酸化物絶縁層上 に 第 1 の ド レ イ ン 電 極 層 と 電 気 的 に 接 続 す る 接 続 電 極 層 と 、 第 1 の 酸 化 物 絶 縁 層 及 び 接 続 電極層上に第2の酸化物絶縁層と、第2の酸化物絶縁層上に保護絶縁層と、保護絶縁層上 に接続電極層と電気的に接続する画素電極層と、を有し、駆動回路部は、第2のゲート電 極 層 と 、 第 2 の ゲ ー ト 電 極 層 上 に ゲ ー ト 絶 縁 層 と 、 ゲ ー ト 絶 縁 層 上 に 第 2 の 酸 化 物 半 導 体 層と、第2の酸化物半導体層上に該第2の酸化物半導体層と一部が重なる第2のソース電 極層及び第2のドレイン電極層と、を含む第2のトランジスタと、第2のソース電極層、 第 2 の ド レ イ ン 電 極 層 、 及 び 第 2 の 酸 化 物 半 導 体 層 上 に 第 2 の 酸 化 物 絶 縁 層 と 、 第 2 の 酸 化物絶縁層上に保護絶縁層と、を有し、第1のゲート電極層、ゲート絶縁層、第1の酸化 物半導体層、第1のソース電極層、第1のドレイン電極層、第1の酸化物絶縁層、第2の 酸化物絶縁層、保護絶縁層及び画素電極層は透光性を有することを特徴とする表示装置で ある。

[ 0 0 1 0 ]

なお、本明細書において第1、第2として付される序数詞は便宜上用いるものであり、工程順又は積層順を示すものではない。また、発明を特定するための事項として固有の名称を示すものではない。

[ 0 0 1 1 ]

上記第1のトランジスタの第1のゲート電極層、第1のソース電極層及び第1のドレイン

電極層は、金属酸化物で形成されており、第2のトランジスタの第2のゲート電極層、第 2のソース電極層及び第2のドレイン電極層は、金属で形成されている。

#### [0012]

上記金属酸化物には、酸化インジウム、酸化インジウム酸化スズ合金、酸化インジウム酸 化亜鉛合金、または酸化亜鉛を用いることができる。

#### [ 0 0 1 3 ]

また、 画素部の第 2 の酸化物絶縁層と保護絶縁層の間には、透光性を有する平坦化絶縁層が形成されていても良い。

#### [0014]

また、駆動回路部の第2の酸化物半導体層と重なる保護絶縁層上には、導電層が形成されても良い。

#### [0015]

また、第1の酸化物絶縁層及び第2の酸化物絶縁層には、スパッタ法で形成される無機絶縁膜を用いると良い。例えば、酸化珪素、窒化酸化珪素、酸化アルミニウム、または酸化窒化アルミニウムなどを用いることができる。

#### [0016]

また、第2のトランジスタの第2の酸化物半導体層と第2のソース電極層との間、及び第 2の酸化物半導体層と第2のドレイン電極層とのそれぞれの間には、酸化物導電層が形成 されている構成としても良い。この様な構成とすることで接触抵抗を低減することができ 、高速動作が可能なトランジスタを実現できる。なお、酸化物導電層としては、酸化亜鉛 を成分として含むものが好ましく、酸化インジウムを含まないものであることが好ましい 。そのような酸化物導電層として、酸化亜鉛、酸化亜鉛アルミニウム、酸窒化亜鉛アルミ ニウム、酸化亜鉛ガリウムなどが挙げられる。

#### [0017]

また、本明細書で開示する本発明の他の一態様は、画素部となる領域に第1のゲート電極層を形成し、駆動回路層上にゲート電極層を形成し、第1のゲートート電極層を形成し、駆動回路層上にゲート電極層を形成し、第1のゲートート絶縁層を形成した。第1のゲートール経層を形成した。第1のゲートール経層を形成した。第1のドレイン電極層を形成して第1のトランスタを形成し、第1の酸化物に第2のゲートの酸化物半導体層を形成し、第1の酸化物半導体層を形成し、第1の酸化物半導体層の一部と重なる第2の酸化物半導体層の第2のドレイン電極層を形成して第2のドレイン電極層を形成が第2のドレイン電極層を形成が第2のドレイン電極層と電気的に接続する接続電極層を形成することを特徴とする表示装置の作製統電極層と電気的に接続する画素電極層を形成することを特徴とする表示装置の作製統電極層と電気的に接続する画表である。

## [0018]

上記作製方法の構成において、第1のゲート電極層、ゲート絶縁層、第1の酸化物半導体層、第1のソース電極層、第1のドレイン電極層、第1の酸化物絶縁層、第2の酸化物絶縁層、保護絶縁層及び画素電極層は透光性を有する。

## [0019]

また、第1の酸化物半導体層及び第2の酸化物半導体層上に形成される酸化物絶縁層の形成は、酸化物半導体層を脱水化または脱水素化した後、大気に触れることなく行い、酸化物半導体層への水や水素の再混入を防止することが好ましい。

#### [0020]

本明細書において、脱水化または脱水素化とは、水や $H_2$ を脱離させていることのみを示すものではなく、H、O H などを脱離することも含まれる。

## [0021]

50

10

20

30

脱水化または脱水素化は、窒素、または希ガス(アルゴン、ヘリウムなど)の不活性気体雰囲気下で、400 以上基板の歪み点未満、好ましくは425 以上700 以下の加熱処理で行うことが好ましい。

#### [0022]

窒素、または希ガス(アルゴン、ヘリウムなど)の不活性気体雰囲気下での加熱処理を行った場合、酸化物半導体層は加熱処理により酸素欠乏型となって低抵抗化、即ちn型化(n型化など)させ、その後、酸化物半導体層に接する酸化物絶縁層の形成を行うことにより酸化物半導体層を酸素過剰な状態とすることで高抵抗化、即ちi型化させているとも言える。これにより、電気特性が良好で信頼性のよいトランジスタを有する表示装置を作製し、提供することが可能となる。

[0023]

脱水化または脱水素化を行った酸化物半導体層の熱処理条件は、脱水化または脱水素化後の酸化物半導体層に対してTDS(昇温脱離ガス分析)で450 まで測定を行っても水の脱離を示す2つのピーク、少なくとも300 付近に現れる1つのピークは検出されない程度とする。従って、脱水化または脱水素化が行われた酸化物半導体層を用いたトランジスタに対してTDSで450 まで測定を行っても少なくとも300 付近に現れる水のピークは検出されない。

#### [0024]

脱水化または脱水素化を行った酸化物半導体層は大気に触れさせることなく、水または水 素を再び混入させないことが重要である。脱水化または脱水素化を行い、酸化物半導体層 を低抵抗化、即ちn型化(n<sup>-</sup>型、n<sup>+</sup>型など)させた後、高抵抗化させてi型とした酸 化 物 半 導 体 層 を 用 い た ト ラ ン ジ ス タ は 、 そ の し き い 値 電 圧 値 が 正 で あ り 、 所 謂 ノ ー マ リ ー オフ特性を示す。表示装置に用いるトランジスタは、ゲート電圧が0Vにできるだけ近い 正のしきい値電圧であることが好ましい。アクティブマトリクス型の表示装置においては 、 回 路 を 構 成 す る ト ラ ン ジ ス タ の 電 気 特 性 が 重 要 で あ り 、 こ の 電 気 特 性 が 表 示 装 置 の 性 能 を左右する。特に、トランジスタのしきい値電圧は重要である。トランジスタのしきい値 電 圧 値 が 負 で あ る と 、 ゲ ー ト 電 圧 が 0 V で も ソ ー ス 電 極 と ド レ イ ン 電 極 の 間 に 電 流 が 流 れ る、所謂ノーマリーオン特性となり、該トランジスタで構成した回路を制御することが困 難となる。また、しきい値電圧値が正であっても、その絶対値が高いトランジスタの場合 には、駆動電圧が足りずにスイッチング動作そのものができないことがある。 n チャネル 型のトランジスタの場合は、ゲート電圧に正の電圧を印加してはじめてチャネルが形成さ れて、ドレイン電流が流れ出すトランジスタであることが望ましい。駆動電圧を高くしな いとチャネルが形成されないトランジスタや、負の電圧状態でもチャネルが形成されてド レイン電流が流れるトランジスタは、回路に用いるトランジスタとしては不向きである。

[0025]

脱水化または脱水素化を行った温度から降温させる際の雰囲気は、昇温時または加熱処理時の雰囲気と異なる雰囲気に切り替えてもよい。例えば、脱水化または脱水素化を行った同じ炉で大気に触れさせることなく、炉の中を高純度の酸素ガス、N<sub>2</sub>Oガス、または超乾燥エア(露点が - 40 以下、好ましくは - 60 以下)で満たして冷却を行うことができる。

[0026]

また、トランジスタは静電気などにより破壊されやすいため、ゲート線またはソース線に対して、画素部のトランジスタの保護用の保護回路を同一基板上に設けることが好ましい。 、保護回路は、酸化物半導体層を用いた非線形素子を用いて構成することが好ましい。

[0027]

本発明の一態様の表示装置は、同一基板上において、駆動回路用トランジスタを有する駆動回路部、及び画素用トランジスタを有する画素部が作製される。そのため、表示装置の製造コストを低減することができる。

## 【発明の効果】

[0028]

10

20

30

脱 水 化 ま た は 脱 水 素 化 を 行 う 加 熱 処 理 が 行 わ れ た 酸 化 物 半 導 体 層 を 用 い る こ と に よ り 、 電 気特性が良好なトランジスタを作製することができる。また、画素回路に用いるトランジ スタを透光性を有する材料で形成することで、開口率が高く、表示特性の優れた表示装置 を作製することができる。また、同一基板上に画素回路と駆動回路を有する表示装置にお いて、該回路が必要とする電気特性を得やすい様に、該回路のそれぞれを構造の異なるト ランジスタで形成することができる。

【図面の簡単な説明】

- [0029]

- 【図1】本発明の一態様を示す断面工程図。

- 【図2】本発明の一態様を示す断面工程図。

- 【図3】本発明の一態様を示す断面図。

- 【図4】本発明の一態様を示す断面図及び平面図。

- 【図5】本発明の一態様を示す断面図及び平面図。

- 【図6】本発明の一態様を示す断面図。

- 【図7】表示装置のブロック図を説明する図。

- 【図8】信号線駆動回路の構成を説明する図及び動作を説明するタイミングチャート。

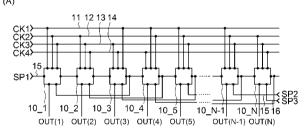

- 【図9】シフトレジスタの構成を示す回路図。

- 【図10】シフトレジスタの構成を説明する図及び動作を説明するタイミングチャート。

- 【図11】表示装置を説明する断面図。

- 【図12】表示装置を説明する平面図。

- 【図13】表示装置を説明する平面図。

- 【図14】表示装置の等価回路を示す図。

- 【図15】表示装置を説明する断面図。

- 【図16】表示装置を説明する平面図。

- 【図17】表示装置を説明する平面図。

- 【図18】表示装置の等価回路を示す図。

- 【図19】表示装置を説明する断面図。

- 【図20】表示装置を説明する平面図。

- 【図21】表示装置を説明する断面図。

- 【図22】表示装置を説明する平面図。

- 【図23】表示装置を説明する断面図。

- 【図24】表示装置を説明する平面図。

- 【図25】電子機器を示す図。

- 【図26】電子機器を示す図。

- 【図27】電子機器を示す図。

- 【図28】本発明の一態様を示す断面図。

- 【発明を実施するための形態】

- [0030]

以下では、本発明の実施の形態について図面を用いて詳細に説明する。ただし、本発明は 以下の説明に限定されず、その形態および詳細を様々に変更し得ることは、当業者であれ ば容易に理解される。また、本発明は以下に示す実施の形態の記載内容に限定して解釈さ れるものではない。なお、本明細書中の図面において、同一部分または同様な機能を有す る部分には同一の符号を付し、その説明は省略する場合がある。

[0031]

(実施の形態1)

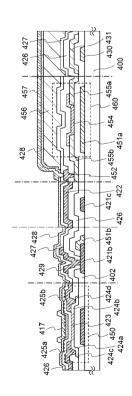

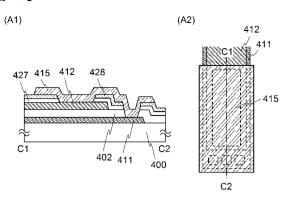

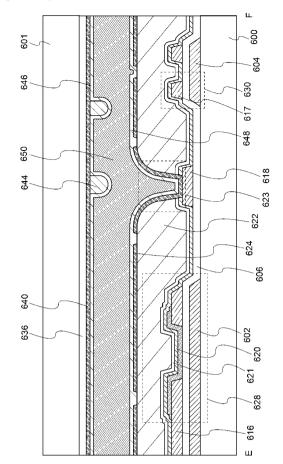

本実施の形態では、表示装置及びその作製方法の一形態を図面を用いて詳細に説明する。 図 1 ( E )に同一基板上に形成された駆動回路のトランジスタ、画素部のトランジスタ及 び ゲ ー ト 配 線 ( ゲ ー ト 電 極 ) の コ ン タ ク ト 部 の 断 面 構 造 の 一 例 を 示 す 。

[0032]

トランジスタ450は、チャネルエッチ型と呼ばれるボトムゲート型のトランジスタであ

10

20

30

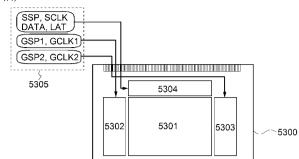

40

り、トランジスタ460は、ボトムコンタクト型(逆コプラナ型とも呼ぶ)と呼ばれるボ トムゲート型のトランジスタである。

## [0033]

画素に配置されるトランジスタ460は、絶縁表面を有する基板400上に、ゲート電極層451a、ゲート絶縁層402、チャネル形成領域を含む酸化物半導体層454、ソース電極層455a、及びドレイン電極層455bを有する。また、トランジスタ460を覆い、酸化物半導体層454の上面及び側面に接する酸化物絶縁層426が設けられている。

# [ 0 0 3 4 ]

また、画素に配置されるトランジスタ460には、シングルゲート構造のトランジスタを 用いる例を説明したが、必要に応じて、チャネル形成領域を複数有するマルチゲート構造 のトランジスタを用いても良い。

## [0035]

なお、酸化物半導体層454は透光性を有し、ソース電極層455aの一部、及びドレイン電極層455bの一部と重なるように形成されている。また、酸化物半導体層454は、透光性を有するゲート絶縁層402を介してゲート電極層451aと重なっている。画素に配置されるトランジスタ460のチャネル形成領域は、酸化物半導体層454のうち、ソース電極層455aの側面と、該側面と向かい合うドレイン電極層455bの側面とで挟まれる領域、即ち、ゲート絶縁層402と接し、且つゲート電極層451aと重なる領域である。

#### [0036]

また、高開口率を有する表示装置を実現するために、トランジスタ460のソース電極層 455a、及びドレイン電極層455bには透光性を有する導電膜を用いる。

#### [ 0 0 3 7 ]

また、トランジスタ460のゲート電極層451aにも透光性を有する導電膜を用いる。

## [0038]

また、駆動回路部に配置されるトランジスタ450は、絶縁表面を有する基板400上に、ゲート電極層421a、ゲート絶縁層402、酸化物半導体層403、ソース電極層425a、及びドレイン電極層425bで構成される。ここで、酸化物半導体層403は、少なくともチャネル形成領域423、高抵抗ソース領域424a、及び高抵抗ドレイン領域424bを有する。また、チャネル形成領域423、ソース電極層425a、及びドレイン電極層425b上には透光性を有する酸化物絶縁層427及び保護絶縁層428が設けられている。

## [ 0 0 3 9 ]

また、酸化物絶縁層426と重なる酸化物半導体層403の第1領域424c、第2領域424dは、チャネル形成領域423と同じ酸素過剰な状態であり、リーク電流の低減や、寄生容量を低減する機能を果たしている。なお、酸化物絶縁層426が酸化物半導体層403と重ならない構成とする場合は、酸化物半導体層403の第1領域424c、第2領域424dは形成されない。

## [0040]

以下、図 1 ( A )、( B )、( C )、( D )、( E )を用い、同一基板上にトランジスタ 4 5 0 及びトランジスタ 4 6 0 を作製する工程を説明する。

## [0041]

まず、絶縁表面を有する基板400上に金属膜を形成した後、第1のフォトリソグラフィ 工程及びエッチング工程により、ゲート電極層421a、421bを形成する。なお、ゲート電極層421bは、ゲート配線に相当するが、便宜上ゲート電極層として表記する。

#### [0042]

なお、フォトリソグラフィエ程に用いるレジストマスクはインクジェット法で形成してもよい。インクジェット法では、フォトマスクを使用しないため、製造コストを低減することができる。

20

10

30

40

20

30

40

50

#### [0043]

ゲート電極層421a、421bに用いる金属膜としては、A1、Cr、Ta、Ti、Mo、Wから選ばれた元素、または上述した元素を成分とする合金か、上述した元素を組み合わせた積層膜等が挙げられる。

## [0044]

基板400には、例えば、アルミノシリケートガラス、アルミノホウケイ酸ガラス、バリウムホウケイ酸ガラスなどを用いることができる。また、後の加熱処理の温度が高い場合には、歪み点が730 以上のものを用いると良い。

## [0045]

なお、ガラス基板に代えて、セラミック基板、石英基板、サファイア基板などの絶縁体からなる基板を用いても良い。

#### [0046]

また、下地膜となる絶縁層を基板 4 0 0 とゲート電極層 4 2 1 a 、 4 2 1 b の間に設けて もよい。下地膜は、基板 4 0 0 からの不純物元素の拡散を防止する機能があり、窒化珪素 膜、酸化珪素膜、窒化酸化珪素膜、又は酸化窒化珪素膜から選ばれた膜の単層構造、また は上記複数の膜の積層構造により形成することができる。

## [0047]

次いで、ゲート電極層421a、421bを覆って透光性を有する導電膜を成膜した後、第2のフォトリソグラフィエ程及びエッチング工程により、ゲート電極層451a、451bを形成する。なお、ゲート電極層451bは、ゲート配線層に相当するが、便宜上ゲート電極層として表記する。

透光性を有する導電膜には、可視光に対して透光性を有する導電材料、例えば In-Sn-O系、In-Sn-Zn-O系、In-Sn-Zn-O系、In-Sn-Zn-O系、In-Sn-Zn-O系、In-Sn-Zn-O系、In-Zn-O系、In-Zn-O系、In-Zn-O系、In-Zn-O系、In-Zn-O系、In-Zn-O系、In-Zn-O系、In-Zn-O系、In-Zn-O系、In-Zn-O系、In-Zn-O系、In-Zn-O系、In-Zn-O系、In-Zn-O系、In-Zn-O系、In-Zn-O系、In-Zn-O系、In-Zn-O系、In-Zn-O系、In-Zn-O系、In-Zn-O系、In-Zn-O系、In-Zn-O系、In-Zn-O系 In-Zn-O系 In-Zn-O In-Zn-O系 In-Zn-O0 I

## [0048]

本実施の形態では、配線抵抗を低減するため、画素部に配置されるゲート配線の一部をゲート電極層 4 2 1 a 、 4 2 1 b と同じ金属膜で形成する。

#### [0049]

次 N で、ゲート電極層 4 2 1 a 、 4 2 1 b 、 4 5 1 a 、 4 5 1 b 上にゲート絶縁層 4 0 2 を形成する。

## [0050]

ゲート絶縁層402には、酸化珪素層、窒化珪素層、酸化窒化珪素層または窒化酸化珪素層等の透光性を有する絶縁膜を用いることができ、プラズマCVD法やスパッタリング法等を用いて形成する。また、ゲート絶縁層402は、上記絶縁膜の単層に限らず、異なる膜の積層でも良い。例えば、成膜ガスとして、シラン(SiH₄)、酸素及び窒素を用いてプラズマCVD法により酸化窒化珪素膜を形成することができる。ゲート絶縁層402の膜厚は、100nm以上500nm以下とし、積層の場合は、例えば、膜厚50nm以上200nm以下の第1のゲート絶縁層を形成し、第1のゲート絶縁層上に膜厚5nm以上300nm以下の第2のゲート絶縁層を形成する。

# [0051]

本実施の形態では、ゲート絶縁層 4 0 2 にプラズマ C V D 法で形成した膜厚 1 0 0 n m の酸化窒化珪素 ( S i O N (組成比 N < O ) )を用いる。

#### [0052]

次いで、ゲート絶縁層402上に、透光性を有する導電膜を形成した後、第3のフォトリソグラフィエ程及びエッチング工程により、ソース電極層455a、及びドレイン電極層455bを形成する(図1(A)参照)。

[ 0 0 5 3 ]

透光性を有する導電膜には、ゲート電極層 4 5 1 a 、 4 5 1 b と同様の材料を用いることができる。

[0054]

次いで、 第 4 のフォトリソグラフィエ程及びエッチング工程により、 ゲート絶縁層 4 0 2 を選択的にエッチングしてゲート電極層 4 2 1 b に達するコンタクトホールを形成する。

次いで、ゲート絶縁層402上に膜厚5nm以上200nm以下、好ましくは10nm以上20nm以下の透光性を有する酸化物半導体膜をスパッタ法で形成する。酸化物半導体膜の形成後に脱水化または脱水素化のための加熱処理を行っても酸化物半導体膜を非晶質な状態とするため、膜厚を50nm以下とすることが好ましい。酸化物半導体膜の膜厚を薄くすることで後に加熱処理した場合に、結晶化してしまうのを抑制することができる。

[0056]

[ 0 0 5 7 ]

また、酸化物半導体膜は、 $InMO_3$ ( $ZnO)_m$ (m>0)で表記される薄膜を用いることができる。ここで、Mは、Ga、Al、Mn およびCoから選ばれた一または複数の金属元素を示す。例えばMとして、Ga、Ga 及びAl、Ga 及びMn、またはGa 及びOochoologe of the constant of

[0058]

本実施の形態では、酸化物半導体膜として、In-Ga-Zn-O系酸化物半導体ターゲットを用いてスパッタ法により膜厚15nmのIn-Ga-Zn-O系非単結晶膜を成膜する。

[0059]

In-Ga-Zn-O系非単結晶膜は、In-Ga-Zn-O系酸化物半導体ターゲット(In<sub>2</sub>O<sub>3</sub>:Ga<sub>2</sub>O<sub>3</sub>:ZnO=1:1:1 [mol数比](すなわち、In:Ga:Zn=1:1:0.5 [atom比]))を用い、基板とターゲットの間との距離を100mm、圧力0.6 Pa、直流(DC)電力0.5 kW、酸素(酸素流量比率100%)雰囲気下で成膜することができる。また、他にも、In:Ga:Zn=1:1:1 [atom比]や、In:Ga:Zn=1:1:2 [atom比]の組成比を有するターゲットを用いてもよい。これらのターゲットの充填率は90%以上100%以下、好ましくは95%以上99.9%以下である。充填率の高い金属酸化物ターゲットを用いることにより、成膜した酸化物半導体膜は緻密な膜となる。

[0060]

スパッタ法にはスパッタ用電源に高周波電源を用いるRFスパッタ法と、DCスパッタ法があり、さらにパルス的にバイアスを与えるパルスDCスパッタ法もある。RFスパッタ法は主に絶縁膜を成膜する場合に用いられ、DCスパッタ法は主に導電膜を成膜する場合に用いられる。

[0061]

なお、成膜中に発生するごみを低減し、膜厚分布の均一性を向上させるためには、パルス 直流(DC)電源を用いてスパッタを行うことが好ましい。

[0062]

10

20

30

また、材料の異なるターゲットを複数設置できる多元スパッタ装置もある。多元スパッタ装置は、同一チャンバーで異なる材料を積層成膜することや、同一チャンバーで複数種類の材料を同時に放電させて成膜することができる。

#### [0063]

また、チャンバー内部に磁石機構を備えたマグネトロンスパッタ法を用いるスパッタ装置や、グロー放電を使わずマイクロ波を用いて発生させたプラズマを用いるECRスパッタ法を用いるスパッタ装置がある。

## [0064]

また、成膜中にターゲット物質とスパッタガス成分とを化学反応させてそれらの化合物薄膜を形成するリアクティブスパッタ法や、成膜中に基板にも電圧をかけるバイアススパッタ法などもある。

#### [0065]

なお、酸化物半導体膜をスパッタ法により成膜する前に、アルゴンガスを導入してプラズマを発生させる逆スパッタを行い、ゲート絶縁層 4 0 2 の表面に付着しているゴミを除去することが好ましい。逆スパッタとは、アルゴン雰囲気下で基板側にRF電源を用いて電圧を印加し、イオン化したアルゴンを基板に衝突させて表面を改質する方法である。なお、アルゴンに代えて窒素、ヘリウム、酸素などを用いてもよい。

#### [0066]

また、酸化物半導体膜の成膜前に、不活性ガス雰囲気(窒素、またはヘリウム、ネオン、アルゴン等)下において加熱処理(400 以上基板の歪み点未満)を行い、ゲート絶縁層402内に含まれる水素及び水などの不純物を除去してもよい。

#### [0067]

次いで、酸化物半導体膜を第5のフォトリソグラフィエ程及びエッチング工程により、島状の酸化物半導体層403、453に加工する(図1(B)参照)。また、島状の酸化物半導体層403、453を形成するためのレジストマスクは、インクジェット法で形成してもよい。インクジェット法を用いることで、製造コストを低減することができる。

#### [0068]

なお、本実施の形態では、ゲート電極層 4 2 1 b に達するコンタクトホールの形成は、酸化物半導体膜の成膜前に第 4 のフォトリソグラフィエ程及びエッチング工程により、ゲート絶縁層を選択的にエッチングして行う。一方で、該コンタクトホールの形成は、上述した島状の酸化物半導体層 4 0 3 、 4 5 3 の形成後に行っても良い。その場合には逆スパッタを行い、酸化物半導体層 4 0 3 、 4 5 3 及びゲート絶縁層 4 0 2 の表面に付着しているレジスト残渣などを除去することが好ましい。

## [0069]

また、ゲート絶縁層上に酸化物半導体膜を成膜した後にゲート電極層421bに達するコンタクトホールを形成し、その後、酸化物半導体膜を選択的にエッチングして島状の酸化物半導体層403、453に加工する工程としてもよい。

## [0070]

次いで、酸化物半導体層 4 0 3 、 4 5 3 の脱水化または脱水素化を行う。脱水化または脱水素化を行う第 1 の加熱処理の温度は、 4 0 0 以上基板の歪み点未満、好ましくは 4 2 5 以上とする。なお、 4 2 5 以上であれば熱処理時間は 1 時間以下でよいが、 4 2 5 以下であれば加熱処理時間は、 1 時間よりも長時間行うこととする。

## [0071]

ここでは、加熱処理装置の一つである電気炉に基板を導入し、酸化物半導体層 4 0 3 、 4 5 3 に対して窒素雰囲気下において加熱処理を行う。本実施の形態では、酸化物半導体層 4 0 3 、 4 5 3 の脱水化または脱水素化を行う加熱温度 T から、再び水が入らないような十分な温度まで同じ炉を用い、具体的には加熱温度 T よりも 1 0 0 以上下がるまで窒素雰囲気下で徐冷する。なお、雰囲気は窒素に限定されず、ヘリウム、ネオン、アルゴン等を用いても良い。

## [0072]

50

10

20

30

20

30

40

50

なお、第1の加熱処理においては、窒素、またはヘリウム、ネオン、アルゴン等の希ガスに、水や水素などが含まれないことが好ましい。ここで、加熱処理装置に導入する窒素、またはヘリウム、ネオン、アルゴン等の希ガスの純度は、6N(99.9999%)以上、好ましくは7N(99.9999%)以上とすることが好ましい。

## [0073]

酸化物半導体層 4 0 3 、 4 5 3 は、第 1 の加熱処理によって結晶化し、微結晶膜または多結晶膜となる場合がある。また、酸化物半導体層 4 0 3 、 4 5 3 は、第 1 の加熱処理によって酸素欠乏型となり、キャリア濃度が 1 × 1 0 <sup>1 8</sup> / c m <sup>3</sup> 以上に高まるため低抵抗化する。

また、ゲート電極層 4 5 1 a、 4 5 1 b も 第 1 の加熱処理によって結晶化し、微結晶膜または多結晶膜となる場合がある。例えば、ゲート電極層 4 5 1 a、 4 5 1 b に酸化インジウム酸化スズ合金膜を用いる場合は、 4 5 0 1 時間の第 1 の加熱処理で容易に結晶化するが、該ゲート電極層 4 5 1 a、 4 5 1 b に酸化珪素を含む酸化インジウム酸化スズ合金膜を用いる場合は、結晶化が起こりにくい。

#### [0074]

また、酸化物半導体層の第1の加熱処理は、島状の酸化物半導体層に加工する前の酸化物 半導体膜に行うこともできる。その場合には、第1の加熱処理後に第5のフォトリソグラ フィエ程を行う。

# [0075]

次いで、ゲート絶縁層402、及び酸化物半導体層403、453上に、スパッタ法で透光性を有する酸化物絶縁層を形成する。そして、第6のフォトリソグラフィエ程によりレジストマスクを形成し、エッチング工程により選択的に酸化物絶縁層426を形成し、その後レジストマスクを除去する。この段階で酸化物半導体層403、453の周縁及び側面は、酸化物絶縁層426と重なる構造となる。また、第6のフォトリソグラフィエ程及びエッチング工程により、ゲート電極層421bに達するコンタクトホールと、ドレイン電極層455bに達するコンタクトホールの形成も行う(図1(C)参照)。

#### [0076]

酸化物絶縁層426は、1nm以上の膜厚とし、上述した酸化物絶縁層に水、水素等の不 純物を混入させない方法を適宜用いて形成することができる。本実施の形態では、スパッ 夕法で成膜した酸化珪素膜で酸化物絶縁層426を形成する。

## [0077]

成膜時の基板温度は、室温以上300 以下とすればよく、本実施の形態では100 とする。酸化珪素膜のスパッタ法による成膜は、希ガス(代表的にはアルゴン)雰囲気下、酸素雰囲気下、または希ガス(代表的にはアルゴン)及び酸素雰囲気下において行うことができる。

## [0078]

また、ターゲットには、酸化珪素ターゲットまたは珪素ターゲットを用いることができる。例えば、珪素ターゲットを用いる場合は、酸素及び希ガス雰囲気下でスパッタを行うことにより酸化珪素を形成することができる。低抵抗化した酸化物半導体層403、453に接して形成する酸化物絶縁層は、水分、水素イオン、またはOH゚などの不純物を極力含まず、これらの外部からの侵入をブロックすることのできる無機絶縁膜を用いると良い。代表的には酸化珪素膜、窒化酸化珪素膜、酸化アルミニウム膜、または酸化窒化アルミニウム膜などを用いることができる。

# [0079]

本実施の形態では、ホウ素を添加した柱状多結晶珪素ターゲット(抵抗率 0 . 0 1 cm、純度 6 N)を用い、基板とターゲットの間との距離(T-S間距離)を 8 9 mm、圧力 0 . 4 Pa、直流(DC)電力 6 k W、酸素(酸素流量比率 1 0 0 %)雰囲気下でパルス D C スパッタ法により成膜する。膜厚は 3 0 0 n m とする。

#### [0080]

次いで、ゲート絶縁層402、酸化物絶縁層426、及び酸化物半導体層403、453

上に金属膜を形成した後、第7のフォトリソグラフィ工程により、レジストマスクを形成し、エッチング工程にてソース電極層425a、及びドレイン電極層425bを形成する。また、ゲート電極層421bに電気的に接続する接続電極層429と、ドレイン電極層455bと電気的に接続する接続電極層452も形成する。

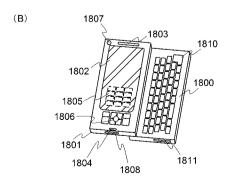

[0081]

該金属膜の成膜方法には、スパッタ法、真空蒸着法(電子ビーム蒸着法など)、アーク放電イオンプレーティング法、またはスプレー法を用いることができる。金属膜としては、Ti、Mo、W、Al、Cr、Cu、Ta、から選ばれた元素、または上述した元素を成分とする合金か、上述した元素を組み合わせた合金等を用いる。また、該金属膜は、上述した元素の単層に限定されず、異なる元素の積層を用いても良い。本実施の形態では、チタン膜(膜厚100nm)の3層構造の金属膜を形成する。また、チタン膜に換えて窒化チタン膜を用いてもよい。

[ 0 0 8 2 ]

また、第7のフォトリソグラフィエ程後のエッチング工程においては、酸化物半導体層403、453上に接する金属膜を選択的に除去する必要がある。この様な場合は、アルカリ性のエッチャント(例えば、アンモニア過水(31重量%過酸化水素水:28重量%アンモニア水:水=5:2:2))などを用いれば、金属膜を選択的に除去し、In-Ga-Zn-O系酸化物半導体からなる酸化物半導体層403、453を残存させることができる。

[0083]

なお、ソース電極層425a、及びドレイン電極層425bを形成するためのレジストマスクをインクジェット法で形成してもよい。インクジェット法を用いることで、製造コストを低減することができる。

[0084]

次いで、酸化物絶縁層426、ソース電極層425a、ドレイン電極層425b、接続電極層429、及び接続電極層452上に透光性を有する酸化物絶縁層427を形成する(図1(D)参照)。酸化物絶縁層427としては、酸化珪素膜、窒化酸化珪素膜、酸化アルミニウム膜、または酸化窒化アルミニウム膜などを用いる。本実施の形態では、スパッタ法で形成した酸化珪素膜を用いて酸化物絶縁層427を形成する。

[0085]

次いで、窒素ガス等の不活性ガス雰囲気下、200 以上400 以下、好ましくは25 0 以上350 以下で第2の加熱処理を行う。例えば、窒素雰囲気下で250 、1時間の加熱処理を行う。

[0086]

第2の加熱処理では、酸化物絶縁層427と酸化物半導体層403の一部、及び酸化物絶縁層426と酸化物半導体層453が接した状態で加熱される。このため、第1の加熱処理で低抵抗化された酸化物半導体層403、453は、酸化物絶縁層427、426から酸素が供給されて酸素過剰な状態となり、高抵抗化(i型化)される。

[0087]

なお、酸化物半導体層 4 0 3 が 1 5 n m 未満の場合、酸化物半導体層 4 0 3 において、金属膜からなるソース電極層 4 2 5 a 及びドレイン電極層 4 2 5 b と重なる領域では、該領域の酸素が該金属膜側に移動しやすくなり、該領域は全て n 型化する。また、酸化物半導体層 4 0 3 の膜厚が 1 5 n m 以上 5 0 n m 以下の場合は、該金属膜と該領域の界面近傍がn 型化するが、その下側はi 型または n 型化した状態となる。

[0088]

なお、本実施の形態では、酸化珪素膜成膜後に第 2 の加熱処理を行ったが、加熱処理のタイミングは酸化珪素膜成膜以降であれば問題なく、酸化珪素膜成膜直後に限定されるものではない。

[0089]

10

20

30

次いで、酸化物絶縁層427上に透光性を有する保護絶縁層428を形成する(図1(E)参照)。保護絶縁層428としては、窒化珪素膜、窒化酸化珪素膜、または窒化アルミニウム膜などを用いる。本実施の形態では、RFスパッタ法を用いて成膜した窒化珪素膜で保護絶縁層428を形成する。

[0090]

また、図示はしないが、画素部において酸化物絶縁層427と保護絶縁層428の間に透光性を有する平坦化絶縁層を設けても良い。平坦化絶縁層としては、アクリル系樹脂、ポリイミド、ベンゾシクロブテン系樹脂、ポリアミド、またはエポキシ系樹脂等の耐熱性を有する有機材料を用いることができる。また、上記有機材料の他に、低誘電率材料(1ow・k 材料)、シロキサン系樹脂、PSG(リンガラス)、BPSG(リンボロンガラス)等を用いることができる。なお、これらの材料で形成される絶縁層を複数積層させてもよい。

[0091]

以上の工程により、同一基板上にチャネルエッチ型のトランジスタ450、及びボトムコンタクト型のトランジスタ460を作製することができる。なお、ボトムコンタクト型のトランジスタ460は、接続電極層452以外は、透光性を有する材料で構成されているため、開口率を向上させることができる。

[0092]

トランジスタ450の様なチャネルエッチ型は、チャネル長を短く形成しやすく、駆動回路の様な高速動作を必要とするトランジスタの形成に有利である。すなわち、同一基板上に形成する複数の回路の全てをトランジスタ460の様なボトムコンタクト型で形成するよりも高速動作が可能な表示装置を作製することができる。

[0093]

また、表示装置に必要な画素電極は画素部の保護絶縁層428上に設け、トランジスタ460のドレイン電極層と電気的に接続させる。ここでは、接続電極層452と接続させれば良い。なお、画素電極には、ゲート電極層451a、451b、ソース電極層455a、及びドレイン電極層455bと同様の透光性を有する導電膜を用いることができる。

[0094]

本発明の一態様は、同一基板上に駆動回路と画素回路を有した表示装置において、該回路が必要とする電気特性を得やすい様に該回路のそれぞれを構造の異なるトランジスタで形成するものであり、本実施の形態の様に、駆動回路にチャネルエッチ型のトランジスタ450、画素回路にボトムコンタクト型のトランジスタ460を用いることによって表示特性の優れた表示装置を作製することができる。

[0095]

なお、本実施の形態は他の実施の形態と自由に組み合わせることができる。

[0096]

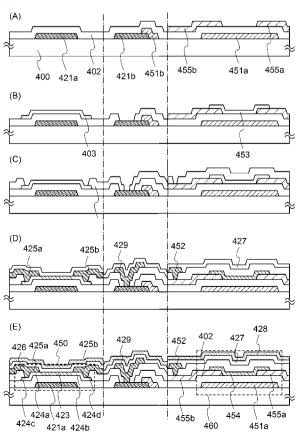

(実施の形態2)

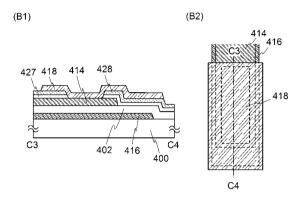

本実施の形態では、トランジスタの作製工程の一部が実施の形態 1 と異なる例を図 2 に示す。図 2 は、図 1 と工程が一部異なる点以外は同じであるため、同じ箇所には同じ符号を用い、同じ箇所の詳細な説明は省略する。

[0097]

まず、実施の形態1に従って、基板上にゲート電極層421a、451a、及びゲート絶縁層402を形成し、ゲート絶縁層402を介してゲート電極層451aと一部が重なるソース電極層455a及びドレイン電極層455bを形成する。そして、ゲート絶縁層402、ソース電極層455a、及びドレイン電極層455b上に酸化物半導体膜の成膜を行う。

[0098]

次いで、酸化物半導体膜の脱水化または脱水素化を行う。脱水化または脱水素化を行う第 1の加熱処理の温度は、400 以上基板の歪み点未満、好ましくは425 以上とする。なお、425 以上であれば熱処理時間は1時間以下でよいが、425 未満であれば 10

20

30

40

加熱処理時間は、1時間よりも長時間行うこととする。ここでは、加熱処理装置の一つである電気炉に基板を導入し、酸化物半導体膜に対して窒素雰囲気下において加熱処理を行った後、大気に触れることなく、酸化物半導体膜への水や水素の再混入を防ぐ。その後、同じ炉に高純度の酸素ガス、高純度の $N_2$  Oガス、又は超乾燥エア(露点が - 4 0 以下、好ましくは - 6 0 以下)を導入して冷却を行う。酸素ガスまたは $N_2$  Oガスに、水、水素などが含まれないことが好ましい。または、加熱処理装置に導入する酸素ガスまたは $N_2$  Oガスの純度を、6 N (9 9 . 9 9 9 9 %)以上、好ましくは 7 N (9 9 . 9 9 9 9 %)以上、好ましくは 7 N (9 9 . 9 9 9 9 %)以上、(即ち酸素ガスまたは $N_2$  Oガス中の不純物濃度を 1 N P P M 以下、好ましくは 0 . 1 N P P M 以下)とすることが好ましい。

## [0099]

また、脱水化または脱水素化を行う第1の加熱処理後に200 以上400 以下、好ましくは200 以上300 以下の温度で酸素ガスまたはN<sub>2</sub>〇ガス雰囲気下での加熱処理を行ってもよい。

## [0100]

以上の工程を経ることによって酸化物半導体膜全体は酸素過剰な状態となり、酸化物半導体膜を高抵抗化、即ちi型化させることができる。なお、本実施の形態では、酸化物半導体膜成膜直後に第1の加熱処理を行う例を示したが、第1の加熱処理は、酸化物半導体膜成膜以降の工程であれば特に限定されない。

## [0101]

次いで、フォトリソグラフィ工程によりレジストマスクを形成し、エッチング工程にて酸化物半導体膜及びゲート絶縁層402を選択的にエッチングして、ゲート電極層421bに達するコンタクトホールを形成する。その後、レジストマスクを除去する(図2(A)参照)。

#### [ 0 1 0 2 ]

次いで、フォトリソグラフィ工程によりレジストマスクを形成し、エッチング工程にて酸化物半導体膜を選択的にエッチングして島状に加工する。そして、レジストマスクを除去し、ゲート絶縁層402上に酸化物半導体層404、405を形成する(図2(B)参照)。

## [0103]

次いで、ゲート絶縁層402、及び酸化物半導体層404、405上にスパッタ法で酸化物絶縁層を形成した後、フォトリソグラフィエ程によりレジストマスクを形成する。そして、エッチング工程にて酸化物絶縁層426を形成し、レジストマスクを除去する。この段階で、酸化物半導体層404、405と酸化物絶縁層426が重なる領域が形成される。また、この工程によりゲート電極層421bに達するコンタクトホールの形成と、ドレイン電極層455bに達するコンタクトホールの形成も行う(図2(C)参照)。

#### [0104]

酸化物絶縁層には、水分、水素イオン、OH^などの不純物を極力含まず、これらが外部から侵入することをブロックする無機絶縁膜を用いると良い。代表的には酸化珪素膜、窒化酸化珪素膜、酸化アルミニウム膜、または酸化窒化アルミニウム膜などを用いることができる。

# [ 0 1 0 5 ]

次いで、ゲート絶縁層402、酸化物絶縁層426、及び酸化物半導体層404、405上に酸化物導電膜と金属膜の積層を形成する。スパッタ法を用いれば、酸化物導電膜と金属膜の積層を大気に触れることなく連続的に成膜することができる。

#### [0106]

酸化物導電膜としては、酸化亜鉛を成分として含むものが好ましく、酸化インジウムを含まないものであることが好ましい。そのような酸化物導電膜として、酸化亜鉛、酸化亜鉛アルミニウム、酸窒化亜鉛アルミニウム、酸化亜鉛ガリウムなどが挙げられる。本実施の形態では酸化亜鉛膜を用いる。

## [0107]

50

10

20

30

また、金属膜としては、Ti、Mo、W、A1、Cr、Cu、Ta、から選ばれた元素、または上述した元素を成分とする合金か、上述した元素を組み合わせた合金等を用いることができる。また、該金属膜は、上述した元素の単層に限定されず、異なる元素の積層でも良い。本実施の形態では、モリブデン膜、アルミニウム膜、及びモリブデン膜を積層した三層積層膜を用いる。

[0108]

次いで、フォトリソグラフィエ程により、レジストマスクを形成し、エッチング工程にて金属膜を選択的にエッチングしてソース電極層445a、ドレイン電極層445b、接続電極層449、及び接続電極層442を形成した後、レジストマスクを除去する。

[0109]

なお、レジストマスクを除去するために用いられるレジスト剥離液はアルカリ性溶液であり、レジスト剥離液を用いる場合は、上記電極層をマスクとして酸化亜鉛膜も選択的にエッチングされる。従って、ソース電極層 4 4 5 a に接する酸化物導電層 4 4 6 a、ドレイン電極層 4 4 5 b に接する酸化物導電層 4 4 6 b が形成される。

[0110]

なお、酸化物半導体層と酸化物導電層はエッチング速度に差があるため、酸化物半導体層 上に接する酸化物導電層は、時間制御で除去することができる。

[0111]

また、金属膜を選択的にエッチングした後、酸素アッシング処理でレジストマスクを除去した後、ソース電極層445a、ドレイン電極層445b、接続電極層449、及び接続電極層442をマスクとして酸化亜鉛膜を選択的にエッチングしてもよい。

[0112]

ソース電極層445aと酸化物半導体層404との間に設けられる酸化物導電層446aはソース領域として機能し、ドレイン電極層445bと酸化物半導体層404との間に設けられる酸化物導電層446bはドレイン領域として機能する。酸化物導電層446a及び酸化物導電層446bを設けることによって、酸化物半導体層404とソース電極層445a及びドレイン電極層445bとの接触抵抗を下げることができる。この様に、電流経路の低抵抗化が図られたトランジスタは高速動作が可能となり、周辺回路(駆動回路)の周波数特性を向上させることができる。

[0113]

モリブデンは、酸化物半導体との接触抵抗が比較的高い材料である。モリブデンは、チタンに比べて酸化しにくいため、酸化物半導体層から酸素を引き抜く作用が弱く、酸化物半導体層の接触界面がn型化しないためである。この様な場合において、酸化物半導体層と金属電極層との間に酸化物導電層を介在させることは、接触抵抗を低減させるための大変有効な手段となる。

[0114]

また、同じ工程で接続電極層449に接する酸化物導電層448が形成され、接続電極層442に接する酸化物導電層447が形成される(図2(D)参照)。

[0115]

次いで、トランジスタの電気的特性のばらつきを軽減するため、不活性ガス雰囲気下、例えば窒素ガス雰囲気下で第2の加熱処理を行ってもよい。第2の加熱処理は、150以上350未満で行うことが好ましく、例えば、窒素雰囲気下で250、1時間の加熱処理を行う。

[0116]

なお、第2の加熱処理により、酸化物半導体層404,454中に酸素の含侵または拡散が行われる。酸化物半導体層404,454中への酸素の含侵または拡散によりチャネル形成領域を高抵抗化(i型化)を図ることができる。それにより、電気特性がノーマリーオフとなるトランジスタを得ることができる。また、第2の加熱処理により、酸化物導電層446a、446b、447、448を結晶化させ、導電性を向上させることもできる

10

20

30

50

#### [0117]

次いで、酸化物絶縁層426、ソース電極層445a、ドレイン電極層445b上に酸化物絶縁層427、保護絶縁層428を形成する(図2(E)参照)。酸化物絶縁層427、保護絶縁層428は、実施の形態1と同様の材料及び作製方法で形成することができる

#### [ 0 1 1 8 ]

以上の工程により、同一基板上にトランジスタ440と、トランジスタ460を作製することができる。

## [0119]

駆動回路部に配置されるトランジスタ440は、絶縁表面を有する基板400上に、ゲート電極層421a、ゲート絶縁層402、酸化物半導体層404、酸化物導電層446a、446b、ソース電極層445a、及びドレイン電極層445bで構成される。ここで、酸化物半導体層404は、少なくともチャネル形成領域443、高抵抗ソース領域444a、及び高抵抗ドレイン領域444bを有する。また、チャネル形成領域443、ソース電極層445a、及びドレイン電極層445b上には酸化物絶縁層427及び保護絶縁層428が設けられる。

## [0120]

高抵抗ソース領域444aとソース電極層445aとの間にはソース領域として機能する酸化物導電層446aが設けられ、高抵抗ドレイン領域444bとドレイン電極層445bとの間にはドレイン領域として機能する酸化物導電層446bが設けられ、接触抵抗の低減を図っている。

#### [0121]

また、酸化物絶縁層426と重なる酸化物半導体層404の第1領域444c、第2領域4444 d は、チャネル形成領域443と同じ酸素過剰な状態であり、リーク電流の低減や、寄生容量を低減する機能も果たしている。なお、酸化物絶縁層426が酸化物半導体層404と重ならない構成とする場合は、酸化物半導体層404の第1領域444 c、第2領域4444 d は形成されない。

#### [0122]

なお、本実施の形態は他の実施の形態と自由に組み合わせることができる。

# [0123]

(実施の形態3)

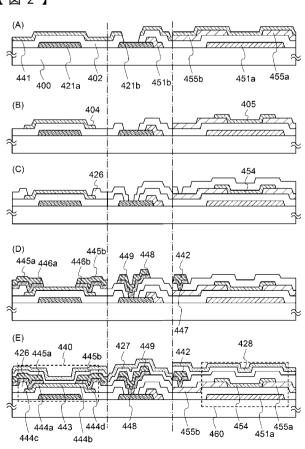

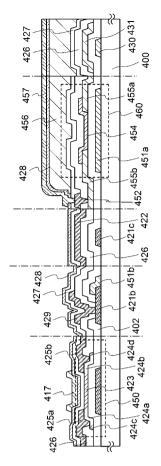

本実施の形態では、実施の形態1または2に示したアクティブマトリクス基板を用いて、液晶表示装置を構成する一例を示す。

## [0124]

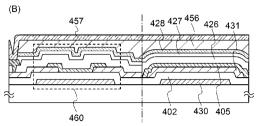

アクティブマトリクス基板の断面構造の一例を図3に示す。

#### [0125]

実施の形態 1 及び 2 では、同一基板上に駆動回路部のトランジスタ、画素部のトランジスタ及びゲート配線(ゲート電極)コンタクト部を図示したが、本実施の形態では、それらに加え、保持容量、ゲート配線とソース配線の交差部も図示して説明する。

## [0126]

容量、ゲート配線、ソース配線は、実施の形態1または2に示す作製工程と同じ工程で形成することができ、フォトマスク枚数の増加や、工程数の増加することなく作製することができる。また、画素部の表示領域となる部分においては、ゲート配線、ソース配線、及び容量配線層が透光性を有する導電膜で形成されており、高い開口率を実現している。また、表示領域でない部分のソース配線層は、配線抵抗を低減するために金属配線を用いることができる。

#### [0127]

図 3 において、トランジスタ 4 5 0 は、駆動回路部に設けられるトランジスタであり、画素電極層 4 5 7 と電気的に接続するトランジスタ 4 6 0 は、画素部に設けられるトランジスタである。

10

20

30

40

20

30

40

50

[0128]

基板 4 0 0 上方に形成されるトランジスタ 4 6 0 として、本実施の形態では、実施の形態 1 または 2 のトランジスタ 4 6 0 と同じ構造を用いる。

[0129]

トランジスタ460のゲート電極層451aと同じ透光性を有する材料、及び同じ工程で形成される容量配線層430は、誘電体となるゲート絶縁層402を介して容量電極431と重なり、保持容量を形成する。なお、容量電極431は、トランジスタ460のソース電極層455aまたはドレイン電極層455bと同じ透光性を有する材料、及び同じ工程で形成される。従って、トランジスタ460が透光性を有していることに加え、保持容量も透光性を有するため、開口率を向上させることができる。

[0130]

保持容量が透光性を有することは、開口率を向上させる上で重要である。特に10インチ以下の小型の液晶表示パネルにおいて、画素寸法を微細化しても、高い開口率を実現することができる。また、トランジスタ460及び保持容量の構成部材に透光性を有する膜を用いることで、広視野角を実現するため、1画素を複数のサブピクセルに分割しても高い開口率を実現することができる。例えば、一つの画素内に2~4個のサブピクセル及び保持容量を有する場合においても、トランジスタが透光性を有していることに加え、それぞれの保持容量も透光性を有するため、開口率を向上させることができる。

[0131]

なお、保持容量は、画素電極層 4 5 7 の下方に設けられ、容量電極 4 3 1 は画素電極層 4 5 7 と電気的に接続される。

[ 0 1 3 2 ]

本実施の形態では、容量配線層430、ゲート絶縁層402、及び容量電極431を用いて保持容量を形成する例を示したが、保持容量を形成する構造については特に限定されない。例えば、容量配線層を設けず、隣り合う画素のゲート配線の一部を容量配線層としても良い。また、ゲート絶縁層の他に保護絶縁層や平坦化絶縁層などの画素部の構成に用いられる絶縁層を誘電体として用いても良い。

[ 0 1 3 3 ]

また、ゲート配線層、ソース配線層、及び容量配線層は画素密度に応じて複数本設けられるものである。また、端子部においては、ゲート配線と同電位の第1の端子電極、ソース配線と同電位の第2の端子電極、容量配線層と同電位の第3の端子電極などが複数並べられて配置される。それぞれの端子電極の数は、それぞれ任意な数で設ければ良いものとし、実施者が適宣決定すれば良い。

[0134]

ゲート配線コンタクト部において、ゲート電極層421bは、低抵抗の金属材料で形成することができる。ゲート電極層421bは、ゲート配線に達するコンタクトホールを介して接続電極層429と電気的に接続される。

[0135]

駆動回路のトランジスタ 4 5 0 のゲート電極層は、酸化物半導体層の上方に設けられた導電層 4 1 7 と電気的に接続させる構造としてもよい。

[ 0 1 3 6 ]

また、配線交差部において、図3に示すように寄生容量を低減するため、ゲート配線層421cとソース配線層422との間には、ゲート絶縁層402及び酸化物絶縁層426を積層する構成としている。なお、図3ではゲート配線層421cを金属膜とする例を示したが、トランジスタ460のゲート電極層451aと同じ透光性を有する導電膜を用いて形成することもできる。

[0137]

また、アクティブマトリクス型の液晶表示装置を作製する場合には、アクティブマトリクス基板と、対向電極が設けられた対向基板との間に液晶層を設け、アクティブマトリクス 基板と対向基板とを固定する。なお、対向基板に設けられた対向電極と電気的に接続する 共通電極をアクティブマトリクス基板上に設け、共通電極と電気的に接続する第4の端子電極を端子部に設ける。この第4の端子電極は、共通電極を固定電位、例えばGND、0Vなどに設定するための端子である。第4の端子電極は、画素電極層457と同じ透光性を有する材料で形成することができる。

[0138]

また、ゲート電極、ソース電極、ドレイン電極、画素電極、その他の電極、及び各種配線層に同じ材料を用いれば、スパッタターゲットや製造装置を共通とすることができる。また、その材料コスト及びエッチング時に使用するエッチャントやエッチングガスに要するコストを低減することができ、結果として製造コストを削減することができる。

[0139]

また、図3の構造において、平坦化絶縁層456として感光性の樹脂材料を用いる場合、 レジストマスクを形成する工程を省略することができる。

[0140]

なお、本実施の形態は他の実施の形態と自由に組み合わせることができる。

[0141]

(実施の形態4)

また、本実施の形態では、トランジスタと同一基板上に設けられる端子部の構成の一例を図4を用いて説明する。なお、図4において、図3と同じ箇所には同じ符号を用いて説明する。

[0142]

図4(A1)、図4(A2)は、ゲート配線端子部の断面図及び上面図をそれぞれ図示している。図4(A1)は図4(A2)中のC1-C2線に沿った断面図に相当する。

[0143]

図4(A1)において、酸化物絶縁層427と保護絶縁層428の積層上に形成される導電層415は、入力端子として機能する接続用の端子電極である。また、図4(A1)において、端子部では、ゲート配線層421cと同じ材料で形成される第1の端子411と、ソース配線層422と同じ材料で形成される接続電極層412とがゲート絶縁層402を介して重なり、導電層415で導通させている。導電層415は、画素電極層457と同じ透光性を有する材料、同じ工程で形成することができる。

[0144]

また、図4(B1)、及び図4(B2)は、ソース配線端子部の断面図及び上面図をそれぞれ図示している。また、図4(B1)は、図4(B2)中のC3-C4線に沿った断面図に相当する。

[0145]

図4(B1)において、酸化物絶縁層427と保護絶縁層428の積層上に形成される導電層418は、入力端子として機能する接続用の端子電極である。また、図4(B1)において、端子部では、ゲート配線層421cと同じ材料で形成される電極層416が、ソース配線と電気的に接続される第2の端子414の下方にゲート絶縁層402を介して重なる。電極層416は第2の端子414とは電気的に接続しておらず、電極層416を第2の端子414と異なる電位、例えばフローティング、GND、0Vなどに設定すれば、ノイズ対策のための容量、または静電気対策のための容量とすることができる。また、第2の端子414は、導電層418と電気的に接続している。導電層418は、画素電極層457と同じ透光性を有する材料、同じ工程で形成することができる。

[0146]

ゲート配線、ソース配線、共通電位線、及び電源供給線は画素密度に応じて複数本設けられるものである。また、端子部においては、ゲート配線と同電位の第1の端子、ソース配線と同電位の第2の端子、電源供給線と同電位の第3の端子、共通電位線と同電位の第4の端子などが複数並べられて配置される。それぞれの端子の数は、それぞれ任意な数で設ければ良いものとし、実施者が適宣決定すれば良い。

[0147]

10

20

30

40

20

30

40

50

なお、本実施の形態は他の実施の形態と自由に組み合わせることができる。

## [0148]

(実施の形態5)

本実施の形態では、液晶表示装置の構成及び作製方法の一例について説明する。

#### [0149]

本実施の形態においては、液晶素子(液晶表示素子ともいう)を含む表示装置について説明するが、これに限らず電子インクなど、電気的作用によりコントラストが変化する表示 媒体も適用することができる。

## [0150]

なお、本明細書中における表示装置には、表示素子が封止された状態にあるパネルと、該パネルを動作させるためのIC(集積回路)等が含まれる。また、該表示素子が形成されている素子基板には、電流を表示素子に供給するための手段が各画素に備えられている。また、コネクター、例えばFPC(Flexible printed circuit)もしくはTAB(Tape Automated Bonding)テープもしくはTCP(Tape Carrier Package)が取り付けられたモジュール、TABテープやTCPの先にプリント配線板が設けられたモジュール、または表示素子にCOG(Chip On Glass)方式によりICが直接実装されたモジュールも全て表示装置に含むものとする。

## [0151]

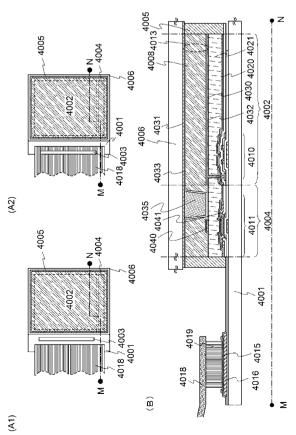

表示装置の一形態に相当する液晶表示パネルの外観及び断面について、図5を用いて説明する。図5(A1)、(A2)は、トランジスタ4010、4011、及び液晶素子4013を第1の基板4001と第2の基板4006との間にシール材4005によって封止したパネルの平面図である。また、図5(B)は、図5(A1)、(A2)のM-Nにおける断面図に相当する。

# [0152]

第1の基板4001上に設けられた画素部4002と、走査線駆動回路4004とを囲むようにして、シール材4005が設けられている。また画素部4002と、走査線駆動回路4004の上に第2の基板4006が設けられている。よって、画素部4002と、走査線駆動回路4004とは、第1の基板4001とシール材4005と第2の基板4006とによって、液晶層4008と共に封止されている。また、第1の基板4001上のシール材4005によって囲まれている領域とは異なる領域に、別途用意された基板上に単結晶半導体膜または多結晶半導体膜で形成された信号線駆動回路4003が実装されている。

## [0153]

なお、別途形成した駆動回路の接続方法は、特に限定されるものではなく、COG法、ワイヤボンディング法、或いはTAB法などを用いることができる。図5(A1)は、COG法により信号線駆動回路4003を実装する例であり、図5(A2)は、TAB法により信号線駆動回路4003を実装する例である。

## [0154]

また、第1の基板4001上に設けられた画素部4002と走査線駆動回路4004は、トランジスタを複数有している。図5(B)では、画素部4002に含まれるトランジスタ4010と、走査線駆動回路4004に含まれるトランジスタ4011とを例示している。トランジスタ4010、4011上には絶縁層4041、4020、4021が設けられている。

#### [ 0 1 5 5 ]

トランジスタ4010、4011には、実施の形態1または2で示した酸化物半導体層を含む信頼性の高いトランジスタを適用することができる。駆動回路用のトランジスタ4011としては、実施の形態1または2で示したトランジスタ450、画素用のトランジスタ4010としては、実施の形態1または2で示したトランジスタ460を用いることができる。本実施の形態において、トランジスタ4010、4011はnチャネル型トラン

ジスタである。

## [0156]

絶縁層4021上において、駆動回路用のトランジスタ4011の酸化物半導体層のチャネル形成領域と重なる位置に導電層4040が設けられている。導電層4040を酸化物半導体層のチャネル形成領域と重なる位置に設けることによって、トランジスタ4011のしきい値電圧の変化量を低減することができる。また、導電層4040は、電位がトランジスタ4011のゲート電極と同じでもよいし、異なっていても良く、第2のゲート電極として機能させることもできる。また、導電層4040の電位はGND、0V、或いはフローティング状態であってもよい。

## [0157]

また、液晶素子4013が有する画素電極4030は、トランジスタ4010と電気的に接続されている。そして液晶素子4013の対向電極4031は、第2の基板4006上に形成されている。画素電極4030と対向電極4031と液晶層4008とが重なっている部分が、液晶素子4013に相当する。なお、画素電極4030、対向電極4031には、それぞれ配向膜として機能する絶縁層4032、4033が設けられている。

#### [0158]

なお、第1の基板4001、第2の基板4006としては、透光性基板を用いることができ、ガラス、セラミックス、プラスチックを用いることができる。プラスチックとしては、FRP(Fiberglass-Reinforced Plastics)板、PVF(ポリビニルフルオライド)フィルム、ポリエステルフィルムまたはアクリル樹脂フィルムを用いることができる。

#### [0159]

また、4035は、絶縁層を選択的にエッチングすることで得られる柱状のスペーサであり、画素電極4030と対向電極4031との間の距離(セルギャップ)を制御するために設けられている。なお、球状のスペーサを用いても良い。

## [0160]

また、対向電極 4 0 3 1 は、トランジスタ 4 0 1 0 と同一基板上に設けられる共通電位線と電気的に接続される。共通接続部を用いて、一対の基板間に配置される導電性粒子を介して対向電極 4 0 3 1 と共通電位線を電気的に接続することができる。なお、導電性粒子はシール材 4 0 0 5 に含有させる。

## [0161]

また、配向膜を用いないブルー相を示す液晶を用いてもよい。ブルー相は液晶相の一つであり、コレステリック液晶を昇温していくと、コレステリック相から等方相へ転移する直前に発現する相である。ブルー相は狭い温度範囲でしか発現しないため、液晶層 4 0 0 8 に用いる場合は、温度範囲を改善するために 5 重量%以上のカイラル剤を混合させた液晶組成物とすることが好ましい。ブルー相を示す液晶とカイラル剤とを含む液晶組成物は、応答速度が 1 m s e c 以下と短く、光学的等方性であるため配向処理が不要であり、視野角依存性が小さい特徴を有する。

## [0162]

トランジスタ4011では、酸化物半導体層に接して絶縁層4041が形成されている。 絶縁層4041は、実施の形態1で示した酸化物絶縁層427と同様な材料及び方法で形成することができ、ここでは、スパッタ法で形成した酸化珪素膜を用いる。

## [0163]

また、絶縁層4041上に保護絶縁層4020を形成する。保護絶縁層4020は、実施の形態1で示した保護絶縁層428と同様な材料及び方法で形成すればよい。ここでは、保護絶縁層4020として、プラズマCVD法で形成した窒化珪素膜を用いる。

#### [0164]

また、平坦化絶縁層として絶縁層4021を形成する。絶縁層4021としては、アクリル系樹脂、ポリイミド、ベンゾシクロブテン系樹脂、ポリアミド、エポキシ系樹脂等の耐熱性を有する有機材料を用いることができる。また上記有機材料の他に、低誘電率材料(

10

20

30

40

20

30

40

50

1 ow - k材料)、シロキサン系樹脂、 P S G (リンガラス)、 B P S G (リンボロンガラス)等を用いることができる。なお、これらの材料で形成される絶縁層を複数積層させることで、絶縁層 4 0 2 1 を形成してもよい。

#### [ 0 1 6 5 ]

なおシロキサン系樹脂とは、シロキサン系材料を出発材料として形成されたSi-O-S i 結合を含む樹脂に相当する。シロキサン系樹脂の置換基としては、有機基(例えばアル キル基やアリール基)やフルオロ基を用いても良い。また、有機基はフルオロ基を有して いても良い。

## [0166]

絶縁層4021の形成法は、特に限定されず、その材料に応じて、スパッタ、SOG、スピンコート、ディップ、スプレー塗布、インクジェット、スクリーン印刷、オフセット印刷等を用いることができ、また、ドクターナイフ、ロールコーター、カーテンコーター、ナイフコーター等を用いて形成することができる。絶縁層4021の焼成工程と半導体層のアニールを兼ねることで工程を削減することが可能となる。

#### [0167]

画素電極 4 0 3 0 、対向電極 4 0 3 1 は、酸化タングステンを含むインジウム酸化物、酸化タングステンを含むインジウム亜鉛酸化物、酸化チタンを含むインジウム酸化物、酸化チタンを含むインジウム錫酸化物、インジウム錫酸化物(以下、ITOと示す)、インジウム亜鉛酸化物、酸化ケイ素を添加したインジウム錫酸化物などの透光性を有する導電性材料を用いることができる。

#### [0168]

また、画素電極 4 0 3 0、対向電極 4 0 3 1 として、導電性高分子(導電性ポリマーともいう)を含む導電性組成物を用いて形成することができる。導電性組成物を用いて形成した画素電極は、シート抵抗が 1 0 0 0 0 0 / 以下、波長 5 5 0 n m における光の透過率が 7 0 %以上であることが好ましい。また、導電性組成物に含まれる導電性高分子の抵抗率が 0 . 1 ・ c m 以下であることが好ましい。

## [0169]

導電性高分子としては、いわゆる 電子共役系導電性高分子を用いることができる。例えば、ポリアニリンまたはその誘導体、ポリピロールまたはその誘導体、ポリチオフェンまたはその誘導体、若しくはこれらの 2 種以上の共重合体などがあげられる。

#### [ 0 1 7 0 ]

また、別途形成された信号線駆動回路4003と、走査線駆動回路4004または画素部4002に与えられる各種信号及び電位は、FPC4018を通じて供給されている。

#### [0171]

接続端子電極4015は、画素電極4030と同じ導電膜で形成され、端子電極4016は、トランジスタ4011のソース電極層及びドレイン電極層と同じ導電膜で形成されている。

## [0172]

接続端子電極 4 0 1 5 は、異方性導電膜 4 0 1 9 を介して F P C 4 0 1 8 が有する端子と電気的に接続されている。

# [ 0 1 7 3 ]

また、図 5 においては、信号線駆動回路 4 0 0 3 を別途形成し、第 1 の基板 4 0 0 1 に実装している例を示しているがこの構成に限定されない。走査線駆動回路を別途形成して実装しても良いし、信号線駆動回路の一部または走査線駆動回路の一部のみを別途形成して実装しても良い。

# [0174]

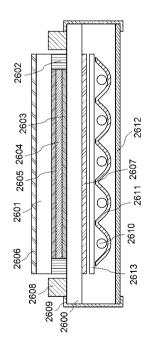

図 6 は、本明細書に開示する作製方法により作製されるトランジスタ基板 2 6 0 0 を用いた表示装置として、液晶表示モジュールを構成する一例を示している。

#### [ 0 1 7 5 ]

トランジスタ基板 2 6 0 0 と対向基板 2 6 0 1 がシール材 2 6 0 2 により固着され、その

20

30

40

50

間にトランジスタ等を含む画素部2603、液晶層を含む表示素子2604、着色層26 05が設けられ表示領域を形成している。

## [0176]

着色層2605は、カラー表示を行う場合に必要であり、RGB方式の場合は、赤、緑、青の各色に対応した着色層が各画素に対応して設けられている。トランジスタ基板2600と対向基板2601の外側には偏光板2606、2607、拡散板2613が配設されている。

## [0177]

光源は冷陰極管2610と反射板2611により構成される。回路基板2612には、コントロール回路や電源回路などの外部回路が組みこまれており、フレキシブル配線基板2609を介してトランジスタ基板2600配線回路部2608と接続される。また偏光板と液晶層との間に位相差板を設けてもよい。

#### [0178]

液晶表示モジュールには、TN(Twisted Nematic)モード、IPS(In-Plane‐Switching)モード、FFS(Fringe Field Switching)モード、MVA(Multi‐domain Vertical Alignment)モード、PVA(Patterned Vertical Alignment)モード、ASM(Axially Symmetric aligned Micro‐cell)モード、OCB(Optical Соmpensated Birefringence)モード、FLC(Ferroelectric Liuuid Crystal)モード、AFLC(AntiFerroelectric Liuuid Сrystal)モードなどを用いることができる。

## [0179]

以上の工程により、表示装置として信頼性の高い液晶表示パネルを作製することができる

## [0180]

なお、本実施の形態は他の実施の形態と自由に組み合わせることができる。

#### [0181]

## (実施の形態6)

本実施の形態では、同一基板上に作製したトランジスタで構成された駆動回路及び画素部を動作させる例について説明する。

## [0182]

本実施の形態では、実施の形態1に従ったトランジスタの作製方法を用いて、同一基板上に画素部及び駆動回路部を形成する。なお、実施の形態1に示すトランジスタは、nチャネル型トランジスタであり、該駆動回路部は、nチャネル型トランジスタのみで構成することができる一部の回路に限られる。

# [0183]

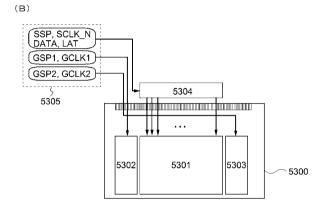

アクティブマトリクス型表示装置のブロック図の一例を図7(A)に示す。表示装置の基板5300上には、画素部5301、第1の走査線駆動回路5302、第2の走査線駆動回路5303、及び信号線駆動回路5304が配置されている。画素部5301には、複数の信号線が信号線駆動回路5304から延伸して配置され、複数の走査線が第1の走査線駆動回路5302、及び第2の走査線駆動回路5303から延伸して配置されている。なお走査線と信号線との交差領域には、各々、表示素子を有する画素がマトリクス状に配置されている。また、表示装置の基板5300は、FPC(F1exib1e Printed Circuit)等の接続部を介して、タイミング制御回路5305(コントローラ、制御ICともいう)に接続されている。

## [0184]

図7(A)に示す第1の走査線駆動回路5302、第2の走査線駆動回路5303、及び信号線駆動回路5304は、画素部5301と同じ基板5300上に形成される。そのため、外部に設ける駆動回路等の部品の数が減るので、コストの低減を図ることができる。

20

30

40

50

また、基板 5 3 0 0 と外部の駆動回路との接続部(FPC等)を減らすことができるため、信頼性や歩留まりの向上を図ることができる。

## [0185]

なお、タイミング制御回路5305は、第1の走査線駆動回路5302に対して、第1の 走査線駆動回路用スタート信号(GSP1)、走査線駆動回路用クロック信号(GCLK 1)等を供給する。また、第2の走査線駆動回路5303に対しては、第2の走査線駆動 回路用スタート信号(GSP2)(スタートパルスともいう)、走査線駆動回路用クロック信号(GCLK2)等を供給する。

## [0186]

また、信号線駆動回路 5 3 0 4 に対しては、信号線駆動回路用スタート信号(SSP)、信号線駆動回路用クロック信号(SCLK)、ビデオ信号用データ(DATA)(単にビデオ信号ともいう)、ラッチ信号(LAT)等を供給するものとする。なお各クロック信号は、周期のずれた複数のクロック信号でもよいし、クロック信号を反転させた信号(CKB)とともに供給されるものであってもよい。なお、第 1 の走査線駆動回路 5 3 0 2、または第 2 の走査線駆動回路 5 3 0 3 の一方は省略することが可能である。

## [ 0 1 8 7 ]

図7(B)では、駆動周波数が低い回路(例えば、第1の走査線駆動回路5302、第2の走査線駆動回路53030を画素部5301と同じ基板5300に形成し、信号線駆動回路5304を画素部5301とは別の基板に形成する構成について示している。当該構成により、電界効果移動度が比較的小さいトランジスタを用いても、画素部と同一基板上に駆動回路の一部を構成することができる。従って、コストの低減や歩留まりの向上などを図ることができる。

## [0188]

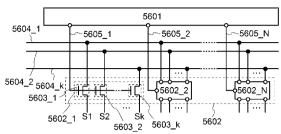

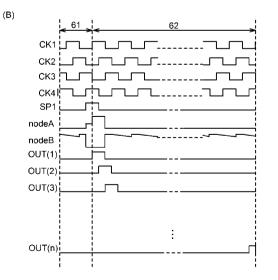

次に、nチャネル型トランジスタで構成する信号線駆動回路の構成及び動作の一例について、図8(A)、図8(B)を用いて説明する。

## [0189]

信号線駆動回路は、シフトレジスタ5601、及びスイッチング回路5602を有する。スイッチング回路5602は、スイッチング回路5602\_1~5602\_N(Nは自然数)で構成される。また、スイッチング回路5602\_1~5602\_Nは、各々、トランジスタ5603\_1~5603\_k(kは自然数)で構成される。ここで、トランジスタ5603\_1~5603\_kは、nチャネル型トランジスタである。

## [0190]

信号線駆動回路の接続関係について、スイッチング回路 5 6 0 2 \_\_ 1 を例として説明する。トランジスタ 5 6 0 3 \_\_ 1 ~ 5 6 0 3 \_\_ k の第 1 端子は、各々、配線 5 6 0 4 \_\_ 1 ~ 5 6 0 4 \_\_ k と接続される。トランジスタ 5 6 0 3 \_\_ 1 ~ 5 6 0 3 \_\_ k の第 2 端子は、各々、信号線 S 1 ~ S k と接続される。トランジスタ 5 6 0 3 \_\_ 1 ~ 5 6 0 3 \_\_ k のゲートは、配線 5 6 0 5 \_\_ 1 と接続される。

## [0191]

シフトレジスタ 5 6 0 1 は、配線 5 6 0 5 \_\_ 1 ~ 5 6 0 5 \_\_ N に順番にHレベル(H信号、高電源電位レベル、ともいう)の信号を出力し、スイッチング回路 5 6 0 2 \_\_ 1 ~ 5 6 0 2 \_\_ N を順番に選択する機能を有する。

#### [0192]

スイッチング回路 5 6 0 2 \_\_ 1 は、配線 5 6 0 4 \_\_ 1 ~ 5 6 0 4 \_\_ k と信号線 S 1 ~ S k との導通状態(第 1 端子と第 2 端子との間の導通)に制御する機能、即ち配線 5 6 0 4 \_\_ 1 ~ 5 6 0 4 \_\_ k の電位を信号線 S 1 ~ S k に供給するか否かを制御する機能を有する。このように、スイッチング回路 5 6 0 2 \_\_ 1 は、セレクタとしての機能を有する。またトランジスタ 5 6 0 3 \_\_ 1 ~ 5 6 0 4 \_\_ 1 ~ 5 6 0 4 \_\_ k と信号線 S 1 ~ S k との導通状態を制御する機能、即ち配線 5 6 0 4 \_\_ 1 ~ 5 6 0 4 \_\_ k の電位を信号線 S 1 ~ S k に供給する機能を有する。このように、トランジスタ 5 6 0 3 \_\_ 1 ~ 5 6 0 3 \_\_ k は、各々、スイッチとしての機能を有する。

20

30

40

50

[0193]

なお、配線 5 6 0 4 \_\_ 1 ~ 5 6 0 4 \_\_ k には、各々、ビデオ信号用データ(DATA)が入力される。ビデオ信号用データ(DATA)は、画像情報または画像信号に応じたアナログ信号である場合が多い。

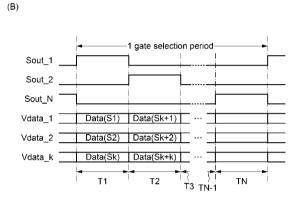

[0194]

次に、図8(A)の信号線駆動回路の動作について、図8(B)のタイミングチャートを参照して説明する。図8(B)には、信号Sout\_1~Sout\_N、及び信号Vdata\_1~Vdata\_kの一例を示す。信号Sout\_1~Sout\_Nは、各々、シフトレジスタ5601の出力信号の一例であり、信号Vdata\_1~Vdata\_kは、各々、配線5604\_1~5604\_kに入力される信号の一例である。なお、信号線駆動回路の1動作期間は、表示装置における1ゲート選択期間に対応する。1ゲート選択期間は、一例として、期間T1~期間TNに分割される。期間T1~TNは、各々、選択された行に属する画素にビデオ信号用データ(DATA)を書き込むための期間である。

[0195]

なお、本実施の形態の図面において、信号波形のなまり等は、明瞭化のために誇張して表記している場合がある。従って、必ずしもそのスケールには限定されない。

[0196]

期間T1~期間TNにおいて、シフトレジスタ5601は、Hレベルの信号を配線5605\_1~5605\_Nに順番に出力する。例えば、期間T1において、シフトレジスタ5601は、ハイレベルの信号を配線5605\_1に出力する。このとき、トランジスタ5603\_1~5603\_kはオンになり、配線5604\_1~5604\_kと、信号線S1~Skとが導通状態になる。そして、配線5604\_1~5604\_kには、Data(S1)~Data(Sk)が入力される。Data(S1)~Data(Sk)は、各々、トランジスタ5603\_1~5603\_kを介して、選択される行に属する画素のうち、1列目~k列目の画素に書き込まれる。こうして、期間T1~TNにおいて、選択された行に属する画素に、k列ずつ順番にビデオ信号用データ(DATA)が書き込まれる

[0197]

以上のように、ビデオ信号用データ(DATA)が複数の列ずつ画素に書き込まれることによって、ビデオ信号用データ(DATA)の数、または配線の数を減らすことができる。よって、外部回路との接続数を減らすことができる。また、ビデオ信号が複数の列ずつ画素に書き込まれることによって、書き込み時間を長くすることができ、ビデオ信号の書き込み不足を防止することができる。

[0198]

なお、シフトレジスタ5601及びスイッチング回路5602としては、実施の形態1、または2に示すトランジスタで構成される回路を用いることが可能である。この場合、シフトレジスタ5601が有する全てのトランジスタを単極性のトランジスタで構成することができる。

[0199]

次に、走査線駆動回路の構成について説明する。走査線駆動回路は、シフトレジスタを有している。また場合によってはレベルシフタやバッファ等を有していても良い。走査線駆動回路において、シフトレジスタにクロック信号(CLK)及びスタートパルス信号(SP)が入力されることによって、選択信号が生成される。生成された選択信号はバッファにおいて緩衝増幅され、対応する走査線に供給される。走査線には、1ライン分の画素のトランジスタのゲート電極が接続されている。そして、1ライン分の画素のトランジスタを一斉にONにしなくてはならないので、バッファは大きな電流を流すことが可能なものが用いられる。

[0200]

走査線駆動回路及び/または信号線駆動回路の一部に用いるシフトレジスタの一形態について図9及び図10を用いて説明する。

20

30

40

50

[0201]

シフトレジスタは、第1のパルス出力回路10\_1乃至第Nのパルス出力回路10\_N(Nは3以上の自然数)を有している(図9(A)参照)。シフトレジスタの第1のパルス出力回路10\_Nには、第1の配線11より第1のクロック信号CK1、第2の配線12より第2のクロック信号CK2、第3の配線13より第3のクロック信号CK3、第4の配線14より第4のクロック信号CK4が供給される

[0202]

また、第1のパルス出力回路10\_1では、第5の配線15からのスタートパルスSP1(第1のスタートパルス)が入力される。また2段目以降の第nのパルス出力回路10\_n(nは、2以上N以下の自然数)では、一段前段のパルス出力回路からの信号(前段信号OUT(n‐1)という)が入力される。

[0203]

また、第1のパルス出力回路10\_1では、2段後段の第3のパルス出力回路10\_3からの信号が入力される。同様に2段目以降の第nのパルス出力回路10\_nでは、2段後段の第(n+2)のパルス出力回路10\_(n+2)からの信号(後段信号OUT(n+2)という)が入力される。

[0204]

従って、各段のパルス出力回路からは、後段及び/または二つ前段のパルス出力回路に入力するための第1の出力信号OUT(1)(SR)乃至OUT(N)(SR)、別の回路等に電気的に入力される第2の出力信号OUT(1)乃至OUT(N)が出力される。なお、図9(A)に示すように、シフトレジスタの最終段の2つの段には、後段信号OUT(n+2)が入力されないため、一例としては、別途第2のスタートパルスSP2、第3のスタートパルスSP3をそれぞれ入力する構成とすればよい。

[ 0 2 0 5 ]

なお、クロック信号(CK)は、一定の間隔でHレベルとLレベル(L信号、低電源電位レベル、ともいう)を繰り返す信号である。ここで、第1のクロック信号(CK1)~第4のクロック信号(CK4)は、順に1/4周期分遅延している(すなわち、互いに90°位相がずれている)。本実施の形態では、第1のクロック信号(CK1)~第4のクロック信号(CK4)を利用して、パルス出力回路の駆動の制御等を行う。なお、クロック信号は、入力される駆動回路に応じて、GCK、SCKということもあるが、ここではCKとして説明を行う。

[0206]

第1の入力端子21、第2の入力端子22及び第3の入力端子23は、第1の配線11~第4の配線14のいずれかと電気的に接続されている。例えば、図9(A)において、第1のパルス出力回路10\_1は、第1の入力端子21が第1の配線11と電気的に接続され、第3の入力端子22が第2の配線12と電気的に接続され、第3の入力端子23が第3の配線13と電気的に接続されている。また、第2のパルス出力回路10\_2は、第1の入力端子21が第2の配線12と電気的に接続され、第2の入力端子22が第3の配線13と電気的に接続され、第3の入力端子23が第4の配線14と電気的に接続されている。

[0207]

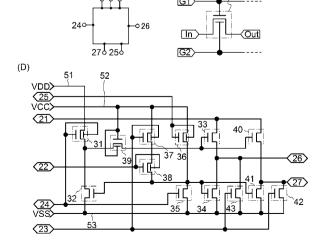

第1のパルス出力回路10\_1~第Nのパルス出力回路10\_Nの各々は、第1の入力端子21、第2の入力端子22、第3の入力端子23、第4の入力端子24、第5の入力端子25、第1の出力端子26、第2の出力端子27を有しているとする(図9(B)参照)。

[0208]

第1のパルス出力回路10\_1において、第1の入力端子21に第1のクロック信号CK1が入力され、第2の入力端子22に第2のクロック信号CK2が入力され、第3の入力端子23に第3のクロック信号CK3が入力され、第4の入力端子24にスタートパルス

が入力され、第5の入力端子25に後段信号OUT(3)が入力され、第1の出力端子26より第1の出力信号OUT(1)(SR)が出力され、第2の出力端子27より第2の出力信号OUT(1)が出力されていることとなる。

[0209]

なお、第1のパルス出力回路10\_1~第Nのパルス出力回路10\_Nには、3端子のトランジスタの他に、4端子のトランジスタ28(図9(C)参照)を用いることができる。なお、本明細書において、トランジスタが半導体層を介して二つのゲート電極を有する場合、半導体層より下方のゲート電極を下方のゲート電極、半導体層に対して上方のゲート電極を上方のゲート電極とも呼ぶ。トランジスタ28は、下方のゲート電極に入力される第1の制御信号G1及び上方のゲート電極に入力される第2の制御信号G2によって、In端子とOut端子間の電気的な制御を行うことのできる素子である。

[0210]

酸化物半導体をトランジスタのチャネル形成領域を含む半導体層に用いた場合、製造工程により、しきい値電圧がマイナス側、或いはプラス側にシフトすることがある。そのため、チャネル形成領域を含む半導体層に酸化物半導体を用いたトランジスタでは、しきい値電圧の制御を行うことのできる構成が好適である。図9(C)に示すトランジスタ28は、チャネル形成領域の上下にゲート絶縁層を介してゲート電極が設けられており、上方及び/または下方のゲート電極の電位を制御することにより、しきい値電圧を所望の値に制御することができる。

[0211]

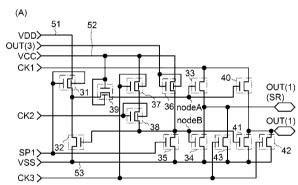

次に、パルス出力回路の具体的な回路構成の一例について、図9(D)を用いて説明する。

[0212]

図9(D)に示したパルス出力回路は、第1のトランジスタ31~第13のトランジスタ43を有している。また、上述した第1の入力端子21~第5の入力端子25、及び第1の出力端子26、第2の出力端子27に加え、第1の高電源電位VDDが供給される電源線51、第2の高電源電位VCCが供給される電源線52、及び低電源電位VSSが供給される電源線53を有し、それぞれに接続された第1のトランジスタ31~第13のトランジスタ43に対して信号、または電源電位を供給する。

[0213]

ここで、図9(D)の各電源線の電源電位の大小関係は、第1の電源電位VDDは第2の電源電位VCC以上の電位とし、第2の電源電位VCCは第3の電源電位VSSより大きい電位とする。なお、第1のクロック信号(CK1)~第4のクロック信号(CK4)は、一定の間隔でHレベルとLレベルを繰り返す信号であり、例えば、HレベルのときはVDD、LレベルのときはVSSとする。

[0214]

なお、電源線 5 1 の電位 V D D を、電源線 5 2 の電位 V C C より高くすることにより、動作に影響を与えることなく、トランジスタのゲート電極に印加される電位を低く抑えることができ、トランジスタのしきい値のシフトを低減し、劣化を抑制することができる。

[0215]

また、図9(D)に図示するように、第1のトランジスタ31~第13のトランジスタ43のうち、第1のトランジスタ31、第6のトランジスタ36乃至第9のトランジスタ39には、図9(C)で示した4端子のトランジスタ28を用いることが好ましい。

[0216]

第1のトランジスタ31、第6のトランジスタ36乃至第9のトランジスタ39の動作は、ソースまたはドレインとなる電極の一方が接続されたノードの電位をゲート電極の制御信号によって切り替えることが求められる。また、ゲート電極に入力される制御信号に対する応答が速い(オン電流の立ち上がりが急峻)ことでよりパルス出力回路の誤動作を低減することができるトランジスタであることが好ましい。従って、4端子のトランジスタ28を用いることによりしきい値電圧を制御することができ、誤動作がより低減できるパ

10

20

30

40

ルス出力回路とすることができる。なお、図9(D)では第1の制御信号G1及び第2の制御信号G2が同じ制御信号としたが、異なる制御信号が入力される構成としてもよい。

[0217]

図 9 ( D ) において第 1 のトランジスタ 3 1 は、第 1 端子が電源線 5 1 に電気的に接続され、第 2 端子が第 9 のトランジスタ 3 9 の第 1 端子に電気的に接続され、ゲート電極(下方のゲート電極及び上方のゲート電極)が第 4 の入力端子 2 4 に電気的に接続されている

[0218]

第 2 のトランジスタ 3 2 は、第 1 端子が電源線 5 3 に電気的に接続され、第 2 端子が第 9 のトランジスタ 3 9 の第 1 端子に電気的に接続され、ゲート電極が第 4 のトランジスタ 3 4 のゲート電極に電気的に接続されている。

[0219]

第3のトランジスタ33は、第1端子が第1の入力端子21に電気的に接続され、第2端子が第1の出力端子26に電気的に接続されている。

[ 0 2 2 0 ]

第4のトランジスタ34は、第1端子が電源線53に電気的に接続され、第2端子が第1の出力端子26に電気的に接続されている。

[ 0 2 2 1 ]

第5のトランジスタ35は、第1端子が電源線53に電気的に接続され、第2端子が第2のトランジスタ32のゲート電極及び第4のトランジスタ34のゲート電極に電気的に接続され、ゲート電極が第4の入力端子24に電気的に接続されている。

[ 0 2 2 2 ]

第6のトランジスタ36は、第1端子が電源線52に電気的に接続され、第2端子が第2のトランジスタ32のゲート電極及び第4のトランジスタ34のゲート電極に電気的に接続され、ゲート電極(下方のゲート電極及び上方のゲート電極)が第5の入力端子25に電気的に接続されている。

[0223]

第7のトランジスタ37は、第1端子が電源線52に電気的に接続され、第2端子が第8のトランジスタ38の第2端子に電気的に接続され、ゲート電極(下方のゲート電極及び上方のゲート電極)が第3の入力端子23に電気的に接続されている。

[0224]

第 8 のトランジスタ 3 8 は、第 1 端子が第 2 のトランジスタ 3 2 のゲート電極及び第 4 のトランジスタ 3 4 のゲート電極に電気的に接続され、ゲート電極(下方のゲート電極及び上方のゲート電極)が第 2 の入力端子 2 2 に電気的に接続されている。

[0225]

第9のトランジスタ39は、第1端子が第1のトランジスタ31の第2端子及び第2のトランジスタ32の第2端子に電気的に接続され、第2端子が第3のトランジスタ33のゲート電極及び第10のトランジスタ40のゲート電極に電気的に接続され、ゲート電極(下方のゲート電極及び上方のゲート電極)が電源線52に電気的に接続されている。

[0226]

第10のトランジスタ40は、第1端子が第1の入力端子21に電気的に接続され、第2端子が第2の出力端子27に電気的に接続され、ゲート電極が第9のトランジスタ39の第2端子に電気的に接続されている。

[0227]

第 1 1 のトランジスタ 4 1 は、第 1 端子が電源線 5 3 に電気的に接続され、第 2 端子が第 2 の出力端子 2 7 に電気的に接続され、ゲート電極が第 2 のトランジスタ 3 2 のゲート電極及び第 4 のトランジスタ 3 4 のゲート電極に電気的に接続されている。

[0228]

第 1 2 のトランジスタ 4 2 は、第 1 端子が電源線 5 3 に電気的に接続され、第 2 端子が第 2 の出力端子 2 7 に電気的に接続され、ゲート電極が第 7 のトランジスタ 3 7 のゲート電

10

20

30

40

極(下方のゲート電極及び上方のゲート電極)に電気的に接続されている。

#### [0229]

第13のトランジスタ43は、第1端子が電源線53に電気的に接続され、第2端子が第1の出力端子26に電気的に接続され、ゲート電極が第7のトランジスタ37のゲート電極(下方のゲート電極及び上方のゲート電極)に電気的に接続されている。

## [0230]

図 9 ( D ) において、第 3 のトランジスタ 3 3 のゲート電極、第 1 0 のトランジスタ 4 0 のゲート電極、及び第 9 のトランジスタ 3 9 の第 2 端子の接続箇所をノード A とする。また、第 2 のトランジスタ 3 2 のゲート電極、第 4 のトランジスタ 3 4 のゲート電極、第 5 のトランジスタ 3 5 の第 2 端子、第 6 のトランジスタ 3 6 の第 2 端子、第 8 のトランジスタ 3 8 の第 1 端子、及び第 1 1 のトランジスタ 4 1 のゲート電極の接続箇所をノード B とする(図 1 0 ( A ) 参照)。

#### [ 0 2 3 1 ]

図10(A)に、図9(D)で説明したパルス出力回路を第1のパルス出力回路10<u></u>1に適用した場合に、第1の入力端子21乃至第5の入力端子25と第1の出力端子26及び第2の出力端子27に入力または出力される信号を示す。

## [0232]

具体的には、第1の入力端子21に第1のクロック信号CK1が入力され、第2の入力端子22に第2のクロック信号CK2が入力され、第3の入力端子23に第3のクロック信号CK3が入力され、第4の入力端子24にスタートパルスが入力され、第5の入力端子25に後段信号OUT(3)が入力され、第1の出力端子26より第1の出力信号OUT(1)(SR)が出力され、第2の出力端子27より第2の出力信号OUT(1)が出力される。

#### [ 0 2 3 3 ]

なお、トランジスタとは、ゲートと、ドレインと、ソースとを含む少なくとも三つの端子を有する素子であり、ドレイン領域とソース領域の間にチャネル領域を有しており、ドレイン領域とチャネル領域とソース領域とを介して電流を流すことが出来る。ここで、ソースとドレインとは、トランジスタの構造や動作条件等によって変わるため、いずれがソースまたはドレインであるかを限定することが困難である。そこで、ソース及びドレインとして機能する領域を、ソースもしくはドレインと呼ばない場合がある。その場合の一例としては、それぞれを第1端子、第2端子と表記する場合がある。

## [0234]

なお、図10(A)において、ノードAを浮遊状態とすることによりブートストラップ動作を行うための、容量素子を別途設けても良い。またノードBの電位を保持するため、一方の電極をノードBに電気的に接続した容量素子を別途設けてもよい。

## [0235]

ここで、図10(A)に示したパルス出力回路を複数具備するシフトレジスタのタイミングチャートを図10(B)に示す。なお、シフトレジスタが走査線駆動回路である場合、図10(B)中の期間61は垂直帰線期間であり、期間62はゲート選択期間に相当する

# [0236]

なお、図10(A)に示すように、ゲートに第2の電源電位VCCが印加される第9のトランジスタ39を設けておくことにより、ブートストラップ動作の前後において、以下のような利点がある。

#### [ 0 2 3 7 ]

ゲート電極に第2の電源電位 V C C が印加される第9のトランジスタ39がない場合、ブートストラップ動作によりノードA の電位が上昇すると、第1のトランジスタ31の第2端子であるソースの電位が上昇していき、第1の電源電位 V D D より大きくなる。そして、第1のトランジスタ31のソースが第1端子側、即ち電源線51側に切り替わる。そのため、第1のトランジスタ31においては、ゲートとソースの間、ゲートとドレインの間

10

20

30

40

20

30

40

50

ともに、大きなバイアス電圧が印加されるために大きなストレスがかかり、トランジスタ の劣化の要因となりうる。

[0238]

そこで、ゲート電極に第2の電源電位VCCが印加される第9のトランジスタ39を設けておくことにより、ブートストラップ動作によりノードAの電位は上昇するものの、第1のトランジスタ31の第2端子の電位の上昇を生じないようにすることができる。つまり、第9のトランジスタ39を設けることにより、第1のトランジスタ31のゲートとソースの間に印加される負のバイアス電圧の値を小さくすることができる。よって、本実施の形態の回路構成とすることにより、第1のトランジスタ31のゲートとソースの間に印加される負のバイアス電圧も小さくできるため、ストレスによる第1のトランジスタ31の劣化を抑制することができる。

[0239]

なお、第9のトランジスタ39を設ける箇所については、第1のトランジスタ31の第2端子と第3のトランジスタ33のゲートとの間に第1端子と第2端子を介して接続されるように設ける構成であればよい。なお、本実施形態でのパルス出力回路を複数具備するシフトレジスタの場合、走査線駆動回路より段数の多い信号線駆動回路では、第9のトランジスタ39を省略してもよく、トランジスタ数を削減できる利点がある。

[0240]

なお、第1のトランジスタ31乃至第13のトランジスタ43の半導体層として、酸化物半導体を用いることにより、トランジスタのオフ電流を低減し、オン電流及び電界効果移動度を高めることが出来ると共に、劣化の度合いを低減することが出来るため、回路内の誤動作を低減することができる。また酸化物半導体を用いたトランジスタは、アモルファスシリコンを用いたトランジスタに比べ、ゲート電極に高電位が印加されることによるトランジスタの劣化の程度が小さい。そのため、第2の電源電位VCCを供給する電源線に、第1の電源電位VDDを供給しても同様の動作が得られ、且つ回路間を引き回す電源線の数を低減することができるため、回路の小型化を図ることが出来る。

[ 0 2 4 1 ]

なお、第7のトランジスタ37のゲート電極(下方のゲート電極及び上方のゲート電極)に第3の入力端子23によって供給されるクロック信号、第8のトランジスタ38のゲート電極(下方のゲート電極及び上方のゲート電極)に第2の入力端子22によって供給されるクロック信号は、第7のトランジスタ37のゲート電極(下方のゲート電極及び上方のゲート電極)に第2の入力端子22によって供給されるクロック信号、第8のトランジスタ38のゲート電極(下方のゲート電極及び上方のゲート電極)に第3の入力端子23によって供給されるクロック信号となるように、結線関係を入れ替えても同様の作用を奏する。

[0242]

なお、図10(A)に示すシフトレジスタにおいて、第7のトランジスタ37及び第8のトランジスタ38が共にオンの状態から、第7のトランジスタ37がオフ、第8のトランジスタ38がオンの状態、次いで第7のトランジスタ37がオフ、第8のトランジスタ38がオフの状態とすることによって、第2の入力端子22(CK2)及び第3の入力端子23(CK3)の電位が低下することで生じるノードBの電位の低下が、第7のトランジスタ37のゲート電極の電位の低下、及び第8のトランジスタ38のゲート電極の電位の低下に起因して2回生じることとなる。

[ 0 2 4 3 ]

一方、図10(A)に示すシフトレジスタにおいて、第7のトランジスタ37及び第8のトランジスタ38が共にオンの状態から、第7のトランジスタ37がオン、第8のトランジスタ38がオフの状態、次いで、第7のトランジスタ37がオフ、第8のトランジスタ38がオフの状態とすることによって、第2の入力端子22(CK2)及び第3の入力端子23(CK3)の電位が低下することで生じるノードBの電位の低下を、第8のトランジスタ38のゲート電極の電位の低下による一回に低減することができる。

[0244]

そのため、第7のトランジスタ37のゲート電極(下方のゲート電極及び上方のゲート電極)に第3の入力端子23からクロック信号CK3が供給され、第8のトランジスタ38のゲート電極(下方のゲート電極及び上方のゲート電極)に第2の入力端子22からクロック信号CK2が供給される結線関係とすることが好適である。なぜなら、ノードBの電位の変動回数が低減され、ノイズを低減することが出来るからである。

[0245]

このように、第1の出力端子26及び第2の出力端子27の電位をLレベルに保持する期間に、ノードBに定期的にHレベルの信号が供給される構成とすることにより、パルス出力回路の誤動作を抑制することができる。

[0246]

なお、本実施の形態は他の実施の形態と自由に組み合わせることができる。

[0247]

(実施の形態7)

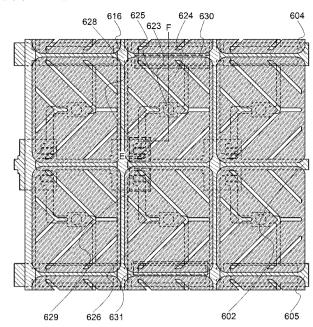

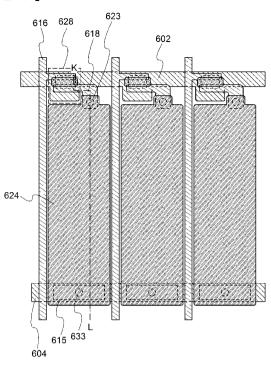

本実施の形態では、表示装置の一形態として、実施の形態1または2で示すトランジスタを有し、表示素子として液晶素子を用いた液晶表示装置の例を図11乃至図24を用いて 説明する。

[0248]

はじめにVA(Vertical Alignment)型の液晶表示装置について示す。VA型の液晶表示装置とは、液晶表示パネルの液晶分子の配列を制御する方式の一種である。VA型の液晶表示装置は、電圧が印加されていないときにパネル面に対して液晶分子が垂直方向を向く方式である。本実施の形態では、特に画素(ピクセル)をいくつかの領域(例えば2~4個のサブピクセル)に分け、それぞれ別の方向に分子を倒すよう工夫されている。これをマルチドメイン化あるいはマルチドメイン設計という。以下の説明では、マルチドメイン設計が考慮された液晶表示装置について説明する。

[0249]

図12及び図13は、それぞれ画素電極及び対向電極を示している。なお、図12は画素電極が形成される基板側の平面図であり、図中に示す切断線E-Fに対応する断面構造を図11に表している。また、図13は対向電極が形成される基板側の平面図である。以下の説明ではこれらの図を参照して説明する。

[0250]

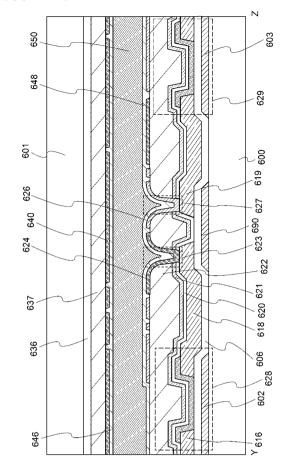

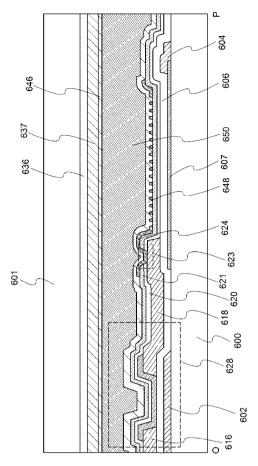

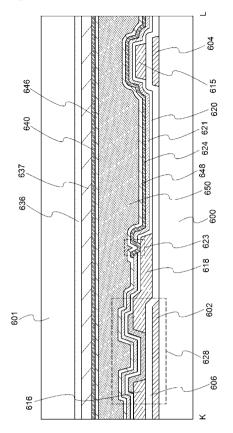

図11は、トランジスタ628とそれに接続する画素電極層624、及び保持容量部63 0が形成された基板600と、対向電極層640等が形成される対向基板601とが重ね合わせられ、液晶が注入された状態を示している。

[0251]

対向基板 6 0 1 には、着色膜 6 3 6、対向電極層 6 4 0 が形成され、対向電極層 6 4 0 上に突起 6 4 4 が形成されている。画素電極層 6 2 4 上には配向膜 6 4 8 が形成され、同様に対向電極層 6 4 0 及び突起 6 4 4 上にも配向膜 6 4 6 が形成されている。基板 6 0 0 と対向基板 6 0 1 の間に液晶層 6 5 0 が形成されている。

[0252]

基板600上には、トランジスタ628とそれに接続する画素電極層624、及び保持容量部630が形成される。画素電極層624は、絶縁膜620、絶縁膜621、及び絶縁膜622に形成されたコンタクトホール623を通じて配線618と接続する。トランジスタ628には実施の形態1及び2で示すトランジスタを適宜用いることができる。また、保持容量部630は、トランジスタ628のゲート配線602と同時に形成した第1の容量配線604と、ゲート絶縁層606と、配線616、618と同時に形成した第2の容量配線617で構成される。

[0253]

画素電極層624と液晶層650と対向電極層640が重なり合うことで、液晶素子が形成されている。

10

20

30

40

20

30

40

50

[ 0 2 5 4 ]

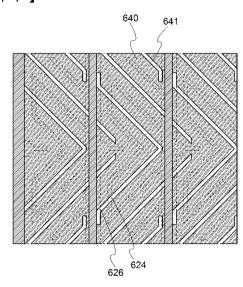

図12に基板600上の平面構造を示す。画素電極層624は、実施の形態1で示した材料を用いて形成する。画素電極層624にはスリット625を設ける。スリット625は液晶の配向を制御するためのものである。

[0255]

図12に示すトランジスタ629とそれに接続する画素電極層626及び保持容量部63 1は、それぞれトランジスタ628、画素電極層624及び保持容量部630と同様に形成することができる。トランジスタ628とトランジスタ629は共に配線616と接続している。この液晶表示パネルの画素(ピクセル)は、画素電極層624と画素電極層626はサブピクセルである。本形態では2つのサブピクセルで画素が構成されているが、更に複数のサブピクセルで構成することもできる。

[0256]

図13に対向基板側の平面構造を示す。対向電極層640は、画素電極層624と同様の材料を用いて形成することが好ましい。対向電極層640上には液晶の配向を制御する突起644が形成されている。なお、図13に基板600上に形成される画素電極層624及び画素電極層624及び画素電極層624及び画素電極層624及び画素電極層624及び画素電極層624及び画素電極層626が重なり合って配置されている様子を示している。

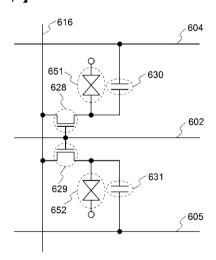

[0257]

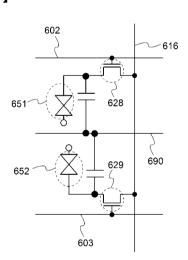

この画素構造の等価回路を図14に示す。トランジスタ628とトランジスタ629は、 共にゲート配線602、配線616と接続している。この場合、容量配線604と容量配 線605の電位を異ならせることで、液晶素子651と液晶素子652の動作を異ならせ ることができる。すなわち、容量配線604と容量配線605の電位を個別に制御するこ とにより液晶の配向を精密に制御して視野角を広げている。

[ 0 2 5 8 ]

スリット625を設けた画素電極層624に電圧を印加すると、スリット625の近傍には電界の歪み(斜め電界)が発生する。このスリット625と、対向基板601側の突起644とを交互に咬み合うように配置することで、斜め電界を効果的に発生させて液晶の配向を制御することで、液晶が配向する方向を場所によって異ならせている。すなわち、マルチドメイン化して液晶表示パネルの視野角を広げている。

[0259]

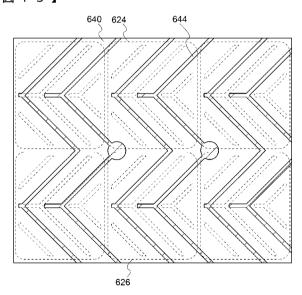

次に、上記とは異なる V A 型の液晶表示装置について、図 1 5 乃至図 1 8 を用いて説明する。

[0260]

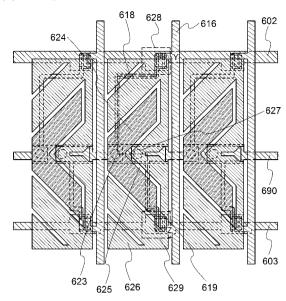

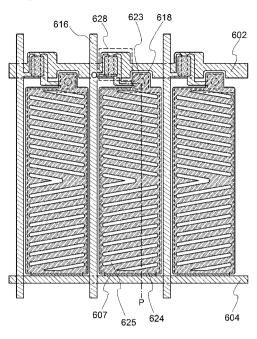

図15と図16は、VA型液晶表示パネルの画素構造を示している。図16は基板600 の平面図であり、図中に示す切断線Y-Zに対応する断面構造を図15に表している。

[ 0 2 6 1 ]

この画素構造は、一つの画素に複数の画素電極が有り、それぞれの画素電極にトランジスタが接続されている。各トランジスタは、異なるゲート信号で駆動されるように構成されている。すなわち、マルチドメイン設計された画素において、個々の画素電極に印加する信号を独立して制御する構成を有している。

[0262]

画素電極層 6 2 4 は、コンタクトホール 6 2 3 で配線 6 1 8 を介してトランジスタ 6 2 8 と接続されている。また、画素電極層 6 2 6 は、コンタクトホール 6 2 7 で配線 6 1 9 を介してトランジスタ 6 2 9 と接続されている。

[0263]

トランジスタ628とトランジスタ629は、実施の形態1または2で示すトランジスタを適宜用いることができる。トランジスタ628のゲート配線602と、トランジスタ629のゲート配線603には、異なるゲート信号を与えることができるように分離されている。一方、データ線として機能する配線616は、トランジスタ628とトランジスタ

20

30

40

50

6 2 9 で共通に用いられている。また、配線 6 1 8 、 6 1 9 の下部には、ゲート絶縁層 6 0 6 を介して容量配線 6 9 0 が設けられている。

## [0264]

画素電極層624と画素電極層626の形状は異なっており、スリット625によって分離されている。V字型に広がる画素電極層624の外側を囲むように画素電極層626が形成されている。画素電極層624と画素電極層626に印加する電圧をトランジスタ628及びトランジスタ629により異ならせることで、液晶の配向を制御している。この画素構造の等価回路を図18に示す。トランジスタ628はゲート配線602と接続している。また、トランジスタ628とトランジスタ629は、共に配線616と接続している。ゲート配線602とゲート配線603に異なるゲート信号を与えることで、液晶素子651と液晶素子652の動作を異ならせることができる。すなわち、トランジスタ628とトランジスタ629の動作を個別に制御することにより、液晶素子651と液晶素子652の液晶の配向を精密に制御して視野角を広げることができる。

#### [0265]

対向基板601には、着色膜636、対向電極層640が形成されている。また、着色膜636と対向電極層640の間には平坦化膜637が形成され、液晶の配向乱れを防いでいる。図17に対向基板側の平面構造を示す。対向電極層640は異なる画素間で共通化されている電極であるが、スリット641が形成されている。このスリット641と、画素電極層624及び画素電極層626側のスリット625とを交互に咬み合うように配置することで、斜め電界を効果的に発生させて液晶の配向を制御することができる。これにより、液晶が配向する方向を場所によって異ならせることができ、視野角を広げている。なお、図17には、基板600上に形成される画素電極層624及び画素電極層626を破線で示し、対向電極層640と、画素電極層624及び画素電極層626が重なり合って配置されている様子を示している。

## [0266]

画素電極層624及び画素電極層626上には配向膜648が形成され、同様に対向電極層640上にも配向膜646が形成されている。基板600と対向基板601の間に液晶層650が形成されている。また、画素電極層624と液晶層650と対向電極層640が重なり合うことで、第1の液晶素子651が形成されている。また、画素電極層626と液晶層650と対向電極層640が重なり合うことで、第2の液晶素子652が形成されている。図15乃至図18で説明する表示パネルの画素構造は、一画素に第1の液晶素子と第2の液晶素子が設けられたマルチドメイン構造となっている。

## [0267]

次に、横電界方式の液晶表示装置について示す。横電界方式は、セル内の液晶分子に対して水平方向に電界を加えることで液晶を駆動して階調表現する方式である。この方式によれば、視野角を約180度にまで広げることができる。以下の説明では、横電界方式を採用する液晶表示装置について説明する。

## [0268]

図19は、電極層607、トランジスタ628、及び画素電極層624が形成された基板600と、対向基板601を重ね合わせ、液晶を注入した状態を示している。対向基板601には、着色膜636、平坦化膜637などが形成されている。なお、画素電極は、基板600側に有るので、対向基板601側に対向電極は設けられていない。また、基板600と対向基板601の間に、配向膜646及び配向膜648を介して液晶層650が形成されている。

# [0269]

基板600上には、電極層607及び電極層607に接続する容量配線604、並びにトランジスタ628が形成される。容量配線604はトランジスタ628のゲート配線60 2と同時に形成することができる。トランジスタ628としては、実施の形態1乃至5で示したトランジスタを適用することができる。電極層607は、実施の形態1または2で 示す画素電極層と同様の材料を用いることができる。また、電極層607は略画素の形状に区画化した形状で形成する。なお、電極層607及び容量配線604上にはゲート絶縁層606が形成される。

[0270]

トランジスタ628の配線616、配線618がゲート絶縁層606上に形成される。配線616は、液晶表示パネルにおいてビデオ信号をのせるデータ線であり、一方向に伸びる配線であると同時に、トランジスタ628のソース領域又はドレイン領域と接続し、ソース及びドレインの一方の電極となる。配線618は、ソース及びドレインの他方の電極となり、画素電極層624と接続する配線である。

[ 0 2 7 1 ]

配線616、配線618上に絶縁膜620及び絶縁膜621が形成される。また、絶縁膜621上には、絶縁膜620、621に形成されるコンタクトホール623を介して、配線618に接続する画素電極層624が形成される。画素電極層624は、実施の形態3で示した画素電極層457と同様の材料を用いて形成することができる。

[0272]

[ 0 2 7 3 ]

このようにして、基板600上にトランジスタ628とそれに接続する画素電極層624が形成される。なお、保持容量は電極層607と画素電極層624の間で形成している。

図 2 0 は、画素電極の構成を示す平面図である。図 2 0 に示す切断線 O - P に対応する断面構造を図 1 9 に表している。画素電極層 6 2 4 にはスリット 6 2 5 が設けられる。スリット 6 2 5 は、液晶の配向を制御するためのものである。

[0274]

この場合、電界は、電極層607と画素電極層624の間で発生する。電極層607と画素電極層624の間にはゲート絶縁層606が形成されているが、ゲート絶縁層606の厚さは50~200nmであり、2~10μmである液晶層の厚さと比較して十分薄いので、実質的に基板600と平行な方向(水平方向)に電界が発生する。この電界により液晶の配向が制御され、基板と略平行な方向の電界を利用して液晶分子を水平に回転させる。この場合、液晶分子はどの状態でも水平であるため、見る角度によるコントラストの変化は無く、視野角が広がることとなる。また、電極層607と画素電極層624は共に透光性の電極であるので、開口率を向上させることができる。

[0275]

次に、横電界方式の液晶表示装置の他の一例について示す。

[0276]

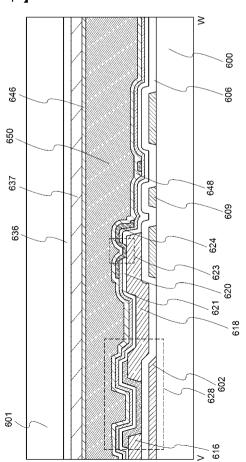

図 2 1 と図 2 2 は、 I P S 型の液晶表示装置の画素構造を示している。図 2 2 は平面図であり、図中に示す切断線 V - Wに対応する断面構造を図 2 1 に表している。

[0277]

図 2 1 は、トランジスタ 6 2 8 とそれに接続する画素電極層 6 2 4 が形成された基板 6 0 0 と、対向基板 6 0 1 を重ね合わせ、液晶を注入した状態を示している。対向基板 6 0 1 には、着色膜 6 3 6、平坦化膜 6 3 7 などが形成されている。なお、対向基板 6 0 1 側に対向電極は設けられていない。また、基板 6 0 0 と対向基板 6 0 1 の間に、配向膜 6 4 6 及び配向膜 6 4 8 を介して液晶層 6 5 0 が形成されている。

[0278]

基板600上には、共通電位線609、及びトランジスタ628が形成される。共通電位線609は、トランジスタ628のゲート配線602と同時に形成することができる。なお、トランジスタ628には、実施の形態1または2で示したトランジスタを用いることができる。

[0279]

トランジスタ628の配線616、配線618は、ゲート絶縁層606上に形成される。 配線616は、液晶表示パネルにおいてビデオ信号を供給するためのデータ線であり、ト ランジスタ628のソース領域又はドレイン領域と接続し、ソース及びドレインの一方の 10

20

30

40

電極としても作用する。配線618は、画素電極層624と接続する配線であり、トランジスタ628のソース及びドレインの他方の電極としても作用する。

[0280]

配線616、配線618上には、絶縁膜620及び絶縁膜621が形成される。また、絶縁膜620、621上には、コンタクトホール623を介して配線618に接続する画素電極層624が形成される。画素電極層624は、実施の形態3で示した画素電極層457と同様の材料を用いて形成することができる。なお、図22に示すように、画素電極層624は、共通電位線609と同時に形成した櫛形の電極との間に横電界が発生するように形成される。また、画素電極層624の櫛歯の部分は、共通電位線609と同時に形成した櫛形の電極と交互に咬み合うように形成される。

[0281]

画素電極層 6 2 4 と共通電位線 6 0 9 との間に電界を生じさせると、この電界により液晶の配向が制御される。従って、基板と略平行な方向の電界を利用して液晶分子を水平に回転させることができる。この場合、液晶分子はどの状態でも水平であるため、見る角度によるコントラストの変化は無く、視野角が広がることとなる。

[ 0 2 8 2 ]

このようにして、基板600上にトランジスタ628とそれに接続する画素電極層624が形成される。保持容量は、共通電位線609、ゲート絶縁層606、及び容量電極615で形成している。なお、容量電極615と画素電極層624はコンタクトホール633を介して接続されている。

[0283]

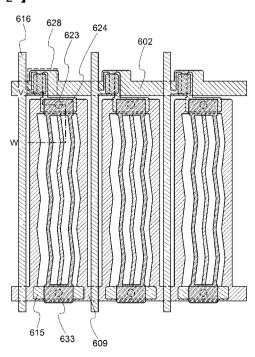

次に、TN型の液晶表示装置の形態について示す。

[0284]

図 2 3 と図 2 4 は、TN型の液晶表示装置の画素構造を示している。図 2 4 は平面図であり、図中に示す切断線 K - L に対応する断面構造を図 2 3 に表している。

[0285]

画素電極層 6 2 4 は、コンタクトホール 6 2 3 で配線 6 1 8 を介してトランジスタ 6 2 8 と接続している。データ線として機能する配線 6 1 6 は、トランジスタ 6 2 8 と接続している。トランジスタ 6 2 8 には、実施の形態 1 または 2 に示すトランジスタのいずれかを用いることができる。

[0286]

画素電極層624は、実施の形態3で示した画素電極層457と同様の材料を用いて形成することができる

[ 0 2 8 7 ]

対向基板 6 0 1 には、着色膜 6 3 6、対向電極層 6 4 0 が形成されている。また、着色膜 6 3 6と対向電極層 6 4 0 の間には平坦化膜 6 3 7 が形成され、液晶の配向乱れを防いでいる。液晶層 6 5 0 は、画素電極層 6 2 4と対向電極層 6 4 0 の間に配向膜 6 4 8 及び配向膜 6 4 6を介して形成されている。液晶素子は、画素電極層 6 2 4、液晶層 6 5 0 及び対向電極層 6 4 0 が重なり合うことで形成されている。

[0288]

また、着色膜636は、基板600側に形成されていても良い。また、基板600のトランジスタが形成されている面とは逆の面、及び対向基板601の対向電極層640が形成されている面とは逆の面に偏光板を貼り合わせておく。

[0289]

以上の工程により、開口率が高い液晶表示装置を作製することができる。

[0290]

なお、本実施の形態は他の実施の形態と自由に組み合わせることができる。

[0291]

(実施の形態8)

本明細書に開示する表示装置は、さまざまな電子機器(遊技機も含む)に適用することが

10

20

30

40

できる。電子機器としては、例えば、テレビジョン装置(テレビ、またはテレビジョン受信機ともいう)、コンピュータ用などのモニタ、デジタルカメラ、デジタルビデオカメラ、デジタルフォトフレーム、携帯電話機(携帯電話、携帯電話装置ともいう)、携帯型ゲーム機、携帯情報端末、音響再生装置、パチンコ機などの大型ゲーム機などが挙げられる

[0292]

図 2 5 ( A ) は、携帯電話機の一例を示している。携帯電話機 1 1 0 0 は、筐体 1 1 0 1 に組み込まれた表示部 1 1 0 2 の他、操作ボタン 1 1 0 3 、外部接続ポート 1 1 0 4 、スピーカー 1 1 0 5 、マイク 1 1 0 6 などを備えている。

[0293]

図 2 5 ( A ) に示す携帯電話機 1 1 0 0 は、表示部 1 1 0 2 を指などで触れることで、情報を入力ことができる。また、通話やメールの送受信などの操作は、表示部 1 1 0 2 を指などで触れることにより行うことができる。

[0294]

表示部1102の画面は主として3つのモードがある。第1は、画像の表示を主とする表示モードであり、第2は、文字等の情報の入力を主とする入力モードである。第3は表示 モードと入力モードの2つのモードが混合した表示+入力モードである。

[0295]

例えば、通話や、メールを作成する場合は、表示部1102を文字の入力を主とする文字 入力モードとし、画面に表示させた文字の入力操作を行えばよい。この場合、表示部11 02に認識性良くキーボードまたは番号ボタンを表示させることが好ましい。

[0296]

また、携帯電話機1100内部に、ジャイロ、加速度センサ等の傾きを検出するセンサを有する検出装置を設けることで、携帯電話機1100の向き(縦か横か)を判断して、表示部1102の画面表示を自動的に切り替えるようにすることができる。

[0297]

また、画面モードの切り替えは、表示部1102を触れること、または筐体1101の操作ボタン1103の操作により行われる。また、表示部1102に表示される画像の種類によって切り替えるようにすることもできる。例えば、表示部に表示する画像信号が動画のデータであれば表示モード、テキストデータであれば入力モードに切り替える。

[0298]

また、入力モードにおいて、表示部1102の光センサで検出される信号を検知し、表示部1102のタッチ操作による入力が一定期間ない場合には、画面のモードを入力モードから表示モードに切り替えるように制御してもよい。

[0299]

表示部1102は、イメージセンサとして機能させることもできる。例えば、表示部1102で、掌紋や指紋等を撮像し、本人認証を行うことができる。また、近赤外光を発光する光源を用いれば、指静脈、掌静脈などを撮像することもできる。ここで、表示部1102には、実施の形態1または2に示すトランジスタ460が複数配置されている。トランジスタ460は、透光性を有しているため、トランジスタ460の下部に光センサを配置することができる。また、近赤外光を発光する光源を用いる場合においてもトランジスタ460によって遮光されないため、被写体に対して十分な光量の近赤外光を照射することができる。

[0300]

図 2 5 ( B ) も携帯電話機の一例である。図 2 5 ( B ) を一例とした携帯型情報端末は、複数の機能を備えることができる。例えば電話機能に加えて、コンピュータを内蔵し、様々なデータ処理機能を備えることもできる。

[0301]

図 2 5 ( B ) に示す携帯型情報端末は、筐体 1 8 0 0 及び筐体 1 8 0 1 の二つの筐体で構成されている。筐体 1 8 0 0 には、表示パネル 1 8 0 2 、スピーカー 1 8 0 3 、マイクロ

10

20

30

40

フォン 1 8 0 4 、ポインティングデバイス 1 8 0 6 、カメラ 1 8 0 7 、外部接続端子 1 8 0 8 などを備え、筐体 1 8 0 1 には、キーボード 1 8 1 0 、外部メモリスロット 1 8 1 1 などを備えている。また、アンテナは筐体 1 8 0 1 内部に内蔵されている。

#### [0302]

また、表示パネル 1 8 0 2 はタッチパネルを備えており、図 2 5 ( B ) には映像表示されている複数の操作キー 1 8 0 5 を点線で示している。

#### [0303]

また、上記構成に加えて、非接触ICチップ、小型記録装置などを内蔵していてもよい。 【 0 3 0 4 】

表示装置は、表示パネル1802として用いられ、使用形態に応じて表示の方向が適宜変化する。また、表示パネル1802と同一面上にカメラ1807を備えているため、テレビ電話が可能である。スピーカー1803及びマイクロフォン1804は音声通話に限らず、録音、再生などにも使用できる。さらに、筐体1800と筐体1801は、スライドし、図25(B)のように展開している状態から重なり合った状態とすることができ、携帯に適した小型化が可能である。

#### [0305]

外部接続端子1808は、電源入力や情報通信ための入出力端子であり、充電及びパーソナルコンピュータなどとのデータ通信が可能である。また、外部メモリスロット1811 に記録媒体を挿入し、より大量のデータ保存及び移動に対応できる。

## [0306]

また、上記機能に加えて、赤外線通信機能、テレビ受信機能などを備えたものであっても よい。

## [0307]

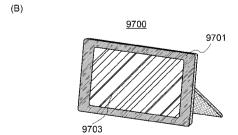

図26(A)は、テレビジョン装置の一例を示している。テレビジョン装置9600は、 筐体9601に表示部9603が組み込まれている。表示部9603により、映像を表示 することが可能である。また、ここでは、スタンド9605により筐体9601を支持し た構成を示している。

#### [0308]

テレビジョン装置9600の操作は、筐体9601が備える操作スイッチや、リモコン操作機9610により行うことができる。リモコン操作機9610が備える操作キー9609により、チャンネルの切り替えや音量の操作を行うことができ、表示部9603に表示される映像を操作することができる。また、リモコン操作機9610に、当該リモコン操作機9610から出力する情報を表示する表示部9607を設ける構成としてもよい。

## [0309]

なお、テレビジョン装置 9 6 0 0 は、受信機やモデムなどを備えた構成とする。受信機により一般のテレビ放送の受信を行うことができ、さらにモデムを介して有線または無線による通信ネットワークに接続することにより、一方向(送信者から受信者)または双方向(送信者と受信者間、あるいは受信者間同士など)の情報通信を行うことも可能である。

## [0310]

図26(B)は、デジタルフォトフレームの一例を示している。デジタルフォトフレーム 9700には、筐体9701に表示部9703が組み込まれている。表示部9703は、 各種画像を表示することが可能であり、例えばデジタルカメラなどで撮影した画像データ を表示させることで、通常の写真立てと同様に機能させることができる。

# [0311]

なお、デジタルフォトフレーム9700は、操作部、外部接続用端子(USB端子等)、外部メモリスロットなどを備える構成とする。これらの構成は、表示部と同一面に組み込まれていてもよいが、側面や裏面に備えるとデザイン性が向上するため好ましい。例えば、デジタルフォトフレームの外部メモリスロットに、デジタルカメラで撮影した画像データを記憶したメモリを挿入して画像データを取り込み、取り込んだ画像データを表示部9703に表示させることができる。

10

20

30

40

[0312]

また、デジタルフォトフレーム9700は、無線で情報を送受信できる構成としてもよい 。無線により、所望の画像データを取り込み、表示させる構成とすることもできる。

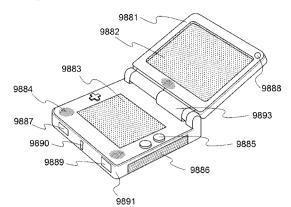

[ 0 3 1 3 ]

図27は携帯型遊技機であり、筐体9881と筐体9891の2つの筐体で構成されており、連結部9893により、開閉可能に連結されている。筐体9881には表示部988 2が組み込まれ、筐体9891には表示部9883が組み込まれている。

[0314]

また、図27に示す携帯型遊技機は、スピーカー9884、外部メモリスロット9886、LEDランプ9890、入力手段(操作キー9885、接続端子9887、センサ9888(力、変位、位置、速度、加速度、角速度、回転数、距離、光、液、磁気、温度、化学物質、音声、時間、硬度、電場、電流、電圧、電力、放射線、流量、湿度、傾度、振動、におい、または赤外線を測定する機能を含むもの)、マイクロフォン9889)等を備えている。もちろん、携帯型遊技機の構成は上述のものに限定されず、少なくとも本時に開示する表示装置を備えた構成であればよく、その他付属設備が適宜設けられた構成とすることができる。図27に示す携帯型遊技機は、記録媒体に記録されているプログラムまたはデータを読み出して表示部に表示する機能や、他の携帯型遊技機と無線通信を行って情報を共有する機能を有する。なお、図27に示す携帯型遊技機が有する機能はこれに限定されず、様々な機能を有することができる。

[0315]

以上のように、他の実施の形態で示した表示装置は、上記のような様々な電子機器の表示部に配置することができる。

[0316]

なお、本実施の形態は他の実施の形態と自由に組み合わせることができる。

[0317]

(実施の形態9)

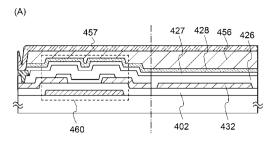

本実施の形態では、保持容量の構成について、実施の形態3と異なる例を図28(A)及び図28(B)を用いて説明する。図28(A)、(B)は、画素部のトランジスタ460と保持容量の断面図である。なお、図28(A)、(B)では、図3と保持容量の構成が異なる点以外は同じであるため、同じ箇所には同じ符号を用い、同じ箇所の詳細な説明は省略する。

[0318]

図28(A)は、誘電体に酸化物絶縁層426、427、保護絶縁層428及び平坦化絶縁層456を用い、画素電極層457と容量配線層432とで保持容量を形成する例である。容量配線層432は、画素部のトランジスタ460のソース電極層と同じ透光性を有する材料、及び同じ工程で形成されるため、トランジスタ460のソース配線層と重ならないようにレイアウトされる。

[0319]

図 2 8 ( A ) に示す保持容量は、一対の電極及び誘電体が透光性を有しており、保持容量全体として透光性を有する。

[0320]

また、図28(B)は、図28(A)と異なる保持容量の構成の例である。

[0321]

図28(B)は、誘電体にゲート絶縁層402を用い、容量配線層430、容量電極43 1及び酸化物半導体層405とで保持容量を形成する例である。ここで、容量電極431 に接して形成された酸化物半導体層405は、保持容量の一方の電極として機能する。な お、酸化物半導体層405は、トランジスタ460のソース電極層またはドレイン電極層 と同じ透光性を有する材料、及び同じ工程で形成する。また、容量配線層430は、トラ ンジスタ460のゲート電極層と同じ透光性を有する材料、及び同じ工程で形成されるた め、トランジスタ460のゲート配線層と重ならないようにレイアウトされる。 10

20

30

- -

40

50

```

[0322]

```

また、図示はしないが、容量電極431は画素電極層457と電気的に接続されている。

## [0323]

図28(B)に示す保持容量も、一対の電極及び誘電体が透光性を有しており、保持容量 全体として透光性を有する。

## [0324]

図28(A)及び図28(B)に示す保持容量は、透光性を有しており、表示画像の高精 細化を図るために画素寸法を微細化しても、十分な容量を得ることができ、且つ、高い開 口率を実現することができる。

## [0325]

なお、本実施の形態は他の実施の形態と自由に組み合わせることができる。

#### 【符号の説明】

## [0326]

- 1 1 配線

- 1 2 配線

- 1 3 配線

- 1 4 配線

- 配線 1 5

- 2 1 入力端子

- 2 2 入力端子

- 2 3 入力端子

- 2 4 入力端子

- 2 5 入力端子

- 2 6 出力端子

- 2 7 出力端子

- 2 8 トランジスタ

- 3 1 トランジスタ

- 3 2 トランジスタ

- 3 3 トランジスタ

- 3 4 トランジスタ

- 3 5 トランジスタ

- 3 6 トランジスタ

- 3 7 トランジスタ

- 3 8 トランジスタ 3 9 トランジスタ

- 4 0 トランジスタ

- 4 1 トランジスタ

- 4 2 トランジスタ

- 4 3 トランジスタ

- 5 1 電源線

- 5 2 電源線

- 電源線 5 3

- 6 1 期間

- 6 2 期間

- 4 0 0 基板

- 4 0 2 ゲート絶縁層

- 4 0 3 酸化物半導体層

- 4 0 4 酸化物半導体層

- 4 0 5 酸化物半導体層

- 4 1 1 端子

10

20

30

40

50

| 4 4 2   | to to Table 12 R |    |

|---------|------------------|----|

| 4 1 2   | 接続電極層            |    |

| 4 1 4   | 端子               |    |

| 4 1 5   | 導電層              |    |

| 4 1 6   | 電極層              |    |

| 4 1 7   | 導電層              |    |

| 4 1 8   | 導電層              |    |

| 4 2 2   | ソース配線層           |    |

| 4 2 3   | チャネル形成領域         |    |

| 4 2 6   | 酸化物絶緣層           |    |

| 4 2 7   | 酸化物絶緣層           | 10 |

| 4 2 8   | 保 護 絶 縁 層        |    |

| 4 2 9   | 接続電極層            |    |

| 4 3 0   | 容量配線層            |    |

| 4 3 1   | 容量電極             |    |

| 4 3 2   | 容量配線層            |    |

| 4 4 0   | トランジスタ           |    |

| 4 4 2   | 接 続 電 極 層        |    |

| 4 4 3   | チャネル形成領域         |    |

| 4 4 7   | 酸化物導電層           |    |

| 4 4 8   | 酸化物導電層           | 20 |

| 4 4 9   | 接続電極層            |    |

| 4 5 0   | トランジスタ           |    |

| 4 5 2   | 接続電極層            |    |

| 4 5 3   | 酸化物半導体層          |    |

| 4 5 4   | 酸化物半導体層          |    |

| 4 5 6   | 平坦化絶緣層           |    |

| 4 5 7   | 画素電極層            |    |

| 4 6 0   | トランジスタ           |    |

| 4 2 1 a | ゲート電極層           |    |

| 4 2 1 b | ゲート電極層           | 30 |

| 4 2 1 c | ゲート配線層           |    |

| 4 2 4 a | 高抵抗ソース領域         |    |

| 4 2 4 b | 高抵抗ドレイン領域        |    |

| 4 2 4 c | 第 1 領 域          |    |

| 4 2 4 d | 第 2 領域           |    |

| 4 2 5 a | ソース電極層           |    |

| 4 2 5 b | ドレイン電極層          |    |

| 4 4 4 a | 高抵抗ソース領域         |    |

| 4 4 4 b | 高抵抗ドレイン領域        |    |

| 4 4 4 c | 第 1 領 域          | 40 |

| 4 4 4 d | 第 2 領域           |    |

| 4 4 5 a | ソース電極層           |    |

| 4 4 5 b | ドレイン電極層          |    |

| 4 4 6 a | 酸化物導電層           |    |

| 4 4 6 b | 酸化物導電層           |    |

| 4 5 1 a | ゲート電極層           |    |

| 4 5 1 b | ゲート電極層           |    |

| 4 5 5 a | ソース電極層           |    |

| 4 5 5 b | ドレイン電極層          |    |

| 6 0 0   | 基板               | 50 |

|         |                  |    |

| 6 | 0 | 1   | 対 向 基 板       |

|---|---|-----|---------------|

| 6 | 0 | 2   | ゲート配線         |

| 6 | 0 | 3   | ゲート配線         |

| 6 | 0 | 4   | 容量配線          |

| 6 | 0 | 5   | 容量配線          |

|   | 0 |     | ゲート絶縁層        |

|   | 0 |     | 電極層           |

|   | 0 |     | 共通電位線         |

|   |   |     |               |

|   | 1 |     | 容量電極          |

|   | 1 |     | 配線            |

|   | 1 |     | 容量配線          |

| 6 | 1 | 8   | 配 線           |

| 6 | 1 | 9   | 配 線           |

| 6 | 2 | 0   | 絶 縁 膜         |

| 6 | 2 | 1   | 絶 縁 膜         |

|   | 2 |     | 絶縁膜           |

|   | 2 |     | コンタクトホール      |

|   | 2 |     | コンファーホール画素電極層 |

|   |   |     |               |

|   | 2 |     | スリット          |

|   | 2 |     | 画素電極層         |

|   |   | 7   | コンタクトホール      |

|   | 2 |     | トランジスタ        |

| 6 | 2 | 9   | トランジスタ        |

| 6 | 3 | 0   | 保持容量部         |

| 6 | 3 | 1   | 保持容量部         |

|   | 3 |     | コンタクトホール      |

|   | 3 |     | 着色膜           |

|   | 3 |     | 着色膜           |

|   |   | 7   |               |

|   |   |     | 平坦化膜          |

|   | 3 |     | 着色膜           |

|   | 4 |     | 対 向 電 極 層     |

|   | 4 |     | スリット          |

| 6 | 4 | 4   | 突起            |

| 6 | 4 | 6   | 配 向 膜         |

| 6 | 4 | 8   | 配 向 膜         |

|   | 5 |     | 液晶層           |

|   | 5 |     | 液晶素子          |

|   | 5 |     | 液晶素子          |

|   | 9 |     |               |

|   |   |     | 容量配線          |

|   |   | 0 0 | 携帯電話機         |

|   |   | 0 1 | 筐体            |

|   |   | 0 2 |               |

| 1 | 1 | 0 3 | 操 作 ボ タ ン     |

| 1 | 1 | 0 4 | 外 部 接 続 ポ ー ト |

| 1 | 1 | 0 5 | スピーカー         |

| 1 | 1 | 0 6 | マイク           |

| 1 | 8 | 0 0 | 筐 体           |

|   |   | 0 1 | 筐体            |

|   |   | 0 2 |               |

|   |   | 0 3 |               |

| 1 | J | 0 3 | スこ カ          |

| 1 8 0 4 | マイクロフォン        |    |

|---------|----------------|----|

| 1 8 0 5 | 操 作 <b>キ</b> 一 |    |

| 1 8 0 6 | ポインティングデバイス    |    |

| 1 8 0 7 | カメラ            |    |

| 1 8 0 8 | 外 部 接 続 端 子    |    |

| 1810    | キーボード          |    |

|         |                |    |

| 1 8 1 1 | 外部メモリスロット      |    |

| 2 6 0 0 | トランジスタ基板       |    |

| 2 6 0 1 | 対向基板           | 40 |

| 2 6 0 2 | シール材           | 10 |

| 2 6 0 3 | 画素部            |    |

| 2 6 0 4 | 表示素子           |    |

| 2 6 0 5 | 着色層            |    |

| 2 6 0 6 | 偏 光 板          |    |

| 2 6 0 7 | 偏 光 板          |    |

| 2 6 0 8 | 配 線 回 路 部      |    |

| 2 6 0 9 | フレキシブル配線基板     |    |

| 2 6 1 0 | 冷陰極管           |    |

| 2 6 1 1 | 反射 板           |    |

| 2 6 1 2 | 回路基板           | 20 |

| 2 6 1 3 | 拡散板            |    |

| 4 0 0 1 | 基板             |    |

| 4 0 0 2 | 画素部            |    |

| 4 0 0 3 | 信号線駆動回路        |    |

| 4 0 0 4 | 走査線駆動回路        |    |

| 4 0 0 5 | シール材           |    |

| 4005    | 基板             |    |

| 4 0 0 8 |                |    |

| 4008    | 液晶層            |    |

|         | トランジスタ         | 30 |

| 4 0 1 1 | トランジスタ         | 30 |

| 4 0 1 3 | 液晶素子           |    |

| 4 0 1 5 | 接続端子電極         |    |

| 4 0 1 6 | 端子電極           |    |

| 4 0 1 8 | F P C          |    |

| 4 0 1 9 | 異方性導電膜         |    |

| 4 0 2 0 | 保護絶縁層          |    |

| 4 0 2 1 | 絶縁層            |    |

| 4 0 3 0 | 画素電極           |    |

| 4 0 3 1 | 対 向 電 極        |    |

| 4 0 3 2 | 絶緣層            | 40 |

| 4 0 4 0 | 導電層            |    |

| 4 0 4 1 | 絶緣層            |    |

| 5 3 0 0 | 基 板            |    |

| 5 3 0 1 | 画素部            |    |

| 5 3 0 2 | 走 査 線 駆 動 回 路  |    |

| 5 3 0 3 | 走査線駆動回路        |    |

| 5 3 0 4 | 信号線駆動回路        |    |

| 5 3 0 5 | タイミング制御回路      |    |

| 5 6 0 1 | シフトレジスタ        |    |

| 5 6 0 2 | スイッチング回路       | 50 |

|         |                |    |

```

5 6 0 3

トランジスタ

5 6 0 4

配 線

5 6 0 5

配線

9 6 0 0

テレビジョン装置

9 6 0 1

筐体

9 6 0 3

表示部

スタンド

9 6 0 5

9 6 0 7

表示部

9 6 0 9

操作キー

10

リモコン操作機

9 6 1 0

デジタルフォトフレーム

9 7 0 0

9 7 0 1

筐体

9 7 0 3

表示部

9 8 8 1

筐体

9 8 8 2

表示部

9 8 8 3

表示部

9 8 8 4

スピーカー

9 8 8 5

操作キー

9 8 8 6

外部メモリスロット

20

9 8 8 7

接続端子

9 8 8 8

センサ

マイクロフォン

9 8 8 9

9 8 9 0

LEDランプ

9 8 9 1

筐体

9 8 9 3

連結部

【図2】

【図1】

```

【図3】

【図4】

【図5】

【図6】

(C)

(B)

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【図20】

【図21】

【図22】

【図23】

【図24】

【図25】

【図26】

(A)

【図27】

# 【図28】

## フロントページの続き

(72)発明者 細羽 みゆき

神奈川県厚木市長谷398番地 株式会社半導体エネルギー研究所内

(72)発明者 坂倉 真之

神奈川県厚木市長谷398番地 株式会社半導体エネルギー研究所内

(72)発明者 及川 欣聡

神奈川県厚木市長谷398番地 株式会社半導体エネルギー研究所内

Fターム(参考) 5F110 AA02 AA30 BB02 CC03 CC07 DD02 DD03 DD04 DD07 DD13

DD14 DD15 DD17 EE03 EE04 EE06 EE07 EE08 EE14 EE38

EE44 FF02 FF03 FF04 FF09 FF28 FF30 GG01 GG24 GG25

GG35 GG43 GG57 GG58 HK02 HK03 HK04 HK07 HK08 HK21

HK22 HK32 HK33 HM17 HM18 HM19 NN04 NN22 NN23 NN24

NN25 NN34 NN40 NN72 NN78 PP10 PP13 QQ06 QQ09 QQ19