# (19) 国家知识产权局

# (12) 发明专利申请

(10) 申请公布号 CN 116564795 A (43) 申请公布日 2023. 08. 08

(21)申请号 202310048415.5

(22)申请日 2023.01.31

(30) 优先权数据 2022-016461 2022.02.04 JP

(71) 申请人 株式会社博迈立铖 地址 日本东京都

(72) 发明人 近藤祯彦 池田润也

(74) 专利代理机构 北京尚诚知识产权代理有限公司 11322 专利代理师 龙淳 程采

(51) Int.CI.

*H01L* 21/02 (2006.01) *H01L* 21/304 (2006.01)

权利要求书1页 说明书10页 附图4页

#### (54) 发明名称

SiC外延基板及其制造方法

#### (57) 摘要

本发明提供一种能够得到平坦性优异的SiC外延基板的新型的基板制造方法和平坦性优异的SiC外延基板。该SiC外延基板(1)在碳化硅基板(2)的表面具有使碳化硅外延生长而成的外延膜(3),SiC外延基板(1)具有由外延膜(3)构成的主面(1a)和作为其相反面的主面(1b),在主面(1b)上,满足以10mm见方的位点为基准的SBIR的最大值为0.1μm以上1.5μm以下的条件。

1.一种SiC外延基板,其特征在于:

在碳化硅基板的表面具有使碳化硅外延生长而成的外延膜,

所述SiC外延基板具有由所述外延膜构成的第一主面和作为其相反面的第二主面,直径为150mm以上,

在所述第二主面上,以10mm见方的位点为基准的SBIR的最大值为0.1μm以上1.5μm以下,并且在所述第一主面上,以10mm见方的位点为基准的SFQR的最大值为0.1μm以上1.5μm以下。

2. 如权利要求1所述的SiC外延基板,其特征在于:

所述SBIR在0.5µm以下的位点比率为65%以上。

3. 如权利要求1或2所述的SiC外延基板,其特征在于:

所述SFQR在0.3µm以下的位点比率为85%以上。

4. 如权利要求1~3中任一项所述的SiC外延基板,其特征在于:

所述SiC外延基板的直径为200mm以上。

- 5.一种SiC外延基板的制造方法,其特征在于,包括:

- (a)准备板状的碳化硅基板的工序;

- (b) 在所述碳化硅基板的表面使碳化硅外延生长而形成由外延膜构成的第一主面的工序:

- (c) 在所述外延膜的表面形成保护膜的工序;

- (d) 对所述碳化硅基板的所述第一主面的相反面以所述第一主面的形状为基准进行研削或研磨加工而形成第二主面的工序:和

- (e)除去所述保护膜的工序。

- 6. 如权利要求5所述的SiC外延基板的制造方法,其特征在于:

所述保护膜由抗蚀剂或液体蜡形成。

7. 如权利要求6所述的SiC外延基板的制造方法,其特征在于:

所述抗蚀剂是含有选自乳酸乙酯和乙酸丁酯中的至少1种的正型抗蚀剂。

8. 如权利要求6所述的SiC外延基板的制造方法,其特征在于:

所述液体蜡是含有选自松香和异丙醇中的至少1种的液体蜡。

9. 如权利要求5~8中任一项所述的SiC外延基板的制造方法,其特征在于:

在所述(e)工序中,施加超声波振动或者使所述碳化硅基板上下摇动。

10. 如权利要求5~9中任一项所述的SiC外延基板的制造方法,其特征在于:

所述SiC外延基板的基板面上的残留物小于0.1个/cm<sup>2</sup>。

# SiC外延基板及其制造方法

#### 技术领域

[0001] 本发明涉及在碳化硅基板的表面具有外延膜的SiC外延基板及其制造方法。

### 背景技术

[0002] 在碳化硅(以下有时也称为"SiC")基板的表面形成有由碳化硅构成的外延膜的 SiC外延基板通常利用气相生长法进行。但是,已知在使该SiC气相生长时,也会附着于与外延膜的形成面相反的表面(背面)等上,SiC生长为突起状。

[0003] 这样,一旦SiC在基板的背面生长,就会导致基板面发生变化、或者因三维生长的突起而产生凹凸,在任何情况下都会发生变化而偏离预想的基板形状,因而导致该基板的平坦性变差。因此,使用这些基板制作半导体元件时,也成为对半导体元件的特性造成不良影响的原因。

[0004] 在这种情况下,需要通过对基板的背面进行研磨等,将未预定的因外延生长而形成的SiC除去的操作。在进行这样的除去操作的情况下,形成保护基板表面的保护膜、进行除去操作后,再除去该保护膜,因此SiC基板的制造工艺的工序变得复杂。

[0005] 因此,提出了一种SiC基板的制造方法,其在外延生长之前,在背面形成保护膜,在保护膜上形成突起,如此能够容易地除去形成于基板背面的SiC的突起等(例如参照专利文献1)。

[0006] 现有技术文献

[0007] 专利文献

[0008] 专利文献1:日本特开2015-160750号公报

[0009] 然而,在通过外延生长来形成外延膜时,除了上述的问题以外,有时还会损害平坦性。

[0010] 例如与SiC基板的中央部相比,SiC基板的外延膜在外周部发生原料气体的震动,因此外延生长的速度有时会发生变化,所形成的外延膜的厚度产生偏差。

[0011] 另外,所使用的SiC基板原本的平坦性也存在偏差,例如厚度在中央部和外周部稍有差异,整体呈锥形时,外延膜有时会延续基板原本的平坦性,也无法确保所形成的SiC外延基板的平坦性。

[0012] 这样,如果无法充分确保SiC外延基板的平坦性,则在之后进行的光刻工序中就会出现问题。即,将SiC外延基板的背面固定于真空卡盘,在具有外延膜的表面形成掩模图案,此时,一旦SiC外延基板的平坦性变差,掩模图案的位置就会偏离所希望的位置,所得到的半导体芯片的成品率降低。

#### 发明内容

[0013] 发明所要解决的技术问题

[0014] 因此,为了解决上述问题,提供能够得到平坦性优异的SiC外延基板的新型的基板制造方法和平坦性优异的SiC外延基板,本发明的发明人进行了精心研究。

[0015] 用于解决技术问题的技术方案

[0016] 一个实施方式的SiC外延基板是在碳化硅基板的表面具有使碳化硅外延生长而成的外延膜的SiC外延基板,上述SiC外延基板具有由上述外延膜构成的第一主面和作为其相反面的第二主面,在上述第二主面上,以10mm见方的位点为基准的SBIR的最大值满足0.1μm以上1.5μm以下的条件。

[0017] 一个实施方式的SiC外延基板的制造方法包括: (a) 准备板状的碳化硅基板的工序; (b) 在上述碳化硅基板的表面使碳化硅外延生长而形成由外延膜构成的第一主面的工序; (c) 在上述外延膜的表面形成保护膜的工序; (d) 对上述碳化硅基板的上述第一主面的相反面以上述第一主面的形状为基准进行研削或研磨加工而形成第二主面的工序; 和 (e) 除去上述保护膜的工序。

[0018] 发明效果

[0019] 利用一个实施方式的SiC外延基板及其制造方法,能够提供平坦性高的SiC外延基板。另外,该平坦性高的SiC外延基板在作为半导体芯片的制造工序之一的光刻中,能够抑制掩模图案相对于基板主面的垂直方向上的偏移,能够提高半导体芯片的制造成品率。

## 附图说明

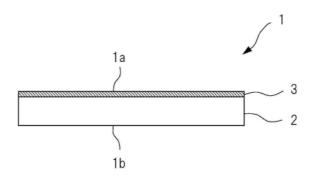

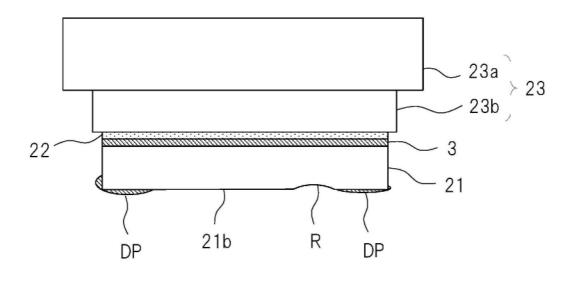

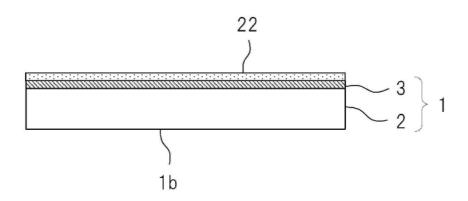

[0020] 图1是一个实施方式的SiC外延基板的侧视图。

[0021] 图2是表示在图1的SiC外延基板中对评价平坦性的位点进行划分的一个例子的图。

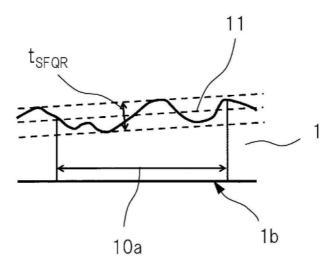

[0022] 图3是用于对SBIR的测定方法进行说明的图。

[0023] 图4是用于对SFQR的测定方法进行说明的图。

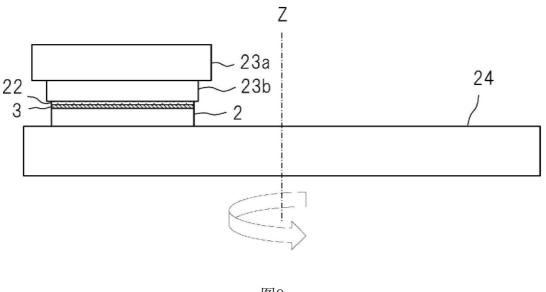

[0024] 图5是用于对一个实施方式的SiC外延基板的制造方法进行说明的图。

[0025] 图6是用于对一个实施方式的SiC外延基板的制造方法进行说明的图。

[0026] 图7是用于对一个实施方式的SiC外延基板的制造方法进行说明的图。

[0027] 图8是用于对一个实施方式的SiC外延基板的制造方法进行说明的图。

[0028] 图9是用于对一个实施方式的SiC外延基板的制造方法进行说明的图。

[0029] 图10是用于对一个实施方式的SiC外延基板的制造方法进行说明的图。

[0030] 附图标记说明

[0031] 1:SiC外延基板;1a、1b:主面;2、21:碳化硅基板;3:外延膜;10:位点;22:保护膜;23:真空卡盘;23a:底板;23b:吸附板;24:研磨平板。

#### 具体实施方式

[0032] 以下,对作为本发明的一个实施方式的SiC外延基板及其制造方法进行说明。

[0033] 其中,在用于对本实施方式进行说明的全部附图中,原则上对相同的部件标注相同的符号,并省略其重复的说明。另外,为了容易理解附图,即使是俯视图,有时也标注剖面线,即使是截面图,有时也省略剖面线。

[0034] <研究过程>

[0035] 首先,为了对本实施方式进行说明,对现有技术的问题进行补充说明。例如在上述现有技术中所说明的专利文献1中,除了上述所说明的确保平坦性以外,如下所述,在实用

上也存在成为技术问题的方面。

[0036] 例如在该专利文献1所记载的SiC外延基板的制造方法中,在碳化硅基板上,在形成外延膜之前先形成保护膜,之后再进行外延生长。并且,之后通过保护膜的揭开剥离 (lift-off)除去附着于背面的物质。但是,在该方法中,由于在带有保护膜的状态下进行外延生长,因此无法使用抗蚀剂等有机物作为保护膜。

[0037] 另外,在该专利文献1中,为了将外延生长后的保护膜揭开剥离(lift-off),使用各向异性蚀刻、Wet蚀刻,但在这种情况下,附着物可能成为障碍,导致保护膜部分残留。

[0038] 另外,在除去保护膜时也考虑了使用胶带剥离,但在这种情况下,由于胶带的密合力不一致、或者在进行剥离时作用力不一致,仍然可能导致保护膜部分残留,还可能产生胶带残渣等污染物。

[0039] 在本发明中,除了在上述所要解决的技术问题中记载的平坦性以外,关于如上所述在专利文献1中成为技术问题的保护膜,还对更简便地形成和除去该保护膜、并且能够抑制残留等发生的技术进行了研究。以下,将这一点也包括在内对本实施方式的技术思想进行详细说明。

[0040] <SiC外延基板>

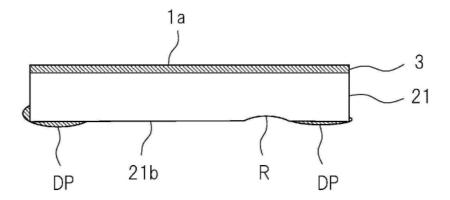

[0041] 本实施方式的SiC外延基板例如图1所示,可以列举在碳化硅基板2的表面形成有外延膜3的SiC外延基板1。该SiC外延基板1是平板状的基板,具有由外延膜3构成的主面1a (第一主面)和作为其相反面的主面1b (第二主面)。在本说明书中,有时也将由该外延膜3构成的面(主面1a)或形成外延膜3的碳化硅基板2的面称为"正面",将该正面的相反面称为"背面"。

[0042] 碳化硅基板2是由单晶的碳化硅(SiC)构成的基板。其中,在本实施方式中,是制成SiC外延基板1时的平坦性如后所述地满足规定范围的良好的基板。

[0043] 外延膜3是在碳化硅基板2的正面使碳化硅外延生长而成的外延膜。

[0044] 该SiC外延基板1的大小没有特别限定,在制造半导体芯片时,如果考虑其效率性等,则基板的直径优选为150mm以上,更优选为200mm以上。

[0045] 如上所述,SiC外延基板1在碳化硅基板2的表面形成有外延膜3,在该基板的平坦性非常好的方面具有特征。

[0046] 关于SiC外延基板1的平坦性,具体着眼于SBIR(Site Back Surface Referenced Ideal Ranges、位点背面基准理想范围),发现了该特性变得良好的新的制造方法,因此能够得到平坦性极好的SiC外延基板1。

[0047] 即,关于本实施方式的SiC外延基板1的SBIR,在SiC外延基板1的主面1b上,满足以10mm见方的位点为基准时的最大值在0.1μm以上1.5μm以下的条件。

[0048] 这样,通过使SBIR处于规定的范围,本实施方式的SiC外延基板1作为基板的平坦性良好,在制造半导体芯片时,能够使芯片的制造成品率变得良好。更具体而言,在进行光刻工序时,在SiC外延基板1的外延膜3上形成掩模图案,但由于SiC外延基板1的平坦性良好,因此所形成的掩模图案成为所希望的图案,能够抑制在垂直方向上相对于基板的主面发生偏移。因此,在使用该SiC外延基板1制造半导体芯片时,与掩模图案的偏移变得非常小,因此能够提高其制造成品率。

[0049] 另外,该SBIR在0.5µm以下的位点比率优选为65%以上。如果满足这样的位点比率

的条件,则在SiC外延基板1中,平坦性非常好,能够进一步提高半导体芯片的制造成品率。

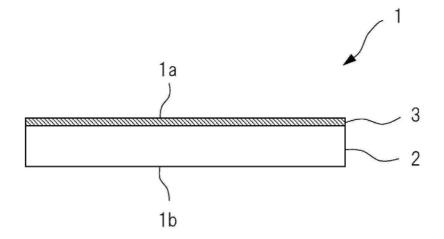

[0050] 其中,上述位点比率是在SiC外延基板1上如图2所示划分位点时,由SBIR为0.5μm以下的位点数相对于全部位点数之比(SBIR为0.5μm以下的位点数/全部位点数)算出的比率。

[0051] 在测定该SBIR时,首先,如图2所示,在SiC外延基板1上,例如将10mm见方的大小作为1个位点(评价区域),划分确定多个位点10。以该10mm见方的位点为基准,如下所述求出SBIR。其中,在本实施方式中,显示了设定10mm见方的位点的例子,以该位点为基准评价平坦性,但该位点的大小能够任意变更。

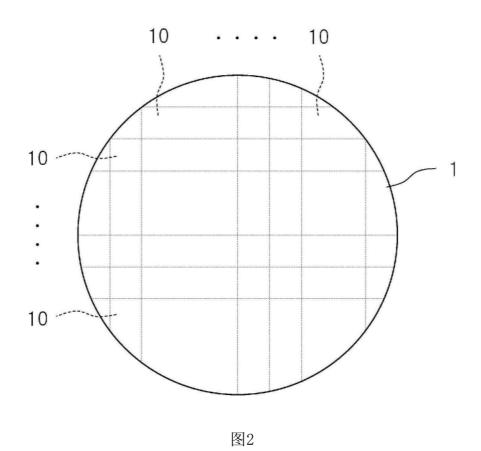

[0052] 接着,如图3所示,将SiC外延基板1的作为测定对象的主面1b的相反面主面1a吸附并固定于平坦面,从而使主面1a平坦。其中,图3中的箭头10a示意性地表示了正方形位点中的一条边的长度。SBIR是规定范围(例如10mm见方的范围)的位点中的以主面1b为基准的位点表面上的最高点的高度与最低点的高度之差(图3中用箭头t<sub>SRIR</sub>表示的高度差)。

[0053] 在本实施方式中,SBIR的最大值优选为1.5µm以下,该值越小对焦精度越高,因而优选。利用本实施方式,在将SiC外延基板1划分成以10mm见方为单位的多个位点时,特别优选最大值为上述范围(0.1µm以上1.5µm以下),并且SBIR在0.5µm以下的位点比率为65%以上。通过满足这样的条件,能够精度良好地进行光刻加工,并能够提高所得到的半导体芯片的制造成品率。另外,上述位点比率越高越好,由此,还能够在应用光刻加工时实现更微细的配线图案。通过提高平坦性,能够使用曝光波长短且DOF(Depth of Focus,聚焦深度)的范围小、即焦点深度浅的曝光装置,并能够实现更微细的配线图案,因而更优选。

[0054] 另外,关于SiC外延基板1的平坦性,还发现SFQR(Site Front side least sQuares focal plane Range、位点正面最小二乘焦平面范围),能够得到该特性也好的制品。

[0055] 即,本实施方式的SiC外延基板1的SFQR在SiC外延基板1的主面1a上,满足以10mm 见方的位点为基准时的最大值为0.1µm以上1.5µm以下的条件。

[0056] 这样,通过使SFQR处于规定的范围,本实施方式的SiC外延基板1作为基板的平坦性更好,在制造半导体芯片时,能够使芯片的制造成品率良好。更具体而言,在进行光刻工序时,在SiC外延基板1的外延膜3上形成掩模图案,但由于SiC外延基板1的平坦性良好,因此所形成的掩模图案成为所希望的图案,能够抑制垂直方向上相对于基板的主面发生偏移。因此,在使用该SiC外延基板1制造半导体芯片时,能够使与掩模图案的偏移非常小,因此能够提高其制造成品率。

[0057] 另外,该SFQR在0.3µm以下的位点比率优选为85%以上。如果满足这样的位点比率的条件,则在SiC外延基板1上平坦性非常好,能够进一步提高半导体芯片的制造成品率。

[0058] 其中,上述位点比率是在SiC外延基板1上如图2所示划分位点时,由SFQR为0.3µm以下的位点数相对于全部位点数之比(SFQR为0.3µm以下的位点数/全部位点数)算出的比率。

[0059] 在测定该SFQR时,首先,与上述SBIR的测定同样,如图2所示,在SiC外延基板1上,例如将10mm见方的大小作为1个位点(评价区域),划分确定多个位点10。以该10mm见方的位点为基准,如下所述求出SFQR。其中,在本实施方式中,设定了10mm见方的位点,以该位点为基准评价平坦性,但该位点的大小能够任意变更。

[0060] 接着,如图4所示,将SiC外延基板1的作为测定对象的主面1a的相反面主面1b吸附并固定于平坦面,从而使主面1b平坦。其中,图4中的箭头10a示意性地表示了正方形位点中的一条边的长度。SFQR是在该状态下使用最小二乘法,基于规定范围(例如10mm见方的范围)的位点的表面形状算出基准面11,从该基准面11至所测定的位点表面上的最高点的距离与从该基准面11至位点表面上的最低点的距离的合计(图4中用箭头t<sub>CFOR</sub>表示的距离)。

[0061] 在本实施方式中,SFQR的最大值优选为1.5µm以下,该值越小,在利用步进器(缩小投影曝光装置)进行曝光时的对焦精度越高,因而优选。利用本实施方式,在将SiC外延基板1划分成以10mm见方为单位的多个位点时,优选最大值为上述范围(0.1µm以上1.5µm以下),并且SFQR在0.3µm以下的位点比率为85%以上。通过满足这样的条件,能够精度良好地进行光刻加工,并能够提高所得到的半导体芯片的制造成品率。另外,上述位点比率越高越好,由此,在应用光刻加工时,也能够实现更微细的配线图案。

[0062] <SiC外延基板的制造方法>

[0063] 接着,以上述所说明的SiC外延基板1为例,对本实施方式的SiC外延基板的制造方法进行详细说明。

[0064] (a) 基板的准备工序

[0065] 首先,准备板状的碳化硅基板((a)工序)。如图5所示,该工序是准备碳化硅基板21的工序。该图5是示意性地表示碳化硅基板21的侧面的图。该碳化硅基板21是构成SiC外延基板1的碳化硅基板2的材料,是平板状的碳化硅基板。

[0066] 如上所述,该碳化硅基板21为平板状,具有主面21a和主面21b。此时,将主面21a作为使碳化硅外延生长的面,主面21b为其相反面(通过研磨或研削进行加工的面)。

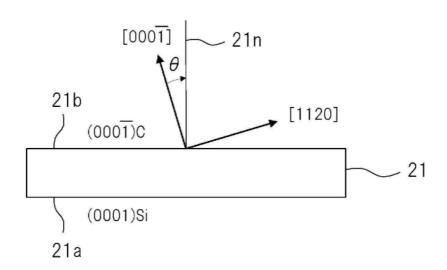

[0067] 此处所准备的碳化硅基板21优选为具有偏角 $\theta$ 的偏角基板。具体而言,优选主面21b、或主面21b的法线21n从[000-1]方向向[1120]方向倾斜角度 $\theta$ 。该偏角 $\theta$ 优选为0.5°以上8°以下,更优选为0.5°以上5°以下。

[0068] 在准备上述碳化硅基板21时,首先,利用线锯将碳化硅单晶的坯料切成板状。然后,因为线锯的切断面产生了波纹或凹凸,所以使用金刚石研削磨石或金刚石浆料等选择性地除去凹凸部分,使其平坦化。

[0069] 优选对平坦化后的碳化硅基板的主面21a实施CMP(化学机械研磨)。具体而言,优选利用CMP进行研磨,直至第一主面的表面粗糙度Ra成为1nm以下。更优选主面21a的表面粗糙度Ra为0.2nm以下。

[0070] 表面粗糙度Ra例如可以利用白色干涉显微镜进行测定。例如是对于主面21a以100 μm长测定3处,取平均而得到的值。表面粗糙度Ra理想地也可以为0nm,但现实中表面粗糙度Ra不可能达到0nm。因此,表面粗糙度Ra的优选范围的下限值大于0。其中,本说明书中的表面粗糙度Ra是JIS B 0601-2001所规定的表面粗糙度Ra。

[0071] 另外,此时所准备的碳化硅基板21为了在主面21a进行外延生长,优选使其表面粗糙度Ra为0.2nm以下。这样,通过形成平滑的面,由后述外延生长所形成的外延膜也能够成为具有延续了其平滑性的优选面的膜。

[0072] 另一方面,主面21b在后述的形成外延膜的工序中有时会形成附着物或者产生龟裂,是再之后在后述的研磨或研削的工序中除去其表层,重新形成平滑面的面。因此,在上述(a)工序所准备的碳化硅基板21中,该主面21b不需要预先进行用于提高平滑性的加工。

即,该主面21b例如可以是其表面粗糙度Ra为200nm以上的粗糙的面。

[0073] 这样,在碳化硅基板21中,以一面为平滑面、另一方为粗糙不平滑的面的状态准备即可,不需要准备两面均为平滑面的基板,因此就这一点而言,能够降低制造成本。

[0074] (b) 外延膜的生长工序

[0075] 接着,在(a)工序中准备的碳化硅基板的表面使碳化硅外延生长,形成第一主面,该第一主面形成有外延膜((b)工序)。该工序是在准备好的碳化硅基板21的主面21a形成外延膜3的工序。

[0076] 该外延膜3的形成可以列举如下的方法。例如将碳化硅基板21载置在涂布了SiC的板上,将其设置于涂布了SiC的基座内,利用感应加热等对板和基座进行加热,从而将碳化硅基板21的温度升温至碳化硅能够外延生长的温度、例如1500℃以上1700℃以下。

[0077] 一边维持该加热状态,一边在减压下流入作为载气的氢气、以及作为原料气体的单硅烷和丙烷等、作为掺杂气体的氮气等的混合气体,在碳化硅基板21的表面使碳化硅外延生长。

[0078] 由此,能够在碳化硅基板21的主面21a上形成外延膜3,如图6所示,能够得到外延膜3堆积于碳化硅基板21的整个主面21a的基板。如此形成的外延膜3的表面成为最终得到的SiC外延基板1的主面1a。

[0079] 此时所得到的外延膜3的厚度可以根据半导体器件所需求的性能任意设定。作为外延膜3的厚度,例如可以为1μm以上100μm以下。

[0080] 另外,此时,在碳化硅基板21的主面21a以外的面有时因SiC的外延生长而形成附着物DP。另外,碳化硅基板21有时形成龟裂R。在本实施方式中,即使形成这样的附着物DP或龟裂R,也不会对最终得到的SiC外延基板造成影响,其理由在后述的(d)研削或研磨加工工序中说明。

[0081] (c) 保护膜的形成工序

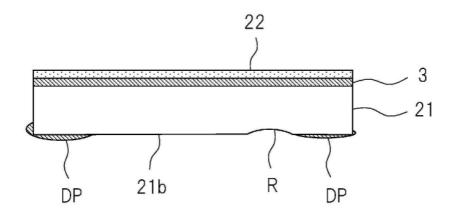

[0082] 接着,在(b)工序中形成的外延膜的表面形成保护膜((c)工序)。在该工序中,在通过上述(b)工序而形成于碳化硅基板21的主面21a上的外延膜3的表面形成保护膜。利用该(c)工序,如图7所示,在外延膜3上形成保护膜22。

[0083] 在本实施方式中,在形成外延膜3后形成保护膜22,保护膜不会如上述专利文献1 所记载的那样暴露在高温的条件下,不需要高温耐受性,能够没有特别限定地使用公知的 保护膜,可以使用宽泛的保护膜。

[0084] 在此所形成的保护膜22,可以通过将液态材料涂布在外延膜3上并干燥,形成具有一定膜厚的保护膜,也可以预先以一定的膜厚形成保护膜,再将其粘贴到外延膜3上。

[0085] 在使用液态材料的情况下,可以应用公知的薄膜形成技术,例如可以列举旋涂、浸涂、喷涂等方法,其中,从容易形成均匀膜厚的保护膜的方面考虑,优选旋涂。此时所使用的液态材料的粘度优选为100mPa•s以下,更优选为50mPa•s以下。

[0086] 另外,在本实施方式中,特别优选使用能够减轻对基板的负荷并良好地保持平坦性的材料。作为这样的保护膜22的材料,可以列举抗蚀剂、液体蜡等。利用这些材料,容易形成保护膜22,其除去也能够以简易的操作进行,从而优选。

[0087] 在此能够使用的抗蚀剂只要能够保护外延膜3就没有特别限定,可以使用公知的抗蚀剂,例如可以列举0FPR-800、500、8600、8600LB、TSMR-8900、V90(以上均由东京应化

工业株式会社生产,商品名)等正型抗蚀剂。该正型抗蚀剂例如含有乳酸乙酯、乙酸丁酯等成分。

[0088] 在此能够使用的液体蜡只要能够保护外延膜3就没有特别限定,可以使用公知的液体蜡,例如可以列举SKYLIQUID LA-3011H、4011H、5011H、5511H(以上均由日化精工株式会社生产,商品名)等。该液体蜡例如含有松香、异丙醇(IPA)等成分。

[0089] 通过使用上述那样的抗蚀剂或液体蜡,无需如专利文献1所记载的那样进行各向异性蚀刻或Wet蚀刻,能够通过简便的操作除去保护膜,还能够抑制保护膜的残留。

[0090] 在本实施方式中,为了获得平坦性,使用液态材料。假如粘贴膜而形成保护膜,则由于膜较厚,平坦性可能不均匀。通过利用例如旋涂等形成液态材料而制成保护膜,能够将面内的膜厚分布控制在例如20%以下,由此能够获得预期的平坦性。

[0091] (d)研削或研磨加工工序

[0092] 然后,在形成保护膜后,对碳化硅基板21的主面21a的相反面21b以外延膜3的表面(主面1a)的形状为基准进行研削或研磨加工,形成主面1b((d)工序)。

[0093] 关于该加工工序,以下,以研磨的情况为例进行说明。在该研磨中,首先,通过吸附或粘接等将保护膜22侧的面与具有碳化硅基板21、外延膜3和保护膜22的基板固定。如图8 所示,例如用于固定的真空卡盘23由底板23a和吸附板23b构成,与未图示的真空装置连接。利用该真空装置,通过其吸引作用,能够将基板固定在吸附板23b的表面。

[0094] 如此固定了作为研磨加工对象的碳化硅基板21的真空卡盘23如图9所示,将其研磨面面向单面研磨机的研磨平板24配置,并使其与研磨平板24接触,从而能够研磨成所希望的形状。其中,研磨平板24例如以沿着铅直方向设置的Z轴为中心进行旋转。

[0095] 该工序中的研磨只要是能够对碳化硅基板21进行研磨的方法即可,可以利用公知的方法进行,没有特别限定。另外,单面研磨机优选能够调整按压力。

[0096] 在该研磨加工中,可以向研磨平板24滴加金刚石浆料,保持主面1a并将主面1b按压在研磨平板24上。研磨平板24可以使用金属平板或聚氨酯系垫、无纺布垫等。

[0097] 此时,研磨平板24的转速优选为10rpm以上30rpm以下,按压力优选为5kPa以上20kPa以下,使用金刚石浆料的金刚石粒径为0.5μm以上5μm以下的浆料。另外,优选研磨量为1μm以上10μm以下,研磨面的表面粗糙度Ra为0.3nm以上1nm以下。

[0098] 其中,在碳化硅那样的高硬度材料的基板的研磨中,可以应用使用游离磨粒的加工(抛光加工)、或使用固定磨粒的加工(研磨加工)、使用金刚石轮的加工等。

[0099] 另外,以上以研磨为例进行了说明,但也可以使用研削盘进行加工。在使用研削盘的情况下,也同样保持形成有保护膜22的主面1a侧,进行主面1b的研削即可。保持方法同上,可以一边保持主面1a使主面1b与研削磨石接触,一边给予一定量的切入进行研削。

[0100] 研削磨石含有金刚石磨粒,其粒度优选为#2000以上#8000以下。研削磨石例如可以使用陶瓷粘接磨石、树脂粘接磨石。

[0101] 磨石的转速优选为2000rpm以上5000rpm以下,切入优选为0.2μm/min以上2μm/min以下。在研削磨石的冷却中,使用纯水或含有添加剂的水,研削量为1μm以上10μm以下、研磨面的表面粗糙度Ra为0.3nm以上1nm以下即可。

[0102] 另外,在这样的研削、研磨加工后,为了除去研磨伤,还可以根据需要进行CMP(抛光)。另外,在要求更平滑的表面的情况下,也可以实施CMP(抛光)。

[0103] 另外,该研磨加工以主面1a的形状为基准进行。此时,优选加工成与主面1a的形状对应的面,得到主面1b。形成如此对应的面时,SiC外延基板1的厚度是几乎相同的厚度,其形状在正面和背面相对应的位置具有同样的倾斜,因此能够得到平坦性非常好的基板。

[0104] 在本实施方式中,对于SiC外延基板不进行双面加工,而是进行了单面加工。双面加工因为外延膜的膜面也被研磨,所以难以控制外延膜的膜厚,但单面加工在能够控制外延膜的膜厚方面优异。

[0105] 如此得到的SiC外延基板1能够满足上述本实施方式所说明的SiC外延基板的特性、例如SBIR和SFQR。

[0106] 另外,在本发明的SiC外延基板中,外延膜优选基底面位错密度(BPD密度)为0.01cm<sup>-2</sup>以下,更优选基底面位错密度为0.001cm<sup>-2</sup>以下,特别优选基底面位错密度为零。满足上述的SBIR和SFQR并且位点比率高时,能够抑制形成于外延膜的元件不良,因此能够抑制针对该元件制作具有基底面位错密度低的外延膜的SiC外延基板所需的工时浪费。另外,外延膜也可以具有缓冲层和漂移层。上述缓冲层可以由2层以上构成(例如具有低浓度层和空穴阻挡层),作为空穴阻挡层,优选具有杂质浓度例如为5×10<sup>18</sup>cm<sup>-3</sup>以上1×10<sup>19</sup>cm<sup>-3</sup>以下并且基底面位错密度为0cm<sup>-2</sup>以上0.01cm<sup>-2</sup>以下的层。

[0107] 研磨加工结束后,从真空卡盘23上取下,如图10所示,得到形成有主面1b的带保护膜22的SiC外延基板1。

[0108] (e) 保护膜的除去工序

[0109] 然后,在(d)工序之后,从图10所示的带保护膜22的SiC外延基板1除去保护膜22((e)工序)。通过进行该(e)工序,能够得到SiC外延基板1。保护膜的除去可以通过根据所使用的保护膜的材料进行适于其除去的方法而实现。

[0110] 在使用抗蚀剂作为保护膜的情况下,使用能够将所使用的抗蚀剂剥离的溶剂或剥离液即可,例如可以列举丙酮、N- 甲基-2- 吡咯烷酮 (NMP)等有机溶剂、剥离液-104、105、106、502A、SST-A47、Klean Strip HP、Klean Strip HP-2 (以上均由东京应化工业株式会社生产,商品名)等。

[0111] 在使用液体蜡作为保护膜的情况下,可以列举利用刮刀的除去、利用碱清洗的除去等。作为清洗剂,例如可以列举DEVEL、KILALACLEAN(以上均由日化精工株式会社生产,商品名)。

[0112] 将上述那样的清洗剂或剥离液收纳在保护膜除去槽内,在其中配置结束了(d)工序的碳化硅基板。清洗剂或剥离液的温度没有特别指定,适合在常温(20℃附近)以上60℃以下使用。

[0113] 剥离时间为2分钟以上10分钟以下,剥离后的基板被冲洗,使其不残留剥离液的残渣。利用旋转干燥机等使冲洗后的基板干燥。如此,能够得到目标SiC外延基板1。

[0114] 在该保护膜的除去工序中,为了高效地除去保护膜22,可以对保护膜除去槽施加超声波振动(例如45kHz-600W),还可以将配置于保护膜除去槽内的碳化硅基板在除去槽内上下摇动。

[0115] 除去保护膜后的SiC外延基板1在对必要的检查项目进行检查后,满足规定特性的基板用于半导体芯片的制造工序。特别是在上述中,在将抗蚀剂或液体蜡作为保护膜的情况下,也能够非常良好地进行其除去,所得到的SiC外延基板1的基板面上的残留物能够小

于0.1个/cm²,能够得到非常好的制品。

[0116] 如此得到的SiC外延基板1是上述说明的平坦性良好的基板,能够显著提高后续的半导体芯片的制造成品率。

[0117] 实施例

[0118] 以下,参照实施例对本实施方式的单晶制造装置和单晶制造方法进行详细说明。 但本发明的解释当然并不限定于该实施例的记载。

[0119] (实施例1)

[0120] 准备主面21a为(0001)Si面且偏角 $\theta$ 为4°的直径150mm的碳化硅基板21。对主面21a 实施CMP至表面粗糙度Ra达到0.5nm以下(主面1b的表面粗糙度Ra为约2nm)。

[0121] 之后,在碳化硅基板的主面21a上使碳化硅外延生长,形成厚度10μm的外延膜3。生长温度设定为1600℃,生长时的生长室内的压力设定为30kPa。将原料气体中的C/Si设定为1.25或1.4。载气使用氢气,作为原料气体,使用丙烷和硅烷。另外,作为掺杂剂源,使用氮气。

[0122] 接着,在形成于碳化硅基板21表面的外延膜3的表面(主面1a)上成型保护膜22。在保护膜的成型中,使用旋涂机(东京毅力科创株式会社制造、商品名:CLEAN TRACK Mark),作为保护膜,使用正型抗蚀剂(东京应化株式会社生产、商品名:OFPR-8600LB)。该抗蚀剂的成分含有乳酸乙酯、乙酸丁酯等。

[0123] 将保护膜的成型条件设定为基板转速:1500rpm、旋转时间:30sec、涂布量:3.6mL、烘干温度:140度、烘干时间:120sec、冷却时间:60sec,形成厚度约1μm的均匀厚度的膜。

[0124] 接着,保持形成有保护膜22的主面1a,进行主面21b的研磨。关于保持方法,以在研磨中姿势不发生变化的方式,通过真空吸附进行固定,使用单面研磨机(不二越机械株式会社制造、商品名:SLM-35),以主面1a为基准,对主面21b进行研磨至表面粗糙度Ra达到0.5nm,形成主面1b。

[0125] 主面21b的研磨结束后,进行保护膜22的剥离。将保护膜的剥离液NMP储存在保护膜除去槽内,将结束了背面研磨后的碳化硅基板浸渍、配置在保护膜除去槽中。

[0126] 剥离液的温度为60℃,进行5分钟浸渍,使保护膜剥离。利用冲洗液对剥离后的基板进行冲洗,除去剥离液的残渣后,利用旋转干燥机使基板干燥,得到SiC外延基板1。

[0127] (比较例1)

[0128] 除了在实施例1中不进行主面21a的研磨(背面研磨)以外,利用与实施例1相同的操作,制作SiC外延基板。

[0129] 「平坦性的评价]

[0130] 准备上述实施例1和比较例1所得到的SiC外延基板各100片,作为各基板的平坦性的评价,测定SBIR和SFQR。考查分别测定100片时的最大值、平均值,关于SBIR考查0.5μm以下和0.8μm以下的位点比率,关于SFQR考查0.3μm以下和0.5μm以下的位点比率。将其结果汇总示于表1。

[0131] 「表1]

[0132]

|      |               | 实施例 1  | 比较例 1  |

|------|---------------|--------|--------|

| SBIR | 平均值           | 0.15µm | 0.48µm |

|      | 最大值           | 0.93µm | 1.80µm |

|      | 0.5μm 以下的位点比率 | 99%    | 62%    |

|      | 0.8μm 以下的位点比率 | 100%   | 91%    |

| SFQR | 平均值           | 0.09µm | 0.23μm |

|      | 最大值           | 0.76µm | 1.32µm |

|      | 0.5µm 以下的位点比率 | 98%    | 80%    |

|      | 0.8μm 以下的位点比率 | 99.7%  | 98%    |

[0133] (实施例2)

[0134] 除了在实施例1中使用液体蜡作为保护膜以外,利用相同的操作制造SiC外延基 板。

[0135] 这里所使用的液体蜡使用含有松香、异丙醇(IPA)的液体蜡(日化精工株式会社生 产、商品名:SKYLIQUID LA-3011H),并使用涂布装置(不二越机械株式会社制造、商品名: SCMM-7).

[0136] 将保护膜的成型条件设定为基板转速:2500rpm、旋转时间:10sec、涂布量:2mL、烘 干温度:95度、烘干时间:20sec、冷却时间:60sec,形成厚度约2µm的均匀厚度的膜。

[0137] 能够确认该实施例2所得到的SiC外延基板也具有与实施例1同等的平坦性。

[0138] 根据以上的结果可知,利用本实施方式的SiC外延基板及其制造方法,能够利用简 便的操作可靠地得到平坦性非常优异的SiC外延基板。

[0139] 以上,基于实施方式对本发明的发明人所完成的发明进行具体说明,但本发明并 不限定于上述实施方式,当然能够在不脱离其要旨的范围内进行各种变更。

图1

图3

图4

图5

图6

图7

图8

图9

图10