# (19) 国家知识产权局

# (12) 发明专利

(10) 授权公告号 CN 107658274 B (45) 授权公告日 2022. 12. 27

(21)申请号 201710450368.1

(22) 申请日 2017.06.15

(65) 同一申请的已公布的文献号 申请公布号 CN 107658274 A

(43) 申请公布日 2018.02.02

(30) 优先权数据

62/366,295 2016.07.25 US 15/371,869 2016.12.07 US

(73) 专利权人 台湾积体电路制造股份有限公司 地址 中国台湾新竹市新竹科学工业园力行 六路8号

(72) 发明人 洪瑞斌 许峰诚 陈硕懋 郑心圃 廖德堆

(74) 专利代理机构 北京律盟知识产权代理有限 责任公司 11287

专利代理师 路勇

(51) Int.CI.

**H01L 23/31** (2006.01)

H01L 23/528 (2006.01)

*H01L* 21/56 (2006.01)

H01L 21/60 (2006.01)

(56) 对比文件

US 2013/0292831 A1,2013.11.07

US 2015/0228580 A1,2015.08.13

US 2014/0103488 A1,2014.04.17

US 2013/0093078 A1,2013.04.18

US 2008/0017968 A1,2008.01.24

US 2011/0237004 A1,2011.09.29

US 2015/0318262 A1,2015.11.05

US 2011/0129960 A1,2011.06.02

审查员 杨帆

权利要求书5页 说明书9页 附图19页

#### (54) 发明名称

半导体封装结构及其制造方法

#### (57) 摘要

本揭露提供一种半导体封装结构及其制造方法。一种半导体封装结构包含重布层RDL、芯片、多个互连凸块及囊封物。所述重布层具有彼此相对的第一表面及第二表面。所述芯片在多个接点垫面对所述第一表面的情况下放置在所述重布层上方且电连接到所述重布层。所述互连凸块放置在所述第一表面上方且电连接到所述重布层的所述第一表面上方,且所述囊封物封围所述芯片并环绕所述互连凸块的侧向壁。本揭露提供的半导体封装结构及其制造方法能够使半导体封装结构的总体厚度减小。

1.一种半导体封装结构,其包括:

重布层RDL,其具有彼此相对的第一表面及第二表面;

芯片,其在多个接点垫面对所述第一表面的情况下放置在所述重布层上方且电连接到 所述重布层:

多个互连凸块,其放置在所述第一表面上方且电连接到所述重布层;

第二重布层,其在所述重布层的所述第二表面下方,其中所述第二重布层具有彼此相对的第三表面及第四表面且所述第三表面面对所述第二表面:

多个第二芯片,其放置在所述第二重布层上方且电连接到所述第二重布层,其中所述 多个第二芯片包含面对所述第二重布层的所述第三表面的多个接点垫,所述多个第二芯片 与所述重布层分离,所述多个第二芯片与所述第二重布层分离,所述多个第二芯片包括主 动装置芯片及被动装置芯片,所述主动装置芯片及所述被动装置芯片的厚度不同,所述主 动装置芯片及所述被动装置芯片通过所述第二重布层彼此电通信;

囊封物,其放置在所述重布层的所述第一表面上方,其中所述囊封物封围所述芯片且环绕所述多个互连凸块的侧向壁;及

多个第二互连凸块,其在所述第二表面与所述第三表面之间,且电连接到所述重布层及所述第二重布层,其中所述多个互连凸块中的每一个及所述多个第二互连凸块中的每一个为焊料球。

- 2.根据权利要求1所述的半导体封装结构,其进一步包括放置在所述第二重布层的所述第四表面下方的电路板,及放置在所述第四表面与所述电路板之间以电连接所述第二重布层与所述电路板的多个外部连接器。

- 3.根据权利要求1所述的半导体封装结构,其进一步包括放置在所述囊封物上方,且透过所述多个互连凸块电连接到所述重布层的封装。

- 4.根据权利要求1所述的半导体封装结构,其中所述多个互连凸块中的每一个的两个相对端子从所述囊封物暴露。

- 5.根据权利要求1所述的半导体封装结构,其中所述芯片包括有源装置芯片及无源装置芯片。

- 6.一种半导体封装结构,其包括:

- 第一重布层RDL,其具有彼此相对的第一表面及第二表面;

- 第一芯片,其在多个接点垫面对所述第一表面的情况下放置在所述第一重布层上方且电连接到所述第一重布层:

多个第一互连凸块,其放置在所述第一表面上方且电连接到所述第一重布层;

第一囊封物,其放置在所述第一重布层的所述第一表面上方,其中所述第一囊封物封围所述第一芯片且环绕所述多个第一互连凸块的侧向壁;

第二重布层,其在所述第一重布层的所述第二表面下方,其中所述第二重布层具有彼此相对的第三表面及第四表面且所述第三表面面对所述第二表面;

多个第二芯片,其在多个接点垫面对所述第三表面的情况下放置在所述第二重布层上方,其中所述多个第二芯片包括主动装置芯片及被动装置芯片,所述主动装置芯片及所述被动装置芯片的厚度不同,所述主动装置芯片及所述被动装置芯片通过所述第二重布层彼此电通信;

多个第二互连凸块,其放置在所述第三表面上方且电连接到所述第二重布层;及

第二囊封物,其放置在所述第一重布层与所述第二重布层之间,其中所述第二囊封物 封围所述多个第二芯片且环绕所述多个第二互连凸块的侧向壁,所述多个第二芯片通过所 述第二囊封物与所述第一重布层分离,且所述多个第一互连凸块中的每一个及所述多个第 二互连凸块中的每一个为焊料球。

- 7.根据权利要求6所述的半导体封装结构,其进一步包括放置在所述第二重布层的所述第四表面下方的电路板,及放置在所述第四表面与所述电路板之间以电连接所述第二重布层与所述电路板的多个外部连接器。

- 8.根据权利要求6所述的半导体封装结构,其进一步包括放置在所述第一囊封物上方, 且透过所述多个第一互连凸块电连接到所述第一重布层的封装。

- 9.根据权利要求6所述的半导体封装结构,其中所述多个第一互连凸块中的每一个的两个相对端子从所述第一囊封物暴露。

- 10.根据权利要求6所述的半导体封装结构,其中所述多个第二互连凸块中的每一个的两个相对端子从所述第二囊封物暴露。

- 11.根据权利要求6所述的半导体封装结构,其进一步包括放置在所述第二囊封物中的 多个导电柱,且所述多个导电柱电连接到所述第二重布层。

- 12.根据权利要求6所述的半导体封装结构,其中所述第一芯片包括存储器芯片及被动装置芯片。

- 13.根据权利要求6所述的半导体封装结构,其进一步包括放置在所述第四表面下方且电连接到所述第二重布层的第三芯片。

- 14.一种半导体封装结构,其包括:

重布层RDL,其具有彼此相对的第一表面及第二表面;

多个芯片,其在多个接点垫面对所述第一表面的情况下放置在所述重布层上方且电连接到所述重布层,其中所述多个芯片包括主动装置芯片及被动装置芯片,所述主动装置芯片及所述被动装置芯片的厚度不同,所述主动装置芯片及所述被动装置芯片通过所述重布层彼此电通信;

多个导电柱,其放置在所述第一表面上方且电连接到所述重布层;

多个互连凸块,其放置在所述多个导电柱上方,其中所述多个互连凸块中的每一个连接到所述多个导电柱中的每一个,所述多个导电柱中的每一个的一个端子连接到所述重布层,且所述多个导电柱中的每一个的另一端子连接到所述多个互连凸块中的对应互连凸块,所述多个导电柱的上表面与所述主动装置芯片的上表面实质上水平,所述多个导电柱及所述多个互连凸块的总体高度高于所述主动装置芯片的高度;及

囊封物,其放置在所述重布层的所述第一表面上方,其中所述囊封物封围所述多个芯片且环绕所述多个互连凸块的侧向壁及所述多个导电柱的侧向壁,且所述多个互连凸块的上表面与所述囊封物的上表面实质上水平。

- 15.根据权利要求14所述的半导体封装结构,其进一步包括放置在所述重布层的所述 第二表面下方的电路板,及放置在所述第二表面与所述电路板之间以电连接所述重布层与 所述电路板的多个外部连接器。

- 16.根据权利要求14所述的半导体封装结构,其进一步包括放置在所述囊封物上方,且

透过所述多个互连凸块及所述多个导电柱电连接到所述重布层的封装。

17.根据权利要求14所述的半导体封装结构,其进一步包括放置在所述第二表面下方 且电连接到所述重布层的第二芯片。

18.一种用于制造半导体封装结构的方法,其包括:

在第一载体衬底上方形成第一重布层;

在所述第一重布层上方放置多个第一芯片;

利用多个第一互连凸块将多个封装电连接到所述第一重布层;

在所述多个封装与所述第一重布层之间形成第一囊封物,其中所述第一囊封物是成型 底胶填充层,所述第一囊封物的一部分形成在所述多个第一芯片与所述第一重布层之间;

将所述多个封装附接到暂时衬底,其中所述暂时衬底是挠性膜,所述挠性膜固定在框架上,所述多个封装直接接触所述暂时衬底:

将所述第一重布层划分成若干片,其中所述第一重布层的每一片连接到所述多个封装中的对应封装;

从所述暂时衬底拆卸所述多个封装中的每一个以及对应的所述第一重布层的所述片; 在第二载体衬底上方形成第二重布层;

在所述第二重布层上方放置多个第二芯片,其中所述多个第二芯片包含主动装置芯片 及被动装置芯片,所述主动装置芯片及所述被动装置芯片具有不同的厚度;

利用多个第二互连凸块将所述第一重布层的所述片以及所述对应封装电连接到所述 第二重布层:及

在所述第一重布层与所述第二重布层之间形成第二囊封物,其中所述第一囊封物及所述第二囊封物包括相同材料,且所述多个第一互连凸块及所述多个第二互连凸块包括相同的低熔点材料。

- 19.根据权利要求18所述的方法,其中所述多个第一互连凸块为焊料球,且所述焊料球的两个相对端子从所述第一囊封物暴露。

- 20.根据权利要求18所述的方法,其中所述多个第二互连凸块为焊料球,且所述多个第二互连凸块的两个相对端子从所述第二囊封物暴露。

- 21.根据权利要求18所述的方法,其进一步包括形成在所述第二重布层上方且由所述 第二囊封物环绕的多个导电柱,其中所述多个第二互连凸块为焊料膏,所述导电柱的一个 端子连接到所述第二重布层,且所述导电柱的另一端子连接到所述多个第二互连凸块中的 对应第二互连凸块。

- 22.一种半导体封装结构,其包括:

第一重布层RDL,其具有彼此相对的第一表面及第二表面;

多个第一芯片,其在多个接点垫面对所述第一表面的情况下放置在所述第一重布层的 所述第一表面上方且电连接到所述第一重布层,其中所述多个第一芯片具有相异的厚度, 所述多个第一芯片通过多个导电材料及所述多个接点垫与所述第一重布层的所述第一表 面分离,所述多个第一芯片包含主动装置芯片及被动装置芯片,所述主动装置芯片及所述 被动装置芯片通过所述第一重布层彼此电通信;

第二芯片,其放置在所述第一重布层的所述第二表面下方且电连接到所述第一重布层,其中所述第一重布层放置在所述多个第一芯片与所述第二芯片之间:

多个外部连接器,其放置在所述第一重布层的所述第二表面下方且电连接到所述第二表面:

第二重布层,其在所述第一重布层上方,其中所述第二重布层具有彼此相对的第三表面及第四表面,且所述第三表面面对所述第一重布层的所述第一表面;

互连结构,其在所述第一重布层与所述第二重布层之间且电连接到所述第一重布层及 所述第二重布层,其中所述互连结构包括彼此堆叠的导电柱及导电凸块,所述导电柱及所 述导电凸块的总体高度高于所述多个第一芯片的高度;及

囊封物,其放置在所述第一重布层的所述第一表面上方,其中所述囊封物封围所述多个第一芯片且环绕所述互连结构的侧向壁,且所述导电凸块的上表面与所述囊封物的上表面实质上水平。

- 23.根据权利要求22所述的半导体封装结构,其进一步包括电连接到所述第二重布层的第三芯片。

- 24.根据权利要求22所述的半导体封装结构,其进一步包括电连接到所述第二重布层的封装。

- 25.根据权利要求24所述的半导体封装结构,其进一步包括第二互连结构,所述第二互连结构电连接到所述第二重布层及所述封装。

- 26.根据权利要求25所述的半导体封装结构,其中所述第二互连结构包括导电凸块。

- 27.一种半导体封装结构,其包括:

- 第一重布层RDL,其具有彼此相对的第一表面及第二表面;

- 第二重布层,其在所述第一重布层的所述第一表面上方,其中所述第二重布层具有彼此相对的第三表面及第四表面,且所述第三表面面对所述第一表面;

多个芯片,其放置在所述第一重布层与所述第二重布层之间,其中所述多个芯片包含 主动装置芯片及被动装置芯片,所述主动装置芯片及所述被动装置芯片具有不同的厚度, 所述主动装置芯片及所述被动装置芯片通过所述第一重布层彼此电通信;

互连结构,其放置在所述第一重布层与所述第二重布层之间且电连接到所述第一重布层及所述第二重布层,其中所述互连结构包括彼此堆叠的导电柱及导电凸块,所述导电柱的上表面与所述主动装置芯片的上表面实质上水平,所述导电柱及所述导电凸块的总体高度高于所述主动装置芯片的高度;及

囊封物,其放置在所述第一重布层与所述第二重布层之间,其中所述囊封物环绕所述导电凸块的侧向壁及所述导电柱的侧向壁,且所述导电凸块的上表面与所述囊封物的上表面实质上水平。

- 28.根据权利要求27所述的半导体封装结构,其进一步包括电连接到所述第二重布层的第二芯片。

- 29.根据权利要求27所述的半导体封装结构,其进一步包括电连接到所述第二重布层的封装。

- 30.根据权利要求29所述的半导体封装结构,其进一步包括第二互连结构,所述第二互连结构电连接到所述第二重布层及所述封装。

- 31.根据权利要求27所述的半导体封装结构,其进一步包括多个外部连接器电连接到所述第一重布层。

- 32.一种半导体封装结构,其包括:

- 第一重布层RDL,其具有彼此相对的第一表面及第二表面;

- 第二重布层,其在所述第一重布层的所述第二表面下方,其中所述第二重布层具有彼此相对的第三表面及第四表面,且所述第三表面面对所述第二表面;

第一芯片,其放置在所述第一重布层的所述第一表面上方;

多个第二芯片,其放置在所述第一重布层与所述第二重布层之间,其中所述多个第二芯片具有相异的厚度,所述多个第二芯片放置在同一水平,所述多个第二芯片包含主动装置芯片及被动装置芯片,所述主动装置芯片及所述被动装置芯片通过所述第二重布层彼此电通信;

互连结构,其放置在所述第一重布层与所述第二重布层之间且电连接到所述第一重布层及所述第二重布层,其中所述互连结构包括彼此堆叠的导电柱及导电凸块,且所述导电柱及所述导电凸块包括不同的材料;及

囊封物,其放置在所述第一重布层与所述第二重布层之间,其中所述囊封物环绕所述导电凸块的侧向壁及所述导电柱的侧向壁,所述多个第二芯片通过所述囊封物与所述第一重布层分离,且所述多个第二芯片通过所述囊封物与所述第二重布层分离。

- 33.根据权利要求32所述的半导体封装结构,其进一步包括放置在所述第二重布层的所述第四表面下方的第三芯片。

- 34.根据权利要求33所述的半导体封装结构,其中所述第二重布层放置在所述多个第二芯片与所述第三芯片之间。

# 半导体封装结构及其制造方法

#### 技术领域

[0001] 本揭露是关于一种半导体封装结构及其制造方法。

#### 背景技术

[0002] 半导体封装结构包含多个主动及被动装置芯片。例如双极及场效晶体管的主动装置经配置以控制电流的流动。例如电阻器、电容器及电感器的被动装置用于建立执行各种电功能所必需的电压与电流之间的关系。被动装置与主动装置经电连接以形成使得半导体装置能够执行高速计算及其它有用功能的电路。

[0003] 随着半导体技术的演变,半导体装置变得越来越小。同时,更多功能需要集成到半导体装置中。相应地,半导体装置需要具有包装到较小区域中的越来越大数目个I/0接点垫,且I/0接点垫的密度随时间迅速上升。作为一结果,半导体装置的封装变得更困难,此不利地影响封装的良率。

#### 发明内容

[0004] 在一个示范性方面中,一种半导体封装结构包含重布层(RDL)、芯片、多个互连凸块及囊封物。所述重布层具有彼此相对的第一表面及第二表面。所述芯片在多个接点垫面对所述第一表面的情况下放置在所述重布层上方且电连接到所述重布层。所述互连凸块放置在所述第一表面上方且电连接到所述重布层。所述囊封物放置在所述重布层的所述第一表面上方,且所述囊封物封围所述芯片且环绕所述互连凸块的侧向壁。

[0005] 在另一示范性方面中,一种半导体封装结构包含第一重布层、第一芯片、多个第一互连凸块、第一囊封物、第二重布层、第二芯片、多个第二互连凸块及第二囊封物。所述第一重布层具有彼此相对的第一表面及第二表面。所述第一芯片在多个接点垫面对所述第一表面的情况下放置在所述第一重布层上方且电连接到所述第一重布层。所述第一重封物放置在所述第一重布层的所述第一表面上方且电连接到所述第一重布层。所述第一囊封物放置在所述第一重布层的所述第一表面上方。所述第一囊封物封围所述第一芯片且环绕所述第一互连凸块的侧向壁。所述第二重布层在所述第一重布层的所述第二表面。所述第二重布层具有彼此相对的第三表面及第四表面,且所述第三表面面对所述第二表面。所述第二芯片在多个接点垫面对所述第三表面的情况下放置在所述第二重布层上方。所述第二互连凸块放置在所述第三表面上方且电连接到所述第二重布层。所述第二囊封物放置在所述第一重布层与所述第二重布层之间,且所述第二囊封物封围所述第二芯片且环绕所述第二互连凸块的侧向壁。

[0006] 在又一方面中,一种用于制造半导体封装结构的方法包含:在第一载体衬底上方形成第一重布层;在所述第一重布层上方放置多个第一芯片;利用多个第一互连凸块将多个封装电连接到所述第一重布层;及在所述封装与所述第一重布层之间形成第一囊封物。

#### 附图说明

[0007] 当连同附图一起阅读时,从以下详细说明最佳地理解本揭露的方面。应注意,根据业内标准惯例,各种结构未按比例绘制。实际上,为论述清晰,可任意地增加或减小各种结构的尺寸。

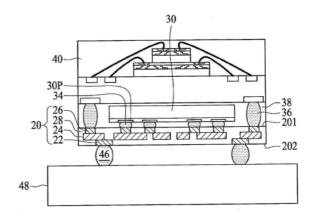

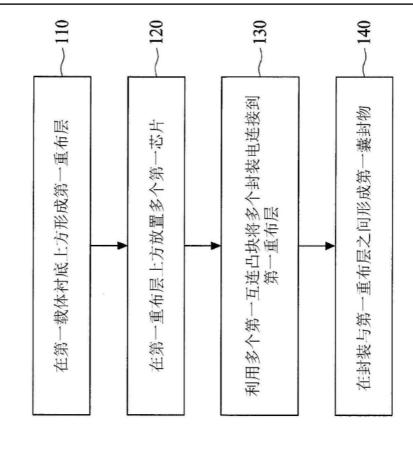

[0008] 图1是图解说明根据本揭露的各种方面的用于制造半导体封装结构的方法的流程图。

[0009] 图2A、图2B、图2C、图2D、图2E、图2F、图2G、图2H及图2I是在根据本揭露的一或多个实施例的制造半导体封装结构的各种操作中的一者时的剖面图。

[0010] 图3是图解说明根据本揭露的各种方面的用于制造半导体封装结构的方法的流程图。

[0011] 图4A、图4B、图4C、图4D、图4E及图4F是在根据本揭露的一或多个实施例的制造半导体封装结构的各种操作中的一者时的剖面图。

[0012] 图5是图解说明根据本揭露的某些实施例的半导体封装结构的示意图。

[0013] 图6是图解说明根据本揭露的某些实施例的半导体封装结构的示意图。

### 具体实施方式

[0014] 本申请案主张在2016年7月25日提出申请的美国临时申请案第62/366,295号的优先权,所述美国临时申请案的全部内容以引用方式并入本文中。

[0015] 以下揭露提供用于实施所提供目标物的不同构件的诸多不同实施例或实例。下文阐述组件及布置的具体实例以简化本揭露。当然,存在仅实例且不意欲为限制性。举例来说,在以下说明中,第一构件形成于第二构件上方或上可包含其中第一构件及第二构件形成为直接接触的实施例,且还可包含其中额外构件可形成于第一构件与第二构件之间使得第一构件及第二构件可不直接接触的实施例。另外,本揭露可在各种实例中重复组件符号及/或字母。此重复是为了简单及清晰目的且其本身不指出所论述的各种实施例及/或配置之间的关系。

[0016] 进一步地,为了说明方便,本文中可使用空间相对术语(例如,"在…下面"、"在…下方"、"下部"、"在…上面"、"上部"、"在…上"及例如此类)来阐述一个组件或构件与另一(些)组件或构件的关系,如各图中所图解说明。所述空间相对术语意欲囊括除各图中所绘示的定向之外的装置在使用或操作中的不同定向。设备可以其它方式经定向(旋转90度或处于其它定向)且相应地可同样地解释本文中所使用的空间相对叙述语。

[0017] 如本文中所使用,例如"第一"、"第二"及"第三"的术语阐述各种组件、组件、区域、层及/或区段,这些组件、组件、区域、层及/或区段不应受这些术语限制。这些术语可仅用于将组件、组件、区域、层或区段彼此区分开。例如"第一"、"第二"及"第三"的术语在用于本文中时不暗示顺序或次序,除非内容脉络清晰指示。

[0018] 如本文中所使用,术语"载体衬底"或"暂时衬底"是指配置为用于例如重布层、芯片、囊封物及其它结构的上覆层的制作便利或用于进行切块的中间衬底的载体。所述载体衬底或所述暂时衬底提供暂时支撑及固定功能,且将从上覆结构经移除。

[0019] 如本文中所使用,术语"被动装置"是指包含电阻器、电容器、电感器或其一组合的装置。

[0020] 如本文中所使用,术语"重布层(RDL)"是指由至少一个导电图案及至少一个绝缘层形成的层堆叠,且经配置以与两个或两个以上装置电通信。

[0021] 如本文中所使用,术语"互连凸块"是指经配置以使两个导电结构透过其两端电互连的导体。在一或多个实施例中,所述互连凸块由可通过低温操作形成的低熔点材料形成。在形成环绕所述互连凸块的侧壁的囊封物之前形成所述互连凸块。在一或多个实施例中,所述互连凸块是焊料凸块、焊料膏或例如此类。

[0022] 在本揭露的某些实施例中,半导体封装结构包含两个或两个以上重布层,且这些RDL替代穿透衬底的通孔结构而透过焊料球或焊料膏连同嵌入于囊封物中的导电柱互连。芯片能够嵌入于所述囊封物中,此降低半导体封装结构的总体高度,且允许具有相异厚度的芯片放置在同一水平。

[0023] 图1是图解说明根据本揭露的各种方面的用于制造半导体封装结构的方法的流程图。方法100以操作110开始,其中在第一载体衬底上方形成第一重布层。方法100以操作120继续,其中在所述第一重布层上方放置多个第一芯片。方法100以操作130继续进行,其中将多个封装与多个第一互连凸块电连接到所述第一重布层。方法100以操作140继续进行,其中在所述封装与所述第一重布层之间形成第一囊封物。

[0024] 方法100仅仅是一实例,且不意欲限制本揭露(除权利要求书中明确陈述的内容之外)。可在方法100之前、期间及之后提供额外操作,且可替换、删去或四处移动所阐述的某些操作以用于方法的额外实施例。

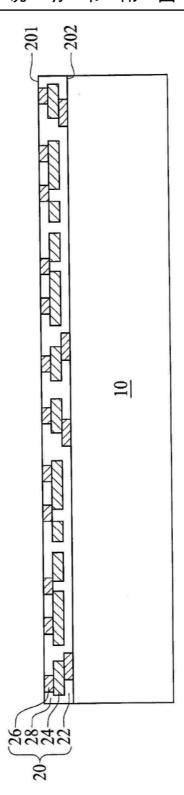

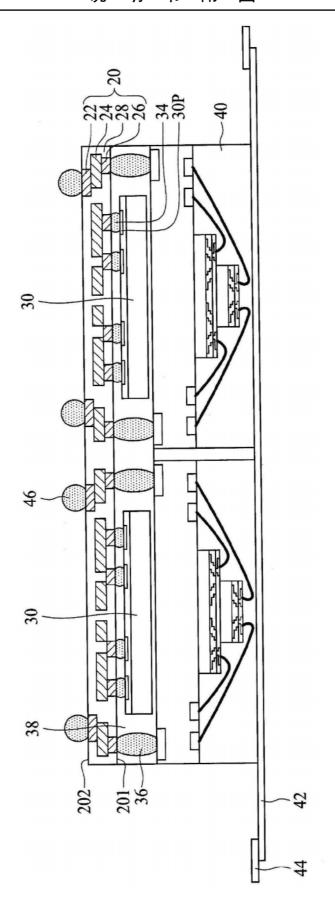

[0025] 图2A、图2B、图2C、图2D、图2E、图2F、图2G、图2H及图2I是在根据本揭露的一或多个实施例的制造半导体封装结构的各种操作中的一者时的剖面图。如图2A中所绘示,第一重布层20形成于第一载体衬底10上方。第一载体衬底10配置为用于形成第一重布层20的暂时载体,且随后将被移除。在一或多个实施例中,第一载体衬底10是例如玻璃衬底的绝缘衬底。第一载体衬底10可包含例如硅衬底的半导体衬底、例如金属衬底的导电衬底或其它适合衬底。第一重布层20具有彼此相对的第一表面201及第二表面202。在某些实施例中,第一重布层20的第二表面202面对第一载体衬底10。第一重布层20由至少一个导电层及至少一个绝缘层形成,且经配置以与两个或两个以上装置电通信。在一或多个实施例中,第一重布层20包含三个导电层22、24、26及环绕导电层22、24、26的至少一个绝缘层28。在某些实施例中,导电层22从第二表面202暴露,且导电层26从第一表面201暴露。在某些实施例中,第一重布层20通过执行数个沉积操作、光刻操作及蚀刻操作而形成。在某些实施例中,导电层22、24、26的材料包含例如铜、钛、类似物或其一组合的金属。至少一个绝缘层28的材料可包含无机及/或有机绝缘材料。

[0026] 如图2B中所绘示,数个第一芯片30放置在第一重布层20上方。在一或多个实施例中,第一芯片30包含主动装置芯片及/或被动装置芯片。以实例方式,主动装置芯片可包含系统单芯片(SOC)、例如DRAM芯片的存储器芯片及/或其它芯片。被动装置芯片可包含形成于其中的电阻器、电容器、电感器或其组合。在某些实施例中,被动装置芯片可呈集成电路的形式,但并不限于此。第一芯片30可透过表面安装技术(SMT)或其它适合接合技术安装在第一重布层20上。在某些实施例中,第一芯片30中的每一者包含多个接点垫30P,且第一芯片30通过如下方式电连接到第一重布层20:透过例如焊料膏、焊料凸块或其它适合导电材

料的导电材料34将接点垫30P接合到第一重布层20的经暴露导电层26。在一或多个实施例中,主动装置芯片及被动装置芯片透过第一重布层20彼此电通信。在某些实施例中,不同第一芯片30的厚度可是相异的。举例来说,主动装置芯片及被动装置芯片的厚度可不同。

[0027] 如图2C中所绘示,多个封装40放置在第一重布层20上方且利用多个第一互连凸块36电连接到第一重布层20。在一或多个实施例中,封装40是包含封装有经暴露外部端子的一或多个芯片的预成型结构。在一或多个实施例中,封装40是例如快闪存储器装置封装的存储器装置封装,但并不限于此。在一或多个实施例中,第一互连凸块36是焊料球,其中所述焊料球的一个端子电连接到封装40的外部端子,且所述焊料球的另一端子电连接到第一重布层20的经暴露导电层26。第一互连凸块36可包含其它类型的导体。

[0028] 如图2D中所绘示,第一囊封物38形成于封装40与第一重布层20之间。在一或多个实施例中,第一囊封物38的材料是模塑料。在某些实施例中,底胶填充层可形成于第一芯片30与第一重布层20之间。在某些实施例中,第一囊封物38是一成型底胶填充(MUF)层且因此不需要额外底胶填充层。在一或多个实施例中,焊料球的两个相对端子从第一囊封物38暴露以分别电连接到封装40及第一重布层20。在某些实施例中,第一囊封物38覆盖第一芯片30的上表面。

[0029] 如图2E中所绘示,封装40附接到暂时衬底42。在一或多个实施例中,暂时衬底42是挠性膜,例如固定在框架44上的胶带。在某些实施例中,暂时衬底42可包含其它类型的衬底,例如刚性衬底。第一载体衬底10然后从第一重布层20拆卸。

[0030] 如图2F中所绘示,第一重布层20从第二表面202薄化以暴露第一重布层20的导电层22。在一或多个实施例中,第一重布层20通过蚀刻经薄化,但不受限制。在某些实施例中,第一重布层20可通过研磨、抛光或其它适合薄化方法经薄化。在某些实施例中,假使导电层22提前从第一重布层20暴露,则可省略薄化操作。在某些实施例中,经暴露导电层22配置为接点垫。

[0031] 如图2G中所绘示,多个第二互连凸块46形成于第一重布层20上方且电连接到经暴露导电层22。在一或多个实施例中,第二互连凸块46是焊料球,但并不限于此。

[0032] 如图2H中所绘示,第一重布层20划分成若干片,且第一重布层20的每一片连接到对应封装40。在一或多个实施例中,第一重布层20可通过锯切或其它适合切割方法来划分。 [0033] 如图2I中所绘示,连接到第一重布层20的对应片的封装40从暂时衬底42拆卸以形成半导体封装结构1。在一或多个实施例中,第二互连凸块46配置为外部连接器,且电连接到放置在第一重布层20的第二表面202上方的电路板48使得电路板48利用第二互连凸块46电连接到第一重布层20。在一或多个实施例中,半导体封装结构1可堆叠在另一封装结构上。

[0034] 第一芯片30嵌入于第一囊封物38中,且因此总体厚度减小。第一互连凸块36在第一囊封物38中且在形成第一囊封物38之前形成,且因此不需要通孔结构来电连接封装40与第一重布层20。因此,降低制造成本及复杂度。另外,阻止第一芯片30在形成通孔结构中由于高温而受热损坏。而且,通过低温操作形成第一互连凸块36,且半导体封装结构1需要一个成型操作来形成第一囊封物38。相应地,减轻翘曲问题。

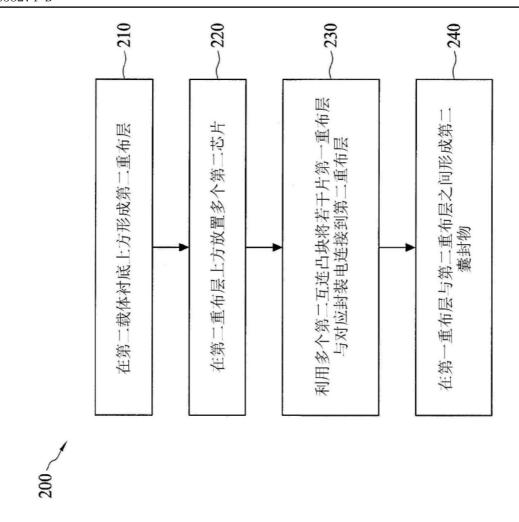

[0035] 图3是图解说明根据本揭露的各种方面的用于制造半导体封装结构的方法的流程图。在一或多个实施例中,方法200是继图1中的方法100的操作140之后。方法200以操作210

继续进行,其中在第二载体衬底上方形成第二重布层。方法200以操作220继续,其中在所述第二重布层上方放置多个第二芯片。方法200以操作230继续进行,其中利用多个第二互连凸块将每一片第一重布层与对应封装电连接到第二重布层。方法200以操作240继续进行,其中在所述第一重布层与所述第二重布层之间形成第二囊封物。

[0036] 方法200仅仅是一实例,且不意欲限制本揭露(除权利要求书中明确陈述的内容之外)。可在方法200之前、期间及之后提供额外操作,且可替换、删去或四处移动所阐述的某些操作以用于方法的额外实施例。

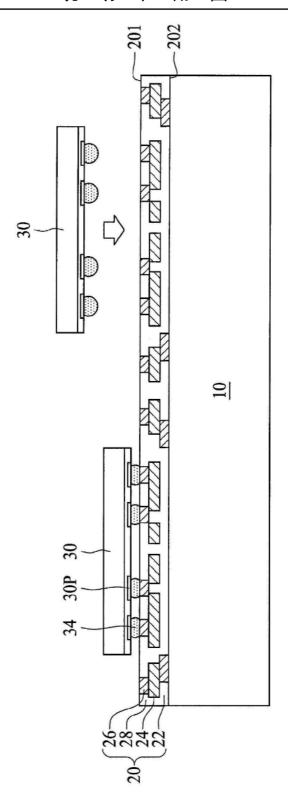

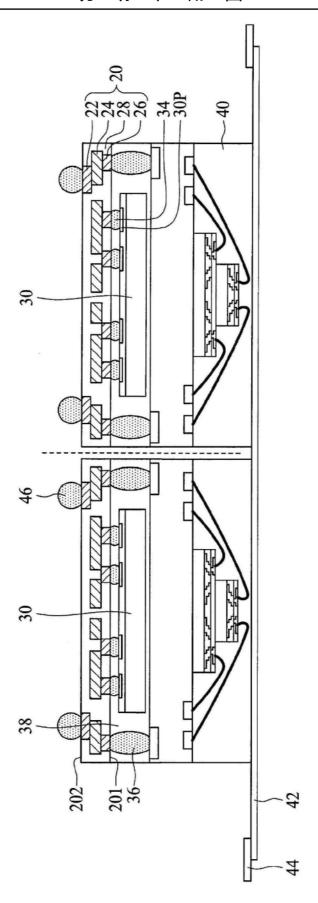

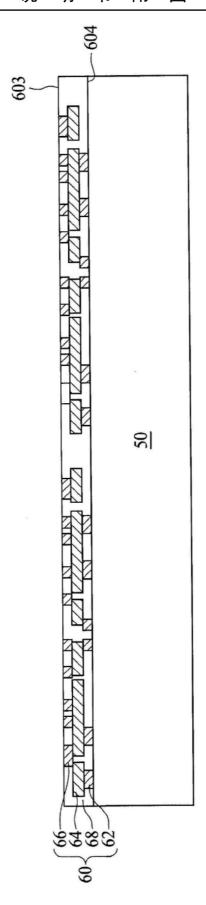

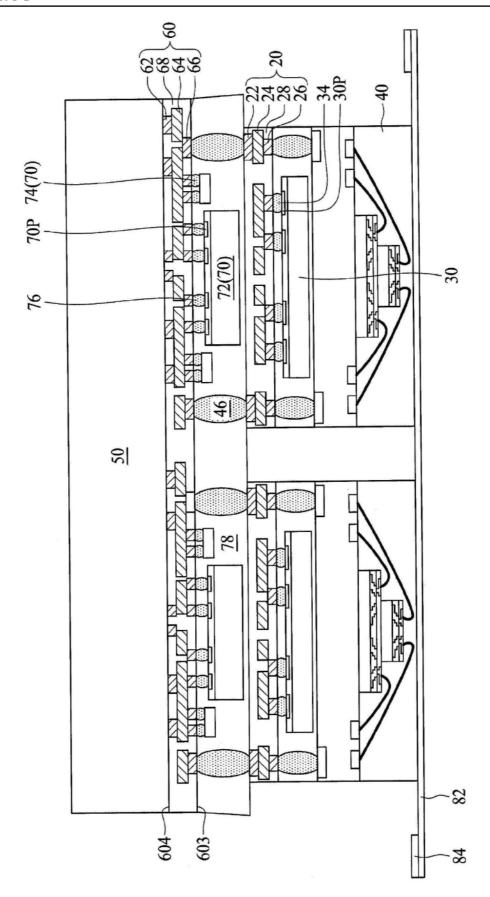

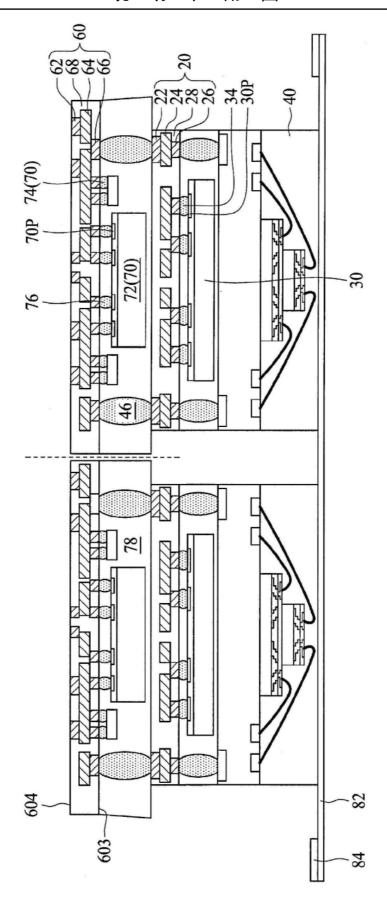

[0037] 图4A、图4B、图4C、图4D、图4E及图4F是在根据本揭露的一或多个实施例的制造半导体封装结构的各种操作中的一者时的剖面图。如图4A中所绘示,第二重布层60形成于第二载体衬底50上方。第二载体衬底50配置为用于形成第二重布层60的暂时载体,且随后将被移除。在一或多个实施例中,第二载体衬底50是例如玻璃衬底的绝缘衬底。第二载体衬底50可包含例如硅衬底的半导体衬底、例如金属衬底的导电衬底或其它适合衬底。第二重布层60具有彼此相对的第三表面603及第四表面604。在某些实施例中,第二重布层60的第四表面604面对第二载体衬底50。第二重布层60由至少一个导电层及至少一个绝缘层形成,且经配置以与两个或两个以上装置电通信。在一或多个实施例中,第二重布层60包含三个导电层62、64、66及环绕导电层62、64、66的至少一个绝缘层68。在某些实施例中,导电层62从第四表面604暴露,且导电层66从第三表面603暴露。在某些实施例中,导电层62从第四表面604暴露,且导电层66从第三表面603暴露。在某些实施例中,导电层62人第四表面604暴露,且导电层66从第三表面603暴露。在某些实施例中,导电层62、64、66的材料包含例如铜、钛、类似物或其组合的金属。至少一个绝缘层68的材料可包含无机及/或有机绝缘材料。

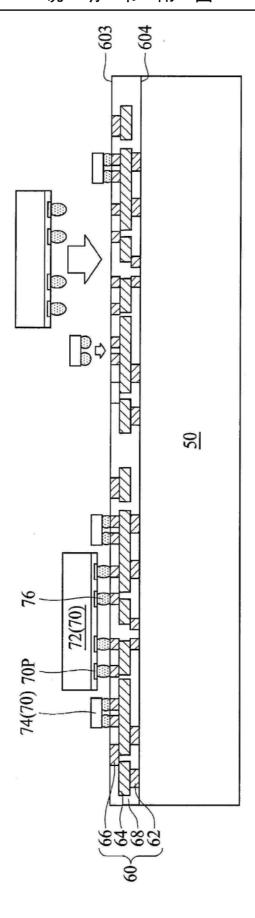

[0038] 如图4B中所绘示,数个第二芯片70放置在第二重布层60上方。在一或多个实施例中,第二芯片70包含主动装置芯片72及/或被动装置芯片74。以实例方式,主动装置芯片72可包含系统单芯片(SOC)。被动装置芯片74可包含形成于其中的电阻器、电容器、电感器或其组合。在某些实施例中,被动装置芯片74可呈集成电路的形式,但并不限于此。第二芯片70可透过表面安装技术(SMT)或其它适合接合技术安装在第二重布层60上。在某些实施例中,第二芯片70中的每一者包含多个接点垫70P,且第二芯片70通过如下方式电连接到第二重布层60:透过例如焊料膏、焊料凸块或其它适合导电材料的导电材料76将接点垫70P接合到第二重布层60的经暴露导电层66的一部分。在一或多个实施例中,主动装置芯片72及被动装置芯片74透过第二重布层60彼此电通信。在某些实施例中,不同第二芯片70的厚度可是相异的。举例来说,主动装置芯片72及被动装置芯片74的厚度不同。

[0039] 如图4C中所绘示,包含连接到通过图2A到2I中所图解说明的方法形成的对应封装40的第一重布层20片的半导体封装结构放置在第二重布层60上,且利用多个第二互连凸块46电连接到第二重布层60。在一或多个实施例中,第二互连凸块46是焊料球,其中所述焊料球的一个端子电连接到第一重布层20,且所述焊料球的另一端子电连接到第二重布层60的经暴露导电层66的另一部分。第二互连凸块46可包含其它类型的导体。

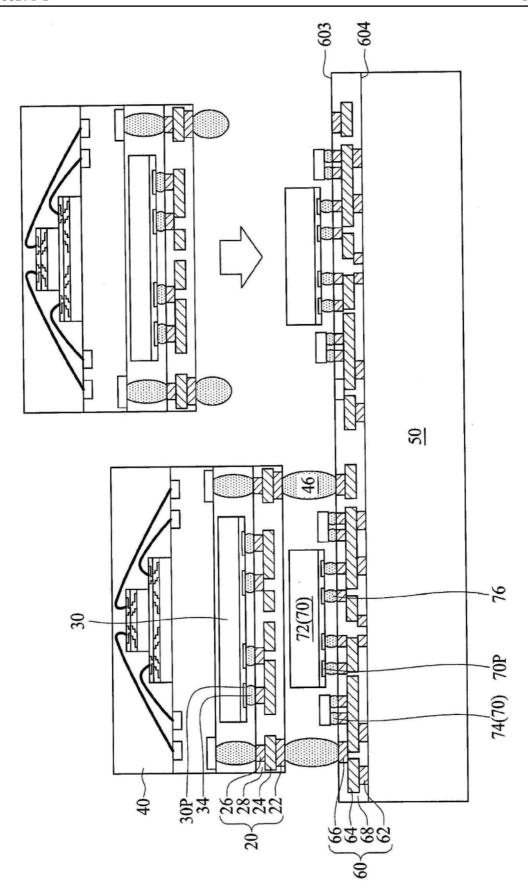

[0040] 如图4D中所绘示,第二囊封物78放置在第一重布层20与第二重布层60之间。在一或多个实施例中,第二囊封物78封围第二芯片70且环绕第二互连凸块46的侧向壁。在一或多个实施例中,第二囊封物78的材料是模塑料。在某些实施例中,底胶填充层可形成于第二芯片70与第二重布层60之间。在某些实施例中,第二囊封物78是一成型底胶填充(MUF)层且

因此不需要额外底胶填充层。在一或多个实施例中,焊料球的两个相对端子从第二囊封物78暴露以分别电连接到第一重布层20及第二重布层60。

[0041] 如图4E中所绘示,封装40附接到另一暂时衬底82。在一或多个实施例中,暂时衬底82是挠性膜,例如固定在框架84上的胶带。在某些实施例中,暂时衬底82可包含其它类型的衬底,例如刚性衬底。第二载体衬底50然后从第二重布层60拆卸。在某些实施例中,第二重布层60从第四表面604经薄化以暴露第二重布层60的导电层62。在一或多个实施例中,第二重布层60通过蚀刻经薄化,但不受限制。在某些实施例中,第二重布层60可通过研磨、抛光或其它适合薄化方法经薄化。在某些实施例中,假使导电层62提前从第二重布层60暴露,则可省略薄化操作。在某些实施例中,经暴露导电层62配置为接点垫。

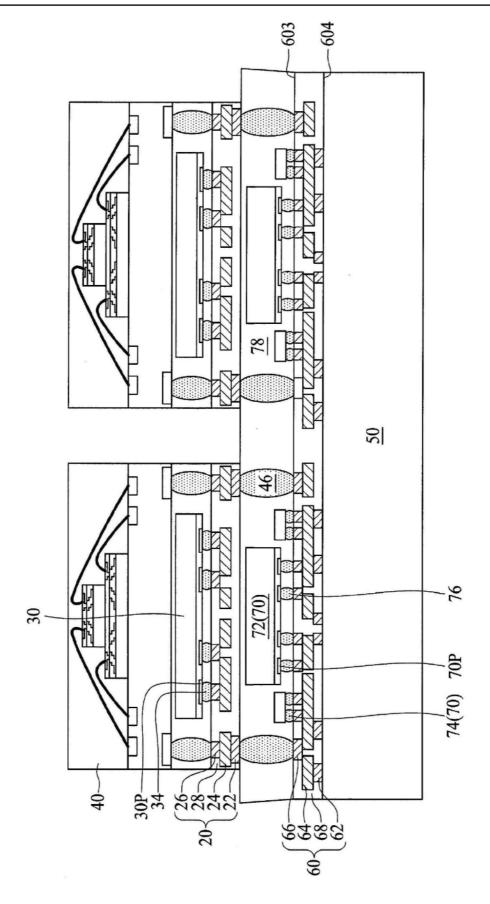

[0042] 如图4F中所绘示,数个外部连接器86形成于第二重布层60的第四表面604上方且电连接到第二重布层60的经暴露导电层62的一部分。在一或多个实施例中,外部连接器86布置为球栅阵列(BGA),但并不限于此。在一或多个实施例中,数个第三芯片88可放置在第二重布层60的第四表面604上方且电连接到第二重布层60的经暴露导电层62的另一部分。在某些实施例中,第三芯片88是一被动装置芯片,所述被动装置芯片可包含形成于其中的电阻器、电容器、电感器或其组合。第三芯片88透过第二重布层60与第二芯片70电通信,且透过第一重布层20与第一芯片30电通信。第二重布层60通过任何适合切割方法经锯切。随后,暂时衬底82经移除以形成半导体封装结构2。

[0043] 第一芯片30及第二芯片70嵌入于第一囊封物38及第二囊封物78中,且因此总体厚度减小。第一互连凸块36形成于第一囊封物38中,且第二互连凸块46形成于第二囊封物78中,且因此不需要通孔结构。因此,降低制造成本及复杂度。另外,阻止第一芯片30及第二芯片70在形成通孔结构中由于高温而受热损坏。而且,通过低温操作形成第一互连凸块36及第二互连凸块46,且半导体封装结构2需要两个成型操作来形成第一囊封物38及第二囊封物78。相应地,减轻翘曲问题。

[0044] 本揭露不限于上文所提及的实施例,且可具有其它不同实施例。为简化说明且为了本揭露的实施例中的每一者之间的比较方便,用完全相同编号来标记以下实施例中的每一者中的完全相同组件。为使比较实施例之间的差异更容易,以下说明将详述不同实施例当中的相异点且将不冗余地阐述完全相同特征。

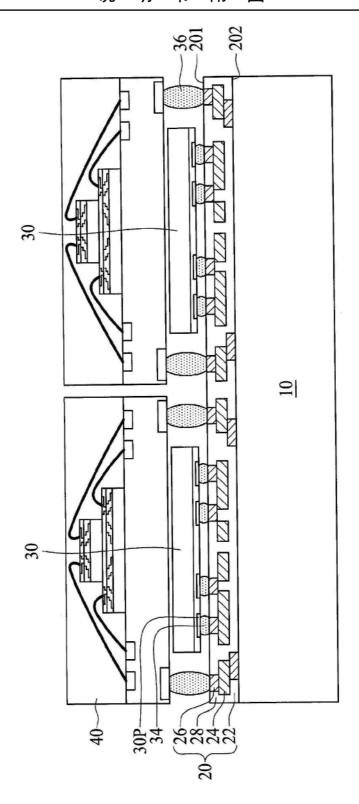

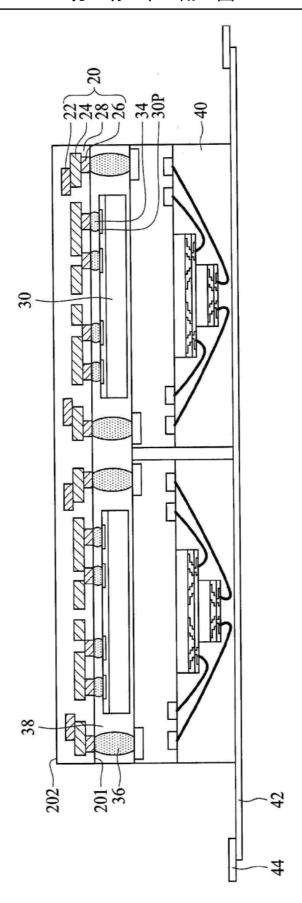

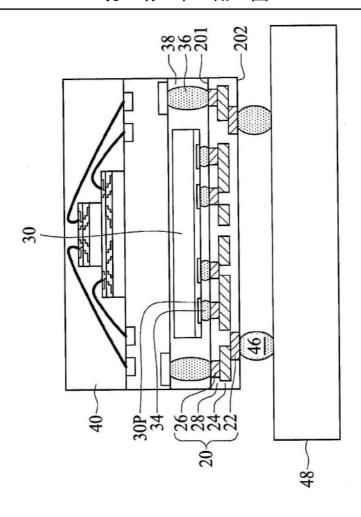

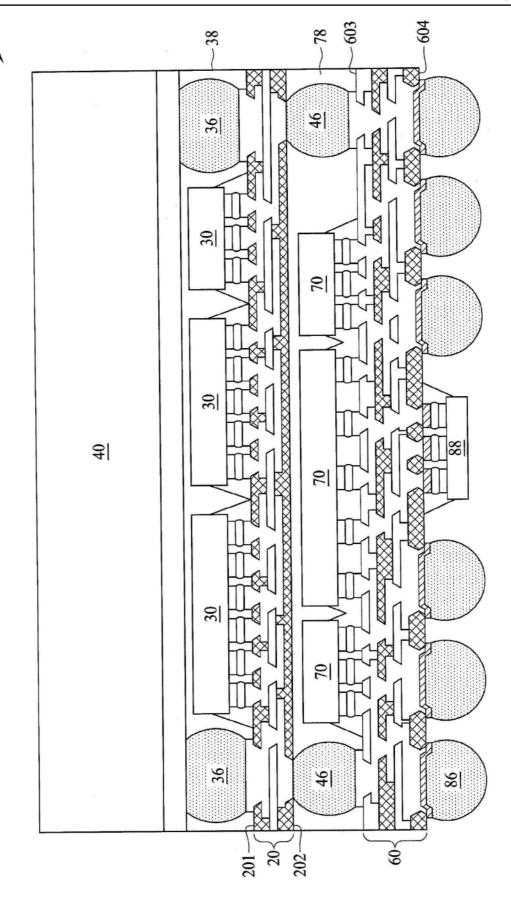

[0045] 图5是图解说明根据本揭露的某些实施例的半导体封装结构3的示意图。如图5中所展示,半导体封装结构3包含第一重布层(RDL)20、第一芯片30、第一互连凸块36、第一囊封物38、第二重布层60、第二芯片70、第二互连凸块46及第二囊封物78。第一重布层20具有彼此相对的第一表面201及第二表面202。第一芯片30在多个接点垫30P面对第一表面201的情况下放置在第一重布层20上方且电连接到第一重布层20。第一互连凸块36放置在第一表面201上方且电连接到第一重布层20。第一囊封物38放置在第一重布层20的第一表面201上方。第一囊封物38封围第一芯片30且环绕第一互连凸块36的侧向壁。第二重布层60在第一重布层20的第二表面202上方。第二重布层60具有彼此相对的第三表面603及第四表面604,且第三表面603面对第二表面202。第二芯片70在多个接点垫70P面对第三表面603的情况下放置在第二重布层60上方。第二互连凸块46放置在第三表面603上方且电连接到第二重布层60。第二囊封物78放置在第一重布层20与第二重布层60之间。第二囊封物78封围第二芯片70且环绕第二互连凸块46的侧向壁。在一或多个实施例中,半导体封装结构3进一步包含

放置在第一囊封物38上方且透过第一互连凸块36电连接到第一重布层20的封装(未展示)。在一或多个实施例中,第二互连凸块46的高度高于第二芯片70的高度。在一或多个实施例中,半导体封装结构3进一步包含放置在第二重布层60的第四表面604上方的电路板(未展示)以及放置在第四表面604与电路板之间以电连接第二重布层60与电路板的外部连接器86。

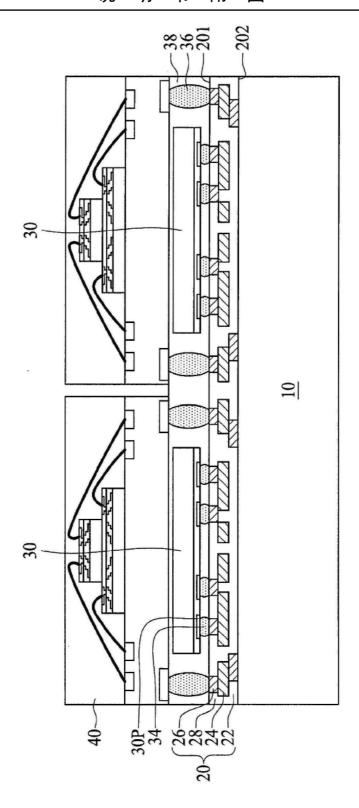

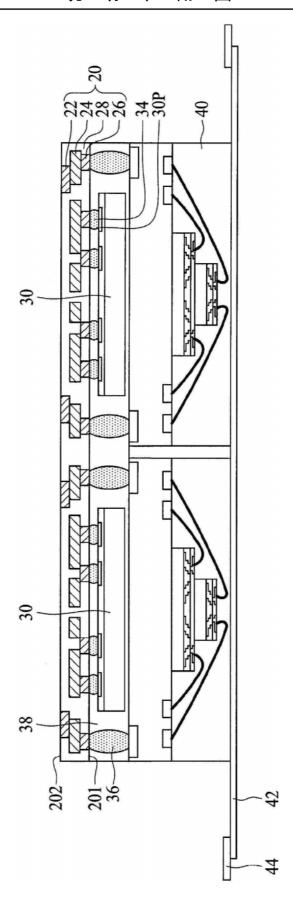

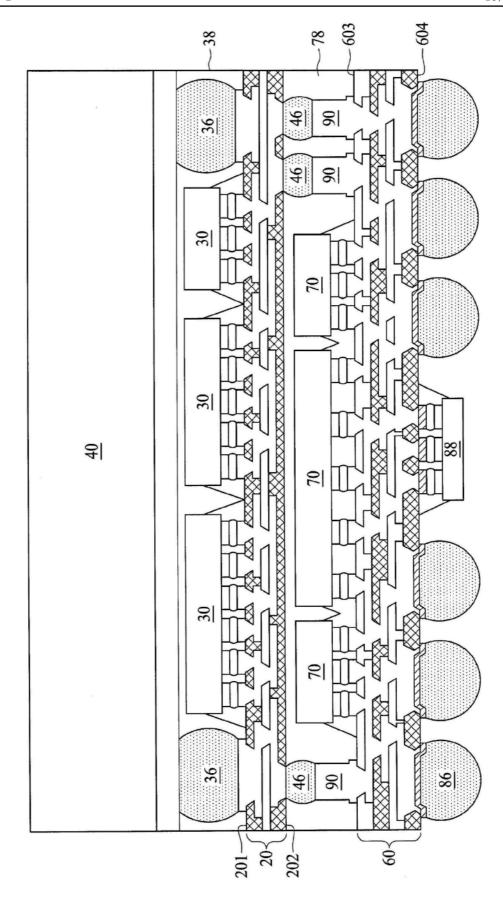

[0046] 图6是图解说明根据本揭露的某些实施例的半导体封装结构4的示意图。如图6中所展示,半导体封装结构4与图5中的半导体封装结构3之间的差异之一是:半导体封装结构4进一步包含放置在第二囊封物78中的导电柱90。在某些实施例中,第二互连凸块46中的每一者是焊料膏,其中导电柱90的一个端子连接到第二重布层60,且导电柱90的另一端子连接到对应第二互连凸块46。导电柱90及第二互连凸块46的制作及材料是不同的。在一或多个实施例中,导电柱90通过沉积、光刻及蚀刻操作而形成,且因此毗邻导电柱90之间的间距可减小。相应地,与焊料膏相关联的导电柱90能够实现第一重布层20与第二重布层60之间的精细间距结合。导电柱90与第二互连凸块46之间的高度比可基于不同考虑而修改。在某些实施例中,导电柱90的上表面与第二芯片70的上表面实质上水平。在某些实施例中,导电柱90的上表面低于第二芯片70的上表面。在一或多个实施例中,导电柱90及第二互连凸块46的总体高度高于第二芯片70的高度。

[0047] 在本揭露中,芯片嵌入于囊封物中,且因此半导体封装结构的总体厚度减小。由于芯片当中的电通信路径的减少而改进系统性能。所述芯片经配置以用于提供不同功能性,例如主动装置芯片及被动装置芯片可具有不同厚度,且因此选择芯片的灵活性增加。不需要通孔结构,且因此降低制造成本及复杂度。阻止所述芯片在形成通孔结构中由于高温而受热损坏。与通孔结构相比较,互连凸块由可通过低温操作形成的低熔点材料形成。因此,减少热预算。而且,半导体封装结构需要较少成型操作来形成囊封物。相应地,减轻翘曲问题。

[0048] 在一个示范性方面中,一种半导体封装结构包含重布层(RDL)、芯片、多个互连凸块及囊封物。所述重布层具有彼此相对的第一表面及第二表面。所述芯片在多个接点垫面对所述第一表面的情况下放置在所述重布层上方且电连接到所述重布层。所述互连凸块放置在所述第一表面上方且电连接到所述重布层。所述囊封物放置在所述重布层的所述第一表面上方,且所述囊封物封围所述芯片且环绕所述互连凸块的侧向壁。

[0049] 在另一示范性方面中,一种半导体封装结构包含第一重布层、第一芯片、多个第一互连凸块、第一囊封物、第二重布层、第二芯片、多个第二互连凸块及第二囊封物。所述第一重布层具有彼此相对的第一表面及第二表面。所述第一芯片在多个接点垫面对所述第一表面的情况下放置在所述第一重布层上方且电连接到所述第一重布层。所述第一互连凸块放置在所述第一表面上方且电连接到所述第一重布层。所述第一囊封物放置在所述第一重布层的所述第一表面上方。所述第一囊封物封围所述第一芯片且环绕所述第一互连凸块的侧向壁。所述第二重布层在所述第一重布层的所述第二表面上方。所述第二重布层具有彼此相对的第三表面及第四表面,且所述第三表面面对所述第二表面。所述第二芯片在多个接点垫面对所述第三表面的情况下放置在所述第二重布层上方。所述第二互连凸块放置在所述第三表面上方且电连接到所述第二重布层。所述第二囊封物放置在所述第一重布层与所述第二重布层之间,且所述第二囊封物封围所述第二芯片且环绕所述第二互连凸块的侧向

壁。

[0050] 在又一方面中,一种用于制造半导体封装结构的方法包含:在第一载体衬底上方形成第一重布层;在所述第一重布层上方放置多个第一芯片;利用多个第一互连凸块将多个封装电连接到所述第一重布层;及在所述封装与所述第一重布层之间形成第一囊封物。

[0051] 前文概述数个实施例的结构使得所属领域的技术人员可更佳地理解本揭露的方面。所属领域的技术人员应了解,其可容易地使用本揭露作为设计或修改用于实施相同目的及/或达成本文中介绍的实施例的相同优点的其它过程及结构的基础。所属领域的技术人员也应认识到,这些等效构造不背离本揭露的精神及范围,且其可在本文中做出各种改变、替代及更改而不背离本揭露的精神及范围。

### [0052] 符号说明

- [0053] 3 半导体封装结构

- [0054] 4 半导体封装结构

- [0055] 10 第一载体衬底

- [0056] 20 第一重布层

- [0057] 22 导电层/经暴露导电层

- [0058] 24 导电层

- [0059] 26 导电层/经暴露导电层

- [0060] 28 绝缘层

- [0061] 30 第一芯片

- [0062] 30P 接点垫

- [0063] 34 导电材料

- [0064] 36 第一互连凸块

- [0065] 38 第一囊封物

- [0066] 40 封装

- [0067] 42 暂时衬底

- [0068] 44 框架

- [0069] 46 第二互连凸块

- [0070] 48 电路板

- [0071] 50 第二载体衬底

- [0072] 60 第二重布层

- [0073] 62 导电层/经暴露导电层

- [0074] 64 导电层

- [0075] 66 导电层/经暴露导电层

- [0076] 68 绝缘层

- [0077] 70 第二芯片

- [0078] 70P 接点垫

- [0079] 72 主动装置芯片

- [0080] 74 被动装置芯片

- [0081] 76 导电材料

| [0082] | 78  | 第二囊封物 |

|--------|-----|-------|

| [0083] | 82  | 暂时衬底  |

| [0084] | 84  | 框架    |

| [0085] | 86  | 外部连接器 |

| [0086] | 88  | 第三芯片  |

| [0087] | 90  | 导电柱   |

| [8800] | 201 | 第一表面  |

| [0089] | 202 | 第二表面  |

| [0090] | 603 | 第三表面  |

| [0091] | 604 | 第四表面  |

图1

图2A

图2B

图2C

图2D

图2E

图2F

图2G

图2H

图2I

图3

图4A

图4B

图4C

图4D

图4E

图4F

图5

图6