(19) **日本国特許庁(JP)**

# (12) 特 許 公 報(B2)

(11)特許番号

特許第5114832号 (P5114832)

(45) 発行日 平成25年1月9日(2013.1.9)

(24) 登録日 平成24年10月26日(2012.10.26)

(51) Int.Cl. F 1

HO 1 L

29/739

(2006.01)

HO 1 L

29/78

6 5 5 A

HO 1 L

29/78

(2006.01)

HO 1 L

29/78

6 5 2 G

HO 1 L

29/78

6 5 2 K

HO 1 L

29/78

6 5 3 C

請求項の数 11 (全 35 頁)

(21) 出願番号 特願2005-231240 (P2005-231240)

(22) 出願日 平成17年8月9日 (2005.8.9) (65) 公開番号 特開2006-237553 (P2006-237553A)

(43) 公開日 平成18年9月7日 (2006.9.7) 審査請求日 平成20年7月15日 (2008.7.15)

(31) 優先権主張番号 特願2004-256251 (P2004-256251)

(32) 優先日 平成16年9月2日 (2004.9.2)

(33) 優先権主張国 日本国(JP)

(31) 優先権主張番号 特願2005-20334 (P2005-20334) (32) 優先日 平成17年1月27日 (2005.1.27)

(33) 優先権主張国 日本国(JP)

||(73)特許権者 000005234

富士電機株式会社

神奈川県川崎市川崎区田辺新田1番1号

|(74)代理人 100104190

弁理士 酒井 昭徳

||(72)発明者 武井 学

神奈川県横須賀市長坂二丁目2番1号 富士電機アドバンストテクノロジー株式会社

内

審査官 崎間 伸洋

最終頁に続く

### (54) 【発明の名称】半導体装置およびその製造方法

### (57)【特許請求の範囲】

### 【請求項1】

第1導電型単結晶半導体基板の第1の主面を選択的に覆う第1の絶縁膜と、

前記第1の絶縁膜の窓部において前記単結晶半導体基板に接触する第1の第1導電型半 導体領域と、

前記第1の絶縁膜の窓部の外側において前記第1の絶縁膜の上に設けられた第1の第2 導電型半導体領域と、

前記第1の第2導電型半導体領域内に設けられた第2の第1導電型半導体領域と、

前記第1の第1導電型半導体領域、前記第2の第1導電型半導体領域および前記第1の 第2導電型半導体領域を覆う第2の絶縁膜と、

前記第2の絶縁膜の上に設けられた多結晶半導体領域と、

前記第2の第1導電型半導体領域および前記第1の第2導電型半導体領域の両方に接触する第1の電極と、

前記第1の電極と前記多結晶半導体領域との間に設けられた第3の絶縁膜と、

前記単結晶半導体基板の第2の主面に沿って設けられた第2の第2導電型半導体領域と

前記第2の第2導電型半導体領域に接触する第2の電極と、

を備え、

前記第1の第1導電型半導体領域は、前記単結晶半導体基板よりも高濃度の第1導電型 にドープされており、

前記単結晶半導体基板が単結晶シリコンでできており、

前記第1の第1導電型半導体領域、前記第2の第1導電型半導体領域および前記第1の 第2導電型半導体領域よりなる半導体膜の全部が、単結晶シリコンよりも移動度が低い多 結晶シリコンでできていることを特徴とする半導体装置。

### 【請求項2】

前記単結晶半導体基板と前記第2の第2導電型半導体領域との間に、前記単結晶半導体 基板よりも高不純物濃度の第3の第1導電型半導体領域が設けられていることを特徴とす る請求項1に記載の半導体装置。

#### 【請求項3】

単結晶シリコンからなる第1導電型単結晶半導体基板の第1の主面上に第1の絶縁膜を 形成する第1の工程と、

前記第1の絶縁膜の一部を除去して窓部を形成する第2の工程と、

前記第1の絶縁膜および前記単結晶半導体基板の、前記窓部において露出した部分の上に、単結晶シリコンよりも移動度が低い多結晶シリコンからなる第1導電型半導体膜を積層する第3の工程と、

前記第1導電型半導体膜の上に第2の絶縁膜および多結晶半導体膜を順次形成する第4 の工程と、

前記多結晶半導体膜の一部を除去して、前記第1導電型半導体膜の、前記単結晶半導体基板と接触する第1の第1導電型半導体領域の上の部分に前記多結晶半導体膜を残し、前記第1導電型半導体膜の、前記第1の絶縁膜と前記第1の主面との間に第1の第2導電型半導体領域を形成し、さらに該第1の第2導電型半導体領域を形成する第5の工程と、

前記多結晶半導体膜の上に第3の絶縁膜を積層し、該第3の絶縁膜にコンタクトホールを開口して前記第2の第1導電型半導体領域および前記第1の第2導電型半導体領域の一部を露出させ、前記第3の絶縁膜の上に、前記コンタクトホールを介して前記第2の第1導電型半導体領域および前記第1の第2導電型半導体領域の一部に接触する第1の電極を形成する第6の工程と、

前記単結晶半導体基板の第2の主面を研削し、その研削面に沿って第2の第2導電型半 導体領域を形成する第7の工程と、

前記第2の第2導電型半導体領域に接触する第2の電極を形成する第8の工程と、 を含み、

前記第3の工程において、前記第1導電型半導体膜を、前記単結晶半導体基板よりも高 濃度の第1導電型にドープすることを特徴とする半導体装置の製造方法。

### 【請求項4】

前記第7の工程において、前記単結晶半導体基板の第2の主面を研削した後に、その研削面に沿って前記単結晶半導体基板よりも高不純物濃度の第3の第1導電型半導体領域を前記第2の第2導電型半導体領域よりも深く形成することを特徴とする請求項3に記載の半導体装置の製造方法。

### 【請求項5】

前記単結晶半導体基板の、前記第1の絶縁膜の窓部において前記第1の第1導電型半導体領域が接する部分に第2導電型拡散層がセルごとに独立して設けられていることを特徴とする請求項1または2に記載の半導体装置。

## 【請求項6】

順電圧阻止時の印加電圧が、素子内のいずれの部分においてもアバランシェ降伏が発生しない範囲内の電圧であるときに、前記第2導電型拡散層が完全に空乏化することを特徴とする請求項5に記載の半導体装置。

#### 【請求項7】

前記第2導電型拡散層内の、前記第1の絶縁膜の窓部において前記第1の第1導電型半 導体領域が接する部分に第1導電型拡散層が設けられていることを特徴とする請求項5ま たは6に記載の半導体装置。 10

20

30

40

#### 【請求項8】

順電圧阻止時の印加電圧が、素子内のいずれの部分においてもアバランシェ降伏が発生 しない範囲内の電圧であるときに、前記第1導電型拡散層が完全に空乏化することを特徴 とする請求項7に記載の半導体装置。

### 【請求項9】

前記第1導電型拡散層が前記多結晶半導体領域の下まで伸びていることを特徴とする請求項8に記載の半導体装置。

### 【請求項10】

前記第2の工程と前記第3の工程の間に、前記第1の絶縁膜の窓部からイオン注入を行って、前記単結晶半導体基板の、前記第1の第1導電型半導体領域が接する部分に自己整合的に第2導電型拡散層をセルごとに独立して形成する工程をさらに有することを特徴とする請求項3または4に記載の半導体装置の製造方法。

### 【請求項11】

前記第2導電型拡散層を形成する際に、同第2導電型拡散層内の、前記第1の第1導電型半導体領域が接する部分に第1導電型拡散層を形成することを特徴とする請求項10に記載の半導体装置の製造方法。

【発明の詳細な説明】

#### 【技術分野】

#### [00001]

この発明は、半導体装置およびその製造方法に関し、特にIGBT(絶縁ゲート型バイポーラトランジスタ)を構成するパワー半導体装置およびその製造方法に関する。

#### 【背景技術】

## [0002]

IGBTについては、これまで数多くの改良によって、その性能の向上が図られてきている。ここで、IGBTの性能とは、オフ時には、電圧を保持して電流を完全に遮断し、一方、オン時には、できる限り小さい電圧降下、すなわち、できる限り小さいオン抵抗で電流を流すというスイッチとしての性能のことである。なお、IGBTの動作の本質に鑑みて、本明細書では、コレクタを「アノード」と表記し、エミッタを「カソード」と表記する。以下に、IGBTの特性等について説明する。

#### [0003]

(IGBT性能のトレードオフについて)

IGBTの保持可能な最大電圧、すなわち耐圧の大きさと、オン時の電圧降下との間には、二律背反の関係(いわゆるトレードオフ関係)が存在し、高耐圧のIGBTほどオン電圧が高くなる。最終的には、このトレードオフ関係の限界値は、シリコンの物性で決まる。このトレードオフを限界まで向上させるためには、電圧保持時に局所的な電界集中が生じるのを防ぐなど、設計面での工夫が必要である。

### [0004]

また、IGBTの性能を表すもう一つの重要な指標として、オン電圧とスイッチング損失(特に、ターンオフ損失)のトレードオフ関係がある。IGBTは、スイッチングデバイスであるため、オンからオフまたはオフからオンの動作を行う。このスイッチング動作の瞬間に、時間当たり大きな損失が発生する。一般に、オン電圧の低いIGBTほどターンオフが遅いので、ターンオフ損失が大きい。以上のようなトレードオフ関係を改善することによって、IGBTの性能の向上を図ることができる。なお、ターンオン損失のオン電圧に対する依存性は小さい。ターンオン損失は、IGBTと組み合わせて使われる還流ダイオードの特性に大きく左右される。

### [0005]

### (トレードオフの改善について)

オン電圧とターンオフ損失のトレードオフ関係(以下、オン電圧 - ターンオフ損失の関係とする)を最適化するには、IGBTがオン状態のときの内部の過剰キャリア分布を最適化することが有効である。オン電圧を下げるには、過剰キャリア量を増やしてドリフト

10

20

30

40

層の抵抗値を下げればよい。しかし、ターンオフ時には、この過剰キャリアをすべてデバイスの外に掃き出すか、または、電子 - ホール再結合により消滅させる必要がある。そのため、過剰キャリア量を増やすと、ターンオフ損失が増加してしまう。従って、このトレードオフ関係を最適化するには、同じオン電圧でターンオフ損失を最小にすればよい。

### [0006]

最適なトレードオフを実現するには、アノード側のキャリア濃度を下げるとともに、カソード側のキャリア濃度を上げることによって、アノード側とカソード側のキャリア濃度の比率が1:5程度になるようにすればよい。さらに、ドリフト層のキャリアライフタイムをできるだけ大きく保つことによって、ドリフト層内の平均キャリア濃度が高くなるようにすればよい。

### [0007]

IGBTのターンオフ時には、空乏層は、カソード側のpn接合からドリフト層内部に拡がり、裏面のアノード層へ向かって進展する。その際、ドリフト層内の過剰キャリアのうち、ホールは、電界によって空乏層端から引き抜かれる。このようにして電子過剰状態となり、余った電子は、中性領域を抜けてp型のアノード層に注入される。そして、アノード側pn接合がやや順バイアスされることになるので、注入された電子に応じてホールが逆注入される。この逆注入されたホールは、上述した電界によって引き抜かれるホールと合流して、空乏層に入っていく。

#### [0008]

電荷の担い手であるキャリア(ここでは、ホール)が電界領域を通過してカソード側に抜けるため、電界はキャリアに対して仕事をすることになる。キャリアが電界から受けた仕事は、最終的には、シリコンなどの結晶格子との衝突による格子振動となり、熱として散逸する。この散逸するエネルギーがターンオフ損失となる。ところで、空乏層が伸びきらないうちに引き抜かれるキャリアによって散逸するエネルギーは、空乏層が伸びきったときに引き抜かれるキャリアによって散逸するエネルギーよりも小さい。これは、空乏層が伸びきっていないと、キャリアが空乏層を通過する際の電位差が小さいため、空乏層の電界から受ける仕事が少ないからである。

#### [0009]

ミクロの観点で見ると以上のようになる。これを、デバイスの端子電圧というマクロの観点で見ると、アノード - カソード間電圧が上がり終わる前、すなわち上昇中に流れる電流の方が、上がり終わった後に流れる電流よりも、電圧と電流の積(電圧×電流)で表される損失に対する寄与が少ないということを意味する。以上のことから、後述するIE効果によりカソード側に偏重したキャリア分布は、低電圧で引き抜かれるキャリアの割合が多く、オン電圧が同じであるという条件下では、アノード側偏重のキャリア分布よりもターンオフ損失が小さいということがわかる。

### [0010]

[0011]

アノード側のキャリア濃度を下げるには、アノード層の総不純物量を下げればよい。これ自体は、特に困難なことではない。ただし、600Vなどのように定格耐圧の低いIGBTでは、アノード層の総不純物量を下げるためには、製造工程中に、100μm程度の厚さ、あるいはそれよりも薄いウェハを扱う必要があるため、生産技術上の困難が存在する。一方、カソード側のキャリア濃度を上げるメカニズムは、IE効果と呼ばれている。

IE効果の大きいカソード構造として、プレーナ構造の p ベースを囲むように高濃度 n 層を挿入した H i G T 構造などが提案されている (例えば、特許文献 1、特許文献 2 参照。)。また、トレンチゲート構造において、隣り合うトレンチ間のメサ部に、ドリフト層よりも高濃度の n 層を挿入した C S T B T 構造や、 I E G T (インジェクション エンハンスメント ゲート トランジスタ)構造などが提案されている (例えば、特許文献 3、非特許文献 1 参照。)。一般に、トレンチ型における I E 効果よりも大きい。

### [0012]

20

10

30

20

30

40

50

#### (IE効果について)

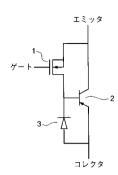

IE効果については、その本質が議論され、報告されている(例えば、非特許文献2参照。)。よく描かれるIGBTの等価回路は、MOSFET(金属-酸化膜-半導体構造を有する絶縁ゲート型電界効果トランジスタ)とバイポーラトランジスタの組み合わせである。しかし、実際のデバイス動作を考えると、図1に示す等価回路のように、MOSFET1とpnpバイポーラトランジスタ2とpinダイオード3の組み合わせであると考えられる。

### [0013]

### [0014]

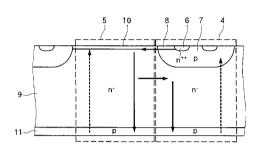

図2に示すように、電子は、MOS部の表面のn<sup>++</sup>領域6から、n<sup>++</sup>領域6を囲むp層7の表面のn<sup>+</sup>反転層8と、n<sup>-</sup>ドリフト層9の表面のn<sup>+</sup>電子蓄積層10を経由して、裏面のpアノード層11に向かって流れる。この電子電流の一部は、pnp-BJT領域4のベース電流となる。pnp-BJT領域4では、pアノード層11から拡散またはドリフトによって流れてきたホールがp層7に流れ込むだけであり、そのpn接合部は、若干逆バイアスされている。従って、そのpn接合部付近のn<sup>-</sup>ドリフト層9中の少数キャリア、すなわちホールの濃度は、極めて低い。

### [0015]

一方、pinダイオード領域5のnカソードは、n ドリフト層9の表面のn 電子蓄積層10である。このn + / n 接合は、若干順バイアスされているので、n ドリフト層9中に電子が注入される。大電流時には、電子濃度は、n ドリフト層9のドーピング濃度よりも遥かに高くなる(高注入状態)。そして、電荷中性条件を満たすため、電子と同じ濃度のホールも存在する。従って、n + / n 接合付近のn ドリフト層9中の少数キャリア、すなわちホールの濃度は、極めて高い。

### [0016]

IGBTにおいて、カソード側偏重の最適キャリア分布を実現するためには、pnp‐BJT領域を減らして、pinダイオード領域を増やすことが重要である。また、n⁺/n‐順バイアス量を増やして、電子注入を促進することが非常に重要である。これまで提案されたIE効果を有する構造では、pinダイオード領域の比率を増やすと同時に、n⁺/n‐順バイアスの増加も実現されている。

### [0017]

ところで、プレーナ構造において、セルピッチに占める p ベースの比率が小さくなると、オン電圧が低減する。これは、 p i n ダイオード領域の比率が大きくなることに加えて、表面付近での横方向電流密度が高くなり、電圧降下が大きくなることによって、 n <sup>+</sup> / n <sup>-</sup> 接合の順バイアスが大きくなる効果が大きいと考えられる。 n <sup>+</sup> / n <sup>-</sup> 接合の順バイアスが大きくなる理由は、 n <sup>+</sup> 層は低抵抗であるため、その電位がカソード電位に等しいが、 n <sup>-</sup> 層は高抵抗であるため、その電位が大電流により持ち上がるからである。

## [0018]

同様に、トレンチ構造において、pnp-BJT領域の比率を減らすことによって、IE効果を高めることができる。pnp-BJT領域の比率を減らすには、例えば一部のメサ部において、pベース領域をフローティング状態とすればよい。また、トレンチを深くして、トレンチ底部をpn接合から離すことによっても、IE効果が大きくなる。さらに

、メサ部の幅を狭くすることによっても、IE効果が大きくなる。これらは、いずれの場合も、メサ部を流れるホール電流密度が大きくなり、電圧降下による $n^+/n^-$ 順バイアスが強くなるためと考えられる。

### [0019]

ここで、ドリフト層のドーピング濃度をNdとし、 $n^+/n^-$ 接合にかかる順バイアスを V nとすると、 $n^+/n^-$ 接合の $n^-$ 層側の電子濃度 n は、次式で表される。ただし、k は ボルツマン定数であり、T は絶対温度である。

$n = Nd^*exp(Vn/kT)$

### [0020]

上記式より明らかなように、 $n^+/n^-$ 接合に印加される順バイアスに応じて、カソード側の電子濃度n は、指数関数的に増大する。順バイアス量を増やす手段として、上述したように、大電流による電圧降下を利用するものがある。また、上記特許文献  $1 \sim 3$  に記載されているように、 $n^+$ 濃度を増やすことによっても、順バイアス量を増やすことができる。ただし、特許文献 1 に記載されている1 に記載されている日 1 に記述されている日 1 に記述されている 1 に記述されている日 1 に記述されている日 1 に記述されている日 1 に記述されている 1 に記述されている

#### [0021]

一方、特許文献 3 に記載されている C S T B T 構造では、表面側の n \*バッファ層は、トレンチゲート酸化膜により挟まれており、そのゲート酸化膜を介してポリシリコン電位へと続いている。そのため、順電圧保持時、すなわちブロッキングモード時には、表面側の n \*バッファ層は、 p n 接合だけでなく、両側のトレンチゲート酸化膜との境界からも空乏化するので、低い順バイアスで完全に空乏化する。従って、表面側の n \*バッファ層は高濃度であるにもかかわらず、その内部の電界は緩和されている。順バイアスをさらに上げても、トレンチ間のメサ部の電界が緩和されていることによって、局所的なピーク電界が現れにくい。

### [0022]

これは、一様、かつ単一の導電型層よりなるドリフト層の代わりに、不純物濃度を高めた縦形層状の n 型領域と縦形層状の p 型領域を交互に繰り返し接合した並列 p n 構造をドリフト部に備える超接合構造のMOSFETの原理にも通ずるものである。このように、CSTBT構造は、IE効果を高めつつも、順耐圧が低下しにくいという特性を有する。表面側の n <sup>+</sup>バッファ層は、n <sup>-</sup>ドリフト層との間に拡散電位を作り、ホールにとっての電位障壁となるので、ドリフト層中のホール濃度が上昇する。

### [0023]

もう一つの説明として、表面側の n \*バッファ層と n <sup>-</sup> 層との間が順バイアスされるので、 n \*層から電子が注入されるからであるということができる。つまり、 n \* / n <sup>-</sup> 接合において、 n \*層が高濃度であれば、電子注入効率が向上するので、 n \*層に入るホール電流に対して、 n <sup>-</sup> 層に注入される電子電流の比率が大きくなる。ホールが n \*層中を少数キャリアとして拡散して流れるためには、 n \* / n <sup>-</sup> 接合が順バイアスされる必要がある。 n \*層濃度が高いほど、熱平衡状態における少数キャリアとしてのホール濃度が小さいため、同じホール電流を流すためには、より高い順バイアス量が必要となる。順バイアス量が大きいと、 n <sup>-</sup> 層に流れ込む電子電流が増えるので、電子濃度が増える。この第2の説明は、物理的には、先の第1の説明を言い換えたものである。

#### [0024]

【特許文献 1 】特開 2 0 0 3 - 3 4 7 5 4 9 号公報

【特許文献2】特表2002-532885号公報

【特許文献3】特開平8-316479号公報

【非特許文献1】アイ. オームラ (I. Omura)、他3名、「キャリア インジェクション エンハンスメント エフェクト オブ ハイ ボルテージ MOS デバイシズ - デバイス フィジックス アンド デザイン コンセプト - (Carrier injection enhancement effect of high voltage MOS devices -Device physics and design concept-)」、ISPSD'97、p.217-220

20

10

30

20

30

40

50

【非特許文献 2 】フロリン・ウドレア、他 1 名、「ア ユニファイド アナリティカル モデル フォア ザ キャリア ダイナミクス イン トレンチ インシュレイテッド ゲート バイポーラ トランジスタズ(TIGBT)(A unified analytical model for the carrier dynamics in Trench Insulated Gate Bipolar Transistors(TIGBT))」、 ISPSD'95、p. 190-195

### 【発明の開示】

【発明が解決しようとする課題】

### [0025]

上述したように、従来のIGBTでも、IE効果によるカソード側に偏重したキャリア分布が実現されている。しかしながら、オン電圧・ターンオフ損失のトレードオフを最適化するには、オン状態におけるカソード側のキャリア濃度をさらに高くする必要がある。つまり、従来のIGBTでは、IE効果がまだ不十分である。CSTBT構造やIEGT構造のように、トレンチゲート構造を採用したものでもトレードオフ特性が向上しているが、それでもなお、さらなる微細化によって特性を改善することができる余地がある。

#### [0026]

しかし、トレンチ構造の製造プロセスは、プレーナ構造の製造プロセスに比べて、長く、複雑である。そのため、トレンチ型デバイスの良品率は、プレーナ型デバイスの良品率よりも低い。従って、トレンチ型デバイスの製品コストは高い。それにもかかわらず、特性の向上を図るため、より一層の微細化を進めると、製造コストはさらに高くなってしまう。なお、トレンチゲート構造では、トレンチ底部に電界が集中しやすく、アバランシェ降伏を起こしやすいため、オン電圧・耐圧のトレードオフが悪化しやすい。また、構造上、ゲートをカソードに対して負電位にした場合に、トレンチ底部の電界強度が増し、さらに耐圧が劣化してしまうという問題を抱えている。

#### [0027]

この発明は、上述した従来技術による問題点を解消するため、従来よりもIE効果の大きい半導体装置、すなわちオン電圧・ターンオフ損失トレードオフが最適化された半導体装置を提供することを目的とする。また、電圧保持時に、局所的な電界集中を防ぐことによって、オン電圧・耐圧のトレードオフの悪化を招くことのない半導体装置を提供することを目的とする。さらに、このような特性を有する半導体装置を、極端に微細でない低コストの製造プロセスを用いて、高良品率で製造することができる半導体装置の製造方法を提供することを目的とする。

## 【課題を解決するための手段】

## [0028]

上述した課題を解決し、目的を達成するために、表面からの電子注入が促進されるような構造、すなわちIE効果の大きい構造を検討した結果、次のような特徴を有する構造が有効であることがわかった。第1に、表面側のpベース層とドリフト層との間に、高濃度のn゚・バッファ層を挿入する。ただし、順バイアス時に電界強度が大きくなりすぎないようにするため、電界が緩和されるような構造にする。第2に、pnp-BJTの面積比率をできるだけ小さくする。ただし、チャネルの実効周辺長が小さくなりすぎると、チャネル部のオン電圧降下が大きくなってしまうので注意が必要である。第3に、ホールがpベース層に流れ込むまでの電流経路を細く、かつ長くする。このような構造とすることによって、オン電圧・ターンオフ損失のトレードオフを改善することができる。

### [0029]

上述した構造を実現するため、<u>この</u>発明にかかる半導体装置は、第1導電型単結晶半導体基板の第1の主面を選択的に覆う第1の絶縁膜と、前記第1の絶縁膜上に設けられた多結晶半導体領域と、前記多結晶半導体領域の周囲を囲む第2の絶縁膜と、前記第1の絶縁膜の窓部において前記単結晶半導体基板に接触する第1の第1導電型半導体領域と、前記第1の絶縁膜の窓部の外側において前記第2の絶縁膜の上に設けられた第2の第1導電型半導体領域と、前記第1の第1導電型半導体領域との間の前記第2の絶縁膜の上に設けられた第1の第2導電型半導体領域と、前記第2の第1

導電型半導体領域および前記第1の第2導電型半導体領域の両方に接触する第1の電極と、前記第1の電極と前記第1の第1導電型半導体領域との間に設けられた第3の絶縁膜と、前記単結晶半導体基板の第2の主面に沿って設けられた第2の第2導電型半導体領域とする、前記第2の第2導電型半導体領域に接触する第2の電極と、を備えることを特徴とする

#### [0030]

<u>この</u>発明にかかる半導体装置は、<u>上記</u>の発明において、前記第1の第1導電型半導体領域は、前記単結晶半導体基板よりも高濃度の第1導電型にドープされていることを特徴とする。

### [0031]

<u>この</u>発明にかかる半導体装置は、<u>上記</u>の発明において、前記単結晶半導体基板と前記第2の第2導電型半導体領域との間に、前記単結晶半導体基板よりも高不純物濃度の第3の第1導電型半導体領域が設けられていることを特徴とする。

### [0032]

<u>この</u>発明にかかる半導体装置は、<u>上記</u>の発明において、前記第1の第1導電型半導体領域、前記第2の第1導電型半導体領域および前記第1の第2導電型半導体領域よりなる半導体膜の全部が多結晶シリコンでできていることを特徴とする。

#### [0033]

<u>この</u>発明にかかる半導体装置は、<u>上記</u>の発明において、前記第1の第1導電型半導体領域、前記第2の第1導電型半導体領域および前記第1の第2導電型半導体領域よりなる半導体膜の一部または全部が単結晶シリコンでできていることを特徴とする。

#### [0034]

また、この発明にかかる半導体装置は、第1導電型単結晶半導体基板の第1の主面を選択的に覆う第1の絶縁膜と、前記第1の絶縁膜の窓部において前記単結晶半導体基板に接触する第1の第1導電型半導体領域と、前記第1の絶縁膜の窓部の外側において前記第1の絶縁膜の上に設けられた第1の第2導電型半導体領域と、前記第1の第2導電型半導体領域、前記第2の第1導電型半導体領域と、前記第1の第1導電型半導体領域、前記第2の第1導電型半導体領域および前記第1の第2導電型半導体領域と、前記第2の第1導電型半導体領域と、前記第2の第1導電型半導体領域と、前記第2の第1導電型半導体領域と、前記第2の第1専電型半導体領域と、前記第2の第1専電型半導体領域と、前記第2の第1専電型半導体領域と、前記第2の第1専電型半導体領域と、前記第2の第2導電型半導体領域と、前記第2の第2導電型半導体領域と、前記第2の第1導電型半導体領域に接触する第2の電極を備え、前記第1の第1導電型半導体領域は、前記第2の第1導電型半導体領域は、前記第1の第1導電型半導体領域、前記第2の第1導電型半導体領域は、前記第2の第1導電型半導体領域は、前記第2の第1導電型半導体領域は、前記第2の第1導電型半導体領域は、前記第2の第1導電型半導体領域は、前記第2の第1導電型半導体領域は、前記第2の第1導電型半導体領域は、前記第2の第1導電型半導体領域は、前記第2の第1導電型半導体領域は、前記第2の第1導電型半導体領域は、前記第2の第1導電型半導体領域は、前記第2の第1導電型半導体領域は、前記第2の第1導電型半導体領域は、前記第2の第1導電型半導体領域は、前記第2の第1導電型半導体領域および前記第1の第1導電型半導体領域は、前記第2の第1導電型半導体領域および前記第1の第1等電型半導体領域は、前記第2の第1等

### [0036]

<u>この</u>発明にかかる半導体装置は、<u>上記</u>の発明において、前記単結晶半導体基板と前記第2の第2導電型半導体領域との間に、前記単結晶半導体基板よりも高不純物濃度の第3の第1導電型半導体領域が設けられていることを特徴とする。

#### [0039]

また、<u>この</u>発明にかかる半導体装置は、第1導電型単結晶半導体基板の第1の主面の下に選択的に埋め込まれた第1の絶縁膜と、前記第1の絶縁膜と前記第1の主面との間に設けられた第1の第2導電型半導体領域と、前記第1の第2導電型半導体領域内に設けられた第1導電型半導体領域と、前記第1の連縁膜が埋め込まれていない領域上の部分を覆う第2の絶縁膜と、前記第2の絶縁膜の上に設けられた多結晶半導体領域と、前記第1導電型半導体領域および前記第1の第2導電型半導体領域の両方に接触する第1の電極と、前記第1の電極と前記多結晶半導体領域との間に設けられた第3の絶縁膜と、前記単結晶半導体基板の第2の主面に沿って設けられた第2の第2導電型半導体領

10

20

30

40

域と、前記第2の第2導電型半導体領域に接触する第2の電極と、を備えることを特徴とする。

#### [0040]

<u>この</u>発明にかかる半導体装置は、<u>上記</u>の発明において、前記単結晶半導体基板と前記第2の第2導電型半導体領域との間に、前記単結晶半導体基板よりも高不純物濃度の第2の第1導電型半導体領域が設けられていることを特徴とする。

#### [0041]

また、この発明にかかる半導体装置の製造方法は、第1導電型単結晶半導体基板の第1 の主面上に第1の絶縁膜および多結晶半導体膜を順次形成する第1の工程と、前記多結晶 半導体膜の一部を除去して窓部を形成する第2の工程と、前記多結晶半導体膜の露出部分 を覆う第2の絶縁膜を形成した後、前記窓部において前記単結晶半導体基板の一部を露出 させる第3の工程と、前記単結晶半導体基板の、前記窓部において露出した部分、および 前記第2の絶縁膜の上に第1導電型半導体膜を積層する第4の工程と、前記第1導電型半 導体膜の、前記単結晶半導体基板と接触する第1の第1導電型半導体領域の隣に第1の第 2 導電型半導体領域を形成し、さらに該第1の第2導電型半導体領域を挟んで前記第1の 第 1 導電型半導体領域の反対側に第 2 の第 1 導電型半導体領域を形成する第 5 の工程と、 前記第1の第1導電型半導体領域、前記第1の第2導電型半導体領域および前記第2の第 1導電型半導体領域の上に第3の絶縁膜を積層し、該第3の絶縁膜にコンタクトホールを 開口して前記第2の第1導電型半導体領域および前記第1の第2導電型半導体領域の一部 を露出させる第6の工程と、前記第3の絶縁膜の上に、前記コンタクトホールを介して前 記第2の第1導電型半導体領域および前記第1の第2導電型半導体領域の一部に接触する 第1の電極を形成した後に、前記単結晶半導体基板の第2の主面を研削し、その研削面に 沿って第2の第2導電型半導体領域を形成する第7の工程と、前記第2の第2導電型半導 体領域に接触する第2の電極を形成する第8の工程を含むことを特徴とする。

#### [0042]

<u>この</u>発明にかかる半導体装置の製造方法は、<u>上記</u>の発明において、前記第4の工程において、前記第1導電型半導体膜を、前記単結晶半導体基板よりも高濃度の第1導電型にドープすることを特徴とする。

### [0043]

<u>この</u>発明にかかる半導体装置の製造方法は、<u>上記</u>の発明において、前記第7の工程において、前記単結晶半導体基板の第2の主面を研削した後に、その研削面に沿って前記単結晶半導体基板よりも高不純物濃度の第3の第1導電型半導体領域を前記第2の第2導電型半導体領域よりも深く形成することを特徴とする。

#### [0044]

<u>この</u>発明にかかる半導体装置の製造方法は、<u>上記</u>の発明において、前記第1導電型半導体膜を多結晶シリコンで形成することを特徴とする。

## [0045]

<u>この</u>発明にかかる半導体装置の製造方法は、<u>上記</u>の発明において、前記第1導電型半導体膜の一部または全部を単結晶シリコンで形成することを特徴とする。

## [0046]

また、この発明にかかる半導体装置の製造方法は、単結晶シリコンからなる第1導電型単結晶半導体基板の第1の主面上に第1の絶縁膜を形成する第1の工程と、前記第1の絶縁膜の一部を除去して窓部を形成する第2の工程と、前記第1の絶縁膜および前記単結晶半導体基板の、前記窓部において露出した部分の上に、単結晶シリコンよりも移動度が低い多結晶シリコンからなる第1導電型半導体膜を積層する第3の工程と、前記第1導電型半導体膜の上に第2の絶縁膜および多結晶半導体膜を順次形成する第4の工程と、前記多結晶半導体膜の一部を除去して、前記第1導電型半導体膜の、前記単結晶半導体基板と接触する第1の第1導電型半導体領域の上の部分に前記多結晶半導体膜を残し、前記第1導電型半導体膜の、前記第1の絶縁膜と前記第1の主面との間に第1の第2導電型半導体領域を形成し、さらに該第1の第2導電型半導体領域内に第2の第1導電型半導体領域を形成し、さらに該第1の第2導電型半導体領域内に第2の第1導電型半導体領域を形

10

20

30

40

成する第5の工程と、前記多結晶半導体膜の上に第3の絶縁膜を積層し、該第3の絶縁膜にコンタクトホールを開口して前記第2の第1導電型半導体領域および前記第1の第2導電型半導体領域の一部を露出させ、前記第3の絶縁膜の上に、前記コンタクトホールを介して前記第2の第1導電型半導体領域および前記第1の第2導電型半導体領域の一部に接触する第1の電極を形成する第6の工程と、前記単結晶半導体基板の第2の主面を研削し、その研削面に沿って第2の第2導電型半導体領域を形成する第7の工程と、前記第2の第2導電型半導体領域に接触する第2の電極を形成する第8の工程と、を含み、前記第3の工程において、前記第1導電型半導体膜を、前記単結晶半導体基板よりも高濃度の第1導電型にドープすることを特徴とする。

#### [0048]

<u>この</u>発明にかかる半導体装置の製造方法は、<u>上記</u>の発明において、前記第7の工程において、前記単結晶半導体基板の第2の主面を研削した後に、その研削面に沿って前記単結晶半導体基板よりも高不純物濃度の第3の第1導電型半導体領域を前記第2の第2導電型半導体領域よりも深く形成することを特徴とする。

#### [0052]

また、<u>この</u>発明にかかる半導体装置の製造方法は、第1導電型単結晶半導体基板の第1の主面の下に選択的に第1の絶縁膜を埋め込む第1の工程と、前記第1の主面上に第2の絶縁膜および多結晶半導体膜を順次形成し、該多結晶半導体膜および前記第2の絶縁膜の一部を除去して、前記第1の絶縁膜が埋め込まれていない領域上の部分に前記第1の絶縁膜の体膜および前記第2の絶縁膜を残す第2の工程と、前記第1の絶縁膜と前記第1の無る事との間に第1の第2導電型半導体領域を形成し、さらに該第1の第2導電型半導体領域内に第1の第2導電型半導体領域を形成する第3の工程と、前記多結晶半導体膜の上に第3の絶縁膜を積層し、該第3の絶縁膜にコンタクトホールを開口して前記第1導電型半導体領域および前記第1の第2導電型半導体領域の一部を露出させる第4の工程と、前記第3の絶縁膜の上に、前記コンタクトホールを介して前記第1導電型半導体領域および前記第1の第2導電型半導体領域の一部に接触する第1の電極を形成した後に、前記単結晶半導体基板の第2の主面を研削し、その研削面に沿って第2の第2導電型半導体領域を形成する第5の工程と、前記第2の第2導電型半導体領域に接触する第2の電極を形成する第6の工程を含むことを特徴とする。

### [0053]

<u>この</u>発明にかかる半導体装置の製造方法は、<u>上記</u>の発明において、前記第5の工程において、前記単結晶半導体基板の第2の主面を研削した後に、その研削面に沿って前記単結晶半導体基板よりも高不純物濃度の第2の第1導電型半導体領域を前記第2の第2導電型半導体領域よりも深く形成することを特徴とする。

### [0054]

<u>この</u>発明にかかる半導体装置の製造方法は、<u>上記</u>の発明において、前記第1の工程において、前記第1の絶縁膜を形成するために、前記単結晶半導体基板に選択的に酸素イオンを注入することを特徴とする。

### [0055]

<u>この</u>発明にかかる半導体装置の製造方法は、<u>上記</u>の発明において、前記第1の工程において、前記単結晶半導体基板に酸素イオンを注入した後、1000 以上の温度でアニールすることにより前記第1の絶縁膜を形成することを特徴とする。

### [0056]

また、<u>この</u>発明にかかる半導体装置は、<u>上記</u>の発明において、前記単結晶半導体基板の、前記第1の絶縁膜の窓部において前記第1の第1導電型半導体領域が接する部分に第2 導電型拡散層がセルごとに独立して設けられていることを特徴とする。

### [0057]

<u>この</u>発明にかかる半導体装置は、<u>上記</u>の発明において、順電圧阻止時の印加電圧が、素子内のいずれの部分においてもアバランシェ降伏が発生しない範囲内の電圧であるときに、前記第 2 導電型拡散層が完全に空乏化することを特徴とする。

10

20

30

#### [0058]

また、<u>この</u>発明にかかる半導体装置は、<u>上記</u>の発明において、前記第 2 導電型拡散層内の、前記第 1 の絶縁膜の窓部において前記第 1 の第 1 導電型半導体領域が接する部分に第 1 導電型拡散層が設けられていることを特徴とする。

### [0059]

また、<u>この</u>発明にかかる半導体装置は、<u>上記</u>の発明において、順電圧阻止時の印加電圧が、素子内のいずれの部分においてもアバランシェ降伏が発生しない範囲内の電圧であるときに、前記第1導電型拡散層が完全に空乏化することを特徴とする。

### [0060]

また、<u>この</u>発明にかかる半導体装置は、<u>上記</u>の発明において、前記第1導電型拡散層が 前記多結晶半導体領域の下まで伸びていることを特徴とする。

#### [0061]

また、<u>この</u>発明にかかる半導体装置の製造方法は、<u>上記</u>の発明において、前記第2の工程と前記第3の工程の間に、前記多結晶半導体膜の窓部からイオン注入を行って、前記単結晶半導体基板の、前記第1の第1導電型半導体領域が接する部分に自己整合的に第2導電型拡散層をセルごとに独立して形成する工程をさらに有することを特徴とする。

#### [0062]

また、<u>この</u>発明にかかる半導体装置の製造方法は、<u>上記</u>の発明において、前記第2の工程と前記第3の工程の間に、前記第1の絶縁膜の窓部からイオン注入を行って、前記単結晶半導体基板の、前記第1の第1導電型半導体領域が接する部分に自己整合的に第2導電型拡散層をセルごとに独立して形成する工程をさらに有することを特徴とする。

#### [ 0 0 6 3 ]

また、<u>この</u>発明にかかる半導体装置の製造方法は、<u>上記</u>の発明において、前記第 2 導電型拡散層を形成する際に、同第 2 導電型拡散層内の、前記第 1 の第 1 導電型半導体領域が接する部分に第 1 導電型拡散層を形成することを特徴とする。

### [0064]

本発明にかかる半導体装置によれば、第1導電型単結晶半導体基板よりなるドリフト層中のキャリア分布が表面偏重型になるので、オン電圧・ターンオフ損失のトレードオフが最適化される。その一方で、カソード領域中の電界強度の局所的なピークを抑えることによって、局所的なアバランシェ降伏が起こりにくくなり、十分な耐圧を確保することができるので、オン電圧・耐圧のトレードオフが悪化するのを防ぐことができる。また、本発明にかかる半導体装置の製造方法によれば、カソード領域が第1の絶縁膜によってドリフト層(第1導電型単結晶半導体基板)から隔てられているので、カソード領域の設計寸法は、ドリフト領域の特性に直接は寄与しない。従って、ソース領域を従来よりも微細化しなくても、トレードオフ特性は不変である。

### 【発明の効果】

## [0065]

本発明にかかる半導体装置およびその製造方法によれば、低コストの製造プロセスを用いて、高良品率で、オン電圧 - ターンオフ損失トレードオフおよびオン電圧 - 耐圧トレードオフの非常に良好なIGBT等の半導体装置を得ることができるという効果を奏する。 【発明を実施するための最良の形態】

#### [0066]

以下に添付図面を参照して、この発明にかかる半導体装置およびその製造方法の好適な実施の形態を詳細に説明する。なお、以下の説明では、第1導電型をn型とし、第2導電型をp型として説明するが、本発明はその逆の場合にも成り立つ。また、以下の説明およびすべての添付図面において、同様の構成には同一の符号を付し、重複する説明を省略する。

### [0067]

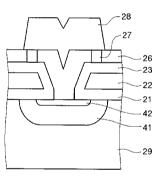

### 実施の形態1.

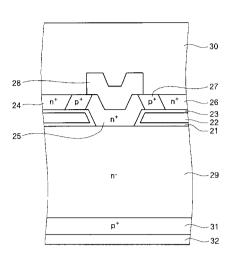

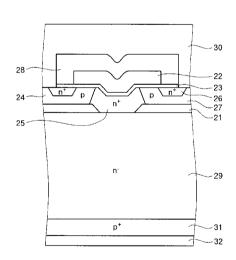

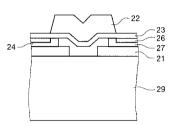

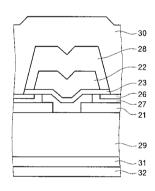

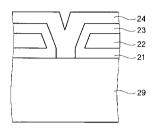

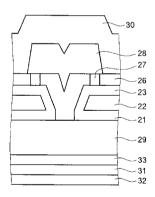

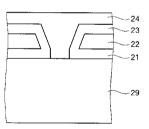

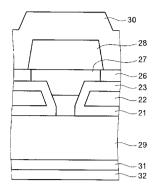

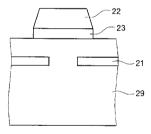

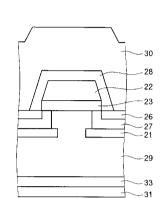

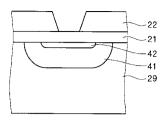

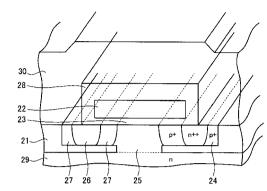

図3は、実施の形態1のIGBTの構成を示す断面図である。図3に示すように、ドリ

20

10

30

40

フト層となる n 単結晶シリコン基板 2 9 の第 1 の主面上に、例えば酸化膜(第 1 の絶縁膜) 2 1 が選択的に形成されている。そして、この酸化膜 2 1 の上に、ゲート電極となるポリシリコン(以下、ゲートポリシリコンとする) 2 2 が堆積されている。ゲートポリシリコン 2 2 の表面は、ゲート酸化膜(第 2 の絶縁膜) 2 3 で覆われている。

### [0068]

ゲート酸化膜23の表面、およびn<sup>単</sup>結晶シリコン基板29の、酸化膜21で覆われていない部分は、ドリフト層(n<sup>単</sup>結晶シリコン基板29)よりも高濃度にn型ドープされたカソード膜24で覆われている。カソード膜24は、例えばポリシリコンでできていてもよいし、n<sup>単</sup>結晶シリコン基板29の、酸化膜21で覆われていない部分からエピタキシャル成長したn型の単結晶シリコンでできていてもよい。カソード膜24の、n<sup>単</sup>結晶シリコン基板29と接触する部分は、n<sup>+</sup>バッファ領域(第1の第1導電型半導体領域)25となる。

#### [0069]

カソード膜 2 4 において、 $n^+$ バッファ領域 2 5 に隣接し、かつゲート酸化膜 2 3 に接する部分には、選択的に高濃度 p型にドープされた pベース領域(第 1 の第 2 導電型半導体領域) 2 7 が設けられている。pベース領域 2 7 の内部の、 $n^+$ バッファ領域 2 5 から離れた部分には、非常に高濃度の $n^+$ ソース領域(第 2 の第 1 導電型半導体領域) 2 6 が形成されている。カソード膜 2 4 の上には、例えば B P S G 等の酸化膜よりなる層間絶縁膜(第 3 の絶縁膜) 2 8 が選択的に形成されている。

### [0070]

層間絶縁膜 2 8 、  $n^+$ ソース領域 2 6 および pベース領域 2 7 の上には、エミッタ電極 (第 1 の電極) 3 0 となるアルミニウム層が形成されている。エミッタ電極 3 0 は、 $n^+$ ソース領域 2 6 の一部または全部とコンタクトしているとともに、pベース領域 2 7 の一部とコンタクトしている。 $n^-$ 単結晶シリコン基板 2 9 の第 2 の主面には、 $p^+$ アノード層 (第 2 の第 2 導電型半導体領域) 3 1 が形成されている。 $p^+$ アノード層 3 1 の表面には、アノード電極 (第 2 の電極) 3 2 となるアルミニウム層が形成されている。なお、特に図示しないが、ドリフト層と $p^+$ アノード層 3 1 との間に、ドリフト層( $n^-$ 単結晶シリコン基板 2 9 ) よりも高不純物濃度の $n^+$ バッファ層(第 3 の第 1 導電型半導体領域)が設けられていてもよい。

## [0071]

ここで、阻止時に耐圧を保持し、導通時には電流を流す n \*ドリフト層を n \*単結晶シリコン基板 2 9 で構成しているのは、以下の理由による。すなわち、ドリフト層は 1 次元的であり、複雑な構造をもたない。従って、物理特性がデバイスそのものの特性を左右する部分であり、物性定数(キャリア移動度およびキャリア寿命)を最大値に保つ必要があるからである。従って、単結晶を用いることが必須である。一方、カソードおよびアノードに関しては、それを構成する材料の物性定数は最重要ではなく、その構造の方が重要である。本実施の形態による I G B T では、カソード領域をドリフト層と構造的に分離している点に特徴があり、 I E 効果向上に有効である。

### [0072]

次に、実施の形態1の作用および効果について説明する。ここでは、カソード膜24がポリシリコンでできているとする。

#### [0073]

### (定常オン状態について)

ゲート電極(ゲートポリシリコン 2 2)にエミッタに対して正の電位を印加すると、 p ベース領域 2 7 の、ゲート酸化膜 2 3 との界面付近の領域が n 型に反転し、チャネルができる。コレクタ・エミッタ間に順バイアスを加えると、電子は、チャネルおよび電子蓄積層( $n^+$ バッファ領域 2 5)を経由して、ドリフト層( $n^-$ 単結晶シリコン基板 2 9)に流れ込み、裏面(第 2 の主面)の  $p^+$ アノード層 3 1 に達する。それによって、裏面の  $p^+$ アノード層 3 1 からドリフト層にホールが注入される。

10

20

30

#### [0074]

注入されたホールは、ドリフト層の表面(第1の主面)に来ると、n<sup>+</sup>バッファ領域25に入る。n<sup>+</sup>バッファ領域25に入ったホールの一部は、n<sup>+</sup>バッファ領域25内で電子と再結合して消滅する。残りのホールは、n<sup>+</sup>バッファ領域25を通過してpベース領域27に流れ込む。ホール電流は、狭くて長いポリシリコン領域(カソード膜24)を流れるため、電圧降下が発生する。従って、電子蓄積層であるn<sup>+</sup>バッファ領域25とn<sup>-</sup>ドリフト層とからなるn<sup>+</sup>/n<sup>-</sup>接合が順バイアスされる。これにより、電子が注入されて、カソード側の電子濃度が上昇し、それに応じて、電荷中性条件を満たすために同濃度のホールが蓄積される。

### [0075]

また、ホールは、 $n^+$ バッファ領域 2 5 に注入されるので、この $n^+$  /  $n^-$ 接合も順バイアスされることになり、電子が注入される。なお、ポリシリコン領域(カソード膜 2 4 )と $n^-$ 単結晶シリコン基板 2 9 とは、そのほとんどの部分において酸化膜 2 1 により分離されている。従って、pnp-BJT領域は、デバイス全体の僅かな部分であり、大部分は、pinダイオード領域である。また、面積を十分に使ってチャネルを形成することができ、チャネル周辺長も自在に大きくすることができる。ただし、周辺長が大きすぎると、伝達特性が高くなりすぎて、短絡時の制限電流が増大し、短絡耐量が低下してしまうので、この点を考慮して周辺長を決定する必要がある。

### [0076]

### (順方向ブロッキング状態について)

次に、ゲート電位をエミッタ電位に比べて同じか負にして、コレクタ・エミッタ間に順バイアスを印加するブロッキングモード時の動作について説明する。 pベース領域 2 7 と n  $^+$ バッファ領域 2 5 からなる p n 接合から空乏層が広がると同時に、ゲート酸化膜 2 3 からも空乏層が広がる。これは、ゲート電極がエミッタ電位以下であるのに対して、n バッファ領域 2 5 が正にバイアスされるからである。n  $^+$ バッファ領域 2 5 は、カソード膜 2 4 となるポリシリコンの厚さ分のみであるので、僅かな順バイアスで完全に空乏化する。n  $^+$ バッファ領域 2 5 の総不純物量を一定値以下に設定しておけば、n  $^+$ バッファ領域 2 5 中の最大電界強度を抑えることができる。

### [0077]

順バイアスをさらに増やしていくと、空乏層は、n・ドリフト層中に伸びる。印加した順バイアスの大部分は、n・ドリフト層によって担われる。カソード領域中の電界強度の局所的なピークを抑えることができるので、局所的なアバランシェ降伏が起こりにくい。従って、十分な耐圧を確保することができる。この結果として、オン電圧・耐圧トレードオフが悪化することはない。これは、従来のプレーナ型またはトレンチ型のIGBTでは、大変に優れている点である。従来のプレーナ型またはトレンチ型のIGBTでは、局所的な電界集中を避けることは困難である。

## [0078]

### (トレードオフ特性について)

ポリシリコンは、単結晶シリコンに比べて移動度およびキャリア寿命の点で劣る。しかし、1000 以上の高温でアニールすることによって、ポリシリコンの移動度およびキャリア寿命は、相当程度、回復する。レーザーアニールによって結晶粒径を制御しつつ移動度を回復する技術も開発されている。このような技術を用いれば、閾値や伝達特性などの特性バラツキを低減することが可能であると考えられる。

## [0079]

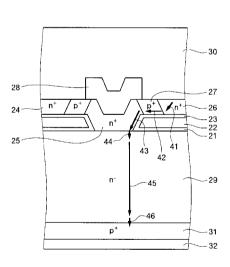

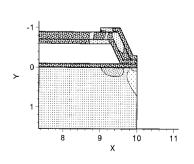

図4に、図3に示す構成のIGBTのオン状態における電位分担を示す。図4に示すように、IGBTのオン電圧は、 $n^+$ ソース領域26内での電圧降下(矢印41で示す)と、チャネル領域(pベース領域27)内での電圧降下(矢印42で示す)と、 $n^+$ バッファ領域25内での電圧降下(矢印43で示す)と、 $n^+$ バッファ領域25と $n^-$ ドリフト層( $n^-$ 単結晶シリコン基板29)との間の順バイアス(矢印44で示す)と、 $n^-$ ドリフト層中での電圧降下(矢印45で示す)と、 $n^-$ ドリフト層と $p^+$ アノード層31との間の電

10

20

30

40

圧降下(矢印46で示す)とを足した値となる。

### [0080]

$n^+ y - \lambda$  領域 2 6 内では、ドーピング濃度が非常に高いため、移動度が低くても抵抗が低いので、電圧降下はほとんどない。また、本実施の形態では、チャネル領域( $p^+ v - \lambda$  名領域 2 7 )の周辺長を比較的自在に設定することができるため、移動度劣化分を補うように周辺長を長くすることによって、電圧降下を従来の I G B T と同じ程度にすることができる。 $p^+ v - \lambda$  できる。 $p^+ v - \lambda$  では、ポリシリコンが低移動度であるため、電圧降下がやや増加するが、後のシミュレーションで示すように、全オン電圧への寄与は小さい。逆に、 $p^+ v - \lambda$  での電圧降下により、 $p^- v - \lambda$  での電位がエミッタ電位に対して上昇する。 $p^+ v - \lambda$  の  $p^+ v - \lambda$  の  $p^+ v - \lambda$  の表面の電子蓄積層では、電子濃度が非常に高く( $p^+ v - \lambda$   $p^+ v$

[0081]

このため、n<sup>+</sup>電子蓄積層とn<sup>-</sup>ドリフト層とからなる接合がより順バイアスされるので、電子が注入され易くなる。つまり、n<sup>+</sup>バッファ領域25において電圧降下が生じることにより、n<sup>-</sup>ドリフト層中のキャリア分布が表面偏重型になる。これによって、オン電圧-ターンオフ損失のトレードオフが最適化される。これは、特に高耐圧IGBTにおけるオン電圧分担の大部分を占めるn<sup>-</sup>ドリフト層中の電圧降下を、ある一定のターンオフ損失に対して最小化することを意味する。

[0082]

(ラッチアップ耐量について)

n <sup>+</sup>バッファ領域 2 5 中のキャリア寿命および移動度が低いと、少数キャリアであるホールの拡散長が短くなり、 n <sup>+</sup>バッファ領域 2 5 中でのキャリアの再結合が増える。その結果、 p ベース領域 2 7 を通り抜けてエミッタ電極 3 0 に流れ込むホール電流が減少する。このため、ラッチアップに寄与するホール電流が減少し、ラッチアップ耐量が向上する

[0083]

ここで、ポリシリコンの物性を敢えて回復させない場合には、 $n^+$ バッファ領域 2 5 中のホール拡散長が $n^+$ バッファ領域 2 5 の長さよりも遥かに短くなる。従って、ホールのほとんどが $n^+$ バッファ領域 2 5 内で再結合により消滅するので、pベース領域 2 7 に到達するホール電流はゼロになる。この場合には、ラッチアップの起こらない、すなわちラッチアップ・フリーの I G B T が実現される。これは、従来の I G B T とは動作が本質的に異なっている。この場合、pベース領域 2 7 は、B J T のコレクタとしては動作しないので、M O S F E T と B J T を組み合わせた従来の I G B T の等価回路モデルは成り立たない。このような I G B T を等価回路で表すと、M O S F E T と p i n ダイオードを組み合わせた回路になる。

[0084]

(微細プロセスについて)

上述したIGBTの構造には、極端な微細化が不要であるという設計上の長所がある。カソード領域は、酸化膜21によりドリフト層と電気的に分離されており、酸化膜21のない部分、すなわち酸化膜21の窓部においてのみドリフト層に接続している。そのため、カソード領域の設計寸法は、ドリフト層の特性には直接は寄与しない。これは、従来のプレーナ型またはトレンチ型のIGBTとは対称的である。従来のIGBTでは、カソード領域のすべてが直接的にドリフト層に接続しており、その設計寸法が直接的に特性に結びついている。従って、本実施の形態では、n+ソース領域26を特に微細化しなくても、トレードオフ特性は不変である。

[0085]

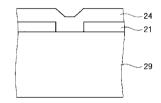

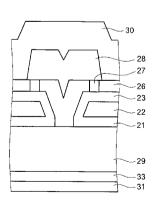

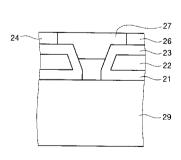

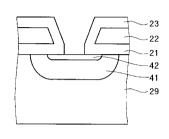

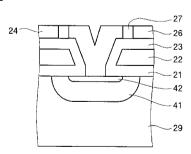

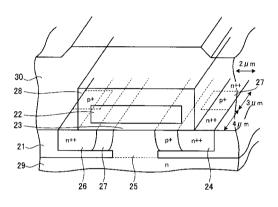

実施の形態2.

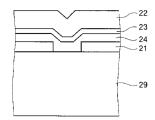

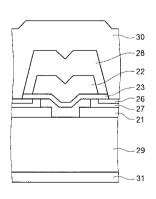

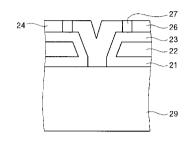

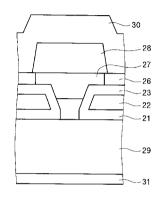

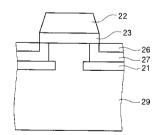

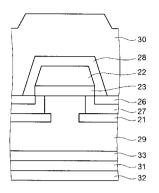

図 5 は、実施の形態 2 の I G B T の構成を示す断面図である。図 5 に示すように、実施の形態 2 が実施の形態 1 と異なるのは、第 1 に、第 1 の絶縁膜となる酸化膜 2 1 の表面と、n 単結晶シリコン基板 2 9 の、酸化膜 2 1 で覆われていない部分が、カソード膜 2 4

10

20

30

40

20

30

40

で覆われていることである。第 2 に、カソード膜 2 4 の表面にゲート酸化膜 2 3 が形成されており、このゲート酸化膜 2 3 上にゲートポリシリコン 2 2 が設けられていることである。第 3 に、ゲートポリシリコン 2 2 の上に層間絶縁膜 2 8 が設けられており、この層間絶縁膜 2 8 によりゲートポリシリコン 2 2 がエミッタ電極 3 0 から絶縁されていることである。第 4 に、エミッタ電極 3 0 が、層間絶縁膜 2 8 およびゲート酸化膜 2 3 を貫通するコンタクトホールを介して  $n^+$ ソース領域 2 6 および p ベース領域 2 7 に接触していることである。

### [0086]

カソード膜 2 4 において、 $n^+$ バッファ領域 2 5 は、 $n^-$ 単結晶シリコン基板 2 9 と接触する部分であり、pベース領域 2 7 は、酸化膜 2 1 の窓部の外側において酸化膜 2 1 の上に設けられている。 $n^+$ ソース領域 2 6 は、pベース領域 2 7 の内部の表面領域に設けられている。その他の構成は、実施の形態 1 と同じである。なお、実施の形態 1 と同様に、ドリフト層と $p^+$ アノード層 3 1 との間に、第 3 の第 1 導電型半導体領域となる高不純物濃度の $n^+$ バッファ層が設けられていてもよい。また、実施の形態 2 の作用および効果も、実施の形態 1 と同じであるので、説明を省略する。

#### [0087]

実施の形態 2 では、ゲート電極(ゲートポリシリコン 2 2 )をカソードに対して正電位にすると、 p ベース領域 2 7 の、ゲート酸化膜 2 3 との界面付近の領域に電子が誘起されて、チャネルが形成される。電子は、このチャネルを通って n <sup>+</sup>バッファ領域 2 5 に入る。 n <sup>+</sup>バッファ領域 2 5 の表面には、極めて高濃度の電子蓄積層が形成されているので、電子電流の多くはこの電子蓄積層を経由して流れる。そして、電子は、ドリフト層(n <sup>-</sup> 単結晶シリコン基板 2 9 )に入ると、電界ドリフトにより裏面の p <sup>+</sup>アノード層 3 1 に注入される。 p <sup>+</sup>アノード層 3 1 に注入される。 p <sup>+</sup>アノード層 3 1 に注入された電子は、拡散によってアノード電極 3 2 まで移動する。

#### [0088]

$n^-$ ドリフト層と $p^+$ アノード層 3 1 との接合が順バイアスされるので、ホールがアノードから注入されて、 $n^-$ ドリフト層中を電界ドリフトにより移動し、 $n^+$ バッファ領域 2 5 に入る。ホールの大部分は、その拡散長が短いため、 $n^+$ バッファ領域 2 5 および  $n^+$ バッファ領域 2 5 の電子蓄積層において電子と再結合して、消滅する。電子蓄積層と $n^-$ ドリフト層とからなる接合が順バイアスされるので、電子蓄積層からの電子注入が促進される(I E 効果)。このため、カソード側のキャリア濃度が高まり、オン電圧・スイッチング損失のトレードオフが良好となる。

#### [0089]

### 実施の形態3.

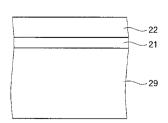

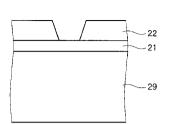

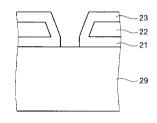

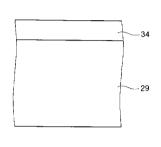

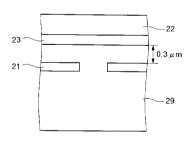

図6~図13は、実施の形態3の製造方法を説明するための断面図である。特に限定しないが、実施の形態3では、実施の形態2の構造を適用した定格600V耐圧のノンパンチスルー型IGBTを製造する場合について説明する。まず、 $n^-$ 単結晶シリコン基板29として、例えば30 cmのn型FZシリコン基板を用意する。そして、熱酸化を行い、その基板のミラー研磨面に例えば0.1 $\mu$ mの厚さの酸化膜21を成長させる(図6)。次いで、パターニングおよびエッチングを行って、酸化膜21の一部を除去する(図7)。

#### [0090]

### [0091]

20

30

40

50

次いで、ゲート酸化膜 2 3 の上に、ゲート電極となるゲートポリシリコン 2 2 を例えば 0 . 5  $\mu$  m の厚さに堆積する。そして、例えば P O C  $1_3$  雰囲気中で 9 0 0 の熱処理を 行い、ゲートポリシリコン 2 2 を高濃度 n 型にドープする(図 9 )。次いで、パターニングおよびエッチングを行って、ゲートポリシリコン 2 2 の一部を除去する。残ったゲートポリシリコン 2 2 をマスクとして、カソード膜 2 4 に、例えば 5 × 1 0  $^{14}$  c m  $^{-2}$  のドーズ量のボロンと、例えば 1 × 1 0  $^{15}$  c m  $^{-2}$  のドーズ量の砒素をイオン注入する。そして、例えば窒素雰囲気中で 1 1 5 0 、 2 時間のドライブを行い、チャネル領域となる p ベース領域 2 7 と n  $^+$  ソース領域 2 6 を形成する(図 1 0 )。

### [0092]

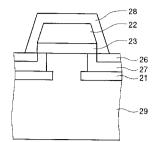

次いで、層間絶縁膜 2 8 として例えば 1  $\mu$  mの厚さの B P S G を堆積し、パターニング およびエッチングを行って、層間絶縁膜 2 8 およびゲート酸化膜 2 3 を貫通するコンタクトホールを形成する。次いで、層間絶縁膜 2 8 の上に、アルミニウム等の金属を例えば 5  $\mu$  mの厚さにスパッタする。そして、アルミニウム等の金属のパターニングおよびエッチングを行い、エミッタ電極 3 0 を形成する(図 1 1 )。次いで、 n - 単結晶シリコン基板 2 9 の裏面を研削して、ウェハ厚を例えば 1 0 0  $\mu$  mにする。その後、その研削面に、例えば 1 × 1 0 14 c m - 2 のドーズ量のボロンをイオン注入する。そして、例えば 3 8 0 で 1 時間のアニールを行い、p + アノード層 3 1 を形成する(図 1 2 )。

#### [0093]

#### [0094]

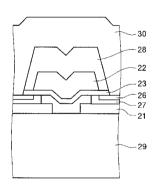

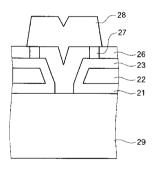

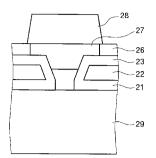

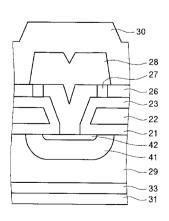

#### 実施の形態4.

図14~図21は、実施の形態4の製造方法を説明するための断面図である。特に限定しないが、実施の形態4では、実施の形態1の構造を適用した定格1200V耐圧のフィールドストップ型IBGTを製造する場合について説明する。ただし、実施の形態4では、ドリフト層(n‐単結晶シリコン基板29)とp⁺アノード層31との間に、フィールドストップ層として、ドリフト層よりも高不純物濃度のn⁺バッファ層33が形成される。

## [0095]

## [0096]

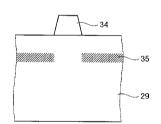

次いで、パターニングおよびエッチングを行って、ゲートポリシリコン 2 2 の一部を除去する(図 1 5)。次いで、熱酸化を行って、ゲートポリシリコン 2 2 の表面を酸化し、例えば 0 . 1  $\mu$  mの厚さのゲート酸化膜 2 3 を形成する。続いて、パターニングおよびエッチングを行って、ゲート酸化膜 2 3 および酸化膜 2 1 の、ゲートポリシリコン 2 2 のない部分を除去する(図 1 6)。次いで、ゲート酸化膜 2 3 および n 単結晶シリコン基板 2 9 の露出部分の上に、例えば 1  $\times$  1 0  $^{16}$  c m  $^{-3}$  の濃度で n 型にドープされたポリシリコンを例えば 0 . 2 5  $\mu$  mの厚さに堆積する(図 1 7)。このポリシリコンは、カソード膜 2 4 であり、後にソース領域、チャネル領域およびバッファ領域となる。

## [0097]

20

30

40

50

。その際、ポリシリコン(カソード膜 2 4 )の結晶粒径が大きくなり、移動度が回復する (図 1 8 )。

### [0098]

次いで、層間絶縁膜28として例えば1µmの厚さのBPSGを堆積し、パターニングおよびエッチングを行って、層間絶縁膜28を貫通するコンタクトホールを形成する(図19)。次いで、層間絶縁膜28の上に、アルミニウム等の金属を例えば5µmの厚さにスパッタする。そして、アルミニウム等の金属のパターニングおよびエッチングを行い、エミッタ電極30を形成する。次いで、n<sup>-</sup>単結晶シリコン基板29の裏面を研削して、ウェハ厚を例えば140µmにする。

### [0099]

その後、その研削面に、例えば  $2 \times 10^{12}$  c  $m^{-2}$  のドーズ量のリン、および例えば  $5 \times 10^{14}$  c  $m^{-2}$  のドーズ量のボロンをイオン注入する。そして、例えば 450 で 5 時間のアニールを行い、 $n^+$  バッファ層 33 および  $p^+$  アノード層 31 を形成する。 $n^+$  バッファ層 33 は  $p^+$  アノード層 31 よりも深い位置に形成される(図 20)。次いで、 $p^+$  アノード層 31 の表面にアルミニウム、チタン、ニッケルおよび金等の金属を蒸着し、アノード電 32 を形成する(図 21)。最後に、ウェハをダイシングしてチップが完成する。

### [0100]

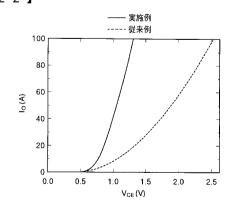

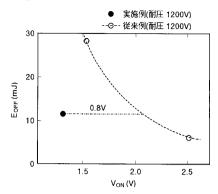

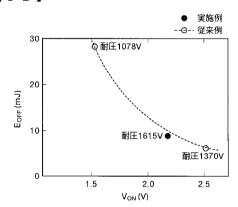

図22は、実施の形態4により製造された定格1200V耐圧のフィールドストップ型IGBT(実施例とする)と、従来の定格1200V耐圧のフィールドストップ型IGBT(従来例とする)の出力特性を示す特性図である。図22に示すように、温度125、電流密度100A/cm²において、実施例のオン電圧は1.4Vであった。それに対して、従来例のオン電圧は2.2Vであった。従って、実施例の方がオン電圧が低いことが確認された。

#### [0101]

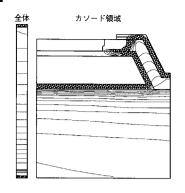

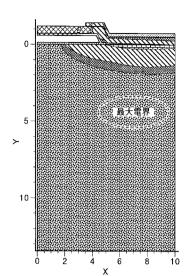

図23に、実施の形態4により製造された定格1200V耐圧のフィールドストップ型IGBTの定常オン状態時のオン電圧分担を示す。図23は、コレクタ・エミッタ間に2Vの電圧を印加した場合に、デバイスの各領域が分担しているバイアスの大きさを表している。全体図(図23の左側の図)を見ると、キャリア濃度の高い表面側(図の上側)では、電気抵抗が低いため、等電位線の間隔が広くなっている。それに対して、キャリア濃度の低い裏面側(図の下側)では、電気抵抗が高いため、等電位線の間隔が狭くなっている。

## [0102]

また、図23のカソード領域の拡大図(図23の右側の図)を見ると、表面のカソード領域(カソード膜24のポリシリコン領域)では、キャリア移動度が単結晶シリコンの1/3以下であるにもかかわらず、等電位線間隔が広い、すなわち抵抗が低いことがわかる。これは、電流の多くが電子蓄積層を流れるからである。また、電子およびホールのライフタイムは、500psである。ポリシリコン中のホール拡散長は、0.5µm程度である。従って、カソード領域に入ったホールの多くは、n<sup>+</sup>バッファ領域25内で再結合により消滅する。また、pベース領域27内のホール電流が極めて小さいために、従来のIGBTで見られたpベース領域内での電圧降下がない。従って、n<sup>+</sup>ソース領域26とpベース領域27との接合が順バイアスされないので、ラッチアップによるサイリスタ動作は起こらない。つまり、ラッチアップ・フリーであるので、短絡耐量および逆バイアス安全動作領域の向上が期待される。

## [0103]

ただし、カソード領域内のホールライフタイムが短すぎると、 n \*バッファ領域 2 5 内のホール電流密度が低くなり、 n \*バッファ領域 2 5 内での電圧降下が小さくなる。この場合、電子蓄積層と n \*ドリフト層との接合の順バイアス量が減少するので、カソード領域からの電子注入が減少してしまう。従って、ある程度のホール電流を確保することによって、 n \*バッファ領域 2 5 内での電圧降下を発生させる方が、 I E 効果が向上する。結果的に、 n \*ドリフト層内のキャリア分布が最適化されることによって、 n \*バッファ領域

25内の電圧降下は相殺される。

### [0104]

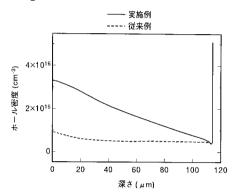

図24は、実施の形態4により製造された定格1200V耐圧のフィールドストップ型IGBT(実施例とする)と、従来の定格1200V耐圧のフィールドストップ型IGBT(従来例とする)のオン状態における縦方向過剰キャリア分布を示す特性図である。図24に示すように、実施例では、カソード側キャリア濃度がアノード側キャリア濃度の約5倍高くなっており、理想的な分布となっていることが確認された。また、図25は、実施の形態4により製造された定格1200V耐圧のフィールドストップ型IGBT(従来例とする)と、従来の定格1200V耐圧のフィールドストップ型IGBT(従来例とする)のオン電圧-ターンオフ損失のトレードオフを示す特性図である。図25に示すように、実施例のトレードオフが従来例に比べて大きく改善されていることが確認された。

[0105]

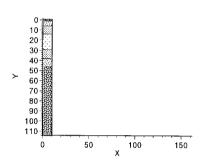

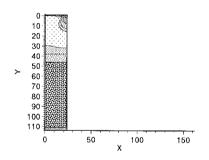

図26は、実施の形態4により製造された定格1200V耐圧のフィールドストップ型 IGBT(実施例とする)のブロッキングモード時の電界分布を示す図である。また、図27は、従来の定格1200V耐圧のフィールドストップ型IGBT(従来例とする)のブロッキングモード時の電界分布を示す図である。両図より、電流1mAのときの実施例の耐圧は1420Vであり、従来のIGBTの耐圧(1370V)よりも改善されていることが確認された。実施例のブロッキングモード時には、電界が平均化されており、1次元理想耐圧に近い数値が得られる。このため、ウェハをさらに薄くしても、従来例と同程度の耐圧を得ることができる。当然のことながら、実施例のオン電圧は低減される。これは、実施例のオン電圧・耐圧のトレードオフが優れていることを意味している。

[ 0 1 0 6 ]

また、図28は、実施の形態4により製造された定格1200V耐圧のフィールドストップ型IGBTのブロッキングモード時の電界分布を拡大して示す図である。図28より、ポリシリコン(カソード膜24)と単結晶シリコン(n<sup>-</sup>単結晶シリコン基板29)との境界面付近で最大電界となっていることがわかる。

#### [0107]

実施の形態5.

図29~図33は、実施の形態5の製造方法を説明するための断面図である。特に限定しないが、実施の形態5では、実施の形態1の構造を適用した定格600V耐圧の逆阻止型IBGTを製造する場合について説明する。ただし、図29~図33には、活性部のみが示されており、分離層領域については図示省略されている。また、分離層領域を形成するプロセスについても図示省略する。

[0108]

まず、 $n^-$ 単結晶シリコン基板 29 として、例えば 30 cmのn 型 F Z シリコン基板 を用意する。そして、分離層領域を形成するために、熱酸化を行い、その基板のミラー研 磨面に例えば 1.6  $\mu$  mの厚さの酸化膜を成長させる。続いて、パターニングおよびエッチングを行って、その酸化膜の一部を除去する。次いで、ボロンソースを塗布し、酸素雰 囲気中で 1.3.0.0 、9.0 時間のドライブを行い、分離層領域を形成する。

[0109]

次いで、熱酸化を行い、例えば  $0.1 \mu m$ の厚さの酸化膜 2.1 を成長させる。続いて、酸化膜 2.1 の上にゲートポリシリコン 2.2 を例えば  $0.5 \mu m$ の厚さに堆積する。そして、例えば  $POC1_3$  雰囲気中で 9.00 の熱処理を行い、ゲートポリシリコン 2.2 を高濃度 n 型にドープする。次いで、パターニングおよびエッチングを行って、ゲートポリシリコン 2.2 の一部を除去する。次いで、熱酸化を行って、ゲートポリシリコン 2.2 の表面を酸化し、例えば  $0.1 \mu m$ の厚さのゲート酸化膜 2.3 を形成する。続いて、パターニングおよびエッチングを行って、ゲート酸化膜 2.3 および酸化膜 2.1 の、ゲートポリシリコン 2.2 のない部分を除去する(図 1.4、図 1.5 および図 1.6 参照)。

[0110]

次いで、 n <sup>-</sup> 単結晶シリコン基板 2 9 の開口部分から、例えば 1 × 1 0 <sup>16</sup> c m <sup>-3</sup>濃度の

10

20

30

40

リンを含む単結晶シリコン層をエピタキシャル法により成長させる。エピタキシャル成長層は、まず n 単結晶シリコン基板 2 9 の開口部分から上方向に向かって成長し、ゲート酸化膜 2 3 上には成長しない。そして、エピタキシャル成長層は、ゲート酸化膜 2 3 の上面の高さまで成長すると、上方向および横方向に向かって成長を続ける。やがて、 n 単結晶シリコン基板 2 9 の隣り合う開口部分から成長してきたエピタキシャル成長層同士が接触し、ゲート酸化膜 2 3 の上面がエピタキシャル成長層で完全に覆われる。このエピタキシャル成長した単結晶シリコン層は、カソード膜 2 4 であり、後にソース領域、チャネル領域およびバッファ領域となる(図 2 9)。

### [0111]

次いで、カソード膜 2 4 に、例えば 1 .  $5 \times 10^{14}$  c m  $^{-2}$  のドーズ量のボロンをイオン注入する。続いて、パターニングしたレジストをマスクとして、カソード膜 2 4 に、例えば  $1 \times 10^{15}$  c m  $^{-2}$  のドーズ量の砒素をイオン注入する。そして、レジストを灰化した後に、例えば窒素雰囲気中で 1 1 5 0 、 2 時間のドライブを行い、チャネル領域となる p ベース領域 2 7 と n  $^+$  ソース領域 2 6 を形成する(図 3 0 )。次いで、層間絶縁膜 2 8 として例えば  $1 \mu$  m の厚さの B P S G を堆積し、パターニングおよびエッチングを行って、層間絶縁膜 2 8 を貫通するコンタクトホールを形成する(図 3 1 )。

### [0112]

次いで、層間絶縁膜 2 8の上に、アルミニウム等の金属を例えば 5  $\mu$  mの厚さにスパッタする。そして、アルミニウム等の金属のパターニングおよびエッチングを行い、エミッタ電極 3 0 を形成する。次いで、 n 単結晶シリコン基板 2 9 の裏面を研削して、ウェハ厚を例えば 1 0 0  $\mu$  mにする。その後、その研削面に、例えば 1 x 1 0  $^{14}$  c m  $^{-2}$  のドーズ量のボロンをイオン注入する。そして、例えば 3 8 0 で 1 時間のアニールを行い、 p  $^+$  アノード層 3 1 を形成する(図 3 2 )。次いで、 p  $^+$  アノード層 3 1 の表面にアルミニウム、チタン、ニッケルおよび金等の金属を蒸着し、アノード電極 3 2 を形成する(図 3 3 )。最後に、ウェハをダイシングしてチップが完成する。

### [0113]

実施の形態5により製造された逆阻止型IBGTは、オン電圧・ターンオフ損失のトレードオフ特性に優れる。また、実施の形態5により製造された逆阻止型IBGTによれば、逆阻止型IBGTに特有の逆バイアス印加モードにおける逆方向漏れ電流が、従来の逆阻止型IBGTに比べて低減される。逆阻止型IGBTにおいては、裏面側のpn接合で発生した電子電流が表面側のpベース領域に注入されると、電子電流がpnp構造のベース電流となる。そのため、増幅効果により、大きなホール電流が表面側のpベース領域から注入される。

### [0114]

電子電流に対するホール電流の大きさ、すなわちエミッタ接地の増幅率を決定する大きな要因の一つは、pベース領域とn型ドリフト層との不純物量比である。この比の値が大きいと、エミッタ注入効率が増加し、増幅率が増大する。従来の定格 6 0 0 V 耐圧の逆阻止型 I B G T では、n 型ドリフト層の不純物量は 1 . 5 × 1 0  $^{12}$  c m  $^{-2}$  程度である。一方、pベース領域の不純物量は 1 . 5 × 1 0  $^{14}$  c m  $^{-2}$  程度であるから、pベース領域とn 型ドリフト層との不純物量比は 1 0 0 倍である。

## [0115]

それに対して、実施の形態 5 により製造された定格 6 0 0 V 耐圧の逆阻止型 I B G T では、 p ベース領域と n 型ドリフト層との不純物量比は 3 0 倍程度である。これは、実施の形態 5 でも p ベース領域 2 7 の不純物量は、従来の逆阻止型 I B G T と同じ 1 . 5 × 1 0  $^{14}$  c m  $^{-2}$  であるが、高濃度の n  $^{+}$  バッファ領域 2 5 が設けられていることによって、 n 型総不純物量が 5 × 1 0  $^{12}$  c m  $^{-2}$  程度に増加しているからである。

#### [0116]

このように、 p ベース領域と n 型ドリフト層との不純物量比が従来よりも低くなっていることによって、エミッタ注入効率が従来の 1 / 3 以下に低減される。このため、増幅率が低下するので、逆漏れ電流が従来の 1 / 3 以下に減少する。また、 p n p 構造の増幅率

10

20

30

40

が低減することによって、逆方向アバランシェ耐圧の向上が実現される。

### [0117]

実施の形態 6.

図34~図41は、実施の形態6の製造方法を説明するための断面図である。特に限定しないが、実施の形態6では、実施の形態2の構造を適用した定格600V耐圧のフィールドストップ型IBGTを製造する場合について説明する。ただし、実施の形態6では、ドリフト層(n 単結晶シリコン基板29)とp +アノード層31との間に、フィールドストップ層として、ドリフト層よりも高不純物濃度のn +バッファ層33が形成される。また、第1の絶縁膜となる酸化膜21は、n 単結晶シリコン基板29の表面(第1の主面)から所定の深さの所に形成され、その酸化膜21とn 単結晶シリコン基板29の表面との間に、n +ソース領域26およびp ベース領域27が形成される。

[0118]

[0119]

次いで、 1300 でアニールを行い、結晶欠陥を回復させる。これによって、図36に示すように、例えば $0.3\mu$  mの厚さの単結晶シリコンの下に、例えば $0.1\mu$  mの厚さの酸化膜 21 が選択的に形成される。この $0.3\mu$  mの厚さの単結晶シリコン層が実施の形態  $1\sim5$  におけるカソード膜 24 に相当する。マスクとした酸化膜 34 を除去した後、熱酸化を行い、基板表面を酸化し、例えば $0.1\mu$  mの厚さのゲート酸化膜 23 を形成する。その際、カソード膜 24 に相当する単結晶シリコン層が例えば $0.05\mu$  mほど膜減りするので、この単結晶シリコン層の厚さは、例えば $0.25\mu$  mとなる。

[0120]

次いで、ゲート酸化膜 2 3 の上にゲートポリシリコン 2 2 を例えば 0 . 5  $\mu$  mの厚さに堆積する。そして、例えば P O C  $1_3$  雰囲気中で 9 0 0 の熱処理を行い、ゲートポリシリコン 2 2 を高濃度 n 型にドープする(図 3 6)。次いで、パターニングおよびエッチングを行って、ゲートポリシリコン 2 2 およびゲート酸化膜 2 3 の一部を除去する(図 3 7)。残ったゲートポリシリコン 2 2 をマスクとして、カソード膜 2 4 に相当する単結晶シリコン層に、例えば 5 × 1 0  $^{14}$  c m  $^{-2}$  のドーズ量のボロンと、例えば 1 × 1 0  $^{15}$  c m  $^{-2}$  のドーズ量の砒素をイオン注入する。そして、例えば窒素雰囲気中で 1 1 5 0 、 2 時間のドライブを行い、チャネル領域となる p ベース領域 2 7 と n  $^+$  ソース領域 2 6 を形成する(図 3 8)。

[0121]

次いで、層間絶縁膜 2 8 として例えば 1  $\mu$  mの厚さの B P S G を堆積し、パターニング およびエッチングを行って、層間絶縁膜 2 8 を貫通するコンタクトホールを形成する(図 3 9)。次いで、層間絶縁膜 2 8 の上に、アルミニウム等の金属を例えば 5  $\mu$  mの厚さに スパッタする。そして、アルミニウム等の金属のパターニングおよびエッチングを行い、エミッタ電極 3 0 を形成する。次いで、 n 単結晶シリコン基板 2 9 の裏面を研削して、ウェハ厚を例えば 1 0 0  $\mu$  mにする。

[0122]

その後、その研削面に、例えば  $2 \times 10^{12}$  c m  $^{-2}$  のドーズ量のリン、および例えば  $5 \times 10^{14}$  c m  $^{-2}$  のドーズ量のボロンをイオン注入する。そして、例えば 1000 で 5 時間のアニールを行い、  $10^{+1}$  n  $10^{+1}$  n

10

20

40

30

ド電極32を形成する(図41)。最後に、ウェハをダイシングしてチップが完成する。 実施の形態6により製造されたIGBTによれば、特性バラツキが少ないという効果と、 漏れ電流が少ないという効果が得られる。

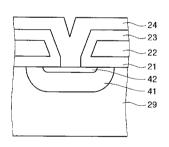

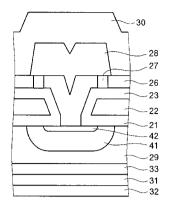

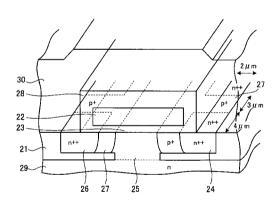

### [0123]

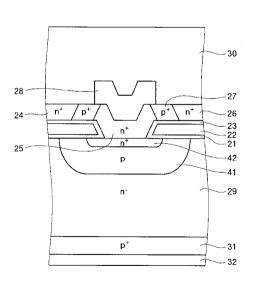

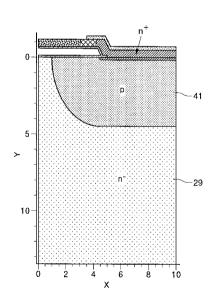

### 実施の形態7.

図42は、実施の形態7のIGBTの構成を示す断面図である。図42に示すように、実施の形態7が実施の形態1と異なるのは、 $n^{-1}$ 単結晶シリコン基板29の、 $n^{+1}$ バッファ領域25が接する部分にp拡散層41が設けられていることと、そのp拡散層41内の、 $n^{+1}$ バッファ領域25が接する部分に $n^{+1}$ 拡散層42が設けられていることである。

#### [0124]

$n^+$ 拡散層 4 2 は、ゲートポリシリコン 2 2 の下まで伸びている。すなわち、このデバイスをエミッタ電極 3 0 側から見たときに、 $n^+$ 拡散層 4 2 の縁がゲートポリシリコン 2 2 とオーバーラップしている。 p 拡散層 4 1 は、 $n^+$ 拡散層 4 2 を囲み、かつ隣接するセルの p 拡散層 4 1 (図には現れていない)に接触しないようにセルごとに独立して設けられている。その他の構成は、実施の形態 1 と同じである。

#### [0125]

これらp拡散層 4 1 および n \*拡散層 4 2 は、順電圧阻止時の印加電圧が、素子内のいずれの部分においてもアバランシェ降伏が発生しない範囲内の電圧であるときに、完全に空乏化する。次に、実施の形態 7 の作用および効果について説明する。実施の形態 7 では、実施の形態 1 の作用および効果に加えて、以下の作用および効果が得られる。

#### [0126]

### (定常オン状態について)

#### [0127]

そして、電子は、p拡散層 4 1 の表面が n 型に反転してできるチャネルを介して、ドリフト層 ( $n^-$ 単結晶シリコン基板 2 9)に流れ込み、裏面 (第 2 の主面)の $p^+$ アノード層 3 1 に達する。それによって、裏面のp n 接合、すなわち $p^+$ アノード層 3 1 とドリフト層との接合は順バイアスされるので、 $p^+$ アノード層 3 1 からドリフト層にホールが注入される。

### [0128]

注入されたホールは、p拡散層 4 1 を経由して n + 拡散層 4 2 に注入される。それによって、 n + 拡散層 4 2 と p 拡散層 4 1 との p n 接合が順バイアスされるので、 n + 拡散層 4 2 から p 拡散層 4 1 に電子が注入され、サイリスタ動作が開始される。この時点で、 p 拡散層 4 1 の表面のチャネルの役目は終了する。つまり、 p 拡散層 4 1 の表面のチャネルは、サイリスタをオンさせるためのものである。一旦サイリスタ動作が開始されると、 p 拡散層 4 1 が本来のドーピング濃度よりもキャリア濃度の高い高注入状態となるので、 p 拡散層 4 1 はデバイス特性にほとんど影響を及ぼさない。

#### [0129]

### (順方向ブロッキング状態およびターンオフ時の状態について)

順方向ブロッキングモード時においてn<sup>+</sup>バッファ領域25が完全に空乏化した後も順バイアスを増やしていくと、空乏層は、p拡散層41とドリフト層(n<sup>-</sup>単結晶シリコン基板29)とのpn接合からも伸び始める。このとき、印加した順バイアスの大部分は、n<sup>-</sup>ドリフト層によって担われる。そして、隣り合うp拡散層41間の距離は短いので、空乏層が容易にピンチオフする。それによって、pn接合の曲率を有する部分がなくなるので、従来のpn接合の曲率を有する部分に電界が集中するのを防ぐことができる。

### [0130]

10

20

30

20

30

40

50

### [0131]

順方向ブロッキングモード時において重要な点は、サイリスタがオン状態のときにカソードとして機能するn+バッファ領域25が完全に空乏化することである。これにより、ターンオフ時にサイリスタ動作が起こらない。つまり、n+バッファ領域25、n+拡散層42、p拡散層41およびn-ドリフト層(n-単結晶シリコン基板29)が空乏化することによって、それらの領域や層の本来の導電型がp型であるかn型であるかということは、デバイス特性に影響を及ぼさない。

### [0132]

このようにして、MOS型サイリスタ素子に特有の可制御電流が低いという問題が解消される。なお、ターンオフ時には、p拡散層41の表面のチャネルではなく、pベース領域27内のチャネルが消失することによって、電流の供給が遮断され、ターンオフ動作が開始される。

## [0133]

図43および図44は、それぞれ実施の形態7の構成を適用した定格1200V耐圧のフィールドストップ型IGBTのドーピング分布およびそれに対応するブロッキングモード時の電界分布を示す図である。これらの図から明らかなように、電界強度は、p拡散層41とn<sup>-</sup>ドリフト層(n<sup>-</sup>単結晶シリコン基板29)との接合部で最大となり、p拡散層41内を第1の主面に近づくに連れて弱くなる。従って、カソード領域中の電界強度が低くなり、カソード領域内でのアバランシェ降伏は起こりにくい。カソード膜24の結晶性に起因する耐圧低下が懸念される場合には、実施の形態7の構成によってカソード膜24内の電界が大きく緩和されるので、理想的な単結晶の平面接合耐圧を得ることができる。

## 【 0 1 3 4 】 実施の形態 8 .

図45~図51は、実施の形態8の製造方法を説明するための断面図である。特に限定しないが、実施の形態8では、実施の形態7の構造を適用した定格1200V耐圧のフィールドストップ型IBGTを製造する場合について説明する。ただし、実施の形態8では

、ドリフト層(n<sup>-</sup>単結晶シリコン基板 2 9)と p <sup>+</sup>アノード層 3 1 との間に、フィールドストップ層として、ドリフト層よりも高不純物濃度の n <sup>+</sup>バッファ層 3 3 が形成される。

### [0135]

まず、実施の形態 4 と同様にして、n <sup>-</sup>単結晶シリコン基板 2 9 、酸化膜 2 1 および n 型のゲートポリシリコン 2 2 の積層構造を形成する(図 1 4)。 n <sup>-</sup>単結晶シリコン基板 2 9 として、例えば 8 0 c mのn型 F Z シリコン基板を用いる。酸化膜 2 1 の厚さとゲートポリシリコン 2 2 の厚さは、実施の形態 4 と同じである。次いで、パターニングおよびエッチングを行って、ゲートポリシリコン 2 2 の一部を除去する。

#### [0136]

### [0137]

これ以降、チップの完成に至るまでのプロセスは、実施の形態 4 と同様である。従って、これ以降のプロセスについては、実施の形態 4 の説明において図 1 6 、図 1 7 、図 1 8

、図19、図20および図21をそれぞれ図46、図47、図48、図49、図50および図51と読み替えるものとして、重複する説明を省略する。

#### [0138]

図52は、実施の形態8により製造された定格1200V耐圧のフィールドストップ型IGBT(実施例とする)と、従来の定格1200V耐圧のフィールドストップ型IGBT(従来例とする)のオン電圧-ターンオフ損失のトレードオフを示す特性図である。図52に示すように、温度125、電流密度100A/cm²において、従来例に対して実施例の方が、トレードオフがやや向上していることが確認された。また、従来例の耐圧が1078~1370Vであるのに対して、実施例の耐圧は1615Vであり、耐圧が大幅(+250~+500V程度)に上昇していることが確認された。

### [0139]

実施の形態 8 により製造された定格 1 2 0 0 V 耐圧のフィールドストップ型 I G B T のプロッキングモード時の電界分布については、図 4 4 に示す通りである。電流 1 m A 時の耐圧は 1 6 1 5 V である。図 4 4 に示すように、p 拡散層 4 1 と n ドリフト層(n 単結晶シリコン基板 2 9 )との接合部で電界強度が最大となる。カソード膜 2 4 と単結晶シリコン (n \*拡散層 4 2 )との境界面付近の電界は、p 拡散層 4 1 によって緩和される。従って、カソード膜 2 4 がポリシリコンでできている場合、ポリシリコンに由来する衝突イオン化率の上昇などの問題が発生したとしても、これを隠蔽することができる。また、隣り合うp 拡散層 4 1 間の空乏層がピンチオフしているので、一次元平面接合の理想耐圧に近い耐圧が得られる。

#### [0140]

### 実施の形態9.

図53は、実施の形態9のIGBTの構成を示す要部断面斜視図である。図53に示すように、実施の形態9のIGBTは、図5に示す実施の形態2のIGBTと同様の断面構成を有する素子である。ただし、実施の形態9では、単結晶シリコン基板29の、酸化膜21の窓部において露出する部分から成長させたエピタキシャル層をカソード膜24としている。実施の形態9では、ストライプセルの上から見て、ソース領域26およびベース領域27の両方ともストライプ状に形成されている。そして、エミッタ電極30は、層間絶縁膜28に開口するコンタクトホールを介してソース領域26とベース領域27の両方に接触している。

### [0141]

デバイス特性の向上を図るためには、微細化によってセルピッチを縮小するのが有利である。従って、ソース領域26の幅は、狭い方が望ましい。しかし、層間絶縁膜28にコンタクトホールを形成する際のパターニングにおいてマスクずれが発生すると、エミッタ電極30がソース領域26に接触しないおそれがある。その場合には、電子電流が流れないため、IGBTがオン状態にならない。これを防ぐには、マスクずれが発生してもエミッタ電極30がソース領域26に確実に接触する程度に、ソース領域26の幅を広くする必要がある。

### [0142]

#### 実施の形態10.

図54は、実施の形態10のIGBTの構成を示す要部断面斜視図である。図54に示すように、実施の形態10のIGBTは、図53に示す実施の形態9のIGBTにおいて、ストライプセルの上から見て、ソース領域26を櫛歯状に形成し、ソース領域26の一部(櫛歯の先端部分)がエミッタ電極30の下側へ伸びてエミッタ電極30と接触し、また櫛歯の歯と歯の間の部分にベース領域27が露出してエミッタ電極30と接触するようにしたものである。なお、特に限定しないが、実施の形態10は、定格1200V耐圧のノンパンチスルー型IGBTの例である。

#### [0143]

実施の形態 9 の I G B T では、実施の形態 9 において説明したように、ソース領域 2 6 の幅を広くする必要があるため、セルピッチを十分に小さくすることができない。そのた

10

20

30

40

め、十分に優れたデバイス特性が得られない可能性がある。また、エミッタ電極 3 0 に接触するベース領域 2 7 が極端に狭くなると、コンタクト抵抗が上昇して寄生サイリスタがラッチアップしやすくなるため、逆バイアス安全動作領域(RBSOA)耐量および短絡耐量が低下するおそれがある。

### [0144]

### [0145]

#### 実施の形態11.

図55は、実施の形態11のIGBTの構成を示す要部断面斜視図である。図55に示すように、実施の形態11のIGBTは、図53に示す実施の形態9のIGBTにおいて、ストライプセルの上から見て、ソース領域26を不連続な島状(長方形状)に形成し、ソース領域26の一部がエミッタ電極30の下側へ伸びてエミッタ電極30と接触し、またソース領域26の島と島の間の部分でベース領域27にエミッタ電極30が接触するようにしたものである。なお、特に限定しないが、実施の形態11は、定格1200V耐圧のノンパンチスルー型IGBTの例である。実施の形態11によれば、実施の形態10と同様に、実施の形態9のIGBTの欠点を克服することができる。

#### [0146]

以上説明したように、実施の形態によれば、 n <sup>-</sup> 単結晶シリコン基板 2 9 よりなるドリフト層中のキャリア分布が表面偏重型になるので、オン電圧 - ターンオフ損失のトレードオフが最適化される。その一方で、カソード領域中の電界強度の局所的なピークを抑えることによって、局所的なアバランシェ降伏が起こりにくくなり、十分な耐圧を確保することができるので、オン電圧 - 耐圧のトレードオフが悪化するのを防ぐことができる。また、カソード領域が酸化膜 2 1 によってドリフト層から隔てられていることによって、カソード領域の設計寸法がドリフト領域の特性に直接、寄与しないので、従来よりも微細化しなくても、トレードオフ特性は不変である。従って、低コストの製造プロセスを用いて、高良品率で、オン電圧 - ターンオフ損失トレードオフおよびオン電圧 - 耐圧トレードオフの非常に良好なIGBTを得ることができる。

## [0147]

以上において、本発明は、上述した実施の形態に限らず、種々変更可能である。例えば、IGBTの耐圧クラス、各部の寸法や濃度、およびドーズ量などは一例であり、変更可能である。

## 【産業上の利用可能性】

## [0148]

以上のように、本発明にかかる半導体装置およびその製造方法は、電力変換装置などに 使用されるパワー半導体装置に有用であり、特に、IGBTに適している。

### 【図面の簡単な説明】

## [0149]

- 【図1】IGBTの等価回路を示す図である。

- 【図2】プレーナ型IGBTの要部の構成を示す断面図である。

- 【図3】実施の形態1のIGBTの構成を示す断面図である。

- 【図4】図3に示す構成のIGBTのオン状態における電位分担を説明するための断面図である。

- 【図5】実施の形態2のIGBTの構成を示す断面図である。

10

20

30

40

```

【図6】実施の形態3の製造方法を説明するための断面図である。

```

- 【図7】実施の形態3の製造方法を説明するための断面図である。

- 【図8】実施の形態3の製造方法を説明するための断面図である。

- 【図9】実施の形態3の製造方法を説明するための断面図である。

- 【図10】実施の形態3の製造方法を説明するための断面図である。

- 【図11】実施の形態3の製造方法を説明するための断面図である。

- 【図12】実施の形態3の製造方法を説明するための断面図である。

- 【図13】実施の形態3の製造方法を説明するための断面図である。

- 【図14】実施の形態4の製造方法を説明するための断面図である。

- 【図15】実施の形態4の製造方法を説明するための断面図である。

- 【図16】実施の形態4の製造方法を説明するための断面図である。

- 【図17】実施の形態4の製造方法を説明するための断面図である。

- 【図18】実施の形態4の製造方法を説明するための断面図である。

- 【図19】実施の形態4の製造方法を説明するための断面図である。

- 【図20】実施の形態4の製造方法を説明するための断面図である。

- 【図21】実施の形態4の製造方法を説明するための断面図である。

- 【図22】実施の形態4により製造されたIGBTの出力特性を示す特性図である。

- 【図23】実施の形態4により製造されたIGBTの定常オン状態時のオン電圧分担を示 す図である。

- 【図24】実施の形態4により製造されたIGBTのオン状態時の過剰キャリア分布を示 す特性図である。

- 【図25】実施の形態4により製造されたIGBTのオン電圧-ターンオフ損失のトレー ドオフを示す特性図である。

- 【図26】実施の形態4により製造されたIGBTのブロッキングモード時の電界分布を 示す図である。

- 【図27】従来のIGBTのブロッキングモード時の電界分布を示す図である。

- 【図28】実施の形態4により製造されたIGBTのブロッキングモード時の電界分布を 示す拡大図である。

- 【図29】実施の形態5の製造方法を説明するための断面図である。

- 【図30】実施の形態5の製造方法を説明するための断面図である。

- 【図31】実施の形態5の製造方法を説明するための断面図である。

- 【図32】実施の形態5の製造方法を説明するための断面図である。

- 【図33】実施の形態5の製造方法を説明するための断面図である。

- 【図34】実施の形態6の製造方法を説明するための断面図である。

- 【図35】実施の形態6の製造方法を説明するための断面図である。

- 【図36】実施の形態6の製造方法を説明するための断面図である。

- 【図37】実施の形態6の製造方法を説明するための断面図である。

- 【図38】実施の形態6の製造方法を説明するための断面図である。

- 【図39】実施の形態6の製造方法を説明するための断面図である。

- 【図42】実施の形態7のIGBTの構成を示す断面図である。

- 【図43】実施の形態7のIGBTのドーピング分布を示す図である。

- 【図45】実施の形態8の製造方法を説明するための断面図である。

- 【図46】実施の形態8の製造方法を説明するための断面図である。

- 【図47】実施の形態8の製造方法を説明するための断面図である。

- 【図48】実施の形態8の製造方法を説明するための断面図である。

- 【図49】実施の形態8の製造方法を説明するための断面図である。

- 【図50】実施の形態8の製造方法を説明するための断面図である。

20

30

- 【図40】実施の形態6の製造方法を説明するための断面図である。

- 【図41】実施の形態6の製造方法を説明するための断面図である。

- 【図44】実施の形態7のIGBTのブロッキングモード時の電界分布を示す図である。

50

20

- 【図51】実施の形態8の製造方法を説明するための断面図である。

- 【図52】実施の形態8により製造されたIGBTのオン電圧-ターンオフ損失のトレードオフを示す特性図である。

- 【図53】実施の形態9のIGBTの構成を示す要部断面斜視図である。

- 【図54】実施の形態10のIGBTの構成を示す要部断面斜視図である。

- 【図55】実施の形態11のIGBTの構成を示す要部断面斜視図である。

#### 【符号の説明】

## [0150]

- 21 第1の絶縁膜(酸化膜)

- 22 多結晶半導体領域(ゲートポリシリコン)

- 23 第2の絶縁膜(ゲート酸化膜)

- 24 第1導電型半導体膜(カソード膜)

- 2 5 第 1 の 第 1 導電型半導体領域 (n + バッファ領域)

- 26 第2の第1導電型半導体領域(n+ソース領域)

- 27 第1の第2導電型半導体領域(pベース領域)

- 28 第3の絶縁膜(層間絶縁膜)

- 29 第1導電型単結晶半導体基板 (n<sup>-</sup>単結晶シリコン基板)

- 3 0 第1の電極(エミッタ電極)

- 3 1 第 2 の第 2 導電型半導体領域 ( p \*アノード層 )

- 32 第2の電極(アノード電極)

- 3 3 第 3 の 第 1 導電型半導体領域(n + バッファ層)

- 4 1 第 2 導電型拡散層(p拡散層)

- 42 第1導電型拡散層(n+拡散層)

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図9】

【図7】

【図10】

【図8】

【図13】

【図12】

【図14】

【図15】

【図17】

【図18】

【図16】

【図19】

【図21】

【図20】

【図22】

【図23】

【図25】

【図24】

【図26】

【図27】

【図29】

【図28】

【図30】

【図31】

【図33】

【図32】

【図34】

【図35】

【図37】

【図36】

【図38】

【図39】

【図40】

【図41】

【図42】

【図43】

【図44】

【図45】

【図46】

【図47】

【図49】

【図48】

【図50】

【図51】

【図53】

【図52】

【図54】

【図55】

### フロントページの続き

# (56)参考文献 特開2002-158356(JP,A) 特開平09-008304(JP,A) 特開平08-097413(JP,A) 特開平09-23232(JP,A) 特開平09-23232(JP,A) 特開2002-261281(JP,A) 特開2004-095954(JP,A) 特開2002-368215(JP,A) 特開2002-368215(JP,A) 特開2006-100779(JP,A)

国際公開第01/004961(WO,A1)

## (58)調査した分野(Int.CI., DB名)

H 0 1 L 2 9 / 7 8 H 0 1 L 2 9 / 7 3 9 H 0 1 L 2 1 / 3 3 6 H 0 1 L 2 1 / 3 3 1