## (19) **日本国特許庁(JP)**

## (12) 公 開 特 許 公 報(A)

(11)特許出願公開番号

特開2004-22902 (P2004-22902A)

(43) 公開日 平成16年1月22日(2004.1.22)

| (51) Int.C1. <sup>7</sup> | F 1             | テーマコード (参考) |

|---------------------------|-----------------|-------------|

| HO1L 29/78                | HO1L 29/78 3O1G | 5F048       |

| HO1 L 21/318              | HO1L 21/318 M   | 5F058       |

| HO1L 21/8238              | HO1L 27/08 321D | 5 F 1 4 O   |

| H O 1 I 27/092            |                 |             |

|                       |                                                        | 審査請求              | 未請求                                         | 謂求項                     | の数 8         | ΟL           | (全           | 16 頁)        |

|-----------------------|--------------------------------------------------------|-------------------|---------------------------------------------|-------------------------|--------------|--------------|--------------|--------------|

| (21) 出願番号<br>(22) 出願日 | 特願2002-177506 (P2002-177506)<br>平成14年6月18日 (2002.6.18) | (71) 出願人          | 000005223<br>富士通株式会社<br>神奈川県川崎市中原区上小田中4丁目1番 |                         |              |              |              |              |

|                       |                                                        | (74) 代理人          | 1号 1000701 弁理士                              | 伊東                      | 忠彦           |              |              |              |

|                       |                                                        | (72) 発明者<br> <br> | 山口 晃央<br>神奈川県川崎市中原区上小田中4丁目1番<br>1号 富士通株式会社内 |                         |              |              |              |              |

|                       |                                                        | Fターム (参           | 考) 5F04                                     | BB11<br>DA25            | AA07<br>BB12 | AB01<br>BC06 | ACO3<br>BDO4 | BB05<br>BE03 |

|                       |                                                        |                   | 5F05                                        | 58 BA20<br>BF23<br>BJ10 | BD01<br>BF30 | BD04<br>BF37 | BD10<br>BH16 | BF04<br>BJ01 |

|                       |                                                        |                   | 最終頁に続く                                      |                         |              |              |              |              |

(54) 【発明の名称】半導体装置の製造方法

### (57)【要約】

【課題】リーク電流の低減を可能とし、さらに薄膜化が 可能な絶縁膜を備えた半導体装置を提供する。

【解決手段】基板上に、シリコン酸化膜、シリコン窒化 膜を形成した後、20 から600 の温度範囲で加熱 して、シリコン窒化膜のプラズマ窒化処理を行う。さら に非酸化性ガス雰囲気中で熱処理を行う。これらの処理 により、このような積層からなるゲート絶縁膜のゲート リーク電流を極めて低減でき、酸化膜換算膜厚を大きく 低減することができる。

【選択図】 図 9

#### 【特許請求の範囲】

#### 【請求項1】

シリコン基板上にシリコンと酸素を含む絶縁膜を形成する工程と、

前記絶縁膜上にシリコン窒化膜を堆積する工程と、

プラズマ窒化処理により前記シリコン窒化膜を改質する工程とを含むことを特徴とする半 導体装置の製造方法。

## 【請求項2】

シリコン基板上のゲート領域を覆うようにシリコンと酸素を含む絶縁膜を形成する工程と

前記絶縁膜上にシリコン窒化膜を堆積する工程と、

プラズマ窒化処理により前記シリコン窒化膜を改質する工程と、

さらにゲート電極を形成する工程とを含むことを特徴とする半導体装置の製造方法。

#### 【請求項3】

請求項1または2記載の半導体装置の製造方法において、

前記絶縁膜はシリコン酸化膜であることを特徴とする半導体装置の製造方法。

#### 【請求項4】

請 求 項 1 ~ 3 の う ち 、 い ず れ か 一 項 記 載 の 半 導 体 装 置 の 製 造 方 法 に お い て 、

前 記 プ ラ ズ マ 窒 化 処 理 は 、 マ イ ク ロ 波 リ モ ー ト プ ラ ズ マ 処 理 装 置 を 使 っ て 行 わ れ る こ と を 特徴とする半導体装置の製造方法。

#### 【請求項5】

請 求 項 1 ~ 4 の う ち 、 い ず れ か 一 項 記 載 の 半 導 体 装 置 の 製 造 方 法 に お い て 、

前 記 シ リ コ ン 窒 化 膜 を 改 質 す る 工 程 は 、 前 記 シ リ コ ン 窒 化 膜 表 面 に 少 な く と も 窒 素 ラ ジ カ ルを供給する工程を含むことを特徴とする半導体装置の製造方法。

#### 【請求項6】

請 求 項 1 ~ 5 の う ち 、 い ず れ か 一 項 記 載 の 半 導 体 装 置 の 製 造 方 法 に お い て 、

前記プラズマ窒化処理を行う工程の後に、非酸化性ガス雰囲気中で熱処理を行う工程をさ らに備えたことを特徴とする半導体装置の製造方法。

#### 【請求項7】

請求項6記載の半導体装置の製造方法において、

前 記 プ ラ ズ マ 窒 化 処 理 を 行 う 工 程 と 前 記 非 酸 化 性 ガ ス 雰 囲 気 中 で 熱 処 理 を 行 う 工 程 と の 間 に、酸化性ガス雰囲気中で熱処理を行う工程をさらに備えたことを特徴とする半導体装置 の製造方法。

#### 【請求項8】

請 求 項 1 ~ 7 の う ち 、 ハ ず れ か 一 項 記 載 の 半 導 体 装 置 の 製 造 方 法 に お い て 、

前 記 絶 縁 膜 に プ ラ ズ マ 窒 化 処 理 を 行 い 、 前 記 絶 縁 膜 を シ リ コ ン 酸 窒 化 膜 に 変 換 す る 工 程 を さらに備えたことを特徴とする半導体装置の製造方法。

#### 【発明の詳細な説明】

#### [0001]

【発明の属する技術分野】

本 発 明 は 一 般 に 半 導 体 装 置 に 係 り 、 特 に シ リ コ ン 窒 化 膜 よ り な る ゲ ー ト 絶 縁 膜 を 有 す る 超 40 高速半導体装置およびその製造方法に関する。

#### [00002]

#### 【従来の技術】

超高速動作が要求されるCMOS-LSIなどの半導体集積回路装置では、半導体集積回 路 装 置 を 構 成 す る 電 界 効 果 型 ト ラ ン ジ ス タ ( M O S F E T ) が 非 常 に 短 い ゲ ー ト 長 を 有 す ることが要求されており、このためMOSFETの微細化に対して多大の努力がなされて いる。

#### [00003]

このように微細化されたMOSFETでは、スケーリング則による要請からゲート長の減 少 に 伴 っ て ゲ ー ト 絶 縁 膜 の 膜 厚 に 対 し て も 制 限 が 加 え ら れ 、 例 え ば ゲ ー ト 長 が 0 . 1 μ m

10

20

50

を切るような半導体装置では、ゲート絶縁膜の膜厚を酸化膜厚換算で 2 n m 程度以下に減少させることが求められている。

#### [0004]

従来、ゲート絶縁膜としては、一般にリーク電流特性が良好で界面準位密度の低いシリコン酸化膜が使用されている。しかしシリコン酸化膜よりなる従来のゲート絶縁膜では、ゲート絶縁膜の物理膜厚の減少に伴い直接トンネル電流が増加してしまい、このためゲート絶縁膜の膜厚が上記の値よりもさらに減少すると、トンネル電流によるゲートリーク電流が大きな問題になる。ゲートリーク電流が増大すると、例えばゲートオフ時において実質的なリーク電流が生じ、半導体装置の回路が正常に動作しない、あるいは消費電力が増加する等の物理法則に起因する本質的な問題が生じてしまう。

#### [0005]

これに対し、従来よりシリコン酸化膜に換えて、ゲート絶縁膜として、物理膜厚が大きくても電気的な換算膜厚が小さいことを特徴とする高誘電率の採用が提案されている。

#### [0006]

ゲート容量 C は、一般に、 C =  $_0$   $_k$  A / d  $_k$  と表される。ただし  $_0$  は真空の誘電率、  $_k$  は絶縁膜の比誘電率、  $_k$  は絶縁膜の面積、  $_k$  は絶縁膜の膜厚である。ここでシリコン酸化膜より高い比誘電率  $_p$  を有する高誘電体膜をゲート絶縁膜として採用すると、前記高誘電体膜がシリコン酸化膜と同じゲート容量を実現する膜厚  $_k$  は、  $_k$  d  $_k$  と表される。ただし  $_k$  な、  $_k$  は、 それぞれシリコン酸化膜の比誘電率  $_k$  ながは厚である。そこで、このような高誘電体膜をゲート絶縁膜に使うことにより、シリコン酸化膜の比誘電率  $_k$  の比を係数として、厚さがd  $_k$  のシリコン酸化膜と同等の電気特性を有するゲート絶縁膜を、物理膜厚  $_k$  のシリコン酸化膜を使って、  $_k$  の の関係により実現することが可能になる。なお、絶縁膜の膜厚  $_k$  の式を用いて、シリコン酸化膜の膜厚  $_k$  のを酸化膜換算膜厚という。

#### [0007]

例えば、ゲート長が  $0.1\mu$  mを切るような超高速 CMOS(Complementary MOS)素子を構成するMOSトランジスタのゲート絶縁膜として、比誘電率がシリコン酸化膜に対して 2.6m のシリコン室化( $Si_3N_4$ )膜を用いることが考えられる。シリコン室化膜は、 $Al_2O_3$ や  $ZrO_2$ ,  $Ta_2O_5$ 等の金属酸化膜系の絶縁膜と比較して、CMOS製造工程との整合性がよく、ゲート絶縁膜への適用が容易であるという特長を有している。これにより、例えばゲート絶縁膜の物理膜厚 2.nm 以上であっても 2.nm 以下の酸化膜換算膜厚を実現でき、半導体装置の動作速度を向上させることができると同時に、トンネル効果によるゲートリーク電流を抑制することが可能になる。

#### [0008]

一方、シリコン基板にシリコン窒化膜を直接積層した場合には、シリコン基板とシリコン窒化膜との界面に窒素が濃集し、チャネル領域を高速で輸送されるキャリアの散乱を生じてしまう現象が知られている。すなわち、このような構成では界面における窒素によりキャリア移動度が劣化し、また同時にシリコン窒化膜中のダングリングボンドによるキャリアの捕獲などにより、半導体装置の閾値特性が不安定になってしまう。

## [ 0 0 0 9 ]

例えばシリコン窒化膜の形成はCVD(化学気相蒸着)法により行われることが多いが、CVD法により形成されたシリコン窒化膜は膜内部に多量の欠陥やダングリングボンド、およびこれらを終端する水素を含んでおり、キャリアが高速で輸送されるチャネル領域に形成されるゲート絶縁膜として適当な膜質を得るのは困難である。またこのような欠陥を解消するために窒素雰囲気中での熱処理を行った場合、窒素原子がシリコン基板との界面にまで拡散してしまい、先に説明したようなキャリアの散乱および移動度の劣化を生じてしまう。さらにダングリングボンドにキャリアが捕獲されることにより、半導体装置の閾値特性が変化してしまう。

#### [0010]

50

10

20

30

このような窒素雰囲気中での熱処理に伴う問題を回避すべく、酸化雰囲気中でCVDシリコン窒化膜を熱処理することも考えられるが、この場合には酸素原子がシリコン基板との界面にまで拡散し、せっかく形成した窒化膜の誘電率を低下させるのみならず、シリコン基板とゲート絶縁膜との界面に酸化膜を形成してしまう。このような酸化膜の形成は、高誘電率のシリコン窒化膜を使った効果を相殺してしまうため、可能な限り抑制する必要がある。

#### [0011]

これに対し従来より、シリコン酸化膜表面をプラズマ窒化処理してシリコン窒化膜、より正確にはシリコン酸窒化膜を形成手法が提案されている。例えばVLSIシンポジウム2001セッションT7A-4を参照。この手法によれば、形成された酸窒化膜内部において窒素原子と酸素原子とが混在し、シリコン基板と酸窒化膜との界面における窒素原子の偏析は生じていない。

[0012]

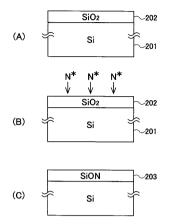

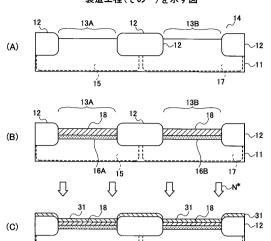

図 1 は、このような酸化膜のプラズマ窒化処理による高誘電率ゲート絶縁膜の形成工程を示す。

[0013]

図1(A)を参照するに、シリコン基板201上には熱酸化膜202が例えば2nmの膜厚に形成されており、図1(B)の工程で前記熱酸化膜202に対してプラズマ窒化処理を行うことにより、熱酸化膜202が窒素ラジカルN\*により窒化され、図1(C)に示すように酸窒化膜に改変される。

[0014]

先にも説明したように、このようにして形成された酸窒化膜中においては酸素原子と窒素原子とが混合して存在しており、シリコン基板との界面における窒素原子の偏析は生じない。このため、このようにして形成された酸窒化膜をゲート絶縁膜に使うことにより、チャネル領域を高速で輸送されるキャリアがゲート絶縁膜とシリコン基板との界面に偏析した窒素原子により散乱される問題は生じない。

[0015]

【発明が解決しようとする課題】

しかしながら、この従来の技術においては、ゲート絶縁膜として形成される膜203が酸窒化膜(SiON膜)であり、シリコン窒化膜と比べると比誘電率が小さく、酸化膜換算膜厚の大幅な減少は望めない。すなわち酸窒化膜の比誘電率は膜中の窒素濃度により左右されるが、SiO2膜を窒化処理した場合、膜中には元々酸素原子が存在しているため、窒素原子の導入量には限界がある。

[0016]

本発明は、上記の問題点に鑑みてなされたもので、本発明の目的は、ゲート絶縁膜のリーク電流の低減を可能とし、ゲート絶縁膜の酸化膜換算膜厚のさらなる減少が可能な半導体 装置の製造方法を提供することである。

[0017]

【課題を解決するための手段】

本発明の一観点によれば、基板上にシリコンと酸素を含む絶縁膜を形成する工程と、前記絶縁膜上にシリコン窒化膜を形成する工程と、プラズマ窒化処理により前記シリコン窒化膜を改質する工程とを含む半導体装置の製造方法が提供される。

[0018]

本発明によれば、基板上にシリコンと酸素とを含む絶縁膜を形成することにより、基板と前記絶縁膜との界面における窒素原子の偏析を抑制することができ、しかも前記絶縁膜上に比誘電率の大きいシリコン窒化膜を形成することにより、前記絶縁膜とシリコン窒化膜とを含めた膜全体の酸化膜換算膜厚を大きく低減することが可能になる。特に前記シリコンと酸素とを含む絶縁膜の膜厚をシリコン窒化膜の膜厚に比較して小さく抑制することにより、小さな酸化膜換算膜厚を実現することができる。

[0019]

50

20

30

シリコン窒化膜中には、一般にダングリングボンドや格子欠陥等が多量に存在するが、本発明では形成されたシリコン窒化膜に対してプラズマ窒化処理を行うことにより、活性な窒素ラジカルがシリコン窒化膜中に侵入し、ダングリングボンドや格子欠陥を終端する。その結果、シリコン窒化はSi₃ N4 の理想的な化学量論組成に近い組成を有し、酸化膜換算膜厚がさらに減少する。その結果、このような膜をゲート絶縁膜に使うことにより、トンネル効果によるゲートリーク電流を抑制しつつ、同時にゲート長の縮小に合わせてゲート絶縁膜の酸化膜換算膜厚を減少させることが可能になる。また、このような構成のゲート絶縁膜は、過加速された電子などのキャリアが侵入してもトラップが少ないため、半導体装置の閾値特性が変動することが少ない。

[ 0 0 2 0 ]

なお本発明の半導体装置の製造方法は、比較的大きな物理膜厚で小さな酸化膜換算膜厚、あるいは実効膜厚を実現できるため、DRAMなどのキャパシタンスの形成に適用した場合、トンネル効果によるリーク電流を抑制しつつ、大きなキャパシタンスを実現することが可能である。

[0021]

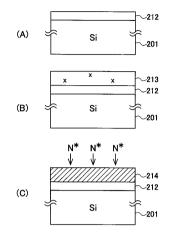

図 2 は、本発明の原理を説明する。ただし図 2 中、先に説明した部分には同一の参照符号を付し、説明を省略する。

[0022]

図 2 ( A )を参照するに、シリコン基板 2 0 1 上にはシリコン酸化膜やシリコン酸窒化膜などの非常に薄い絶縁膜 2 1 2 が形成されており、図 2 ( B )の工程において、図 2 ( A )の構造上にシリコン窒化膜 2 1 3 が堆積される。なお図 2 ( A )の工程において前記絶縁膜 2 1 2 は、 S i と酸素とを含み、シリコン基板との界面に界面準位を形成しない、また元素の偏析が生じないような膜でなければならない。一方、前記シリコン窒化膜 2 1 3 は、 C V D 法などにより堆積することができる。

[0023]

このようにして堆積したシリコン窒化膜 2 1 3 は一般に内部に $\times$ で概略的に示す多量のダングリングボンドや欠陥を含んでおり、その結果、シリコン窒化膜 2 1 3 の化学量論組成  $Si_3N_4$  から離れた組成を有することが多い。そこで本発明では図 2 ( C )の工程において前記シリコン窒化膜 2 1 3 に対してプラズマ窒化処理をさらに行い、形成されたシリコン窒化膜 2 1 3 中に N \*で概略的に示す窒素ラジカルを導入する。導入された窒素ラジカルは前記シリコン窒化膜 2 1 3 中の欠陥やダングリングボンドを終端し、その結果、前記シリコン窒化膜 2 1 3 は、理想的な化学量論組成  $Si_3N_4$  に近い組成を有し、欠陥やダングリングボンドの濃度が減少した高い品質のシリコン窒化膜 2 1 4 に改質される。

[0024]

本発明では、図2(C)の工程においてプラズマ窒化処理により窒素ラジカルを発生させている。このようにして形成された窒素ラジカルは密度の高いシリコン窒化膜213中であっても効率的に侵入でき、所望の改質を生じる。その際、一部はその下の絶縁膜212に到達し、これを窒化する。その結果、膜212および214を合わせた膜全体の比誘電率が向上する。一方、このようにして導入された窒素ラジカルは、前記絶縁膜212と基板201との間の界面に窒素の偏析を生じることはなく、従って、このような膜をチャネル長の短い超高速半導体装置のゲート電極に使った場合にも、偏析した窒素原子によるキャリアの散乱が生じることはない。

[0025]

【発明の実施の形態】

以下、図面に基づいて本発明の実施例を説明する。

(実施例1)

本発明による実施例1は、基板上に熱酸化によりシリコン酸化膜を形成し、次いで、CVD法により成膜したシリコン窒化膜をプラズマ窒化処理し、次いで、非酸化性ガス雰囲気中で熱処理を行うものである。

[0026]

50

40

10

20

30

40

50

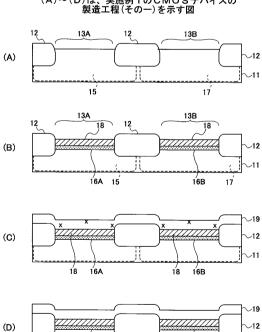

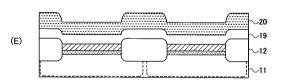

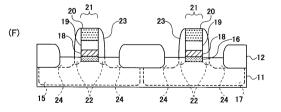

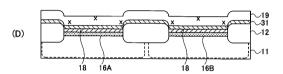

図3(A)~(D)および図4(E)~(F)は、一導電型半導体基板、例えばp型シリコン基板を用いたCMOSデバイスの製造工程を示す図である。

#### [0027]

図 3 ( A )を参照するに、 p 型のシリコン基板 1 1 上には、 L O C O S ( L o c a 1 O x i d a t i o n o f S i l i c o n ) 法や S T I ( S h a l l o w T r e n c h I s o l a t i o n ) 法等により素子分離領域 1 2 が形成されており、これにより素子領域 1 3 A、 1 3 B が画成される。 さらにレジストプロセス(図示せず)により一方の素子領域、例えば素子領域 1 3 B をマスクした状態でイオン注入を行うことにより、 B \* などの p 型ドーパントイオンを素子領域 1 3 A に打込み、 p 型ウェル領域 1 5 を形成する。同様にして、他方の素子領域 1 3 B に A s \* 、 P \* などの n 型ドーパントイオンを打込み、 n 型ウェル領域 1 7 を形成する。

#### [0028]

次に図3(B)の工程においてレジストプロセス(図示せず)により一方の素子領域13 B をマスクし、イオン注入法により先にp型ウェル15が形成された素子領域13 A に B  $^{+}$  またはIn $^{+}$  などのp型ドーパントイオンを打ち込み、nMOSのチャネルドープ領域16 A を形成する。次に、同様にしてn型ウェル17が形成された素子領域13 B に P  $^{+}$  またはA s  $^{+}$  などのn型ドーパントイオンを打込み、pMOSのチャネルドープ領域16 B を形成する。

#### [0029]

図3(B)の工程では、さらに前記シリコン基板11表面のシリコン自然酸化膜をHF処理などによって除去し、さらに熱酸化処理を行うことにより、厚さが1.5nm以下、より好ましくは0.8nm以下のシリコン酸化膜18を形成する。前記熱酸化処理工程は、例えば600~1100 の温度で1分間~20分間行われる。その結果、チャネル領域16A、16Bの表面には熱酸化により、厚さが0.5nm~1.5nmのシリコン酸化膜18が形成される。本実施例では、酸素ガス圧を10Pa、窒素ガス圧を10Paに設定し、850 の温度で8分間のアニールを行い、厚さが1.0nmのシリコン酸化膜18を形成した。

#### [0030]

次に図3(C)の工程でシリコン酸化膜18および素子分離領域12上に、シリコン窒化膜19を、例えば、減圧CVD法により、CVD装置のチャンバー内圧力を1Pa~100Pa、基板温度を600~~800 に設定し、シリコン原料としてジクロロシランガスを1sccm~100sccmの流量で、また窒素原料としてアンモニアガスを1sccm~1000sccmの流量で供給する。前記原料ガスを0.5分間~30分間供給することにより、図3(B)の構造上に、図3(C)に示すように厚さが0.5nm~1.5nmのシリコン窒化膜19を形成する。本実施例では、例えばチャンバー内の圧力を20Pa、ジクロロシランガスの流量を30sccm、アンモニアガスの流量を150sccm、基板を650 に設定して、混合ガスを3分間流し、厚さ1.3nmのシリコン窒化膜19を形成した。

#### [0031]

このようにして C V D 法により作製されたシリコン窒化膜 1 9 には、一般に多量の欠陥、 すなわちダングリングボンド(図 3 ( C )に模式的に「 x 」で示す)が存在している。

#### [0032]

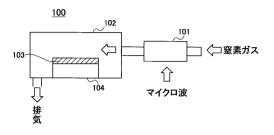

そこで本実施例では図3(D)の工程において、図3(C)のシリコン窒化膜19に対してプラズマ窒化処理を行う。本実施例では、リモートプラズマ窒化装置を用いた。

#### [0033]

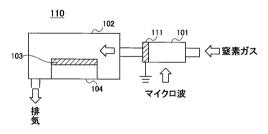

図5は、リモートプラズマ窒化処理装置の要部構成を示した図である。

#### [0034]

図 5 を参照するに、リモートプラズマ窒化装置 1 0 0 は、基板 1 0 3 を処理する処理チャンバー 1 0 2 と、前記処理チャンバー 1 0 2 の外に配置されるリモートプラズマ発生装置 1 0 1 とより構成されている。リモートプラズマ発生装置 1 0 1 には窒素ガスが供給され

30

40

50

、マイクロ波によりこれを励起することで窒素ラジカルおよび窒素イオンが形成される。 形成された窒素ラジカルおよび窒素イオンは前記処理チャンバー102に送られ、ステージ104上に配置された基板103の表面を窒化処理する。

[ 0 0 3 5 ]

[0036]

このプラズマ窒化処理により、シリコン窒化膜 1 9 に侵入した窒素ラジカルおよび窒素イオンがシリコン窒化膜 1 9 のダングリングボンドを終端する。したがって、シリコン酸化膜 1 8 およびシリコン窒化膜 1 9 よりなるゲート絶縁膜のリーク電流を低減することができ、さらなるゲート絶縁膜の酸化膜換算膜厚の低減が可能となる。

[0037]

図 3 ( D )の工程では、さらに前記室化処理の後、例えば N  $_2$  ガス、あるいは H e 、 N e 、 A r 、 K r 、 X e などの不活性ガスよりなる非酸化性ガス雰囲気中で基板を熱処理する

[0038]

より具体的には、前記熱処理は、非酸化性ガス雰囲気中で基板を600~~1100 の温度範囲に加熱し、5~180秒間の範囲でアニールを行う。熱処理は、これらの条件の範囲内で、より高温で短時間に熱処理を行うことが好ましい。このような制御された条件下で熱処理を行うことにより、シリコン窒化膜19中などの窒素原子の基板界面への拡散を抑制しつつ、シリコン窒化膜19中における結晶格子の乱れを除去することができる。この熱処理は、短時間で所望の基板温度に到達することができる、ハロゲンランプを用いたRTP(Rapid Thermal Process)装置やファーネスRTP装置などを用いて行うことが好ましい。本実施例では、N2ガス雰囲気中で、1050 に加熱して、10秒間アニールを行った。

[0039]

この熱処理により、シリコン窒化膜19にプラズマ窒化処理によって生じた損傷、例えば結晶格子の乱れが除去されるとともに、過剰に残留している窒素がシリコン窒化膜19の外部に放出される。したがって、シリコン窒化膜19が緻密化され、ゲート絶縁膜のリーク電流をさらに低減することができる。

[0040]

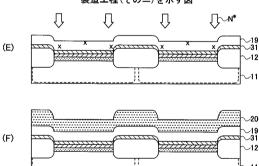

図4(E)を参照するに、次に、基板を別のCVD装置のチャンバーに移し、シリコン窒化膜19上に、ポリシリコン膜20を形成する。例えば、減圧CVD法により、チャンバー内の圧力を10Pa~50Pa、基板を600~650の範囲で加熱して、モノシランガスの流量を50sccm~300sccmに設定する。モノシランガスを5分間~60分間流し、厚さ20nm~200nmのポリシリコン膜20を形成する。本実施例では、チャンバー内の圧力を40Pa、基板温度を620、モノシランガスの流量200sccmに設定した。モノシランガスを20分間流し、厚さ110nmのポリシリコン膜20を形成した。

[0041]

図 4 ( F )を参照するに、次に、前記ポリシリコン膜 2 0 をフォトリソグラフィ法によりパターニングし、前記絶縁膜 1 8 およびシリコン窒化膜 1 9 上にポリシリコンゲート膜 2 0 を有するゲート電極構造 2 1 を形成する。次に、イオン注入法により前記ゲート電極構造 2 1 をマスクに前記 n チャネル領域 1 3 A に A s イオン、 p チャネル領域 1 3 B に B イ

20

30

40

50

オンを打込み、 L D D ( L i g h t l y D o p e d D r a i n ) 領域 2 2 を、前記シリコン基板 1 1 中、前記ゲート電極構造 2 1 の両側に形成する。

[0042]

次に、ゲート電極 2 1 の両側壁面上に C V D 法およびエッチバック法により、例えば S i O っから構成されるサイドウォール絶縁膜 2 3 を形成する。

[0043]

次に、イオン注入法により前記 n チャネル領域 1 3 A に A s イオンを打込み、 p チャネル領域 1 3 B に B イオンを打込み、ソース / ドレイン領域 2 4 を形成する。

[0044]

以上により、図4(F)に示すように、シリコン酸化膜18、シリコン窒化膜19がこの順に積層されたゲート絶縁膜が形成され、CMOSデバイスが形成される。

[0045]

上述したように、シリコン酸化膜 1 8 上に形成されたシリコン窒化膜 1 9 は、シリコン窒化膜 1 9 中のダングリングボンドが、プラズマ窒化処理により窒素ラジカルや窒素イオンで終端され安定化される。したがってゲート絶縁膜のリーク電流を低減することができる。よって、さらなるゲート絶縁膜の薄膜化が可能となる。また、非酸化性ガス雰囲気中で熱処理を行うことにより、プラズマ窒化処理によって生じた損傷を除去することができ、シリコン窒化膜 1 9 が緻密化され、ゲート絶縁膜のリーク電流をさらに低減することができる。

[0046]

(実施例2)

本発明による実施例 2 は、実施例 1 の処理に加え、シリコン酸化膜 1 8 に対してもプラズマ窒化処理を行うものである。

[0047]

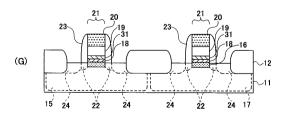

図 6 および図 7 は、一導電型半導体基板、例えば p 型基板を用いた C M O S デバイスの製造工程を示す図である。図中、先に説明した部分に対応する部分には同一の参照符号を付し、説明を省略する。

[0048]

図6(A)および(B)を参照するに、実施例1と同様にして、n型のシリコン基板11上に、素子分離領域12を設け、素子領域13A、13Bを形成し、一方の素子領域13Aにpウェル領域15、他方の素子領域13Bにnウェル領域17を形成する。そして、素子領域13A、13Bにそれぞれチャネルドープ領域16A、16Bを形成し、熱酸化によりシリコン酸化膜18を形成する。本実施例では、850 で8分間のアニールを行い、厚さ1.0nmのシリコン酸化膜18を形成した。

[0049]

本実施例では次に図6(C)の工程において前記シリコン酸化膜18に対してプラズマ窒化処理を、図8に示すリモートプラズマ窒化装置を用いて行う。

[0050]

図8は、リモートプラズマ窒化装置の要部構成を示した図である。

[0051]

図8を参照するに、リモートプラズマ窒化装置110は、図5に示すリモートプラズマ窒化装置100のプラズマ発生装置101にイオンフィルタ111を設けた構成となっており、それ以外は同様の構成を有する。イオンフィルタ111は、金属などの導電性のメッシュで構成され、さらに接地されている。イオンフィルタ111は、プラズマ発生装置101で発生した窒素ラジカルおよび窒素イオンの流路に設けられ、荷電粒子である窒素イオンのみをトラップする。したがって、窒素ラジカルのみがチャンバーに流れるようになっている。

[0052]

例えば、 0 . 5 k W  $\sim$  3 k W の マイクロ波パワーにより発生されたプラズマ中に N  $_2$  ガスと H e ガスをそれぞれ 1 0 0 0 s c c m 、 2 0 0 0 s c c m の流量で供給し、窒素ラジカ

ルおよび窒素イオンを発生させる。その際、このようにして発生した窒素ラジカルおよび窒素イオンはイオンフィルタ 1 1 1 を通され、その結果、窒素イオンが除去される。従って、本実施例では処理チャンバー 1 0 2 内の基板表面には窒素ラジカル N \* のみが供給される。

[0053]

そこで基板を20~600の温度範囲に加熱し、窒素ラジカルN\*を前記シリコン酸化膜18と反応させる。本実施例では、3kWの出力でプラズマを発生させ、窒素ラジカルのみを60秒間流し、基板温度を550とした。この処理により、シリコン酸化膜18の表面側の厚さ0.5nmをシリコン酸窒化膜31に変換した。シリコン酸窒化膜31はシリコン酸化膜18より比誘電率が高いので酸化膜換算膜厚を低減することができ、この処理はゲート絶縁膜の薄膜化に好適である。

[0054]

本実施例では、図8に示すようにイオンフィルタ111によりイオンを除去しているため、チャネル領域に直接に隣接するシリコン酸化膜18をプラズマ窒化する際に、荷電粒子が膜中に導入されることがなく、半導体装置の閾値特性が安定する。

[0055]

図 6 ( D )を参照するに、シリコン酸窒化膜 3 1 上に、実施例 1 と同様にして、シリコン窒化膜 1 9 を形成する。本実施例では基板を 6 5 0 に加熱して混合ガスを 1 分間流し、厚さ 1 . 0 n m のシリコン窒化膜 1 9 を形成した。

[0056]

図7(E)を参照するに、次に、シリコン窒化膜19に対して、実施例1と同様にして、プラズマ窒化処理を行う。本実施例では、3kWの出力でプラズマを発生させ、窒素ラジカルのみを60秒間流し、基板温度を550 とした。このプラズマ窒化処理により、シリコン窒化膜19のダングリングボンドに窒素が結合し、良質なシリコン窒化膜19が形成される。

[0057]

次に、実施例 1 と同様にして、非酸化性ガス雰囲気中で基板をアニールする。本実施例では、N<sub>2</sub> ガス雰囲気中で、1050 に加熱して、10秒間アニールを行った。

[0058]

図 7 ( F )を参照するに、次に、シリコン窒化膜 1 9 上に、実施例 1 と同様にして、ポリシリコン膜 2 0 を形成する。本実施例では、基板を 6 2 0 で加熱して、モノシランガスを 2 0 分間流し、厚さ 1 1 0 n m のポリシリコン膜 2 0 を形成した。

[0059]

図 7 ( G )を参照するに、次に、実施例 1 と同様にして、ゲート電極領域 2 1 、 L D D 領域 2 2 、サイドウォール 2 3 、およびソース / ドレイン領域 2 4 を形成する。

[0060]

以上により、図7(G)に示すように、シリコン酸化膜18、シリコン酸窒化膜31、シリコン窒化膜19がこの順に積層されたゲート絶縁膜が形成され、CMOSデバイスが形成される。

[0061]

上述したように、シリコン酸化膜 1 8 の一部をシリコン窒化処理によりシリコン酸窒化膜 3 1 に変換したことにより、シリコン酸窒化膜はシリコン酸化膜より非誘電率が高いので、酸化膜換算膜厚を低減することができる。またプラズマ窒化処理により、シリコン窒化膜 1 9 のダングリングボンドが窒素ラジカルで終端され膜質が改善される。したがって、ゲートリーク電流を低減することができ、さらなるゲート絶縁膜の薄膜化が可能となる。

[0062]

(実施例3)

本発明による実施例3は、実施例1の処理に加え、プラズマ窒化処理と非酸化性ガス雰囲気中の熱処理との間に、シリコン窒化膜19に対して酸化性ガス雰囲気中で熱処理を行う例である。実施例1と重複する処理については、説明を省略する。

20

30

40

30

40

50

[0063]

実施例 1 において、シリコン室化膜 1 9 にプラズマ室化処理をした後、酸化性ガス雰囲気中で、基板を熱処理する。酸化性ガスは、例えば、NO、N $_2$ O、O $_2$ などである。基板を 7 0 0 ~ 1 1 0 0 の温度範囲に加熱し、 3 秒間 ~ 6 0 秒間の範囲で熱処理を行う。熱処理装置は、例えば、RTP装置等が用いられる。

[0064]

次に、実施例1と同様の処理を行い、シリコン酸化膜、シリコン窒化膜がこの順に積層されたゲート絶縁膜が形成され、CMOSデバイスが形成される。

[0065]

実施例3によれば、プラズマ窒化処理がされたシリコン窒化膜19の最表面には、Si原子とN原子とが未結合のダングリングボンドがなおも存在する。かかるダングリングボンドは、MOSトランジスタのフラットバンドシフトを発生させ、また、MOSトランジスタの閾値電圧の分布を大きくしてしまう。このシリコン窒化膜19を酸化性ガス雰囲気で熱処理することにより、かかるダングリングボンドを酸素により終端でき、シリコン窒化膜19をより安定化することができる。したがって、MOSトランジスタ等のフラットバンドシフトを補償しつつ、リーク電流をさらに低減することができる。

[0066]

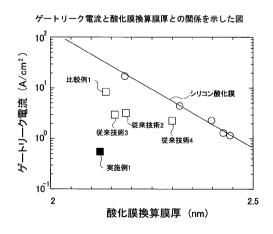

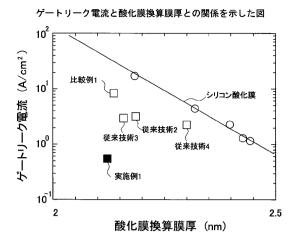

図9は、ゲートリーク電流と酸化膜換算膜厚との関係を示した図である。図9には、本発明による実施例1、本発明によらない比較例1、「従来の技術」の欄で示した従来技術2~4、およびシリコン酸化膜のみのゲート絶縁膜の例を示した。比較例1は、実施例1においてプラズマ窒化処理および非酸化性ガス雰囲気中でのアニールを行っていない例である。

[0067]

図 9 を参照するに、ゲートリーク電流と酸化膜換算膜厚の関係は、シリコン酸化膜のみからなるゲート絶縁膜のデータが示すように、酸化膜換算膜厚が厚くなる程、ゲートリーク電流は低くなっている。プラズマ窒化処理および非酸化性ガス雰囲気中でのアニールを行っていない比較例 1 は、ゲートリーク電流が 9 A / c m² に対して、ほぼ同様の酸化膜換算膜厚を有する実施例 1 は、ゲートリーク電流が 0 . 6 A / c m² となっており、ゲートリーク電流が極めて低いことがわかる。

[0068]

また、実施例1は、従来技術2~4あるいはシリコン酸化膜のみのゲート絶縁膜に対しても、酸化膜換算膜厚の相違を考慮すると、ゲートリーク電流が極めて低いことがわかる。すなわち実施例1のゲート絶縁膜は、ゲートリーク電流が極めて低減されており、ゲート絶縁膜として極めて好適であることがわかる。さらに、実施例1のゲート絶縁膜は薄膜化が可能であり、スケーリング則に沿ったさらなるCMOSデバイスの小型化が実現できる

[0069]

以上本発明の好ましい実施例について詳述したが、本発明は係る特定の実施形態に限定されるものではなく、特許請求の範囲に記載された本発明の要旨の範囲内において、種々の変形・変更が可能である。本実施例では、ゲート絶縁膜に適用した場合について説明したが、本発明によるゲート絶縁膜の製造方法は、例えば、DRAM(Dynamic Random Access Memory)等のキャパシタの製造方法にも適用することができる。

[0070]

また、実施例 2 と実施例 3 を組み合わせてもよい。さらに、実施例 1 から 3 おいてシリコン窒化膜 1 9 に対して、窒素イオンおよび窒素ラジカルによるプラズマ処理について説明したが、窒素ラジカルのみの処理でもよい。

[ 0 0 7 1 ]

以上、本発明を好ましい実施例について説明したが、本発明は特許請求の範囲に記載された要旨内で様々な変形・変更が可能である。

20

30

40

50

(付記1) シリコン基板上にシリコンと酸素を含む絶縁膜を形成する工程と、

前記絶縁膜上にシリコン窒化膜を堆積する工程と、

プラズマ窒化処理により前記シリコン窒化膜を改質する工程とを含むことを特徴とする半 導体装置の製造方法。

(付記2) シリコン基板上のゲート領域を覆うようにシリコンと酸素を含む絶縁膜を形成する工程と、

前記絶縁膜上にシリコン窒化膜を堆積する工程と、

プラズマ窒化処理により前記シリコン窒化膜を改質する工程と、

さらにゲート電極を形成する工程とを含むことを特徴とする半導体装置の製造方法。

(付記3) 付記1または2記載の半導体装置の製造方法において、

前記絶縁膜はシリコン酸化膜であることを特徴とする半導体装置の製造方法。

(付記4) 付記1~3のうち、いずれか一項記載の半導体装置の製造方法において、

前記絶縁膜はシリコン熱酸化膜であることを特徴とする半導体装置の製造方法。

(付記5) 付記1~4のうち、いずれか一項記載の半導体装置の製造方法において、

前記プラズマ窒化処理は、マイクロ波リモートプラズマ処理装置を使って行われることを 特徴とする半導体装置の製造方法。

(付記6) 付記1~5のうち、いずれか一項記載の半導体装置の製造方法において、

前記シリコン窒化膜を改質する工程は、前記シリコン窒化膜表面に少なくとも窒素ラジカルを供給する工程を含むことを特徴とする半導体装置の製造方法。

(付記7) 付記1~6のうち、いずれか一項記載の半導体装置の製造方法において、

前記シリコン窒化膜を改質する工程は、前記シリコン窒化膜表面に窒素ラジカルと窒素イオンとを供給する工程を含むことを特徴とする半導体装置の製造方法。

(付記8) 付記1~7のうち、いずれか一項に記載の半導体装置の製造方法において、

前記プラズマ窒化処理を行う工程の後に、非酸化性ガス雰囲気中で熱処理を行う工程をさらに備えたことを特徴とする半導体装置の製造方法。

(付記9) 付記8記載の半導体装置の製造方法において、

前記プラズマ窒化処理を行う工程と前記非酸化性ガス雰囲気中で熱処理を行う工程との間に、酸化性ガス雰囲気中で熱処理を行う工程をさらに備えたことを特徴とする半導体装置の製造方法。

(付記10) 付記1~9のうち、いずれか一項記載の半導体装置の製造方法において、前記絶縁膜にプラズマ窒化処理を行い、前記絶縁膜をシリコン酸窒化膜に変換する工程をさらに備えたことを特徴とする半導体装置の製造方法。

(付記11) 付記10記載の半導体装置の製造方法において、

前記絶縁膜のプラズマ窒化処理は、マイクロ波リモートプラズマ処理装置を使い、発生した窒素ラジカルを、イオンフィルタを介して前記基板表面に供給する工程を含むことを特徴とする半導体装置の製造方法。

(付記12) 付記8または9記載の半導体装置の製造方法において、

前記非酸化性ガス雰囲気中での熱処理処理は、600 から1100 の範囲の基板温度で実行されることを特徴とする半導体装置の製造方法。

(付記13) 付記1~12のうち、いずれか1項記載の半導体装置の製造方法において

前記シリコン窒化膜は、化学気相蒸着法により堆積されることを特徴とする半導体装置の 製造方法。

(付記14) 付記1~13のうち、いずれか1項記載の半導体装置の製造方法において

前記プラズマ窒化処理は、20 から600 の範囲の基板温度で実行されることを特徴とする半導体装置の製造方法。

[0072]

【発明の効果】

本発明によれば、基板上にシリコンと酸素とを含む絶縁膜を形成することにより、基板と

前記絶縁膜との界面における窒素原子の偏析を抑制することができ、しかも前記絶縁膜上に比誘電率の大きいシリコン窒化膜を形成することにより、前記絶縁膜とシリコン窒化膜とを含めた膜全体の酸化膜換算膜厚を大きく低減することが可能になる。特に前記シリコンと酸素とを含む絶縁膜の膜厚をシリコン窒化膜の膜厚に比較して小さく抑制することにより、小さな酸化膜換算膜厚を実現することができる。

#### 【図面の簡単な説明】

- 【図1】(A)~(C)は、従来のプラズマ窒化処理によるシリコン酸化膜の改質処理を示す図である。

- 【図2】(A)~(C)は、本発明の原理を説明する図である。

- 【図3】(A)~(D)は、実施例1のCMOSデバイスの製造工程(その一)を示す図である。

- 【図4】(E)~(F)は、実施例1のCMOSデバイスの製造工程(その二)を示す図である。

- 【図5】実施例1のリモートプラズマ窒化装置の要部構成を示した図である。

- 【 図 6 】( A ) ~ ( D )は、 実 施 例 2 の C M O S デバイスの製造工程(その一)を示す図 である。

- 【図7】(E)~(G)は、実施例2のCMOSデバイスの製造工程(その二)を示す図である。

- 【 図 8 】 実 施 例 2 の リ モ ー ト プ ラ ズ マ 窒 化 装 置 の 要 部 構 成 を 示 し た 図 で あ る 。

- 【 図 9 】 ゲートリーク電流と酸化膜換算膜厚との関係を示した図である。

#### 【符号の説明】

- 1 1 シリコン基板

- 12 素子分離領域

- 13A、13B 素子領域

- 1 5 p ウェル領域

- 16A、16B チャネルドープ領域

- 17 n ウェル領域

- 18 シリコン酸化膜

- 19 シリコン窒化膜

- 20 ポリシリコン膜

- 2 1 ゲート電極

- 2 2 L D D 領域

- 2 3 サイドウォール 絶縁膜

- 24 ソース/ドレイン領域

- 3 1 シリコン酸窒化膜

- 100、110 リモートプラズマ窒化装置

20

10

## 【図1】

# (A)~(C)は、従来のプラズマ窒化処理による シリコン酸化膜の改質処理を示す図

#### 【図2】

#### (A)~(C)は、本発明の原理を説明する図

## 【図3】

# (A)~(D)は、実施例1のCMOSデバイスの 製造工程(その一)を示す図

16B

## 【図4】

# (E)~(F)は、実施例1のCMOSデバイスの 製造工程(その二)を示す図

## 【図5】

#### 実施例1のリモートプラズマ窒化装置の要部構成を示した図

## 【図6】

#### (A)~(D)は、実施例2のCMOSデバイスの 製造工程(その一)を示す図

## 【図7】

(E)~(G)は、実施例2のCMOSデバイスの 製造工程(その二)を示す図

## 【図8】

#### 実施例2のリモートプラズマ窒化装置の要部構成を示した図

## 【図9】

## フロントページの続き

F ターム(参考) 5F140 AA24 AA39 AB03 BA01 BC06 BD01 BD02 BD05 BD07 BD09 BD10 BE01 BE02 BE05 BE07 BE08 BE10 BE13 BE16 BE17 BE19 BF01 BF04 BG08 BG12 BG28 BG52 BG53 BH15 BK02 BK13 CB01 CB04 CB08