# (19)中华人民共和国国家知识产权局

# (12)发明专利申请

(10)申请公布号 CN 110660673 A (43)申请公布日 2020.01.07

(21)申请号 201911044053.2

(22)申请日 2019.10.30

(71)申请人 长江存储科技有限责任公司 地址 430074 湖北省武汉市洪山区东湖开 发区关东科技工业园华光大道18号 7018室

(72)发明人 黄腾

(74)专利代理机构 上海盈盛知识产权代理事务 所(普通合伙) 31294

代理人 董琳 高德志

(51) Int.CI.

*H01L 21/336*(2006.01)

*H01L 21/02*(2006.01)

H01L 29/78(2006.01)

权利要求书2页 说明书8页 附图3页

#### (54)发明名称

半导体结构及其形成方法

#### (57)摘要

一种半导体结构及其形成方法,所述形成方法包括:提供半导体衬底,所述半导体衬底上形成有晶体管,所述晶体管包括栅介质层、位于栅介质层上的栅电极、以及位于栅电极和栅介质层两侧的半导体衬底中的源区和漏区;形成覆盖所述晶体管的保护层,所述保护层至少包括富硅氮化硅层,所述富硅氮化硅层用于吸附和存储后段制作工艺中产生的等离子体电荷。由于所述保护层中包括富硅氮化硅层,所述富硅氮化硅层能吸附和存储后段制作工艺中产生的等离子体电荷,从而防止后段工艺过程中产生的等离子体电荷,从而防止后段工艺过程中产生的等离子电荷对栅介质层带来的等离子体诱导损伤,从而保证栅介质层的性能,提高晶体管的性能,并且本发明价方法对于防止等离子体诱导损伤简单有效。

1.一种半导体结构的形成方法,其特征在于,包括:

提供半导体衬底:

所述半导体衬底上形成有晶体管,所述晶体管包括栅介质层、位于栅介质层上的栅电极、以及位于栅电极和栅介质层两侧的半导体衬底中的源区和漏区;

形成覆盖所述晶体管的保护层,所述保护层至少包括富硅氮化硅层,所述富硅氮化硅层用于吸附和存储后段制作工艺中产生的等离子体电荷。

2.如权利要求1所述的半导体结构的形成方法,其特征在于,还包括:在所述保护层上形成底层介质层:

在所述底层介质层和保护层中形成与栅电极和/或源区以及漏区连接的金属插塞;

在形成金属插塞后,进行后段制作工艺,所述富硅氮化硅层用于吸附和存储所述金属插塞中传输的所述后段制作工艺中产生的等离子体电荷。

- 3. 如权利要求1所述的半导体结构的形成方法,其特征在于,所述保护层包括富硅氮化硅层和位于所述富硅氮化硅层上的氮化硅层,所述富硅氮化硅层中的硅元素的含量大于氮化硅层中硅元素的含量。

- 4. 如权利要求1所述的半导体结构的形成方法,其特征在于,所述保护层包括氮化硅层和位于所述氮化硅层上的富硅氮化硅层,所述富硅氮化硅层中的硅元素的含量大于氮化硅层中硅元素的含量。

- 5.如权利要求1或2或3或4所述的半导体结构的形成方法,其特征在于,所述富硅氮化硅层中的硅元素和氮元素的比值≥1:1。

- 6.如权利要求5所述的半导体结构的形成方法,其特征在于,形成所述富硅氮化硅层的工艺为化学气相沉积,所述化学气相沉积采用的气体包括硅烷和氨气,硅烷和氨气的流量比≥1:1。

- 7. 如权利要求5所述的半导体结构的形成方法,其特征在于,所述富硅氮化硅层的厚度范围为30~350埃。

- 8.如权利要求1所述的半导体结构的形成方法,其特征在于,所述后段制作工艺包括互连线制作工艺或者存储阵列制作工艺,所述互连线制作工艺用于形成若干互连线,至少部分所述互连线与所述金属插塞电连接,所述存储阵列制作工艺用于形成存储阵列,至少部分存储阵列与所述金属插塞电连接。

- 9. 如权利要求8所述的半导体结构的形成方法,其特征在于,所述后段制作工艺中采用到等离子刻蚀工艺,所述等离子刻蚀工艺中会产生等离子电荷,所述等离子电荷通过所述金属插塞传输。

- 10.如权利要求7所述的半导体结构的形成方法,其特征在于,所述互连线制作工艺或者存储阵列制作工艺中采用到等离子刻蚀工艺,所述等离子刻蚀工艺中会产生等离子电荷,所述等离子电荷通过所述金属插塞传输。

- 11.一种半导体结构,其特征在于,包括:

半导体衬底,所述半导体衬底上形成有晶体管,所述晶体管包括栅介质层、位于栅介质层上的栅电极、以及位于栅电极和栅介质层两侧的半导体衬底中的源区和漏区;

覆盖所述晶体管的保护层,所述保护层至少包括富硅氮化硅层;

位于所述保护层上的底层介质层;

位于所述底层介质层和保护层中的与栅电极和/或源区以及漏区连接的金属插塞,所述富硅氮化硅层用于吸附和存储所述金属插塞中传输的在形成金属插塞后进行的后段制作工艺中产生的等离子体电荷。

- 12. 如权利要求11所述的半导体结构,其特征在于,所述保护层包括富硅氮化硅层和位于所述富硅氮化硅层上的氮化硅层,所述富硅氮化硅层中的硅元素的含量大于氮化硅层中硅元素的含量。

- 13. 如权利要求11述的半导体结构,其特征在于,所述保护层包括氮化硅层和位于所述 氮化硅层上的富硅氮化硅层,所述富硅氮化硅层中的硅元素的含量大于氮化硅层中硅元素的含量。

- 14. 如权利要求11或12或13所述的半导体结构,其特征在于,所述富硅氮化硅层中的硅元素和氮元素的比值≥1:1。

- 15. 如权利要求15所述的半导体结构,其特征在于,所述富硅氮化硅层的厚度范围为30~350埃。

- 16.如权利要求11所述的半导体结构,其特征在于,所述后段制作工艺包括互连线制作工艺或者存储阵列制作工艺,所述互连线制作工艺用于形成若干互连线,至少部分所述互连线与所述金属插塞电连接,所述存储阵列制作工艺用于形成存储阵列,至少部分存储阵列与所述金属插塞电连接。

- 17.如权利要求16所述的半导体结构,其特征在于,所述后段制作工艺中采用到等离子刻蚀工艺,所述等离子刻蚀工艺中会产生等离子电荷,所述等离子电荷通过所述金属插塞传输。

- 18. 如权利要求16所述的半导体结构,其特征在于,所述互连线制作工艺或者存储阵列制作工艺中采用到等离子刻蚀工艺,所述等离子刻蚀工艺中会产生等离子电荷,所述等离子电荷通过所述金属插塞传输。

# 半导体结构及其形成方法

#### 技术领域

[0001] 本发明涉及半导体制作领域,尤其涉及一种半导体结构及其形成方法。

#### 背景技术

[0002] 在半导体制造领域中,离子注入工艺、化学气相沉积工艺、刻蚀工艺和光刻胶的去除工艺等诸多工艺中都会用到等离子体。理论上等离子体总的对外电性应该是呈现中性的,即正离子与负离子是等量的,但是由于等离子体分布不均匀,从而实际上进入半导体衬底的正离子和负离子在局部区域并不是等量的,因此产生大量游离的电荷,半导体衬底上的金属布线或者多晶硅等导体就像天线一样会收集这些游离的电荷,并且很容易在半导体衬底表面形成电荷的积累,这种电荷的积累会影响栅极介质层(栅极氧化层)的性能,使栅极介质层的各种电学参数(例如绝缘层中的固定电荷、界面态密度、平带电压以及栅极漏电流等)退化,严重时甚至会造成器件的失效,这被称为"等离子体诱导损伤"(Plasma-Induced Damage,PID)。

[0003] 尤其是在集成电路制造工艺的后段制程、即形成金属互连线的过程中,使用了电介质化学气相沉积(DCVD)工艺、等离子刻蚀工艺以及物理气相沉积(PVD)工艺等,更容易使得栅极介质层遭受等离子体诱导损伤。

[0004] 传统的工艺会研究PID比较严重的工艺,从源头出发,减少PID,进而提高栅极介质层的可靠性,但是这种方法比较繁琐,首先寻找PID的源头就是很大的工作量,耗时耗力,而且有些工艺不能轻易改变,会提高大量成本或研发时间,因此这种方法往往不能很快的解决问题,因此寻找更加有效的减少PID对栅极介质层影响的方法成为半导体工程师迫切需要解决的问题

#### 发明内容

[0005] 本发明所要解决的技术问题是在怎样更有效的减少PID对栅极介质层的影响。

[0006] 为此,本发明提供了一种半导体结构的形成方法,包括:

[0007] 提供半导体衬底,所述半导体衬底上形成有晶体管,所述晶体管包括栅介质层、位于栅介质层上的栅电极、以及位于栅电极和栅介质层两侧的半导体衬底中的源区和漏区:

[0008] 形成覆盖所述晶体管的保护层,所述保护层至少包括富硅氮化硅层,所述富硅氮化硅层用于吸附和存储后段制作工艺中产生的等离子体电荷。

[0009] 可选的,还包括:在所述保护层上形成底层介质层;

[0010] 在所述底层介质层和保护层中形成与栅电极和/或源区以及漏区连接的金属插塞:

[0011] 在形成金属插塞后,进行后段制作工艺,所述富硅氮化硅层用于吸附和存储所述金属插塞中传输的所述后段制作工艺中产生的等离子体电荷。

[0012] 可选的,所述保护层包括富硅氮化硅层和位于所述富硅氮化硅层上的氮化硅层, 所述富硅氮化硅层中的硅元素的含量大于氮化硅层中硅元素的含量。 [0013] 可选的,所述保护层包括氮化硅层和位于所述氮化硅层上的富硅氮化硅层,所述富硅氮化硅层中的硅元素的含量大于氮化硅层中硅元素的含量。

[0014] 可选的,所述富硅氮化硅层中的硅元素和氮元素的比值≥1:1。

[0015] 可选的,形成所述富硅氮化硅层的工艺为化学气相沉积,所述化学气相沉积采用的气体包括硅烷和氨气,硅烷和氨气的流量比≥1:1。

[0016] 可选的,所所述富硅氮化硅层的厚度范围为30~350埃。

[0017] 可选的,所述后段制作工艺包括互连线制作工艺或者存储阵列制作工艺,所述互连线制作工艺用于形成若干互连线,至少部分所述互连线与所述金属插塞电连接,所述存储阵列制作工艺用于形成存储阵列,至少部分存储阵列与所述金属插塞电连接。

[0018] 可选的,所述后段制作工艺中采用到等离子刻蚀工艺,所述等离子刻蚀工艺中会产生等离子电荷,所述等离子电荷通过所述金属插塞传输。

[0019] 可选的,所述互连线制作工艺或者存储阵列制作工艺中采用到等离子刻蚀工艺, 所述等离子刻蚀工艺中会产生等离子电荷,所述等离子电荷通过所述金属插塞传输。

[0020] 本发明还提供了一种半导体结构,包括:

[0021] 半导体衬底,所述半导体衬底上形成有晶体管,所述晶体管包括栅介质层、位于栅介质层上的栅电极、以及位于栅电极和栅介质层两侧的半导体衬底中的源区和漏区;

[0022] 覆盖所述晶体管的保护层,所述保护层至少包括富硅氮化硅层;

[0023] 位于所述保护层上的底层介质层:

[0024] 位于所述底层介质层和保护层中的与栅电极和/或源区以及漏区连接的金属插塞,所述富硅氮化硅层用于吸附和存储所述金属插塞中传输的在形成金属插塞后进行的后段制作工艺中产生的等离子体电荷。

[0025] 可选的,所述保护层包括富硅氮化硅层和位于所述富硅氮化硅层上的氮化硅层, 所述富硅氮化硅层中的硅元素的含量大于氮化硅层中硅元素的含量。

[0026] 可选的,所述保护层包括氮化硅层和位于所述氮化硅层上的富硅氮化硅层,所述富硅氮化硅层中的硅元素的含量大于氮化硅层中硅元素的含量。

[0027] 可选的,所述富硅氮化硅层中的硅元素和氮元素的比值≥1:1。

[0028] 可选的,所述富硅氮化硅层的厚度范围为30~350埃。

[0029] 可选的,所述后段制作工艺包括互连线制作工艺或者存储阵列制作工艺,所述互连线制作工艺用于形成若干互连线,至少部分所述互连线与所述金属插塞电连接,所述存储阵列制作工艺用于形成存储阵列,至少部分存储阵列与所述金属插塞电连接。

[0030] 可选的,所述后段制作工艺中采用到等离子刻蚀工艺,所述等离子刻蚀工艺中会产生等离子电荷,所述等离子电荷通过所述金属插塞传输。

[0031] 可选的,所述互连线制作工艺或者存储阵列制作工艺中采用到等离子刻蚀工艺, 所述等离子刻蚀工艺中会产生等离子电荷,所述等离子电荷通过所述金属插塞传输。

[0032] 与现有技术相比,本发明技术方案具有以下优点:

[0033] 本发明的半导体结构的形成方法,包括:提供半导体衬底,所述半导体衬底上形成有晶体管,所述晶体管包括栅介质层、位于栅介质层上的栅电极、以及位于栅电极和栅介质层两侧的半导体衬底中的源区和漏区;形成覆盖所述晶体管的保护层,所述保护层至少包括富硅氮化硅层,所述富硅氮化硅层用于吸附和存储后段制作工艺中产生的等离子体电

荷。通过形成包括富硅氮化硅层的保护层,一方面在后续工艺(后段工艺)中所述保护层用于保护已经形成的半导体器件(比如晶体管);另一方面,所述保护层还在后续在底层介质层中形成金属插塞时作为刻蚀停止层;再一方面,由于所述保护层中包括富硅氮化硅层,所述富硅氮化硅层能吸附和存储后段制作工艺中产生的等离子体电荷,从而防止后段工艺过程中产生的等离子电荷对栅介质层带来的等离子体诱导损伤(Plasma-Induced Damage, PID),从而保证栅介质层的性能,提高晶体管的性能,并且本发明的方法对于防止等离子体诱导损伤简单有效。

[0034] 进一步,还包括:在所述保护层上形成底层介质层;在所述底层介质层和保护层中形成与栅电极和/或源区以及漏区连接的金属插塞;在形成金属插塞后,进行后段制作工艺,所述富硅氮化硅层用于吸附和存储所述金属插塞中传输的所述后段制作工艺中产生的等离子体电荷。由于所述保护层中包括富硅氮化硅层,且所述富硅氮化硅层与金属插塞接触,所述富硅氮化硅层在底层介质层和保护层中形成与栅电极和/或源区以及漏区连接的金属插塞后,进行后段制作工艺时,能更有效的吸附和存储所述金属插塞中传输的所述后段制作工艺中产生的等离子体电荷,从而更好的防止后段工艺过程中产生的等离子电荷对栅介质层带来的等离子体诱导损伤(Plasma-Induced Damage,PID),从而更好的保证栅介质层的性能,提高晶体管的性能。

[0035] 进一步,所述保护层包括氮化硅层和位于所述氮化硅层上的富硅氮化硅层,所述富硅氮化硅层中的硅元素的含量大于氮化硅层中硅元素的含量,所述保护层采用这种特定的结构,一方面所述保护层中的富硅氮化硅层用于后续在底层介质层和保护层中形成与栅电极和/或源区以及漏区连接的金属插塞后,进行后段制作工艺时,所述富硅氮化硅层用于吸附和存储所述金属插塞中传输的所述后段制作工艺中产生的等离子体电荷;另一方面,保护层还包括氮化硅层,且氮化硅层位于富硅氮化硅层的底部,由于氮化硅层的隔离性能原高于富硅氮化硅层的隔离性能,因而所述保护层能更好的防止栅电极与源区、漏区以及后续形成的金属插塞之间的漏电。

[0036] 进一步,所述富硅氮化硅层中的硅元素和氮元素的比值≥1:1,所述氮化硅层中硅元素和氮元素的比值为1:2,且所述富硅氮化硅层的厚度范围为30~350埃,在保证富硅氮化硅层能更好和更有效的吸附和存储后续形成的金属插塞中传输的后段制作工艺中产生的等离子体电荷的同时,保证保护层的隔离性能。

[0037] 本发明的半导体结构,包括覆盖所述晶体管的保护层,所述保护层至少包括富硅氮化硅层;位于所述保护层上的底层介质层;位于所述底层介质层和保护层中的与栅电极和/或源区以及漏区连接的金属插塞,所述富硅氮化硅层用于吸附和存储所述金属插塞中传输的在形成金属插塞后进行的后段制作工艺中产生的等离子体电荷,从而防止后段工艺过程中产生的等离子电荷对栅介质层带来的等离子体诱导损伤(Plasma-Induced Damage, PID),从而保证栅介质层的性能,提高晶体管的性能。

## 附图说明

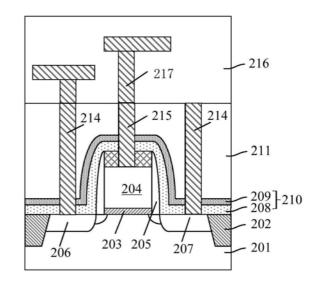

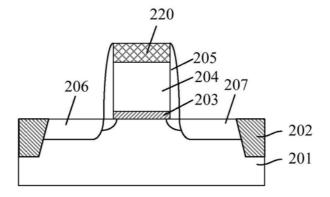

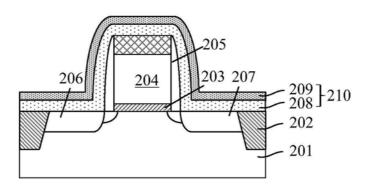

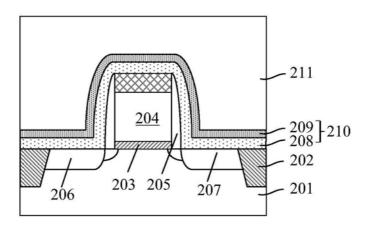

[0038] 图1-图6为本发明实施例半导体结构的形成过程的结构示意图。

### 具体实施方式

[0039] 如背景技术所言,现有亟需一种更加有效的减少PID对栅极介质层影响的方法。

[0040] 为此,本发明提供了一种半导体结构的形成方法,

[0041] 包括:提供半导体衬底,所述半导体衬底上形成有晶体管,所述晶体管包括栅介质层、位于栅介质层上的栅电极、以及位于栅电极和栅介质层两侧的半导体衬底中的源区和漏区;形成覆盖所述晶体管的保护层,所述保护层至少包括富硅氮化硅层,所述富硅氮化硅层的保层用于吸附和存储后段制作工艺中产生的等离子体电荷。通过形成包括富硅氮化硅层的保护层,一方面在后续工艺(后段工艺)中所述保护层用于保护已经形成的半导体器件(比如晶体管);另一方面,所述保护层还在后续在底层介质层中形成金属插塞时作为刻蚀停止层;再一方面,由于所述保护层中包括富硅氮化硅层,所述富硅氮化硅层能吸附和存储后段制作工艺中产生的等离子体电荷,从而防止后段工艺过程中产生的等离子电荷对栅介质层带来的等离子体诱导损伤(Plasma-Induced Damage,PID),从而保证栅介质层的性能,提高晶体管的性能,并且本发明的方法对于防止等离子体诱导损伤简单有效。

[0042] 为使本发明的上述目的、特征和优点能够更加明显易懂,下面结合附图对本发明的具体实施方式做详细的说明。在详述本发明实施例时,为便于说明,示意图会不依一般比例作局部放大,而且所述示意图只是示例,其在此不应限制本发明的保护范围。此外,在实际制作中应包含长度、宽度及深度的三维空间尺寸。

[0043] 图1-图6为本发明实施例半导体结构的形成过程的结构示意图。

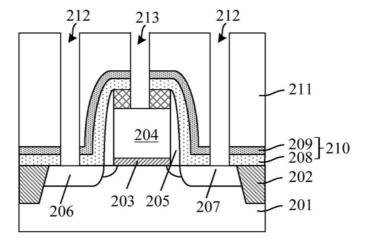

[0044] 参考图1,提供半导体衬底201,所述半导体衬底201上形成有晶体管,所述晶体管包括栅介质层203、位于栅介质层203上的栅电极204、以及位于栅电极204和栅介质层203两侧的半导体衬底201中的源区206和漏区207。

[0045] 所述半导体衬底201的材料可以为单晶硅(Si)、单晶锗(Ge)、或硅锗(GeSi)、碳化硅(SiC);也可以是绝缘体上硅(S0I),绝缘体上锗(G0I);或者还可以为其它的材料,例如砷化镓等Ⅲ-V族化合物。本实施例中,所述半导体衬底201的材料为单晶硅(Si)。

[0046] 所述半导体衬底210上形成的晶体管包括NMOS晶体管和PMOS晶体管,所述晶体管的数量为若干。本实施例中,仅以半导体衬底201上形成一个晶体管作为示例进行说明。

[0047] 根据形成的晶体管的类型的不同,可以向半导体衬底201中掺杂不同类型的杂质离子,形成阱区。在一实施例中,当形成的晶体管为N型的晶体管时,所述阱区离子注入注入的杂质离子为P型杂质离子,所述P型杂质离子为硼离子、镓离子、铟离子中的一种或几种。在另一实施例中,当形成的晶体管为P型的晶体管时,所述阱区离子注入注入的杂质离子为N型的杂质离子,所述N型的杂质离子为磷离子、砷离子、镓离子中的一种或者几种。

[0048] 所述晶体管包括栅介质层203和位于栅介质层203上的栅电极204、以及位于栅电极204和栅介质层203两侧的半导体衬底201中的源区206和漏区207。

[0049] 所述栅介质层203的材料为氧化硅,所述栅电极204的材料为多晶硅或金属。

[0050] 在一实施例中所述栅介质层203和栅电极204形成的具体过程包括步骤:在所述半导体衬底201的栅介质材料层;在所述栅介质材料层上形成栅电极材料层;在所述栅电极材料层上形成图形化的硬掩膜层220;以所述图形化的硬掩膜层220为掩膜刻蚀所述栅电极材料层和栅介质材料层,在半导体衬底201上形成栅介质层203、和位于所述栅介质层203上的栅电极204。

[0051] 所述栅介质层203和栅电极204的两侧侧壁上还形成有侧墙205,所述侧墙205在进行离子注入形成源区206和漏区207时保护栅电极204。所述侧墙205可以为单层或多层堆叠结构(比如双层堆叠结构,包括位于栅电极204侧壁表面的氧化硅层和位于氧化硅层表面的氮化硅层)。

[0052] 所述源区206和漏区207通过对半导体衬底201直接进行离子注入形成或者通过刻蚀栅电极204两侧的半导体衬底201形成凹槽,然后在凹槽中填充应力半导体层(比如锗硅或碳化硅)形成。所述源区206和漏区207均包括浅掺杂区和深掺杂区,所述深掺杂区的深度大于浅掺杂区的深度。

[0053] 所述半导体衬底201内还形成有隔离结构202,所述隔离结构202用于电学隔离相邻的有源区。本实施例中,所述隔离结构为浅沟槽隔离结构,所述隔离结构202的形成过程为:刻蚀所述半导体衬底201形成沟槽;形成覆盖所述半导体衬底201表面的隔离材料层,所述隔离材料层填充满所述沟槽;采用化学机械研磨工艺去除半导体衬底201表面上的隔离材料层,在所述沟槽中形成隔离结构202。

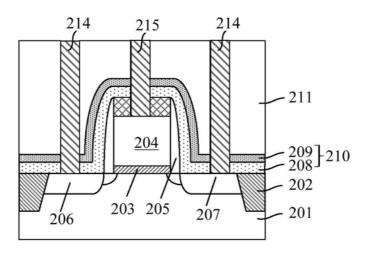

[0054] 参考图2,形成覆盖所述晶体管的保护层210,所述保护层210至少包括富硅氮化硅层209,所述富硅氮化硅层209用于吸附和存储后段制作工艺中产生的等离子体电荷。

[0055] 所述保护层210一方面在后续工艺(后段工艺)中用于保护已经形成的半导体器件(比如晶体管);另一方面,所述保护层210还在后续在底层介质层形成暴露出源区和漏区(和/或栅电极)表面的刻蚀通孔时作为刻蚀停止层;再一方面,由于所述保护层210中包括富硅氮化硅层209,所述富硅氮化硅层209能吸附和存储后段制作工艺中产生的等离子体电荷,从而防止后段工艺过程中产生的等离子电荷对栅介质层带来的等离子体诱导损伤(Plasma-Induced Damage,PID),从而保证栅介质层的性能,提高晶体管的性能,并且本发明的方法对于防止等离子体诱导损伤简单有效。

[0056] 本实施例中,所述保护层210包括氮化硅层208和位于所述氮化硅层208上的富硅氮化硅层209,所述富硅氮化硅层209中的硅元素的含量大于氮化硅层208中硅元素的含量,所述保护层210采用这种特定的结构,一方面所述保护层210中的富硅氮化硅层209用于后续在底层介质层和保护层中形成与栅电极和/或源区以及漏区连接的金属插塞后,进行后段制作工艺时,所述富硅氮化硅层用于吸附和存储所述金属插塞中传输的所述后段制作工艺中产生的等离子体电荷;另一方面,保护层210还包括氮化硅层208,且氮化硅层208位于富硅氮化硅层209的底部,由于氮化硅层208的隔离性能远高于富硅氮化硅层209的隔离性能,因而所述保护层208能更好的防止栅电极204与源区206、漏区207以及后续形成的金属插塞之间的漏电。

[0057] 在另一实施例中,所述保护层仅包括富硅氮化硅层。

[0058] 在又一实施例中,所述保护层包括富硅氮化硅层和位于所述富硅氮化硅层上的氮化硅层,所述富硅氮化硅层中的硅元素的含量大于氮化硅层中硅元素的含量。

[0059] 在一实施例中,通过研究,所述富硅氮化硅层209中的硅元素和氮元素的比值≥1:1,所述氮化硅层208中硅元素和氮元素的比值为1:2,且所述富硅氮化硅层209的厚度范围为30~350埃,在保证富硅氮化硅层209能更好和更有效的吸附和存储后续形成的金属插塞中传输的后段制作工艺中产生的等离子体电荷的同时,保证保护层的隔离性能。

[0060] 在一实施例中,形成所述富硅氮化硅层的工艺为化学气相沉积,所述化学气相沉

积采用的气体包括硅烷和氨气,硅烷和氨气的流量比≥1:1。

[0061] 在一实施例中,在形成保护层210后,请参考图3,在所述保护层210上形成底层介质层211。

[0062] 所述底层介质层211的材料为氧化硅、氟掺杂硅玻璃 (FSG) 或其他合适的介质材料。所述底层介质层211的形成工艺包括化学气相沉积工艺。

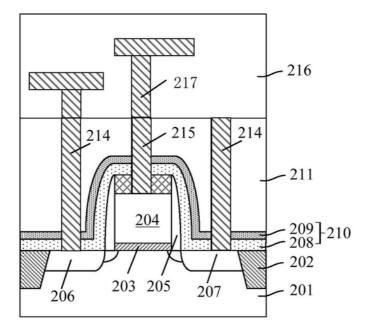

[0063] 结合参考图4和图5,在所述底层介质层211和保护层210中形成与栅电极204和/或源区206以及漏区207连接的金属插塞(214/215)。

[0064] 所述金属插塞的数量为若干,包括与栅电极204连接的金属插塞215,与源区206和漏区207分别连接的金属插塞214。在具体的工艺中,可以只形成与栅电极204连接的金属插塞214,或者只形成与源区206以及漏区207连接的金属插塞215,或者同时形成与栅电极204连接的金属插塞214,以及与源区206以及漏区207连接的金属插塞215。

[0065] 在一实施例中,所述金属插塞214和215的形成过程包括:在所述底层介质层211上形成掩膜层(图中未示出),所述掩膜层中具有暴露出栅电极204、源区206和漏区207上方部分底层介质层表面的若干开口;以所述掩膜层为掩膜采用第一刻蚀工艺刻蚀所述底层介质层211,所述第一刻蚀工艺以保护层210作为刻蚀停止层,在所述底层介质层211形成若干暴露出保护层210部分表面的第一刻蚀孔;进行第二刻蚀工艺,沿第一刻蚀孔继续刻蚀底部的保护层210和栅电极204上硬掩膜层,在底层介质层211和保护层210中形成暴露出栅电极和源区以及漏区表面的若干刻蚀通孔;在所述若干刻蚀通孔中填充金属,形成金属插塞214和215。

[0066] 在一实施例中,还包括:在形成第一刻蚀孔之后,继续刻蚀第一刻蚀孔底部的保护层之前,在所述第一刻蚀孔的侧壁和底部表面形成防扩散阻挡层,所述防扩散阻挡层用于防止刻蚀通孔中形成的金属插塞中的金属原子向外扩散,所述防扩散阻挡层的材料为Ti、TiN、Ta、TaN中的一种或几种;在形成防扩散阻挡层后,刻蚀去除第一刻蚀孔底部的部分防扩散阻挡层,并继续刻蚀第一刻蚀孔底部的保护层,形成刻蚀通孔,因而形成的刻蚀通孔暴露两部分,一部分位于底层介质层211中,一部分位于保护层210中;接着在刻蚀通孔中形成金属插塞(214/215),底层介质层211中的那一部分刻蚀通孔中的金属插塞被扩散阻挡层包围,所述扩散阻挡层能防止金属插塞中的金属原子向外扩散,而保护层210中的那一部分刻蚀通孔中的金属插塞直接与保护层中的富硅氮化硅层209接触,因而扩散阻挡层的存在不会影响富硅氮化硅层209吸附和存储金属插塞中传输的所述后段制作工艺中产生的等离子体电荷。

[0067] 参考图6,在形成金属插塞(214/215)后,进行后段制作工艺,所述富硅氮化硅层209用于吸附和存储所述金属插塞(214/215)中传输的所述后段制作工艺中产生的等离子体电荷。

[0068] 所述后段制作工艺中采用到等离子刻蚀工艺,所述等离子刻蚀工艺中会产生等离子电荷,所述等离子电荷通过所述金属插塞传输,由于所述保护层210中包括富硅氮化硅层209,且所述富硅氮化硅层209与金属插塞(214/215)接触,所述富硅氮化硅层209在底层介质层和保护层中形成与栅电极和/或源区以及漏区连接的金属插塞(214/215)后,进行后段制作工艺时,能更有效的吸附和存储所述金属插塞中传输的所述后段制作工艺中产生的等离子体电荷,从而更好的防止后段工艺过程中产生的等离子电荷对栅介质层带来的等离子

体诱导损伤(Plasma-Induced Damage, PID),从而更好的保证栅介质层的性能,提高晶体管的性能。在其他实施例中,所述等离子电荷还包括等离子增强化学气相沉积(PECVD)和溅射过程中产生的等离子体电荷。

[0069] 本实施例中,所述后段制作工艺包括互连线制作工艺,所述互连线制作工艺用于形成若干互连线217,至少部分所述互连线217与所述金属插塞(214/215)电连接。具体的,在所述底层介质层211上形成上层介质层216,在上层介质层216中形成互连线217。所述上层介质层216可以为单层或多层堆叠结构,相应的所述互连线217也可以为单层或多层堆叠结构,每一层上层介质层中对应形成一层互连线。所述上层介质层通过沉积工艺(包括高密度等离子沉积工艺或等离子增强沉积工艺),所述互连线217通过刻蚀工艺(通过刻蚀通孔在上层介质层中形成凹槽,刻蚀工艺包括等离子体刻蚀工艺)、沉积工艺(用于所述凹槽中形成金属,所述沉积工艺包括电镀工艺和溅射工艺)。所述互连线制作工艺中采用到的等离子刻蚀工艺会产生等离子电荷,所述等离子电荷通过所述金属插塞传输。

[0070] 在其他实施例中,所述后段制作工艺包括互连线制作工艺或者存储阵列制作工艺,所述互连线制作工艺用于形成若干互连线,至少部分所述互连线与所述金属插塞电连接,所述存储阵列制作工艺用于形成存储阵列,至少部分存储阵列与所述金属插塞电连接,所述存储阵列可以形成在半导体衬底201上形成有晶体管之外的区域,所述存储阵列包括3D NAND存储阵列。所述存储阵列制作工艺中采用到等离子刻蚀工艺,所述等离子刻蚀工艺中会产生等离子电荷,所述等离子电荷通过所述金属插塞传输。

[0071] 需要说明的是,所述后段工艺可以为其他能产生等离子电荷的工艺,并且所述产生的等离子电荷能通过金属插塞传输。

[0072] 本发明另一实施例还提供了一种半导体结构,参考图6,包括:

[0073] 半导体衬底201,所述半导体衬底201上形成有晶体管,所述晶体管包括栅介质层203、位于栅介质层203上的栅电极204、以及位于栅电极204和栅介质层203两侧的半导体衬底201中的源区206和漏区207:

[0074] 覆盖所述晶体管的保护层210,所述保护层210至少包括富硅氮化硅层209;

[0075] 位于所述保护层210上的底层介质层211;

[0076] 位于所述底层介质层211和保护层210中的与栅电极204和/或源区以及漏区连接的金属插塞(214/215),所述富硅氮化硅层209用于吸附和存储所述金属插塞(214/215)中传输的在形成金属插塞(214/215)后进行的后段制作工艺中产生的等离子体电荷。

[0077] 本实施例所述保护层210包括氮化硅层208和位于所述氮化硅层208上的富硅氮化硅层209,所述富硅氮化硅层209中的硅元素的含量大于氮化硅层208中硅元素的含量。

[0078] 在另一实施例中,所述保护层仅包括富硅氮化硅层。

[0079] 在又一实施例中,所述保护层包括富硅氮化硅层和位于所述富硅氮化硅层上的氮化硅层,所述富硅氮化硅层中的硅元素的含量大于氮化硅层中硅元素的含量。

[0080] 在一实施例中,所述富硅氮化硅层209中的硅元素和氮元素的比值≥1:1,所述氮化硅层208中硅元素和氮元素的比值为1:2,且所述富硅氮化硅层209的厚度范围为30~350埃。

[0081] 所述后段制作工艺包括互连线制作工艺或者存储阵列制作工艺,所述互连线制作工艺用于形成若干互连线,至少部分所述互连线与所述金属插塞电连接,所述存储阵列制

作工艺用于形成存储阵列,至少部分存储阵列与所述金属插塞电连接。

[0082] 所述后段制作工艺中采用到等离子刻蚀工艺,所述等离子刻蚀工艺中会产生等离子电荷,所述等离子电荷通过所述金属插塞传输。

[0083] 所述互连线制作工艺或者存储阵列制作工艺中采用到等离子刻蚀工艺,所述等离子刻蚀工艺中会产生等离子电荷,所述等离子电荷通过所述金属插塞传输。

[0084] 以上所述仅是本发明的优选实施方式,应当指出,对于本技术领域的普通技术人员,在不脱离本发明原理的前提下,还可以做出若干改进和润饰,这些改进和润饰也应视为本发明的保护范围。

图1

图2

图3

图4

图5

图6