## (19) **日本国特許庁(JP)**

# (12) 公 開 特 許 公 報(A)

(11)特許出願公開番号

特開2006-236768 (P2006-236768A)

(43) 公開日 平成18年9月7日(2006.9.7)

| (51) Int.C1. |       |           | F I  |      |              | テーマコード (参考) |

|--------------|-------|-----------|------|------|--------------|-------------|

| HO1J         | 9/02  | (2006.01) | HO1J | 9/02 | E            | 5 C 1 2 7   |

| HO1J         | 1/316 | (2006.01) | HO1J | 1/30 | $\mathbf{E}$ | 5C135       |

#### 審査請求 有 請求項の数 6 〇1. (全 8 百)

|           |                            |          | 1日本 有 日本項の数 0 0 1 (主 6 頁)         |  |  |  |  |

|-----------|----------------------------|----------|-----------------------------------|--|--|--|--|

| (21) 出願番号 | 特願2005-49287 (P2005-49287) | (71) 出願人 | 000002369                         |  |  |  |  |

| (22) 出願日  | 平成17年2月24日 (2005.2.24)     |          | セイコーエプソン株式会社                      |  |  |  |  |

|           |                            |          | 東京都新宿区西新宿2丁目4番1号                  |  |  |  |  |

|           |                            | (74)代理人  | 100079108                         |  |  |  |  |

|           |                            |          | 弁理士 稲葉 良幸                         |  |  |  |  |

|           |                            | (74)代理人  | 100080953                         |  |  |  |  |

|           |                            |          | 弁理士 田中 克郎                         |  |  |  |  |

|           |                            | (74)代理人  | 100093861                         |  |  |  |  |

|           |                            |          | 弁理士 大賀 眞司                         |  |  |  |  |

|           |                            | (72) 発明者 | 湯田坂 一夫                            |  |  |  |  |

|           |                            |          | 長野県諏訪市大和3丁目3番5号 セイコ               |  |  |  |  |

|           |                            |          | ーエプソン株式会社内                        |  |  |  |  |

|           |                            | F ターム (参 | 考) 5C127 AA01 CC12 DD13 DD57 DD63 |  |  |  |  |

|           |                            |          | DD64 DD99 EE04 EE15               |  |  |  |  |

|           |                            |          | 5C135 BB14 BB15 HH04 HH15         |  |  |  |  |

|           |                            | 1        |                                   |  |  |  |  |

(54) 【発明の名称】スリット形成方法、電子放出素子の製造方法、及び電子デバイス

## (57)【要約】

【課題】 塗布膜に形成すべきスリットの位置を精 緻に制御することが可能なスリット形成技術を提供する

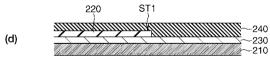

【解決手段】 基板210の所望位置に所望形状の第1絶縁膜220を形成する。そして、第1絶縁膜220の端部eを覆うように、素子電極形成用の導電膜230を形成する(図3(a)参照)。さらに、第1絶縁膜220、導電膜230が形成された基板210の全面に、ポリシラザンなどの液体材料(絶縁性材料)を塗布し、上記と同様のベーク・アニール処理を施すことにより、第2絶縁膜240を形成する。ここで、第1絶縁膜220の端部eを覆う導電膜230第2絶縁膜240の膜厚D2は、他の部分の膜厚D3に較べて薄い。かかる膜厚差(D3-D2)によって生じる膜の収縮度合いの違いにより、第1絶縁膜220の端部eの直上に位置する第2絶縁膜240にスリットST1が形成される(図3(b)参照)。

【選択図】 図3

#### 【特許請求の範囲】

## 【請求項1】

端部を有する段差パターンを基板上に形成する工程と、

少 な く と も 前 記 段 差 パ タ ー ン の 端 部 を 覆 う よ う に 、 塗 布 膜 形 成 用 の 液 体 材 料 を 前 記 基 板 上に塗布する工程と、

塗布した液体材料を乾燥させることによって塗布膜を形成するとともに、当該塗布膜に おける前記段差パターンの端部に対応する位置にスリットを形成する工程と

を含むことを特徴とする塗布膜に対するスリット形成方法。

#### 【請求項2】

請求項1に記載のスリット形成方法において、

前記段差パターンは絶縁性材料によって形成され、前記液体材料は導電性膜形成用の液 体材料であることを特徴とする塗布膜に対するスリット形成方法。

#### 【請求項3】

請求項1に記載のスリット形成方法において、

前 記 段 差 パ タ ー ン は 導 電 性 材 料 に よ っ て 形 成 さ れ 、 前 記 液 体 材 料 は 絶 縁 性 膜 形 成 用 の 液 体材料であることを特徴とする塗布膜に対するスリット形成方法。

#### 【請求項4】

基板上に対向する一対の素子電極を形成する工程と、

前記基板上の前記素子電極間に挟まれた領域に端部を有する段差パターンを形成する工 程と、

少なくとも前記段差パターンの端部を覆うとともに、前記各素子電極の一部をそれぞれ 覆うように、導電膜形成用の液体材料を塗布する工程と、

塗布した液体材料を乾燥させることによって導電膜を形成するとともに、当該導電膜に おける前記段差パターンの端部に対応する位置にスリットを形成する工程と

を含むことを特徴とする電子放出素子の製造方法。

### 【請求項5】

基板上に端部を有する段差パターンを形成する工程と、

少 な く と も 前 記 段 差 パ タ ー ン の 端 部 を 覆 う よ う に 導 電 膜 形 成 用 の 液 体 材 料 を 塗 布 す る 工 程と、

塗布した液体材料を乾燥させることによって導電膜を形成するとともに、当該導電膜に お け る 前 記 段 差 パ タ ー ン の 端 部 に 対 応 す る 位 置 に ス リ ッ ト を 形 成 し 、 一 対 の 素 子 電 極 を 形 成する工程と

を含むことを特徴とする電子放出素子の製造方法。

## 【請求項6】

請 求 項 4 ま た は 5 に 記 載 の 製 造 方 法 に よ っ て 製 造 さ れ た 電 子 放 出 素 子 を 有 す る こ と を 特 徴とする電子デバイス。

【発明の詳細な説明】

#### 【技術分野】

### [00001]

本発明は、スリット形成方法、電子放出素子の製造方法、及び電子デバイスに関する。

## 【背景技術】

## [00002]

従来より、絶縁性の基板上に対向配置された一対の素子電極と、この素子電極に接続し て設けられた導電性薄膜とを備えた電子放出素子が知られている。その例として、M.I . Elinsonが「Radio・Eng.・Electron・Phys.、10、1 2 9 0 、 ( 1 9 6 5 ) 」に発表した電子放出素子がある。

#### [00003]

このような電子放出素子における導電性薄膜の形成は、通常、真空蒸着法や、エッチン グ、リフトオフなどの半導体プロセスを主とする方法で行われる。しかしながら、かかる 方法 は 特 殊 で 高 価 な 製 造 装 置 を 必 要 と し 、 パ タ ー ニ ン グ に 伴 う 複 数 の 工 程 が 必 要 と な る こ 10

20

30

40

10

20

30

40

50

とから、特に大きな基板に多数の電子放出素子を形成する場合に生産コストが高くなる等の問題がある。

[0004]

このような背景のもと、半導体プロセスを用いることなく、インクジェット装置を用いて導電性薄膜形成用の金属元素を含む液体材料(以下、導電性材料)を基板に塗布することで、導電性薄膜を形成する方法(以下、インクジェット法)が提案されている(例えば、特許文献 1 参照)。

[0005]

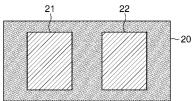

図7は、インクジェット法による電子放出素子の製造プロセスを示す図である。

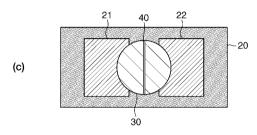

まず、フォトリソグラフィなど利用して基板 2 0 上に 1 対の素子電極 2 1、 2 2 を形成し(図 7 (a)参照)、次いで、インクジェット装置を用いて素子電極 2 1、 2 2 の間に導電性材料を塗布し、これを加熱焼成することで素子電極 2 1、 2 2 に接続された導電性薄膜 3 0 を形成する(図 7 (b)参照)。そして、該導電性薄膜 3 0 にフォーミングと称される通電処理(以下、フォーミング処理)を施し、導電性薄膜にnmサイズの亀裂(スリット)40を発生させるなどして電子放出素子を形成していた(図 7 (c)参照)。

[0006]

【特許文献1】特開2004-192812号公報

【発明の開示】

【発明が解決しようとする課題】

[0007]

ところで、基板 2 0 上に形成される複数の電子放出素子について均一な特性を得るためには、スリット 4 0 の位置(以下、スリット位置)を精緻に制御する必要があるが、フォーミング処理によってスリットを形成する方法ではスリット位置を精緻に制御するのは極めて難しいという問題があった。

[0008]

本発明は以上説明した事情を鑑みてなされたものであり、塗布膜に形成すべきスリット の位置を精緻に制御することが可能なスリット形成技術を提供することを目的とする。

【課題を解決するための手段】

[0009]

上記目的を達成するため、本発明に係る塗布膜に対するスリット形成方法は、端部を有する段差パターンを基板上に形成する工程と、少なくとも前記段差パターンの端部を覆うように、塗布膜形成用の液体材料を前記基板上に塗布する工程と、塗布した液体材料を乾燥させることによって塗布膜を形成するとともに、当該塗布膜における前記段差パターンの端部に対応する位置にスリットを形成する工程とを含むことを特徴とする。

[0010]

かかる構成によれば、段差パターンを形成するといった簡単な方法でスリットの位置を精緻に制御することが可能となる。かかる技術は種々の分野に適用可能であるが、例えば電子放出素子の形成に適用することで、電子放出効率の高い電子放出素子を形成することが可能となる。

[0011]

ここで、上記スリット形成方法にあっては、前記段差パターンは絶縁性材料によって形成され、前記液体材料は導電性膜形成用の液体材料であっても良く、また、前記段差パターンは導電性材料によって形成され、前記液体材料は絶縁性膜形成用の液体材料であっても良い。

[0012]

また、本発明に係る電子放出素子の製造方法にあっては、基板上に対向する一対の素子電極を形成する工程と、前記基板上の前記素子電極間に挟まれた領域に端部を有する段差パターンを形成する工程と、少なくとも前記段差パターンの端部を覆うとともに、前記各素子電極の一部をそれぞれ覆うように、導電膜形成用の液体材料を塗布する工程と、塗布した液体材料を乾燥させることによって導電膜を形成するとともに、当該導電膜における

(4)

前記段差パターンの端部に対応する位置にスリットを形成する工程とを含むことを特徴と する。

#### [0013]

また、本発明に係る別の電子放出素子の製造方法にあっては、基板上に端部を有する段差パターンを形成する工程と、少なくとも前記段差パターンの端部を覆うように導電膜形成用の液体材料を塗布する工程と、塗布した液体材料を乾燥させることによって導電膜を形成するとともに、当該導電膜における前記段差パターンの端部に対応する位置にスリットを形成し、一対の素子電極を形成する工程とを含むことを特徴とする。

#### [0014]

これらの製造方法によって製造された電子放出素子を電子デバイスに適用しても良い。ここで、電子デバイスとは、本発明に係る電子放出素子を備えた一定の機能を奏する機器一般をいい、例えば電気光学装置やメモリを備えて構成される。その構成に特に限定は無いが、例えば画像形成装置、ICカード、携帯電話、ビデオカメラ、パーソナルコンピュータ、ヘッドマウントディスプレイ、リア型またはフロント型のプロジェクター、さらに表示機能付きファックス装置、デジタルカメラのファインダ、携帯型TV、DSP装置、PDA、電子手帳、電光掲示板、宣伝広告用ディスプレイ等が含まれる。

【発明を実施するための最良の形態】

## [0015]

以下、本発明に係る実施形態を説明する前に、本発明の基本原理について説明する。

#### [0016]

#### A . 基本原理

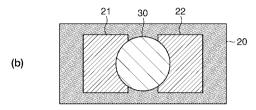

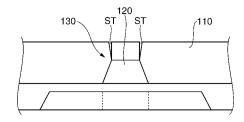

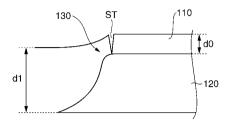

図1は、TFT (Thin Film Transistor)を構成するゲート電極と層間絶縁膜の関係を示す図であり、図2は、図1に示すゲート電極近傍の部分拡大図である。

層間絶縁膜110は、導電性材料によって形成されたゲート電極(段差パターン)12 0を含む基板全面を覆う絶縁膜であり、ポリシラザンを含む液体材料(絶縁性膜形成用の 液体材料)を塗布し、乾燥等することによって形成する。

## [0017]

図1に示すように、塗布法によって層間絶縁膜110を形成すると、ゲート電極(段差パターン)120の端部を覆う部分と他の部分との間で段差130が形成される。この段差部分について断面TEM(Transmission Electron Microscope)やAFM(Atomic Force Microscope)などの方法によって調査すると、当該段差部分にスリットSTが形成されることが判明した(図2参照)。さらに調査を進めたところ、このスリットSTの幅や深さは段差の高さや形状及び層間絶縁膜110の形成条件(材料や乾燥条件など)に起因し、また、他の部分の膜厚d1とゲート電極120を覆う部分の膜厚d0の膜厚差(d1-d0)は、ゲート電極120のパターンサイズに起因することが判明した。

### [0018]

なお、スリットSTが形成されるメカニズムについては未だ明らかではないが、ゲート電極120を覆う部分の膜厚d0と他の部分の膜厚d1の膜厚差(d1-d0)によって生じる膜の収縮度合いの違いがスリットSTの形成に起因したものと推測される。かかる現象を利用した実施形態について図面を参照しながら説明する。

## [0019]

#### B . 第 1 実 施 形 態

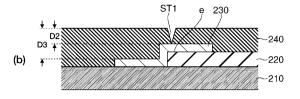

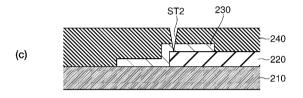

図 3 は、表面伝導型電子放出素子の製造プロセスを示す工程図であり、図 4 は、表面伝導型電子放出素子の平面図である。

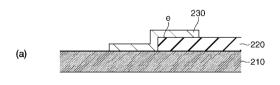

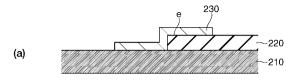

まず、基板210の所望位置にポリシラザンなどの液体材料(絶縁性材料)を塗布し、ベーク・アニール処理(100 で5分程度、さらに350 で60分程度)等を施すことにより、所望形状の第1絶縁膜(段差パターン)220を形成する。そして、第1絶縁膜220の端部eを覆うように、素子電極形成用の導電膜230を形成する(図3(a)参照)。なお、第1絶縁膜220や導電膜230は、物理的気相法(PVD)や化学的気相法(CVD)などを利用して形成しても良い。

20

30

40

#### [0020]

さらに、第1 絶縁膜220、導電膜230が形成された基板210の全面に、ポリシラザンなどの液体材料(絶縁性材料)を塗布し、上記と同様のベーク・アニール処理を施すことにより、第2 絶縁膜240を形成する。ここで、第1 絶縁膜220の端部 e を覆う導電膜230第2 絶縁膜240の膜厚D2は、他の部分の膜厚D3に較べて薄い。かかる膜厚差(D3-D2)によって生じる膜の収縮度合いの違いにより、第1 絶縁膜220の端部 e の直上に位置する第2 絶縁膜240 (段差パターンの端部に対応する位置)にスリットST1が形成される(図3(b)参照)。

#### [0021]

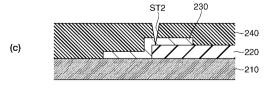

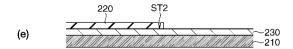

その後、導電膜用のエッチング液を用いてエッチングすることにより、第2絶縁膜240に形成したスリットST1を導電膜230に転写する(図3(c)参照)。その後、さらにエッチングなどを施すことにより、導電膜230に形成したスリットST2の幅や深さを微調整し、第2絶縁膜240を剥離する。この結果、一対の素子電極231、232の間に電子放出部260が形成された表面伝導型電子放出素子が形成される(図4参照)

## [0022]

### C . 第 2 実施形態

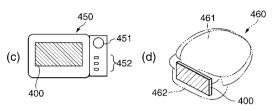

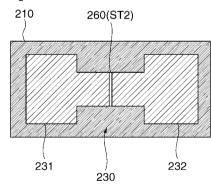

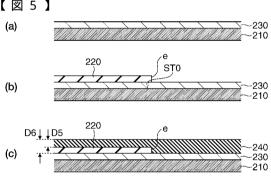

図5は、導電膜230にスリットを形成するプロセスを示す工程図である。

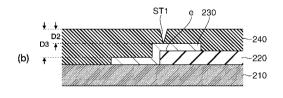

まず、基板210の全面に物理的気相成長法(PVD)、化学的気相成長法(CVD)等を用いて導電膜230を形成する(図5(a)参照)。この導電膜230の上の所望の位置に、ポリシラザンなどの液体材料(絶縁性材料)を塗布し、ベーク・アニール処理(100 で5分程度、さらに350 で60分程度)を施し、さらにフォトエッチングを行うことにより、例えば膜厚0.5μm程度の第1絶縁膜(段差パターン)220を形成する(図5(b)参照)。この第1絶縁膜220は、導電膜230のスリットの形成予定位置ST0の略直上に、その端部eがくるように形成される。

#### [0023]

さらに、第1絶縁膜220が形成された基板210の全面に、ポリシラザンなどの液体材料(絶縁性材料)を塗布し、上記と同様のベーク・アニール処理を施すことにより、例えば膜厚0.3μm程度の第2絶縁膜240を形成する(図5(c)参照)。ここで、第1絶縁膜220を覆う部分の第2絶縁膜240の膜厚D5は他の部分の膜厚D6に較べて薄い。かかる膜厚差(D6-D5)によって生じる膜の収縮度合いの違いにより、第1絶縁膜220の端部eの直上に位置する第2絶縁膜240にスリットST1が形成される(図5(d)参照)。

## [0024]

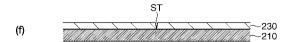

その後、エッチングを施すことで第1絶縁膜220にスリットST2を形成し(図5(e)参照)、さらにエッチングを施すことで導電性膜230の形成予定位置ST0にスリットSTを形成する(図5(f)参照)。その後、さらにエッチングを施すことにより、スリットSTの幅や深さを微調整する。このように導電性膜250の所望位置にスリットSTを形成することで、図4に示すような表面伝導型電子放出素子を形成しても良い。なお、以上説明したスリット形成方法を他の形態の表面伝導型電子放出素子に適用することも可能である。

#### [0025]

具体的には、まず、基板上に対向する一対の素子電極を形成し、前記基板上の前記素子電極間に挟まれた領域に端部を有する第1絶縁膜(段差パターン)を形成する。そして、少なくとも前記第1絶縁膜を覆うとともに、前記各素子電極の一部をそれぞれ覆うように、導電膜形成用の液体材料を塗布する。さらに、塗布した液体材料を乾燥・焼成等することにより、導電膜を形成するとともに、当該導電膜における前記段差パターンの端部に対応する位置にスリットを形成することで、表面伝導型電子放出素子を形成しても良い。

### [0026]

D.第3実施形態

40

30

20

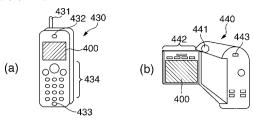

図6は、第3実施形態に係る電子デバイスを例示した図である。

図6(a)は、本発明の製造方法によって製造される携帯電話であり、当該携帯電話430は、電気光学装置(表示パネル)400、アンテナ部431、音声出力部432、音声入力部433及び操作部434を備えている。本発明は、例えば表示パネル400を構成する複数の電子放出素子の製造に適用される。図6(b)は、本発明の製造方法によって製造されるビデオカメラであり、当該ビデオカメラ440は、電気光学装置(表示パネル)400、受像部441、操作部442及び音声入力部443を備えている。本発明は、例えば表示パネル400を構成する複数の電子放出素子の製造に適用される。

#### [0027]

図6(c)は、本発明の製造方法によって製造される携帯型パーソナルコンピュータの例であり、当該コンピュータ450は、電気光学装置(表示パネル)400、カメラ部451及び操作部452を備えている。本発明は、例えば表示パネル400を構成する複数の電子放出素子の製造に適用される。

#### [0028]

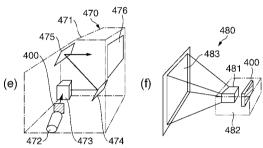

図6(d)は、本発明の製造方法によって製造されるヘッドマウントディスプレイの例であり、当該ヘッドマウントディスプレイ460は、電気光学装置(表示パネル)400、パンド部461及び光学系収納部462を備えている。本発明は、例えば表示パネル400を構成する複数の電子放出素子の製造に適用される。図6(e)は、本発明の製造方法によって製造されるリア型プロジェクターの例であり、当該プロジェクター470は、電気光学装置(光変調器)400、光源472、合成光学系473、ミラー374、375を筐体371内に備えている。本発明は、例えば光変調器400を構成する複数の電子放出素子の製造に適用される。図6(f)は本発明の製造方法によって製造されるフロント型プロジェクターの例であり、当該プロジェクター480は、電気光学装置(画像表示源)400及び光学系481を筐体482内に備え、画像をスクリーン483に表示可能になっている。本発明は、例えば画像表示源400を構成する複数の電子放出素子の製造に適用される。

## [0029]

上記例に限らず本発明は、あらゆる電子デバイスの製造等に適用可能である。例えば、表示機能付きファックス装置、デジタルカメラのファインダ、携帯型TV、DSP装置、PDA、電子手帳、電光掲示盤、宣伝公告用ディスプレイ、ICカードなどにも適用することができる。なお、本発明は上述した各実施形態に限定されることなく、本発明の要旨の範囲内で種々に変形、変更実施が可能である。

【図面の簡単な説明】

## [0030]

- 【図1】本発明の基本原理を説明するための図である。

- 【図2】本発明の基本原理を説明するための図で有る。

- 【図3】第1実施形態に係る電子放出素子の製造プロセスを示す工程図である。

- 【図4】同実施形態に係る電子放出素子の平面図である。

- 【図5】第2実施形態に係る導電性膜のスリット形成プロセスを示す工程図である。

- 【図6】第3実施形態に係る電子デバイスを例示した図である。

- 【図7】従来の電子放出素子の製造プロセスを示す工程図である。

#### 【符号の説明】

### [0031]

1 1 0 ・・・層間絶縁膜、 1 2 0 ・・・ゲート電極、 1 3 0 ・・・段差、 S T ・・・スリット、 2 1 0 ・・・基板、 2 2 0 ・・・第 1 絶縁膜、 2 3 0 ・・・導電膜、 2 4 0 ・・・第 2 絶縁膜、 2 3 1 、 2 3 2 ・・・素子電極、 2 6 0 ・・・電子放出部。

20

30

【図1】

【図2】

【図3】

【図4】

【図5】

【図7】

# 【図6】