## (19) **日本国特許庁(JP)**

# (12) 公 開 特 許 公 報(A)

(11)特許出願公開番号

特開2008-90451 (P2008-90451A)

(43) 公開日 平成20年4月17日(2008.4.17)

(51) Int. Cl.

FL

テーマコード (参考)

GO6F 12/16 (2006, 01) GO6F 12/16 320A 5B018

GO6F 12/16 320F

審査請求 未請求 請求項の数 5 〇L (全 19 頁)

(21) 出願番号 (22) 出願日

特願2006-268549 (P2006-268549) 平成18年9月29日 (2006.9.29)

(71) 出願人 000003078

株式会社東芝

東京都港区芝浦一丁目1番1号

(74)代理人 100058479

弁理士 鈴江 武彦

(74)代理人 100091351

弁理士 河野 哲

(74)代理人 100088683

弁理士 中村 誠

(74)代理人 100108855

弁理士 蔵田 昌俊

(74) 代理人 100075672

弁理士 峰 隆司

弁理士 福原 淑弘

(74)代理人 100109830

最終頁に続く

(54) 【発明の名称】記憶装置

## (57)【要約】

【課題】データ化けの発生を防止でき、信頼性を向上で きる記憶装置を提供する。

【解決手段】記憶装置は、複数のメモリセルMTを有す る半導体メモリ15と、データを一時的に保持するバッ ファ23と、前記バッファに保持されたデータのうち隣 接する複数のメモリセルに格納される所定のデータパタ ーンをチェックし、このチェック結果に応じてアドレス を送信するデータパターンチェック回路27と、送信さ れた前記アドレスのデータの値を補正して前記半導体メ モリに送信するデータ補正回路28とを備えるコントロ ーラ22とを具備する。

【選択図】 図 1

#### 【特許請求の範囲】

## 【請求項1】

複数のメモリセルを有する半導体メモリと、

データを一時的に保持するバッファと、前記バッファに保持されたデータのうち隣接する複数のメモリセルに格納される所定のデータパターンをチェックするデータパターンチェック回路と、このチェック結果に応じて所定のデータパターンと符合するアドレスのデータの値を補正して前記半導体メモリに送信するデータ補正回路とを備えるコントローラとを具備すること

を特徴とする記憶装置。

#### 【請求項2】

複数のメモリセルを有する半導体メモリと、

データを一時的に保持するバッファと、前記バッファに保持されたデータのうち隣接する複数のメモリセルに格納される所定のデータパターンをチェックするデータパターンチェック回路と、このチェック結果に応じて所定のデータパターンと符合するアドレスのデータの値のレベルをシフトして前記半導体メモリに送信するデータ補正回路とを備えるコントローラとを具備すること

を特徴とする記憶装置。

#### 【請求項3】

前記コントローラは、前記データ補正回路の出力信号に補正したデータのアドレスを付加して前記半導体メモリに送信するアドレス発生回路を更に備えること

を特徴とする請求項1または2に記載の記憶装置。

#### 【請求項4】

前記データ補正回路が補正するデータは、書き込み単位のデータ領域に格納され、前記 アドレス発生回路が付加するアドレスは、前記書き込み単位の冗長領域に格納されること を特徴とする請求項3に記載の記憶装置。

#### 【請求項5】

前記複数のメモリセルは、複数の第1、第2書き込み用配線の交差位置にマトリクス状に配置され、

前記所定のデータパターンは、前記第1書き込み用配線方向に沿った第1乃至第3メモリセルのデータパターンであって、前記第2メモリセルに隣接する前記第1、第3メモリセルのデータの値が前記第2メモリセルのデータと異なる値のデータであること

を特徴とする請求項1乃至4のいずれか1項に記載の記憶装置。

【発明の詳細な説明】

## 【技術分野】

# [0001]

この発明は、記憶装置に関し、例えば、フラッシュメモリを搭載したメモリカード等に 適用されるものである。

# 【背景技術】

#### [0002]

近年、その記憶容量の増大に伴って、不揮発性メモリの需要が増大している。しかし不揮発性メモリの記憶容量を増大するためには、高密度記録をする必要があるため、隣接するメモリセル間もますます狭くなる。そのため、メモリセルのデータは、周囲のデータ値の影響を受けて誤読み出しされるデータ化けが発生し、強力な誤り訂正符号(ECC:Error Correcting Code)を用いてもデータの復元が不可能となる。

## [0003]

例えば、1つのメモリセルに1ビットのデータを記録することが可能な2値NAND型フラッシュメモリの場合、メモリセルにデータ"0"を書き込むときにはフローティングゲート(FG)にキャリアを注入する。しかし、高密度記録をするために微細化が進むと、メモリセル間の距離が低減し、隣接するメモリセルのフローティングゲート(FG)間で発生する容量カップリングの値が増大する。ここで、メモリセルにデータ"0"を書き

10

20

30

00

40

込む際にフローティングゲート(FG)にキャリアを注入すると、隣接するメモリセルのフローティングゲートの電位が容量カップリングにより変化する。この電位の変化により、隣接したメモリセルに書き込まれたデータ"1"が、データ"0"として誤読み出されるデータ化けが発生し、データの復元が不可能となり、信頼性が低下するという問題がある。さらに、上記データ化けは、ビット線方向に隣接したメモリセルおよびワード線方向に隣接したメモリセルのいずれの場合であっても発生し得る。

[0004]

上記のように、従来の記憶装置は、データ化けが発生し、信頼性が低下するという問題があった。

[0005]

本願の文献公知発明としては、例えば、以下の特許文献1がある。上記特許文献1には、使用を重ねるにつれて必然的に発生するメモリセル等の劣化に起因するデータ化けによって多値記憶情報が失われても、効率よく且つ正確に誤り検出や誤り訂正を行うことを可能とする半導体記憶装置が記載されている。

【特許文献 1 】特開平 1 1 - 3 1 7 0 9 5 明細書

【発明の開示】

【発明が解決しようとする課題】

[0006]

この発明は、データ化けの発生を防止でき、信頼性を向上できる記憶装置を提供する。

【課題を解決するための手段】

[0007]

この発明の一態様によれば、複数のメモリセルを有する半導体メモリと、データを一時的に保持するバッファと、前記バッファに保持されたデータのうち隣接する複数のメモリセルに格納される所定のデータパターンをチェックするデータパターンチェック回路と、このチェック結果に応じて所定のデータパターンと符合するアドレスのデータの値を補正して前記半導体メモリに送信するデータ補正回路とを備えるコントローラとを具備する記憶装置を提供できる。

[00008]

この発明の一態様によれば、複数のメモリセルを有する半導体メモリと、データを一時的に保持するバッファと、前記バッファに保持されたデータのうち隣接する複数のメモリセルに格納される所定のデータパターンをチェックし、このチェック結果に応じてアドレスを送信するデータパターンチェック回路と、送信された前記アドレスのデータの値のレベルをシフトして前記半導体メモリに送信するデータ補正回路とを備えるコントローラとを具備する記憶装置を提供できる。

【発明の効果】

[0009]

この発明によれば、データ化けの発生を防止でき、信頼性を向上できる記憶装置が得られる。

【発明を実施するための最良の形態】

[0010]

以下、この発明の実施形態について図面を参照して説明する。尚、この説明においては、全図にわたり共通の部分には共通の参照符号を付す。

[0011]

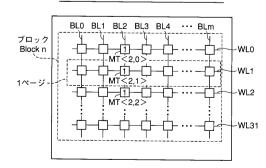

[第1の実施形態(ワード線方向の一例)]

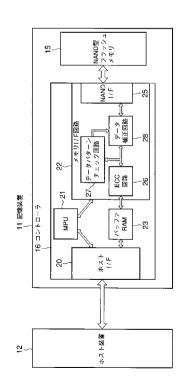

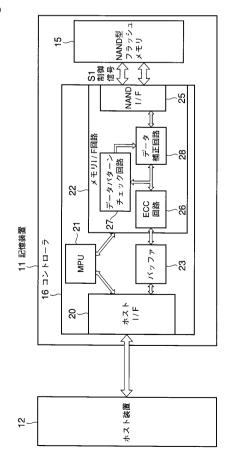

まず、図1乃至図3を用いて、この発明の第1の実施形態に係る記憶装置を説明する。図1は、この実施形態に係る記憶装置を説明するための平面図である。図2、図3は、図1中のNAND型フラッシュメモリを説明するための平面図である。

[0012]

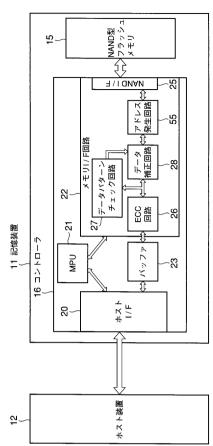

図示するように、記憶装置11は、ホストインターフェイス(以下、ホストI/F)2 0を介して、ホスト装置12とデータ等の送受信を行う。ここで、ホスト装置12は、例 10

20

30

40

えば、パーソナルコンピュータや携帯電話等である。

[0013]

記憶装置 1 1 は、コントローラ 1 6 および N A N D 型 フラッシュメモリ 1 5 を備えている。

[0014]

コントローラ 1 6 は、ホストI / F 2 0 、M P U 2 1 、メモリ I / F 回路 2 2 、および バッファ 2 3 を備えている。

[0015]

ホストI / F 2 0 を介して、データ等の送受信を行う。ホストI / F 2 0 は、例えば、N A N D インターフェイス等である。

[0016]

MPU21は、記憶装置11全体の制御を行う。

[0017]

バッファ R A M 2 3 は、ホスト装置 1 2 または N A N D 型フラッシュメモリ 1 5 に送受信されたデータ、アドレス、コマンド等を一時的に保持するように構成されている。

[0018]

メモリI / F回路 2 2 は、MPU 2 1 の制御に従い、送受信データに後述する補正を行って、NAND型フラッシュメモリ 1 5 にデータ等の送受信を行う。

[0019]

メモリI / F 回路 2 2 は、NANDI / F 2 5、E C C 回路 2 6、データパターンチェック回路 2 7、およびデータ補正回路 2 8 を備えている。

[0020]

NANDI/F25を介して、コントローラ16とNAND型フラッシュメモリ15と でデータ、アドレス、コマンド等の送受信を行う。

[0021]

ECC回路26は、バッファRAM23に送受信されるデータに誤り訂正符号(ECC: Error Correcting Code)を付加するように構成されている。

[0022]

データパターンチェック回路27は、ECC回路26に送受信されるデータパターンを チェックし、後述する所定のデータパターンにつきそのアドレスをデータ補正回路28に 送信してデータパターンをチェックするように構成されている。

[ 0 0 2 3 ]

データ補正回路28は、後述する書き込み動作の際に、データパターンチェック回路27から送信された所定のデータパターンのデータの値を反転してNANDI/F25に送信するように構成されている。

[0024]

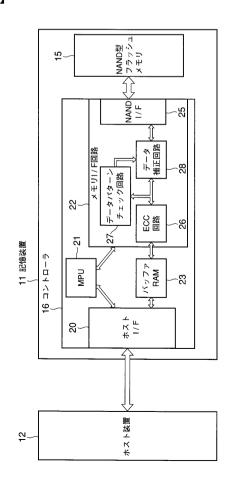

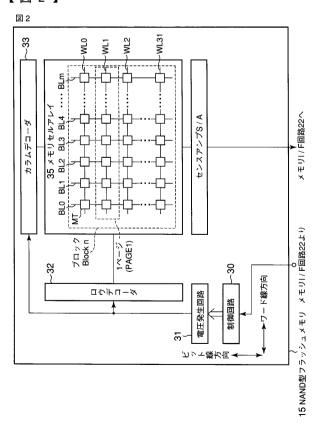

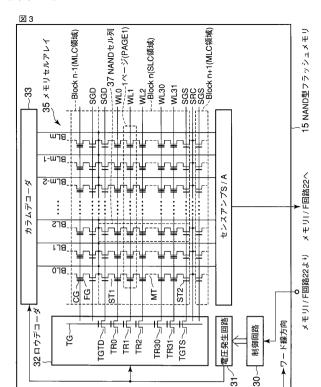

次に、本例のNAND型フラッシュメモリ15について、図2、図3を用いてさらに詳しく説明する。図示するように、NAND型フラッシュメモリ15は、制御回路30、電圧発生回路31、ロウデコーダ32、センスアンプS/A、カラムデコーダ33、メモリセルアレイ35を備えている。

[ 0 0 2 5 ]

制御回路30は、メモリI/F回路22の出力信号に従い、電圧発生回路31の電圧値とロウデコーダ32およびカラムデコーダ33の選択するアドレスを制御するように構成されている。

[0026]

電圧発生回路31は、制御回路30の制御に従い、書込み電圧、消去電圧、読み出し電圧等の所定の値の電圧を発生するように構成されている。

[0027]

ロウデコーダ 3 2 は、メモリコントローラ 1 6 から指定されたアドレスに従い、ワード線WL0~WL31、選択セレクトゲート線SGD、SGSを選択するように構成されて

10

20

30

40

10

20

30

40

50

いる。図 3 に示すように、ロウデコーダ 3 2 は、転送ゲート線 T G にゲートが共通接続されたトランスファゲートトランジスタ T G T D、 T G T S、 転送トランジスタ ( 高電圧系トランジスタ ) T R O ~ T R 3 1 を備えている。

[0028]

転送トランジスタTR0~TR31は、メモリセルトランジスタMTの制御電極CGに 、消去電圧、書き込み電圧等の所定の電圧を印加する。

[0029]

センスアンプS/Aは、ビット線BL0~BL mから読み出されたページごとのデータを増幅し、メモリI/F回路22に送信するように構成されている。

[0030]

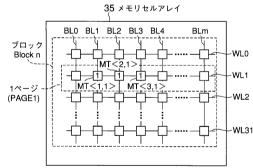

メモリセルアレイ 3 5 は、複数のブロック (Block n-1, Block n, Block n+1,...)を備えている。

[0031]

本例では、NAND型フラッシュメモリ15は、1つのメモリセルトランジスタMTに 1 ビットのデータを記録することが可能な 2 値 NAND型フラッシュメモリである。

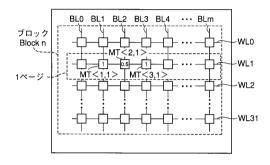

[0032]

図示するように、ブロックBlock nは、ワード線WL0~WL31とビット線BL0~BLmとの交差位置にマトリクス状に配置された複数のメモリセルトランジスタMT0~MTmを備えている。

[0033]

メモリセルトランジスタMT0~MT mのそれぞれは、半導体基板上に設けられたトンネル絶縁膜、トンネル絶縁膜上に設けられた浮遊電極FG、浮遊電極FG上に設けられたゲート間絶縁膜、ゲート間絶縁膜上に設けられた制御電極CGを備えた積層構造である。ビット線BL方向に沿って隣接するメモリセルトランジスタMTは、電流経路であるソース/ドレインを共有し、それぞれの電流経路の一端および他端が直列に、本例では、32個接続するように配置されている。

[0034]

電流経路の一端および他端が直列に接続されたメモリセルトランジスタMTおよび選択トランジスタS1、S2は、NANDセル列37を構成している。選択トランジスタST1、ST2により、このNANDセル列37を選択する。NANDセル列37の電流経路の一端はセンスアンプS/Aに接続され、電流経路の他端はソース線SRCに接続されている。

[0035]

尚、メモリセルトランジスタMTの個数は、本例の32個に限らず、例えば、8個、16個等であっても良い。また、選択トランジスタST1、ST2は、NANDセル列37を選択できる構成であれば、選択トランジスタST1、ST2のいずれか一方のみが設けられていても良い。

[0036]

各ワード線WL方向(ロウ方向)のメモリセルトランジスタMT0~MT mの制御電極CGは、ワード線WL0~WL31のいずれかに共通接続されている。選択トランジスタST1のゲートはセレクトゲートSGSに共通接続され、選択トランジスタST2のゲートはセレクトゲートSGDに共通接続されている。選択トランジスタS1のソースは、ソース線SRCに接続され、選択トランジスタST2のドレインは、ビット線BL0~BLmのいずれかに接続されている。

[0037]

また、ワード線WL0~WL31ごとに、1または複数のページアドレスが割り当てられている。ここでは、説明の便宜上、1本のワード線に対して1つのページアドレスが割り当てられている場合について説明する。図3の破線内で示すように、ワード線WL0~WL31ごとに1ページ(PAGE)が存在する。例えば、ワード線WL1には、ページPAGE 1が存在する。このページは、データの書き込みおよび読み出し単位である。消去動作は

(6)

、ブロックBlock単位で一括して行われる。

## [0038]

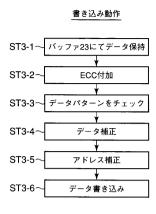

## < 書き込み動作 >

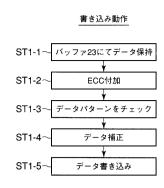

次に、本例に係る記憶装置の書き込み動作について、図4のフロー図に則して説明する。この説明では、ブロックBlock nのページPAGE 1 にデータを書き込む場合を一例に挙げて説明する。

#### [0039]

(ステップST1-1(バッファにてデータ保持))

まず、MPU21は、ホストI/F20を介してホスト装置12から送信された書き込みページデータ、アドレス、コマンド等をバッファRAM23上に展開し、一時的に保持する。

# [0040]

(ステップST1-2(ECC付加))

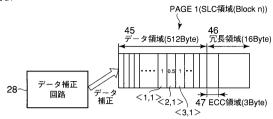

続いて、ECC回路26は、上記RAM23上で展開されたデータに誤り訂正符号(ECC)を付加する。この際、図5等に図示するように、この誤り訂正符号は、書き込みページデータのうちの冗長領域46の一部であるECC領域47に付加される。

## [0041]

尚、本例では、データの補正(後述のステップST1-3およびST1-4)の前に上記誤り訂正符合を付加している。しかし、上記誤り訂正符号は、データの補正(後述のステップST1-3およびST1-4)の後に付加することも可能である。

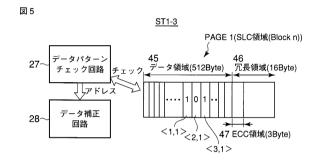

#### [0042]

続いて、図 5 に示すように、データパターンチェック回路 2 7 は、 R A M 2 3 上に展開された 1 ページデータ(PAGE 1 )のうち、データ化けが発生し得る所定のデータパターンが存在するか否かについて判定する。

## [0043]

例えば、データパターンチェック回路 2 7 は、 1 ページデータのデータ領域 4 5 中のアドレス位置 < 1 , 1 > ( < a , b > : a はワード線WL方向、 b はビット線 B L 方向)、位置 < 2 , 1 > 、および位置 < 3 , 1 > のデータの値がそれぞれ " 1 " 、 " 0 " 、 " 1 " である場合、このデータパターンをデータ化けが発生し得るデータパターンとして判定する。そして、データパターンチェック回路 2 7 は、データの値が " 0 " であるアドレス位置 < 2 , 1 > をデータ補正回路 2 8 に送信する。

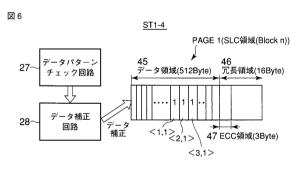

#### [0044]

(ステップST1 - 4 (データ補正))

続いて、データ補正回路28は、データパターンチェック回路27から送信されたアドレス位置のデータの値を反転して、NAND型フラッシュメモリ15に転送する。

#### [0045]

例えば、図 6 に示すように、データ補正回路 2 8 は、データパターンチェック回路 2 7 から送信されたアドレス位置 < 2 , 1 > のデータの値 " 0 "を反転して、データの値を " 1 "として N A N D 型フラッシュメモリ 1 5 に転送する。

# [0046]

(ステップST1-5(データ書き込み))

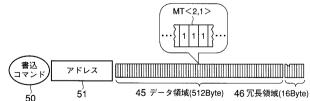

続いて、MPU21は、NANDI/F25を介して、補正後のデータに従ってページデータ(PAGE1)の書き込みデータをNAND型フラッシュメモリ15に送信する。この際のコマンドシーケンスは、例えば、図7のように示される。

# [0047]

図示するように、MPU21は、順次、書き込みコマンド50、書き込みアドレス51、およびデータ領域45と冗長領域46からなる書き込みデータを、NAND型フラッシュメモリ15に送信する。この際、上記のように、例えば、データ領域45のアドレス位置<2,1>のデータは、"1"データとして反転されている。

10

20

30

50

40

[0048]

続いて、データ補正回路 2 8 は、補正後のデータに従ってページデータ(PAGE 1 )のデータを書き込むように、制御回路 3 0 を制御する。その結果、制御回路 3 0 は、データ補正回路 2 8 に従い、電源発生回路 3 1 から発生する書き込み電圧によりキャリアを注入し、ロウデコーダ 3 2 およびカラムデコーダ 3 3 のアドレスを選択するように制御し、ページデータの書き込みを行う。

[0049]

例えば、図 8 に示すように、メモリセルアレイ 3 5 中におけるメモリセルトランジスタ M T < 2 , 1 > には反転された " 1 " データを書き込むため、キャリアを注入しない。その結果、メモリセルトランジスタ M T < 1 , 1 > 、M T < 2 , 1 > 、および M T < 3 , 1 > には、それぞれ " 1 " データ、 " 1 " データ、 " 1 " データを書き込む。

[0050]

以後、上記ステップST1-1~ST1-5をNAND型フラッシュメモリ15の全ページについて繰り返し、書き込み動作を行う。

[0051]

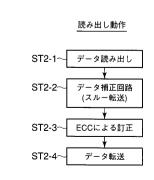

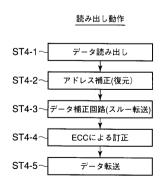

< 読み出し動作 >

次に、本例に係る記憶装置の読み出し動作について、図9のフロー図に則して説明する。この説明では、同様にブロックBlock nのページPAGE1のデータを読み出す場合を一例に挙げて説明する。

[0052]

(ステップST2-1(データ読み出し))

まず、NAND型フラッシュメモリ15中の制御回路30は、電源発生回路31から発生する書き込み電圧、ロウデコーダ32およびカラムデコーダ33のアドレス等を制御し、ページデータ(PAGE1)の読み出しを行う。続いて、制御回路30は、読み出したデータをセンスアンプS/Aにより増幅し、コントローラ16に送信する。

[0053]

(ステップST2-2(スルー転送))

続いて、データ補正回路28は、NANDI/F25を介して送信された読み出しデータをECC回路26に送信する。

[0054]

(ステップST2-3(ECCによる訂正))

続いて、ECC回路26は、誤り訂正符号(ECC)を用いて、読み出されたページデータの誤り訂正を行う。具体的には、ECC回路26は、メモリ15から読み出した誤り訂正符号と、データ領域のデータから新たに生成した誤り訂正符号とに基づいて、ページデータ中のエラービットを検出し、これを訂正する。

[0055]

(ステップST2-4(データ転送))

続いて、MPU21は、ホストI/F20を介して、読み出しデータをホスト装置12に送信する。

[0056]

以後、上記ステップST2-1~ST2-4をNAND型フラッシュメモリ15の全ページについて繰り返し、読み出し動作を行う。

[0057]

上記に説明したように、この実施形態に係る記憶装置によれば、下記(1)乃至(3)の効果が得られる。

[0058]

(1)データ化けの発生を防止でき、信頼性を向上できる。

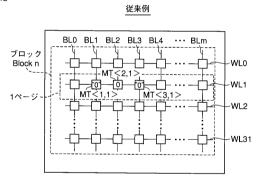

[0059]

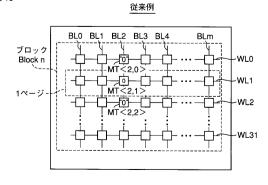

従来の場合には、上記のようなデータパターンチェックやデータ補正を行うことがない。そのため、図11に示すように、例えば、メモリセルMT<2,1>にデータ" 0 "を

10

20

30

40

書き込むときは、フローティングゲート F G にキャリアを注入する。しかし、この際、図12に示すように、微細化による容量カップリングにより、メモリセル M T < 1 , 1 > 、M T < 3 , 1 > に書き込まれたデータ "1"が、データ "0"として誤読み出されるデータ化けが発生し、データの復元が不可能となり、信頼性が低下する。

[0060]

一方、本例に係る記憶装置11は、データパターンチェック回路27およびデータ補正回路28を備えている。そのため、データパターンチェック回路27は、書き込み動作の際に、データ化けが発生し得る所定のデータパターンが存在するか否かについて判定できる。例えば、データパターンチェック回路27は、1ページデータのデータ領域45中のアドレス位置<1,1>、位置<2,1>、および位置<3,1>のデータがそれぞれ"1"、"0"、"1"である場合、データ化けが発生し得るデータパターンとしてデータ補正回路28は、データパターンチェック回路27から送信されたアドレス位置のデータの値を反転してするように補正して、NAND型フラッシュメモリ15に転送できる。例えば、データ補正回路28は、データパターンチェック回路27から送信されたアドレス位置<2,1>の"0"データの値を反転して、"1"データとしてNAND型フラッシュメモリ15に転送する(ステップST1-4)。

[0061]

このように、データ化けが発生し得る所定のデータパターンを書き込み動作の前にあらかじめ回避できるため、データ化けの発生を防止でき、信頼性を向上することができる。

[0062]

(2) 微細化および高密度化に対して有利である。

[0063]

容量カップリングは微細化および高密度化が進み、隣接メモリセルMT間の距離が低減するほど大きくなるところ、上記(1)のように、本例によれば、容量カップリングによるデータ化けの発生を防止することができる。

[0064]

そのため、NAND型フラッシュメモリ15の微細化および高密度化に対して有利である。

[0065]

(3)訂正箇所を低減でき、データの複合性を向上できる。

[0066]

従来、例えば、図11および図12に示すように、容量カップリングにより、メモリセルMT<1,1>、MT<3,1>についてデータ化けが発生する。そのため、このデータ化けを防止するために、誤り訂正符号ECCを付加する場合には、例えば、メモリセルMT<1,1>、MT<3,1>の2箇所のそれぞれについて誤り訂正符号ECCを付加し、読み出しの際にこれらのデータを復元する必要がある。

[0067]

一方、本例に係るデータ補正回路28は、反転されたデータの補正を行うことができる。例えば、データ補正回路28は、アドレス位置<2,1>の"1"データを反転して、"0"データとして元の値にデータを復元する。このように、本例では読み出し動作の際に、例えば、アドレス位置<2,1>の1箇所についてのみデータを復元すれば良いため、復元箇所を低減でき、データの複合性を向上できる。

[0068]

尚、上記第1の実施形態では、1本のワード線WLに1つのページアドレスが割り当てられた場合、つまり、ワード線WL方向に隣接するメモリセルトランジスタMTに同一のページアドレスが割り当てられた場合について説明した。しかし、ワード線WL方向に隣接するメモリセルトランジスタMTに異なるページアドレスが割り当てられた場合であっても、上記同様の効果(1)乃至(3)が得られる。この場合には、データパターンチェック回路27が、ワード線WL方向に隣接するメモリセルトランジスタMTに割り当てられた異なるページアドレスのデータパターンを参照し、データを反転するか否かを決定す

10

20

30

40

る。

[0069]

また、本例では、NAND型フラッシュメモリ15として、2値NAND型フラッシュメモリを一例に挙げて説明した。しかし、NAND型フラッシュメモリ15は、これに限らず、例えば、1つのメモリセルトランジスタMTに多ビットのデータを記録することが可能な多値NAND型フラッシュメモリにも適用することが可能である。

[0070]

[変形例(ビット線方向の一例)]

次に、変形例に係る記憶装置について、図13を用いて説明する。この実施形態は、ビット線BL方向のデータ化けを防止する場合の一例に関するものである。この説明において、上記第1の実施形態と重複する部分の詳細な説明を省略する。

[0071]

上記容量カップカップリングによるデータ化けの発生は、上記第1の実施形態に示した ワード線WL方向に限らず、ビット線BL方向においても同様に発生し得る。そのため、 下記のような変形を行うことが可能である。

[ 0 0 7 2 ]

上記書き込み動作の際のステップST1-3において、データパターンチェック回路2 7は、RAM23上に展開された複数のページデータのうち、データ化けが発生し得るビット線BL方向の所定のデータパターンが存在するか否かについてチェックする。

[0073]

例えば、データパターンチェック回路 2 7 は、ページデータのアドレス位置 < 2 , 0 > 、位置 < 2 , 1 > 、および位置 < 2 , 2 > のデータがそれぞれ " 1 " 、 " 0 " 、 " 1 " である場合、データ化けが発生し得るデータパターンとして、アドレス位置 < 2 , 1 > をデータ補正回路 2 8 に送信する。

[0074]

続いて、データ補正回路28は、データパターンチェック回路27から送信されたアドレス位置のデータを反転して、NAND型フラッシュメモリ15に転送する。

[0075]

例えば、図13に示すように、データ補正回路28は、データパターンチェック回路2 7から送信されたアドレス位置<2,1>の"0"データを反転して"1"データとして 書き込むようにNAND型フラッシュメモリ15に転送する。

[0076]

続いて、制御回路30は、データ補正回路28に従い、電源発生回路31から発生する書き込み電圧によりキャリアを注入し、ロウデコーダ32およびカラムデコーダ33のアドレスを選択するように制御し、ページデータの書き込みを行う。

[0077]

そのため、例えば、図13に示すように、メモリセルアレイ35中におけるメモリセルトランジスタMT<2,1>には反転された"1"データを書き込むため、キャリアを注入しない。その結果、ビット線BL2に沿ったメモリセルトランジスタMT<2,0>、MT<2,1>、およびMT<3,1>には、それぞれ"1"データ、"1"データ、"

[0078]

以後、実質的に同様な上記ステップをNAND型フラッシュメモリ15の全ページについて繰り返し、書き込み動作を行う。

[0079]

また、読み出し動作については下記のようにデータ復元を行う。まず、上記ステップST2-2にて、読み出しデータをECC回路26に送信する。続いて、ステップST2-3にて、ECC回路26により、受信されたデータを誤り訂正符号(ECC)に基づき、誤り訂正をする。

[0800]

10

20

30

40

以後、実質的に同様な上記ステップをNAND型フラッシュメモリ15の全ページについて繰り返し、読み出し動作を行う。

#### [ 0 0 8 1 ]

上記のように、この実施形態に係る記憶装置によれば、上記(1)乃至(3)と同様の 効果が得られる。

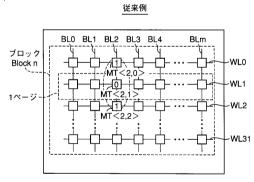

# [0082]

ここで、従来の場合には、上記のようなデータパターンチェックやデータ補正を行うことがない。そのため、図14に示すように、例えば、メモリセルMT<2,1>にデータ "0"を書き込むためのフローティングゲートFGにキャリアを注入する際の容量カップリングにより、メモリセルMT<2,0>、MT<2,2>の電位が変化する。そのため、図15に示すように、メモリセルMT<2,0>、MT<2,2>に書き込まれたデータ "1"が、データ "0"として誤読み出されるデータ化けが発生し、データの復元が不可能となり、信頼性が低下する。

## [0083]

一方、本例によれば、上記書き込み動作の際のステップST1-3において、データパターンチェック回路27は、RAM23上に展開された複数のページデータのうち、データ化けが発生し得るビット線BL方向の所定のデータパターンが存在するか否かについてチェックする。続いて、データ補正回路28は、データパターンチェック回路27から送信されたアドレス位置のデータを反転して、NAND型フラッシュメモリ15を書き込むことができる。

#### [0084]

このように、本例によれば、ビット線BL方向のデータ化けが発生し得る所定のデータパターンを書き込み動作前に回避できることで、ビット線BL方向のデータ化けの発生を防止でき、信頼性を向上できる点で有利である。

#### [0085]

[第2の実施形態(アドレス情報を付加する一例)]

次に、第2の実施形態に係る記憶装置について、図16を用いて説明する。この実施形態は、アドレス情報を付加するアドレス発生回路を更に備える一例に関するものである。この説明において、上記第1の実施形態と重複する部分の詳細な説明を省略する。

#### [ 0 0 8 6 ]

図示するように、本例に係る記憶装置11は、アドレス発生回路55を更に備えている点で上記第1の実施形態と相違している。

#### [0087]

アドレス発生回路 5 5 は、書き込みおよび読み出し動作の際に、補正したデータのアドレスを付加するように構成されている。

## [0088]

#### < 書き込み動作>

本例に係る書き込み動作について、図17のフロー図に則して説明する。この説明では、ワード線WL方向のデータをチェックする場合を一例として説明する。まず、第1の実施形態と同様のステップST3-1~ST3-4を行う。

# [0089]

(ステップST3-5(アドレス補正))

続いて、アドレス補正回路 5 5 は、データ補正回路 2 8 から送信された書き込みデータのうち補正したデータのアドレスを付加する。このステップ S T 3 - 4 のコマンドシーケンスは、図 1 8 のように示される。

# [0090]

図示するように、MPU21は、書き込みコマンド50、書き込みアドレス51、およびデータ領域45と冗長領域46からなる書き込みデータを、順次NAND型フラッシュメモリ15に送信する。この際、例えば、データ領域45のアドレス位置<2,1>のデータは、"1"データとして反転されているに加え、冗長領域46に補正したデータのア

10

20

30

40

ドレス位置 < 2 , 1 > が更に書き込まれている。

## [0091]

以後、上記第1の実施形態と同様のステップST3-6を行い、本例の書き込み動作を 行う。

## [0092]

< 読み出し動作 >

本例に係る書き込み動作について、図19のフロー図に則して説明する。まず、第1の 実施形態と同様のステップST4-1を行う。

## [0093]

(ステップST4-2(アドレス補正)、ステップST4-3(スルー転送)) 続いて、データ補正回路28は、アドレス発生回路55から送信された補正したデータ のアドレスをもとにデータを補正(復元)し、データを転送する。

## [0094]

以後、上記第1の実施形態と同様のステップST4-3~ST4-5を行い、本例の読み出し動作を行う。

#### [0095]

上記のように、この実施形態に係る記憶装置によれば、上記(1)乃至(3)と同様の効果が得られる。

#### [0096]

さらに、本例に係る記憶装置11は、アドレス発生回路55を更に備えている。そのため、アドレス発生回路55は、書き込み動作の際に、データ化けが発生し得るメモリセルトランジスタのアドレスを付加することができる(ステップST3-5)。さらに、読み出し動作の際に、データ補正回路28は、アドレス発生回路55から送信された補正したデータのアドレスをもとにデータを補正(復元)することができる。(ステップST4-2、ST4-3)。

## [0097]

そのため、データ化けが発生し得るアドレス情報をECC回路26に送信することで、 読み出し時にデータ化けが発生し得るデータ箇所を特定でき、ECCの復号性を向上でき る点で有利である。ECC回路26にはデータ化けが発生し得るアドレス情報が送信され ず、どのアドレスのデータに誤訂正符合を付加すべきか判定することができないからであ る。

# [0098]

この様に、エラー位置を示すアドレスが与えられれば訂正能力が増すECCの例として 、例えば、リードソロモン符号の消失訂正復号方式等がある。

## [0099]

[第3の実施形態(データ化けの発生を防止し得る書き込みレベルにシフトする一例)]次に、第3の実施形態に係る記憶装置について、図20を用いて説明する。この実施形態は、データ化けの発生を防止し得る書き込みレベルにシフトするようにデータ補正を行う一例に関するものである。この説明において、上記第1の実施形態と重複する部分の詳細な説明を省略する。

# [ 0 1 0 0 ]

図示するように、本例に係るデータ補正回路28は、書き込み動作の際に、データ化けの発生を防止し得る書き込みレベルにシフトさせるような制御信号S1を制御回路30に送信するように構成されている点で上記第1の実施形態と相違している。

#### [ 0 1 0 1 ]

## <書き込み動作>

本例に係る読み出し動作は、以下の点で上記第1の実施形態と相違している。まず、上記ステップST1-4の際に、データ補正回路28は、データパターンチェック回路27から送信されたアドレス位置のデータを完全に反転せず、データ化けの発生を防止し得る書き込みレベルにシフトするようにデータを補正する制御信号S1をNAND型フラッシ

10

20

30

40

ュメモリ15に送信する。

## [0102]

本例の場合、例えば、図21に示すように、データ補正回路28は、データパターンチェック回路27から送信されたアドレス位置<2,1>の"消去"データを、データ化けの発生を防止し得る書き込み電圧"半書込"レベル(半値レベル)にシフトさせるようにデータを補正するように制御信号S1を送信する。

#### [ 0 1 0 3 ]

続いて、上記ステップST1-5の際に、上記制御信号S1を受けた制御回路30は、この制御信号S1に従い、電源発生回路31から発生する書き込み電圧レベルをシフトさせ、ロウデコーダ32およびカラムデコーダ33のアドレスを選択するように制御し、ページデータの書き込みを行う。

[0104]

そのため、本例の場合、例えば、図22に示すように、メモリセルアレイ35中におけるメモリセルトランジスタMT<2,1>には、シフトさせた"半書込"データを書き込む。その結果、メモリセルトランジスタMT<1,1>、MT<2,1>、およびMT<3,1>には、それぞれ"書込"データ、"半書込"データ、"書込"データを書き込む

[0105]

以後、上記第1の実施形態と同様のステップを行い、本例の読み出し動作を行う。

[0106]

< 読み出し動作 >

本例に係る読み出し動作は、以下の点で上記第1の実施形態と相違している。まず、上記ステップST2-2の際に、データ補正回路28は、NAND型フラッシュメモリ15から送信された読み出しデータのうち、電圧値をシフトするように補正したデータを元の値に復元する。

[0107]

本例の場合、例えば、データ補正回路 2 8 は、N A N D 型フラッシュメモリ 1 5 から送信されたアドレス位置 < 2 , 1 > の"半書込"データを、元の値の"消去"レベルに復元する。

[0108]

他方、メモリセルトランジスタMT<1,1>、およびMT<3,1>は、それぞれ" 1書込"データ、"1書込"データが安定して読み出せることになる。

[0109]

以後、上記第1の実施形態と同様のステップを行い、本例の読み出し動作を行う。

[0110]

上記のように、この実施形態に係る記憶装置によれば、上記(1)乃至(3)と同様の効果が得られる。

[0111]

さらに、本例によれば、データ補正回路 2 8 は、データパターンチェック回路 2 7 から送信されたアドレス位置のデータを完全に反転せず、データ化けの発生を防止し得る書き込みレベル(半値レベル)にシフトするようにデータを補正する制御信号 S 1 を N A N D 型フラッシュメモリ 1 5 に送信する。続いて、上記制御信号 S 1 を受けた制御回路 3 0 は、この制御信号 S 1 に従い、電源発生回路 3 1 から発生する書き込み電圧レベルをシフトさせてページデータの書き込みを行うことができる。

[ 0 1 1 2 ]

このように、本例によれば、完全にデータを反転しないで書き込みレベルをシフトさせた方が総合的にデータ化けを防止できる場合に有効である。

[0113]

尚、上記実施形態および変形例においては、データを"消去"から"書込"に反転する場合、または"消去"から"半書込"にシフトさせる場合をデータ補正の一例として説明

10

20

30

40

した。しかし、データ補正は、上記の例に限られず、データの書込みにより、周囲のメモリセルトランジスタMTにデータ化けが発生し得る場合は、データ化けの発生を防止できるように(例えば、書き込みデータを"書込"から"消去"等のように)データを補正する限り、上記と同様の効果を得ることが可能である。

[0114]

例えば、上記ステップST1-3(データパターンをチェック)の際に、アドレス位置 < 1 , 1 > 、位置 < 2 , 1 > 、および位置 < 3 , 1 > のデータがそれぞれ " 消去 " 、 " 書 込 " 、 " 消去 " である場合を一例に挙げる。この場合、続いて、メモリセルトランジスタ M T < 2 , 1 > のフローティングゲートFGにキャリアを注入すると、隣接するメモリセルトランジスタ M T < 1 , 1 > 、 M T < 3 , 1 > のデータが " 書込 " から " 消去 " に誤読み出しされるデータ化けが発生するとする。このような場合には、続くステップST1-4 の際に、データ補正回路 2 8 は、メモリセルトランジスタ M T < 2 , 1 > に " 1 " から " 0 " にデータを反転させるように書き込み動作を行うことも可能である。

[0115]

また、上記説明においては、SLC領域であるブロックBlock nを一例として説明した。しかし、多ビットのデータを記録することが可能なMLC領域として構成された多値NAND型フラッシュメモリである他のブロックBlock n-1, Block n+1であっても同様に適用でき、同様の効果を得ることができる。

[0116]

さらに、上記説明においては、ビット線BL方向またはワード線WL方向のいずれか一方の方向についてデータパターンをチェックし、データ補正を行う場合を一例として示した。しかし、ビット線BL方向およびワード線WL方向のいずれの方向についても、データパターンを考慮し、データ補正を行っても良い。

[ 0 1 1 7 ]

以上、第1乃至第3の実施形態および変形例を用いて本発明の説明を行ったが、この発明は上記各実施形態および変形例に限定されるものではなく、実施段階ではその要旨を逸脱しない範囲で種々に変形することが可能である。また、上記各実施形態および変形例には種々の段階の発明が含まれており、開示される複数の構成要件の適宜な組み合わせにより種々の発明が抽出され得る。例えば各実施形態および変形例に示される全構成要件からいくつかの構成要件が削除されても、発明が解決しようとする課題の欄で述べた課題の少なくとも1つが解決でき、発明の効果の欄で述べられている効果の少なくとも1つが得られる場合には、この構成要件が削除された構成が発明として抽出され得る。

【図面の簡単な説明】

[0118]

- 【図1】この発明の第1の実施形態に係る記憶装置を説明するための平面図。

- 【図2】図1中のNAND型フラッシュメモリを示すブロック図。

- 【 図 3 】 図 1 中 の N A N D 型 フ ラ ッ シ ュ メ モ リ を 示 す 回 路 図 。

- 【図4】第1の実施形態に係る記憶装置の書き込み動作を示すフロー図。

- 【図5】第1の実施形態に係る記憶装置の一書き込みステップ(ST1-3)を示す図。

- 【図6】第1の実施形態に係る記憶装置の一書き込みステップ(ST1-4)を示す図。

- 【 図 7 】 第 1 の 実 施 形 態 に 係 る 記 憶 装 置 の 一 書 き 込 み ス テ ッ プ の 書 き 込 み シ ー ケ ン ス を 示 す 図 。

- 【 図 8 】 第 1 の実 施 形 態 に 係 る 書 き 込 み 動 作 後 の メ モ リ セ ル ア レ イ を 示 す 図 。

- 【図9】第1の実施形態に係る記憶装置の読み出し動作を示すフロー図。

- 【図10】第1の実施形態に係る記憶装置の一読み出しステップ(ST2-2)を示す図

【図11】従来例に係る書き込み動作後のメモリセルアレイを示す図。

【図 1 2 】従来例に係るビット線方向のデータ化けを発生する記憶装置を説明するための図。

【図13】この発明の変形例に係る書き込み動作後のメモリセルアレイを示す図。

10

20

30

- -

40

- 【図14】従来例に係る書き込み動作後のメモリセルアレイを示す図。

- 【図 1 5 】従来例に係るワード線方向のデータ化けを発生する記憶装置を説明するための図。

- 【図16】この発明の第2の実施形態に係る記憶装置を示す平面図。

- 【図17】第2の実施形態に係る記憶装置の書き込み動作を示すフロー図。

- 【図18】第2の実施形態に係る記憶装置の一書き込みステップの書き込みシーケンスを示す図。

- 【図19】第2の実施形態に係る記憶装置の読み出し動作を示すフロー図。

- 【図20】この発明の第3の実施形態に係る記憶装置を示す平面図。

- 【図21】第3の実施形態に係る一書き込みステップを示す図。

- 【図22】第3の実施形態に係る書き込み動作後のメモリセルアレイを示す図。

【符号の説明】

[0119]

1 1 … 記憶装置、 1 2 … ホスト装置、 1 5 … N A N D 型フラッシュメモリ、 1 6 … コントローラ、 2 0 … ホストI / F、 2 1 … M P U、 2 2 … メモリI / F回路、 2 3 … バッファR A M、 2 5 … N A N D I / F、 2 6 … E C C 回路、 2 7 … データパターンチェック回路、 2 8 … データ補正回路。

# 【図1】

図 1

# 【図2】

# 【図3】

## 【図4】

図 4

# 【図5】

# 【図6】

ビット繰行回 ◀

# 【図8】

# 図 8 本例に係る書き込み後のメモリセルアレイ

# 【図7】

# 【図9】

図 9

# 【図10】

# 図 10 ST2-2 PAGE 1(SLC領域(Block n)) 45 データ領域(512Byte) 元長領域(16Byte) フライ語 データ補正 回路 ボータ 横正(復元) マース オア ECC領域(3Byte) マース ストライ語 マース ストライ語 マース オア ECC領域(3Byte) マース ストライ語 スト

# 【図11】

# 【図12】

図 12

# 【図14】

図 14

# 【図13】

図 13

# 変形例に係る書き込み後のメモリセルアレイ

# 【図15】

図 15

# 【図16】

図 16

# 【図17】

図 17

# 【図18】

図 18

# 【図20】

図 20

# 【図19】

図 19

# 【図21】

図 21

# 【図22】

図 22

## 本例に係る書き込み後のメモリセルアレイ

# フロントページの続き

(74)代理人 100084618

弁理士 村松 貞男

(74)代理人 100092196

弁理士 橋本 良郎

(72)発明者 助川 博

東京都港区芝浦一丁目1番1号 株式会社東芝内

F ターム(参考) 5B018 GA02 GA04 HA14 HA40 MA24 NA06